DXP的铺铜层间距修改,不影响各层布线

ProtelDXP布局布线规则设置方法

ProtelDXP布局布线规则设置方法设计PCB及设置PCB工作区现在我们可以开始在PCB上放置元件并在板上布线。

在将元件定位在板子上之前,我们需要设置PCB工作区,如栅格、层和设计规则。

让我们设置一些选项,这样可以使定位元件更容易些。

从菜单选择Tools ? Preferences(热键T,P)打开System Preferences 对话框。

在Options标签的Editing Options单元,确认Snap to Center选项被选中。

这会使你在抓住一个元件定位时,光标就会定位在元件的参考点上。

点击System Preferences 对话框中Display标签其为当前。

在Show单元,将Show Pad Nets、Show Pad Numbers 和 Via Nets 选项取消选择。

在Draft Thresholds单元,将Strings栏设为4 pixels,然后关闭对话框。

设置栅格在开始定位元件之前,我们需要确认放置栅格设置正确。

放置在PCB工作区的所有对象均排列在称为捕获栅格(snap grid )上。

这个栅格需要设置得适合我们要使用的布线技术。

我们的教程电路用的是标准英制元件,其最小引脚间距为100mil。

我们将这个捕获栅格设定为100mil的一个平均分数,50或25mil,这样所有的元件引脚在放置时均将落在栅格点一。

当然,板子上的导线宽度和间距分别是12mil和13mil(这是PCB板向导使用的默认值),在平行的导线的中心之间允许最小为25mil。

所以最合适的捕获栅格应设为25mil。

完成以下步骤设置捕获栅格:从菜单选择Design ? Options(热键D,O)打开Board Options 对话框。

在Grids标签,将对话框中的Snap X、Snap Y、ComponentX 和 Component Y 栏的值设为25mil。

注意这个对话框也用来定义电气栅格。

电气栅格在你放置一个电气对象时工作,它将忽略捕获栅格而同时捕获电气对象。

Protel_DXP2004_覆铜高级规则

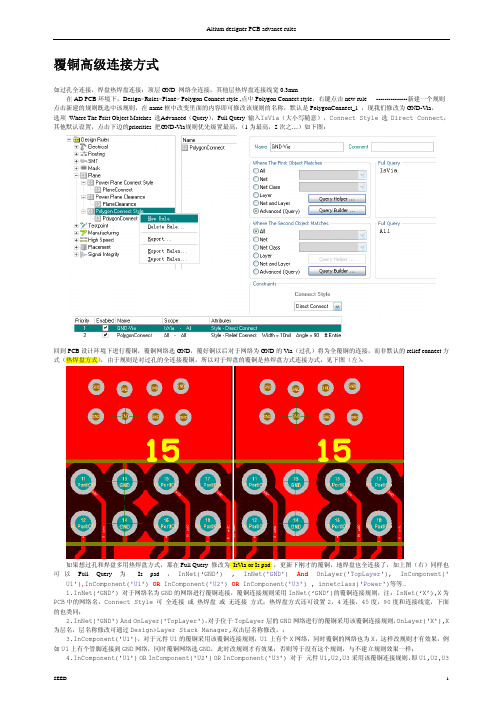

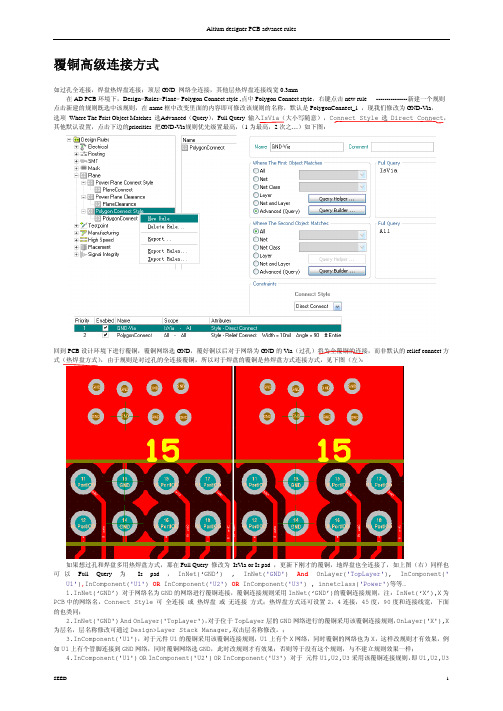

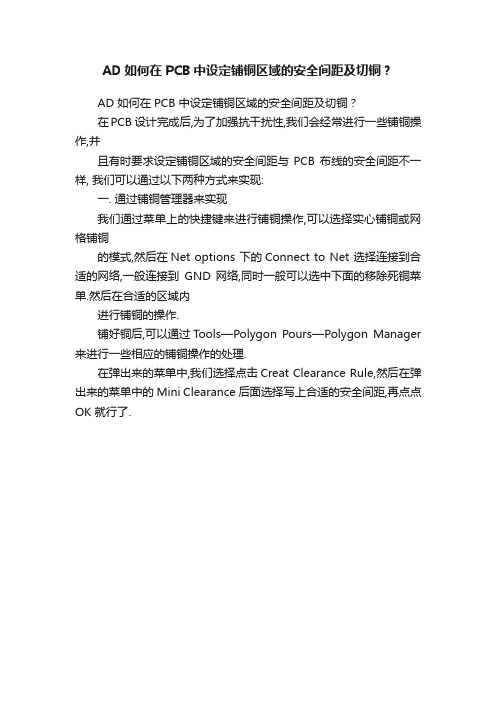

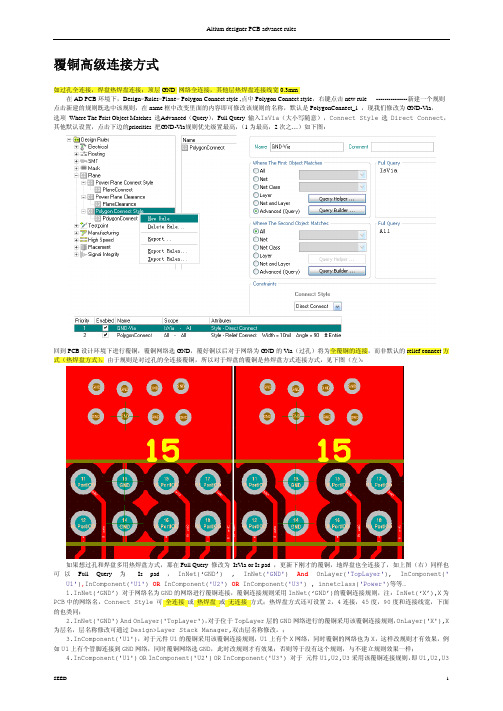

覆铜高级连接方式如过孔全连接,焊盘热焊盘连接;顶层GND 网络全连接,其他层热焊盘连接线宽0.3mm在AD PCB环境下,Design>Rules>Plane> Polygon Connect style ,点中Polygon Connect style,右键点击new rule ---------------新建一个规则点击新建的规则既选中该规则,在name框中改变里面的内容即可修改该规则的名称,默认是PolygonConnect_1 ,现我们修改为GND-Via,选项Where The Frist Object Matches 选Advanced(Query),Full Query 输入IsVia(大小写随意),Connect Style 选 Direct Connect,其他默认设置,点击下边的priorities 把GND-Via规则优先级置最高,(1为最高,2次之…)如下图:回到PCB设计环境下进行覆铜,覆铜网络选GND,覆好铜以后对于网络为GND的Via(过孔)将为全覆铜的连接,而非默认的relief connect方式(热焊盘方式),由于规则是对过孔的全连接覆铜,所以对于焊盘的覆铜是热焊盘方式连接方式,见下图(左):如果想过孔和焊盘多用热焊盘方式,那在Full Query 修改为IsVia or Is pad ,更新下刚才的覆铜,地焊盘也全连接了,如上图(右)同样也可以Full Query为 Is pad ,InNet(‘GND’) , InNet('GND') And OnLayer('TopLayer'), InComponent(' U1'),InComponent('U1') OR InComponent('U2') OR InComponent('U3') , innetclass('Power')等等…1.InNet(‘GND’) 对于网络名为GND的网络进行覆铜连接,覆铜连接规则采用InNet(‘GND’)的覆铜连接规则,注:InNet(‘X’),X为PCB中的网络名,Connect Style 可全连接或热焊盘或无连接方式;热焊盘方式还可设置2,4连接,45度,90度和连接线宽,下面的也类同;2.InNet('GND') And OnLayer('TopLayer'),对于位于TopLayer层的GND网络进行的覆铜采用该覆铜连接规则,OnLayer('X'),X 为层名,层名称修改可通过Design>Layer Stack Manager,双击层名称修改。

Altium Designer PCB 覆铜式布线方法

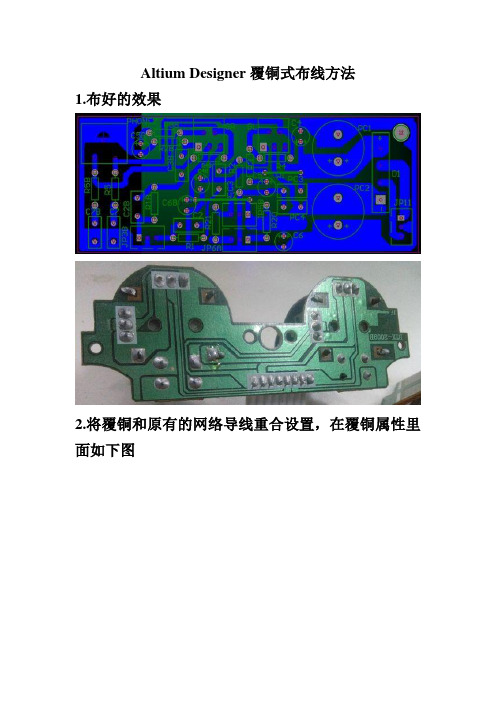

Altium Designer覆铜式布线方法

1.布好的效果

2.将覆铜和原有的网络导线重合设置,在覆铜属性里面如下图

3.将覆铜时候焊盘设置成全部连接,而非热焊盘连接,规则设置

4.前面两项设置好以后覆铜效果如下图覆盖GND网络并全部连接GND焊盘

5.单独设置覆铜和覆铜,覆铜和导线以及过孔的间距,而不影响原来设定的导线和导线的间距。

如下面步骤

新建一个规则如上图

右边出现设置框-在上面的“where the first object matches”框下面的高级旁边,点“询问构建器”,左边的“条件类型/操作员”点中出现的下拉框选择“object kind is”,在右边的“条件值”选择“poly”然后确定

设置框右边出现“Ispolygon”,将其改为“Inpolygon”,即第二个字母s改为n,同时下面的间隙设置就是单独设置这个的。

注意:种方法改的最小间距只是置覆铜和覆铜,覆铜和导线以及过孔的间距,而不影响原来设定的导线和导线的间距。

ad铺铜间距设置

ad铺铜间距设置在我们日常生活中,铺铜的应用越来越广泛,无论是电子产品、通信设备还是新能源领域,铺铜都发挥着重要作用。

铺铜工艺的关键在于间距设置,合理的间距可以提高产品的性能和稳定性。

本文将详细介绍铺铜间距设置的方法与技巧,以及常见问题及其解决措施。

一、铺铜概述铺铜是指在PCB(印刷电路板)或其他类似基板上,通过化学镀或电镀的方式,使铜层均匀地覆盖在基板表面。

铺铜技术可以提高电路板的导电性、散热性能以及电磁屏蔽效果。

在实际应用中,铺铜层的厚度、密度以及间距等参数都需要严格控制。

二、铺铜间距设置的重要性1.影响导电性能:合理的铺铜间距可以保证电流在电路板上的传输效率,降低电阻损耗。

2.影响散热性能:铺铜间距设置得当,有利于热量在基板上的扩散,提高产品的散热效果。

3.影响电磁兼容性:合理的铺铜间距有助于减小电磁干扰,提高产品的电磁兼容性。

4.影响产品稳定性:铺铜间距设置不当,可能导致铜层断裂、脱落等现象,影响产品的稳定性和可靠性。

三、铺铜间距设置的方法与技巧1.参照设计规范:根据产品需求和实际应用场景,参照相关设计规范进行铺铜间距设置。

2.软件辅助设计:利用专业软件(如Altium Designer、Cadence等)进行铺铜设计,通过调整参数实现间距设置。

3.经验积累:在实际工程中不断总结经验,掌握合适的铺铜间距设置方法。

四、常见问题及解决措施1.间距过大:可能导致电路传输性能降低、散热效果不佳等问题。

解决措施:适当减小间距,提高铜层密度。

2.间距过小:可能导致铜层断裂、脱落,影响产品稳定性。

解决措施:适当增大间距,确保铜层完整性。

3.铺铜不均匀:可能原因是基板表面处理不当、铺铜液参数不合理等。

解决措施:优化工艺流程,调整参数。

五、总结与建议铺铜间距设置是影响产品性能和稳定性的关键因素。

设计人员在进行铺铜设计时,应充分考虑产品需求、实际应用场景以及相关规范,掌握合适的间距设置方法。

Protel DXP-Altium Designer 修改铺铜间距的方法(图文)

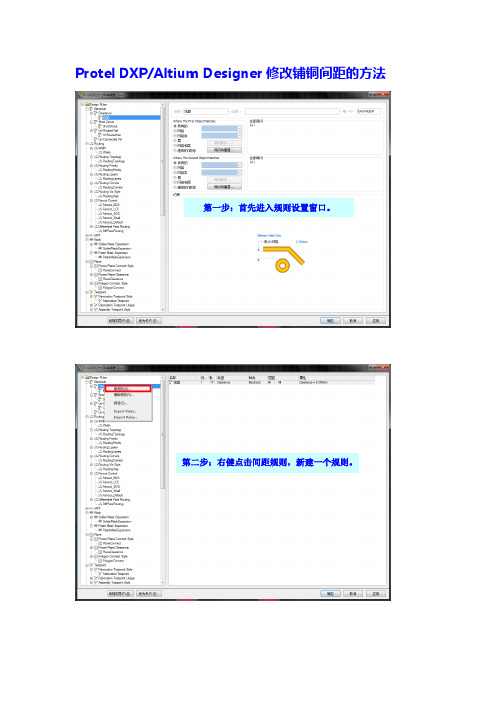

Protel DXP/Altium Designer修改铺铜间距的方法

第一步:首先进入规则设置窗口。

第二步:右健点击间距规则,新建一个规则。

第三步:点击新建的规则,出现以上对话框。

点选新出来的对话框中的,

然后再点选右边的。

第四步:在新出来的对话框中,选择条件类型中的。

第五步:选择好条件类型后,再选择条件值为Poly.然后单击确定按钮。

第六步:在回到主对话框中,点击会出来新的对话框。

按图中说明更改对话框中的文字。

改好后点击确认。

第七步:点击主窗口中的优先权按钮。

在出现的新对话框中把刚才新建的规则设置为优先就可以了。

回到主窗口后就可以随意更改铺铜与其它网络和焊盘的间距了。

MarvenHe。

PADS Layout的敷铜

第12章PADS Layout的敷铜敷铜就是将设计好的电路板覆盖上一层铜箔。

PADS Layout的敷铜功能强大而且具有较大的灵活性。

一旦掌握了敷铜的一些基本操作后,就可以快速地建立并编辑用于屏蔽的绝缘铜皮区域、电源和地线层等区域。

本章将介绍敷铜的一些基础方法和高级技巧。

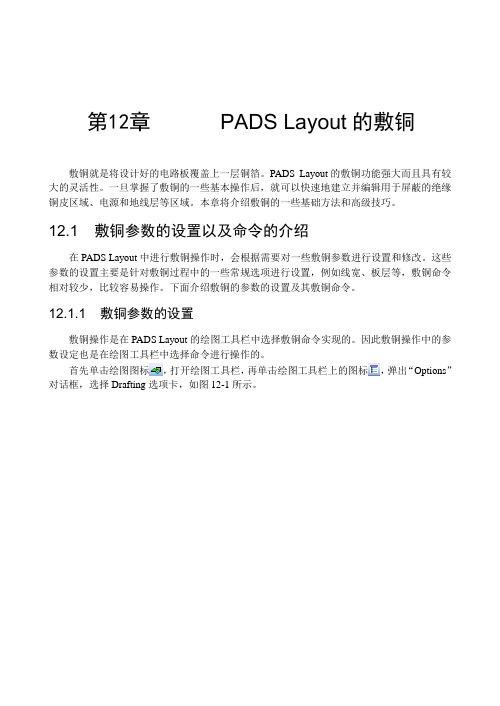

12.1 敷铜参数的设置以及命令的介绍在PADS Layout中进行敷铜操作时,会根据需要对一些敷铜参数进行设置和修改。

这些参数的设置主要是针对敷铜过程中的一些常规选项进行设置,例如线宽、板层等,敷铜命令相对较少,比较容易操作。

下面介绍敷铜的参数的设置及其敷铜命令。

12.1.1 敷铜参数的设置敷铜操作是在PADS Layout的绘图工具栏中选择敷铜命令实现的。

因此敷铜操作中的参数设定也是在绘图工具栏中选择命令进行操作的。

首先单击绘图图标,打开绘图工具栏,再单击绘图工具栏上的图标,弹出“Options”对话框,选择Drafting选项卡,如图12-1所示。

246图12-1 Options对话框在图12-1中Hatch(影线)和Flood(灌制)区域的设置是针对敷铜操作而言的,也就是说在敷铜的参数设定中只要对这两项进行设置就可以了。

注意在敷铜时点击右键可以对其参数进行修改设置,为了便于理解这些设置内容会在后面作简要说明。

下面对这两项内容进行说明:一、Hatch(影线)影线的设置可分为两部分。

(1)观察影线的效果。

∙Normal(显示影线)。

∙No Hatch(无影线)。

∙See Through(采用宽的影线网络)。

(2)影线的方向(在有影线的前提下)。

∙Orthogonal(直线)。

∙Diagonal(45°斜线)。

247二、 灌制(Flood )(Flood )灌制的设置可分为两部分。

(1) 量化。

∙ Min Hatch (最小灌制区域,键入的数值为面积)。

∙ Smoothing (灌铜区域的拐角转化为圆角的半径,键入一个较大的值会得到一个更圆滑的圆角)。

di dt 动点 铺铜面积

di dt 动点铺铜面积

在电子设计领域,铺铜是一种常见的操作,它可以起到屏蔽、散热、提高信号完整性等作用。

铺铜的操作步骤如下:

1. 放置铺铜:直接点击软件中的图案即可。

2. 设置铺铜相关参数:包括填充模式、孤岛范围、是否去除死铜、连接的网络等。

3. 选择铺铜区域:一般选择一个比板子外形大一点的矩形形状,对于有特殊要求的,则需要添加屏蔽区域。

4. 设置铺铜网络:点击设置中“链接到网络选项即可”。

5. 铺铜效果呈现:在Top面和Bottom层都会有铺铜效果,其中Top层为红色,bottom 层为蓝色。

6. 设置铺铜间距:设置走线与铺铜之间的距离。

7. 调整铺铜过孔的连接方式:选择连接类型为Direct Connect即可。

通过铺铜,可以提高PCB板的整体性能和美观度。

但在实际操作中,需要根据具体的设计要求和情况进行适当的调整和优化。

如果你需要了解更多关于铺铜的信息,请提供更多的背景和需求,以便我能更好地为你解答。

Protel DXP2004覆铜高级规则

覆铜高级连接方式如过孔全连接,焊盘热焊盘连接;顶层GND 网络全连接,其他层热焊盘连接线宽0.3mm在AD PCB环境下,Design>Rules>Plane> Polygon Connect style ,点中Polygon Connect style,右键点击new rule ---------------新建一个规则点击新建的规则既选中该规则,在name框中改变里面的内容即可修改该规则的名称,默认是PolygonConnect_1 ,现我们修改为GND-Via,选项Where The Frist Object Matches 选Advanced(Query),Full Query 输入IsVia(大小写随意),Connect Style 选 Direct Connect,其他默认设置,点击下边的priorities 把GND-Via规则优先级置最高,(1为最高,2次之…)如下图:回到PCB设计环境下进行覆铜,覆铜网络选GND,覆好铜以后对于网络为GND的Via(过孔)将为全覆铜的连接,而非默认的relief connect方式(热焊盘方式),由于规则是对过孔的全连接覆铜,所以对于焊盘的覆铜是热焊盘方式连接方式,见下图(左):如果想过孔和焊盘多用热焊盘方式,那在Full Query 修改为IsVia or Is pad ,更新下刚才的覆铜,地焊盘也全连接了,如上图(右)同样也可以Full Query为 Is pad ,InNet(‘GND’) , InNet('GND') And OnLayer('TopLayer'), InComponent(' U1'),InComponent('U1') OR InComponent('U2') OR InComponent('U3') , innetclass('Power')等等…1.InNet(‘GND’) 对于网络名为GND的网络进行覆铜连接,覆铜连接规则采用InNet(‘GND’)的覆铜连接规则,注:InNet(‘X’),X为PCB中的网络名,Connect Style 可全连接或热焊盘或无连接方式;热焊盘方式还可设置2,4连接,45度,90度和连接线宽,下面的也类同;2.InNet('GND') And OnLayer('TopLayer'),对于位于TopLayer层的GND网络进行的覆铜采用该覆铜连接规则,OnLayer('X'),X 为层名,层名称修改可通过Design>Layer Stack Manager,双击层名称修改。

DXP_AD09铺铜规则设置.docx

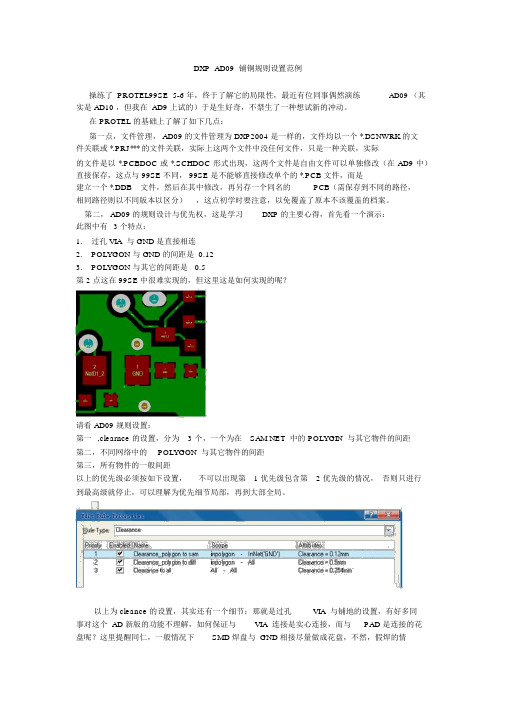

DXP_AD09 铺铜规则设置范例操练了 PROTEL99SE 5-6 年,终于了解它的局限性,最近有位同事偶然演练AD09 (其实是 AD10 ,但我在 AD9 上试的)于是生好奇,不禁生了一种想试新的冲动。

在 PROTEL 的基础上了解了如下几点:第一点,文件管理, AD09 的文件管理为 DXP2004 是一样的,文件均以一个 *.DSNWRK 的文件关联或 *.PRJ*** 的文件关联,实际上这两个文件中没任何文件,只是一种关联,实际的文件是以 *.PCBDOC 或 *.SCHDOC 形式出现,这两个文件是自由文件可以单独修改(在 AD9 中)直接保存,这点与 99SE 不同, 99SE 是不能够直接修改单个的 *.PCB 文件,而是建立一个 *.DDB文件,然后在其中修改,再另存一个同名的PCB(需保存到不同的路径,相同路径则以不同版本以区分),这点初学时要注意,以免覆盖了原本不该覆盖的档案。

第二, AD09 的规则设计与优先权,这是学习DXP 的主要心得,首先看一个演示:此图中有 3 个特点:1.过孔 VIA 与 GND 是直接相连2.POLYGON 与 GND 的间距是 0.123.POLYGON 与其它的间距是 0.5第 2 点这在 99SE 中很难实现的,但这里这是如何实现的呢?请看 AD09 规则设置:第一,clearnce 的设置,分为 3 个,一个为在SAM NET 中的 POLYGIN 与其它物件的间距第二,不同网络中的POLYGON 与其它物件的间距第三,所有物件的一般间距以上的优先级必须按如下设置,不可以出现第 1 优先级包含第 2 优先级的情况,否则只进行到最高级就停止,可以理解为优先细节局部,再到大部全局。

以上为 cleance 的设置,其实还有一个细节:那就是过孔VIA 与铺地的设置,有好多同事对这个 AD 新版的功能不理解,如何保证与VIA 连接是实心连接,而与PAD 是连接的花盘呢?这里提醒同仁,一般情况下SMD 焊盘与 GND 相接尽量做成花盘,不然,假焊的情况会的大堆。

Altium Designer 覆铜与导线或过孔的间距设置

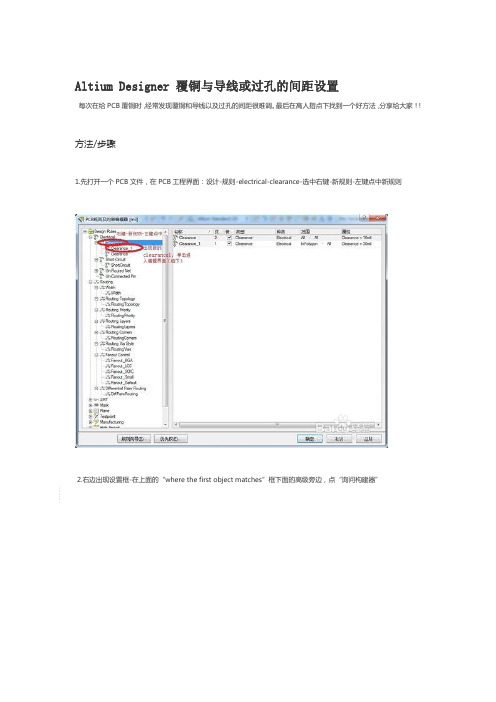

Altium Designer 覆铜与导线或过孔的间距设置1每次在给PCB覆铜时,经常发现覆铜和导线以及过孔的间距很难调。

最后在高人指点下找到一个好方法,分享给大家!!方法/步骤1.先打开一个PCB文件,在PCB工程界面:设计-规则-electrical-clearance-选中右键-新规则-左键点中新规则2.右边出现设置框-在上面的“where the first object matches”框下面的高级旁边,点“询问构建器”3.-左边的“条件类型/操作员”点中出现的下拉框选择“object kind is”,在右边的“条件值”选择“poly”然后确定4.设置框右边出现“Ispolygon”,将其改为“Inpolygon”,即第二个字母s改为n5.这时就可以更改最底下的“约束”里面“最小间隔”的值!注意:种方法改的最小间距只是覆铜与导线或过孔的间距,如果直接改默认Clearance会连引脚和导线的间距也改掉,导致部分和引脚靠的近的导线报错。

Altium Designer 敷铜间距设置,真实有效在任一PCB视图时,点击设计->规则,弹出规则设置对话框,如下图找到Clearance,如下图,使用右键单击,选择新规则,如下图在新规则上单击,在右侧where the first object matches,下选择custom query,然后点击查询构建器,如下图在查询构建器里选择In Any Polygon,并点击确定,如下图设置需要的间距,如下图,然后修改规则名称(我的是Polygon),并点击应用(还有下一步很重要)在规则编辑器左下角点击优先权按钮,如下图在优先权编辑器里点击增加和减少优先权提升新规则权限,使其高于Clearance,如下图修改后点击关闭,在规则编辑器再次点击应用或确定即可。

ad中覆铜和焊板之间的间距设置

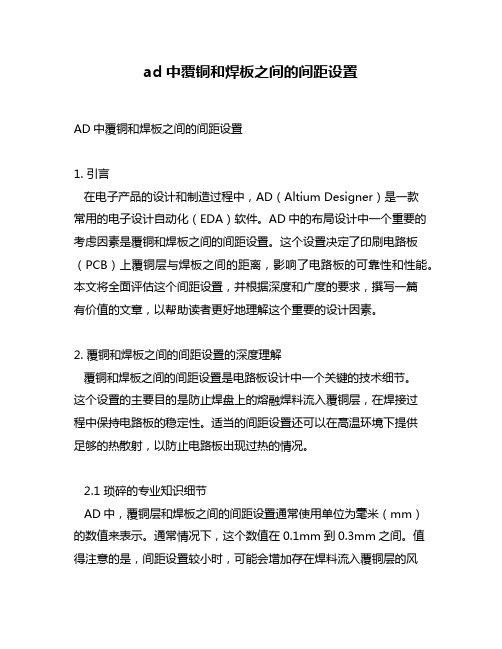

ad中覆铜和焊板之间的间距设置AD中覆铜和焊板之间的间距设置1. 引言在电子产品的设计和制造过程中,AD(Altium Designer)是一款常用的电子设计自动化(EDA)软件。

AD中的布局设计中一个重要的考虑因素是覆铜和焊板之间的间距设置。

这个设置决定了印刷电路板(PCB)上覆铜层与焊板之间的距离,影响了电路板的可靠性和性能。

本文将全面评估这个间距设置,并根据深度和广度的要求,撰写一篇有价值的文章,以帮助读者更好地理解这个重要的设计因素。

2. 覆铜和焊板之间的间距设置的深度理解覆铜和焊板之间的间距设置是电路板设计中一个关键的技术细节。

这个设置的主要目的是防止焊盘上的熔融焊料流入覆铜层,在焊接过程中保持电路板的稳定性。

适当的间距设置还可以在高温环境下提供足够的热散射,以防止电路板出现过热的情况。

2.1 琐碎的专业知识细节AD中,覆铜层和焊板之间的间距设置通常使用单位为毫米(mm)的数值来表示。

通常情况下,这个数值在0.1mm到0.3mm之间。

值得注意的是,间距设置较小时,可能会增加存在焊料流入覆铜层的风险,而间距设置过大,则可能会降低电路板在高温环境下的热散射能力。

2.2 设计中需要考虑的因素在确定覆铜和焊板之间的间距设置时,设计工程师需要考虑多种因素。

需要考虑电路板的尺寸和布局,以确保间距设置在全板范围内都是一致的。

需要根据焊接工艺和焊接设备的要求,选择合适的间距设置。

如果焊接工艺要求使用较大尺寸的焊盘,可能需要增加间距以适应焊盘的尺寸。

3. 实际案例和经验分享3.1 案例一:电源模块设计在设计电源模块时,我遇到了一个问题:电源模块上的焊盘非常小,但又需要在高温环境下工作。

经过仔细考虑,我决定将覆铜和焊板之间的间距设置为0.2mm,这样可以保证焊盘大小的匹配,并提供足够的散热能力。

3.2 案例二:高频电路设计在设计高频电路时,覆铜和焊板之间的间距设置尤为重要。

为了减少线路传输中的干扰,我将间距设置为0.1mm,以提供良好的电磁屏蔽效果,并确保信号传输的稳定性。

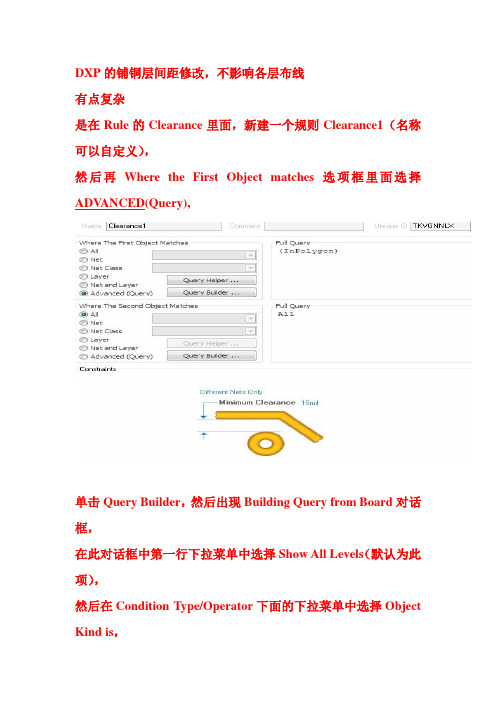

DXP的铺铜层间距修改,不影响各层布线

DXP的铺铜层间距修改,不影响各层布线

有点复杂

是在Rule的Clearance里面,新建一个规则Clearance1(名称可以自定义),

然后再Where the First Object matches选项框里面选择ADV ANCED(Query),

单击Query Builder,然后出现Building Query from Board对话框,

在此对话框中第一行下拉菜单中选择Show All Levels(默认为此项),

然后在Condition Type/Operator下面的下拉菜单中选择Object Kind is,

然后再右边的Condition V ALUE下面的下拉菜单中选择Ploy,这样在右边Query Preview中就会显示IsPolygon,单击OK 确定保存退出,

接下来还没有完,在Full Query 显示框中将IsPolygon,

改为InPolygon(DXP中的bug必须这样改,2004版本好像不用改)

最后一步了,下面就可以在Constraints里面修改你自己需要的间距了(根据你们的制版工艺水平)。

这样就只影响铺铜的间距,不影响各层布线的间距了。

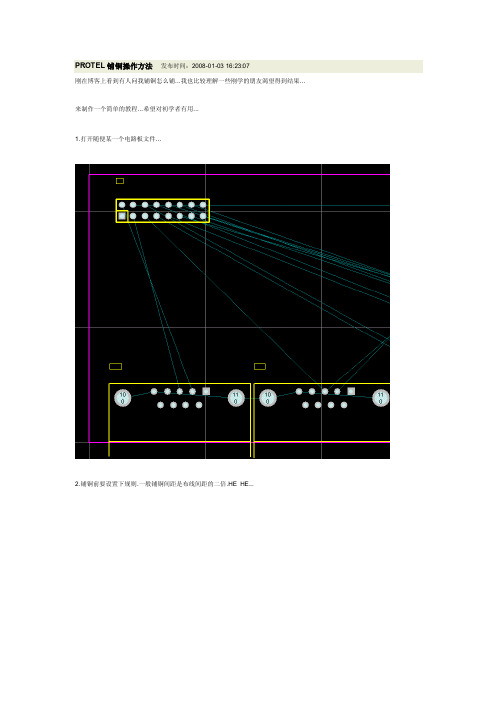

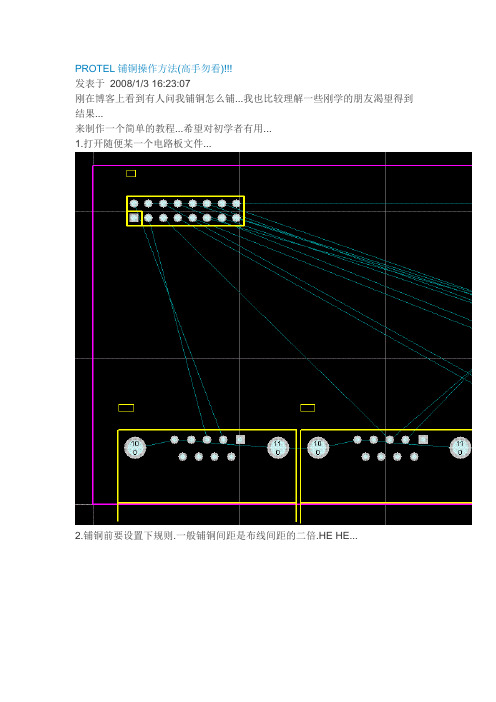

PROTEL铺铜操作方法

PROTEL铺铜操作方法发布时间:2008-01-03 16:23:07

刚在博客上看到有人问我铺铜怎么铺...我也比较理解一些刚学的朋友渴望得到结果... 来制作一个简单的教程...希望对初学者有用...

1.打开随便某一个电路板文件...

2.铺铜前要设置下规则.一般铺铜间距是布线间距的二倍.HE HE...

3.我在这里把间距改为0.5MM

4.执行铺铜...

5.第一个地方是设置网络...你可以选择你要铺的网络.我在这里是0.你可能是GND或别的什么的...第二个地方是设置栅格...如果上面的数字比下面大.那就网格.反之铺出来是实心的...第三个是层的设置....我在这里是顶层...你也可以根据自己的需要来改变层...设置完了点OK.就可以画了...哈哈...

6.按上面设置铺完的效果图...如果有什么不对.你可以多操作几次就OK...。

AD如何在PCB中设定铺铜区域的安全间距及切铜?

AD如何在PCB中设定铺铜区域的安全间距及切铜?

AD 如何在PCB 中设定铺铜区域的安全间距及切铜?

在PCB 设计完成后,为了加强抗干扰性,我们会经常进行一些铺铜操作,并

且有时要求设定铺铜区域的安全间距与PCB 布线的安全间距不一样, 我们可以通过以下两种方式来实现:

一. 通过铺铜管理器来实现

我们通过菜单上的快捷键来进行铺铜操作,可以选择实心铺铜或网格铺铜

的模式,然后在Net options 下的Connect to Net 选择连接到合适的网络,一般连接到GND 网络,同时一般可以选中下面的移除死铜菜单.然后在合适的区域内

进行铺铜的操作.

铺好铜后,可以通过T ools—Polygon Pours—Polygon Manager 来进行一些相应的铺铜操作的处理.

在弹出来的菜单中,我们选择点击Creat Clearance Rule,然后在弹出来的菜单中的Mini Clearance 后面选择写上合适的安全间距,再点点OK 就行了.。

Altium Designer 高级覆铜布线规则

覆铜高级连接方式如过孔全连接,焊盘热焊盘连接;顶层GND 网络全连接,其他层热焊盘连接线宽0.3mm在AD PCB环境下,Design>Rules>Plane> Polygon Connect style ,点中Polygon Connect style,右键点击new rule ---------------新建一个规则点击新建的规则既选中该规则,在name框中改变里面的内容即可修改该规则的名称,默认是PolygonConnect_1 ,现我们修改为GND-Via,选项Where The Frist Object Matches 选Advanced(Query),Full Query 输入IsVia(大小写随意),Connect Style 选 Direct Connect,其他默认设置,点击下边的priorities 把GND-Via规则优先级置最高,(1为最高,2次之…)如下图:回到PCB设计环境下进行覆铜,覆铜网络选GND,覆好铜以后对于网络为GND的Via(过孔)将为全覆铜的连接,而非默认的relief connect方式(热焊盘方式),由于规则是对过孔的全连接覆铜,所以对于焊盘的覆铜是热焊盘方式连接方式,见下图(左):如果想过孔和焊盘多用热焊盘方式,那在Full Query 修改为IsVia or Is pad ,更新下刚才的覆铜,地焊盘也全连接了,如上图(右)同样也可以Full Query为 Is pad ,InNet(‘GND’) , InNet('GND') And OnLayer('TopLayer'), InComponent(' U1'),InComponent('U1') OR InComponent('U2') OR InComponent('U3') , innetclass('Power')等等…1.InNet(‘GND’) 对于网络名为GND的网络进行覆铜连接,覆铜连接规则采用InNet(‘GND’)的覆铜连接规则,注:InNet(‘X’),X为PCB中的网络名,Connect Style 可全连接或热焊盘或无连接方式;热焊盘方式还可设置2,4连接,45度,90度和连接线宽,下面的也类同;2.InNet('GND') And OnLayer('TopLayer'),对于位于TopLayer层的GND网络进行的覆铜采用该覆铜连接规则,OnLayer('X'),X 为层名,层名称修改可通过Design>Layer Stack Manager,双击层名称修改。

PROTEL铺铜操作方法

PROTEL铺铜操作方法(高手勿看)!!!发表于2008/1/3 16:23:07刚在博客上看到有人问我铺铜怎么铺...我也比较理解一些刚学的朋友渴望得到结果...来制作一个简单的教程...希望对初学者有用...1.打开随便某一个电路板文件...2.铺铜前要设置下规则.一般铺铜间距是布线间距的二倍.HE HE...3.我在这里把间距改为0.5MM4.执行铺铜...5.第一个地方是设置网络...你可以选择你要铺的网络.我在这里是0.你可能是GND或别的什么的...第二个地方是设置栅格...如果上面的数字比下面大.那就网格.反之铺出来是实心的...第三个是层的设置....我在这里是顶层...你也可以根据自己的需要来改变层...设置完了点OK.就可以画了...哈哈...6.按上面设置铺完的效果图...如果有什么不对.你可以多操作几次就OK...∙系统分类: PCB∙用户分类: Protel∙标签: PROTEL PROTEL99铺铜PCB设计灌铜现格过小而生产时格蚀刻不出来或因为格太小造成印绿油时格内产生气泡,造成绿油易脱落。

2:remove dead copper 最后选上,以免产生特别小的无连接的小铜渣,造成制造过程中铜渣翻卷造成的短路等等。

2:pour over all same net ,是铺铜将所有同一网络的管脚或过孔连上(已有布线连接的,无连接布线的(在间距规则允许的条件下)肯定会连上,大于间距规则的管脚则铺不上,例如某些笨蛋连接一个QFP芯片的多个gnd时间距规则0.25mm ,管脚间距只有0.2mm ,他想借铺铜连接所有gnd (免连线),结果都开路了)所有建议大家不要偷懒,先将所有线布同,再铺铜# re:PROTEL铺铜操作方法(高手勿看)!!! 2008/1/4 11:17:31 zhjook补:2铺铜在输出gerber时右击cam output *** ,选中最右边的advanced ,将里边的use soft ARC的勾去掉,否则在铺铜与线拐角的地方在输出的gerber中的铺铜的圆弧部分会转换为几个直线(类似多边形的效果),会造成这种位置的间距小于设计规则,缩小的值起决于铺铜用的线宽和圆弧半径(即间距规则的大小)例如铺铜线宽0.25mm,规则0.25mm ,出gerber后的间距只有0.225~0.23左右,对于密度较大的板影响较大# re:PROTEL铺铜操作方法(高手勿看)!!! 2008/1/4 15:48:54 wang1jin感谢上面这位兄弟的补充...哈哈.非常详细...谢谢...# re:PROTEL铺铜操作方法(高手勿看)!!! 2008/1/15 10:23:09 chenhui0324谢谢你们了,真的非常感谢,(*^__^*) 嘻嘻……# re:PROTEL铺铜操作方法(高手勿看)!!! 2008/2/2 10:03:36 luohaoclearace的规则设置不太好。

ad铺铜间距设置

ad铺铜间距设置(原创版)目录1.铺铜间距的定义和重要性2.铺铜间距的设置方法3.铺铜间距对电路板性能的影响4.铺铜间距的优化建议正文一、铺铜间距的定义和重要性铺铜间距是指印刷电路板上相邻铜箔走线之间的距离。

这个距离对于电路板的性能和可靠性至关重要,因为它直接影响到电流的流动和热量的传递。

如果间距设置不当,可能会导致电路板性能下降、发热过多、甚至短路等故障。

二、铺铜间距的设置方法铺铜间距的设置主要取决于电路板的工作电压、电流、走线宽度和厚度等因素。

一般来说,铺铜间距的设置方法有以下几种:1.根据相关标准和规范进行设置,例如我国电子行业标准 GB/T 10759-2008《印制电路板设计规范》中对于铺铜间距有详细的规定。

2.根据电路板的工作电压和电流进行设置,一般来说,电压和电流越高,所需的铺铜间距就越大。

3.根据走线宽度和厚度进行设置,一般来说,走线宽度和厚度越大,所需的铺铜间距就越大。

三、铺铜间距对电路板性能的影响铺铜间距的大小对于电路板的性能有着重要的影响,主要表现在以下几个方面:1.电流流动:如果铺铜间距过小,电流在走线中的流动会受到阻碍,可能会导致电路板性能下降。

2.热量传递:如果铺铜间距过小,走线之间的热量传递会受到影响,可能会导致电路板发热过多。

3.信号干扰:如果铺铜间距过小,走线之间的信号干扰会增强,可能会导致电路板信号质量下降。

四、铺铜间距的优化建议为了优化铺铜间距,可以采取以下几个措施:1.根据电路板的工作电压和电流选择合适的铺铜间距。

2.在设计电路板时,尽量增加走线的宽度和厚度,以减小铺铜间距。

3.在布局电路板时,尽量减少走线之间的交叉和靠近,以减小铺铜间距。

PCB板铺铜规则设置

一、pcb覆铜技巧:1、如果PCB的地较多,有SGND、AGND、GND,等等,就要根据PCB板面位置的不同,分别以最主要的“地”作为基准参考来独立覆铜,数字地和模拟地分开来敷铜自不多言,同时在覆铜之前,首先加粗相应的电源连线:5.0V、3.3V等等,这样一来,就形成了多个不同形状的多变形结构。

2、对不同地的单点连接,做法是通过0欧电阻或者磁珠或者电感连接;3、晶振附近的覆铜,电路中的晶振为一高频发射源,做法是在环绕晶振敷铜,然后将晶振的外壳另行接地。

4、孤岛(死区)问题,如果觉得很大,那就定义个地过孔添加进去也费不了多大的事。

5、在开始布线时,应对地线一视同仁,走线的时候就应该把地线走好,不能依靠于覆铜后通过添加过孔来消除为连接的地引脚,这样的效果很不好。

6、在板子上最好不要有尖的角出现(《=180度),因为从电磁学的角度来讲,这就构成的一个发射天线!对于其他总会有一影响的只不过是大还是小而已,我建议使用圆弧的边沿线。

7、多层板中间层的布线空旷区域,不要敷铜。

因为你很难做到让这个敷铜“良好接地”8、设备内部的金属,例如金属散热器、金属加固条等,一定要实现“良好接地”。

9、三端稳压器的散热金属块,一定要良好接地。

晶振附近的接地隔离带,一定要良好接地。

总之:PCB上的敷铜,如果接地问题处理好了,肯定是“利大于弊”,它能减少信号线的回流面积,减小信号对外的电磁干扰。

二、pcb覆铜设置:1、pcb覆铜安全间距设置:覆铜的安全间距(clearance)一般是布线的安全间距的二倍。

但是在没有覆铜之前,为布线而设置好了布线的安全间距,那么在随后的覆铜过程中,覆铜的安全间距也会默认是布线的安全距离。

这样与预期的结果不一样。

一种笨方法就是在布好线之后,把安全距离扩大到原来的二倍,然后覆铜,覆铜完毕之后再把安全距离改回布线的安全距离,这样DRC检查就不会报错了。

这种办法可以,但是如果要重新更改覆铜的话就要重复上面的步骤,略显麻烦,最好的办法是单独为覆铜的安全距离设置规则。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DXP的铺铜层间距修改,不影响各层布线

有点复杂

是在Rule的Clearance里面,新建一个规则Clearance1(名称可以自定义),

然后再Where the First Object matches选项框里面选择ADV ANCED(Query),

单击Query Builder,然后出现Building Query from Board对话框,

在此对话框中第一行下拉菜单中选择Show All Levels(默认为此项),

然后在Condition Type/Operator下面的下拉菜单中选择Object Kind is,

然后再右边的Condition V ALUE下面的下拉菜单中选择Ploy,这样在右边Query Preview中就会显示IsPolygon,单击OK 确定保存退出,

接下来还没有完,在Full Query 显示框中将IsPolygon,

改为InPolygon(DXP中的bug必须这样改,2004版本好像不用改)

最后一步了,下面就可以在Constraints里面修改你自己需要的间距了(根据你们的制版工艺水平)。

这样就只影响铺铜的间距,不影响各层布线的间距了。