专用集成电路设计

集成电路设计岗位招聘笔试题与参考答案(某大型集团公司)

招聘集成电路设计岗位笔试题与参考答案(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在集成电路设计中,以下哪种类型的设计通常负责处理数字逻辑功能?A、模拟集成电路B、数字集成电路C、混合信号集成电路D、射频集成电路2、以下哪种技术用于在集成电路设计中实现晶体管间的连接?A、光刻技术B、蚀刻技术C、键合技术D、离子注入技术3、在CMOS工艺中,P型MOSFET的阈值电压通常会随着温度的升高而:A. 增加B. 减少C. 不变D. 先增加后减少4、下列哪一项不是减少互连延迟的有效方法?A. 使用更细的金属线B. 使用更高介电常数的绝缘材料C. 减少金属层之间的距离D. 使用铜代替铝作为互连线材料5、集成电路设计中,以下哪种工艺主要用于制造CMOS(互补金属氧化物半导体)逻辑电路?A. 双极型工艺B. 金属氧化物半导体工艺C. 双极型/金属氧化物半导体混合工艺D. 双极型/CMOS混合工艺6、在集成电路设计中,以下哪个参数通常用来描述晶体管的开关速度?A. 饱和电压B. 输入阻抗C. 开关时间D. 集成度7、在集成电路设计中,用于描述电路逻辑功能的硬件描述语言不包括以下哪一种?A. VerilogB. VHDLC. C++D. SystemVerilog8、下列选项中,哪一个不是ASIC(专用集成电路)设计流程中的一个阶段?A. 逻辑综合B. 布局布线C. 系统集成D. 物理验证9、以下哪种工艺技术通常用于制造高性能的集成电路?A. 混合信号工艺B. CMOS工艺C. GaN(氮化镓)工艺D. BiCMOS工艺二、多项选择题(本大题有10小题,每小题4分,共40分)1、在CMOS工艺中,关于阱(well)的概念,下列说法正确的有:A. NMOS晶体管通常位于P型阱中B. PMOS晶体管通常位于N型阱中C. N阱用于隔离不同区域的晶体管,防止电流泄露D. P阱可以与N阱共存于同一层硅片上而不会相互影响2、关于集成电路版图设计中的DRC(Design Rule Check)规则,下列哪些陈述是正确的?A. DRC规则是为了确保电路性能优化B. DRC规则定义了最小特征尺寸、最小间距等制造限制C. 违反DRC规则可能会导致制造缺陷,如短路或开路D. DRC规则在所有半导体制造工艺中都是相同的3、关于集成电路设计,以下哪些是典型的电路设计类型?()A、模拟电路设计B、数字电路设计C、混合信号电路设计D、射频电路设计E、光电子电路设计4、在集成电路设计中,以下哪些因素会影响电路的功耗?()A、晶体管的工作状态B、电源电压C、电路的复杂度D、芯片的温度E、外部负载5、在集成电路设计过程中,下列哪些技术用于提高电路的性能?A. 使用更先进的制程技术B. 优化电路布局减少信号延迟C. 增加电源电压以提升速度D. 减少电路层数降低制造成本E. 应用低功耗设计方法6、下列哪些是实现CMOS逻辑门时需要考虑的关键因素?A. 输入电平的阈值B. 输出驱动能力C. 功率消耗D. 静态电流消耗E. 电路的工作频率7、以下哪些技术或方法属于集成电路设计中的模拟设计领域?()A. 信号处理算法B. 逻辑门电路设计C. 模拟电路仿真D. 功耗分析E. 版图设计8、在集成电路设计中,以下哪些步骤是进行版图设计的必要阶段?()A. 电路原理图设计B. 布局规划C. 逻辑分割D. 布局布线E. 版图检查9、在CMOS工艺中,影响MOSFET阈值电压的因素有哪些?A. 氧化层厚度B. 衬底掺杂浓度C. 栅极材料类型D. 源漏区掺杂浓度E. 温度F. 器件尺寸三、判断题(本大题有10小题,每小题2分,共20分)1、集成电路设计岗位的工程师需要具备扎实的数学基础和电子工程知识。

电子电气工程中的集成电路设计

电子电气工程中的集成电路设计电子与电气工程是一门涉及电力、电子、通信等多个领域的学科,其中集成电路设计作为电子与电气工程的重要分支之一,扮演着至关重要的角色。

本文将从集成电路的定义、发展历程、设计流程以及应用领域等方面进行探讨。

一、集成电路的定义集成电路是指将多个电子元件(如晶体管、电阻、电容等)封装在一个芯片上的技术,通过在芯片上刻制电路图案,实现电子元件的功能集成。

集成电路的核心是芯片,它可以实现多种功能,如处理信号、存储数据等。

二、集成电路的发展历程集成电路的发展经历了数十年的演进。

20世纪50年代,人们开始尝试将多个晶体管集成在一个芯片上,从而诞生了第一代集成电路。

60年代至70年代,随着技术的进步,集成度不断提高,出现了大规模集成电路(LSI)和超大规模集成电路(VLSI)。

80年代至今,随着微电子技术的不断发展,集成度进一步提高,出现了超大规模集成电路(ULSI)和超大规模集成电路(GSI)。

三、集成电路的设计流程集成电路的设计过程包括电路设计、物理设计和验证等多个阶段。

首先,通过电路设计,完成电路图的设计与优化,确定电路的功能和性能。

其次,进行物理设计,包括布局设计和布线设计,将电路图转化为物理结构。

最后,进行验证,通过模拟、仿真和测试等手段,验证电路的正确性和性能。

四、集成电路的应用领域集成电路广泛应用于各个领域,如通信、计算机、医疗、汽车等。

在通信领域,集成电路被用于手机、网络设备等通信设备中,实现信号处理和数据传输功能。

在计算机领域,集成电路被用于处理器、内存等核心部件中,提高计算机的性能和效率。

在医疗领域,集成电路被用于医疗设备中,如心脏起搏器、血压计等,实现医疗监测和治疗功能。

在汽车领域,集成电路被用于汽车电子系统中,如发动机控制单元、车载导航等,提高汽车的安全性和智能化水平。

总结起来,集成电路设计是电子与电气工程中的重要分支,它通过将多个电子元件集成在一个芯片上,实现电路的功能集成。

专用集成电路6-Calibre和Diva

6、版图验证工具 、

Outline

IC设计的基本知识 版图验证工具Diva 版图验证工具Calibre

1、IC设计的基本知识

ASIC设计方法分类:

定制 (Custom) ) 全定制 (Full-Custum) ) 基于包 (Cell-Based) ) 门陈列 (Gate Arrays) ) 线性陈列 (Linear Arrays) )

选择PEX运行设置文件pex_runset,操作步骤与DRC, LVS相同。

输出格式设为CALIBREVIEW

Run PEX运行三次

第一次,这里三个选项都选中, 第一次,这里三个选项都选中, 出现Calibre 出现Calibre finished with Error:SIGABRT错误 Error:SIGABRT错误 第二次,选中第二、三个选项, 第二次,选中第二、三个选项, 出现Calibre 出现Calibre finished with Error:SIGABRT错误 Error:SIGABRT错误 第三次, 第三次,仅选中最后一个选项

选择你的LVS运行目录

然后,保存lvs_runset文件,操作方法与前面保存drc_runset 文件一模一样。

这步操作是选择 从电路导出网表, 让这个导出的网表 与版图生成的网表 进行LVS。

然后就可以点“Run LVS”运行LVS。

LVS通过

(3)寄生参数抽取 (3)寄生参数抽取 PEX

规则文件同LVS 规则文件同LVS

反相器的抽取视图

(3)版图与电路对照验证LVS

LVS的任务是证明这个版图就是想要的那一个,也 就是说证明这个版图实现的功能与图

diva的LVS规则文件 的 规则文件 工艺库名

用于下一代汽车专用集成电路(ASIC)的嵌入式现场可编程逻辑门阵列(eFPGA)

对于最近研究过新车的任何人来说,很难不注意到汽车电子产品的发展是多么的迅速。

仅仅将三年前的汽车安全性技术与今天的技术进行对比,您就会发现摄像头数量已显著增加,以支持诸如全景可视、驾驶员注意力分散监测器、立体视觉摄像头、前向摄像头和多个后视摄像头等应用。

除了摄像头,系统功能也增强了,包括自动紧急制动、车道偏离警告、后方盲点检测和交通标志识别等。

这一趋势表明,汽车电子类产品在持续快速地创新,但这也给汽车原始设备制造商(OEM)带来了全新的挑战,包括:·当研发一辆新车的平均时间从48个月缩短至24个月左右(请参阅缩短研发生命周期和降低设计复杂性对汽车行业的影响),同时还要支持长达10年以上的生命周期时,如何快速开发新特性和安全性功能?·平台架构的确定都比车辆上市提前数年,如何预测所需的硬件和软件需求?·当汽车用户拿消费类电子产品来做比较时,如何提高汽车电子产品的性能和质量以满足用户的期望?专用集成电路(ASIC)解决方案为了去解决这些问题,汽车原始设备制造商需要重新考虑他们的系统架构,并在其设计中添加灵活性,进而能够在设计过程的后期进行更改,并增加不断开发的特性和功能。

这种重新设计的系统架构使原始设备制造商与其他竞争对手相比具有差异化,并为使用标准硬件器件无法解决的技术难题提供解决方案。

传统上,先进驾驶辅助系统(ADAS)架构器件的选择都依赖于现成的器件,这些器件的设计旨在支持特定的汽车安全功能和环境需求。

对于诸如防抱死制动系统(ABS)等非差异化功能,这种方法是非常适合的。

但是,如果您正在设计创新的安全功能,许多原始设备制造商选择构建自己的定制ASIC。

与任何现成的器件相比,定制ASIC提供了最低的总体成本和最高的性能:然而,ASIC会带来风险。

如果您没有确定所有必需的功能,那么您将无法进行更改,除非对ASIC进行成本高昂且耗费时日的重新设计。

尽管存在固有风险,但是一家创新型汽车公司特斯拉(Tesla)仍然认为ASIC 路线是他们提供先进安全性功能的最佳选择。

专用集成电路史密斯pdf

专用集成电路史密斯pdf专用集成电路(Application Specific Integrated Circuit,简称ASIC)是指根据特定需求和要求而定制设计的集成电路。

它与通用集成电路(General Purpose Integrated Circuit)相比,能够实现更高的性能、更低的功耗和更高的集成度。

下面将从历史、应用和设计流程三个方面进行介绍。

首先让我们回顾一下ASIC的历史。

在20世纪60年代,集成电路技术开始崭露头角,并引发了数字电子技术革命。

然而,当时的集成电路还是以通用目的为主,无法完全满足各种特定需求。

因此,为了进一步提高电路的性能和集成度,专用集成电路应运而生。

20世纪70年代,随着集成电路工艺技术的发展,ASIC开始得到更广泛的应用,并成为各个领域中关键技术的支持。

接下来我们来了解ASIC的应用领域。

在通信行业,ASIC被广泛应用于手机、通信基站等设备中,能够提供更高的容量和更快的数据传输速度。

在汽车电子领域,ASIC可用于驾驶辅助系统、发动机管理系统等,提高了车辆的安全性和效能。

此外,ASIC还广泛应用于医疗设备、工业自动化、航空航天等领域,在各个领域都发挥着至关重要的作用。

最后是ASIC的设计流程。

通常,ASIC设计流程包括需求分析、架构设计、逻辑设计、物理设计、验证和制造等阶段。

在需求分析阶段,设计人员与客户充分沟通,明确电路的功能、性能和约束条件。

然后,在架构设计阶段,设计人员根据需求分析结果进行电路的整体架构设计,确定模块划分和接口定义。

接下来是逻辑设计阶段,设计人员将架构进行细化,进行逻辑电路的设计和优化。

然后,物理设计阶段主要是进行版图设计,将逻辑电路转化为物理结构,并进行布局和布线优化。

验证阶段用于验证电路的正确性和性能是否满足需求。

最后,制造阶段将设计好的电路进行芯片制造,并进行测试和封装,最终形成可商用的ASIC芯片。

综上所述,专用集成电路在无数领域有着广泛的应用。

混合信号专用集成电路设计课程设计

混合信号专用集成电路设计课程设计一、课程简介混合信号专用集成电路设计课程旨在讲解混合信号集成电路的设计原理、设计思路、设计流程等基本知识,培养学生深入了解混合信号集成电路设计的能力。

本文档是本课程的课程设计报告,将详细介绍我们小组在课程设计中所完成的任务。

二、任务详情2.1 任务背景本次任务要求我们设计一款混合信号专用集成电路,这款电路要有一定的选择和控制能力,能够按照特定的输入信号输出相应的信号。

同时,这款电路也要具备一定的抗干扰能力和误差控制能力。

2.2 任务要求我们的任务是根据任务背景,设计出一套完整的混合信号集成电路,包括电路的原理图、PCB电路板和测试代码。

同时,我们还需要对本次任务的整体设计流程进行梳理分析,并对测试结果给出分析和思路。

2.3 设计流程2.3.1 电路原理图设计我们首先需要完成电路原理图的设计,并通过仿真软件对电路进行验收。

在设计时,需要考虑各种因素的影响,包括传输延时、线路阻抗匹配、信号采集等等。

2.3.2 PCB电路板设计完成电路原理图设计后,我们需要进行PCB电路板的设计。

在设计时,需要将原理图中的元器件在板子上布局,同时考虑到电路的稳定性和抗干扰能力等因素。

2.3.3 测试代码设计完成PCB电路板设计后,我们需要编写测试代码,对电路进行功能测试和性能测试,验证设计的正确性。

2.4 设计思路我们的设计思路主要包括如下几个方面:2.4.1 选择合适的器件在混合信号集成电路的设计中,选择合适的器件是非常重要的。

需要根据设计要求,选择合适的模拟电路和数字电路,确保电路可以良好地工作。

2.4.2 考虑电路的抗干扰能力混合信号集成电路的稳定性和抗干扰能力都是非常重要的。

我们需要尽可能地减小电路的噪声干扰和误差,确保电路在各种环境下都可以良好地工作。

2.4.3 进行模拟仿真和电路测试在设计完成后,需要进行模拟仿真和电路测试,确保电路的功能正确和性能良好。

需要设计测试用例,尽可能地覆盖各种场景,确保电路的全面性和正确性。

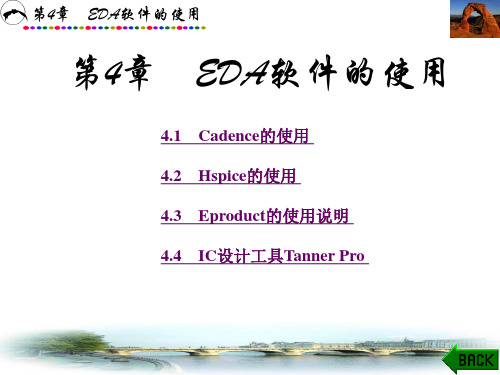

专用集成电路设计实践(西电版)第4章 EDA软件的使用

第4章 EDA软件的使用

图4-5 CreateNewFile对话框

第4章 EDA软件的使用

图4-6 电路图编辑窗口

第4章 EDA软件的使用

对于已存在的工程,可以先寻找并复制工程的路径,在

Terminal对话框中输入cd和空格后粘贴路径名,然后回车,再 输入启动命令icfb&,回车后即会出现CIW窗口。在CIW窗口 中选择Tools/LibraryManager,出现一个LibraryManager对话框, 如图4-3所示。其中最左边一栏是cds.lib里的库文件,左键双 击要打开的工程名,在Cell下就会出现工程中所有的电路图名, 双击要打开的电路图,在View中就会出现schematic,点击右键 打开即可。

第4章 EDA软件的使用

4.1.3 电路图仿真 1.添加激励 要对所设计的电路进行仿真,就需要加激励,即电源、地、 输入信号等。 加电源:按I键,点击Browse,弹出如图4-8所示的窗口。 双击analogLib,在Cell中选择常用的电源,一般为vpwl(分段线 性电压源,仿真瞬态响应时使用)和vdc(直流电源,仿真直流和 交流响应时使用)。按Q键,设置电源大小。将电源激励一端 连在电源线上,另一端接地。 加地:按I键,点击Browse,弹出如图4-8所示的框图。双 击analogLib,在Cell中选择gnd,连在需要接地的地方即可。 其他输入信号要按电路具体情况和要仿真的功能而定, 如图4-9所示。

第4章 EDA软件的使用

当把电路全部输入完毕后,点击左上角的CheckandSave

按钮,检查无错误后即可。四条线连到一个节点时会有警告, 此时不影响电路的正确性,所以要分清警告是这种情况,还是 其他情况,若是其他情况就有可能影响电路。电路检查若有 错误,则在图4-2所示窗口查看错误,然后根据具体错误逐步 改正。若要查找电路图中的某条线,点击电路图所在界面的 Edit Search Find,然后在出现的界面中点击SearchFor pin name)等。 net name。也可以查找器件名(SearchFor 名(SearchFor inst name),查找引脚

集成电路设计中的全定制电路设计

集成电路设计中的全定制电路设计全定制电路设计是集成电路设计的一个重要分支,它与传统的标准细胞库设计方法相比,具有更大的灵活性和更高的性能。

本文将详细介绍全定制电路设计的基本概念、设计流程、优势以及应用。

1. 全定制电路设计的基本概念全定制电路设计,顾名思义,就是根据特定的应用需求,为特定的功能设计电路。

与标准细胞库设计方法不同,全定制电路设计不依赖于预先定义的单元库,而是完全根据设计的实际需求来定制电路。

这种设计方法可以在保证性能的同时,最大限度地减少电路的面积和功耗。

2. 全定制电路设计的设计流程全定制电路设计通常包括以下几个基本步骤:2.1 需求分析在需求分析阶段,设计师需要充分理解电路的功能需求,包括输入输出信号、工作频率、功耗等关键参数。

这一步是整个设计过程的基础,直接关系到后续电路设计的成败。

2.2 逻辑设计在逻辑设计阶段,设计师需要根据需求分析的结果,设计出满足功能要求的逻辑电路。

这一步通常使用硬件描述语言(HDL)进行描述,如Verilog或VHDL。

2.3 电路合成在电路合成阶段,需要将逻辑设计阶段得到的描述转化为具体的电路结构。

这一步涉及到电路的优化和布局,目的是为了在满足性能要求的同时,尽可能减少电路的面积和功耗。

2.4 仿真验证在仿真验证阶段,需要使用专门的仿真工具对设计好的电路进行功能和性能的验证。

这一步是非常重要的,因为它可以帮助设计师及时发现并修复设计中的错误。

2.5 物理设计在物理设计阶段,需要将电路合成阶段得到的结构映射到具体的集成电路工艺上,进行版图绘制和后端处理。

这一步需要考虑到电路的布局、布线、功耗分布等因素,以保证电路在实际制造过程中的性能和可靠性。

3. 全定制电路设计的优势全定制电路设计具有以下几个显著的优势:3.1 性能优化由于全定制电路设计是完全根据实际需求来定制电路,因此可以在保证功能的同时,实现最优的性能。

这与标准细胞库设计方法相比,可以显著提高电路的运行速度和效率。

集成电路设计基础Ch03

15

华•侨•大•学

• 专用集成电路系统实验室

2. 图案发生器方法

(PG: Pattern Generator)

在PG法中, 规定layout 的基本图形为矩形. 任 何版图都将分解成一 系列各种大小、不同 位置和方向的矩形条 的组合. 每个矩形条用 5个参数进行描述:

(X, Y, A, W, H)

2020/3/30

18

华•侨•大•学

• 专用集成电路系统实验室

4. 电子束扫描法(E-Beam Scanning)

采用电子束对抗蚀剂进行曝光,由 于高速的电子具有较小的波长。分 辨率极高。先进的电子束扫描装置 精度50nm,这意味着电子束的步进 距 离 为 5 0 nm, 轰 击 点 的 大 小 也 为 50nm

三、显影: 晶圆用真空吸盘吸牢,高速旋转, 将显影液喷射到晶圆上。显影后,用清 洁液喷洗。

四、烘干: 将显影液和清洁液全部蒸发掉。

2020/3/30

27

华•侨•大•学

• 专用集成电路系统实验室

3.3.2 曝光方式

1. 接触式曝光方式中,把掩膜以0.05 0.3ATM 的压力压在涂光刻胶的晶圆上, 曝光光源的波长在0.4m左右。

常用OMR83,负片型。

光刻胶对大部分可见光灵敏,对黄光不灵敏,可在黄光下 操作。

再烘晶圆再烘,将溶剂蒸发掉,准备曝光

2020/3/30

24

华•侨•大•学

• 专用集成电路系统实验室Leabharlann 正性胶与负性胶光刻图形的形成

2020/3/30

25

华•侨•大•学

• 专用集成电路系统实验室

涂光刻胶的方法(见下图):

2020/3/30

19

asic 芯片

asic 芯片ASIC芯片(Application-Specific Integrated Circuit)是一类专用集成电路芯片,也称为定制芯片。

相比于通用集成电路(如处理器、存储器等),ASIC芯片是根据特定的应用需求而设计的,因此能够提供更高的性能和更低的功耗。

ASIC芯片在各个领域都得到广泛应用,包括通信、计算机、工业控制、汽车、医疗等。

下面将从设计流程、应用案例和未来发展趋势三个方面来介绍ASIC芯片。

首先是ASIC芯片的设计流程。

ASIC芯片的设计是一个复杂的过程,通常分为前端设计和后端设计两个阶段。

前端设计主要包括功能设计、电路设计和逻辑验证。

功能设计是根据需求规格书确定芯片的功能模块和接口,并进行功能分析;电路设计则是根据功能要求,设计电路的结构和参数,如时钟、存储器、逻辑门等;逻辑验证是通过仿真和验证工具对设计进行全面测试,以确保功能的正确性。

后端设计主要包括物理设计、布局设计和版图设计。

物理设计是将逻辑电路映射到实际的物理器件,进行数电转换、时序优化等操作;布局设计则是确定各个电路模块的位置和相互连接方式;版图设计则是将布局设计结果转化为最终的芯片版图。

完成设计后,还需要进行流片和封装测试。

流片是指将版图发送给芯片制造企业,进行样片生产;封装测试则是将芯片封装为最终的芯片模块,并经过各种测试和验收,确保芯片的可靠性和稳定性。

其次是ASIC芯片的应用案例。

ASIC芯片广泛应用于各个领域,以下以通信和计算机领域为例介绍两个典型的应用案例。

在通信领域,ASIC芯片被广泛用于移动通信设备中,如手机、路由器和基站等。

它们能够提供高效的信号处理、数据传输和接口控制功能,满足不同通信标准和需求。

例如,LTE芯片可以实现高速无线数据传输,提供更快的网络连接速度;而基站芯片能够实现大规模的无线通信覆盖,提供更好的通信服务质量。

在计算机领域,ASIC芯片被广泛用于数据中心和云计算设备中。

它们能够提供高性能的计算、存储和网络功能,满足大规模数据处理和分析的需求。

集成电路设计与研发

集成电路设计与研发一、概述集成电路设计与研发是电子信息领域中的重要领域之一。

集成电路是现代电子设备中必不可少的核心元器件之一,负责实现各种功能和电路控制。

集成电路设计与研发是通过对电路原理、材料、工艺等方面的深入研究和应用,来设计和制造各种类型的集成电路,以满足不同领域的需求。

本文将从集成电路设计的基本概念、技术、流程和应用等方面进行详细的介绍和分析。

二、基本概念1. 集成电路集成电路(Integrated Circuit,IC)是指多个电子器件和相应的电子元件,可在单一半导体材料片上制造成一个完整的电子电路系统。

它由许多个非常小的、微观等级的可重复元件组成,可以完成不同的电路功能。

集成电路与传统的离散型电路相比,具有运算速度快、尺寸小、性能稳定等优点。

2. 集成电路设计集成电路设计是指通过对原理图、逻辑表达式、算法或者其他集成电路的描述进行设计和模拟验证,产生满足特定功能需求的新的电路网络,实现自动控制、音频处理、图像处理、通信等各种应用。

它包括电路设计、数字电路设计、模拟电路设计、射频电路设计等。

3. 集成电路测试集成电路测试是指对集成电路进行可靠性、功能、性能、电气、物理、环境等全面测试,以保证集成电路有良好的性能和可靠性。

测试方法包括外界模拟测试、逻辑函数测试、电性能测试等。

三、技术发展1. 原理模拟设计技术原理模拟设计技术是一种集成电路设计和验证方法,它是通过计算机软件模拟电路的整体结构与性能,来评估集成电路的性能和可行性。

它可以极大地节省设计周期和成本,提高设计效率和设计质量。

2. 自动化设计技术自动化设计技术是通过计算机辅助设计工具来实现高效的设计和测试,解决设计过程中困难的问题。

它包括逻辑设计、自动布局和布线、电气仿真与DFT等。

3. 射频技术射频技术是集成电路设计和研发中的重要技术之一。

它可以实现高性能、低噪声和高频率的射频电路设计,解决无线通信领域的问题。

目前,射频技术在5G通信领域得到广泛应用。

中科院_段成华_专用集成电路设计_作业 2

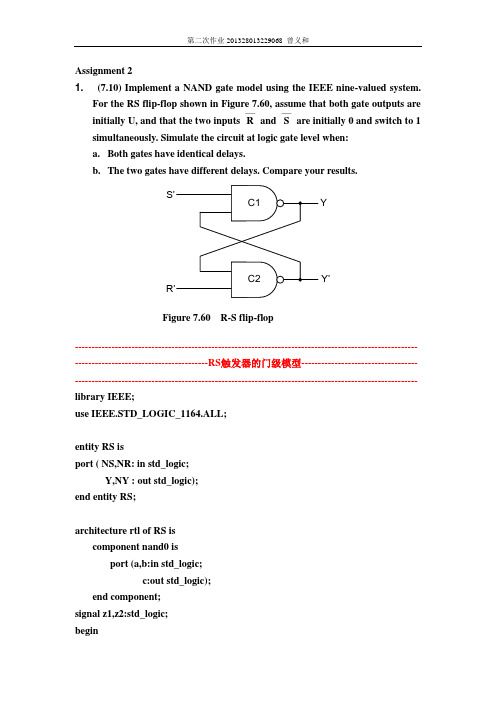

Assignment 21. (7.10)Implement a NAND gate model using the IEEE nine-valued system.For the RS flip-flop shown in Figure 7.60, assume that both gate outputs are initially U, and that the two inputs R——and S——are initially 0 and switch to 1 simultaneously. Simulate the circuit at logic gate level when:a.Both gates have identical delays.b.The two gates have different delays. Compare your results.YY’Figure 7.60 R-S flip-flop------------------------------------------------------------------------------------------------------- ----------------------------------------RS触发器的门级模型----------------------------------- ------------------------------------------------------------------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity RS isport ( NS,NR: in std_logic;Y,NY : out std_logic);end entity RS;architecture rtl of RS iscomponent nand0 isport (a,b:in std_logic;c:out std_logic);end component;signal z1,z2:std_logic;beginNY<=z2;Y<=z1;u1:nand0 port map(NS,z2,z1);u2:nand0 port map(NR,z1,z2);end architecture rtl;------------------------------------------------------------------------------------------------------- ----------------------------------RS触发器的门级模型测试激励----------------------------- ------------------------------------------------------------------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity RS_TB isend entity RS_TB;architecture RTL of RS_TB iscomponent RS isport ( NS,NR: in std_logic;Y,NY: out std_logic);end component;signal NY :std_logic:='1';signal Y :std_logic:='1';signal NS :std_logic:='0';signal NR :std_logic:='0';beginDUT:RS port map(NS => NS,NR => NR,y => y,NY => NY);processbeginNS <= '0';NR <= '0';wait for 0.1 us;NS <= '1';NR <= '1';wait for 0.1 us;end process;end architecture RTL;------------------------------------------------------------------------------------------------------- --------------共同延迟的RS电路门级仿真、此次采用的是VCS 2009.12--------------- -------------------------------------------------------------------------------------------------------一、建立和设置环境变量二、分析三、Elaboration四、仿真1、调用DVE2、查看仿真波形3、根据DVE检查波形,分析功能上图是VCS图形界面的DVE工具显示的波形图,从上面可以得到一下几个结论:1、初始状态输出端为‘U’,输入端均为‘0’;2、在1ns的反应延迟之后,输出端根据当前状态被置为‘1’;3、在100ns时,输入端同时置‘1’,此时输出端出现震荡状态。

专用集成电路(ASIC及FPGA)项目可行性研究报告方案(可用于发改委立项及银行贷款+2013详细案例范文)

专用集成电路(ASIC及FPGA)项目可行性研究报告方案(可用于发改委立项及银行贷款+2013详细案例范文)【编制机构】:博思远略咨询公司(360投资情报研究中心)【研究思路】:【关键词识别】:1、专用集成电路(ASIC及FPGA)项目可研2、专用集成电路(ASIC 及FPGA)市场前景分析预测3、专用集成电路(ASIC及FPGA)项目技术方案设计4、专用集成电路(ASIC及FPGA)项目设备方案配置5、专用集成电路(ASIC及FPGA)项目财务方案分析6、专用集成电路(ASIC及FPGA)项目环保节能方案设计7、专用集成电路(ASIC及FPGA)项目厂区平面图设计8、专用集成电路(ASIC及FPGA)项目融资方案设计9、专用集成电路(ASIC及FPGA)项目盈利能力测算10、项目立项可行性研究报告11、银行贷款用可研报告12、甲级资质13、专用集成电路(ASIC及FPGA)项目投资决策分析【应用领域】:【专用集成电路(ASIC及FPGA)项目可研报告详细大纲——2013年发改委标准】:第一章专用集成电路(ASIC及FPGA)项目总论1.1 项目基本情况1.2 项目承办单位1.3 可行性研究报告编制依据1.4 项目建设内容与规模1.5 项目总投资及资金来源1.6 经济及社会效益1.7 结论与建议第二章专用集成电路(ASIC及FPGA)项目建设背景及必要性2.1 项目建设背景2.2 项目建设的必要性第三章专用集成电路(ASIC及FPGA)项目承办单位概况3.1 公司介绍3.2 公司项目承办优势第四章专用集成电路(ASIC及FPGA)项目产品市场分析4.1 市场前景与发展趋势4.2 市场容量分析4.3 市场竞争格局4.4 价格现状及预测4.5 市场主要原材料供应4.6 营销策略第五章专用集成电路(ASIC及FPGA)项目技术工艺方案5.1 项目产品、规格及生产规模5.2 项目技术工艺及来源5.2.1 项目主要技术及其来源5.5.2 项目工艺流程图5.3 项目设备选型5.4 项目无形资产投入第六章专用集成电路(ASIC及FPGA)项目原材料及燃料动力供应6.1 主要原料材料供应6.2 燃料及动力供应6.3 主要原材料、燃料及动力价格6.4 项目物料平衡及年消耗定额第七章专用集成电路(ASIC及FPGA)项目地址选择与土建工程7.1 项目地址现状及建设条件7.2 项目总平面布置与场内外运7.2.1 总平面布置7.2.2 场内外运输7.3 辅助工程7.3.1 给排水工程7.3.2 供电工程7.3.3 采暖与供热工程7.3.4 其他工程(通信、防雷、空压站、仓储等)第八章节能措施8.1 节能措施8.1.1 设计依据8.1.2 节能措施8.2 能耗分析第九章节水措施9.1 节水措施9.1.1 设计依据9.1.2 节水措施9.2 水耗分析第十章环境保护10.1 场址环境条件10.2 主要污染物及产生量10.3 环境保护措施10.3.1 设计依据10.3.2 环保措施及排放标准10.4 环境保护投资10.5 环境影响评价第十一章劳动安全卫生与消防11.1 劳动安全卫生11.1.1 设计依据11.1.2 防护措施11.2 消防措施11.2.1 设计依据11.3.2 消防措施第十二章组织机构与人力资源配置12.1 项目组织机构12.2 劳动定员12.3 人员培训第十三章专用集成电路(ASIC及FPGA)项目实施进度安排13.1 项目实施的各阶段13.2 项目实施进度表第十四章专用集成电路(ASIC及FPGA)项目投资估算及融资方案14.1 项目总投资估算14.1.1 建设投资估算14.1.2 流动资金估算14.1.3 铺底流动资金估算14.1.4 项目总投资14.2 资金筹措14.3 投资使用计划14.4 借款偿还计划第十五章专用集成电路(ASIC及FPGA)项目财务评价15.1 计算依据及相关说明15.1.1 参考依据15.1.2 基本设定15.2 总成本费用估算15.2.1 直接成本估算15.2.2 工资及福利费用15.2.3 折旧及摊销15.2.4 修理费15.2.5 财务费用15.2.6 其它费用15.2.7 总成本费用15.3 销售收入、销售税金及附加和增值税估算15.3.1 销售收入估算15.3.2 增值税估算15.3.2 销售税金及附加费用15.4 损益及利润及分配15.5 盈利能力分析15.5.1 投资利润率,投资利税率15.5.2 财务内部收益率、财务净现值、投资回收期15.5.3 项目财务现金流量表15.5.4 项目资本金财务现金流量表15.6 不确定性分析15.6.1 盈亏平衡15.6.2 敏感性分析第十六章经济及社会效益分析16.1 经济效益16.2 社会效益第十七章专用集成电路(ASIC及FPGA)项目风险分析17.1 项目风险提示17.2 项目风险防控措施第十八章专用集成电路(ASIC及FPGA)项目综合结论第十九章附件1、公司执照及工商材料2、专利技术证书3、场址测绘图4、公司投资决议5、法人身份证复印件6、开户行资信证明7、项目备案、立项请示8、项目经办人证件及法人委托书10、土地房产证明及合同11、公司近期财务报表或审计报告12、其他相关的声明、承诺及协议13、财务评价附表《专用集成电路(ASIC及FPGA)项目可行性研究报告》主要图表目录图表项目技术经济指标表图表产品需求总量及增长情况图表行业利润及增长情况图表2013-2020年行业利润及增长情况预测图表项目产品推销方式图表项目产品推销措施图表项目产品生产工艺流程图图表项目新增设备明细表图表主要建筑物表图表主要原辅材料品种、需要量及金额图表主要燃料及动力种类及供应标准图表主要原材料及燃料需要量表图表厂区平面布置图图表总平面布置主要指标表图表项目人均年用水标准图表项目年用水量表图表项目年排水量表图表项目水耗指标图表项目污水排放量图表项目管理机构组织方案图表项目劳动定员图表项目详细进度计划表图表土建工程费用估算图表固定资产建设投资单位:万元图表行业企业销售收入资金率图表投资计划与资金筹措表单位:万元图表借款偿还计划单位:万元图表正常经营年份直接成本构成表图表逐年直接成本图表逐年折旧及摊销图表逐年财务费用图表总成本费用估算表单位:万元图表项目销售收入测算表图表销售收入、销售税金及附加估算表单位:万元图表损益和利润分配表单位:万元图表财务评价指标一览表图表项目财务现金流量表单位:万元图表项目资本金财务现金流量表单位:万元图表项目盈亏平衡图图表项目敏感性分析表图表敏感性分析图图表项目财务评价主要数据汇总表【更多增值服务】:专用集成电路(ASIC及FPGA)项目商业计划书(风险投资+融资合作)编制专用集成电路(ASIC及FPGA)项目细分市场调查(市场前景+投资期市场调查)分析专用集成电路(ASIC及FPGA)项目IPO上市募投(甲级资质+符合招股书)项目可研编制专用集成电路(ASIC及FPGA)项目投资决策风险评定及规避策略分析报告专用集成电路(ASIC及FPGA)项目资金申请报告(2013年度)【博思远略咨询优势】:【博思远略成功案例】:1.500千瓦太阳能储能充电站项目可行性研究报告2.新建纳米晶染料敏化太阳能电池生产线项目可行性研究报告3.新能源(磁动力)产业基地项目可行性研究报告4.年产4000万平米锂电池隔膜项目可行性研究报告5.年产200MW 太阳能晶体硅片项目可行性研究报告6.3000吨太阳能级多晶硅生产项目可行性研究报告7.透明导电膜(TCO)玻璃项目商业计划书8.200MW太阳能薄膜板厂及1GW太阳能发电站项目9.循环经济静脉产业园项目可行性研究报告10.治理矿渣废水及矿渣综合利用项目可行性研究报告11.可再生资源回收加工中心项目可行性研究报告12.某经济开发区循环经济产业园项目可研报告13.电子废物拆解及处理项目可行性研究报告14.年产20万吨绿色节能多高层钢结构项目可行性研究报告15.收集、净化废矿物油项目可行性研究报告16.高性能微孔滤料生产线建设项目可行性研究报告17.工业废水及城市污水处理项目可研报告18.太阳能节能设备项目可行性研究报告19.高效节能生物污水处理项目可行性研究报告20.年处理2000吨钕铁硼废料综合利用项目21.山东烟台某文化产业园区可行性研究报告22.文化创意旅游产业区项目可行性研究报告23.3D产业动漫工业园项目可行性研究报告24.四川省动漫产业基地项目可行性研究报告25.创意产业园综合服务平台建设项目可行性研究报告26.历史文化公园项目可行性研究报告27.生物麻纤维绿色环保功能型面料生产线项目28.氟硅酸综合清洁利用项目可行性研究报告29.年产300万码研磨垫项目可行性研究报告30.年产20万吨有机硅项目可行性研究报告31.车用稀土改性镍氢动力电池生产基地建设项目可行性研究报告32.12万吨/年磷精矿(浮选)、配套8万吨/年饲料级磷酸三钙项目33.电石下游精细化工品生产装置建设项目可研34.含氟高分子材料及含氟精细化学品系列产品项目35.精细化工产业配套园项目建议书兼可研报告36.大气颗粒物监测仪器生产项目可研报告37.矿山机械及配件制造项目可行性研究报告38.汽车配套高分子材料成型产品生产项目39.年产3万吨异形精密汽车锻件项目可行性研究报告40.汽车商业旅游综合体项目可行性研究报告41.新建磁动力轿车项目可行性分析报告42.4万吨PA6浸胶帘子线(含鱼网丝)项目申请报告43.年产20万辆电动车项目可行性研究报告44.扩建年产30000套各类重型汽车差速器总成生产线项目45.高科技农业园区建设项目可行性研究报告46.绿色农产品配送中心项目立项报告47.富硒食品工业园项目可行性研究报告48.采用生物发酵技术生产优质低温肉制品项目立项报告49.蔬菜、瓜果、花卉设施栽培项目可行性研究报告50.新型水体富营养化处理项目商业计划书51.现代农业生态观光示范园区建设项目52.5000吨水果储藏保鲜气调库可行性研究报告53.我国国际生态橄榄油物流中心基地项目可行性研究报告54.综合物流园区项目可行性研究报告55.大型水果物流中心建设项目可行性研究报告56.超五星级园林式温泉度假酒店可行性研究报告57.信息安全灾难恢复信息系统项目可研报告58.“祥云”高校云服务平台成果转化项目可行性研究报告59.气象数据处理解释中心项目申请报告60.电子束辐照项目可行性研究报告61.年产3000台智能设备控制系统电液伺服系统项目可行性研究报告62.年产3000万根纳米碳碳素纤维加热管/加热板项目63.压敏电阻片及SPD电涌保护器项目可行性研究报告64.智能电网电能量综合管理系统项目可行性研究报告65.10万套镁合金手提电脑外壳压铸生产线可行性研究报告66.年产10万吨金属镁及镁合金加工生产项目可行性研究报告67.38万吨废钢铁加工处理生产线项目可行性研究报告68.年产80万吨铁矿石采选工程项目可行性研究报告69.年产1万吨高性能铜箔生产项目可行性研究报告70.年产3万吨碳酸二甲酯项目可行性研究报告71.新建年产500吨钼制品生产线可行性研究报告72.3万锭亚麻高档生态面料生产线项目立项报告73.年产废纸再造30万吨白板纸并自备20000KW热电厂项目立项报告74.年产6000万套烟用商标纸彩色印刷项目立项报告75.11.6万立方米竹板材加工项目可行性研究报告76.北京某小区汽车远程遥控监控防盗系统项目可研报告77.山东淄博张周路花卉种植基地产业化项目78.山东烟台某企业年产1000吨海红果汁产品扩建3万吨项目79.韩国某品牌天然抗肿瘤新药进入中国市场商业计划书80.大连某IT企业财务软件外包投资价值分析报告81.电热水循环式床垫专利实施项目商业计划书82.辽宁省朝阳市某企业年产12万吨鱼/禽饲料农业产业化发展项目83.粉煤灰纤维及经纬线造纸三项专利产品项目84.河北唐山某企业年产30吨超级电容器电极用多孔复合材料项目85.杭州某企业年产30万吨630ERW大口径高频直缝焊管项目86.江苏连云港某企业集团果蔬(脱水)加工项目87.鄂尔多斯某企业年产250吨纳米二氧化钛粉体项目88.广东惠州某企业集成电路封装项目89.新疆某企业液态原料奶冷链物流系统改造项目90.14万吨棉秸秆高密度压缩板材项目91.湖南省双语智能幼儿园项目投资价值分析报告92.烟台某企业5000吨蔬菜果品气调保鲜库建设项目93.江苏某企业年产1万吨钢结构项目可行性研究94.新疆石河子1500吨辣椒色素生产项目95.河北邯郸某集团南瓜粉及系列产品加工建设项目96.河北25mw非晶硅薄膜太阳能电池生产项目97.杭州高新区某企业PDP等离子体大屏幕显示板项目98.吉林省梅河口市100万只朗德鹅填饲、屠宰加工基地建设项目99.湖南常德某集团特种钢结构涂料生产线项目100.福建某生物科技有限公司引进战略投资者商业计划书101.安康市再生资源回收加工中心项目可行性研究报告102.福建省企业信息化项目资金申请报告103.山东省某企业技术改造专项资金项目资金申请报告104.武汉市某企业节能专项资金申请报告105.重庆某集团引进年产200万台汽车直流电机生产线项目106.鹤岗市绿色无害优质大米综合开发项目107.山东省东营开发区某高新企业国家中小企业发展专项资金申请报告108.大连市某企业环境保护专项资金申请报告109.山东淄博某纺织集团青岛三万锭精梳天然彩色棉纺纱分厂建设项目110.河南驻马店某企业彩钢夹芯板项目111.辽宁凌源某企业年产15万吨超细矿石微粉可行性研究报告112.辽宁鞍山年产20万吨630ERW大口径高频直缝焊管项目113.北京昌平生态农业观光园区项目可行性研究报告114.云南昆明某企业年产6000吨浓缩峰蜜生产项目115.广东深圳150mm重掺硅单晶抛光片出口建设项目116.衢州年产5万辆电动观光车及配套零部件项目117.绿色充电电池投资价值分析报告118.江苏南通米糠综合利用项目119.广东东莞年产80万只节能灯和卤素灯项目120.内蒙某企业年产15000吨氯化钡生产项目121.西安某矿山机械制造公司粉碎机项目122.湖南再制造产业园区项目可行性研究报告123.河北某公司年产300吨磷酸铁锂项目可行性研究报告124.上海某船舶制造有限公司80万吨/年拆船项目可行性研究报告125.郑州某企业汽车铝合金轮毂镀膜加工项目126.广州某企业胎盘系列化妆品生产项目127.福建漳州某企业年产30吨白光LED荧光粉项目可行性研究报告128.速溶型纤维蛋白胶产业化项目投资价值分析报告129.临沂某化工企业年产20万吨保险粉项目可行性研究报告130.某投资公司投资北京健康体检中心项目可行性研究报告131.长沙某科研机构电热远红外高科技研发中心项目132.青岛某企业年产10万套健身器材生产线项目可行性研究报告133.河南某企业迁扩建年产8万吨碳素制品生产线项目134.山东德州某企业年产15万台太阳能热水器建设项目135.广东某企业年产5万台空气能热泵热水器项目136.江西南昌化工循环产业园区项目137.大连某企业年产4000台套不锈钢橱柜可行性研究报告138.上海某公司瑜伽教练学校商业计划书139.山西阳泉洗精长烟煤50万吨每年洁净化综合利用项目140.北京某快餐集团直营20家连锁店可行性研究报告141.广东梅州某集团甲流诊断试剂项目可行性研究报告142.潍坊年产5000吨花生制品生产线可行性报告143.山东淄博城市创意产业园可行性报告144.齐鲁石化某企业20万吨PVC技改项目145.齐鲁石化某企业乙烯燃气管件生产线技术改造项目项目146.内蒙古某企业年产3万台/套新型太阳能水泵系统项目147.河南平顶山20万吨PVC粒料与1.5亿平米环保型PVC壁纸联产项目148.辽宁某企业燃油燃气锅炉项目149.广西南宁铁路货场建设物流园区项目150.济南微晶玻璃板材生产线投资项目151.中油集团某机械厂CNG气瓶生产线技术改造项目152.西安车辆GPS定位导航电子地图市场分析与投资项目153.无锡某物联网高技术企业传感器项目154.江苏常州60吨/年甲基戊炔醇项目155.高纯金属材料投资项目价值分析报告156.稀土永磁电机项目投资经济效益分析报告157.全自动按摩椅项目投资价值分析报告158.北京某高新企业Kx2100系列分布智能火灾探测系统项目159.6000万平米胶粘制品生产项目可行性研究报告160.五万锭精梳纱生产线高新技术改造项目可研报告161.年产10万吨超细矿石微粉可行性研究报告162.年产2000万块新型空心砖生产线项目申请报告163.年产2.0亿标块粉煤灰蒸压砖项目建议书164.年产6000万块煤矸石空心砖项目可行性研究报告165.年产500万平方米高档陶瓷墙地砖生产线项目可研报告166.大理石板型材生产线项目可行性研究报告167.年产8000万吨高性能建筑乳胶涂料可行性研究报告168.云南红河州开远市方解石粉加工厂项目可行性研究报告169.废矿物油再生利用项目可研报告170.煤层气开发项目可行性研究报告171.高新技术研发中心扩建项目可行性研究报告172.陕西东方塑业有限公司年产8000吨塑料管生产线项目可研报告;173.低压过热蒸汽废轮胎、废塑料高分子复合材料还原分离装置生产项目可行性研究报告;174.北京奥祥通风设备有限公司通风设备生产项目可行性研究报告;175.山东临沂休闲农业与乡村旅游示范园项目可行性研究报告;176.河南立新设备有限公司高效混凝土搅拌成套设备和报废汽车发动机制造空压机项目可行性研究报告;177.江苏省旺鑫金属结构工程公司太阳能光伏发电装备制造组建配套建设项目可行性研究报告;178.河北张家口嘉年华草原冰雪文化主题公园项目规划方案179.河北石家庄百果园休闲农庄项目建议书;180.融世通机电(大连)有限公司复印机再制造项目申请报告;181.河南鼎泰岩土工程有限公司多边形高强混凝土桩生产项目可行性研究报告;182.新疆伊利农胜科技公司西北型节能日光温室项目可行性研究报告;183.贵州六盘水茂霖苗圃农民专业合作社项目可行性研究报告;184.郑州久筑建筑公司商品混凝土搅拌站建设项目节能评估报告;185.山东神越新材料有限公司年产2.5万吨多层共挤功能性薄膜项目可行性研究报告;186.天津润德文化公司年产10万套舞台设备项目可行性研究报告;187.北京顺义绿能农业发展有限公司特种养殖及绿色生态农庄项目建议书;188.山东潍坊2000吨果蔬种植园区项目可研报告;189.江苏连云港海运集团集装箱租赁项目可行性研究报告;190.北京中建科新科技公司移动式建筑垃圾破碎站项目可行性研究报告;191.安徽省欣荣现代农工有限公司申报2013年提升棉花生产能力条件建设项目可行性研究报告;192.厦门市台新商贸有限公司荔枝保鲜项目可行性研究报告;193.山东淄博鲁盛联合公司合成氨项目可行性研究报告;194.黑龙江某医院购置X线电子计算机断层扫描装置(CT)资金申请报告;195.北京锐视科技有限公司激光投影3D显示技术项目资金申请报告;196.为河南洛阳绿盟菌业有限公司完成年1万吨工厂化北虫草高效种植项目可行性研究报告;197.为内蒙古呼和浩特蒙塞食品有限公司完成牛羊屠宰深加工生产线建设项目可行性研究报告.……更多案例详情请联系博思远略咨询公司案例研究中心或在百度中搜索“博思远略”“360投资情报研究中心”【关于博思远略咨询公司】:北京博思远略咨询有限公司为客户提供专业权威细分市场调查、项目可研报告、项目申请报告、专项资金申请报告、国际标准格式商业计划书、IPO募投项目可研报告编制服务——高端博士团队|丰富成功案例经验|工程咨询甲级资质|高通过率品质保障|全程申报辅助| 【完】。

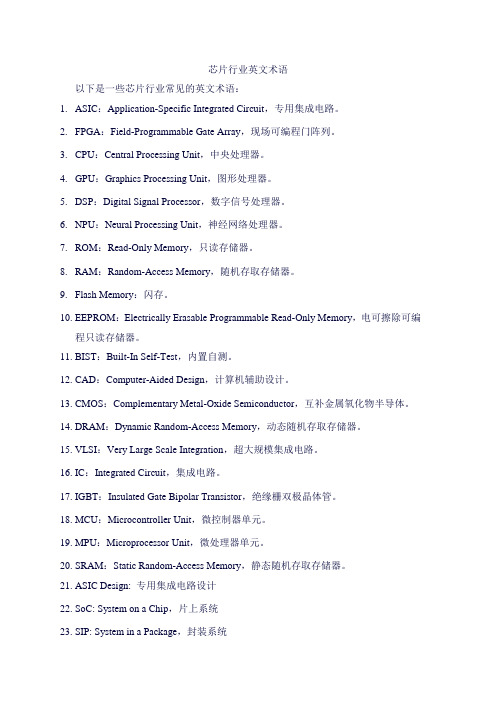

芯片行业英文术语

芯片行业英文术语以下是一些芯片行业常见的英文术语:1.ASIC:Application-Specific Integrated Circuit,专用集成电路。

2.FPGA:Field-Programmable Gate Array,现场可编程门阵列。

3.CPU:Central Processing Unit,中央处理器。

4.GPU:Graphics Processing Unit,图形处理器。

5.DSP:Digital Signal Processor,数字信号处理器。

6.NPU:Neural Processing Unit,神经网络处理器。

7.ROM:Read-Only Memory,只读存储器。

8.RAM:Random-Access Memory,随机存取存储器。

9.Flash Memory:闪存。

10.EEPROM:Electrically Erasable Programmable Read-Only Memory,电可擦除可编程只读存储器。

11.BIST:Built-In Self-Test,内置自测。

12.CAD:Computer-Aided Design,计算机辅助设计。

13.CMOS:Complementary Metal-Oxide Semiconductor,互补金属氧化物半导体。

14.DRAM:Dynamic Random-Access Memory,动态随机存取存储器。

15.VLSI:Very Large Scale Integration,超大规模集成电路。

16.IC:Integrated Circuit,集成电路。

17.IGBT:Insulated Gate Bipolar Transistor,绝缘栅双极晶体管。

18.MCU:Microcontroller Unit,微控制器单元。

19.MPU:Microprocessor Unit,微处理器单元。

20.SRAM:Static Random-Access Memory,静态随机存取存储器。

FPGA和ASIC的概念及区别

FPGA和ASIC的概念,他们的区别?答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

FPGA与ASIC实现系统设计的比较在当今的电子设备中集成电路的应用已经越来越广泛,几乎涉及到每一种电子设备中。

集成电路按其实现技术可以分为2大类:可编程逻辑器件(包括CPLD和FPGA等)和专用集成电路(ASIC)。

下面我们分别从这2类集成电路的特点和如何使用这2类集成电路来实现我们的设计需求来进行比较,以为我们以后的系统设计提供借鉴。

首先我们以FPGA为代表比较可编程逻辑器件和ASIC,它们最大的区别就是FPGA在不知道使用者的具体需求之前就已经按一定的配置制造好了所有的电路,使用者再根据自己的设计需要选用其中的电路来使用,而ASIC是根据使用者的设计需求来制造其中的电路。

由于以上原因使得这2类集成电路具有如下特点:ASIC由厂家定制,有比较低的单片生产成本,但却有很高的设计成本以及缓慢的上市时间;FPGA则具有高度的灵活性,低廉的设计成本以及适中的器件成本和快速的面世时间。

下面我们分别简单介绍使用ASIC和FPGA实现某一设计的的步骤:要设计并生产一颗ASIC其流程大致如下:首先是系统设计,这其中包括设计好系统的对外接口,系统内部大的模块划分,内部模块之间的接口确定,系统时钟的确定等等。

然后进行进一步的详细设计,这一步包括各个大模块内部的再次模块划分,内部小模块之间的接口确定等。

再下一步是进行RTL级编码,即使用硬件描述语言进行实际的电路的设计,类似于软件业的代码编写。

RTL级编码完成后进行RTL级仿真,如果功能正确那么下一步利用综合工具生成网表和SDF文件然后进行前仿真,如果前仿真没有问题即可进行布局布线,布局布线完成后再次提取网表和SDF文件,利用布局布线后的网表和SDF文件进行后仿真,如果后仿真也没有问题即可进行样片的生产。

电子电路中的集成电路设计与实现

电子电路中的集成电路设计与实现在当今物联网时代的背景下,电子电路和集成电路已经深入人们的生活,随处可见的智能设备、物联网终端等设备都离不开电路设计和集成电路的支持。

电路设计是电子技术领域的重要分支,而其中的集成电路设计更是电子技术的精髓所在。

本文将分别探讨电子电路中的集成电路设计和实现。

一、电子电路中的集成电路设计集成电路(Integrated Circuit,IC)是指将多种复杂的电路模块、器件以及其他电子元器件集成在一块芯片上的电路电子器件。

集成电路是电子技术发展的重要标志和里程碑,也是电子技术中最具有发展前景和应用价值的领域之一。

集成电路设计的核心是电路模块的设计,而电路设计则需要考虑到多个因素,包括电路的稳定性、可靠性、功耗、速度等。

因此,集成电路设计需要从众多的电路设计模块中选择最为适合的模块进行组合设计。

其次,集成电路设计还需要涉及到EDA(Electronic Design Automation)工具的应用。

EDA是现代电路设计中不可或缺的工具,通过EDA工具,设计师可以快速地完成电路模块的选择、设计和实现,并且进行仿真和验证。

目前,常用的EDA工具包括Cadence、Allegro等。

最后,集成电路设计需要进行高层次设计与底层设计的结合。

高层次设计涉及到系统的框架和功能分配等方面,而底层设计则涉及到电路元器件的布局、堆叠排布等方面。

只有将两者有机地结合起来,才能够完成真正的集成电路设计。

二、电子电路中的集成电路实现与集成电路设计相对应的是集成电路的实现。

集成电路的实现需要掌握生产工艺和制造技术,并且对现代微电子技术有深入的理解。

常用的集成电路实现工艺包括:晶圆加工工艺、光刻技术、化学蚀刻技术等。

这些工艺手段可将设计好的集成电路图案制造出半导体芯片,从而实现整个集成电路的实现。

集成电路实现的关键是工艺的可靠性和稳定性。

制造过程中需要严格控制各种工艺参数,如温度、压力、时间等,以保证整个制造过程的稳定性和可靠性。

数字集成电路设计流程

单片IC

MOS型

按结构分类 混合IC

BiMOS 厚膜混合IC 薄膜混合IC

按规模分类

SSI/MSI/LSI/VLSI/ULSI/GSI

数字电路 按功能分类 模拟电路

组合逻辑电路 时序逻辑电路

线性电路 非线性电路

数模混合电路

集成电路的设计过程: 设计创意 + 仿真验证

功能要求 行为设计(VHDL) 否 行为仿真 是 综合、优化——网表 否

5.可编程器件的ASIC设计

可编程 ASIC 是专用集成电路发展的另一个 有特色的分支,它主要利用可编程的集成电路如 PROM,GAL,PLD,CPLD,FPGA等可编程电路或逻辑阵 列编程,得到ASIC。其主要特点是直接提供软件 设计编程,完成ASIC电路功能,不需要再通过集 成电路工艺线加工。 可编程器件的 ASIC 设计种类较多,可以适 应不同的需求。其中的 PLD和 FPGA是用得比较普 遍得可编程器件。适合于短开发周期,有一定复 杂性和电路规模的数字电路设计。尤其适合于从 事电子系统设计的工程人员利用 EDA 工具进行 ASIC设计。

系统级算法级寄存器传输级也称rtl55系统级行为性能描述cpu存储器控制器芯片电路板子系统算法级算法硬件模块数据结构部件间的物理连接rtl状态表alu寄存mux微存储器芯片宏单逻辑级布尔方程门触发器单元布图电路级微分方程晶体管电阻电容管子布图层次行为域结构域物理域56分类内容语言描述verilog语言等功能描述与逻辑描述功能设计功能图逻辑设计逻辑图电路设计电路图版图设计符号式版图版图举例

1.4.2.半定制设计方法简述

半定制设计方法又分成基于标准单元的设计方 法和基于门阵列的设计方法。 基于标准单元的设计方法是:将预先设计好的 称为标准单元的逻辑单元,如与门,或门,多路开 关,触发器等,按照某种特定的规则排列,与预先 设计好的大型单元一起组成ASIC。基于标准单元的 ASIC又称为CBIC(Cell based IC)。 基于门阵列的设计方法是在预先制定的具有晶 体管阵列的基片或母片上通过掩膜互连的方法完成 专用集成电路设计。 半定制主要适合于开发周期短,低开发成本、 投资、风险小的小批量数字电路设计。

专用集成电路设计桶形移位器

专用集成电路设计桶形移位器

桶形移位器是一种用于数字信号处理的电路,它可以实现数字信号的移位操作。

它的名称源于它的物理形状,类似于一个桶子,内部有多个级联的移位寄存器。

桶形移位器可以用于数据压缩、加密解密、数字滤波等应用领域。

专用集成电路设计的桶形移位器通常采用硅片级别的设计,通过布图、仿真、测试等过程来实现电路的功能。

设计时需要考虑电路的功耗、速度、面积等指标,以满足应用场景的需求。

此外,由于桶形移位器的级联结构,还需要考虑电路的抖动、噪声等问题,以保证电路的可靠性和稳定性。

在实际应用中,桶形移位器通常与其他数字电路结合使用,例如加法器、乘法器、计数器等,以实现复杂的数字信号处理任务。

随着技术的不断进步,桶形移位器的设计也在不断演进,采用更加先进的工艺和算法,以应对更加复杂的应用需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

专用集成电路课程设计简易电子琴通信工程学院011051班侯珂01105023目录1 引言 (1)1.1设计的目的 (1)1.2设计的基本内容 (1)2 EDA、VHDL简介 (2)2.1EDA技术 (2)2.2硬件描述语言——VHDL (2)2.2.1 VHDL的简介 (2)2.2.2 VHDL语言的特点 (3)2.2.3 VHDL的设计流程 (3)3 简易电子琴设计过程 (4)3.1简易电子琴的工作原理 (4)3.2简易电子琴的工作流程图 (4)3.3简易电子琴中各模块的设计 (5)3.3.1 乐曲自动演奏模块 (6)3.3.2 音调发生模块 (6)3.3.3 数控分频模块 (7)3.3.4 顶层设计 (9)4 系统仿真 (10)5 结束语 (11)收获和体会 .............................................. 错误!未定义书签。

参考文献 . (13)附录 (14)1 引言我们生活在一个信息时代,各种电子产品层出不穷,作为一个计算机专业的学生,了解这些电子产品的基本组成和设计原理是十分必要的,我们学习的是计算机组成的理论知识,而课程设计正是对我们学习的理论的实践与巩固。

本设计主要介绍的是一个用超高速硬件描述语言VHDL设计的一个具有若干功能的简易电子琴,其理论基础来源于计算机组成原理的时钟分频器。

摘要本系统是采用EDA技术设计的一个简易的八音符电子琴,该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,它可以通过按键输入来控制音响。

系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、整合。

本系统功能比较齐全,有一定的使用价值。

关键字电子琴、EDA、VHDL、音调发生1.1 设计的目的本次设计的目的就是在掌握计算机组成原理理论的基础上,了解EDA技术,掌握VHDL硬件描述语言的设计方法和思想,通过学习的VHDL语言结合电子电路的设计知识理论联系实际,掌握所学的课程知识,例如本课程设计就是基于所学的计算机原理中的时钟分频器和定时器的基础之上的,通过本课程设计,达到巩固和综合运用计算机原理中的知识,理论联系实际,巩固所学理论知识,并且提高自己通过所学理论分析、解决计算机实际问题的能力。

1.2 设计的基本内容基于MAX+PLUS平台,运用VHDL语言对简易电子琴的各个模块进行设计,并使用EDA 工具对各模块进行仿真验证。

本设计包含如下三个模块:乐曲自动演奏模块,音调发生模块,数控分频模块,最后把各个模块整合后,通过电路的输入输出对应关系连接起来。

2 EDA、VHDL简介2.1 EDA技术EDA技术是在电子CAD技术基础上发展起来的计算机软件系统,有狭义与广义之分,本设计讨论的是狭义的EDA技术。

它是指以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成软件方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直到对于特定目标芯片的适配编译、逻辑映射、逻辑下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

2.2 硬件描述语言——VHDL2.2.1 VHDL的简介VHDL是一种用来描述数字逻辑系统的“编程语言”它的全名是Very-High-Speed Integrated Circuit HardwareDescription Language,诞生于1982年。

1987年底,VHDL 被IEEE(The Institute of Electrical and Electronics Engineers)和美国国防部确认为标准硬件描述语言。

它源于美国政府于1980年开始启动的超高速集成电路计划,VHDL主要用于描述数字系统的结构、行为、功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件、一个电路模块或一个系统)分成外部(或称可是部分,即端口)和内部(或称不可视部分,既设计实体的内部功能和算法完成部分)两部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

应用VHDL进行工程设计的优点是多方面的。

VHDL 的应用必将成为当前以及未来EDA解决方案的核心,更是整个电子逻辑系统设计的核心。

2.2.2 VHDL语言的特点(1)VHDL具有更强的行为描述能力,从而决定了他成为电子工程领域事实上通用的硬件描述语言。

强大的行为描述能力是避开具体的器件结构,从逻辑行为上描述和设计大规模电子系统的重要保证。

(2)VHDL语句的行为描述能力和程序结构,决定了他具有支持大规模设计的分解和已有设计的再利用功能。

高效、高速完成符合市场需求的必须有多人甚至多个代发组共同并行工作才能实现的大规模系统设计。

VHDL中设计实体的概念、程序包的概念、设计库的概念为设计的分解和并行工作提供了有利的支持。

(3)VHDL丰富的仿真语句和库函数,使得在任何大系统的设计早期,就能查验设计系统的功能可行性,随时可对设计进行仿真模拟,使设计者对整个工程的结构和功能可行性做出判断。

(4)用VHDL完成的一个确定的设计,可以利用EDA工具进行逻辑综合和优化,并自动的把VHDL描述设计转变成门级网表(根据不同的实现芯片)。

(5)VHDL对设计的描述具有相对独立性。

设计者可以不懂硬件的结构,也不必管理最终设计实现的目标器件是什么,而进行独立的设计。

正因为VHDL的硬件描述与具体的工艺技术和硬件结构无关,所以VHDL设计程序的硬件实现目标器件有广阔的悬着范围。

(6)VHDL具有类属描述语句和子程序调用等程序,对于完成的设计,在不改变源程序的条件下,只需要改变类属参数量或者函数,就能轻易地改变设计的规模和结构。

2.2.3 VHDL的设计流程用VHDL语言设计电路的流程:在用VHDL语言来设计电路时,主要的过程是这样的:(1)创建VHDL设计工程及使用文本编辑器输入设计源文件。

(2)使用编译工具编译源文件。

VHDL的编译器有很多,ACTIVE公司,MODELSIM公司,SYNPLICITY公司,SYNOPSYS公司,VERIBEST公司等都有自己的编译器。

(3)目标器件的选择和源程序的编译及综合。

(4)编辑测试文件及器件引脚的锁定和适配。

(5)系统的功能仿真。

对进入功能仿真,给测试向量赋值,再设置波形的观察格式。

作为一个独立的设计项目而言,仿真文件的提供足可以证明你设计的完整性。

(6)连接硬件测试系统,进行下载操作,再通过硬件系统进行测试。

(7)综合。

综合的目的是在于将设计的源文件由语言转换为实际的电路。

这一部分的最终目的是生成门电路级的网表(Netlist)。

(8)布局、布线。

这一步的目的是生成用于烧写的编程文件。

在这一步,将用到第(7)步生成的网表并根据CPLD/FPG厂商的器件容量,结构等进行布局、布线。

这就好像在设计PCB时的布局布线一样。

先将各个设计中的门根据网表的内容和器件的结构放在器件的特定部位。

然后,在根据网表中提供的各门的连接,把各个门的输入输出连接起来。

(9)后仿真。

这一步主要是为了确定你的设计在经过布局布线之后,是不是还满足你的设计要求。

3 简易电子琴设计过程3.1简易电子琴的工作原理音乐产生原理及硬件设计由于一首音乐是许多不同的音阶组成的,而每个音阶对应着不同的频率,这样我们就可以利用不同的频率的组合,即可构成我们所想要的音乐了,3.2简易电子琴的工作流程图开始TO初始化并开中断允放TO中断按键按下是否成功识别按键功能根据按键功能,装入音符T到TO中启动TO工作按键释放是否成功?停止TO工作TO中断入重装THO,TLO初值P1.0取反中断返回图3.2 简易电子琴的工作流程图3.3简易电子琴中各模块的设计为了更清楚的了解电子琴的工作过程,我们利用EDA工具(本课程设计Max+plus)对各个模块实施时序仿真(Timing Simulation),由自顶向下的设计方式,最后将三个模块进行整合,做出简易电子琴整个系统的时序仿真图。

3.3.1 乐曲自动演奏模块乐曲自动演奏模块的作用是产生8位发声控制输入信号。

当进行自动演奏时,由存储在此模块中的8位二进制作为发声控制输入,从而自动演奏乐曲。

这段模块的原理图如图3.3所示:CLKAUTO INDEX0[7.0]INDEX2[7.0]3.3 乐曲自动演奏模块原理图乐曲自动演奏模块可以由VHDL语言来实现,下面是一段主要代码:BEGINIF AUTO='0'THENCASE COUNT ISWHEN 0=>INDEX0<="00000100"; --3WHEN 1=>INDEX0<="00000100"; --3WHEN 2=>INDEX0<="00000100"; --3WHEN 3=>INDEX0<="00000100"; --3WHEN 29=>INDEX0<="00000100"; --3WHEN 30=>INDEX0<="00000010"; --2WHEN 31=>INDEX0<="00000010"; --2END CASE;ELSE INDEX0<=INDEX2;END IF;END PROCESS;3.3.2 音调发生模块音调发生模块的作用是产生音阶的分频预置值。

当8位发声控制输入信号中的某一位为高电平时,则对应某一音阶的数值将输出,该数值即为该音阶的分频预置值,分频预置值控制数控分频模块进行分频,由此可得到每个音阶对应的频率。