1F-1504 _ REV

英格索兰无油螺杆机操作维护手册

O.D.P. 开式电机 (IP23)

ppm 百万分之一

cs

捷克语

da

丹麦语

de

德语

el

希腊语

en

英语

es

西班牙语

et

爱沙尼亚语

fi

芬兰语

fr

法语

hu

匈牙利语

it

意大利语

lt

立陶宛语

lv

拉脱维亚语

mt

马其他语

nl

荷兰语

no

挪威语

pl

波兰语

pt

葡萄牙语

sk

斯洛伐克语

sl

撕洛文尼亚语

sv

瑞典语

zh

中文

IRN90-160K-OF 与 IRN125-200H-OF

确认维修人员接受过足够的培训,现职,并阅读过 《维修手册》。

危险

表示如果忽视所出现的危险,将会导致严重伤害、死亡或财 产损失。

警告

表示如果忽视所出现的危险,则可能导致严重伤害、死亡或 财产损失。

5.2 安全预防措施

概览

压缩空气和电都很危险。在对空压机进行任何维修之前,一定 要切断、锁住和标记电源并将空压机中的压力全部释放。

操作过程中所有保护措施必须到位,并将门 / 盖关闭。

本担保不包括腐蚀、磨损或正常损耗。性能担保仅限于本公司建议内已经说明的部分。除满足性能担保责任限于具体检测的情况 外,本公司的担保方式和期限以上文为依据。

本公司除标题内容以外不作任何其他明示或暗示的担保或表示,也不承诺任何适销性和特殊适用性的暗示担保。

本公司以上述方式及期限对任何明显或潜在的非达标设备的修正,将构成本公司履行对该非达标设备的全部责任,不管该责任的 依据是合同、担保过失、赔偿还是与该设备有关或由该设备产生的严格责任或其他责任。

ISP1504_USB

34 .80 7IRELESS IMPORTANT NOTICEDear customer,As from August 2nd2008, the wireless operations of NXP have moved to a new company,ST-NXP Wireless.As a result, the following changes are applicable to the attached document.●Company name - NXP B.V. is replaced with ST-NXP Wireless.●Copyright - the copyright notice at the bottom of each page “© NXP B.V. 200x. Allrights reserved”, shall now read: “© ST-NXP Wireless 200x - All rights reserved”.●Web site - is replaced with ●Contact information- the list of sales offices previously obtained by sendingan email to salesaddresses@ , is now found at under Contacts.If you have any questions related to the document, please contact our nearest sales office.Thank you for your cooperation and understanding.ST-NXP Wireless34 .80 7IRELESS1.General descriptionThe ISP1504 is a Universal Serial Bus (USB) On-The-Go (OTG) transceiver that is fully compliant with Universal Serial Bus Specification Rev.2.0,On-The-Go Supplement to the USB 2.0 Specification Rev.1.3 and UTMI+ Low Pin Interface (ULPI) Specification Rev.1.1.The ISP1504 can transmit and receive USB data at high-speed (480Mbit/s), full-speed (12Mbit/s) and low-speed (1.5Mbit/s), and provides a pin-optimized, physical layer front-end attachment to USB host, peripheral and OTG devices.It is ideal for use in portable electronic devices, such as mobile phones, digital still cameras, digital video cameras, Personal Digital Assistants (PDAs) and digital audio players. It allows USB Application-Specific Integrated Circuits (ASICs), Programmable Logic Devices (PLDs) and any system chip set to interface with the physical layer of the USB through a 12-pin interface.The ISP1504 can interface to the link with digital I/O voltages in the range of 1.65V to 3.6V .The ISP1504 is available in HVQFN32 package.2.FeaturesI Fully complies with:N Universal Serial Bus Specification Rev.2.0N On-The-Go Supplement to the USB 2.0 Specification Rev.1.3N UTMI+ Low Pin Interface (ULPI) Specification Rev.1.1I Interfaces to host,peripheral and OTG device cores;optimized for portable devices or system ASICs with built-in USB OTG device coreI Complete Hi-Speed USB physical front-end solution that supports high-speed (480Mbit/s), full-speed (12Mbit/s) and low-speed (1.5Mbit/s)N Integrated 45Ω±10% high-speed termination resistors, 1.5k Ω±5% full-speed device pull-up resistor, and 15k Ω±5% host termination resistorsN Integrated parallel-to-serial and serial-to-parallel converters to transmit and receive N USB clock and data recovery to receive USB data up to ±500ppmN Insertion of stuff bits during transmit and discarding of stuff bits during receive N Non-Return-to-Zero Inverted (NRZI) encoding and decodingN Supports bus reset, suspend, resume and high-speed detection handshake (chirp)I Complete USB OTG physical front-end that supports Host Negotiation Protocol (HNP)and Session Request Protocol (SRP)ISP1504A; ISP1504CULPI Hi-Speed Universal Serial Bus On-The-Go transceiverRev. 03 — 7 April 2008Product data sheetN Integrated 5V charge pump; also supports external charge pump or 5V V BUSswitchN Complete control over bus resistorsN Data line and V BUS pulsing session request methodsN Integrated V BUS voltage comparatorsN Integrated cable (ID) detectorI Highly optimized ULPI-compliantN60MHz, 8-bit interface between the core and the transceiverN Supports 60MHz output clock configurationN Integrated Phase-Locked Loop (PLL) supporting one crystal or clock frequency:19.2MHz (ISP1504ABS) and 26MHz (ISP1504CBS)N Fully programmable ULPI-compliant register setN Internal Power-On Reset (POR) circuitI Flexible system integration and very low current consumption, optimized for portabledevicesN Power-supply input range is 3.0V to 3.6VN Internal voltage regulator supplies 3.3V and 1.8VN Charge pump regulator outputs 4.75V to 5.25V at a current of up to 50mA,tunable using an external capacitorN Supports external V BUS charge pump or 5V V BUS switch:External V BUS source is controlled using the PSW_N pin; open-drain PSW_Nallows per-port or ganged power controlDigital FAULT input to monitor the external V BUS supply statusN Pin CHIP_SELECT_N 3-states the ULPI interface, allowing bus reuse for otherapplicationsN Supports wide range interfacing I/O voltage of1.65V to3.6V;separate I/O voltagepins minimize crosstalkN Typical operating current of 10mA to 48mA, depending on the USB speed andbus utilization; not including the charge pumpN Typical suspend current of 35µAI Full industrial grade operating temperature range from−40°C to +85°CI4kV ElectroStatic Discharge (ESD) protection at pins DP, DM, ID, V BUS and GNDI Available in a small HVQFN32 (5mm×5mm) Restriction of Hazardous Substances(RoHS) compliant, halogen-free and lead-free package3.ApplicationsI Digital still cameraI Digital TVI Digital Video Disc (DVD) recorderI External storage device, for example:N Magneto-Optical (MO) driveN Optical drive: CD-ROM, CD-RW, DVDN Zip driveI Mobile phoneI MP3 playerI PDA I Printer I ScannerI Set-T op Box (STB)I Video camera4.Ordering information[1]The package marking is the first line of text on the IC package and can be used for IC identification.Table 1.Ordering informationPartPackageType numberMarkingCrystal or clockfrequency Name DescriptionVersionISP1504ABS 504A [1]19.2MHz HVQFN32plastic thermal enhanced very thin quad flat package;no leads; 32terminals; body 5×5×0.85mm SOT617-1ISP1504CBS504C [1]26MHzHVQFN32plastic thermal enhanced very thin quad flat package;no leads; 32terminals; body 5×5×0.85mmSOT617-15.Block diagramFig 1.Block diagramREGISTER MAPULPI INTERFACE CONTROLLERUSB DATA SERIALIZERUSB DATA DESERIALIZER HI-SPEED USB ATXDMDPSTP DIR NXTDATA [7:0]8452120191, 23 to 26,28, 31, 32004aaa478CLOCK27TERMINATION RESISTORSIDDETECTORV BUSCOMPARATORSON-THE-GO MODULESRP CHARGE AND DISCHARGE RESISTORS5 V CHARGE PUMP SUPPLYPOWER-ON RESETPLLCRYSTAL OSCILLATORVOLTAGE REGULATORBAND GAP REFERENCE VOLTAGERREF3internal powerV CC11REG3V3REG1V81418RESET_NGLOBAL RESETGLOBAL CLOCKSXTAL2XTAL11516V CC(I/O)2, 22, 30interface voltagePSW_NDRV V BUS EXTERNALDRV V BUS ID7V BUS13FAULT 612CPGND810C_A C_B 9ISP150417ULPIINTERFACEUSB CABLEV REFCHIP_SELECT_N29V BUS VALID EXTERNAL6.Pinning information6.1Pinning6.2Pin descriptionFig 2.Pin configuration HVQFN32; top view004aaa479ISP1504T ransparent top viewRESET_N ID CPGNDREG1V8FAULTDIR DP STP DM NXT RREF V CC(I/O)V CC(I/O)DATA7DATA0DATA6C _B C _A V C C P S W _N V B U S R E G 3V 3X T A L 1X T A L 2D A T A 1D A T A 2V C C (I /O )C H I P _S E L E C T _ND A T A 3C L O C KD A T A 4D A T A 58177186195204213222231249101112131415163231302928272625terminal 1index areaTable 2.Pin descriptionSymbol [1][2]Pin Type [3]Description [4]DA T A01I/O pin 0 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down V CC(I/O)2P I/O supply rail RREF 3AI/O resistor referenceDM 4AI/O data minus (D −) pin of the USB cable DP 5AI/O data plus (D+) pin of the USB cableFAULT 6I input pin for the external V BUS digital overcurrent or fault detector signal plain input; 5V tolerantID7Iidentification (ID) pin of the micro-USB cableIf this pin is not used, it is recommended to connect to REG3V3.plain input; TTL levelCPGND 8P charge pump groundC_B 9AI/O flying capacitor pin connection for the charge pump C_A 10AI/O flying capacitor pin connection for the charge pump V CC 11P input supply voltage or battery sourcePSW_N12ODactive LOW external V BUS power switch or external charge pump enable open-drain; 5V tolerant[1]Symbol names ending with an underscore N, for example, NAME_N, indicate active LOW signals.[2]For details on external components required on each pin, see bill of materials and application diagrams in Section 16.[3]I = input; O = output; I/O = digital input/output; OD = open-drain output; AI = analog input; AO = analog output; AI/O = analog input/output; P = power or ground pin.[4]A detailed description of these pins can be found in Section 7.9.V BUS 13AI/O V BUS pin of the USB cable 5V tolerantREG3V314P 3.3V regulator output XTAL115AI crystal oscillator or clock input XTAL216AO crystal oscillator outputRESET_N 17I active LOW, asynchronous reset input plain inputREG1V818P 1.8V regulator output DIR 19O ULPI direction signalslew-rate controlled output (1ns)STP 20I ULPI stop signalplain input; programmable pull up NXT 21O ULPI next signalslew-rate controlled output (1ns)V CC(I/O)22P I/O supply railDAT A723I/O pin 7 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down DAT A624I/O pin 6 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down DAT A525I/O pin 5 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down DAT A426I/O pin 4 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down CLOCK 27O 60MHz clock outputslew-rate controlled output (1ns)DAT A328I/O pin 3 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down CHIP_SELECT_N 29I active LOW chip select plain input V CC(I/O)30P I/O supply railDAT A231I/O pin 2 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull down DAT A132I/O pin 1 of the bidirectional ULPI data busslew-rate controlled output (1ns); plain input; programmable pull downGNDdie padPground supply;down bonded to the exposed die pad (heat sink);to be connected to the PCB groundTable 2.Pin description …continuedSymbol [1][2]Pin Type [3]Description [4]7.Functional description7.1ULPI interface controllerThe ISP1504 provides a 12-pin interface that is compliant with UTMI+ Low Pin Interface(ULPI) Specification Rev.1.1. This interface must be connected to the USB link.The ULPI interface controller provides the following functions:•ULPI-compliant interface and register set•Allows full control over the USB peripheral, host and OTG functionality•Parses the USB transmit and receive data•Prioritizes the USB receive data,USB transmit data,interrupts and register operations•Low-power mode•Control of the V BUS charge pump or external source•V BUS monitoring, charging and discharging•6-pin serial mode and 3-pin serial mode•Generates RXCMDs; status updates•Maskable interrupts•Control over the ULPI bus state, allowing pins to 3-state or attach active weakpull-down resistorsFor more information on the ULPI protocol, see Section9.7.2USB data serializer and deserializerThe USB data serializer prepares data to transmit on the USB bus. To transmit data, theUSB link sends a transmit command and data on the ULPI bus. The serializer performsparallel-to-serial conversion, bit stuffing and NRZI encoding. For packets with a PID, theserializer adds a SYNC pattern to the start of the packet, and an EOP pattern to the endof the packet. When the serializer is busy and cannot accept any more data, the ULPIinterface controller deasserts NXT.The USB data deserializer decodes data received from the USB bus. When data isreceived, the deserializer strips the SYNC and EOP patterns, and then performsserial-to-parallel conversion, NRZI decoding and discarding of stuff bits on the datapayload. The ULPI interface controller sends data to the USB link by asserting DIR, andthen asserting NXT whenever a byte is ready. The deserializer also detects variousreceive errors, including bit stuff errors, elasticity buffer underrun or overrun, andbyte-alignment errors.7.3Hi-Speed USB (USB2.0) ATXThe Hi-Speed USB ATX block is an analog front-end containing the circuitry needed totransmit, receive and terminate the USB bus in high-speed, full-speed and low-speed, forUSB peripheral, host and OTG implementations. The following circuitry is included:•Differential drivers to transmit data at high-speed, full-speed and low-speed•Differential and single-ended receivers to receive data at high-speed, full-speed and low-speed•Squelch circuit to detect high-speed bus activity•High-speed disconnect detector•45Ω high-speed bus terminations on DP and DM for peripheral and host modes• 1.5kΩ pull-up resistor on DP for full-speed peripheral mode•15kΩ bus terminations on DP and DM for host and OTG modesFor details on controlling resistor settings, see Table8.7.4Voltage regulatorThe ISP1504 contains a built-in voltage regulator that conditions the V CC supply for use inside the ISP1504. The voltage regulator:•Supports input supply range of 3.0V<V CC<3.6V•Supplies internal circuitry with 1.8V and 3.3VRemark:The REG1V8 and REG3V3 pins require external decoupling capacitors. Fordetails, see Section16.7.5Crystal oscillator and PLLThe ISP1504 has a built-in crystal oscillator and a Phase-Locked Loop (PLL) for clock generation.The crystal oscillator takes a sine-wave input from an external crystal, on the XTAL1 pin, and converts it to a square wave clock for internal use. Alternatively, a square wave clock of the same frequency can also be directly driven into the XTAL1 pin. Using an existing square wave clock can save the cost of the crystal and also reduce the board size.The PLL takes the square wave clock from the crystal oscillator,and multiplies or divides it into various frequencies for internal use.The PLL produces the following frequencies, irrespective of the clock source:•60MHz clock for the ULPI interface controller• 1.5MHz for the low-speed USB data•12MHz for the full-speed USB data•480MHz for the high-speed USB data•Other internal frequencies for data conversion and data recovery7.6OTG moduleThis module contains several sub-blocks that provide all the functionality required by the USB OTG specification. Specifically, it provides the following circuits:•The ID detector to sense the ID pin of the micro-USB cable.The ID pin dictates which device is initially configured as the host and which as the peripheral.•V BUS comparators to determine the V BUS voltage level. This is required for the V BUS detection, SRP and HNP.•Resistors to temporarily charge and discharge V BUS. This is required for SRP.•Charge pump to provide5V power on V BUS.The downstream peripheral can draw its power from the ISP1504 V BUS.7.6.1ID detectorThe ID detector detects which end of the micro-USB cable is plugged in. The detectormust first be enabled by setting the ID_PULLUP register bit to logic1. If the ISP1504senses a value on ID that is different from the previously reported value, an RXCMDstatus update will be sent to the USB link, or an interrupt will be asserted.•If the micro-B end of the cable is plugged in, the ISP1504 will report that ID_GND is logic1. The USB link must change to peripheral mode.•If the micro-A end of the cable is plugged in, the ISP1504 will report that ID_GND is logic0. The USB link must change to host mode.7.6.2V BUS comparatorsThe ISP1504 provides three comparators, V BUS valid comparator, session validcomparator and session end comparator, to detect the V BUS voltage level.7.6.2.1V BUS valid comparatorThis comparator is used by hosts and A-devices to determine whether the voltage onV BUS is at a valid level for operation. The ISP1504 minimum threshold for the V BUS validcomparator is V A_VBUS_VLD.Any voltage on V BUS below V A_VBUS_VLD is considered invalid.During power-up, it is expected that the comparator output will be ignored.7.6.2.2Session valid comparatorThe session valid comparator is a TTL-level input that determines when V BUS is highenough for a session to start.Peripherals,A-devices and B-devices use this comparator to detect when a session is started. The A-device also uses this comparator to determinewhen a session is completed.The session valid threshold of the ISP1504is V B_SESS_VLD, with a hysteresis of V hys(B_SESS_VLD).7.6.2.3Session end comparatorThe ISP1504 session end comparator determines when V BUS is below the B-devicesession end threshold.The B-device uses this threshold to determine when a session has ended. The session end threshold of the ISP1504 is V B_SESS_END.7.6.3SRP charge and discharge resistorsThe ISP1504 provides on-chip resistors for short-term charging and discharging of V BUS.These are used by the B-device to request a session, prompting the A-device to restorethe V BUS power. First, the B-device makes sure that V BUS is fully discharged from theprevious session by setting the DISCHRG_VBUS register bit to logic1 and waiting forSESS_END to be logic1. Then the B-device charges V BUS by setting the CHRG_VBUSregister bit to logic1. The A-device sees that V BUS is charged above the session validthreshold and starts a session by turning on the V BUS power.7.6.4Charge pumpThe ISP1504 uses a built-in charge pump to supply current to V BUS at a nominal voltage of 5V . The charge pump works as a capacitive DC-DC converter. An external holding capacitor,C cp(C_A)-(C_B),is required between the C_A and C_B pins as shown in Figure 3,which also shows a typical OTG V BUS load. The value of C cp(C_A)-(C_B) depends on the amount of current drive required.If the internal charge pump is not used,the C cp(C_A)-(C_B)capacitor is not required.For details on the C_A and C_B pins, see Section 7.9.8.7.7Band gap reference voltageThe band gap circuit provides a stable internal voltage reference to bias the analogcircuitry.The band gap requires an accurate external reference resistor R RREF connected between the RREF and GND pins. For details, see Section 16.7.8Power-On Reset (POR)The ISP1504 has an internal power-on reset circuit that resets all internal logic on power-up. The ULPI interface is also reset on power-up.Remark:When CLOCK starts toggling after power-up, the USB link must issue a reset command over the ULPI bus to ensure correct operation of the ISP1504.7.9Detailed description of pins7.9.1DATA[7:0]The ISP1504 is a Physical layer (PHY) containing a USB transceiver. DATA[7:0] is the bidirectional data bus. The USB link must drive DATA[7:0] to LOW when the ULPI bus is idle. When the link has data to transmit to the PHY , it drives a nonzero value.The data bus can be reconfigured to carry various data types, as given in Section 8 and Section 9.The DA TA[7:0] pins can be 3-stated by driving pin CHIP_SELECT_N to HIGH. Weakpull-down resistors are incorporated into the DATA[7:0]pins as part of the interface protect feature. For details, see Section 9.3.1.Fig 3.External capacitors connection004aaa515ISP1504V BUSC_BC_AC cp(C_A)-(C_B)OTG V BUS4.7 µF0.1 µF7.9.2V CC(I/O)The input power pin that sets the I/O voltage level.For details,see Section12,Section13 and Section16. V CC(I/O) provides power to on-chip pads of the following pins:•CHIP_SELECT_N•CLOCK•DAT A[7:0]•DIR•NXT•RESET_N•STP7.9.3RREFResistor reference analog I/O pin. A resistor, R RREF, must be connected between RREF and GND, as shown in Section16. This provides an accurate voltage reference thatbiases internal analog circuitry.Less accurate resistors cannot be used and will render the ISP1504 unusable.7.9.4DP and DMThe DP (data plus) and DM (data minus) are USB differential data pins. These must beconnected to the D+ and D− pins of the USB receptacle.7.9.5FAULTIf an external V BUS overcurrent or fault circuit is used, the output fault indicator of thatcircuit can be connected to the ISP1504FAULT input pin.The ISP1504will inform the link of V BUS fault events by sending RXCMDs on the ULPI bus.To use the FAULT pin,the link must:•Set the USE_EXT_VBUS_IND register bit to logic1.•Set the polarity of the external fault signal using the IND_COMPL register bit.•Set the IND_P ASSTHRU register bit to logic1.If the FAULT pin is not used, it is recommended to connect to GND.7.9.6IDFor OTG implementations, the ID (identification) pin is connected to the ID pin of themicro-USB receptacle.As defined in On-The-Go Supplement to the USB2.0Specification Rev.1.3, the ID pin dictates the initial role of the link. If ID is detected as HIGH, the linkmust assume the role of a peripheral. If ID is detected as LOW, the link must assume ahost role. Roles can be swapped at a later time by using HNP.If the ISP1504is not used as an OTG PHY,but as a standard USB host or peripheral PHY, the ID pin must be connected to REG3V3.7.9.7CPGNDCPGND indicates the analog ground for the on-board charge pump.CPGND must always be connected to ground, even when the charge pump is not used.7.9.8C_A and C_BThe C_A and C_B pins are to connect the flying capacitor of the charge pump.The output current capability of the charge pump depends on the value of the capacitor used, as shown in T able 3. For maximum efficiency, place capacitors as close as possible to pins.For details, see Section 16.If the charge pump is not used, C_A and C_B must be left floating (not connected).7.9.9V CCV CC is the main input supply voltage for the ISP1504. Decoupling capacitors are recommended. For details, see Section 16.7.9.10PSW_NPSW_N is an active LOW, open-drain output pin. This pin can be connected to an active LOW, external V BUS switch or charge pump enable circuit to control the external V BUSpower source.An external pull-up resistor,R pullup ,is required when PSW_N is used.This pin is open-drain, allowing ganged-mode power control for multiple USB ports. For application details, see Section 16.If the link is in host mode, it can enable the external V BUS power source by setting the DRV_VBUS_EXT bit in the OTG Control register to logic 1. The ISP1504 will drive PSW_N to LOW to enable the external V BUS power source. If the link detects anovercurrent condition (the V BUS state in RXCMD is not 11b), it must disable the external V BUS power source by setting DRV_VBUS_EXT to logic 0.7.9.11V BUSThis pin acts as an input to V BUS comparators, and also as a power pin for the charge pump, and SRP charge and discharge resistors.When the DRV_VBUS bit of the OTG Control register is set to logic 1,the ISP1504drives V BUS to a voltage of 4.4V to 5.25V , with a minimum output current capability of 8mA.The V BUS pin requires a capacitive load as shown in Section 16.Fig 4.Charge pump capacitorTable 3.Recommended charge pump capacitor valueC cp(C_A)-(C_B)I L (max)22nF 8mA 270nF50mA004aaa516I LISP1504V BUSC_A C_BC cp(C_A)-(C_B)To prevent electrical overstress, it is strongly recommended that you attach a seriesresistor on the V BUS pin (R VBUS). R VBUS must not be attached when using the ISP1504internal charge pump. For details, see Section16.7.9.12REG3V3 and REG1V8Regulator output voltage. These supplies are used to power the ISP1504 internal digitaland analog circuits, and must not be used to power external circuits.For correct operation of the regulator, it is recommended that you connect REG3V3 andREG1V8 to decoupling capacitors. For examples, see Section16.7.9.13XTAL1 and XTAL2XT AL1is the crystal input,and XT AL2is the crystal output.The allowed frequency on the XT AL1 pin depends on the ISP1504 product version.If the link requires a 60MHz clock from the ISP1504, then either a crystal must beattached, or a clock of the same frequency must be driven into XTAL1, with XTAL2 leftfloating.If a crystal is attached,it requires external load capacitors to GND on each terminal of the crystal. For details, see Section16.If at any time the system wants to stop the clock on XTAL1, the link must first put theISP1504 into low-power mode. The clock on XTAL1 must be restarted before low-powermode is exited.7.9.14RESET_NAn active LOW asynchronous reset pin that resets all circuits in the ISP1504. TheISP1504 contains an internal power-on reset circuit, and therefore using the RESET_Npin is optional. If RESET_N is not used, it must be connected to V CC(I/O).For details on using RESET_N, see Section9.3.2.7.9.15DIRULPI direction output pin. Controls the direction of the data bus. By default, the ISP1504holds DIR at LOW, causing the data bus to be an input. When DIR is LOW, the ISP1504listens for data from the link. The ISP1504 pulls DIR to HIGH only when it has data tosend to the link, which is for one of two reasons:•To send the USB receive data,RXCMD status updates and register reads data to the link.•To block the link from driving the data bus during power-up, reset and low-power (suspend) mode.The DIR pin can also be 3-stated by driving CHIP_SELECT_N to HIGH.For details on DIR usage, refer to UTMI+ Low Pin Interface (ULPI) Specification Rev.1.1.7.9.16STPULPI stop input pin. The link must assert STP to signal the end of a USB transmit packetor a register write operation. When DIR is asserted, the link can optionally assert STP toabort the ISP1504, causing it to deassert DIR in the next clock cycle. A weak pull-upresistor is incorporated into the STP pin as part of the interface protect feature.For details, see Section9.3.1.The STP input will be ignored when CHIP_SELECT_N is driven to HIGH.For details on STP usage, refer to UTMI+ Low Pin Interface (ULPI) Specification Rev.1.1.7.9.17NXTULPI next data output pin.The ISP1504holds NXT at LOW,by default.When DIR is LOW and the link is sending data to the ISP1504, NXT will be asserted to notify the link toprovide the next data byte. When DIR is at HIGH and the ISP1504 is sending data to thelink,NXT will be asserted to notify the link that another valid byte is on the bus.NXT is not used for register read data or the RXCMD status update.The NXT pin can also be 3-stated by driving CHIP_SELECT_N to HIGH.For details on NXT usage,refer to UTMI+Low Pin Interface(ULPI)Specification Rev.1.1.7.9.18CLOCKA 60MHz interface clock to synchronize the ULPI bus. The ISP1504 provides twoclocking options:• A crystal is attached between the XT AL1 and XTAL2 pins.• A clock is driven into the XT AL1 pin, with the XTAL2 pin left floating.For details on CLOCK usage, refer to UTMI+ Low Pin Interface (ULPI) SpecificationRev.1.1.7.9.19CHIP_SELECT_NActive LOW chip select pin. If CHIP_SELECT_N is not used, it must be connected toGND. For more information on using CHIP_SELECT_N, see Section9.3.3.7.9.20GND (die pad)Global ground signal, except for the charge pump that uses CPGND. The die pad isexposed on the underside of the package as a ground plate. This acts as a ground to allcircuits in the ISP1504, except the charge pump. To ensure correct operation of theISP1504, GND must be soldered to the cleanest ground available.。

维沙易 Siliconix S11-2419-Rev. C 自动车双渣道 40V 175°C MOS

Automotive Dual N-Channel 40 V (D-S) 175 °C MOSFETFEATURES•Halogen-free According to IEC 61249-2-21Definition•TrenchFET ® Power MOSFET •AEC-Q101 Qualified d•100 % R g and UIS Tested•Compliant to RoHS Directive 2002/95/ECNotesa.Package limited.b.Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2 %.c.When mounted on 1" square PCB (FR4 material).d.Parametric verification ongoing.e.See solder profile (/doc?73257). The PowerPAK SO-8L. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection..f.Rework conditions: manual soldering with a soldering iron is not recommended for leadless components.PRODUCT SUMMARYV DS (V)40R DS(on) (Ω) at V GS = 10 V 0.020R DS(on) (Ω) at V GS = 4.5 V 0.028I D (A) per leg 8ConfigurationDualORDERING INFORMATIONPackagePowerPAK SO-8L Lead (Pb)-free and Halogen-freeSQJ970EP-T1-GE3ABSOLUTE MAXIMUM RATINGS (T C = 25 °C, unless otherwise noted)PA AMETE SYMBOL LIMIT UNIT Drain-Source Voltage V DS40VGate-Source Voltage V GS ± 20Continuous Drain Current aT C = 25 °C I D 8A T C = 125 °C8Continuous Source Current (Diode Conduction)a I S 8Pulsed Drain Current bI DM 32Single Pulse Avalanche Current L = 0.1 mH I AS 28Single Pulse Avalanche Energy E AS 39mJ Maximum Power Dissipation bT C = 25 °C P D 48W T C = 125 °C 16Operating Junction and Storage Temperature Range T J , T stg- 55 to + 175°C Soldering Recommendations (Peak Temperature)e, f260THERMAL RESISTANCE RATINGSPA AMETE SYMBOL LIMIT UNIT Junction-to-Ambient PCB Mount cR thJA 85°C/WJunction-to-Case (Drain)R thJC3.1Notesa.Pulse test; pulse width ≤ 300 μs, duty cycle ≤ 2 %.b.Guaranteed by design, not subject to production testing.c.Independent of operating temperature.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS (T C = 25 °C, unless otherwise noted)PA AMETE R SYMBOLTEST CONDITIONS MIN.TYP.MAX.UNITStaticDrain-Source Breakdown Voltage V DS V GS = 0, I D = 250 μA 40--V Gate-Source Threshold Voltage V GS(th)V DS = V GS , I D = 250 μA 1.5 2.0 2.5Gate-Source LeakageI GSS V DS = 0 V, V GS = ± 20 V--± 100nAZero Gate Voltage Drain Current I DSS V GS = 0 V V DS = 40 V --1μA V GS = 0 V V DS = 40 V, T J = 125 °C --50V GS = 0 V V DS = 40 V, T J = 175 °C--150On-State Drain Current aI D(on)V GS = 10 V V DS ≥ 5 V 30--A Drain-Source On-State Resistance aR DS(on)V GS = 10 VI D = 10.2 A -0.0160.020ΩV GS = 4.5 V I D = 8.7 A-0.0220.028V GS = 10 V I D = 10.2 A, T J = 125 °C -0.0250.031V GS = 10 VI D = 10.2 A, T J = 175 °C-0.0290.036Forward Transconductance b g fsV DS = 15 V, I D = 10.2 A-28-S Dynamic bInput Capacitance C issV GS = 0 V V DS = 20 V, f = 1 MHz -17302165pFOutput CapacitanceC oss -260325Reverse Transfer Capacitance C rss -130165Total Gate Charge c Q gV GS = 10 V V DS = 20 V, I D = 10.2 A -3455nC Gate-Source Charge c Q gs - 5.2-Gate-Drain Charge c Q gd - 6.5-Gate Resistance R g f = 1 MHz0.71 3.927.12ΩTurn-On Delay Time c t d(on)V DD = 20 V, R L = 20 ΩI D ≅ 1 A, V GEN = 10 V, R g = 1 Ω-1015ns Rise Time ct r-812Turn-Off Delay Time c t d(off) -5075Fall Time c t f -1015Source-Drain Diode Ratings and Characteristics bPulsed Current a I SM --32A Forward VoltageV SDI F = 2.9 A, V GS = 0-0.81.1VTYPICAL CHARACTERISTICS(T ATransfer Characteristics Capacitance Transfer Characteristics TransconductanceGate ChargeTYPICAL CHARACTERISTICS(T A = 25 °C, unless otherwise noted)On-Resistance vs. Drain Current Source Drain Diode Forward Voltage On-Resistance vs. Junction Temperature Drain-Source Breakdown vs. Junction Temperature On-Resistance vs. Gate-to-Source VoltageThreshold VoltageTHERMAL RATINGS(T A = 25 °C, unless otherwise noted)Safe Operating AreaTHERMAL RATINGS(T A = 25 °C, unless otherwise noted)Normalized Thermal Transient Impedance, Junction-to-CaseNote•The characteristics shown in the two graphs- Normalized Transient Thermal Impedance Junction-to-Ambient (25 °C)- Normalized Transient Thermal Impedance Junction-to-Case (25 °C)are given for general guidelines only to enable the user to get a “ball park” indication of part capabilities. The data are extracted from single pulse transient thermal impedance characteristics which are developed from empirical measurements. The latter is valid for the part mounted on printed circuit board - FR4, size 1" x 1" x 0.062", double sided with 2 oz. copper, 100 % on both sides. The part capabilities can widely vary depending on actual application parameters and operating conditions.Vishay Silico nix maintains wo rldwide manufacturing capability. Pro ducts may be manufactured at o ne o f several qualified lo catio ns. Reliability data fo r Silico n Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?65282.Legal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.。

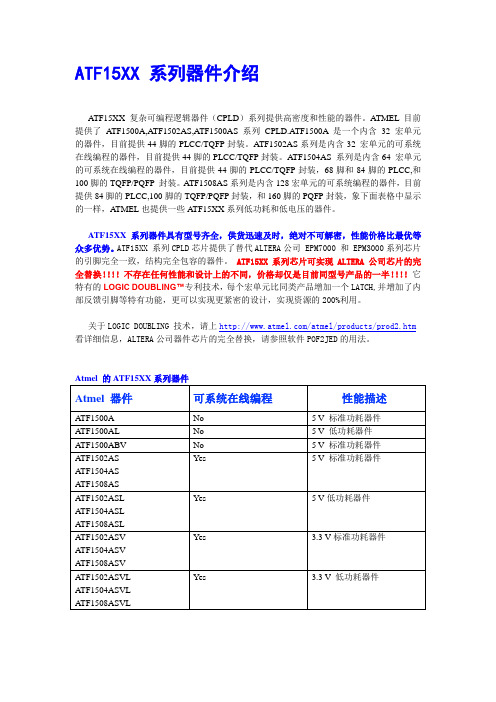

ATF15XX 系列器件介绍

ATF15XX 系列器件介绍A TF15XX 复杂可编程逻辑器件(CPLD)系列提供高密度和性能的器件。

A TMEL 目前提供了ATF1500A,A TF1502AS,A TF1500AS 系列CPLD.ATF1500A 是一个内含32 宏单元的器件,目前提供44脚的PLCC/TQFP封装。

ATF1502AS系列是内含32 宏单元的可系统在线编程的器件,目前提供44脚的PLCC/TQFP封装。

A TF1504AS 系列是内含64 宏单元的可系统在线编程的器件,目前提供44脚的PLCC/TQFP封装,68脚和84脚的PLCC,和100脚的TQFP/PQFP 封装。

A TF1508AS系列是内含128宏单元的可系统编程的器件,目前提供84脚的PLCC,100脚的TQFP/PQFP封装,和160脚的PQFP封装,象下面表格中显示的一样,ATMEL也提供一些ATF15XX系列低功耗和低电压的器件。

ATF15XX 系列器件具有型号齐全,供货迅速及时,绝对不可解密,性能价格比最优等众多优势。

ATF15XX 系列CPLD芯片提供了替代ALTERA公司 EPM7000 和 EPM3000系列芯片的引脚完全一致,结构完全包容的器件。

ATF15XX系列芯片可实现ALTERA 公司芯片的完全替换!!!!不存在任何性能和设计上的不同,价格却仅是目前同型号产品的一半!!!!它特有的LOGIC DOUBLING™专利技术,每个宏单元比同类产品增加一个LATCH,并增加了内部反馈引脚等特有功能,更可以实现更紧密的设计,实现资源的200%利用。

关于LOGIC DOUBLING 技术,请上/atmel/products/prod2.htm 看详细信息,ALTERA公司器件芯片的完全替换,请参照软件POF2JED的用法。

下面是ATMEL公司的POF2JED软件的应用向导,这个软件转换一个可编程的输出文件(.POF文件),将它转换为A TMEL公司的可编程文件(.JED 文件),没有任何功能或者性能上的区别。

TF维修手册中文_说明书

镀锌

4

BZ1203

活络接头

1/2”

镀锌

5

BZ1204

三通

1/2”

镀锌

6

BZ1205

8-Q11F-6.4

1/2”

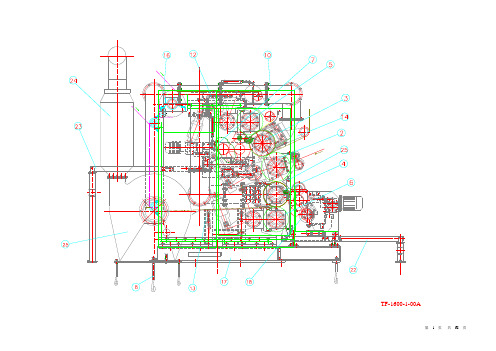

TF-1600-1-1300A

TF-1600-1-1300B

TF-1600-1-1300

序号

图号

名称

规格

备注

1

1301

过纸辊

2

1303

蒸汽箱

3

BZ1301

8-Q11F-6.4

1/2”

GB9877.2

21

BZ0715

胀套

Z2-55*85

GB5867

22

BZ0716

轴承

22209

GB288

23

BZ0717

密封圈

B-60*80*8

GB9877.2

24

BZ0718

轴承

NU209

GB283

25

BZ0719

密封圈

B-60*80*8

GB9877.2

26

BZ0720

汽缸

MAL-CA-25*75-SDB

28

0146

上齿轮

29

BZ0112

万向联轴节

罗曼19

30

BZ0113

O型密封圈

185*3.55

GB3452.1

31

BZ0114

涨套

Z3-100*145

GB5867

32

BZ0115

涨套

Z3-70*110

GB5867

33

BZ0116

轴承

6212

意法半导体电机控制参考指南说明书

电机控制3 意法半导体电机控制生态系统4 PMSM & BLDC电机8 3相感应电机(ACIM)12 步进电机14 直流有刷电机16 通用电机18 开关磁阻电机19 微控制器25 STM32电机控制生态系统29 电机驱动器IC39 电源模块44 功率MOSFET46 IGBT47 600-650 V IGBT系列48 1200 V IGBT系列49 二极管 & 整流器50 晶闸管、双向可控硅和交流开关 52 MOSFET和IGBT栅极驱动器56 碳化硅和氮化镓栅极驱动器58 信号调理ST对电机控制的承诺推进了环保革命。

在环保革命理念的指引下,电机控制正向着更高效电机和驱动器的方向快速发展。

此外,为了支持新技术的市场占有率,需要以最低成本提高集成度,同时提升安全性和可靠性。

ST致力于电机控制方面的研究已有20余年,是最早意识到这些趋势的公司。

意法半导体正通过一系列的创新突飞猛进,诸如集成式智能功率模块和系统级封装、单片式电机驱动器、快速高效的功率开关、具有电压暂态保护功能的可控硅、以及功能强大且安全的微控制器等。

无论您使用哪种电机技术(从传统的和坚固的,到最现代的和最高效的),ST都能够提供合适的电子器件和完整的生态系统(包括一系列评估板、参考设计、固件和开发工具),以简化和加速设计流程。

保持最新资讯更多信息和最新材料,请访问ST网站的控制应用页面http:///motorcontrol3意法半导体电机控制PMSM &永磁同步电机和直流无刷电机因其更高效、运行更安静、更可靠等优点,正在越来越多的应用中替代直流有刷电机。

尽管结构不同,但所有三相永磁电机(BLDC、PMSM或PMAC)都是由脉冲宽度调制(PWM)的三相桥(三个半桥)驱动,以便采用频率幅度可变的电压和电流为电机供电。

为了提供最高水平设计灵活性,ST的产品组合包括面向高压和低压应用的特定产品,如单片驱动IC、功率MOSFET、IGBT、栅极驱动器、功率模块和专用微控制器,用于满足广泛的应用需求。

梭哈7100系列底部挂载驱动器套件标准负载平行扭筒电动机操作与维护手册说明书

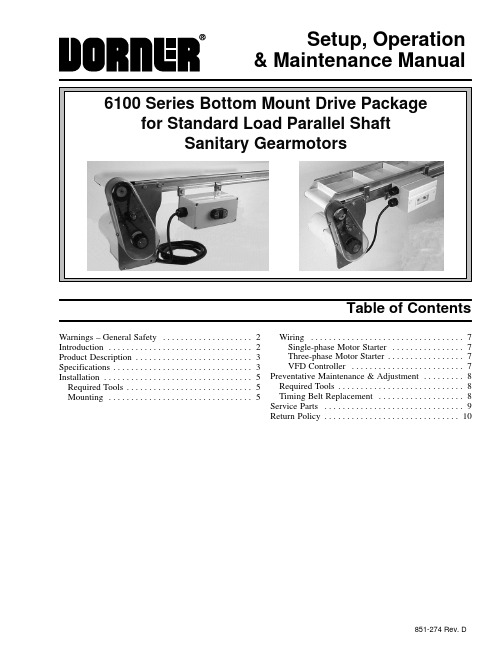

Setup, Operation& Maintenance ManualTable of ContentsWarnings – General Safety2. . . . . . . . . . . . . . . . . . . .Introduction2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Product Description3. . . . . . . . . . . . . . . . . . . . . . . . . . Specifications3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Installation5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Required Tools5. . . . . . . . . . . . . . . . . . . . . . . . . . . . Mounting5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Wiring7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .Single-phase Motor Starter7. . . . . . . . . . . . . . . .Three-phase Motor Starter7. . . . . . . . . . . . . . . . .VFD Controller7. . . . . . . . . . . . . . . . . . . . . . . . . Preventative Maintenance & Adjustment8. . . . . . . . . Required Tools8. . . . . . . . . . . . . . . . . . . . . . . . . . . . Timing Belt Replacement8. . . . . . . . . . . . . . . . . . . Service Parts9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Return Policy10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .851-274 Rev. D6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMM851-274 Rev. D 2Dorner Mfg. Corp.IntroductionIMPORTANT: Some illustrations may showguards removed. Do NOT operate equipment with-out guards.Upon receipt of shipment:D Compare shipment with packing slip. Contact factory regarding discrepancies.D Inspect packages for shipping damage. Contact carrier regarding damage.D Accessories may be shipped loose. See accessory in-structions for installation.Dorner 6100 Series conveyors are covered by patent number 5174435 and corresponding patents and patent applications in other countries.Dorner ’s Limited Warranty applies.Dorner reserves the right to make changes at any time without notice or obligation.Warnings – General Safety6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMMDorner Mfg. Corp.3851-274 Rev. DRefer to Figure 1 for typical components.A ConveyorB Mounting BracketC GearmotorD Timing Belt TensionerE CoverF Timing BeltG Drive PulleyH Driven Pulley IMotor ControlTypical ComponentsAB DFFigure 1EGCH ISpecificationsGearmotor Mounting Package Models:Example:Drive/Driven Pulleys (See tables 2 & 3)= Flat Belt (or add cleat type)* See “Ordering and Specifications ” Catalog for details.Table 1: Gearmotor SpecificationsProduct DescriptionSpecificationsTable 2: Standard Load Fixed Speed Parallel Shaft 60 Hz Gearmotors(vp) = voltage and phase11 = 115 V, Single-phase23 = 230 V, Three-phaseTable 3: Standard Load Variable Speed Parallel Shaft VFD Gearmotors* At 60 HzNOTE: For belt speed other than those listed,contact factory for details.6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMM851-274 Rev. D4Dorner Mfg. Corp.6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMMDorner Mfg. Corp.5851-274 Rev. DRequired ToolsD Wrenches (for hexagon head fasteners)7 mm & 10 mm D 2.5 mm hex key wrench D Straight edge D Torque wrenchMountingIllustration ReferencesJ Bottom Mounting Plate Assembly K Drive Pulley L Driven Pulley M KeyN M6 x 30 mm, Hexagon Head Screws (2 x)O Timing Belt P CoverQ Accessory Mounting Clips (2x)R M6 x 20 mm, Hexagon Head Screws (2x)S Typical Motor Starter1.Typical components (Figure 2)NOTE: Three-phase Motor Starter shown, Single-phase Starter or VFD Controller similar.J NO Figure 2LMKPRQS2.Locate drive output shaft (T of Figure 3) and removetwo (2) screws (U).TFigure 3U3.Attach bottom mounting plate assembly (J) withscrews (N). Tighten to 92 in-lb (10.4 Nm).Figure 4JN4.Install key (M of Figure 5).Figure 5LMOK5.Wrap timing belt (O) around driven pulley (L) anddrive pulley (K). Install driven pulley (L) onto conveyor shaft.Installation6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMM851-274 Rev. D 6Dorner Mfg. Corp.ing a straight edge (V of Figure 6), align drivenpulley (L) with drive pulley (K). Tighten driven pulley set screws (W).Figure 6LKVW7.Depending on conveyor belt travel (direction 1 or 2),locate timing belt tensioner (X of Figure 7) asshown. Tension timing belt to obtain 0.125¨ (3 mm)deflection for 1.0 lb (456 grams) of force at timingbelt mid-point (Y). Tighten tensioner screw to 92in-lb (10.4 Nm).12YFigure 7NOTE: Do not over-tighten screws (Z of Figure 8).8.Install cover (P of Figure 8) and tighten four (4)screws (Z) to 35 in-lb (4 Nm).Figure 8PZZ9.Attach accessory mounting clips (Q of Figure 9) toconveyor.Figure 9Q NOTE: Three-phase Motor Starter shown,Single-phase Starter similar. For VFD controller mounting, see accessory instructions.10.Attach motor starter (S of Figure 10) to clips withscrews (R). Tighten to 92 in-lb (10.4 Nm).RR Figure 10SInstallation6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMMDorner Mfg. Corp.7851-274 Rev. DWiringSingle-phase Motor StarterNOTE: Power cord must be plugged into a GFI out-let. No additional wiring is required.Three-phase Motor StarterNOTE: 230 volt three-phase manual motor startersmust be wired in accordance with applicable electrical codes.1.Loosen cover screws (AA of Figure 11). Removecover.ABFigure 11AANOTE: Line cord must be 0.28¨ (7 mm) minimum to0.47¨ (12 mm) maximum in diameter.2.Insert line cord through grip (AB) and tighten nut.3.For correct three-phase motor shaft rotation, con-nect line phase sequence L1, L2 & L3 to terminals as shown (Figure 12).Ground L1L2L3135Figure 12NOTE: left terminal marked4.(see Figure 12).5.Replace starter cover and tighten screws (AA ofFigure 11).VFD ControllersNOTE: Refer to VFD Controller Set-up, Operation &Maintenance Manual.Installation6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMM851-274 Rev. D 8Dorner Mfg. Corp.Required ToolsD Wrenches (for hexagon head fasteners)7 mm & 10 mm D 2.5 mm hex key wrench D Torque wrenchTiming Belt Replacement1.Loosen four (4) screws (Z of Figure 13) and removecover (P).Figure 13ZP Z2.Loosen tensioner (X of Figures 14).Figure 14XO3.Remove timing belt (O).NOTE: If timing belt does not slide over pulleyflange, loosen driven pulley set screws (W of Figure 15) and remove pulley with belt. For re-installation,see steps 5 and 6 on pages 5 and 6.Figure 15W4.Install new timing belt.5.Depending on conveyor belt travel (direction 1 or 2),locate timing belt tensioner (X of Figure 16) as shown. Tension timing belt to obtain 0.125¨ (3 mm)deflection for 1.0 lb (456 grams) of force at timing belt mid-point (Y). Tighten tensioner screw to 92in-lb (10.4 Nm).12YFigure 16NOTE: Do not over-tighten screws (Z of Figure 13).6.Replace cover (P of Figure 13) and tighten four (4)screws (Z) to 35 in-lb (4 Nm).Preventive Maintenance & Adjustment6100 Series Bottom Mount Drive Package for Standard Load Parallel Shaft Sanitary Gearmotors SOMMDorner Mfg. Corp.9851-274 Rev. DNOTE: For replacement parts other than those shown on this page, contact an authorized Dorner Service Center or the factory.Figure 171234567Service PartsReturn PolicyFor replacement parts, contact an authorizedDorner Service Center or the factory.851-274 Rev. D Printed in U.S.A.200。

LS变频器说明书iS5-中文说明书

在某些确定的条件下可以识别导致人身伤害的危险。 由于危险电压可能已出现,所以应有意识地特别注意。

在某些确定的条件下可以识别潜在的危险。 仔细阅读相关信息并遵守相关指令。

为了方便取阅使用说明书,请就近保存。

仔细阅读本说明书,使 SV-iS5 系列变频器的性能达到最佳化,并确保安全地使用。

危险

当电源已经送电或变频器处于运行状态时,不要打开变频器的外壳。 否则,可能发生电击。

位,否则可能发生意外事故。

不要修改或变动变频器内部任何东西。 变频器的电子热保护功能可能无法保护电机。 在变频器的输入侧不要使用电磁式交流接触器作为变频器频繁启停的开关。 使用噪声滤波器来降低变频器产生的电磁干扰的影响,否则,附近的电子设备可能会受到干扰。 如果输入电压不平衡,需要安装交流电抗器。来自变频器的潜在高次谐波可能会引起电力电容器和发生

第一章 安装 .....................................................................................................................................10 1.1 检查 ..................................................................................................................................................... 10 1.2 环境条件 ............................................................................................................................................. 10 1.3 安装 ..................................................................................................................................................... 10 1.4 其它注意事项 ..................................................................................................................................... 11 1.5 尺寸 ..................................................................................................................................................... 12 1.6 基本配线 ............................................................................................................................................. 17 1.7 电源端子 ............................................................................................................................................. 18 1.7.1 类型 A 构造 ............................................................................................................................... 19 1.7.2 类型B 构造 ................................................................................................................................. 19 1.7.3 类型C 构造 ................................................................................................................................. 20 1.7.4 电源端子配线 ............................................................................................................................. 21 1.8 控制端子 ............................................................................................................................................. 23 1.8.1 控制端子配线 ............................................................................................................................. 24 1.8.2 键盘和 RS485电路连接配线 ..................................................................................................... 25

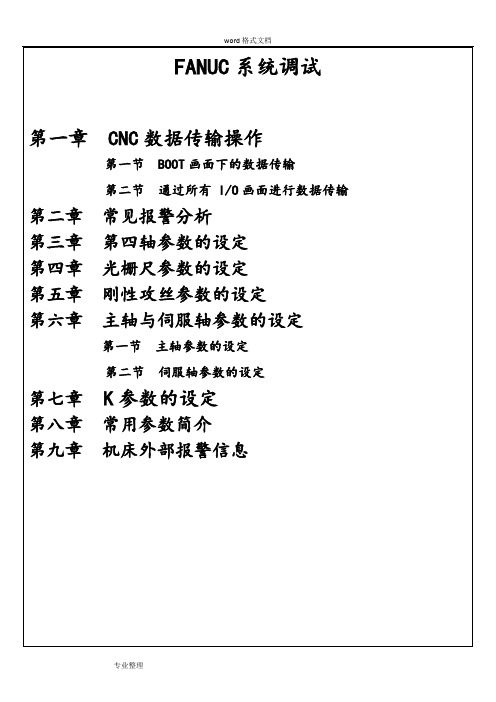

FANUC系统机床调试

2:

1

SELECT---YES---YES---SELECT---

面

2

(3.SYSTEM DATA LONDING)

SELECT---YES---YES---SELECT---

第二节通过ALL I/O 画面进行数据传输

1:由于上电后的状态英文, 很多人不认识,所以我们先把语言改为汉

----左

2:PLC及PLC参数的传入

a.首先选择键,出现上页左图4-----扩展2次------出现左图1---选择“PMCMNT”-----左图2,选择“I/O”-----选择“操作”-----选择“列

c. 如果使用USB经行操作的话,需要把左图 2 中装置中的光标移至”USB MEMORY”,即可对PLC和PLC参数进行操作。

3:PLC及PLC参数的备份

首先选择键

3-----选择

注

1.在传入的过程中,显示面板右下角会有

“输入”字样闪烁,在传入过程中不要有

其它页面操作,以免导致丢失数据

2.程序锁钥匙一定要打开

如果程序号8000-8999的程序无法操作,检查参数3202#0(0:不禁止编辑1:禁止编辑)

如果程序号9000--9999的程序无法操

作,检查参数3202#4 (0:不禁止编辑

1:禁止编辑)

键

有IO

303

word格式文档。

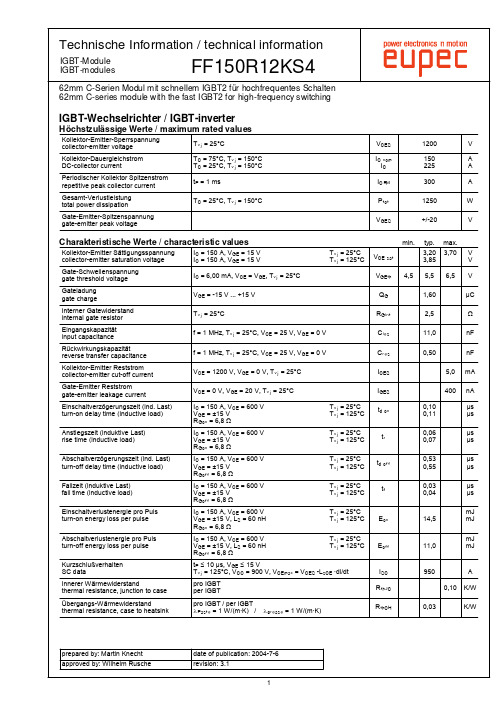

FF150R12KS4资料

NutzungsbedingungenDie in diesem Produktdatenblatt enthaltenen Daten sind ausschließlich für technisch geschultes Fachpersonal bestimmt. Die Beurteilung der Geeignetheit dieses Produktes für die von Ihnen anvisierte Anwendung sowie die Beurteilung der Vollständigkeit der bereitgestellten Produktdaten für diese Anwendung obliegt Ihnen bzw. Ihren technischen Abteilungen.In diesem Produktdatenblatt werden diejenigen Merkmale beschrieben, für die wir eine liefervertragliche Gewährleistungübernehmen. Eine solche Gewährleistung richtet sich ausschließlich nach Maßgabe der im jeweiligen Liefervertrag enthaltenen Bestimmungen. Garantien jeglicher Art werden für das Produkt und dessen Eigenschaften keinesfalls übernommen.Sollten Sie von uns Produktinformationen benötigen, die über den Inhalt dieses Produktdatenblatts hinausgehen und insbesondere eine spezifische Verwendung und den Einsatz dieses Produktes betreffen, setzen Sie sich bitte mit dem für Siezuständigen Vertriebsbüro in Verbindung (siehe , Vertrieb&Kontakt). Für Interessenten halten wir ApplicationNotes bereit.Aufgrund der technischen Anforderungen könnte unser Produkt gesundheitsgefährdende Substanzen enthalten. Bei Rückfragenzu den in diesem Produkt jeweils enthaltenen Substanzen setzen Sie sich bitte ebenfalls mit dem für Sie zuständigen Vertriebsbüro in Verbindung.Sollten Sie beabsichtigen, das Produkt in gesundheits- oder lebensgefährdenden oder lebenserhaltenden Anwendungsbereichen einzusetzen, bitten wir um Mitteilung. Wir weisen darauf hin, dass wir für diese Fälle- die gemeinsame Durchführung eines Risiko- und Qualitätsassessments;- den Abschluss von speziellen Qualitätssicherungsvereinbarungen;- die gemeinsame Einführung von Maßnahmen zu einer laufenden Produktbeobachtung dringend empfehlen und gegebenenfalls die Belieferung von der Umsetzung solcher Maßnahmen abhängig machen.Soweit erforderlich, bitten wir Sie, entsprechende Hinweise an Ihre Kunden zu geben.Inhaltliche Änderungen dieses Produktdatenblatts bleiben vorbehalten.Terms & Conditions of usageThe data contained in this product data sheet is exclusively intended for technically trained staff. You and your technical departments will have to evaluate the suitability of the product for the intended application and the completeness of the productdata with respect to such application.This product data sheet is describing the characteristics of this product for which a warranty is granted. Any such warranty is granted exclusively pursuant the terms and conditions of the supply agreement. There will be no guarantee of any kind for the product and its characteristics.Should you require product information in excess of the data given in this product data sheet or which concerns the specific application of our product, please contact the sales office, which is responsible for you (see , sales&contact). For those that are specifically interested we may provide application notes.Due to technical requirements our product may contain dangerous substances. For information on the types in question please contact the sales office, which is responsible for you.Should you intend to use the Product in health or live endangering or life support applications, please notify. Please note, that for any such applications we urgently recommend- to perform joint Risk and Quality Assessments;- the conclusion of Quality Agreements;- to establish joint measures of an ongoing product survey,and that we may make delivery depended on the realizationof any such measures.If and to the extent necessary, please forward equivalent notices to your customers.Changes of this product data sheet are reserved.。

ATMEL AVR1504 数据手册

AVR1504: Xplain training - XMEGA EventsystemPrerequisites• Required knowledgeBasic knowledge of microcontrollers and the C programming language Completed AVR1500: Xplain training – XMEGA™ BasicsRecommended to have finished AVR1501: Xplain training – XMEGA Timer/Counter• Software prerequisitesAtmel ® AVR ® Studio ® 4.18 SP2 or later WinAVR/GCC 20100110 or later • Hardware prerequisites Xplain evaluation board JTAGICE mkII• Estimated completion time 2 hours1 IntroductionThe Event System is a set of features for inter-peripheral communication. It enables the possibility for a change of state in one peripheral to automatically trigger actions in other peripherals. What change of state in a peripheral, that will trigger actions in other peripherals is configurable in software. It is a simple, but powerful system as it allows for autonomous control of peripherals without any use of interrupts or CPU and DMA resources.The indication of a change of state in a peripheral is referred to as an event. The events are passed between the peripherals using a dedicated routing network called the Event Routing Network. This consists of eight multiplexers, where all events are routed into all multiplexers.8-bitMicrocontrollersApplication NoteRev. 8313A-AVR-06/102AVR15048313A-AVR-06/102 Introduction to the Event SystemThis introduction is intended to give you a basic overview of the terminology and behavior which is needed to understand the Event System and the tasks in this training. The tasks in this training will show you how the Event System works in more detail.The figure below illustrates the Event System. The figure shows the different parts that makes it operate; the event sources, the channel MUX’s and the event action selection in the event user/peripheral.The figure shows a simplified version with one timer/counter as event generator and one ADC as an event user. The event channel MUX’s can select one of threeavailable sources to be routed though the corresponding event channel.Events can be generated by the following peripherals:• Timer/Counters (TCxn) • Real Time counter (RTC)• Analog to Digital converters (ADCx) • Analog Comparators (ACx) • Ports (PORTx)• System clock (clksys)Each of these peripherals has several sources for events. Examples of sources are timer/counter overflow, pin change on a port or A/D conversion completed. The full list of available event sources is shown in the register description for the Event System in the Atmel XMEGA A manual.The channel multiplexers (MUX) selects what source is routed into each of the 8 event system channels available. Each event system channel allows one source that generates events to that channel. The EVSYS.CHxMUX registers controls the event source for each channel.AVR150438313A-AVR-06/10Events can be used by the following peripherals: • Timer/Counters• Analog to Digital Converters • Digital to Analog Converters• Direct Memory Access Controller (DMAC)Usage of events is controlled on the individual peripherals. Configuration registers on the individual peripheral allows you to select what event channel to use as input and what the event action is for that channel. Several peripherals can be using the same event channel as input. This is convenient for allowing several actions start at the same time.For example: starting input capture of a Timer/Counter at the same time as starting a conversion in an ADC. The available event actions are shown in the register description for each peripheral.4AVR15048313A-AVR-06/103 OverviewHere is a short overview of the tasks in this training:Task 1: 32-bit Timer/CounterThis task shows the basic Event System setup with event user and event generator and how this can be used for making a 32-bit timer.Task 2: Input capture with filteringInput capture with a Timer/Counter is controlled with events in Atmel XMEGA, and this task shows you how flexible this is.Task 3: Synchronized triggeringMore than one peripheral can use events from one event channel, and this can be used to synchronize event actions in the peripherals.Task 4: Manually generating eventsEvents can be generated from software, and this task gives you a basic example on how to do this.GOOD LUCK!AVR150458313A-AVR-06/104 Task 1: 32-bit Timer/CounterBy using the overflow event from one Timer/Counter as the clock input/source to another Timer/Counter, it is possible to use the Event System for making a 32-bit Timer/Counter. In this setup it is also possible to do input capture in order to have 32-bit input capture. In the Timer/Counter hands-on session we use the Peripheral Clock as input to the timer/counter TCC0, and the event system will be used as input totimer/counter TCC1. The following figure shows this conceptually:The AVR1001 – using the Atmel XMEGA event system application note contains a code example on how to implement a 32-bit Timer/Counter with input capture.The goal for this task is that you:• Understand the basics of using the Event System, and how to configure an event channel• Know how to use an event channel in a peripheral module • Understand how to use an event channel to clock a timerTASK:1. Locate the Atmel XMEGA-EventSystem folder and open the 32bitTimerCounter.aps project file in AVR Studio2. Spend some time to understand the code, how it works, and ensure you know the basics of how the Event System is set up3. Build the project, ensure there are no errors (you can ignore the warning) and start a debug session4. Run the code, and you will see that the LEDs are counting upwards with the clock tick rate of the most significant TC which is clocked from the event system5. Break and place a breakpoint as indicated below:6AVR15048313A-AVR-06/106. Run the code again and see that it breaks when the least significant timer is close to overflow. If you single step a few times, the timer will overflow, and you will see that the LED is counting. If you expand the IO view for TCC1, you can see how CNT increase when TCC0 overflows7. If you wish to write some code in this task, you can add code to make a 48- or 64-bit timer ☺AVR150478313A-AVR-06/105 Task 2: Input Capture with FilteringIn Task 1 we used the Event System to trigger events that were the clock source to a Timer/Counter (TC). In general, a peripheral may perform different actions when receiving an event. For instance, for the TC, see the timer event action list in the CTRLD register shown in the register description of the Timer counter in the Atmel XMEGA A Manual. Take a look at this table to understand what event actions the timer can use.By having the Event System able to trigger input capture is much more flexible than having one or a few capture pins. Because a pin change on any I/O pin can be used to generate an event, this means that any I/O pin can be used as an input capture pin.In fact, any event can trigger an input capture, not just pin changes. In this task we will stick to the basics and we will use a pin change event to do input capture. To make this work we need to configure the following:• Timer TCC0 to perform input capture on capture channel A (CCA) when getting an event on channel 0• Event System routing to route PORTE pin 0 events into event channel 0• Input sensing on PORTE pin 0 to specify if rising edge, falling edge, both edges or the level of the pin generates eventsThe goal for this task is that you:• Understand how to set up input capture using a timer and the Event System • Know how filtering on the I/O pins is handled by the Event System TASK:1. Locate the InputCapture.aps Atmel AVR Studio project file. Open the task2.c file and familiarize yourself with the code2. The code is almost done, but you need to configure the event channel 0 MUX to use pin 0 of PORTF as input to this event channel. If you need help, see how this is done in Task 13. Build the project, ensure there are no errors (you may ignore the warning) and open the debug file in AVR Studio4. Run the code; press the switch a few times5. Each press will generate an event (or in fact two events) that trigger the input capture. The capture values are continuously read and output to the LEDsWhy does each press generate two events?8AVR15048313A-AVR-06/106. Let’s look at the Error flag. The Error flag is set when there is a buffer overflow for the input captures registers in the TC. You can study Section 14.5 (double buffering) in the Atmel XMEGA A manual to see how this works7. Add error_count to the Watch window so you can follow the number of overflow errors8. Run the code, press the switch many times with short intervals, break and see if any errors occurred. You should be able to generate some9. We are using noise from the buttons to generate quickly enough to get a buffer overflow. If it is difficult to press the switch to generate overflow, you can add a delay (for example _delay_ms(200); ) in the while(1) loop so the CCA register is not read that often 10. W hile the debug session is still stopped, locate the Event System in the IO view and expand it to see the current configuration11. T he first instance of the Digital Filter, represents the filter for event channel 0AVR150498313A-AVR-06/1012. C hange the digital filter to set how many pin change events must be sampled by the peripheral clock before the event is passed through 13. R un the code again, press the switch and see how the different filter value is able to reduce the error_count10AVR15048313A-AVR-06/106 Task 3: Synchronized TriggeringIt is possible to let different peripherals use the same event channel as input, and by doing this several peripherals can use the same event. This can for example be used to synchronize actions. Here are a few examples where this is useful:• For doing an input capture and start an ADC conversion at the same time, in order to give the conversion a time stamp• For starting conversions on two ADCs at the same time • Other combinations of ADC, DAC, Timer/counter and DMAIn this task we are going to keep it simple and use the Event System to initiate input capture on 3 timers (TCC0, TCD0 and TCE0) simultaneously. Timer/counter TCF0 overflow is used as the event trigger source (generator).The goal for this task is that you:• Are able to configure the Event System • Understand synchronized Triggering TASK:1. Locate the folder for Task 3 and open the SynchronizedTriggering.aps project. Look at the task3.c file and familiarize yourself with the code2. The code is almost complete, but we need to do some changes:a. Add code that sets up the timer/counter TCD0 and TCE0 in the sameway as TCC0b. Set up overflow of timer/counter TCF0 as input to event channel 0c. Build the project, ensure there are no errors, and start debugging inAtmel AVR Studio3. Let’s run the code and make sure that the event is triggered as expected, and that the input capture happens4. Break the execution, and place a breakpoint as indicated below:AVR1504118313A-AVR-06/105. Add a watch on the capture_values variable by right clicking on the variable and selecting “Add watch : “capture_values”. This array contains capture values from all three timers6. Run the code and observe that the capture_values variable gets updatedYou can notice that all the capture values are almost the same. Why are they not exactly the same?If you have time, add code to set all the count (CNT) values of the timer/counter tozero before the while loop. Are the capture values the same now? Why?12AVR15048313A-AVR-06/107 Task 4: Manually Generating EventsEvents can be generated manually from software. This is done by STROBE registers or by accessing the registers directly during on-chip debugging. Writing the STROBE register triggers the operation.It is possible to generate events on several channels at the same time by writing to several bit locations at once. This can be useful for synchronizing event actions, for on-chip debug or using events to keep track of program execution status.Manually generated events last for one clock cycle and will overwrite events from other event sources during that clock cycle.The goal for this task is that you:• Know how to generate events from software• Understand when generating events from software can be useful • Know how to synchronize several timer/counters TASK:1. Locate the ManuallyGeneratingEvent.aps project and open it in Atmel AVR Studio2. Open the task4.c file and familiarize yourself with the code. The code is similar to task3, but notice that timer/counter TCC0, TCD0 and TCE0 are now running with a clock prescaler/divider of 1 (same speed as the CPU). In addition the timer/counters are now configured to RESTART when an event is received3. Build the project, ensure there are no errors, and start debugging the project4. Place a breakpoint in the main loop5. Add a watch to capture_values so you can keep track of the compare values6. Notice that the capture_values are now different values even if the input capture happens on the exact clock cycle. This is like in Task 3 because the timers are started at different clock cyclesAVR1504138313A-AVR-06/107. The code is almost done, but you need to add code to generate events from software on event channel 08. Place a breakpoint in the code so you can single step after the software events are generated9. Run the code and ensure that it stops at the breakpoint 10. O pen the Event System in the IO view and single step to see that the STROBE register is being written, and cleared again in the next cycle11. U se “Run to cursor” to see that the compare_values are updated with new values after the event triggered the input capture. Notice that all the timers are now perfectly synchronized 12. T he STROBE register can be written during on-chip debug, for example by using the IO view to set the bits. The bits that are written will be cleared in the next cycle. You can test this, but keep in mind that the capture values for the timer are not kept if the buffer is full. Instead you will get an error8 SummaryIn this hands-on we have learned how the Event System operates, how to configure it and we have shown you potential uses for the Event System.14AVR15048313A-AVR-06/109 Resources• Atmel XMEGA Manual and Datasheetso /xmega• Atmel AVR Studio with help fileso /products/AVR/• WINAVR GCC compilero /• Atmel IAR Embedded Workbench ® compilero /10 Atmel Technical Support CenterAtmel has several support channels available:o Web portal: http://support.atmel.no/ All Atmel microcontrollers o Email: ************* All Atmel AVR products o Email: *************** All 32-bit AVR productsPlease register on the web portal to gain access to the following services:o Access to a rich FAQ databaseo Easy submission of technical support requests o History of all your past support requestso Register to receive Atmel microcontrollers’ newsletterso Get information about available trainings and training material8313A-AVR-06/10He a dqu a rters Intern a tion a lAtmel Corporation2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong Road Kwun Tong, Kowloon Hong KongTel: (852) 2245-6100 Fax: (852) 2722-1369Product ContactAtmel Europe Le Krebs8, Rue Jean-Pierre Timbaud BP 30978054 Saint-Quentin-en-Yvelines Cedex FranceTel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg. 1-24-8 ShinkawaChuo-ku, Tokyo 104-0033 JapanTel: (81) 3-3523-3551 Fax: (81) 3-3523-7581Web SiteTechnical Support *************Sales Contact/contactsLiterature Request/literatureDisclaimer: The information in this document is provided in connection with Atmel products. N o license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2010 Atmel Corporation. All rights reserved . Atmel ®, Atmel logo and combinations thereof, AVR ®, AVR ® logo, AVR Studio ® and others, are the registered trademarks, XMEGA™ and others are trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。

ATF1504AS_05资料