基于FPGA和SDRAM的雷电地闪探测单元存储系统设计

基于FPGA的DDR2 SDRAM存储器用户接口设计

基于FPGA 的DDR2SDRAM 存储器用户接口设计杨斌,段哲民,高峰(西北工业大学电子信息学院,陕西西安710129)摘要:使用功能强大的FPGA 来实现一种DDR2SDRAM 存储器的用户接口。

该用户接口是基于XILINX 公司出产的DDR2SDRAM 的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,可知本设计具有很大的使用前景。

本设计通过采用多路高速率数据读写操作仿真验证,可知其完全可以满足时序要求,由综合结果可知其使用逻辑资源很少,运行速率很高,基本可以满足所有设计需要。

关键词:DDR2SDRAM ;FPGA ;用户接口;DDR2SDRAM 存储控制器中图分类号:TN919.8文献标识码:A文章编号:1674-6236(2012)23-0147-03Design of DDR2SDRAM memory user interface based on FPGAYANG Bin ,DUAN Zhe -min ,GAO Feng(School of Electronic Information ,Northwestern Polytechnical University ,Xi ’an 710129,China )Abstract:The user interface of a DDR2SDRAM memory is implemented by using the powerful FPGA .The user interface is based on DDR2SDRAM memory controller produced by the XILINX company .The company produced such memory controllers with high efficiency and used widely .So that this design has great prospects .Through the simulation of multi -channel high -speed data read and write operations we can know that it can fully meet the timing requirements .Through the synthesis results we can know that the use of logic resources is very little ,run rate is high .It can basically meet all design needs.Key words:DDR2SDRAM ;FPGA ;user interface ;DDR2SDRAM memory controller收稿日期:2012-08-06稿件编号:201208014作者简介:杨斌(1981—),男,陕西佳县人,硕士研究生。

基于FPGA的Verilog语言描述的SDRAM接口电路设计

基于FPGA的SDRAM存储器接口实现摘要随着信息科学的飞速发展,人们面临的信号处理任务越来越繁重,对数据采集处理系统的要求也越来越高。

单片机、DSP等微处理器内部RAM 有限,这就需要在微处理器的外部扩展存储器。

同步动态随机访问存储器具有价格低廉、密度高、数据读写速度快的优点,从而成为数据缓存的首选存储介质,在数据采集系统和图像处理系统等方面中有着重要和广泛的应用。

SDRAM 的读写逻辑复杂,最高时钟频率达100MHz 以上,普通单片机无法实现复杂的SDRAM 控制操作。

复杂可编程逻辑器件CPLD具有编程方便,集成度高,速度快,价格低等优点。

因此选用CPLD 设计SDRAM 接口控制模块, 简化主机对SDRAM 的读写控制。

通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

论文开始介绍了SDRAM接口设计研究的背景和研究的目的及意义,引出对SDRAM的研究,详细介绍了SDRAM的基本原理、内部结构、基本操作和工作时序,以及设计的重点及难点。

在这些理论基础上对SDRAM 接口进行模块化设计,了解设计中所使用的硬件和软件。

最后用Verilog语言在软件QuartusⅡ设计CPLD芯片,通过在硬件和软件上的调试基本实现了SDRAM接口的设计。

关键词SDRAM;接口;Verilog;CPLDThe Implementation of SDRAM MemoryInterface Based on the EPM570AbstractWith the rapid development of information science, people face more and more onerous task of signal processing, the requirements of data acquisition and processing system are getting higher and higher. Microprocessor such as single-chip microprocessor, DSP etc, their RAM is limited, which requires external expansion in the microprocessor memory. Synchronous Dynamic Random Access Memory has a low cost, high density, fast read and write data on the merits, thereby becoming the first choice for data cache storage medium, which paly an important role and widely used in the data acquisition system and image processing systems.SDRAM read and write logic is complex, the maximum clock frequency reaches above 100MHz, the ordinary microcontroller can not achieve complex SDRAM control operation. Complex programmable logic device has advantages such as programming convenience, high integrity, high speed and low cost etc. Therefore select CPLD to design control module of SDRAM interface , to simplify the host to read and write control of the SDRAM. Through the design of SDRAM controller interface based on CPLD, you can connect SDRAM in the external of STM series, ARM series, STC series single chip microprocessor and the DSP, increase system storage space.At the beginning of paper introduces the research background, research purpose and significance of the study of SDRAM interface design, leads to the study of SDRAM, detailed introduces information of SDRAM about the basic principles, the internal structure, the basic operation and timing of work, and the design emphasis and difficulty. Based on these theories, modularing the designof SDRAM interface, understanding hardware and software used in the design. Finally, it uses Verilog language in Quartus Ⅱsoftware to design CPLD chip, Through the hardware and the software realization SDRAM the commissioning of the basic design of the interface.Keywords SDRAM; Interface; Verilog; CPLD目录摘要 (I)Abstract (II)第1章绪论 (1)1.1 课题背景 (1)1.2 课题研究的目的及意义 (1)1.3 同步动态随机存储器简介 (2)1.4 论文的结构和框架 (3)第2章SDRAM的工作原理 (4)2.1 存储器的概述 (4)2.1.1 存储器的分类 (4)2.1.2 存储器的技术指标 (5)2.1.3 存储器的比较 (5)2.2 SDRAM的工作原理 (6)2.2.1 SDRAM存储的基本原理 (6)2.2.2 SDRAM的内部结构 (7)2.3 本章小结 (8)第3章SDRAM的基本操作 (9)3.1 SDRAM的基本操作 (9)3.1.1 芯片初始化 (9)3.1.2 行有效 (9)3.1.3 列读写 (10)3.1.4 读操作 (11)3.1.5 写操作 (12)3.2 SDRAM的工作特性 (13)3.2.1 模式寄存器的设置 (13)3.2.2 预充电 (14)3.2.3 刷新 (15)3.3 SDRAM接口设计的要求 (16)3.3.1 存储器接口解决数据存取的难点 (17)3.3.2 存储器接口在工作方式上的初步优化 (17)3.4 本章小结 (18)第4章系统结构及硬件设计 (19)4.1 SDRAM接口设计的整体结构 (19)4.1.1 控制接口模块 (19)4.1.2 CAS延迟模块 (20)4.1.3 突发长度模块 (22)4.1.4 地址转换模块 (22)4.2 EPM570芯片简介 (23)4.2.1 MAXⅡ系列芯片功能简介 (24)4.2.2 逻辑阵列 (25)4.2.3 全局时钟 (25)4.2.4 I/O端口结构 (26)4.3 MT48LC系列芯片简介 (26)4.4 本章小结 (28)第5章软件设计与实现 (30)5.1 利用QuartusⅡ进行设计的流程 (30)5.2 软件的设计 (31)5.2.1 Verilog语言的特点 (31)5.2.2 采用Verilog设计综合的过程 (32)5.2.3 SDRAM接口设计的仿真 (34)5.3 本章小结 (36)结论 (37)致谢 (38)参考文献 (39)附录A (41)附录B (46)附录C (51)第1章绪论1.1课题背景数据采集处理技术是现代信号处理的基础,广泛应用于雷达、声纳、软件无线电、瞬态信号测试等领域。

基于FPGA的SDRAM控制器设计

基于FPGA的SDRAM控制器设计摘要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器设计方法,采用Verilog语言完成的控制器的设计,可以很方便地对SDRAM进行操作。

控制器在大容量数据记录仪扩展缓存得到了很好的应用。

关键字:FPGA;SDRAM;V erilog;1 引言在进行高速数据记录仪的开发中,由于硬盘固有的寻道延时,不能实现外部数据实时写入。

采用固态硬盘成本又比较高,所以在设计中考虑外加大容量数据缓存。

在各种随机存储器件中,SRAM的价格低,设计简单,但容量一般都不大;DDR速度快、容量大,但硬件和软件设计都比较复杂。

SDRAM具价格低、体积小、速度快、容量大的优点,是满足高速数据记录设计带宽的理想器件。

但是,与SRAM相比较,SDRAM的控制逻辑复杂,接口方式与普通的存储器差异很大。

为了解决这个矛盾,需要设计专用的SDRAM控制器,本文中提出了SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。

该设计采用了Altera公司的CycloneII系列EP2C35F484C8N作为主控芯片。

系统工作时钟为75M。

2 SDRAM工作原理简介本设计采用SDRAM芯片选用Winbond公司的W982516,4M×4BANKS×16BIT,两片并成32位数据总线,突发读写速度可达到300Mbytes/s。

W982516采用了54引脚的TSOP封装,工作电压为3.3V,并且采用同步接口方式(所有的信号都是时钟信号的上升沿触发),与系统时钟同步运行。

W982516行地址数目是13,列地址数目是9。

与各种SDRAM 一样,这种SDRAM具有以下几个特点:(1)采取行列地址复用原则,SDRAM的地址线在不同的命令下提供不同的地址,行列地址复用13根地址线。

(2)需要定时刷新。

(3)在进行读写时,需先激活行。

换页读写时要预充关闭的行,然后再激活新的行进行读写。

基于fpga的sdram课程设计

基于FPGA的SDRAM控制器课程设计一、引言随着嵌入式系统应用的不断扩展,高速大容量存储器的需求日益增长。

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)作为一种高速动态存储器,广泛应用于各种高性能系统中。

为了实现高效的数据存储和读取,基于FPGA(Field Programmable Gate Array,现场可编程门阵列)的SDRAM控制器设计成为了研究的热点。

本课程设计将介绍基于FPGA的SDRAM控制器设计的相关知识,并探讨其实现方法。

二、SDRAM控制器设计原理SDRAM控制器的主要功能是实现SDRAM芯片与FPGA之间的通信。

它需要将FPGA发出的时序和控制信号转换为符合SDRAM规格的信号,以实现对SDRAM芯片的读写操作。

在设计SDRAM控制器时,需要考虑以下几个关键因素:1.SDRAM规格:不同的SDRAM芯片具有不同的规格,包括数据宽度、工作电压、刷新周期等。

在设计控制器时,需要了解目标SDRAM芯片的规格,以确保正确的通信。

2.时序控制:SDRAM通信涉及到复杂的时序控制,包括数据读写时序、刷新时序等。

控制器需要根据SDRAM规格生成正确的时序信号,以保证数据正确读写。

3.地址管理:SDRAM控制器需要管理SDRAM芯片的地址,包括行地址和列地址。

控制器需要生成正确的地址信号,并根据地址信号实现数据读写。

4.数据传输:控制器需要实现数据的正确传输,包括数据的读写操作和数据的格式化。

根据目标应用需求,可以选择合适的传输模式,如突发传输、页模式传输等。

三、基于FPGA的SDRAM控制器设计实现基于FPGA的SDRAM控制器设计可以通过硬件描述语言(如VHDL或Verilog)实现。

以下是一个简单的基于FPGA的SDRAM控制器设计的实现步骤:1.确定SDRAM规格:首先需要确定目标SDRAM芯片的规格,包括数据宽度、工作电压、刷新周期等。

基于FPGA的DDR2 SDRAM数据存储研究

21 D R . D 2系统 架构 功能定 义

1 D R D A 概 述 D 2S R M

D R ( obeD t R t 2 S R M 器 件 是 由 D 2 D u l a ae ) D A a JD C 电子设备 工程 联 合 委员 会 ) 行 开发 的新 EE( 进

摘

要: D 2S R M具有存取速度快, D R D A 容量大等特点, 它在 内存、 显存及数据暂存方面有着广

泛 的应 用。本 文基 于 X l xV n x x0 P A对 D R D A 数 据存 取 做 了较 为 详 细的探 in ie5 F 7 T F G i D 2S R M

沿 同时进行数 据传输 的基本 方式 , D R 但 D 2内存 却

拥有两倍于上一代 D R内存预读取能力( i数 D 4b t 据读预取) 。即 D R D 2内存每个时钟能够以4 倍外

收 稿 日期 : 09一l 4 20 2—1

同而不同 ,ie Vrx t 5内部是 F O形式的接 口。 I F () 2 控制逻辑层

第2 7卷 第 2期

21 年 00 4月

贵州大学学报( 自然科 学版)

Ju a uzo n esy( a rl c ne) or l f i uU i r t N t a Si cs n oG h v i u e

Vo.2 o 1 7 N .2 A r 00 p .2 1

准, 与用于 写入 的数据 中心 对准 。 对 D R D A 器 件 的读 取 和写 入 访 问 为 D 2S R M

4 l) F G 0n ,P A芯片的集成度成倍提高 , n 时钟频率

已经达 到数吉 赫兹 。 数 据 采集 系统 采样 频 率 的不 断 提高 对数 据 存 储也提 出 了越 来越高 的要求 , 高速 采样 和大容量 持 续存储 已经成 为存储 领域 的一个发展 方 向 , 并且 已

基于FPGA的多通道实时地震勘探采集系统设计

(Ministry of Education Key Laboratory of Cognitive Radio,Guilin University of Electronic Technology,Guilin 541004,China)

Abstract:Since the defects(few channels and poor real ⁃ time performance) of the current seismic exploration acquisition system result in low⁃efficiency geological exploration and increase of the exploration cost,a multi⁃channel real⁃time seismic ex⁃ ploration acquisition system based on FPGA is designed,which can realize 48⁃channel real⁃time acquisition of seismic wave sig⁃ nals in seismic exploration. In the system,the FPGA is taken as its main control core,and six 8⁃channel 24⁃bit Δ⁃Σ type ADC chips with high dynamic range is used for multi⁃channel acquisition of seismic wave signals. During the acquisition process,the IP core is used to control the 2 Gb high⁃speed DDRⅡ SDRAM memory for the acquired data real⁃time storage. The long⁃distance data transmission is realized through RS 485 serial port communication after data acquisition. The experimental test results show that the seismic exploration system has the 48 ⁃channel real⁃time acquisition capability,and the characteristics of large storage capacity,high real⁃time performance and perfect stability.

基于FPGA的SDRAM控制器设计

基于FPGA的SDRAM控制器设计西南交通大学电气工程学院宋一鸣雷娟李春茂(610031)摘要:本文介绍了SDRAM的结构和控制时序特点,介绍了基于FPGA的SDRAM控制器设计的关键技术,并引入仲裁机制,从而可以快速高效地控制SDRAM。

关键词:SDRAM,FPGA,Verilog,状态机,仲裁机制。

引言SDRAM是新一代的高速、高容量动态存储器,与SRAM相比,不仅容量大得多,并且价格也很便宜。

特别是目前的PCI总线已取代ISA总线成为控制系统总线的主流,随之而来的是对数据访问需求量的增大,SRAM的速度和容量已远远不能满足这些系统的需要。

目前市场上有一些通用的SDRAM控制器,但设置复杂,并且由于是通用的,无法针对特定的系统,因此性能不能发挥到最好,这在很大程度上抵消了使用SDRAM的优势。

因此,我们提出使用可编程逻辑器件平台并通过使用硬件描述语言,针对特定的系统定制自己需要的SDRAM控制器,不仅可以节省系统资源,而且可以最大限度地发挥SDRAM的作用,从而提升系统的性能。

本在一项图像处理系统中采用Verilog语言在FPGA上实现了SDRAM控制器的设计,成功地使SDRAM通过PCI接口与PC机内存之间完成可靠的数据交换。

本文分为三部份,第一部份以Micron公司的128Mb的SDRAM芯片为例介绍SDRAM控制的时序,第二部份介绍基于FPGA的SDRAM控制器设计的关键技术,第三部份介绍以上设计的实现和仿真结果。

SDRAM的控制时序SDRAM需要正确的上电逻辑和模式设置来进入期望的工作模式。

访问特定的逻辑单元必须先激活相应的存储块,并锁定对应的行列地址。

另外,必须有定时的刷新逻辑保持数据不丢失,SDRAM有多种操作模式,由引脚CS#、RAS#、CAS#、WE#和地址信号的不同状态来决定,SDRAM控制器必须为SDRAM提供满足时序要求的这些控制信号,以准确地控制SDRAM的各种不同操作。

基于FPGA的SDRAM控制器的设计和实现

p sd fr i pe e t g te S A oe o m lm ni h DR M cnrl r b sd o P A. T e h rce s c fte crep n ig n ot l ae n F G oe h c aatr t s o h orso dn i i

摘 要 为扩展 T -0 S11处理 器的外部 S R M 存储 空 间,提 出一种 基 于 F G DA P A的 S R M 控制 器的 实现 方 DA

法。分析 了 所用 S R M的特点、原理,介绍 了S R M控制器的组成框图厦各模块功能。给 出了读写 S R M DA DA DA

的 时序 图以厦 S R M存储板 的性 能参 数。FG 中采 用了模 块 化设 计方式 ,该设 计将 T 11处理 器的 外部 DA PA S一 0

通用性 , 本文中提出了一种通用 的 S R M控制器 DA

的 FG P A设计 ,F G P A内部采用状态机的方式 。该 设计采用了 A D公司的 D P处理芯片 T 一 0 作为 S S 11

主控系统。

一11 0 虽然能直接访 问 S R M,但 DA

容量有限。这里将其外部 S R M存储容量扩展到 DA 52 bt, 1M y 使用 的是 T e S一1 1的主机 (M H) 0 /S 空

型号容量为 52 bt 的 S R M,M 4 L 18 4 2 1M y e DA T8c2M A 采用 了 5 4引脚 的 T O S P封装 ,工作 电压 为 33 , . V

收稿 日期 : 06 l41 2 0 -l3

作者简介 :杨海涛 (90 ,男,硕 士研 究生。研 究 方向 : 18 一)

数字信号处理。 苏 涛 (9 8一) 16 ,男,教授 ,硕士生 导师。

基于FPGA的SDRAM控制器设计

1引言

在高速实时或者非实时信号处理系统当中,随着采样速率的不断提高 ,使用大容量 存储器实现数据缓存 是一个必不可少 的环节 ,也是系统实现 中的重点和难点之一 。 S A ( DR M 同步 动态 随机访 问存储 器 )具 有价格低 廉、密 度高 、数据读 写速度 快 的优 点 ,

从而 成为数 据缓存 的首选 存储 介质 。但 S AM 的控制 逻辑 比较复杂 ,对 时序 要求也 十 DR 分 严格 ,使 用 很不 方便 ,这 就要 求 有一 个专 门的控 制器 ,使 系 统 用 户能 很方 便地 操作

2 4

维普资讯

科 技 论 文

预充 电(R C A G ) P E H R E :用来使特定存储体中打开的行或所有存储体中打开的行无 效 。在预 充 电命 令 发 出后一个规 定 时间 内存储 体对 随后 的行存 取是有 效 的 ,输 入端A1 0 用于 决定是一 个还 是全部 的存储 体被预 充 电。一 旦一个存 储体 已经被 预充 电 ,它就处于 待机状态 并在任 一 读或 写命令 被发送 到该存储 体之 前必须 启动 。 自动刷新 (UT F S :刷 新是 为了维持 S AM中 的数据 ,定 时的刷新 周期 A OR R H) E E DR

基于FPGA的高可靠性SDRAM控制器设计与实现

cekn n ri l o t l oue r l m ua d n ac( M . iay te P Ahrw r ipe e - hcigadc t a cnr d l tpe o l r u dny T R) Fn l, G ad a l n ic om i d re l h F em m

lz d i p c lcrma n tce vr n n .T i o t l ri d ulrz d fo tp t otm ,icu ig t o ly ie n s a e ee t o g ei n i me t h sc nr l smo a ie r m o ob to o o e n l d n w a —

Ab ta tA d s n meh d o ihrl bl DR sr c : ei to fhg ei it S AM o t l r ae n F G sp p sd frd t ah t g a i y c nr l s dO P A i r oe o aac c eui oe b o —

t o n e t g o h o t le r o ltd,a d t et s e ut h w a h sd sg shg l eib ea d min a d tsi ft ec n r lra e c mp ee n o n e tr s l s o t tt i e in i ihy rla l h s h n l xb e,whc a e p vd d a ud c o e iain o r cia aa c c es se i p c lcr ma — fe il ih c n b r ie sg ia e frr a z to fap a tc d t a h y tm n s a e ee to g o n l l

基于FPGA SDRAM的AXIS_SDRAM接口设计与实现

信息科学科技创新导报 Science and Technology Innovation Herald134DOI:10.16660/ki.1674-098X.2020.11.134基于FPGA SDRAM的AXIS_SDRAM接口设计与实现李浩 申伟(中国航天科工重庆金美通信 重庆 400000)摘 要:由于FPGA片内存储资源有限,扩展外部存储空间是必要的,然而众多存储芯片总线结构复杂,控制繁琐。

为此,本文以赛灵思的FPGA为平台,设计一种以常用而快捷的axi_stream的形式访问SDRAM的接口。

关键词:FPGA SDRAM AXIS FIFO BRAM 中图分类号:TP334 文献标识码:A 文章编号:1674-098X(2020)04(b)-0134-02随着芯片的不断更新换代,集成ARM核的FPGA芯片得到了广泛的应用[1]。

axi的总线协议在FPGA里面应用也越来越广。

axi_stream协议为axi的一种总线标准。

本文将采用axi_stream的时序以fifo与bram的形式访问SDRAM的设计与实现方法。

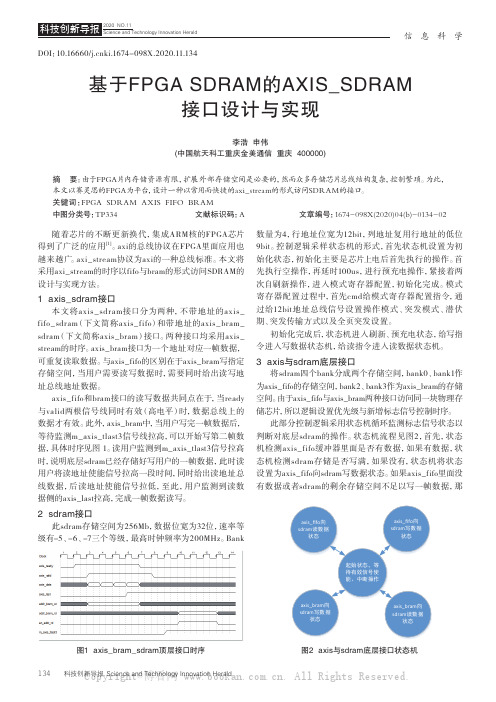

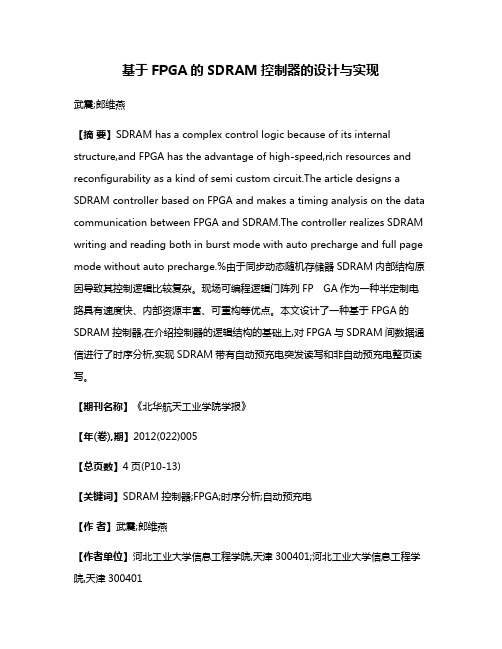

1 axis_sdram接口本文将axis_sdram接口分为两种,不带地址的axis_fifo_sdram (下文简称axis_fifo )和带地址的axis_bram_sdram (下文简称axis_bram)接口。

两种接口均采用axis_stream的时序。

axis_bram接口为一个地址对应一帧数据,可重复读取数据。

与axis_fifo的区别在于axis_bram写指定存储空间,当用户需要读写数据时,需要同时给出读写地址总线地址数据。

axis_fifo和bram接口的读写数据共同点在于,当ready 与valid两根信号线同时有效(高电平)时,数据总线上的数据才有效。

此外,axis_bram中,当用户写完一帧数据后,等待监测m_axis_tlast3信号线拉高,可以开始写第二帧数据,具体时序见图 1。

基于FPGA的SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现1.设计SDRAM控制器的功能:SDRAM控制器的主要功能是控制SDRAM的读写操作,包括地址、数据和控制信号的生成以及时序管理。

其次,还需要实现初始化、写入数据、读取数据等相关功能。

2.确定SDRAM的总线类型:SDRAM控制器需要根据不同的SDRAM接口类型进行设计,例如,DDR、SDR、LPDDR等。

不同的接口类型有不同的时序和数据传输方式,因此根据使用的SDRAM类型确定总线宽度、传输速率和时序约束等。

3.确定FPGA型号和资源:根据SDRAM控制器的设计规模和FPGA的资源情况选择合适的FPGA型号。

资源包括逻辑门、存储器单元、DSP片等,选择合适的型号可以满足设计要求并提高系统性能。

4.设计时序控制电路:根据SDRAM的时序要求,设计时序控制电路来实现SDRAM读写操作的同步和序列控制。

时序控制电路通常包括时钟分频模块、时钟同步模块、读写状态机和地址计数器等功能模块。

5.实现控制信号与FPGA引脚的映射:将SDRAM控制器内部产生的控制信号映射到FPGA引脚上,以便与SDRAM进行数据的传输和时钟同步。

通过FPGA引脚的选择和约束来满足SDRAM接口要求。

6.进行功能仿真和时序分析:在FPGA设计工具中进行功能仿真和时序分析,验证SDRAM控制器的设计是否满足功能要求,并检查时序约束是否满足。

7.进行硬件布局和布线:根据FPGA设计工具生成的后端文件,进行硬件布局和布线,将逻辑电路映射到FPGA芯片上,并考虑时序约束和引脚约束等因素,以满足设计要求。

8.进行SDRAM控制器的验证和调试:通过连接SDRAM和FPGA开发板,验证SDRAM控制器的读写操作是否正常,检查数据的正确性和时序的准确性。

9.进行性能优化和资源利用:根据实际需求,考虑对SDRAM控制器进行性能优化,例如增加缓存、提高数据通路宽度等。

同时,优化资源利用,减小逻辑门延迟和功耗等。

基于FPGA的SDRAM控制器的设计与实现

基于FPGA的SDRAM控制器的设计与实现武震;郎维燕【摘要】SDRAM has a complex control logic because of its internal structure,and FPGA has the advantage of high-speed,rich resources and reconfigurability as a kind of semi custom circuit.The article designs a SDRAM controller based on FPGA and makes a timing analysis on the data communication between FPGA and SDRAM.The controller realizes SDRAM writing and reading both in burst mode with auto precharge and full page mode without auto precharge.%由于同步动态随机存储器SDRAM内部结构原因导致其控制逻辑比较复杂。

现场可编程逻辑门阵列FP GA作为一种半定制电路具有速度快、内部资源丰富、可重构等优点。

本文设计了一种基于FPGA的SDRAM控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM带有自动预充电突发读写和非自动预充电整页读写。

【期刊名称】《北华航天工业学院学报》【年(卷),期】2012(022)005【总页数】4页(P10-13)【关键词】SDRAM控制器;FPGA;时序分析;自动预充电【作者】武震;郎维燕【作者单位】河北工业大学信息工程学院,天津300401;河北工业大学信息工程学院,天津300401【正文语种】中文【中图分类】TP2730 引言SDRAM(Synchronous Dynamic Random Access Memory)具有价格低廉、容量大、速度快等优点,但是SDRAM的控制逻辑相对复杂,对时序要求也比较严格,这就需要有一个专门的控制器。

地震数据采集中基于FPGA的多DDR SDRAM控制器设计

地震数据采集中基于FPGA的多DDR SDRAM控制器设计马灵;杨俊峰;宋克柱;王砚方

【期刊名称】《中国科学技术大学学报》

【年(卷),期】2010(040)009

【摘要】实现高速大容量数据的无死时间乒乓存储是地震数据采集系统的一项关键技术,本设计采用在一片FPGA中,通过共享同一个PLL和DLL来实现2个DDR SDRAM控制器,应用于海上高精度地震拖缆采集与记录系统中光纤控制接口板上,完成对水下地震采集数据的接收、乒乓缓存、数据拼接及时序转道序功能.最终系统仿真和测试结果表明,该控制器能够在133 MHz频率上稳定运行,达到了预期的设计目标.

【总页数】7页(P939-945)

【作者】马灵;杨俊峰;宋克柱;王砚方

【作者单位】中国科学技术大学近代物理系,安徽合肥,230026;中国科学技术大学近代物理系,安徽合肥,230026;中国科学技术大学近代物理系,安徽合肥,230026;中国科学技术大学近代物理系,安徽合肥,230026

【正文语种】中文

【中图分类】TN919.6

【相关文献】

1.基于FPGA的DDR3SDRAM控制器的设计与优化 [J], 宋明;赵英潇;林钱强

2.基于FPGA的DDR3 SDRAM控制器设计与实现方法 [J], 丁培培;郑列;李宏

3.基于FPGA的DDR3 SDRAM控制器设计及实现 [J], 韩进;张览;刘锴

4.基于FPGA的DDR2_SDRAM控制器用户接口设计 [J], 韩笑;闫永立;李勇彬;马嘉莉;吴斌

5.基于FPGA的DDR2 SDRAM控制器设计 [J], 钱素琴;刘晶华

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的三维闪电探测仪电路系统设计

基于FPGA的三维闪电探测仪电路系统设计

李力;彭军;蓝天飞;甘少明

【期刊名称】《吉林大学学报:理学版》

【年(卷),期】2022(60)4

【摘要】针对传统二维闪电探测仪鉴别闪电信号波形速度较慢且不准确,数据质量受元器件老化影响,且元器件数量较多、集成度较低、可靠性较差、升级空间较小,只能用线性电源工作,对供电稳定性要求严格等问题,通过超大规模现场可编程门阵列、片上可编程系统与现代电子表面贴装技术研发抗干扰的三维闪电探测仪.探测仪天线采用正交环结构并加装屏蔽罩以提高接收信号精度,避免天线效应;前置信道板应用大规模集成电路、表面贴装元器件与多层板工艺减少输出信号背景噪声;信号处理板基于嵌入式软核灵活构建中央处理器以快速鉴别闪电波形;供电模组使用适应能力强、转换效率高的开关电源获取多种电压.该设计实现了稳定低功耗的三维闪电探测仪.

【总页数】8页(P977-984)

【作者】李力;彭军;蓝天飞;甘少明

【作者单位】湖北省气象信息与技术保障中心;十堰市气象局

【正文语种】中文

【中图分类】TN98

【相关文献】

1.基于LabVIEW和FPGA的数字电路板比对测试系统设计

2.基于FPGA的集成电路测试系统设计探讨

3.基于FPGA的生命探测仪算法研究与系统设计

4.基于FPGA的电路板智能测试系统设计

5.三维闪电探测仪状态检测监控系统设计与实现

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA瞬变微光能量探测系统的数据采集和存储设计

基于FPGA瞬变微光能量探测系统的数据采集和存储设计梁义涛;汶德胜;王宏;冉晓强

【期刊名称】《电子技术应用》

【年(卷),期】2006(32)10

【摘要】在分析目标信号特性的基础上,提出瞬变微光信号探测系统数据采集和存储单元实现方案.针对系统对数据采集和存储的特殊要求,采用FPGA技术,完成了高性能数据采集系统设计.以Altera公司的FPGA为硬件设计载体,使用VHDL语言对数据采集和存储的控制逻辑和时序进行了硬件描述.在QuartusⅡ集成环境中进行软件设计和仿真,结果与设计吻合.

【总页数】3页(P46-48)

【作者】梁义涛;汶德胜;王宏;冉晓强

【作者单位】中国科学院西安光学精密机械研究所,陕西,西安,710068;中国科学院研究生院,北京,100039;中国科学院西安光学精密机械研究所,陕西,西安,710068;中国科学院西安光学精密机械研究所,陕西,西安,710068;中国科学院西安光学精密机械研究所,陕西,西安,710068;中国科学院研究生院,北京,100039

【正文语种】中文

【中图分类】TP3

【相关文献】

1.瞬变光多事件探测系统FPGA程控预处理电路设计 [J], 梁义涛;汶德胜;王宏;王锋;冉晓强;车嵘

2.基于FPGA的高速数据采集存储系统设计 [J], 任勇峰;张凯华;程海亮

3.基于FPGA的数据采集存储系统的设计与实现 [J], 李金猛

4.基于FPGA的36通道同步数据采集存储控制器设计与实现 [J], 李艳平;徐海贤

5.基于FPGA高速数据采集与存储系统的设计 [J], 贾亮;王真真;马兴;赵璐

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[ 关键 词 ] F P GA;S D RAM ;地 闪探 测 ;存 储 系统

[ 中图分类号]T P 3 3 4 . 7 [ 文 献 标 志 码] A [ 文章编号]1 6 7 3—1 4 0 9( 2 0 1 3 )1 9— 0 0 7 1 —0 4

基于 F P GA 和 S DR AM 的 雷 电 地 闪 探 测 单 元 存 储 系 统 设 计

陈 晓 静 ( 长江大学电子信息学院, 湖北 荆州 4 3 4 0 2 3 )

李 开 成 ,李 沁 ( 华中科技大学电气与电子工程学院, 湖北 武汉 4 3 0 0 7 4 )

[ 摘 要 ] 针 对 雷 电地 闪信 号 存 储 的特 点 ,提 出 了基 于 F P GA 和 S D R AM 的 地 闪探 测 单 元 存 储 系 统 的 总 体 设

1 系统 设 计

1 . 1 S DR A M 存 储 容 量 计 算 及 选 型

根 据雷 电信 号存 储 的要求 ,需要 存 储至 少 1 0次雷 电闪击 的数据 ,每 次 闪击 包 括雷 电特 征量 和 三通 道 的波形 数 据 。雷 电特征量 包 括波达 时 间 、方 位 角 、磁场 / 电场 峰值 等 ,每 次 闪 击特 征 量 占用 空 间不 到 1 0 0字 ,所 以 1 K 字 的存储 空 间足 以存放 1 O次 闪击 的雷 电特征量 。三通道 包 括两路 从正 交环 天线输 入 的 磁 场信号 ,一路从 平板 电场 天线 输入 的 大气 电场 信号 。波 形 数据 所 占容量 大 小 与通 道 数 、通 道采 样 率 、 采样 位宽 、采 样 时间有 关 ,地 闪信号 频率 覆盖 范 围在 3 0 0 k Hz以下 ,并考 虑 留有裕 量 ,探 测 单元 的采 样 频率 定为 2 MHz ,采 样时 间应 保证 能完 整 保存 全 部 闪击 的 波形 ,1 s的采 样 时 间 足 以满 足要 求 。按 照 采 样频率 2 MHz ,采样 位宽 1 4 b i t s( 约 2字节 ) ,3 通 道 ,1 s 采 样 时 间 ,1 0次 闪击 计算 ,需 要 存 储容 量 大

长江大学学报 ( 自科 版 ) 2 0 1 3 年7 月号理 工上旬刊 第 1 0 卷第1 9 期

J o u r n a l o f Y a n g t z e Un i v e r s i t y( N a t S c i E d i t ) J u 1 . 2 0 1 3 ,Vo 1 . 1 0 No . 1 9

雷 电灾 害是指 雷雨 云 中 电能 释放 、击 中物 体或 所形 成 的强烈 电磁 辐射 而造 成损 失 的灾害现 象 。随着 高科 技 的发展 ,雷 电灾 害越来 越 严重 ,雷 电监 测与 气象 灾害 预警 技术 的研究 显 得尤 为迫切 。雷 电地 闪探 测单 元是 全能 型雷 电探 测设 备 的一个 子课 题 ,全能 型雷 电探 测设 备 的研制 和应 用将会 满 足有关 部 门雷 电 监 测 和气象 灾 害预警 应 用 的需 求 。雷 电地 闪探测 单元 口 的主要 任务 是拾 取天 线接 收 的地 闪磁 场信 号和 大 气 电场信 号 ,并提 取雷 电信 号 的特征 量包 括波 达 时 间 、磁 场 / 电场 峰值 、方 位 角 等信 息 ,同时 保存 地 闪 波形 数据 供探 测站 主机 读取 。雷 电地 闪信 号 采集 属 于 多 通道 高 速 数据 采 集 ,因此 采用 F P G A 完 成 雷 电 地 闪 探测单 元 的设计 。探 测单 元 中 的存 储 系统必 不 可少 ,因为探测 站 主机需 要采 集处 理 的数据 不仅包 括 地 闪 信号 ,而 且还包 括 云 闪 、光 探测单 元 等其他 信 号 ,这些 信号具 有并 发特 性 ,因此 要求 各探 测单元 必 须 具备 存储 的环 节 ,以防止 主机不 能 及 时 处 理数 据 而 造 成 的 数据 丢 失 。考虑 到 雷 电地 闪信 号 采 集 速 率 高 、存 储容 量 大 、存 取 速度快 以及 成本 因 素 ,地 闪探 测单 元存 储 系统采 用 S D R AM 来 设计 。

计 ,介 绍 了 S D RA M 控制器设计 中的关键 问题及解 决方 案,给 出了 S D RAM 接 口硬 件 电 路 , 详 细 介 绍 了 S D R AM 控 制 器 的核 心 部 分 —— 时序 控 制 器 的状 态 转 换设 计 , 最 后 给 出 S I GNAL TA P I I 的 运行 结 果 。实 际

[ 收稿日期]2 0 1 3 一O l 一1 2 [ 基金项目]国家自然科学基金项目 ( 5 1 0 7 7 0 5 8 ) 。

[ 作者简介]陈晓静 ( 1 9 8 0 一 ) ,女 ,讲师 ,博士生 ,现 主要从 事电磁测 量与仪器方面的研究工作。

小为 2 ×3 ×2 M ×1 0字节 = = = 1 2 0 M 字节 。

该 设计 选 用 S DR AM 型号 为 MT4 8 L C 3 2 M1 6 A2 o,该 芯 片 的主要 特 点 为 :3 . 3 V 电源供 电 ,工 作 频 率 1 3 3 MHz ,所有 信号 传输 在 系统时 钟 的上升 沿进 行 ,内部 采用 流水线 技 术 ,列 地址 可 以在任 何 时钟 周 期 内改变 ,可被 配置 为猝 发长 度 为 l 、2 、4 、8或整 页猝 发 读 写模 式 ,具 有 自刷 新 节 电功能 ,可 实 现 自 动 预充 电 ,行刷 新周 期 6 4 ms ,1 3 3 MHz 工作 频 率下 C AS延 时为 5 . 4 n s ,芯片位宽 为 1 6 b i t s ,存 储体共有