SOPC课程设计实验报告--基于 NIOS 的 μCOS-II 实验

sopc实验心得

sopc实验心得

在进行SOPC(系统级可编程器件)实验的过程中,我深刻体会到了它的强大和灵活性。

SOPC是一种基于现场可编程门阵列(FPGA)技术的系统设计方法,它将硬件与软件相结合,可以实现高度集成和可重构的设计。

在实验中,我首先学习了SOPC的基本概念和原理,了解了它的组成部分以及各个组件之间的连接方式。

然后,我利用Quartus II软件进行了仿真和综合,将设计的硬件描述语言(HDL)代码转化为FPGA可以理解的形式。

通过仿真,我可以预先验证设计的正确性,并对其进行修改和优化。

接着,我进行了FPGA的编程和配置,将设计好的逻辑电路加载到FPGA芯片中。

通过这一步骤,我可以将自己的设计直接在硬件上实现,并进行实时的测试和调试。

这种即时性和灵活性是SOPC的一个重要优点,它使得我们能够更加高效地进行系统级设计和验证。

在SOPC实验中,我还学习了使用Nios II软核处理器进行嵌入式系统设计。

Nios II是一款可编程的32位RISC处理器,可以根据需求进行定制和配置。

通过Nios II,我可以在FPGA上实现复杂的嵌入式系统,并编写C语言程序进行控制和操作。

总的来说,SOPC实验让我深入了解了系统级可编程器件的原理和应用。

通过实践,我学会了使用Quartus II软件进行FPGA设计和配置,掌握了硬件描述语言

和嵌入式系统的开发方法。

这些知识和技能对我未来的学习和工作都具有重要的意义,我相信在不久的将来,SOPC技术将会在各个领域得到广泛应用。

《SOPC技术》课程实验报告模板

《SOPC技术》课程实验报告姓名:学号:班级:同组者:指导教师:高金定信息科学与工程学院2013-2014学年第一学期《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验1:基于LPM的正弦信号发生器的设计二、任务及要求【任务】在QuartusII平台上,采用查找表的设计方法,利用LPM兆功能模块,完成64点(8位)的正弦信号发生器的设计。

正弦信号发生器结构框图如下:【要求】1.数据存储ROM和地址信号发生器均由LPM模块实现。

2.在Quartus II软件上进行时序仿真。

3.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)【思考】1.编写DAC0832数模转换程序,利用示波器观察输出信号波形。

2.如何在此基础上设计方波、三角波等信号发生器?如何实现波形幅度等参数可调?三、实验程序(原理图)四、仿真及结果分析五、硬件验证1、选择模式:2、引脚锁定情况表:六、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验2:基于DSP Builder正弦信号发生器的设计二、任务及要求【任务】采用DSP Builder系统建模的方法,设计正弦信号发生器,要求采用查找表的方法,完成正弦信号发生器模块的建模、仿真。

Signal Compiler【要求】:1.完成模型构建及仿真,得到如下波形图。

2.将模型转换成VHDL硬件描述语言,利用Modelsim软件进行RTL仿真。

3.再在Quartus II软件上进行编译、时序仿真与时序分析。

4.利用Signal Tap II嵌入式逻辑分析仪进行在线测试与分析。

(此步需使用实验箱,并且要确保实验箱与电脑处于在线可下载状态)三、仿真模型及参数四、仿真及结果分析五、小结《SOPC技术》课程实验报告学生姓名:所在班级:指导教师:高金定老师记分及评价:一、实验名称实验3:基于DSP Builder的FIR数字低通滤波器的设计二、任务及要求【任务】:调用DSP Builder模块,设计FIR低通数字滤波器,完成建模与仿真。

嵌入式μCOS-II内核实验四(哲学家就餐问题的实现)

目录

• 引言 • 哲学家就餐问题概述 • μcos-ii内核任务管理 • 哲学家就餐问题的μcos-ii实现 • 实验结果与分析 • 总结与展望

01

引言

嵌入式系统与μcos-ii内核简介

嵌入式系统

是一种专用的计算机系统,主要用于控制、监视或帮助操作 机器设备。它通常具有实时性、可靠性和低功耗等特点,广 泛应用于工业控制、智能家居、医疗设备等领域。

任务优先级与调度

任务优先级

在μcos-ii内核中,每个任务都有自己 的优先级。优先级高的任务会优先获 得CPU的使用权。

任务调度

μcos-ii内核使用基于优先级的抢占式任务 调度算法。当一个高优先级的任务就绪时, 内核会立即抢占当前正在运行的任务,并切 换到高优先级的任务上运行。

任务同步与通信

任务同步

解决方案的分类与比较

解决方案分类

解决哲学家就餐问题的方案可以分为两类:静态方案和动态方案。静态方案在 系统启动时分配固定的资源,而动态方案则在运行时动态地分配资源。

解决方案比较

静态方案实现简单,但可能导致死锁或饥饿问题。动态方案可以更好地解决这 些问题,但实现起来较为复杂,需要更多的系统资源和时间。在实际应用中, 需要根据具体需求和系统限制选择合适的解决方案。

05

实验结果与分析

实验环境与配置

01

硬件平台

ARM Cortex-M4微控制器 (具体型号为

STM32F407ZGT6)

02

开发环境

Keil uVision5

03

04

实验任务

实现基于μcos-ii内核的多任务 切换

配置参数

任务优先级、任务堆栈大小、 任务状态等

SOPC设计基础实验报告

黑龙江科技大学SOPC设计基础实验报告学院:黑龙江科技大学学号: ********** 姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容1 添加SOPC硬核1,.创建一个工程,取名。

2.添加.bdf文件,取名和工程名同名。

3.在Tools菜单下打开SOPC Builder。

4.创建系统,取名NIOS2,选择使用Verilog语言。

5.设置系统主频和指定FPGA。

6.加入NIOS2 CPU模块,选择型号,并设置相关参数。

7.依次添加定时器、Butoon PIO、LCD控制器、外部RAM和Flash接口、外部RAM和Flash总线、JTAG UART接口,并将这些模块命名成自己熟悉的名字。

8.分配IP模块的地址和中断号9.配置NIOS2 系统10.生成NIOS2并加入到工程中2 创建PLL器件由于Sdram的时钟是由fpga提供的,所以要创建一个PLL器件来实现对时钟的控制,Quartus II提供了Megawizard Plug-In Manager工具对Plug-In器件以及IP Core进行创建和管理,在Megawizard Plug-In Manager中可以创建各种逻辑门电路以及存储器件。

选择Tools/Megawizard Plug-In Manager点击“Next”,进入Manager,选择“IO/ALTPLL”,选择输出文件类型为“VHDL”,选择输出文件的名字“mypll”点击“Next”,选择器件的速度为8,输出的频率为50MHz,其它设置不变。

点击“Next”,去掉复位、使能等选项点击“Next”,进入Clock c0的设定。

改变“Enter output clock frequency”为50MHz点击“Next”,进入Clock c1的设定,不作改变点击“Next”进入Clock e0的设定。

SOPC实验报告

SOPC系统设计技术实验报告姓名:学号:院系: 信息科学与工程学院专业:电子科学与技术指导老师:完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉Quartus II、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。

二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II 9.0,SOPC Builder 9.0, NIOS II IDE 9.0。

(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。

三、实验步骤3.1硬件设计根据实验内容,可以得出本次实验的硬件结构图如图3.1所示:图3.1 硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II系统。

4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU的配置向导对话框,如图1.4所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。

然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图1.6所示。

基于NiosII的SOPC多处理器系统设计方法

altera_avalon_mutex _lock( ) altera_avalon_mutex _unlock ( ) altera_avalon_mutex _is_mine( ) altera_avalon_mutex _firs t_lock( )

4 NiosII 多处理器系统设计实例

下面将利用 SO PC Builder 建立一 个基于 标准模板 的 3 处理器、共 享 片 上 存储 器 的 N iosII系 统, 之 后在 N iosII

paper@ m esnet . com . cn( 投稿专用)

19 2007 年第 3 期 M icrocontrollers & Em bedded Syst ems

3. 2 启动地址

在多处理器系统中, 每个处理器必须从自己的存 储区 域启动。为了从同一个非易 失性存 储器中 的不 同区域 启 动多处理器, 简单地设置每个处理器的复位地址为所 期望 的启动地址。在启动地址之 间要留 出足够 的空 间存放 启

动代码。 NiosII Flash Programmer 能 够将 多个 处理 器 的启 动

在多处理器系统中, 多个处理器可能使用同一个程 序 存储器, 每个 处理器 的程序 必须 存放在 不同 的位 置。Ni osII 和 SOPC Builder 提供一个简单的存储器分区模式, 允 许多个处理器在同一存储器的不同区域运行各自的 软件。 分区模式使 用处 理 器的 异 常地 址, 可以 在 S OPC Builder 中进行设置。NiosII IDE 负责 根据 异常 地址 计算 出不 同 代码段链接的位置。如 果 2 个 不同 的处理 器被 链接到 同 一存储器, 那么每个处理器的异常地址用来决定处理器 软 件存放的基地址, 其末地址由下一个异常地址或者存储 器 的末地址决定。对于每个处理器, 软件有 5 个主要的代 码 段需要被链接到存储器中的固定地址, 分别是:

SOPC课程设计实验报告

SOPC课程设计实验报告基于SOPC的警示灯设计2013电子信息工程3班李婕20134557罗丹妮20134563一、设计目的1、熟悉掌握SOPC的基本流程2、设计一个警示灯并满足基本要求3、通过设计发现问题并解决二、设计设备1、硬件:PC机、SOPC-NIOS II EDA/SOPC系统开发平台2、软件:QUARTUS II、SOPC Builder、NIOS II ID E三、设计内容•初始状态为红灯(LED2)熄灭,绿灯(LED1)点亮,数码管显示为0。

•当按键按下,红灯(LED2)闪烁,绿灯(LED1)熄灭,同时蜂鸣器响起,数码管开始倒计时9S,此状态持续时间为9s。

•9s后,恢复初始状态。

四、设计步骤1、使用Quartus II建立一个工程文件和顶层文件;2、使用SOPC Builder建立一个简单Nios II硬件系统1)启动SOPC Builder2)指定目标FPGA3)添加NiosII内核及其他外设A、添加NiosII、SRAM、JTAG-UART、Avalon总线的I P核B、添加一个2位的输入型PIO作为按键keyC、添加两个1位的输出型PIO作为 led1及led2的输出端口D、添加一个1位的输出型PIO作为蜂鸣器的输入端口AE、添加一个3位的输出型PIO作为数码管的位选selF、添加一个8位的输出型PIO作为数码管的段选dat4)指定基地址和中断优先级5)设置NiosII复位和异常地址6) 编译生成NiosII系统SOPC Builder行程图如下:3、在Quartus II中建立一个蜂鸣器1)用VHDL语言编写蜂鸣器程序2)编译成功后Creat symbol,生成Project sing4、在Quartus II中编译Nios II硬件系统并生成配置文件1)在Quartus II加入Nios II系统符号到顶层文件2)给各端口加入输入输出引脚,并重命名3)设置参数4)编译顶层文件5)分配管脚6)再次编译5、在Nios II IDE中建立C/C++工程,编写用户程序6、编译用户程序7、下载.SOF至FPGA,运行程序,观察结果五、设计程序蜂鸣器程序(VHDL):LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY sing1 ISPORT(CLK:IN STD_LOGIC;p:IN STD_LOGIC;-- DIGIT:BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);SPEAKER:OUT STD_LOGIC);END ENTITY;ARCHITECTURE SONG OF sing1 ISSIGNAL DRIVER,ORIGIN:STD_LOGIC_VECTOR(12 DOWNTO 0); SIGNAL COUNTER:INTEGER RANGE 0 TO 140;SIGNAL COUNTER1:INTEGER RANGE 0 TO 3;SIGNAL COUNTER2:INTEGER RANGE 1 TO 10000000; SIGNAL DIGIT :STD_LOGIC_VECTOR(6 DOWNTO 0); SIGNAL COUNT :STD_LOGIC_VECTOR(1 DOWNTO 0); SIGNAL CARRIER,CLK_4MHZ,CLK_4HZ:STD_LOGIC;BEGINPROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THENIF COUNTER1=1 THEN CLK_4MHZ<='1';COUNTER1<=2;ELSIF COUNTER1=3 THEN CLK_4MHZ<='0';COUNTER1<=0;ELSE COUNTER1<=COUNTER1+1;END IF;IF COUNTER2=5000000 THEN CLK_4HZ<='1';COUNTER2<=5000001;ELSIF COUNTER2=10000000 THEN CLK_4HZ<='0';COUNTER2<=1;ELSE COUNTER2<=COUNTER2+1;END IF;END IF;END PROCESS;PROCESS(CLK_4MHZ)BEGINIF CLK_4MHZ'EVENT AND CLK_4MHZ='1' THEN IF DRIVER="1111111111111"THENCARRIER<='1';DRIVER<=ORIGIN;ELSEDRIVER<=DRIVER+1;CARRIER<='0';END IF;END IF;END PROCESS;PROCESS(CARRIER)BEGINif(p='1')thenIF CARRIER'EVENT AND CARRIER='1' THEN COUNT<=COUNT+1;IF COUNT="00"THENSPEAKER<='1';ELSESPEAKER<='0';END IF;END IF;end if;END PROCESS;PROCESS(CLK_4HZ)BEGINIF CLK_4HZ'EVENT AND CLK_4HZ='1' THEN IF COUNTER=140 THENCOUNTER<=0;ELSE COUNTER<=COUNTER+1;END IF;END IF;CASE COUNTER ISWHEN 2 =>DIGIT<="0000011"; WHEN 3 =>DIGIT<="0000011"; WHEN 4 =>DIGIT<="0000101"; WHEN 5 =>DIGIT<="0000101"; WHEN 6 =>DIGIT<="0000101"; WHEN 7 =>DIGIT<="0000110"; WHEN 8 =>DIGIT<="0001000"; WHEN 9 =>DIGIT<="0001000"; WHEN 10 =>DIGIT<="0001000"; WHEN 11 =>DIGIT<="0010000"; WHEN 12 =>DIGIT<="0000110"; WHEN 13 =>DIGIT<="0001000"; WHEN 14 =>DIGIT<="0000101"; WHEN 15 =>DIGIT<="0000101"; WHEN 16 =>DIGIT<="0101000"; WHEN 17 =>DIGIT<="0101000"; WHEN 18 =>DIGIT<="0101000"; WHEN 19 =>DIGIT<="1000000"; WHEN 20 =>DIGIT<="0110000"; WHEN 21 =>DIGIT<="0101000"; WHEN 22 =>DIGIT<="0011000"; WHEN 23 =>DIGIT<="0101000"; WHEN 24 =>DIGIT<="0010000"; WHEN 25 =>DIGIT<="0010000"; WHEN 26 =>DIGIT<="0010000"; WHEN 27 =>DIGIT<="0010000"; WHEN 28 =>DIGIT<="0010000"; WHEN 29 =>DIGIT<="0010000"; WHEN 30 =>DIGIT<="0000011"; WHEN 31 =>DIGIT<="0000000"; WHEN 32 =>DIGIT<="0010000"; WHEN 33 =>DIGIT<="0010000"; WHEN 34 =>DIGIT<="0010000"; WHEN 35 =>DIGIT<="0011000"; WHEN 36 =>DIGIT<="0000111"; WHEN 37 =>DIGIT<="0000111"; WHEN 38 =>DIGIT<="0000110"; WHEN 39 =>DIGIT<="0000110"; WHEN 40 =>DIGIT<="0000101"; WHEN 41 =>DIGIT<="0000101"; WHEN 42 =>DIGIT<="0000101"; WHEN 43 =>DIGIT<="0000110";WHEN 46 =>DIGIT<="0010000"; WHEN 47 =>DIGIT<="0010000"; WHEN 48 =>DIGIT<="0000011"; WHEN 49 =>DIGIT<="0000011"; WHEN 50 =>DIGIT<="0001000"; WHEN 51 =>DIGIT<="0001000"; WHEN 52 =>DIGIT<="0000110"; WHEN 53 =>DIGIT<="0000101"; WHEN 54 =>DIGIT<="0000110"; WHEN 55 =>DIGIT<="0001000"; WHEN 56 =>DIGIT<="0000101"; WHEN 57 =>DIGIT<="0000101"; WHEN 58 =>DIGIT<="0000101"; WHEN 59 =>DIGIT<="0000101"; WHEN 60 =>DIGIT<="0000101"; WHEN 61 =>DIGIT<="0000101"; WHEN 62 =>DIGIT<="0000101"; WHEN 63 =>DIGIT<="0000101"; WHEN 64 =>DIGIT<="0011000"; WHEN 65 =>DIGIT<="0011000"; WHEN 66 =>DIGIT<="0011000"; WHEN 67 =>DIGIT<="0101000"; WHEN 68 =>DIGIT<="0000111"; WHEN 69 =>DIGIT<="0000111"; WHEN 70 =>DIGIT<="0010000"; WHEN 71 =>DIGIT<="0010000"; WHEN 72 =>DIGIT<="0000110"; WHEN 73 =>DIGIT<="0001000"; WHEN 74 =>DIGIT<="0000101"; WHEN 75 =>DIGIT<="0000101"; WHEN 76 =>DIGIT<="0000101"; WHEN 77 =>DIGIT<="0000101"; WHEN 78 =>DIGIT<="0000101"; WHEN 79 =>DIGIT<="0000101"; WHEN 80 =>DIGIT<="0000011"; WHEN 81 =>DIGIT<="0000101"; WHEN 82 =>DIGIT<="0000011"; WHEN 83 =>DIGIT<="0000011"; WHEN 84 =>DIGIT<="0000101"; WHEN 85 =>DIGIT<="0000110"; WHEN 86 =>DIGIT<="0000111"; WHEN 87 =>DIGIT<="0010000";WHEN 90 =>DIGIT<="0000110"; WHEN 91 =>DIGIT<="0000110"; WHEN 92 =>DIGIT<="0000110"; WHEN 93 =>DIGIT<="0000110"; WHEN 94 =>DIGIT<="0000101"; WHEN 95 =>DIGIT<="0000110"; WHEN 96 =>DIGIT<="0001000"; WHEN 97 =>DIGIT<="0001000"; WHEN 98 =>DIGIT<="0001000"; WHEN 99 =>DIGIT<="0010000"; WHEN 100=>DIGIT<="0101000"; WHEN 101=>DIGIT<="0101000"; WHEN 102=>DIGIT<="0101000"; WHEN 103=>DIGIT<="0011000"; WHEN 104=>DIGIT<="0010000"; WHEN 105=>DIGIT<="0010000"; WHEN 106=>DIGIT<="0011000"; WHEN 107=>DIGIT<="0010000"; WHEN 108=>DIGIT<="0001000"; WHEN 109=>DIGIT<="0001000"; WHEN 110=>DIGIT<="0000110"; WHEN 111=>DIGIT<="0000101"; WHEN 112=>DIGIT<="0000011"; WHEN 113=>DIGIT<="0000011"; WHEN 114=>DIGIT<="0000011"; WHEN 115=>DIGIT<="0000011"; WHEN 116=>DIGIT<="0001000"; WHEN 117=>DIGIT<="0001000"; WHEN 118=>DIGIT<="0000110"; WHEN 119=>DIGIT<="0001000"; WHEN 120=>DIGIT<="0000110"; WHEN 121=>DIGIT<="0000011"; WHEN 122=>DIGIT<="0000011"; WHEN 123=>DIGIT<="0010000"; WHEN 124=>DIGIT<="0000011"; WHEN 125=>DIGIT<="0000101"; WHEN 126=>DIGIT<="0000110"; WHEN 127=>DIGIT<="0001000"; WHEN 128=>DIGIT<="0000101"; WHEN 129=>DIGIT<="0000101"; WHEN 130=>DIGIT<="0000101"; WHEN 131=>DIGIT<="0000101";WHEN 134=>DIGIT<="0000101"; WHEN 135=>DIGIT<="0000101"; WHEN 136=>DIGIT<="0000000"; WHEN 137=>DIGIT<="0000000"; WHEN 138=>DIGIT<="0000000"; WHEN 139=>DIGIT<="0000000"; WHEN OTHERS=>DIGIT<="0000000";END CASE;CASE DIGIT ISWHEN "0000011"=>ORIGIN<="0100001001100";WHEN "0000101"=>ORIGIN<="0110000010001";WHEN "0000110"=>ORIGIN<="0111000111110";WHEN "0000111"=>ORIGIN<="1000000101101";WHEN "0001000"=>ORIGIN<="1000100010001";WHEN "0010000"=>ORIGIN<="1001010110010";WHEN "0011000"=>ORIGIN<="1010000100101";WHEN "0101000"=>ORIGIN<="1011000001000";WHEN "0110000"=>ORIGIN<="1011100011110";WHEN "1000000"=>ORIGIN<="1100010001000";WHEN OTHERS=>ORIGIN<="1111111111111";END CASE;END PROCESS;END SONG;警示灯总程序:#include <stdio.h>#include <sys/unistd.h>#include <io.h>#include <string.h>#include "system.h"#include "altera_avalon_pio_regs.h"#include "alt_types.h"#include "sys/alt_irq.h"int num;static void Button_ISR_Init(void);static void Button_Irq_Handler(void* context,alt_u32 id);alt_u8 segtab[10]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; //0~9段码static void display(int num);//按键初始化static void Button_ISR_Init(void){IOWR_ALTERA_AVALON_PIO_IRQ_MASK(KEY_BASE,0xff); //允许8个按键中断IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_BASE,0); //清除中断标志寄存器alt_irq_register(KEY_IRQ,NULL,Button_Irq_Handler); //注册中断}static void display(int num){IOWR_ALTERA_AVALON_PIO_DATA(SEL_BASE,0); //数码管位选IOWR_ALTERA_AVALON_PIO_DATA(DAT_BASE,segtab[num]); //显示倒计时usleep(1000);}/*------------------------------------------------------------------***********************按键中断处理函数*****************************-----------------------------------------------------------------*/static void Button_Irq_Handler(void* context,alt_u32 id){int i;for(i=0;i<9;i++){num=9-i;display(num);IOWR_ALTERA_AVALON_PIO_DATA(A_BASE, 1);//蜂鸣器响起IOWR_ALTERA_AVALON_PIO_DATA(LED1_BASE, 0);IOWR_ALTERA_AVALON_PIO_DATA(LED2_BASE, 1);usleep(500000);IOWR_ALTERA_AVALON_PIO_DATA(LED2_BASE, 0);usleep(500000);}IOWR_ALTERA_AVALON_PIO_DATA(A_BASE, 0);//蜂鸣器关闭IOWR_ALTERA_AVALON_PIO_EDGE_CAP(KEY_BASE,0);num=0;display(num);}int main(void){printf("Begin!\n");Button_ISR_Init(); //按键中断初始化while(1){usleep(100000);IOWR_ALTERA_AVALON_PIO_DATA(LED1_BASE, 1);IOWR_ALTERA_AVALON_PIO_DATA(LED2_BASE, 0);num=0;display(num);}return 0;}六、设计结果按键未按下时,处于初始状态:LED1亮,LED2灭,数码管显示为0,蜂鸣器未启动;按键按下之后,LED1灭,LED2闪烁,数码管进入9秒倒计时并且蜂鸣器响;9秒后恢复初始状态。

基于NiosⅡ的SOPC系统设计与研究的开题报告

基于NiosⅡ的SOPC系统设计与研究的开题报告一、选题背景及意义SOPC(System-on-a-Programmable-Chip,可编程芯片系统)是一种新的系统设计方法,其核心是将CPU、DSP、FPGA等各种数字电路系统的设计集成到一个单一的可编程处理器芯片中,这种设计方法在数字电路领域中具有非常广泛的应用前景和研究价值。

而在这种系统设计方法中,Nios Ⅱ是基于可编程逻辑设备的嵌入式处理器,具有易于设计与控制、可裁剪性强、资源占用小等优点,广泛应用于SOPC系统的设计与实现之中。

因此,本次选题旨在通过对于Nios Ⅱ的SOPC系统设计与研究进行深入探索,探究其在实际应用中的优势与不足之处,为其进一步的优化和完善提供参考依据。

二、研究方法及流程1、资料收集:在本研究中,需要深入了解Nios Ⅱ处理器的内部结构与工作原理、SOPC系统的设计与构建过程、各种数字电路模块的实现方法等相关资料,并进行整理和分析。

2、系统设计:在收集和分析相关资料的基础上,进行简化的Nios Ⅱ处理器设计和SOPC系统架构设计,并利用Quartus II工具进行系统实现和验证。

3、系统测试:完成系统的实现之后,进行系统测试,包括硬件实验和软件编程测试两个方面。

4、分析评估:分析实验数据,评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,提出系统的改进和优化方案。

三、预期结果及意义1、在实验设计过程中,通过对Nios Ⅱ的SOPC系统架构设计与实现,可以深刻理解可编程处理器芯片中各种数字电路模块的工作原理与相互联接关系,彻底掌握SOPC系统的设计与构建方法。

2、通过实验测试和数据分析,可以全面评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,研究其应用前景和推广价值,并针对其不足之处提出系统的改进和优化方案,提高系统的性能水平和可靠性。

3、研究成果可为相关技术研究和应用推广提供科学依据和参考借鉴,促进数字电路领域技术的创新和发展。

基于NiosⅡ的SOPC多处理器系统设计方法

2 2 硬 件 互 斥核 。

Nol处理 器 允 许 使用 其 硬 件 互 斥 核 部 件 对 共 享 资 源 i I s

进 行 保 护处 理 。这 个 硬 件 互斥 核 不 是 一 个 NisI 理 器 内 ol处

部 的 部件 , 是一 个 称 为 Mue 而 t x的 S P ul r 件 。 O CB i e 组 d 互 斥核 也可 看 作 一种 共 享 资 源 , 供 一 个 原子 的“ 试 提 测 和置位” 作 , 操 处理 器 测 试 Mue 否 可 行 。如 果 可 行 , t x是 就 在 某 个操 作 中 获 取 它 。 当 处 理 器 结 束 与 Mue 相 关 的 共 tx 享 资 源 使用 时 , 放 该 Mue ; 时 , 一 个 处 理 器 可 能 获 释 tx 此 另

、 , n … nr莹g田 商~ 。 t - - 、 rJ . '

连接 , 在 于 多个 处 理 器 的 软件 设 计 , 它 们 正 常 操 作 , 而 使 相

互 之 间 不 产 生 冲 突 。NisI 处 理器 系统 分 为 2类 : 类 ol 多 一 是 共 享 资 源 的 多处 理 器 系统 ; 一 类 处 理 器 相 互 独 立 , 另 之 间不 进 行 信 息 交 换 。

本 文 将 对 基 于 NisI的 S C 多处 理 器 系 统 的 实 现 ol 0P 原 理 、 计 流 程 和 方 法进 行 详 细 的讨 论 。 设

数据错误 , 少使应用程序出错 , 至使系统崩溃 。 至 甚 共 享存 储 器 的 处 理器 需 要 一个 机 制 来 通 知其 他 处 理 器 何 时 正在 使 用 共享 资源 , 以便 不 受 其 他 处理 器 的干 扰 。

2 1 共 享 存储 器 .

基于NiosⅡ的U盘安全控制器设计与实现

基于NiosⅡ的U盘安全控制器设计与实现杨献超,苏锦海,张立朝摘要:针对U盘等存储设备的安全隐患及用户的安全需求,分析目前常见的解决方法,遵循灵活方便、高安全性的原则,利用SoPC技术,设计实现了一款基于NiosⅡ的U盘安全控制器。

详细论述了安全控制器的系统设计、硬件架构、固件划分和工作流程。

采用高强度的密码算法,对普通U盘中的数据进行扇区级的加解密,保证U盘中数据的安全,具有灵活安全、易于升级的特点。

关键词: U盘;USB主机;NiosⅡ;安全控制器目前,U盘等USB移动存储载体由于其容量大、价格低、携带方便、可靠性高等优点,得到了越来越广泛的应用,在生活、工作中随处可见。

然而,USB移动存储载体的便利性及其自身安全脆弱性的矛盾十分突出。

本文针对U盘的安全隐患,分析目前较为常见的解决方法,利用SoPC技术,设计实现了一款基于Nios Ⅱ处理器的U盘安全控制器。

该控制器位于PC机和U盘之间,通过对U盘进行扇区级的加解密操作,将普通U盘升级为安全U盘,保证U盘中数据的安全性。

控制器遵循USB MassStorage类协议,无需专用驱动,即插即用,具有灵活方便、安全性高等优点[1]。

1 安全控制器的整体设计1.1 安全U盘解决方案分析U盘最为突出的安全问题是其内部所存储的数据都以明文形式存储,任何人得到该存储载体,即可对其中的数据进行任意的操作。

因此,普通U盘一旦丢失,其存储的数据则毫无安全性可言。

针对这一问题,目前已经有多种解决方法,其中较为常见、安全性较高的是采用专用安全U盘的方法。

专用安全U盘的硬件架构如图1所示,主要由微处理器、存储芯片(NandFlash)、USB模块及加解密模块等组成[2]。

当U盘和PC机进行数据传输时,加解密模块在微处理器的控制下对数据流进行加解密操作,使得U盘存储芯片中的数据都以密文形式存在。

当PC机对数据进行读写时,首先需要进行身份认证,若认证不通过,则读写操作不能进行,即使攻击者将安全U盘物理分解,直接读取存储芯片,而由于存储芯片中的数据是以密文形式存在的,攻击者也只能获得数据的密文。

SOPC实验报告

SOPC设计基础实验报告学院:电子与信息工程学院学号:姓名:实验一开发软件使用练习一实验目的实验目的:掌握基于SOPC硬核处理器的设计流程。

二实验设备安装Quartu II的PC、实验箱三实验内容和步骤1)打开Quarts II 11.1,建立工程2)在菜单栏的File中选择New选项3)默认是New Quartus II Project,选OK4)选择Next,工程目录选择自己新建的文件夹,工程名输入E_Play5)源文件添加,点击Next直接跳过6)选择编号为EP4CE6E22C8的器件7)EDA工具选择,直接点击Next跳过8)项目信息显示,点击Finish完成空工程的建立9)配置无用引脚:在主页面菜单栏点击Assignments,接着在下拉框中选择Device选项,出现如下窗口:As input tri-stated with weak pull-up.点击OK完成。

创建软核处理器系统1)点击菜单栏的Tools,在下拉框中选择SOPC Builder选项,将System Name定为E_Play,下方的Target HDL选VHDL,最后点击OK确认。

2)Device Family选择Cylone IV E,Clock Frequency定为50MHz3)配置软核处理器系统点开左侧Processors总选项,双击Nios II Processor,选择Nios II/e另外在JTAG Debug Module选项中选择第一项,点击Finish完成配置4)配置存储器点开左侧Memories and Memory Controllers总选项,点开第二个On-Chip分选项,双击On-Chip-Memory,在Total memory sizes后输入4096点击Finish,在Onchip-memory2_0上右击,Rename为onchip-memory5)点开左侧Interface Protocols总选项,点开Serial分选项,双击JTAG UART,点击Finish完成6)在jtag_uart_0上右击,Rename为jtag_uart产生软核处理器系统1)双击cpu_0,将Reset Vector和Exception Vector的Memory均设置为onchip_memory,点击Finish完成。

SOPC课程设计报告

中国地质大学(武汉)机电学院电子信息工程专业片上系统设计报告指导老师:小组成员:日期:设计题目:基于NIOSII软核的两轮自平衡小车摘要:本设计采用FPGA的SOPC技术利用在FPGA内部构建NIOSII软核并在软核中例化定时器模块、PWM模块、UART模块和外部中断等特定的IP核。

在规定10ms 周期内CPU需要完成采集MPU6050陀螺仪和加速度计的数据,通过卡尔曼滤波计算出小车的姿态;通过外部中断触发方式采集电机自带编码器的输出脉冲信号,计算当前小车左右轮子车速;采用PID闭环控制算法,计算出维持车身姿态的电机驱动信号PWM波的占空比,驱动电机实现小车平衡。

关键词:FPGA;SOPC;NIOSII;IP核;陀螺仪;卡尔曼滤波;PID算法1.系统方案1.1 系统结构1.1.1 系统总体框架SOPC最小系统CPUEPCSSDRAM内置外设电机驱动减速电机电机自带编码器MPU6050蓝牙无线收发JTAG_UART图1 系统整体框图此设计的二轮平衡车系统主要分为以下功能模块:(1)Nios II软核:用来读取各传感器数据,进行算法运算,产生控制信号维持平衡车姿态。

(2)JTAG_UART:用来下载程序和调试软件各部分功能。

(3)MPU6050:六轴姿态传感器,内部集成三轴陀螺仪和三轴加速度计,用以检测小车姿态。

(4)蓝牙无线收发:连接Nios II软核中的串口内置外设,用以将传感器数据发送给上位机,来进行小车算法调试。

(5)电机驱动:用来将Nios II软核输出的PWM信号转换成电机驱动电流,驱动大功率电机正常运转。

(6)电机自带编码器:用来检测小车左右两个电机的转速,反馈给软核用于下一步运动的解算。

本设计利用FPGA的SOPC功能在FPGA芯片内部利用SOPC Builder设计符合系统要求的Nios II软核,在顶层文件中添加该软核和其他一些硬件资源(PLL,逻辑单元等)并完成引脚分配,最终实现实际电路的综合,配合Nios II IDE 开发软件,开发系统软核实现控制二轮小车直立等动作。

实验10_SOPC_UCOSII操作系统OK

实验10_SOPC_UCOSII操作系统OK引言:在嵌入式系统中,操作系统是一种软件模块,它的目标是有效地管理系统的资源,并为应用程序提供一个良好的运行环境。

本实验将介绍SOPC_UCOSII操作系统,通过实践来学习如何在其上运行应用程序。

本实验分为以下几个部分:1.SOPC_UCOSII操作系统的介绍2.实验环境搭建3.实验步骤详解4.实验总结与展望一、SOPC_UCOSII操作系统的介绍SOPC(System on Programmable Chip,可编程芯片系统)是一种集成电路系统设计方法,它是将处理器、外设、总线和存储空间等硬件资源集成在一颗可编程逻辑器件(如FPGA)中的理念。

SOPC_UCOSII操作系统是基于SOPC架构设计的一种实时嵌入式操作系统。

UCOSII(MicroC/OS-II,Micro Controller Operating System-II)是美国Micrium公司开发的一款商业操作系统,经过多年的发展与优化,已经成为嵌入式系统领域最受欢迎的操作系统之一二、实验环境搭建1. 使用Altera的Quartus II软件进行FPGA设计和编译。

2.使用FPGA硬件平台开发板进行实验,如DE1-SoC开发板。

3. 使用Altera提供的示例设计进行实验。

三、实验步骤详解2. 使用Quartus II软件创建一个新的工程,选择目标FPGA芯片型号,并进行必要的设置。

3.导入SOPC_UCOSII的示例设计,该设计包含了处理器、外设、总线和存储空间等硬件资源的配置。

4. 编译工程,生成SOPC_UCOSII的.bit文件。

6. 使用终端仿真软件(如SecureCRT),通过串口连接到FPGA开发板。

7.启动FPGA开发板,并观察SOPC_UCOSII的运行情况。

8.在SOPC_UCOSII上运行应用程序,观察其输出结果和运行状态。

四、实验总结与展望通过本实验,我们学习了SOPC_UCOSII操作系统的搭建和运行方式,并在其上成功运行了应用程序。

基于NIOS II内核的嵌入式SOPC开发板的实现

基于NIOS II内核的嵌入式SOPC开发板的实现随着大规模集成电路技术的进步和制造工艺水平的提高,嵌入式系统的开发变得日益复杂。

传统的嵌入式系统设计方法已经不能适应当前嵌入式系统设计的需要。

单个芯片容量的增大、功能的增加、体积的减小使得设计变得更加便利,同时也为嵌入式系统设计开发开辟了新的天地即片上系统(System on Chip,SoC)技术。

1 嵌入式系统的开发过程根据IEEE的定义,嵌入式系统是控制、监视或者辅助设备、机器和车间运行的装置。

因此,嵌入式系统是软件和硬件的综合体,以应用为中心,以计算机技术为基础,软硬件资源可裁剪,适应应用系统对功能、可靠性、成本、体积、功耗等严格要求的专用计算机系统。

一般而言嵌入式系统的开发主要包括4个部分:处理器、存储器、输入/输出(I/O)和软件,如图1所示。

2 Nios II内核嵌入式开发板的实现嵌入式系统的核心部件是各种类型的嵌入式处理器。

因此,我们着眼于嵌入式处理器的SoC开发。

本节将对基于Nios II内核的嵌入式SOPC开发板设计进行详细的介绍。

2.1 Nios II 内核的设计Nios II系列嵌入式处理器是一款采用流水线技术、单指令流的RISC CPU,广泛应用于嵌入式系统。

Nios II包括3种内核,即快速的F(最高性能的优化)内核、经济的E(最小逻辑占用的优化)内核以及标准的S(平衡于性能和尺寸)内核,每种内核根据不同的性能而优化。

考虑到性能和成本,通常采用Nios II标准内核设计。

Nios II嵌入式CPU支持32位指令集,32位数据线宽度,32个通用寄存器,32个外部中断源,2 GB寻址空间,包含高达256个用户自定义的CPU定制指令。

其可选的片上JTAG 调试模块是基于别界测试的调试逻辑,支持硬件断点、数据触发和片外片内的调试跟踪。

Nios II标准内核设计框图如图2所示。

Nios CPU的所有数据、程序都是通过Avalon总线传输的,系统的FPGA片外PIO(外围IO)包括一个串行口、显示、键盘、存储器,片内PIO采用FIFO实现。

基于Nios Ⅱ的SOPC系统设计

能囤 l

建立项层图

l

用S OPCBule建 i r d 立 Nis 理 器及 o处

所需外设接口

段. 借助 于 以计 算 机 为平 台的 E A工具 进行 _。 D 2 j

2 基 于 No l S C 设 计 流 程 is l的 0P

基本的 S P O C系统 , 致 可 以分 为 F G 存 大 P A、

1 概

述

S P S s m O rga a l C i1 O C fyt nP ormm be hp 即可 编 e

程 的片上 系统 是 一种 特殊 的片 上系 统(o )其 实 s c,

质就 是 S C技术 f O 由单 个 芯 片 完成 整 个 系统 的 主 要 逻辑 功 能1只 是 它利 用 了 F G , P A或 C L P D器 件 的可编 程 性来 进 行 S C设 计 n。S P O ] O C最早 是 由 美 国 At a 司 于 2 0 lr 公 e 0 0年 提 出来 的 , 同时推 出 并

于设计 工程 Байду номын сангаас件 ,建立 N o 核 。具 体流 程 如 图 2 is

所 示 [。 3 ]

21 硬 件 设 计 .

根 据 系统 要实 现 的功 能 . 定 No 处 理器 和 确 is

外 围器件 , : 如 显示 屏 、 钮 、 按 蜂鸣器 、 储器等 。 存 接

下 来 ,在 S P ule 中 建 立 系 统 要 添 加 的模 O CB i r d 块 , 括 : i I3 bt P 定 时 器 、 键 P O、 包 No I 2 i C U、 s 按 I L D PO、 部 R C I 外 AM 总 线 ( ao Avl n三 态 桥 ) 外 部 、

基于NiosⅡ的通用信号源的SOPC设计与实现

图3.2DSPBuilder在MatJ曲平台设计DDS模型图3.3Simulink模拟示波器组件对DDS模型的显示波形图3.4是本设计中DDS部分在QuartusH原理图输入界面的顶层结构图。

累加器模块直接调用QuartuslI软件自带的功能函数模块来实现,位宽选择32位,裁剪掉一些不需要的进位、溢出和使能等功能,以减小资源占有量。

此处之所以选择32位的累加器,是为了提高DDS的精度。

由式(3.12)可知,在DDS输入时钟为160MHz的情况下,频率分辨率为160X106/2”=0.03725Hz,可见最低频率也可以达到0.03725Hz。

加法器则使用了软件提供的兆功能模块,设计时需要选择同步时钟,并且在加减选择时选择加法器,同样是32位的位宽。

这两个器件的关键在于其中的流水线设置,如果不设置流水线,模块在完成功能时达不到高速,甚至会成为整体系统中速度无法图3.5Quartusll中DDS模块的时序仿真图§3.3DDS噪声分析DDS噪声主要分为两大类119】:相位噪声和杂散噪声。

其中相位噪声主要由参考时钟信号的相位噪声、参考时钟的频率和输出频率之比的关系和器件本身的噪声基底决定。

从理论上讲,输出信号的相位噪声相对于时钟信号有2019(fc/)自)dB的改善。

总的来说,相位噪声相比杂散噪声比较小洲。

杂散噪声的来源主要有三种【19l:相位截断噪声、幅度量化噪声、DAC非线性转换噪声。

其中幅度量化噪声与DAC非线性转换噪声的产生原因主要与DAC器件有关,选用分辨率高以及转换线性度较高的DAC可以很明显的改善这两种杂散噪声。

余下对输出频谱影响较大的就是相位截断噪声,通过改善相位杂散噪声可以很明显的改善信号输出谱的质量【211,而且它的改善方法也较容易在FPGA内实现,因此下文将主要分析DDS的相位截断杂散噪声。

§33.1DDS的相位截断杂散噪声分析在DDS系统中,为了追求较高的频率分辨率,往往会把相位累加器的位数Ⅳ取的很大。

SOPC实验报告

SOPC系统设计技术实验报告姓名:学号:院系: 信息科学与工程学院专业:电子科学与技术指导老师:完成日期: 2015年04月25日实验二、NIOSII实现串口收发数据及LCD显示一、实验目的(1)进一步熟悉Quartus II、SOPC Builder、NIOS II IDE的操作;(2)掌握SOPC硬件系统及NIOS II软件的开发流程。

二、实验内容(1)、实验平台:硬件:PC级、SmartSOPC+教学实验开发平台;软件:Quartus II ,SOPC Builder ,NIOS II IDE 。

(2)、实验内容:建立包含SDRAM、JTAG_UART、Timer、LCD的NIOS II处理器系统,通过JTAG_UART从IDE的控制端窗口读取输入值N,计算1至N的累加值,并将计算结果及计算花费时间的显示在LCD中。

三、实验步骤硬件设计根据实验内容,可以得出本次实验的硬件结构图如图所示:图硬件设计结构图具体硬件设计步骤如下:1)、在Quartus II中建立一个工程命名为:smallCore,器件设置为EP3C55F484C8;2)、以原理图输入方式建立空白顶层模块,并保持;3)、打开SOPC Builder,命名SOPC系统名称为nios2system,开始建立NIOS II系统。

4)、双击SOPC Builder主界面左侧中的“Nios II Processor”,出现Nios II CPU的配置向导对话框,如图所示,在这里可以有三种Nios II CPU选择,我们选择快速型的Nios II/f,不使用硬件乘法器及除法器。

然后单击Next进入下一步配置;Instruction Cache项中选择2 Kbytes,在Data Cache项中选择512 Bytes,单击Next进行下一步配置;在“Advanced Features”和“MMU and MPU Settings”选项卡中选择默认参数,然后单击Next,到了“JTAG Debug Module”选项卡,如图所示。

sopc实验报告

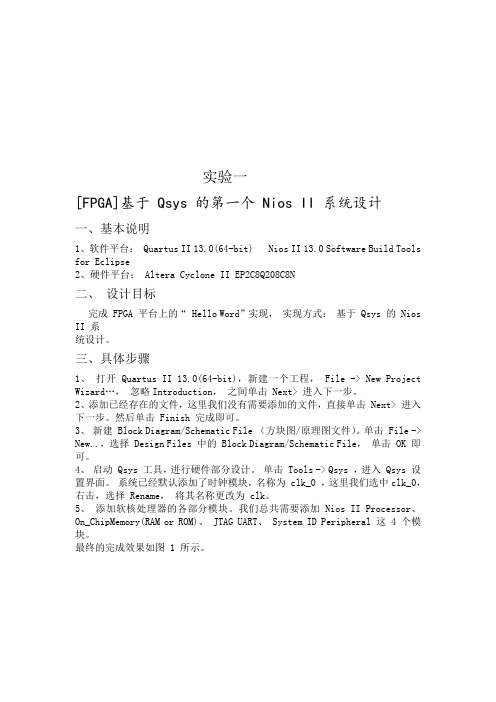

实验一[FPGA]基于 Qsys 的第一个 Nios II 系统设计一、基本说明1、软件平台: Quartus II 13.0(64-bit) Nios II 13.0 Software Build Tools for Eclipse2、硬件平台: Altera Cyclone II EP2C8Q208C8N二、设计目标完成 FPGA 平台上的“ Hello Word”实现,实现方式:基于 Qsys 的 Nios II 系统设计。

三、具体步骤1、打开 Quartus II 13.0(64-bit),新建一个工程, File -> New Project Wizard…,忽略Introduction,之间单击 Next> 进入下一步。

2、添加已经存在的文件,这里我们没有需要添加的文件,直接单击 Next> 进入下一步。

然后单击 Finish 完成即可。

3、新建 Block Diagram/Schematic File (方块图/原理图文件)。

单击 File -> New..,选择 Design Files 中的 Block Diagram/Schematic File,单击 OK 即可。

4、启动 Qsys 工具,进行硬件部分设计。

单击 Tools -> Qsys ,进入 Qsys 设置界面。

系统已经默认添加了时钟模块,名称为 clk_0 ,这里我们选中clk_0,右击,选择 Rename,将其名称更改为 clk。

5、添加软核处理器的各部分模块。

我们总共需要添加 Nios II Processor、On_ChipMemory(RAM or ROM)、 JTAG UART、 System ID Peripheral 这 4 个模块。

最终的完成效果如图 1 所示。

图 1 Qsys Connections 完成效果6、进行软核的相关设置。

首先双击 nios2_qsys,进入处理器设置模块。

基于NiosⅡ处理器的SOPC应用平台的研究与应用的开题报告

基于NiosⅡ处理器的SOPC应用平台的研究与应用的开题报告一、选题背景基于NiosⅡ处理器的SOPC应用平台是一种基于可编程逻辑器件的应用系统实现方式。

该平台将可编程逻辑与CPU、RAM、Flash、各类接口电路等资源集成在一起,能够实现内部硬件资源灵活配置。

SOPC应用平台的设计与实现,是目前FPGA技术有重要的应用领域。

二、研究内容本文的研究内容主要有以下几个方面:(1)SOPC应用平台的设计与实现该部分主要包括可编程逻辑设计、硬件资源连接与配置、外设驱动开发等内容,实现集成的硬件资源与软件设计的有机结合。

(2)NiosⅡ处理器的软件设计该部分主要包括处理器初始化、软件开发环境的搭建、驱动程序的编写、各类接口的控制等内容,实现针对特定硬件资源的软件控制程序。

(3)应用案例的实现与测试该部分主要通过应用实例,验证SOPC应用平台的实现与可行性。

应用案例包括数字信号处理、网络通信、图像处理等领域。

三、研究方法本文采用文献调研、实验研究与案例分析相结合的研究方法。

(1)文献调研:该部分主要搜集相关领域的文献,对SOPC应用平台的相关知识进行了解,为后续实验研究与应用提供参考。

(2)实验研究:该部分主要进行SOPC应用平台的硬件与软件开发实验,实现各种接口电路的控制,验证设计的正确性与可靠性。

(3)案例分析:该部分主要通过应用实例,探究SOPC应用平台在数字信号处理、网络通信、图像处理等领域的应用,验证其实现的可行性。

四、研究意义(1)本文的研究成果有助于掌握基于NiosⅡ处理器的SOPC应用平台的设计与实现方法,提高应用平台的开发和应用水平。

(2)应用案例的实现与测试将验证该平台在数字信号处理、网络通信、图像处理等领域应用的可行性,拓展了应用平台的应用领域。

(3)该平台的成功研究开发,有助于为可编程逻辑领域的发展提供技术支持与推动。

五、进度计划第一阶段(4-6周):文献调研与总体规划第二阶段(6-8周):SOPC应用平台的硬件设计与实现第三阶段(8-10周):NiosⅡ处理器软件设计与外设驱动开发第四阶段(10-12周):应用案例实现与测试第五阶段(12-14周):论文撰写和修改六、预期目标(1)完成基于NiosⅡ处理器的SOPC应用平台的设计、实现和应用分析。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 3.运行结果

五、运行情况与问题分析

1、建立工程时,注意不能出现中文或者空格,且工程名需与文件名一致, 选定芯片;

2、在生成 CPU 硬件系统时,定义端口时,需注意设定端口输入与输出的位 宽,需与程序定义的数值一致,否则运行溢出报错,须修改;

3、建立图形文件后,需进行编译,出现错误得返回原理图核对,找到错误 修改后重新编译;

void LCD_Show_Text(char*Text);

void LCD_Line2();

void LCD_Test();

5

山东工商学院

//========================= #endif //_LCD_H_

课程设计报告

5、连接开发板,将文件下载到开发板,运行文件检验是否正确。 6、检查错误并修改,知道结果正确。 7、运行结果

在 Nios II 里建立工程,选择相应的模块,编写需要嵌入的软件,添加缺少 的头文件对应的宏定义,编译工程,进行软件下载,在观察结果。

四、设计步骤

1、打开 Quartus II 新建工程

1

山东工商学院

2、打开 SOPC Builder 生成相应的硬件如图所示

课程设计报告

图 1.SoPC 配置

建立好后点击 Generate 运行,看是否出错,然后点击 exit 退出。 3、调用刚才生成的硬件系统,在 Quartus II 中建立图形文件,然后进行引脚锁

4

山东工商学院

课程设计报告

OSTaskCreateExt(task2, NULL, (void *)&task2_stk[TASK_STACKSIZE-1], TASK2_PRIORITY, TASK2_PRIORITY, task2_stk, TASK_STACKSIZE, NULL, 0);

OSTaskCreateExt(task3, NULL, (void *)&task3_stk[TASK_STACKSIZE-1], TASK3_PRIORITY, TASK3_PRIORITY, task3_stk, TASK_STACKSIZE, NULL, 0);

IORD(base, 1)

#define lcd_write_data(base,data) IOWR(base, 2, data)

#define lcd_read_data(base)

IORD(base, 3)

//==========================

void LCD_Init();

7

山东工商学院

指导教师评语

课程设计报告

课程设计成绩: 指导教师签字:

8

4、进行引脚锁定时,注意引脚文件的编写,否则选择引脚文件点击 Run 后 会不成功,从而影响后面程序的调试;

6

山东工商学院

课程设计报告

六、结论

采用NIOSⅡ集成开发环境提供的快捷开发手段,在Cyclone 1C6Q240C8芯片 上创建了一个用户定制CPU和外设的片上系统,同时完成对液晶显示器和LED的 编程控制。整个系统充分体现了SOPC设计方法的灵活性,设计时只定制系统需 要的外设器件接口,避免过多的外围电路和器件造成体积、功耗的增多和可靠性 的下降。由于采用软核结构,方便系统的升级和扩展,而不必硬件改版,节约了 成本,加快开发进度,缩短了产品的开发周期。

二、设计要求

从零开始建立一个基于 Nios II 的 μC/OS-II 应用实验系统(也可以认为 是一个Nios II+μC/OS-II 的应用框架)具有以下一些作用。

(1) 读者可以借助 SOPC Builder 工具自行对 Nios II 软核处理器进行配 置。

(2) 很多范例都是纯硬件的VHDL代码,需要自行从零开始建立 Nios II 系统,不能够直接使用 Altera 公司已经建立好的 Nios II 系统。

{

ile (1)

{

printf("Hello from task2\n");

OSTimeDlyHMSM(0, 0, 5, 0);

}

}

void task3(void* pdata)

{

while (1)

{

printf("Hello from task3\n");

OSTimeDlyHMSM(0, 0, 4, 0);

FPGA-CPLD 原理及应用课程设计报告

题目: 基于 NIOS 的 μC/OS-II 实验

学院: 信息与电子工程学院 专业: 电子科学与技术 学号: 姓名: 指导老师: 时间:2013-7-15~2013-7-20

山东工商学院

课程设计报告

一、摘要

本实验项目使用 Quartus II、SOPC Builder 和 Nios II EDS 从零开始构建一 个能够在 DE2-115 实验平台上运行的 μC/OS-II 操作系统的 Nios II 系统。初 学者可以借此范例熟悉 Quartus II、SOPC Builder、Nios II EDS 的使用,并且了 解基于 FPGA 的嵌入式系统开发流程。 关键词: SOPC Builder Nios II DE2 Nios II EDS

void task1(void* pdata)

{

while (1)

{

printf("Hello from task1\n");

OSTimeDlyHMSM(0, 0, 6, 0);

}

}

/* Prints "Hello World" and sleeps for three seconds */

void task2(void* pdata)

七、心得体会

经过本次 SOPC 课程设计实验,使我更加熟悉了 Quartus Ⅱ与 Nios Ⅱ DE2 以及开发板的使用,熟练掌握了从理论设计到硬件开发的流程,了解了万年历通 过编程实现的整个过程。从整个实验实现的过程中,碰到一些以前未出现过的问 题,在自己的努力以及同学、老师的帮助下,使自己的理论及操作水平有所提高。

定。 引脚锁定引脚文件如下:

2

山东工商学院

课程设计报告

图 2.引脚配置

然后进行编译,在 Quartus I 下生成文件如下图: 4、Nios II 运行

打开 Nios II IDE2,建立工程,选择 count_binary 模块,添加一个 LCD.h 的 顶层文件。

在此写出 C 语言程序代码。

#include <stdio.h> #include "includes.h"

/* Definition of Task Stacks */

#define TASK_STACKSIZE

2048

OS_STK task1_stk[TASK_STACKSIZE];

OS_STK task2_stk[TASK_STACKSIZE];

OS_STK task3_stk[TASK_STACKSIZE];

}

}

/* The main function creates two task and starts multi-tasking */

int main(void)

{

OSTaskCreateExt(task1, NULL, (void *)&task1_stk[TASK_STACKSIZE-1], TASK1_PRIORITY, TASK1_PRIORITY, task1_stk, TASK_STACKSIZE, NULL, 0);

SOPC Builder 是在 Quartus II 里的 SOPC Builder 进行的,先建立工程在 SOPC Builder 里添加硬件,包括 CPU ,PLL,onchip_memory,SSRAM,SDRAM Tristate Bridge, Flash, JTAG UART,UART, Timer System ID 2、Quartus II 硬件处理 硬件会自动建立一个顶层模块,通过建一个原理图来对对应的硬件进行输 入输出的添加,再锁定引脚,编译工程,硬件下载。 3、Nios II DE2 嵌入软件编写

OSStart(); return 0;

}

LCD.h 的顶层文件为:

#ifndef _LCD_H_

#define _LCD_H_

//LCD Module 16*2

#define lcd_write_cmd(base,data) IOWR(base, 0, data)

#define lcd_read_cmd(base)

3

山东工商学院

课程设计报告

/* Definition of Task Priorities */

#define TASK1_PRIORITY

1

#define TASK2_PRIORITY

2

#define TASK3_PRIORITY

3

/* Prints "Hello World" and sleeps for three seconds */