BCP69_NL中文资料

BCP69T1中文资料

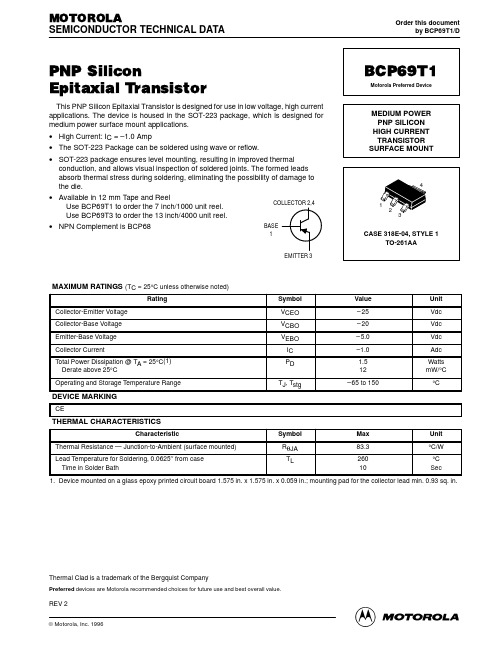

MAXIMUM RATINGS (TC = 25°C unless otherwise noted)

Rating Collector-Emitter Voltage Collector-Base Voltage Emitter-Base Voltage Collector Current Total Power Dissipation @ TA = 25°C(1) Derate above 25°C Operating and Storage Temperature Range Symbol VCEO VCBO VEBO IC PD TJ, Tstg Value – 25 – 20 – 5.0 –1.0 1.5 12 – 65 to 150 Unit Vdc Vdc Vdc Adc Watts mW/°C °C

1

元器件交易网 BCP69T1

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted)

Characteristics Symbol Min Typ Max Unit

OFF CHARACTERISTICS

Collector-Emitter Breakdown Voltage (IC = –100 µAdc, IE = 0) Collector-Emitter Breakdown Voltage (IC = –1.0 mAdc, IB = 0) Emitter-Base Breakdown Voltage (IE = –10 µAdc, IC = 0) Collector-Base Cutoff Current (VCB = – 25 Vdc, IE = 0) Emitter-Base Cutoff Current (VEB = – 5.0 Vdc, IC = 0) V(BR)CES V(BR)CEO V(BR)EBO ICBO IEBO – 25 – 20 – 5.0 — — — — — — — — — — –10 –10 Vdc Vdc Vdc µAdc µAdc

NC7WZ07P6X_NL中文资料

© 2005 Fairchild Semiconductor Corporation DS500218March 1999Revised February 2005NC7WZ07 TinyLogic £ UHS Dual Buffer (Open Drain Outputs)NC7WZ07TinyLogic £ UHS Dual Buffer (Open Drain Outputs)General DescriptionThe NC7WZ07 is a dual buffer with open drain outputs from Fairchild's Ultra High Speed Series of TinyLogic £ in the space saving SC70 6-lead package. The device is fab-ricated with advanced CMOS technology to achieve ultra high speed with high output drive while maintaining low static power dissipation over a very broad V CC operating range. The device is specified to operate over the 1.65V to 5.5V V CC range. The inputs and outputs are high imped-ance when V CC is 0V. Inputs tolerate voltages up to 7V independent of V CC operating voltage.Featuress Space saving SC70 6-lead packages Ultra small MicroPak ¥ Pb-Free leadless package s Ultra High Speed: t PZL 2.3 ns Typ into 50 pF at 5V V CC s High I OL Output Drive: 24 mA at 3V V CC s Broad V CC Operating Range: 1.65V to 5.5V s Matches the performance of LCX when operated at 3.3V V CC s Power down high impedance inputs/outputss Overvoltage tolerant inputs facilitate 5V to 3V translation s Patented noise/EMI reduction circuitry implementedOrdering Code:Pb-Free package per JEDEC J-STD-020B.Note 1: “_NL” indicates Pb-Free product (per JEDEC J-STD-020B). Device is available in Tape and Reel only.TinyLogic £ is a registered trademark of Fairchild Semiconductor Corporation.MicroPak ¥ is a trademark of Fairchild Semiconductor Corporation.Order Package Product Code Package DescriptionSupplied AsNumber Number Top Mark NC7WZ07P6X MAA06A Z076-Lead SC70, EIAJ SC88, 1.25mm Wide3k Units on Tape and ReelNC7WZ07P6X_NL (Note 1)MAA06A Z07Pb-Free 6-Lead SC70, EIAJ SC88, 1.25mm Wide3k Units on Tape and ReelNC7WZ07L6XMAC06AD3Pb-Free 6-Lead MicroPak, 1.0mm Wide5k Units on Tape and Reel 2N C 7W Z 07Logic SymbolIEEE/IECPin DescriptionsFunction TableY AH HIGH Logic Level L LOW Logic LevelConnection DiagramsPin Assignments for SC70(Top View)Pin One Orientation DiagramAAA represents Product Code Top Mark - see ordering codeNote: Orientation of Top Mark determines Pin One location. Read the top product code mark left to right, Pin One is the lower left pin (see diagram).Pad Assignments for MicroPak(Top Thru View)Pin Names Description A 1, A 2Data Inputs Y 1, Y 2OutputInput Output A Y L L HZNC7WZ07Absolute Maximum Ratings (Note 2)Recommended Operating Conditions (Note 3)Note 2: Absolute maximum ratings are DC values beyond which the device may be damaged or have its useful life impaired. The datasheet specifica-tions should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading vari-ables. Fairchild does not recommend operation outside datasheet specifi-cations.Note 3: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSupply Voltage (V CC ) 0.5V to 7V DC Input Voltage (V IN ) 0.5V to 7V DC Output Voltage (V OUT ) 0.5V to 7VDC Input Diode Current (I IK )@ V IN 0.5V50 mA DC Output Diode Current (I OK )@ V OUT 0.5V 50 mA DC Output Current (I OUT ) 50 mA DC V CC /GND Current (I CC /I GND )r 100 mAStorage Temperature (T STG )65q C to 150q CJunction Temperature under Bias (T J )150q CJunction Lead Temperature (T L )(Soldering, 10 seconds)260q C Power Dissipation (P D ) @ 85q C180 mWSupply Voltage Operating (V CC ) 1.65V to 5.5V Supply Voltage Data Retention (V CC ) 1.5V to 5.5V Input Voltage (V IN )0V to 5.5V Output Voltage (V OUT )0V to 5.5VOperating Temperature (T A ) 40q C to 85q CInput Rise and Fall Time (t r , t f )V CC 1.8V, 2.5V r 0.2V 0 ns/V to 20 ns/V V CC 3.3V r 0.3V 0 ns/V to 10 ns/V V CC 5.0V r 0.5V 0 ns/V to 5 ns/VThermal Resistance (T JA )350q C/W Symbol ParameterV CC T A 25q CT A 40q C to 85q C Units Conditions(V)Min TypMaxMin MaxV IH HIGH Level Input Voltage 1.65 to 1.950.75 V CC0.75 V CC V 2.3 to 5.50.7 V CC0.7 V CCV IL LOW Level Input Voltage 1.65 to 1.950.25 V CC 0.25 V CC V 2.3 to 5.50.3 V CC0.3 V CC I LKG HIGH Level Output 1.65 to 5.5r 5r 10P AV IN V IHLeakage CurrentV OUT V CC or GNDV OLLOW Level Output Voltage1.650.00.10.0VV IN V ILI OL 100 P A1.80.00.10.12.30.00.10.13.00.00.10.14.50.00.10.11.650.080.240.24VI OL 4 mA 2.30.100.30.3I OL 8 mA 3.00.160.40.4I OL 16 mA 3.00.240.550.55I OL 24 mA 4.50.250.550.55I OL 32 mAI IN Input Leakage Current 0 to 5.5r 0.1r 1.0P A 0 d V IN d 5.5V I OFF Power Off Leakage Current 0.0110P A V IN or V OUT 5.5V I CCQuiescent Supply Current1.65 to 5.51.010P A V IN 5.5V, GND 4N C 7W Z 07AC Electrical CharacteristicsNote 4:C PD is defined as the value of the internal equivalent capacitance which is derived from dynamic operating current consumption (I CCD ) at no output loading and operating at 50% duty cycle. (See Figure 2.) C PD is related to I CCD dynamic operating current by the expression: I CCD (C PD )(V CC )(f IN ) (I CC static).AC Loading and WaveformsC L includes load and stray capacitance Input PRR 1.0 MHz; t W 500 nsFIGURE 1. AC Test CircuitInput AC Waveform; t r t f 1.8 ns;PRR 10 MHz; Duty Cycle 50%FIGURE 2. I CCD Test CircuitFIGURE 3. AC WaveformsSymbol ParameterV CC T A 25q CT A 40q C to 85q C UnitsConditionsFigure (V)Min Typ Max Min Max Numbert PZLPropagation Delay1.65 1.8 6.611.5 1.812.6nsFigures 1, 31.8 1.8 5.59.5 1.810.5C L 50 pF2.5 r 0.2 1.23.7 5.8 1.2 6.4RU 500:3.3 r 0.30.8 2.94.40.8 4.8RD 500:5.0 r 0.50.5 2.3 3.50.5 3.9V I 2 x V CCt PLZPropagation Delay1.65 1.8 5.511.5 1.812.6nsFigures 1, 31.8 1.8 4.39.5 1.810.5C L 50 pF2.5 r 0.2 1.2 2.8 5.8 1.2 6.4RU 500:3.3 r 0.30.8 2.14.40.8 4.8RD 500:5.0 r 0.50.51.4 3.50.53.9V I 2 x V CCC IN Input Capacitance 0 2.5pF C OUT Output Capacitance 0 4.0pF C PDPower Dissipation 3.33pF(Note 4)Figure 2Capacitance5.04NC7WZ07Tape and Reel SpecificationTAPE FORMAT for SC70TAPE DIMENSIONS inches (millimeters)PackageTape Number Cavity Cover Tape DesignatorSection Cavities Status Status Leader (Start End)125 (typ)Empty Sealed P6XCarrier 3000Filled Sealed Trailer (Hub End)75 (typ)EmptySealedPackage Tape Size DIM A DIM B DIM F DIM K o DIM P1DIM W SC70-68 mm0.0930.0960.138 r 0.0040.053 r 0.0040.1570.315 r 0.004(2.35)(2.45)(3.5 r 0.10)(1.35 r 0.10)(4)(8 r 0.1) 6N C 7W Z 07Tape and Reel Specification (Continued)TAPE FORMAT for MicroPakREEL DIMENSIONS inches (millimeters)PackageTape Number Cavity Cover Tape DesignatorSection Cavities Status Status Leader (Start End)125 (typ)Empty Sealed L6XCarrier 5000Filled Sealed Trailer (Hub End)75 (typ)EmptySealedTape Size A B C D N W1W2W38 mm7.00.0590.5120.795 2.1650.331 0.059/ 0.0000.567W1 0.078/ 0.039(177.8)(1.50)(13.00)(20.20)(55.00)(8.40 1.50/ 0.00)(14.40)(W1 2.00/ 1.00)NC7WZ07 Physical Dimensions inches (millimeters) unless otherwise noted6-Lead SC70, EIAJ SC88, 1.25mm WidePackage Number MAA06A8N C 7W Z 07 T i n y L o g i c £ U H S D u a l B u f f e r (O p e n D r a i n O u t p u t s )Physical Dimensions inches (millimeters) unless otherwise noted (Continued)Pb-Free 6-Lead MicroPak, 1.0mm WidePackage Number MAC06AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

HCNW137中文资料

The 6N137, HCPL-26XX, HCPL06XX, HCPL-4661, HCNW137, and HCNW26X1 are suitable for high speed logic interfacing, input/output buffering, as line receivers in environments that conventional line receivers cannot tolerate and are recommended for use in extremely high ground or induced noise environments.

Small-Outline SO-8 Single Channel Package HCPL-0600 HCPL-0630 HCPL-0601 HCPL-0631 HCPL-0611 HCPL-0661 Dual Channel Package

Widebody (400 Mil) Single Channel Package HCNW137 HCNW2601 HCNW2611

1-146 5965-3594E

元器件交易网

an open collector Schottkyclamped transistor. The internal shield provides a guaranteed common mode transient immunity specification of 5,000 V/µs for the HCPL-X601/X631 and HCNW2601, and 10,000 V/µs for the HCPL-X611/X661 and HCNW2611.

Functional Diagram

2N3906中文资料(nte)中文数据手册「EasyDatasheet - 矽搜」

VCE = 1V, I C = 1mA

40 − − 80 − −

2N3905 2N3906

VCE = 1V, I C = 10mA

50 − 150 100 − 300

2N3905 2N3906

VCE = 1V, I C = 50mA

30 − − 60 − −

2N3905 2N3906

VCE = 1V, I C = 100mA

芯片中文手册,看全文,戳

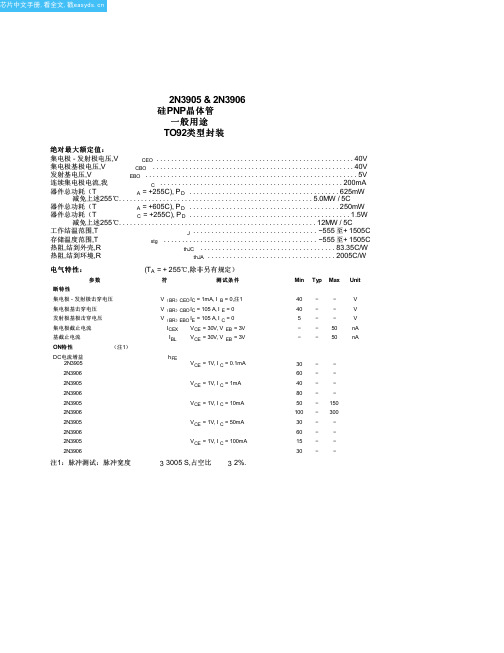

2N3905 & 2N3906 硅PNP晶体管

一般用途

TO92类型封装

绝对最大额定值:

集电极 - 发射极电压,V

CEO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40V

器件总功耗(T

C = +255C), PD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5W

减免上述255℃. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12MW / 5C

减免上述255℃. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5.0MW / 5C

器件总功耗(T

6N134中文资料

6N134中⽂资料FeaturesDual Marked with Device Part Number and DSCC Drawing NumberManufactured and Tested on a MIL-PRF-38534 Certified LineQML-38534, Class H and K Five Hermetically Sealed Package Configurations Performance Guaranteed over -55°C to +125°C ? High Speed: 10 M Bit/sCMR: > 10,000 V/µs Typical 1500 Vdc Withstand Test Voltage2500 Vdc Withstand Test Voltage for HCPL-565X High Radiation Immunity 6N137, HCPL-2601, HCPL-2630/-31 Function Compatibility ? Reliability DataTTL Circuit CompatibilityApplicationsMilitary and SpaceHigh Reliability SystemsTransportation, Medical, and Life Critical SystemsLine ReceiverVoltage Level ShiftingIsolated Input Line Receiver Isolated Output Line Driver Logic Ground Isolation Harsh Industrial EnvironmentsIsolation for Computer,Communication, and Test Equipment SystemsDescriptionThese units are single, dual and quad channel, hermetically sealed optocouplers. The products are capable of operation and storage over the full military temperature range and can be purchased as either standard product or with full MIL-PRF-38534 Class Level H or K testing or from the appropri-ate DSCC Drawing. All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DSCC Quali-fied Manufacturers List QML-38534 for Hybrid Microcircuits.Quad channel devices areavailable by special order in the 16 pin DIP through hole packages.Truth Table(Positive Logic)Multichannel DevicesInput Output On (H)L Off (L)HFunctional DiagramMultiple Channel Devices AvailableSingle Channel DIP Input Enable Output On (H)H L Off (L)H H On (H)L H Off (L)LH*See matrix for available extensions.Hermetically Sealed, High Speed,High CMR, Logic Gate Optocouplers Technical Data6N134*81028HCPL-563X HCPL-663X HCPL-565X 5962-98001HCPL-268K HCPL-665X 5962-90855HCPL-560XCAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.V CC V OUTV E GNDThe connection of a 0.1 µF bypass capacitor between V CC and GND is recommended.Selection Guide–Package Styles and Lead Configuration OptionsPackage16 Pin DIP 8 Pin DIP 8 Pin DIP 8 Pin DIP 16 Pin Flat Pack 20 Pad LCCC Lead Style Through Hole Through Hole Through Hole Through Hole Unformed Leads Surface MountChannels 212242Common Channel V CC , GND None V CC , GND V CC , GND V CC , GND None WiringWithstand Test Voltage 1500 Vdc 1500 Vdc 1500 Vdc 2500 Vdc 1500 Vdc 1500 Vdc Agilent Part # & Options Commercial6N134*HCPL-5600HCPL-5630HCPL-5650HCPL-6650HCPL-6630MIL-PRF-38534, Class H 6N134/883BHCPL-5601HCPL-5631HCPL-5651HCPL-6651HCPL-6631MIL-PRF-38534, Class K HCPL-268K HCPL-560K HCPL-563K HCPL-665K HCPL-663K Standard Lead Finish Gold Plate Gold Plate Gold Plate Gold Plate Gold PlateSolder PadsSolder Dipped Option #200Option #200Option #200Option #200Butt Cut/Gold Plate Option #100Option #100Option #100Gull Wing/Soldered Option #300Option #300Option #300Class H SMD Part #Prescript for all below None 5962-None None None None Either Gold or Solder 8102801EX 9085501HPX 8102802PX 8102805PX 8102804FX 81028032XGold Plate 8102801EC 9085501HPC 8102802PC 8102805PC 8102804FCSolder Dipped 8102801EA 9085501HPA 8102802PA 8102805PA81028032A Butt Cut/Gold Plate 8102801UC 9085501HYC 8102802YC Butt Cut/Soldered 8102801UA 9085501HYA 8102802YA Gull Wing/Soldered 8102801TA 9085501HXA8102802ZA Class K SMD Part #Prescript for all below 5962-5962-5962-5962-5962-Either Gold or Solder 9800101KEX 9085501KPX 9800102KPX 9800104KFX 9800103K2XGold Plate 9800101KEC 9085501KPC 9800102KPC 9800104KFCSolder Dipped 9800101KEA 9085501KPA 9800102KPA 9800103K2AButt Cut/Gold Plate 9800101KUC 9085501KYC 9800102KYC Butt Cut/Soldered 9800101KUA 9085501KYA 9800102KYA Gull Wing/Soldered9800101KTA 9085501KXA 9800102KZA*JEDEC registered part.Each channel contains a GaAsP light emitting diode which isoptically coupled to an integrated high speed photon detector. The output of the detector is an open collector Schottky clamped transistor. Internal shields provide a guaranteed common mode transient immunityspecification of 1000 V/µs. For Isolation Voltage applications requiring up to 2500 Vdc, the HCPL-5650 family is also available. Package styles for these parts are 8 and 16 pin DIP through hole (case outlines P andE respectively), and 16 pin surface mount DIP flat pack(case outline F), leadless ceramic chip carrier (case outline 2).Devices may be purchased with a variety of lead bend and plating options. See Selection Guide Table for details. Standard Microcircuit Drawing (SMD)parts are available for each package and lead style.Because the same electrical die (emitters and detectors) are used for each channel of each device listed in this data sheet, absolute maximum ratings, recommended operating conditions, electrical specifications, and performance characteristics shown in the figures are identical for all parts.Occasional exceptions exist due to package variations and limitations,and are as noted. Additionally, the same package assembly processes and materials are used in all devices. These similarities give justification for the use of data obtained from one part torepresent other parts’ performance for reliability and certain limited radiation test results.Outline Drawings16 Pin DIP Through Hole, 2 ChannelsFunctional DiagramsNote: All DIP and flat pack devices have common V CC and ground. Single channel DIP has an enable pin 7. LCCC (leadless ceramic chip carrier) package has isolated channels with separate VCC and ground connections. All diagrams are “top view.”Leaded Device MarkingLeadless Device MarkingNOTE: DIMENSIONS IN MILLIMETERS (INCHES).COMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)COUNTRY OF MFR.Agilent CAGE CODE*Agilent DESIGNATORDSCC SMD*PIN ONE/ ESD IDENTAgilent P/N DSCC SMD** QUALIFIED PARTS ONLYCOMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)DSCC SMD*Agilent CAGE CODE*Agilent DESIGNATORCOUNTRY OF MFR.Agilent P/N PIN ONE/ ESD IDENTDSCC SMD** QUALIFIED PARTS ONLYOutline Drawings (continued)16 Pin Flat Pack, 4 Channels8 Pin DIP Through Hole, 2 Channels 2500 Vdc Withstand Test Voltage20 Terminal LCCC Surface Mount,2Channels8 Pin DIP Through Hole, 1 and 2 Channels0.36 (0.014)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).2.29 (0.090) 2.79 (0.110)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES). SOLDER THICKNESS 0.127 (0.005) MAX.Hermetic Optocoupler OptionsRecommended Operating ConditionsParameterSymbol Min.Max.Units Input Current, Low Level, Each Channel I FL 0250µA Input Current, High Level, Each Channel*I FH 1020mA Supply Voltage, OutputV CC 4.55.5VFan Out (TTL Load) Each ChannelN6*Meets or exceeds DSCC SMD and JEDEC requirements.Absolute Maximum Ratings(No derating required up to +125°C)Storage Temperature Range, T S ...................................-65°C to +150°C Operating Temperature, T A..........................................-55°C to +125°C Case Temperature, T C ................................................................+170°C Junction Temperature, T J ...........................................................+175°C Lead Solder Temperature ...............................................260°C for 10 s Peak Forward Input Current, I F PK , (each channel,≤1 ms duration)......................................................................40 mA Average Input Forward Current, I F AVG (each channel)................20 mA Input Power Dissipation (each channel).....................................35 mW Reverse Input Voltage, V R (each channel).........................................5 V Supply Voltage, V CC (1 minute maximum)........................................7 V Output Current, I O (each channel)...............................................25 mA Output Power Dissipation (each channel). (40)mW Output Voltage, V O (each channel)..................................................7 V*Package Power Dissipation, P D (each channel)........................200 mW*Selection for higher output voltages up to 20 V is available.Single Channel Product OnlyEmitter Input Voltage, V E ...............................................................5.5 VNote enable pin 7. An external 0.01 µF to 0.1 µF bypass capacitor must be connected between V CC and ground for each package type.8 Pin Ceramic DIP Single Channel SchematicESD Classification(MIL-STD-883, Method 3015)HCPL-5600/01/0K ...............................................................(?), Class 16N134, 6N134/883B, HCPL-5630/31/3K, HCPL-5650/51, HCPL-6630/31/3K and HCPL-6650/51/5K.......................(Dot), Class 3Electrical Characteristics (T= -55°C to +125°C, unless otherwise specified)*Identified test parameters for JEDEC registered parts.**All typical values are at V CC = 5 V , T A = 25°C. Recommended Operating Conditions (cont’d.)Single Channel Product Only [10]ParameterSymbol Min.Max.Units High Level Enable Voltage V EH 2.0V CC V Low Level Enable VoltageV EL0.8VElectrical Characteristics, (Contd.) T= -55°C to +125°C unless otherwise specifiedSingle Channel Product Only Low Level I EL V CC = 5.5 V,1, 2, 3-1.45-2.0mA Enable Current V E = 0.5 V High Level V EH 1, 2, 3 2.0V10Enable Voltage Low Level V EL 1, 2, 30.8VEnable Voltage*Identified test parameters for JEDEC registered part.**All typical values are at V CC = 5 V , T A = 25°C.Typical Characteristics, T = 25°C, V = 5 VDual and Quad Channel Product Only Input-Input I I-I 0.5nA Relative Humidity = 45%4Leakage CurrentV I-I = 500 V, t = 5 s Resistance (Input-Input)R I-I 1012V I-I = 500 V 4Capacitance (Input-Input)C I-I0.55pF f = 1 MHz4Notes:1. Each channel.2. All devices are considered two-terminal devices; I I-O is measured between all input leads or terminals shorted together and alloutput leads or terminals shorted together.3. Measured between each input pair shorted together and all output connections for that channel shorted together.4. Measured between adjacent input pairs shorted together for each multichannel device.5. t PHL propagation delay is measured from the 50% point on the leading edge of the input pulse to the 1.5 V point on the leadingedge of the output pulse. The t PLH propagation delay is measured from the 50% point on the trailing edge of the input pulse to the1.5 V point on the trailing edge of the output pulse.6. The HCPL-6630, HCPL-6631, and HCPL-663K dual channel parts function as two independent single channel units. Use the singlechannel parameter limits for each channel.7. CM L is the maximum rate of rise of the common mode voltage that can be sustained with the output voltage in the logic low state(V O < 0.8 V). CM H is the maximum rate of fall of the common mode voltage that can be sustained with the output voltage in the logic high state (V O > 2.0 V).8. This is a momentary withstand test, not an operating condition.9. It is essential that a bypass capacitor (0.01 to 0.1 µF, ceramic) be connected from V CC to ground. Total lead length between bothends of this external capacitor and the isolator connections should not exceed 20 mm.10. No external pull up is required for a high logic state on the enable input.11. The t ELH enable propagation delay is measured from the 1.5 V point on the trailing edge of the enable input pulse to the 1.5 Vpoint on the trailing edge of the output pulse.12. The t EHL enable propagation delay is measured from the 1.5 V point on the leading edge of the enable input pulse tothe 1.5 Vpoint on the leading edge of the output pulse.13. Standard parts receive 100% testing at 25°C (Subgroups 1 and 9). SMD and 883B parts receive 100% testing at 25, 125, and-55°C (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).14. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteedto limits specified for all lots not specifically tested.15. Not required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.16. Required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.17. Not required for HCPL-5650, HCPL-5651 and 8102805 types.18. Required for HCPL-5650, HCPL-5651 and 8102805 types only.Figure 1. High Level Output Currentvs. Temperature.5 VV O * C L INCLUDES PROBE AND STRAY WIRING CAPACITANCE. Figure 4. Test Circuit for t PHL and t PLH .*I +5 V OUTPUT V O MONITORING NODEFigure 7. Test Circuit for Common Mode Transient Immunity and Typical Waveforms.11OUTPUT V OMONITORINGNODET A = +125 °C* ALL CHANNELS TESTED SIMULTANEOUSLY.V CCI O = 25 mAFigure 10. Operating Circuit for Burn-In and Steady State Life Tests. Figure 8. Test Circuit for t EHL and t ELH.Figure 9. Enable Propagation Delayvs. Temperature.MIL-PRF-38534 Class H,Class K, and DSCC SMDTest ProgramAgilent’s Hi-Rel Optocouplers arein compliance with MIL-PRF-38534 Classes H and K. Class Hand Class K devices are also incompliance with DSCC drawings81028, 5962-90855 and 5962-98001.Testing consists of 100% screen-ing and quality conformanceinspection to MIL-PRF-38534./doc/4e2d970a03d8ce2f006623a8.htmlData subject to change.Copyright ? 1999 Agilent TechnologiesObsoletes 5968-4743E5968-9407E (10/00)。

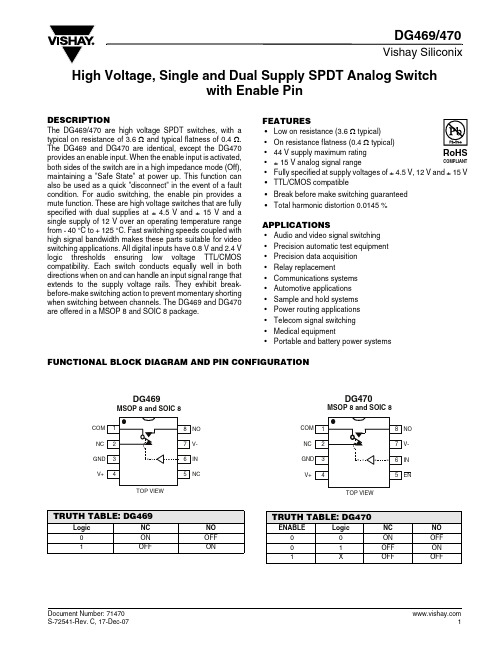

DG469资料

Vishay SiliconixDG469/470High Voltage, Single and Dual Supply SPDT Analog Switchwith Enable PinFEATURES•Low on resistance (3.6 Ω typical)•On resistance flatness (0.4 Ω typical) •44 V supply maximum rating •± 15 V analog signal range••TTL/CMOS compatible •Break before make switching guaranteed •Total harmonic distortion 0.0145 %APPLICATIONS•Audio and video signal switching •Precision automatic test equipment •Precision data acquisition •Relay replacement•Communications systems •Automotive applications •Sample and hold systems •Power routing applications •Telecom signal switching •Medical equipment•Portable and battery power systemsDESCRIPTIONThe DG469/470 are high voltage SPDT switches, with a typical on resistance of 3.6 Ω and typical flatness of 0.4 Ω.The DG469 and DG470 are identical, except the DG470provides an enable input. When the enable input is activated,both sides of the switch are in a high impedance mode (Off),maintaining a "Safe State" at power up. This function can also be used as a quick "disconnect" in the event of a fault condition. For audio switching, the enable pin provides a mute function. These are high voltage switches that are fully specified with dual supplies at ± 4.5 V and ± 15 V and a single supply of 12 V over an operating temperature range from - 40 °C to + 125 °C. Fast switching speeds coupled with high signal bandwidth makes these parts suitable for video switching applications. All digital inputs have 0.8 V and 2.4 V logic thresholds ensuring low voltage TTL/CMOS compatibility. Each switch conducts equally well in both directions when on and can handle an input signal range that extends to the supply voltage rails. They exhibit break-before-make switching action to prevent momentary shorting when switching between channels. The DG469 and DG470are offered in a MSOP 8 and SOIC 8 package.FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATIONTRUTH TABLE: DG469Logic NC NO 0ON OFF 1OFFONTRUTH TABLE: DG470ENABLELogic NC NO 00ON OFF 01OFF ON 1XOFFOFFVishay SiliconixDG469/470Notes:a. - 40 °C to 85 °C datasheet limits apply.Notes:a. Signals on S X , D X , or IN X exceeding V+ or V- will be clamped by internal diodes. Limit forward diode current to maximum current ratings.b. All leads welded or soldered to PC Board.c. Derate 4.0 mW/°C above 70 °C.d. Derate 5.0 mW/°C above 70 °C.ORDERING INFORMATIONTemp Range PackagePart NumberDG469/470- 40 °C to 125 °C a8-Pin MSOPDG469EQ-T1-E3DG470EQ-T1-E38-Pin Narrow SOICDG469EY -T1-E3DG470EY -T1-E3ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameter Limit Unit V+ to V- 44VGND to V- 25Digital Inputs a, V S , V D(V-) - 2 to (V+) + 2or 30 mA, whichever occurs firstContinuous Current (NO, NC, or COM)120mA Current (Any terminal except NO, NC, or COM)30Peak Current, (Pulsed 1 ms, 10 % Duty Cycle)200Storage T emperature - 65 to 150°C Power Dissipation (Package)b8-Pin MSOP c 320mW8-Pin Narrow SOIC d400SPECIFICATIONS FOR DUAL SUPPLIESParameter Symbol Test Conditions Unless Specified V+ = 15 V , V- = - 15 V V IN = 2.4 V , 0.8 V a Temp b Typ c - 40 to 125 °C- 40 to 85 °CUnitMin d Max d Min d Max dAnalog Switch Analog Signal Range e V ANALOGFull - 1515- 1515VOn-Resistance r ON I S = 50 mA, V D = - 10 V to + 10 VRoom Full 3.66867ΩOn-Resistance Match Δr ON I S = 50 mA, V D = ± 10 V Room Full 0.120.40.90.40.5On-Resistance Flatness r FLATNESS I S = 50 mA, V D = - 5 V, 0 V , + 5 VRoom Full 0.40.50.90.50.8Switch OffLeakage Current I S(off)V D = ± 14 V , V S = ± 14 VRoom Full ± 0.1- 0.5- 200.520- 0.5- 2.50.52.5nA I D(off)Room Full ± 0.1- 0.5- 200.520- 0.5- 2.50.52.5Channel On Leakage Current I D(on)V S = V D = ± 14 VRoom Full± 0.2- 0.5- 200.520- 0.5- 50.55Digital Control Input Current, V IN Low I IL V IN Under T est = 0.8 V Full 0.05- 11- 11µA Input Current, V IN High I IH V IN Under T est = 2.4 VFull 0.05- 11- 11Input Capacitance eC INf = 1 MHzRoom3.7pFVishay SiliconixDG469/470Dynamic Characteristics T urn-On Time t ON R L = 300 Ω, C L = 35 pFV S = ± 10 V Room Full 129166200166185nsT urn-Off Time t OFF Room Full 80108135108120Break-Before-MakeTime Delay t D V S = 10 VR L = 300 Ω, C L = 35 pF Room 15Charge Injection e Q V g = 0 V , R g = 0 Ω, C L = 1 nFRoom 58pCOff Isolation eOIRR R L = 50 Ω, C L = 5 pFf = 1 MHzRoom - 57dB Channel-to-Channel Crosstalk eX T ALK Room - 63Source Off Capacitance e C S(off) f = 1 MHzRoom 37pF Drain Off Capacitance e C D(off)Room 85Channel On Capacitance e C D(on)Room125Power Supplies Power Supply Current I+V+ = 16.5 V, V- = - 16.5 VV IN = 0 or 5 VRoom Full 3.06767µANegative Supply Current I- Room Full - 0.4- 0.5- 4.5- 0.5- 4.5Ground CurrentI GNDRoom Full- 3.0- 6- 7- 6- 7SPECIFICATIONS FOR DUAL SUPPLIESParameter Symbol Test Conditions Unless Specified V+ = 15 V, V- = - 15 V V IN = 2.4 V , 0.8 V a Temp b Typ c - 40 to 125 °C- 40 to 85 °CUnitMin d Max d Min d Max dSPECIFICATIONS FOR DUAL SUPPLIESParameter Symbol Test Conditions Unless Specified V+ = 4.5 V , V- = - 4.5 V V IN = 2.4 V , 0.8 V a Temp b T yp c - 45 to 125 °C- 40 to 85 °CUnitMin d Max d Min d Max dAnalog Switch Analog Signal Range e V ANALOGFull - 4.54.5- 4.54.5V On-Resistance e r ON I S = 50 mA, V D = - 2 V to + 2 VRoom Full 811161115ΩOn-Resistance Match e Δr ONI S = 50 mA, V D = ± 2 VRoom Full0.60.70.90.70.8Dynamic Characteristics T urn-On Time e t ON R L = 300 Ω, C L = 35 pFV S = 2 V Room Full 24526534065310nsT urn-Off Time e t OFF Room Full 145163200163185Break-Before-Make eTime Delay t D V S = 2 VR L = 300 Ω, C L = 35 pF Room Full 15Charge Injection e QV g = 0 V , R g = 0 Ω, C L = 1 nFFull58pCPower Supplies Power Supply Current e I+V IN = 0 or 4.5 VRoom Full 3.06767µANegative Supply Current e I- Room Full - 0.4- 0.5- 4.5- 0.5- 4.5Ground Current eI GNDRoom Full3.0- 6- 7- 6- 7Vishay SiliconixDG469/470Notes: a. V IN = input voltage to perform proper function.b. Room = 25 °C, Full = as determined by the operating temperature suffix.c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.d. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.e. Guaranteed by design, not subject to production test.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS FOR UNIPOLAR SUPPLIESParameter Symbol Test Conditions Unless Specified V+ = 12 V , V- = 0 V V IN = 2.4 V, 0.8 V a Temp b T yp c - 40 to 125 °C- 40 to 85 °CUnitMin d Max d Min d Max dAnalog Switch Analog Signal Range e V ANALOGFull 1212VOn-Resistance r ON I S = 25 mA, V D = 0 V to + 10 V Room Full 7.58.5148.511.3ΩOn-Resistance Match Δr ON I S = 25 mA, V D = + 10 V Room Full 0.40.450.90.450.5On-Resistance Flatness r FLATNESSI S = 25 mA,V D = 0 V , + 5 V , + 10 VRoom Full2.52.62.92.62.8Dynamic Characteristics Turn-On Time t ON R L = 300 Ω, C L = 35 pFV S = 10 V Room Full 190200255200240nsTurn-Off Time t OFF Room Full 100110135110120Break-Before-MakeTime Delay t D V S = 10 VR L = 300 Ω, C L = 35 pF Room 50Charge Injection e QV g = 0 V , R g = 0 Ω, C L = 1 nFRoom2.4pCPower Supplies Power Supply Current I+V IN = 0 or 5 VRoom Full 3.06767µANegative Supply Current I- Room Full - 0.4- 0.5- 4.5- 0.5- 4.5Ground CurrentI GNDRoom Full- 3.0- 6- 7- 6- 7Vishay SiliconixDG469/470TYPICAL CHARACTERISTICSDD Leakage Current vs. TemperatureD DVishay SiliconixDG469/470TYPICAL CHARACTERISTICSCharge Injection vs. Analog VoltageCharge Injection vs. Analog VoltageSwitching Time vs. Temperature andDual Supply VoltageSingle Supply VoltageVishay SiliconixDG469/470TYPICAL CHARACTERISTICSTEST CIRCUITSInsertion Loss, Off-Isolation, Crosstalkvs. FrequencySwitching Threshold vs. Dual Supply VoltageSwitching Threshold vs. Signal Supply VoltageDG469, DG470 Total Harmonic DistortionFigure 1. Switching TimeVishay SiliconixDG469/470New ProductTEST CIRCUITSVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for SiliconTechnology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?71470.Figure 2. Break-Before-MakeFigure 3. Charge InjectionFigure 4. Off-Isolation Figure 5. Source/Drain Capacitances元器件交易网Legal Disclaimer NoticeVishayNoticeSpecifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc., or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.Information contained herein is intended to provide a product description only. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications.Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Vishay for any damages resulting from such improper use or sale.元器件交易网。

NCHC69A3中文资料

NTH / NCH SeriesSaRonixCrystal Clock OscillatorTechnical Data3.3V, LVCMOS / HCMOS, Tri-State141 Jefferson Drive • Menlo Park, CA 94025 • USA • 650-470-7700 • 800-227-8974 • Fax 650-462-9894DS-159 REV DSymmetry:Rise and Fall Times:Logic 0:Logic 1:Load:Period Jitter RMS:0.5 MHz to 106.25 MHzFrequency Stability:Frequency Range:±20, ±25, ±50 or ±100 ppm over all conditions: calibrationtolerance, operating temperature, input voltage change,load change, 30 day aging, shock and vibration.Temperature Range:Operating:Storage:0 to +70°C or -40 to +85°C, See Part Numbering Guide-55 to +125°CSupply Voltage:Recommended Operating: 3.3V ±10%Supply Current:20mA max, 0.5 to 30 MHz25mA max, 30+ to 50 MHz30mA max, 50+ to 80 MHz35mA max, 80+ to 106.25 MHzACTUAL SIZEDescriptionA crystal controlled, low current, lowjitter and high frequency oscillator withprecise rise and fall times demanded innetworking applications. The tri-statefunction on the NTH enables the outputto go high impedance. Device is pack-aged in a 14 or an 8-pin DIP compatibleresistance welded, all metal groundedcase to reduce EMI. True SMD DIL14versions for IR reflow are available, se-lect option "S" in part number builder.See separate data sheet for SMD packagedimensions.Output Drive:45/55% max 0.5 to 70 MHz max40/60% max @ 50% V DD4ns max 0.5 to 50 MHz, 20% to 80% V DD3ns max 50+ to 80 MHz1.5ns max 80+ to 106.25 MHz10% V DD max90% V DD min50 pF, 0.5 to 50 MHz30pF, 50+ to 70 MHz15pF, 70+ to 106.25 MHz8ps maxHCMOSMechanical:Shock:Solderability:Terminal Strength:Vibration:Solvent Resistance:Resistance to Soldering Heat:MIL-STD-883, Method 2002, Condition BMIL-STD-883, Method 2003MIL-STD-883, Method 2004, Conditions A & CMIL-STD-883, Method 2007, Condition AMIL-STD-202, Method 215MIL-STD-202, Method 210, Condition A, B or CEnvironmental:Gross Leak Test:Fine Leak Test:Thermal Shock:Moisture Resistance:MIL-STD-883, Method 1014, Condition CMIL-STD-883, Method 1014, Condition A2MIL-STD-883, Method 1011, Condition AMIL-STD-883, Method 1004Applications & FeaturesADSL, DSLDS3, ES3, E1, STS-1, T1Ethernet Switch, Gigabit EthernetFibre Channel ControllerMPEGNetwork ProcessorsVoice Over Packet32 Bit MicroprocessorsTri-State output on NTHLVCMOS / HCMOS compatibleAvailable up to 106.25 MHz•••••••••••Output WaveformT r T fCMOSLogic 180% V DD50% V DD20% V DDLogic 0SYMMETRYSaRonixSaRonixSaRonixCrystal Clock Oscillator3.3V, LVCMOS / HCMOS,141 Jefferson Drive • Menlo Park, CA 94025 • USA • 650-470-7700 • 800-227-8974 • Fax 650-462-9894SaRonixTrue SMD Adaptor - 7.57mm HighSaRonix 141 Jefferson Drive • Menlo Park, CA 94025 • USA • 650-470-7700 • 800-227-8974 • Fax 650-462-9894。

PCM69中文资料

TTL/CMOS Compatible IIH = ±5µA IIL = ±5µA +2 0 Serial, MSB First, BTC(1) 16.9344 +VD 0.8 V V MHz

fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz fS = 352.8kHz (f = 1kHz)

®

PCM67/69A

2

元器件交易网

PIN ASSIGNMENTS

PCM67P PCM67U DESCRIPTION +5V Analog Supply Voltage Left Voltage Common No Connection Left Current Output (0 to 1.2mA) Servo Decoupling Capacitor Reference Decoupling Capacitor Right Current Output (0 to 1.2mA) No Connection Right Voltage Common Analog Common Digital Common Mode Control 2 Right Data Input Bit Clock System Clock Word Clock Left Data Input Mode Control 3 Mode Control 1 +5V Digital Supply Voltage MNEMONIC +VA LVCOM NC LIOUT SRVCAP REFCAP RIOUT NC RVCOM ACOM DCOM MC2 RDATA BTCK SYSCK WDCK LDATA MC3 MC1 +VD PCM69AP PCM69AU 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

BCP69-25中文资料

,,,, ,,,,

0.30 4 3.90 4.80 7.65

7.00 3.85 3.60 3.50

solder lands solder resist occupied area solder paste

7.40

,, ,, ,, ,,,,,,

1 2 3 1.20 (3x) 1.30 (3x) 5.90 6.15 Dimensions in mm.

MSA443

Fig.2 Standard PCB footprint for mounting SOT223 (reflow soldering).

2003 Nov 25

5

元器件交易网

Philips Semiconductors

Product specification

PNP medium power transistor; 20 V, 1 A

2003 Nov 25

3

元器件交易网

Philips Semiconductors

Product specification

PNP medium power transistor; 20 V, 1 A

BCP69

handbook, halfpage

1.6

MLE311

Ptot (W) 1.2

元器件交易网

DISCRETE SEMICONDUCTORS

DATA SHEET

dbook, halfpage

M3D087

BCP69 PNP medium power transistor; 20 V, 1 A

Product specification Supersedes data of 2002 Nov 15 2003 Nov 25

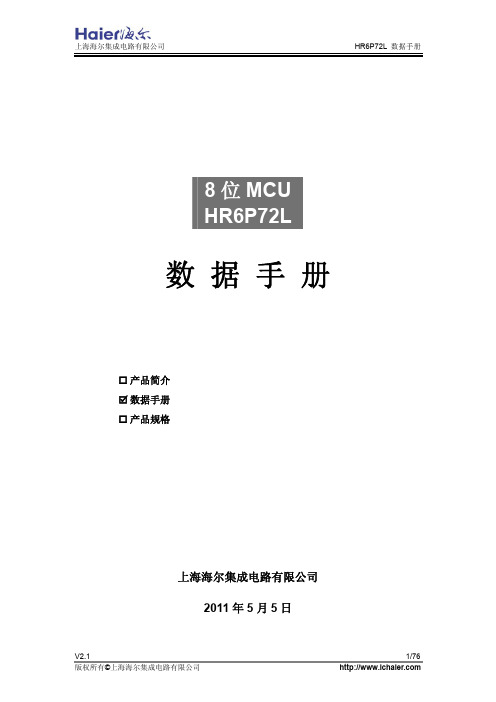

数据手册_HR6P72L_Datasheet_C V2.1

海尔 MCU 芯片使用注意事项

关于芯片的上/下电 海尔 MCU 芯片具有独立电源管脚。当 MCU 芯片应用在多电源供电系统时,应先对 MCU 芯片上电,再 对系统其它部件上电;反之,下电时,先对系统其它部件下电,再对 MCU 芯片下电。若操作顺序相反则

可能导致芯片内部元件过压或过流,从而导致芯片故障或元件退化。具体可参照芯片的数据手册说明。

关于芯片的 ESD 防护措施

海尔 MCU 芯片具有满足工业级 ESD 标准保护电路。建议用户根据芯片存储/应用的环境采取适当静电防护 措施。应注意应用环境的湿度;建议避免使用容易产生静电的绝缘体;存放和运输应在抗静电容器、抗静 电屏蔽袋或导电材料容器中;包括工作台在内的所有测试和测量工具必须保证接地;操作者应该佩戴静电 消除手腕环手套,不能用手直接接触芯片等。

关于芯片的初始化

海尔 MCU 芯片具有各种内部和外部复位。对于不同的应用系统,有必要对芯片寄存器、内存、功能模块 等进行初始化,尤其是 I/O 管脚复用功能进行初始化,避免由于芯片上电以后,I/O 管脚状态的不确定情况 发生。

关于芯片的管脚

海尔 MCU 芯片具有宽范围的输入管脚电平,建议用户输入高电平应在 VIHMIN 之上,低电平应在 VILMAX 之 下。避免输入电压介于 VIHMIN 和 VILMAX 之间,以免波动噪声进入芯片。对于未使用的输入管脚,应通过电 阻上拉至电源电平或下拉至地。对于未使用的管脚,建议用户设为输出状态,并通过电阻接至电源或地。 对未使用的管脚处理因应用系统而异,具体遵循应用系统的相关规定和说明。

上海海尔集成电路有限公司

HR6P72L 数据手册

目录

内容目录

第 1 章 芯片简介 .................................................................................................... 10

69TK11中文资料

Snap-Action Temperature ControlsThe 69T line of 3/4” (19mm) bimetal disc temperature controls from Therm-O-Disc offers multiple temperature operation in a unique, cost-effective design. Our “TK” model offers an increased temperature depression for even greater design flexibility. The snap-action bimetal disc provides high-speed contact separation resulting in exceptional life characteristics at electrical loads up to 25 amps at 240VAC. By utilizing heaters mounted internally, the open or close calibration of the bimetal disc can be biased lower. The more power applied to the internal heaters the more supplemental heat is generated to bias the operating temperature of the control. The 69T is a cost-effective alternative in applications where multiple temperature control is required.Features and BenefitsThe 69T features include:•Internal heater construction for consistent temperature depression.•Available in automatic reset SPST and SPDT switch configurations.•Snap-action bimetal disc for high-speed contact separation.• A wide variety of terminal and mounting options for design flexibility.•Welded construction for integrity of current-carrying components.•Exposed or enclosed bimetal disc for either increased thermal response or protection from airborne contaminants.Switch Actions and Typical ApplicationsThe 69T is available in two automatic reset switch actions:Automatic Reset SPST – In this design, the switch can be built to either open or close its electrical contacts on temperature rise. Once the temperature of the bimetal disc has returned to the specified reset temperature, the contacts automatically return to their original state. The SPST switch action is typically used to regulate clothes dryer drum temperatures (see figures 1 and 2).Automatic Reset SPDT – This design is the same as the SPST described above with the addition of an auxiliary set of contacts that open and close in opposition to the main contacts.Refer to the “General Electrical Ratings” chart for rating limitations on the auxiliary contacts. Typical uses of this construction include fan speed changeover at a specified temperature and lighting of an indicator lamp when an abnormal temperature condition has been reached (see figure 3).CAUTION. . . When designing a circuit for a single pole double throw control, an electrical load must be applied to terminal number 2 and/or 3 to avoid a possible short-circuit condition.69T, 69TK SeriesInternal Heater Biased Temperature ControlsSPST Automatic Reset Airstream MountingFigure 1SPST Automatic Reset Surface MountingFigure 2SPDT Automatic Reset Airstream MountingFigure 3Dimensions are shown in inches and (millimeters).1.688(42.88)2.00(50.8)1.11(28.2)0.81(20.8)0.89(22.6)1.40(35.6)0.39(9.9)Ø0.93(23.6)0.170(4.32)1.563(39.70)0.170(4.32)1.563(39.70) 1.750(44.50)1.63(41.4)0.89(22.6)1.36(34.5)0.02(.5)Ø0.93(23.6)0.170(4.32)2.00(50.8)1.688 (42.88)1.563(39.70)1.63(41.4)1.36(34.5)0.39(9.9)0.89(22.6)Mounting ConfigurationsAirstream Mounting – This mounting configuration positions the bimetal disc .39” (9.9mm)through a hole in the mounting surface to sense temperature within an enclosure such as a heater box or air duct. Airstream configurations may be specified with a flange (see figures 1 and 3)or without a flange (see figure 4)to suit specific application needs.Surface Mounting – This optional mounting configuration positions the bimetal disc firmly against the mounting surface to sense the actual mounting surface temperature (see figure 2).SPST Automatic Reset Airstream MountingFigure 4Dimensions are shown in inches and (millimeters).Thermal ResponseAn exposed or enclosed bimetal disc may be specified with any of the airstream or surface mounting configurations. The enclosed disc construction provides greater protection than the exposed disc construction, keeping airborne contaminants, such as dirt and dust, from entering the control. It also protects the bimetal disc from possible physical damage during assembly and in the final application. In applications where faster response to radiant heat is required, an exposed bimetaldisc or an optional black oxide mounting finish may be specified.1.06(26.9)1.63(41.4)1.36(34.5)0.39(9.9)Ø0.93(23.6)Terminal ConfigurationsStandard terminations for the 69T are .250” x .032” (6.3 x .8mm) tin-plated brass blade terminals formed at 90 angular degrees to the thermostat mounting surface. Terminal angles of 0 and 30 degrees can also be provided.Terminal orientation – For added flexibility, the orientation of the terminals with respect to the mounting bracket can be specified in 45 angular degree increments (see figure 5).Terminals 90°to mounting Terminals 45°counterclockwise Terminals 45°clockwise to holes (standard)to mounting holes mounting holesFigure 5Temperature DepressionThe amount of change in the open or close calibration that results from energizing the internal heaters is referred to as temperature depression. The amount of depression which can be realized in an actual application is dependent upon several characteristics. Heater wattage and voltage, ambient, airflow, thermal off-set and rate of temperature change are all variables which affect temperature depression. As a point of reference, the depression chart reflects the approximate temperature shift after energizing the internal heaters in a circulating air chamber. Due to the material rating of the thermostat body, limitations to the heater wattage and thermostat calibration are necessary. Refer to the temperature depression chart for maximum heater and calibration combinations.Temperature DepressionInternal Heater Maximum Temperature Depression* Voltage Wattage Calibration Open Close120VAC 2.00180°F (82.2°C)13°F (7.2°C)15°F (8.3°C)120VAC 1.40233°F (111.7°C)9°F (5.0°C)11°F (6.1°C)120VAC** 3.90155°F (68.3°C)27°F (15°C)32°F (17.8°C)24VAC 2.00171°F (77.2°C)10°F (5.6°C)11°F (6.1°)NOTE:*Depression data obtained in a controlled test environment; application performance may vary.**TK style configurations.Calibration Temperatures, Differentials and TolerancesTo use the calibration chart, locate the range in the left hand column, in which the highest calibration set point (open or close) falls. Then locate, across the top, the range in which the nominal dif-ferential falls. The standard open and close set point tolerances are shown where the two columns converge. The chart also indicates what differentials are available in each of the calibration set point ranges. Tighter open and close tolerances are available at added cost. Thermocouple samples can be provided to assist in determining the appropriate calibration temperature for specific application.For more information on tightened tolerances or availability of differentials not listed in the chart,please consult one of our sales engineers.Calibration Temperatures, Differentials and Standard Tolerance of the 69T, 69TK SeriesProduct Numbering SystemNominal Differentials(temperature difference between nominal open and close set point)10-14°F*15-19°F 20-29°F 30-39°F 40-59°F 60-80°F 5.5-8°C 8.5-10.5°C 11-16°C 16.5-21.5°C 22-33°C 33.5-44.5°C Open Close Open Close Open Close Open Close Open Close Open Close 0°-79°F ±5±6±5±6±5±6±5±7±5±7––-18°-26°C ±3±3.5±3±3.5±3±3.5±3±4±3±4––80°-233°F ±5±5±5±5±5±5±5±7±5±7––28°-111.7°C±3±3±3±3±3±3±3±4±3±4––Highest Calibration Set Point Range (Open or (Close)General Electrical RatingsThe 69T, 69TK series of controls has been rated by major agencies throughout the world. The agency ratings can be used as a guide when evaluating specific applications. However, the mechanical, electrical, thermal and environmental conditions to which a control may be exposed in an application may differ significantly from agency test conditions. Therefore, the user must not rely solely on agency ratings, but must perform adequate testing of the product to confirm that the control selected will operate as intended in the user’s application.Thermostat Contact Inductive Pilot duty Resistive Volts AC Agency Type Arrangement Amperes VA Amperes RecognitionFLA LRA69T Contacts 1 & 3106048025120UL69TX*SPST or SPDT53048025240E19279——12512.5277-4801472——1201060——240530——480Contacts 1 & 2——125—120-277SPDT 5.834.8——1202.917.4——2402.515.0——48069T Contacts 1 & 3106012525120CSA69T*SPST or SPDT53012525240LR1028121240010600——125—240-480Contacts 1 & 2——125—120-277SPDTThese are consolidated ratings some of which are limited to 6,000 cycles. For complete and current ratings, please contact our Sales Engineering Department. At thermostat end-of-life, the contacts may remain permanently closed or open.* The 69TX has electrical clearances of 1/4” through air and 3/8” over surface which may be required for some heating and air conditioning applications. Overall physical dimensions are the same as the 69T.Important NoticeUsers must determine the suitability of the control for their application, including the level of reliability required, and are solely responsible for the function of the end-use product.These controls contain exposed electrical components and are not intended to withstand exposure to water or other environmental contaminants which can compromise insulating components. Such exposure may result in insulation breakdown and accompanying localized electrical heating.A control may remain permanently closed or open as a result of exposure to excessive mechanical, electrical, thermal or environmental conditions or at normal end-of-life. If failure of the control to operate could result in personal injury or property damage, the user should incorporate supplemental system control features to achieve the desired level of reliability and safety. For example, backup controls have been incorporated in a number of applications for this reason.。

BCP69贴片三极管 SOT-223三极管封装BCP69参数

VCE=-10V, IC=-5mA VCE=-1V, IC=-1A

Transition frequency

fT

VCE=-5V,IC=-10mA, f=100MHz 40

Collector output capacitance

Cob

VCB=-5V, IE=0, f=1MHz

Typ Max Unit V V V

2 包装规格(Packing spec):

封装 载带/盖带

卷盘

包装箱

PKG

tape

Reel

Box

只/盘 盘/盒

只/盒

pcs/reel reel/box pcs/box

7”盘 SOT-23 包

SOT-223 IC-ZD-04 (IC-JP-04) 装箱 *1 1000

10

10000

盒/箱

只/箱

box/carton pcs/carton

Reel

包装箱 Box

13” SOT223 IC-ZD-04 (IC-JP-01) IC14#

只/盘 盘/盒

只/盒

pcs/reel reel/box pcs/box

2500

2

5000

盒/箱

只/箱

box/carton pcs/carton

8

40000

Hale Waihona Puke 2. 7 寸 包装流程图(Packing procedure):

0.278

0.091(BSC)

0.177

0.185

0.035

0.045

0°

10°

SOT223 包装(SOT223 PACKING)

编带包装(Tape&Reel Packing):

半导体器件芯片常用型号参数12页word文档

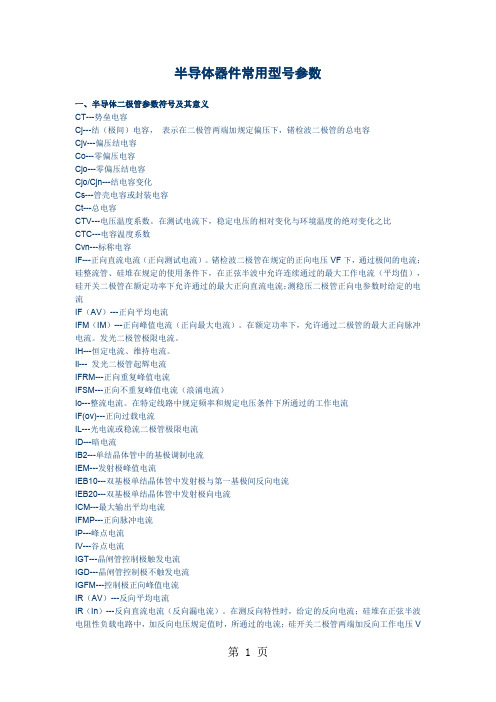

半导体器件常用型号参数一、半导体二极管参数符号及其意义CT---势垒电容Cj---结(极间)电容,表示在二极管两端加规定偏压下,锗检波二极管的总电容Cjv---偏压结电容Co---零偏压电容Cjo---零偏压结电容Cjo/Cjn---结电容变化Cs---管壳电容或封装电容Ct---总电容CTV---电压温度系数。

在测试电流下,稳定电压的相对变化与环境温度的绝对变化之比CTC---电容温度系数Cvn---标称电容IF---正向直流电流(正向测试电流)。

锗检波二极管在规定的正向电压VF下,通过极间的电流;硅整流管、硅堆在规定的使用条件下,在正弦半波中允许连续通过的最大工作电流(平均值),硅开关二极管在额定功率下允许通过的最大正向直流电流;测稳压二极管正向电参数时给定的电流IF(AV)---正向平均电流IFM(IM)---正向峰值电流(正向最大电流)。

在额定功率下,允许通过二极管的最大正向脉冲电流。

发光二极管极限电流。

IH---恒定电流、维持电流。

Ii--- 发光二极管起辉电流IFRM---正向重复峰值电流IFSM---正向不重复峰值电流(浪涌电流)Io---整流电流。

在特定线路中规定频率和规定电压条件下所通过的工作电流IF(ov)---正向过载电流IL---光电流或稳流二极管极限电流ID---暗电流IB2---单结晶体管中的基极调制电流IEM---发射极峰值电流IEB10---双基极单结晶体管中发射极与第一基极间反向电流IEB20---双基极单结晶体管中发射极向电流ICM---最大输出平均电流IFMP---正向脉冲电流IP---峰点电流IV---谷点电流IGT---晶闸管控制极触发电流IGD---晶闸管控制极不触发电流IGFM---控制极正向峰值电流IR(AV)---反向平均电流IR(In)---反向直流电流(反向漏电流)。

在测反向特性时,给定的反向电流;硅堆在正弦半波电阻性负载电路中,加反向电压规定值时,所通过的电流;硅开关二极管两端加反向工作电压VR时所通过的电流;稳压二极管在反向电压下,产生的漏电流;整流管在正弦半波最高反向工作电压下的漏电流。

ITR9606中文资料

160

140

2

120

100 80

60

40

20

0 0 10 20 30 40 50 60 70

Fig.5 Collector Dark Current vs.

Ambient Temperature

10

10 10

10

10

0

25

50 75 100

Fig.4 Collector Current vs. Irradiance

1.3

1.2 IF=20mA

1.1

Ie-Radiant Intensity (mW/sr)

0 25 50 75 100 120

1 25 50 75 100 120

Everlight Electronics Co., Ltd. Device No:CDRX-096-004

http:\\ Prepared date:08-08-2005

http:\\ Prepared date:08-08-2005

Rev 3

Page: 3 of 6

Prepared by:Denky

元器件交易网

█ Typical Electrical/Optical/Characteristics Curves for IR

--- --- 10 μA

VR=5V

--- 940 --- nm

IF=20mA

--- 60 --- Deg

IF=20mA

--- --- 100 nA VCE=20V,Ee=0mW/cm2

VCE(sat) --- --- 0.4 V

IC=2mA ,Ee=1mW/cm2

Collect Current Transfer

ADF4360-1BCPZ资料

Integrated Synthesizer and VCOADF4360-1 Rev.BInformation furnished by Analog Devices is believed to be accurate and reliable.However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: Fax: 781.326.8703© 2004 Analog Devices, Inc. All rights reserved.FEATURESOutput frequency range: 2050 MHz to 2450 MHzDivide-by-2 output3.0 V to 3.6 V power supply1.8 V logic compatibilityInteger-N synthesizerProgrammable dual-modulus prescaler 8/9, 16/17, 32/33 Programmable output power level3-wire serial interfaceAnalog and digital lock detectHardware and software power-down mode APPLICATIONSWireless handsets (DECT, GSM, PCS, DCS, WCDMA)Test equipmentWireless LANsCATV equipment GENERAL DESCRIPTIONThe ADF4360-1 is a fully integrated integer-N synthesizer and voltage-controlled oscillator (VCO). The ADF4360-1 is designed for a center frequency of 2250 MHz. In addition, there is a divide-by-2 option available, whereby the user gets an RF output of between 1025 MHz and 1225 MHz.Control of all the on-chip registers is through a simple 3-wire interface. The device operates with a power supply ranging from 3.0 V to 3.6 V and can be powered down when not in use.FUNCTIONAL BLOCK DIAGRAMCPVCO REFTUNEC CC NOUT AOUT BFigure 1.ADF4360-1Rev. B | Page 2 of 24TABLE OF CONTENTSSpecifications.....................................................................................3 Timing Characteristics.....................................................................5 Absolute Maximum Ratings............................................................6 Transistor Count...........................................................................6 ESD Caution..................................................................................6 Pin Configuration and Function Descriptions.............................7 Typical Performance Characteristics.............................................8 Circuit Description...........................................................................9 Reference Input Section...............................................................9 Prescaler (P/P + 1)........................................................................9 A and B Counters.........................................................................9 R Counter......................................................................................9 PFD and Charge Pump................................................................9 MUXOUT and Lock Detect......................................................10 Input Shift Register.....................................................................10 VCO.............................................................................................10 Output Stage................................................................................11 Latch Structure...........................................................................12 Power-Up.....................................................................................16 Control Latch..............................................................................18 N Counter Latch.........................................................................19 R Counter Latch.........................................................................19 Applications.....................................................................................20 Direct Conversion Modulator..................................................20 Fixed Frequency LO...................................................................21 Interfacing...................................................................................21 PCB Design Guidelines for Chip-Scale Package..........................22 Output Matching........................................................................22 Outline Dimensions.......................................................................23 Ordering Guide.. (23)REVISION HISTORY12/04—Rev. A to Rev. BUpdated Format..................................................................Universal Changes to Specifications................................................................3 Changes to the Timing Characteristics.........................................5 Changes to the Power-Up Section................................................16 Added Table 10...............................................................................16 Added Figure 16..............................................................................16 Changes to Ordering Guide..........................................................23 Updated Outline Dimensions. (23)6/04—Data Sheet Changed from Rev. 0 to Rev. AChanges to Specifications................................................................3 Changes to Table 6..........................................................................12 Changes to Table 7..........................................................................13 Changes to Table 9.. (15)8/03—Revision 0: Initial VersionADF4360-1Rev. B | Page 3 of 24SPECIFICATIONS 1AV DD = DV DD = V VCO = 3.3 V ± 10%; AGND = DGND = 0 V; T A = T MIN to T MAX , unless otherwise noted. Table 1.Parameter B Version Unit Conditions/Comments REF IN CHARACTERISTICS REF IN Input Frequency 10/250 MHz min/max For f < 10 MHz, use a dc-coupled CMOS compatiblesquare wave, slew rate > 21 V/µs.REF IN Input Sensitivity 0.7/AV DD p-p min/max AC-coupled. 0 to AV DD V max CMOS compatible. REF IN Input Capacitance 5.0 pF max REF IN Input Current ±100 µA max PHASE DETECTORPhase Detector Frequency 28 MHz max CHARGE PUMPI CP Sink/Source 3With R SET = 4.7 kΩ. High Value 2.5 mA typ Low Value 0.312 mA typ R SET Range 2.7/10 kΩ I CP 3-State Leakage Current 0.2 nA typ Sink and Source Current Matching 2 % typ 1.25 V ≤ V CP ≤ 2.5 V. I CP vs. V CP 1.5 % typ 1.25 V ≤ V CP ≤ 2.5 V. I CP vs. Temperature 2 % typ V CP = 2.0 V. LOGIC INPUTS V INH , Input High Voltage 1.5 V min V INL , Input Low Voltage 0.6 V max I INH /I INL , Input Current ±1 µA max C IN , Input Capacitance 3.0 pF max LOGIC OUTPUTS V OH , Output High Voltage DV DD – 0.4 V min CMOS output chosen. I OH , Output High Current 500 µA max V OL , Output Low Voltage 0.4 V max I OL = 500 µA. POWER SUPPLIES AV DD 3.0/3.6 V min/V max DV DD AV DD V VCO AV DD AI DD 410 mA typDI DD 4 2.5 mA typ I VCO 4, 524.0 mA typ I CORE = 15 mA.I RFOUT 43.5 – 11.0 mA typ RF output stage is programmable.Low Power Sleep Mode 47 µA typ RF OUTPUT CHARACTERISTICS 5 VCO Output Frequency 2050/2450 MHz min/max I CORE = 15 mA. VCO Sensitivity 57 MHz/V typ Lock Time 6400 µs typ To within 10 Hz of final frequency. Frequency Pushing (Open Loop) 6 MHz/V typ Frequency Pulling (Open Loop) 15 kHz typ Into 2.00 VSWR load. Harmonic Content (Second) −20 dBc typ Harmonic Content (Third) −35 dBc typOutput Power 5, 7−13/−6 dBm typ Programmable in 3 dB steps. See Table 7. Output Power Variation ±3 dB typ For tuned loads, see the Output Matching section. VCO Tuning Range 1.25/2.5 V min/maxADF4360-1Rev. B | Page 4 of 24Parameter B Version Unit Conditions/CommentsNOISE CHARACTERISTICS 1, 5VCO Phase-Noise Performance 8 −110 dBc/Hz typ @ 100 kHz offset from carrier. −130 dBc/Hz typ @ 1 MHz offset from carrier. −141 dBc/Hz typ @ 3 MHz offset from carrier. −148 dBc/Hz typ @ 10 MHz offset from carrier.Synthesizer Phase-Noise Floor 9−172 dBc/Hz typ @ 25 kHz PFD frequency. −163 dBc/Hz typ @ 200 kHz PFD frequency. −147 dBc/Hz typ @ 8 MHz PFD frequency. In-Band Phase Noise 10, 11−81 dBc/Hz typ @ 1 kHz offset from carrier.RMS Integrated Phase Error 120.72 Degrees typ 100 Hz to 100 kHz.Spurious Signals due to PFD Frequency 11, 13−70 dBc typ Level of Unlocked Signal with MTLD Enabled −38 dBm typ1 Operating temperature range is –40°C to +85°C.2Guaranteed by design. Sample tested to ensure compliance. 3I CP is internally modified to maintain constant-loop gain over the frequency range. 4T A = 25°C; AV DD = DV DD = V VCO = 3.3 V; P = 32. 5These characteristics are guaranteed for VCO Core Power = 15 mA. 6Jumping from 2.05 GHz to 2.45 GHz. PFD frequency = 200 kHz; loop bandwidth = 10 kHz. 7Using 50 Ω resistors to V VCO into a 50 Ω load. For tuned loads, see the section. Output Matching 8The noise of the VCO is measured in open-loop conditions. 9The synthesizer phase-noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20 log N (where N is the N divider value). 10The phase noise is measured with the EVAL-ADF4360-xEB1 Evaluation Board and the HP8562E Spectrum Analyzer. The spectrum analyzer provides the REF IN for the synthesizer; offset frequency = 1 kHz. 11f REFIN = 10 MHz; f PFD = 200 kHz; N = 12500; Loop B/W = 10 kHz. 12f REFIN = 10 MHz; f PFD = 1 MHz; N = 2400; Loop B/W = 25 kHz. 13The spurious signals are measured with the EVAL-ADF4360-xEB1 Evaluation Board and the HP8562E Spectrum Analyzer. The spectrum analyzer provides the REF IN for the synthesizer; f REFOUT = 10 MHz @ 0 dBm.ADF4360-1Rev. B | Page 5 of 24TIMING CHARACTERISTICS 1AV DD = DV DD = V VCO = 3.3 V ± 10%; AGND = DGND = 0 V; 1.8 V and 3 V logic levels used; T A = T MIN to T MAX , unless otherwise noted. Table 2.Parameter Limit at T MIN to T MAX (B Version) Unit Test Conditions/Comments t 1 20 ns min LE Setup Timet 2 10 ns min DATA to CLOCK Setup Time t 3 10 ns min DATA to CLOCK Hold Time t 4 25 ns min CLOCK High Duration t 5 25 ns min CLOCK Low Duration t 6 10 ns min CLOCK to LE Setup Time t 720ns minLE Pulse Width1See the section for the recommended power-up procedure for this device.Power-UpCLOCKDATALELEFigure 2. Timing DiagramADF4360-1Rev. B | Page 6 of 24ABSOLUTE MAXIMUM RATINGST A = 25°C, unless otherwise noted. Table 3.Parameter Rating AV DD to GND 1−0.3 V to +3.9 V AV DD to DV DD −0.3 V to +0.3 V V VCO to GND −0.3 V to +3.9 V V VCO to AV DD −0.3 V to +0.3 V Digital I/O Voltage to GND −0.3 V to V DD + 0.3 V Analog I/O Voltage to GND −0.3 V to V DD + 0.3 VREF IN to GND −0.3 V to V DD + 0.3 VOperating Temperature RangeMaximum Junction Temperature 150°CCSP θJA Thermal Impedance(Paddle Soldered) 50°C/W (Paddle Not Soldered) 88°C/W Lead Temperature, SolderingVapor Phase (60 sec) 215°C Infrared (15 sec) 220°C1GND = AGND = DGND = 0 V.Stresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stress rat-ing only; functional operation of the device at these or any other conditions above those indicated in the operational sec-tions of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affect device reliability. This device is a high performance RF integrated circuit with an ESD rating of <1 kV and it is ESD sensitive. Proper precautions should be taken for handling and assembly.TRANSISTOR COUNT 12543 (CMOS) and 700 (Bipolar)ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulateon the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy elec-trostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.ADF4360-1Rev. B | Page 7 of 24PIN CONFIGURATION AND FUNCTION DESCRIPTIONSCPGND AV DD AGND RF OUT A RF OUT B V VCO DATA CLK REF IN DGND C N R SETV T U N E A G N D A G N D A G N D A G N D C C C PC EA G N DD V D DM U X O U TL E04414-003Figure 3. Pin ConfigurationADF4360-1Rev. B | Page 8 of 24TYPICAL PERFORMANCE CHARACTERISTICSFREQUENCY OFFSET (Hz)O U T P U T P O W E R (d B )Figure 4. Open Loop VCO Phase Noise04414-005–145–150–155–140–135–130–125–120–115–110–105–90–95–100–85–80–75–7010010M1M 100k10k 1000FREQUENCY OFFSET (Hz)O U T P U T P O W E R (d B )Figure 5. VCO Phase Noise, 2250 MHz, 200 kHz PFD, 10 kHz Loop Bandwidth04414-006–145–150–155–140–135–130–125–120–115–110–105–90–95–100–85–80–75–7010010M1M 100k10k 1000FREQUENCY OFFSET (Hz)O U T P U T P O W E R (d B )Figure 6. VCO Phase Noise, 1125 MHz,Divide-by-2 Enabled, 200 kHz PFD, 10 kHz Loop BandwidthO U T P U T P O W E R (d B )–2kHz –1kHz 2250MHz 1kHz 2kHzFigure 7. Close-In Phase Noise at 2250 MHz (200 kHz Channel Spacing)O U T P U T P O W E R (d B )–200kHz–100kHz2250MHz100kHz200kHzFigure 8. Reference Spurs at 2250 MHz(200 kHz Channel Spacing, 10 kHz Loop Bandwidth)O U T P U T P O W E R (d B )–90–80–70–60–50–40–30–20–100–1MHz–0.5MHz2250MHz0.5MHz1MHzFigure 9. Reference Spurs at 2250 MHz(1 MHz Channel Spacing, 25 kHz Loop Bandwidth)ADF4360-1Rev. B | Page 9 of 24CIRCUIT DESCRIPTIONREFERENCE INPUT SECTIONThe reference input stage is shown in Figure 10. SW1 and SW2 are normally closed switches. SW3 is normally open. When power-down is initiated, SW3 is closed, and SW1 and SW2 are opened. This ensures that there is no loading of the REF IN pin on power-down.04414-010POWER-DOWNFigure 10. Reference Input StagePRESCALER (P/P + 1)The dual-modulus prescaler (P/P + 1), along with the A and B counters, enables the large division ratio, N , to be realized (N = BP + A). The dual-modulus prescaler, operating at CML levels, takes the clock from the VCO and divides it down to a manage-able frequency for the CMOS A and B counters. The prescaler is programmable. It can be set in software to 8/9, 16/17, or 32/33 and is based on a synchronous 4/5 core. There is a minimum divide ratio possible for fully contiguous output frequencies; this minimum is determined by P , the prescaler value, and is given by (P 2−P).A ANDB COUNTERSThe A and B CMOS counters combine with the dual-modulus prescaler to allow a wide range division ratio in the PLL feed-back counter. The counters are specified to work when the prescaler output is 300 MHz or less. Thus, with a VCOfrequency of 2.5 GHz, a prescaler value of 16/17 is valid, but a value of 8/9 is not valid.Pulse Swallow FunctionThe A and B counters, in conjunction with the dual-modulus prescaler, make it possible to generate output frequencies that are spaced only by the reference frequency divided by R. The VCO frequency equation is()R f A B P f REFIN VCO /×]+×[=where:f VCO is the output frequency of the VCO.P is the preset modulus of the dual-modulus prescaler (8/9, 16/17, and so on).B is the preset divide ratio of the binary 13-bit counter (3 to 8191). A is the preset divide ratio of the binary 5-bit swallow counter (0 to 31). f REFIN is the external reference frequency oscillator.Figure 11. A and B CountersR COUNTERThe 14-bit R counter allows the input reference frequency to be divided down to produce the reference clock to the phase frequency detector (PFD). Division ratios from 1 to 16,383 are allowed.PFD AND CHARGE PUMPThe PFD takes inputs from the R counter and N counter(N = BP + A) and produces an output proportional to the phase and frequency difference between them. Figure 12 is a simpli-fied schematic. The PFD includes a programmable delay ele-ment that controls the width of the antibacklash pulse. This pulse ensures that there is no dead zone in the PFD transfer function and minimizes phase noise and reference spurs. Two bits in the R counter latch, ABP2 and ABP1, control the width of the pulse (see Table 9).04414-012Figure 12. PFD Simplified Schematic and Timing (In Lock)ADF4360-1Rev. B | Page 10 of 24MUXOUT AND LOCK DETECTThe output multiplexer on the ADF4360 family allows the user to access various internal points on the chip. The state of MUXOUT is controlled by M3, M2, and M1 in the function latch. The full truth table is shown in Table 7. Figure 13 shows the MUXOUT section in block diagram form.Lock DetectMUXOUT can be programmed for two types of lock detect: digital and analog. Digital lock detect is active high. When LDP in the R counter latch is set to 0, digital lock detect is set high when the phase error on three consecutive phase detector cycles is less than 15 ns.With LDP set to 1, five consecutive cycles of less than 15 ns phase error are required to set the lock detect. It stays set high until a phase error greater than 25 ns is detected on any subse-quent PD cycle.The N-channel open-drain analog lock detect should be oper-ated with an external pull-up resistor of 10 kΩ nominal. When lock has been detected, the output will be high with narrow low-going pulses.DGNDMUXOUTDV ANALOG LOCK DETECT SDOUT04414-013Figure 13. MUXOUT CircuitINPUT SHIFT REGISTERThe ADF4360 family’s digital section includes a 24-bit input shift register, a 14-bit R counter, and an 18-bit N counter, com-prising of a 5-bit A counter and a 13-bit B counter. Data isclocked into the 24-bit shift register on each rising edge of CLK. The data is clocked in MSB first. Data is transferred from the shift register to one of four latches on the rising edge of LE. The destination latch is determined by the state of the two control bits (C2, C1) in the shift register. The two LSBs are DB1 and DB0, as shown in Figure 2.The truth table for these bits is shown in Table 5. Table 6 shows a summary of how the latches are programmed. Note that the test mode latch is used for factory testing and should not be programmed by the user.Table 5. C2 and C1 Truth TableControl BitsC2 C1 Data Latch 0 0 Control Latch 0 1 R Counter1 0 N Counter (A and B) 11Test Mode LatchVCOThe VCO core in the ADF4360 family uses eight overlapping bands, as shown in Figure 14, to allow a wide frequency range to be covered without a large VCO sensitivity (K V ) and resultant poor phase noise and spurious performance.The correct band is chosen automatically by the band select logic at power-up or whenever the N counter latch is updated. It is important that the correct write sequence be followed at power-up. This sequence is 1. R counter latch 2. Control latch 3. N counter latchDuring band select, which takes five PFD cycles, the VCO V TUNE is disconnected from the output of the loop filter and connected to an internal reference voltage.04414-0140.40.20.60.81.01.21.41.61.82.42.22.02.62.83.01850190019502000205021002150220022502300235024002450250025502600FREQUENCY (MHz)V O L T A G E (V )Figure 14. Frequency vs. V TUNE , ADF4360-1The R counter output is used as the clock for the band select logic and should not exceed 1 MHz. A programmable divider is provided at the R counter input to allow division by 1, 2, 4, or 8 and is controlled by Bits BSC1 and BSC2 in the R counter latch. Where the required PFD frequency exceeds 1 MHz, the divide ratio should be set to allow enough time for correct band selection.After band select, normal PLL action resumes. The nominal value of K V is 57 MHz/V or 28 MHZ/V if divide-by-2 operation has been selected (by programming DIV2 [DB22], high in the N counter latch). The ADF4360 family contains linearization circuitry to minimize any variation of the product of I CP and K V.The operating current in the VCO core is programmable in four steps: 5 mA, 10 mA, 15 mA, and 20 mA. This is controlled by Bits PC1 and PC2 in the control latch.OUTPUT STAGEThe RF OUT A and RF OUT B pins of the ADF4360 family are con-nected to the collectors of an NPN differential pair driven by buffered outputs of the VCO, as shown in Figure 15. To allow the user to optimize the power dissipation versus the output power requirements, the tail current of the differential pair is programmable via Bits PL1 and PL2 in the control latch. Four current levels may be set: 3.5 mA, 5 mA, 7.5 mA, and 11 mA. These levels give output power levels of −13 dBm, −10.5 dBm, −8 dBm, and −6 dBm, respectively, using a 50 Ω resistor to V DD and ac coupling into a 50 Ω load. Alternatively, both outputs can be combined in a 1 + 1:1 transformer or a 180° microstrip coupler (see the Output Matching section). If the outputs are used individually, the optimum output stage consists of a shunt inductor to V DD.Another feature of the ADF4360 family is that the supply current to the RF output stage is shut down until the part achieves lock as measured by the digital lock detect circuitry. This is enabled by the mute-till-lock detect (MTLD) bit in the control latch.RF A RF BFigure 15. Output Stage ADF4360-1LATCH STRUCTURETable 6 shows the three on-chip latches for the ADF4360 family. The two LSBs determine which latch is programmed. Table 6. Latch StructureCONTROL LATCHN COUNTER LATCHR COUNTER LATCHTable 7. Control LatchTable 9. R Counter LatchPOWER-UPPower-Up SequenceThe correct programming sequence for the ADF4360-1 after power-up is: 1. R counter latch 2. Control latch 3. N counter latchInitial Power-UpInitial power-up refers to programming the part after theapplication of voltage to the AV DD , DV DD , V VCO , and CE pins. On initial power-up, an interval is required between programming the control latch and programming the N counter latch. This interval is necessary to allow the transient behavior of the ADF4360-1 during initial power-up to have settled.During initial power-up, a write to the control latch powers up the part and the bias currents of the VCO begin to settle. If these currents have not settled to within 10% of their steady-state value, and if the N counter latch is then programmed, the VCO may not oscillate at the desired frequency, which does not allow the band select logic to choose the correct frequency band and the ADF4360-1 may not achieve lock. If the recommended interval is inserted, and the N counter latch is programmed, the band select logic can choose the correct frequency band, and the part locks to the correct frequency.The duration of this interval is affected by the value of the capacitor on the C N pin (Pin 14). This capacitor is used to reduce the close-in noise of the ADF4360-1 VCO. The recom-mended value of this capacitor is 10 µF. Using this value requires an interval of ≥ 5 ms between the latching in of the control latch bits and latching in of the N counter latch bits. If a shorter delay is required, this capacitor can be reduced. A slight phase noise penalty is incurred by this change, which is explained in the Table 10.Table 10. C N Capacitance vs. Interval and Phase NoiseC N Value Recommended Interval between Control Latch and N Counter Latch Open-Loop Phase Noise @ 10 kHz Offset 10 µF ≥ 5 ms −85 dBc 440 nF≥ 600 µs−84 dBcCLOCKPOWER-UPDATALECONTROL LATCH WRITE TO N COUNTER LATCH WRITE04414-02Figure 16. ADF4360-1 Power-Up TimingHardware Power-Up/Power-DownIf the ADF4360-1 is powered down via the hardware (using the CE pin) and powered up again without any change to the N counter register during power-down, it locks at the correct fre-quency because the part is already in the correct frequency band. The lock time depends on the value of capacitance on the C N pin, which is <5 ms for 10 µF capacitance. The smaller ca-pacitance of 440 nF on this pin enables lock times of <600 µs. The N counter value cannot be changed while the part is in power-down because it may not lock to the correct frequency on power-up. If it is updated, the correct programming se-quence for the part after power-up is to the R counter latch, followed by the control latch, and finally the N counter latch, with the required interval between the control latch and N counter latch, as described in the Initial Power-Up section. Software Power-Up/Power-DownIf the ADF4360-1 is powered down via the software (using the control latch) and powered up again without any change to the N counter latch during power-down, it locks at the correct fre-quency because it is already in the correct frequency band. The lock time depends on the value of capacitance on the C N pin, which is <5 ms for 10 µF capacitance. The smaller capacitance of 440 nF on this pin enables lock times of <600 µs.The N counter value cannot be changed while the part is in power-down because it may not lock to the correct frequency on power-up. If it is updated, the correct programming se-quence for the part after power-up is to the R counter latch, followed by the control latch, and finally the N counter latch, with the required interval between the control latch and N counter latch, as described in the Initial Power-Up section.CONTROL LATCHWith (C2, C1) = (0, 0), the control latch is programmed. Table 7 shows the input data format for programming the control latch. Prescaler ValueIn the ADF4360 family, P2 and P1 in the control latch set the prescaler values.Power-DownDB21 (PD2) and DB20 (PD1) provide programmable power-down modes.In the programmed asynchronous power-down, the device powers down immediately after latching a 1 into Bit PD1, with the condition that PD2 has been loaded with a 0. In the pro-grammed synchronous power-down, the device power-down is gated by the charge pump to prevent unwanted frequency jumps. Once the power-down is enabled by writing a 1 intoBit PD1 (on the condition that a 1 has also been loaded to PD2), the device will go into power-down on the second rising edge of the R counter output, after LE goes high. When the CE pin is low, the device is immediately disabled regardless of the state of PD1 or PD2.When a power-down is activated (either in synchronous or asynchronous mode), the following events occur:•All active dc current paths are removed.•The R, N, and timeout counters are forced to their load state conditions.•The charge pump is forced into three-state mode.•The digital lock detect circuitry is reset.•The RF outputs are debiased to a high impedance state. •The reference input buffer circuitry is disabled.•The input register remains active and capable of loading and latching data. Charge Pump CurrentsCPI3, CPI2, and CPI1 in the ADF4360 family determine Current Setting 1.CPI6, CPI5, and CPI4 determine Current Setting 2. See the truth table in Table 7.Output Power LevelBits PL1 and PL2 set the output power level of the VCO. See the truth table in Table 7.Mute-Till-Lock DetectDB11 of the control latch in the ADF4360 family is the mute-till-lock detect bit. This function, when enabled, ensures that the RF outputs are not switched on until the PLL is locked.CP GainDB10 of the control latch in the ADF4360 family is the charge pump gain bit. When it is programmed to a 1, Current Setting 2 is used. When it is programmed to a 0, Current Setting 1 is used. Charge Pump Three-StateThis bit puts the charge pump into three-state mode when programmed to a 1. It should be set to 0 for normal operation. Phase Detector PolarityThe PDP bit in the ADF4360 family sets the phase detector polarity. The positive setting enabled by programming a 1 is used when using the on-chip VCO with a passive loop filter or with an active noninverting filter. It can also be set to 0. This is required if an active inverting loop filter is used.MUXOUT ControlThe on-chip multiplexer is controlled by M3, M2, and M1.See the truth table in Table 7.Counter ResetDB4 is the counter reset bit for the ADF4360 family. When this is 1, the R counter and the A, B counters are reset. For normal operation, this bit should be 0.Core Power LevelPC1 and PC2 set the power level in the VCO core. The recom-mended setting is 15 mA. See the truth table in Table 7.。

BD6989FVM资料