MIPS流水线CPU模板

MIPS指令五级流水CPU设计剖析

MIPS指令五级流水CPU设计剖析MIPS指令五级流水CPU设计是一种高性能的处理器设计架构,它将指令的执行过程拆分为五个阶段,并且在每个阶段中可以同时处理多条指令,实现了指令级并行处理。

在这种设计中,分别是取指(Instruction Fetch)、译码(Instruction Decode)、执行(Execute)、访存(Memory Access)和写回(Write Back)这五个阶段。

在MIPS指令五级流水CPU设计中,首先是取指(Instruction Fetch)阶段,这是整个处理器开始处理一条指令的阶段。

在这个阶段,处理器从指令存储器中读取即将执行的指令,并将其送入流水线中。

这个阶段还会包括对指令地址的计算和异常处理的操作。

当一条指令流入流水线后,处理器就会进行下一个阶段的操作。

接下来是译码(Instruction Decode)阶段,这个阶段主要是将取到的指令进行解码,确定指令的操作类型和需要操作的寄存器等信息。

在这个阶段,会根据指令的不同分支到不同的功能单元中处理。

同时还会识别指令之间的数据相关性,以便在后续阶段进行相应的控制。

第三个阶段是执行(Execute)阶段,在这个阶段,CPU执行指令的操作,进行算数运算或逻辑运算,或者进行跳转等控制操作。

在这个阶段,CPU还将从寄存器文件中读取数据,并进行相应的运算。

这个阶段涉及到的计算量比较大,所以需要比较多的时钟周期来完成。

接下来是访存(Memory Access)阶段,这个阶段主要是处理访问数据内存的操作,比如从数据内存中读取数据,或将结果写入数据内存等。

在这个阶段,处理器还会涉及到访存相关的操作,比如缓存机制的处理等。

这个阶段的操作通常是比较高速的存储器操作。

最后是写回(Write Back)阶段,这个阶段是处理器的最后一个阶段,处理器将执行结果写回到寄存器文件中,或进行其他相关的操作。

这个阶段可以认为是指令执行的结束阶段,对前面四个阶段产生的结果进行最终的处理。

基于MIPS指令集的流水线CPU设计与实现

基于MIPS指令集的流水线CPU设计与实现刘秋菊;张光照;王仲英【摘要】提出了一种CPU设计方案,实现指令集为MIPS指令集中选取15条指令作为本CPU的基本指令,采用基本5步流水线CPU设计.分析了流水线CPU的逻辑结构与指令的处理过程,给出了取指阶段IF、译码阶段ID、执行阶段EX、内存访问阶段MEM、寄存器写回阶段WB阶段的设计与实现.对流水线产生的相关性问题,采用Bubble法和Forwarding法相结合的方法来消除相关性,在FPGA平台上进行了测试,测试结果表明,该方案符合设计要求.%In this paper,a design method of CPU was proposed,the instruction set of the CPU contained 15 items of MIPS instruction set,and the basic method of five step pipeline CPU design was used.Analyses were conducted on the logic structure of the pipeline CPU and the processing of the instruction.This paper also gave design and realization of stage IF,stage ID,stage EX,stage MEM and stage WB.About the pipeline-related problems,the paper adopted Bubble and Forwarding technologies to eliminate it.The tests on the FPGA platform show that the scheme meets the design requirements.【期刊名称】《实验室研究与探索》【年(卷),期】2017(036)008【总页数】6页(P148-152,172)【关键词】流水线;中央处理器;设计;指令集【作者】刘秋菊;张光照;王仲英【作者单位】郑州工程技术学院信息工程学院,郑州450000;河南经贸职业学院技术科学系,郑州450018;河南经贸职业学院技术科学系,郑州450018【正文语种】中文【中图分类】TP332在工业设计和机器人研究中,微处理器作为控制部件的核心是设计的关键,其性能直接影响整个系统的性能。

MIPS指令五级流水CPU设计资料

0

0

PCSrc

31:26 5:0

CLK A1 A2 A3

1 WE3 RD1 1 RD2 0 1 0 0 WriteReg4:0 1 SrcA

CLK 010 Zero ALUResult A

0 WE 1 ReadData 0 1

ALU

Instruction Memory

20:16

SrcB

Register WD3 File

指令预取

取指令 3 执行指令 3

若 取指 和 执行 阶段时间上 完全重叠 指令周期 减半 速度提高 1 倍

时间?

二、 流水线操作时空图

空间 执行操作 取数操作 分析指令 1 I 2 2 3 3 4 4 5 5 6 6 7 7

1

1

2

2

3

3

4

4

5

5

6

6

7

7

取指令 1 2 3 4 5 6 7 T0 T1 T2 T3 T4 T5 T6 装入阶段 稳定流水阶段

2. 数据相关

不同指令因重叠操作,可能改变操作数的 读/写 访问顺序 • 写后读相关(RAW) SUB R1,R2,R3 ;(R2) (R3) ;(R5)+(R1) ;(R2) R1 R4 ADD R4,R5,R1 • 读后写相关(WAR) STA M,R2 ADD R2,R4,R5 M 存储单元 R2 R3 R3 ;(R4)+(R5) ;(R2)× (R1) ;(R4) (R5)

4.5 MIPS指令五级流水CPU设计

4.5.1 多周期CPU回顾 4.5.2 指令流水基本概念 4.5.3 MIPS指令流水的实现

4.5.1 多周期CPU回顾

多周期CPU特点 – 指令的执行划分为多个步骤 – 每个步骤占用一个CPU周期 – 不同指令的指令周期不同 – 指令串行执行

32位MIPS处理器说明

32位MIPS处理器说明一、实验目的熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。

二、实验原理及实验内容该32位MIPS处理器主要需要设计ALU、单周期、流水线。

下面分别讲述这三个部分的设计原理及实验内容。

1.ALUALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。

输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。

其功能表如下图所示:根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。

设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。

设计框图思路如下:(1)ALU_ADD_SUB这部分是ALU设计中最重要的一部分。

采用了8位超前进位级联,用与门来实现32位全加器。

减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。

需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。

是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。

若为无符号运算,加法结果溢出则最高进位为1,且结果不为负;减法结果溢出等价于结果为负,即最高进位为0。

而结果为0等价于全部位都取0。

(2)ALU_Shift移位运算分别有逻辑左移,逻辑右移,算术右移三种情况。

首先判断是逻辑移位还是算术移位来决定填充0还是填充逻辑位。

之后采取先将操作数根据左移还是右移的判断做出32位扩充,再根据shamt从最高位到最低位判断是否为0来决定取那几位操作数,最后得到移位的结果。

数字系统设计-流水线CPU设计

实验报告课程名称:数字系统设计实验Ⅱ学院:信电系数字系统设计实验Ⅱ流水线MIPS微处理器设计ContentsPart 1实验目的 (3)Part 2实验任务 (3)Part 3实验原理 (4)Part 4实验步骤 (12)1.IF级设计 (12)2.ID级设计 (14)3.Decode单元设计 (16)4.ALU单元设计 (22)5.EX级设计 (27)6.顶层模块设计 (29)Part 5仿真和波形分析 (37)1.IF级仿真分析 (37)2.Decode单元仿真分析 (38)3.ALU仿真分析 (40)4.顶层仿真分析 (41)Part 6心得 (42)实验报告一、实验目的(1)了解提高CPU性能的方法。

(2)理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

(3)掌握流水线MIPS微处理器的工作原理。

(4)掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器。

设计要求:(1)至少执行下列MIPS32指令。

①算数运算指令:ADD ADDU SUB SUBU ADDI ADDU②逻辑运算指令:AND OR NOR XOR ANDI ORI XORI SLT SLTI SLTU SLTIU③移位指令:SLL SLLV SRL SRLV SRA④条件分支指令:BEQ BNE BGEZ BGTZ BLEZ BLTZ⑤无条件跳转指令:J JR⑥数据传输指令:LW SW⑦空指令:NOP(2)在用5级流水线技术,对数据冒险实现转发或阻塞功能。

(3)在XUP Vietex-II Pro开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz.三、实验原理1.流水线MIPS CPU总体设计与构建流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用在高档CPU的构建中。

根据MIPS处理器指令的特点,将整体的处理过程分为取指令(IF)、指令译码、执行、存储器访问和寄存器写回五级,对应多周期CPU的五个处理阶段。

MIPS指令五级流水CPU设计剖析

MIPS指令五级流水CPU设计剖析MIPS指令五级流水将指令的执行过程划分为取指(Instruction Fetch, IF)、译码(Instruction Decode, ID)、执行(Execution, EX)、访存(Memory Access, MEM)和写回(Write Back, WB)五个阶段。

每个阶段由一个独立的硬件逻辑电路实现,这样指令可以在同一时间在不同阶段同时执行,从而提高了CPU的吞吐量。

在取指阶段,CPU从指令缓存(Instruction Cache)中读取指令,并将其送入指令译码阶段。

取指阶段主要包括以下几个步骤:首先,CPU从PC寄存器中读取下一条指令的地址;然后,CPU将这个地址发送到指令缓存中,读取对应的指令;最后,CPU将读取到的指令送入译码阶段。

在译码阶段,CPU对指令进行译码,确定指令的类型和操作数,并将这些信息传递给执行阶段。

译码阶段主要包括以下几个步骤:首先,CPU从指令中解析出操作码和操作数;然后,CPU根据操作码确定指令的类型,并确定需要使用的操作数;最后,CPU将指令类型和操作数传递给执行阶段。

在执行阶段,CPU执行指令的实际操作,并计算结果。

执行阶段主要包括以下几个步骤:首先,CPU根据指令类型和操作数进行相应的运算;然后,CPU将计算结果传递给访存阶段或写回阶段,具体传递给哪个阶段取决于指令的类型;最后,CPU将执行完成的指令从流水线中清除。

在访存阶段,CPU将数据存储到内存或从内存中读取数据,并将数据传递给下一个阶段。

访存阶段主要包括以下几个步骤:首先,CPU将执行阶段产生的数据存储到内存;然后,CPU从内存中读取数据;最后,CPU将读取到的数据传递给写回阶段或下一个指令的取指阶段。

在写回阶段,CPU将执行阶段产生的结果写回到寄存器文件(Register File)中,以保存计算结果。

写回阶段主要包括以下几个步骤:首先,CPU将执行阶段产生的结果写入寄存器文件;然后,CPU更新PC寄存器的值,以指向下一条需要执行的指令;最后,CPU将流水线上所有已经执行完成的指令清除。

MIPS芯片架构说明

MIPS芯片架构说明MIPS(Microprocessor without Interlocked Pipeline Stages)即无竞争流水线微处理器,是一种精简指令集(RISC)的芯片架构。

MIPS 架构由美国斯坦福大学的约翰·亨尼西等人于1981年提出,并于1984年成立MIPS公司进行商业化开发和推广。

MIPS架构在计算机领域有着广泛的应用,尤其在网络设备、数字视频处理、嵌入式系统等领域具有重要地位。

MIPS架构的设计理念是简化指令集,提高流水线效率,以提供高性能和高效能的微处理器。

MIPS指令集体系结构的特征包括:固定长度的32位指令;寄存器-寻址模式;延迟槽;无跳转偏移;定长延迟分支;乱序执行指令流水线;五级流水线等。

MIPS指令集是一种精简的指令集,通过减少指令种类、规定固定的指令格式和长度,以及简化指令的操作模式,达到提高指令执行效率的目的。

MIPS指令集包括加载存储指令,算术逻辑运算指令,分支和跳转指令,协处理器指令等。

MIPS架构采用寄存器-寻址模式来访问数据。

寄存器-寻址模式是指通过指定寄存器的编号来操作数据,而不是通过指定内存地址。

MIPS架构提供了32个通用寄存器,用于存储数据和中间结果,通过对寄存器的操作来实现数据的传输和计算。

这种设计简化了指令的编码和执行,提高了指令执行的效率。

MIPS架构中的延迟槽是指在条件分支指令后的一条或多条指令,不管条件是否满足都会执行。

延迟槽的设计可以充分利用流水线的性能,但需要程序员进行特殊的处理,以确保延迟槽的指令在分支满足或不满足时都能正确执行。

MIPS架构的指令集中,分支和跳转指令的目标地址是相对于当前指令的偏移地址。

相对地址的设计简化了指令的编码和目标地址的计算,提高了指令的执行效率。

MIPS架构中的乱序执行指令流水线是指将多条指令按照最大并行度进行重排序,在这个过程中可能会引入数据依赖、资源竞争等问题。

为了解决这些问题,MIPS架构采取了一系列的措施,如指令重排序、数据前推、动态分支预测等,以提高指令的并行度和流水线的效率。

第5章标量处理机(5.4,5.5,5.6)流水线的冲突MIPS流水线素材

ALU

ALU

DSUB R4,R1,R5

IM

Reg

DM

Reg

ALU

XOR R6,R1,R7

计算机科学与技术系 yangruioot@

对于在一个时钟周期内同一寄存器堆进行操作,在时钟的前半部 分进行写寄存器的操作,后半部分进行读寄存器的操作。

计算机科学与技术系 yangruioot@

如何解决对同一寄存器的访问冲突?

把写操作安排在时钟周期的前半拍完成,

每一个周期作为一个流水段;

在各段之间加上锁存器(流水寄存器)。

IF 段 IM

ID 段 Reg

EX 段

MEM 段 DM

WB 段 Reg

流水寄存器

计算机科学与技术系 yangruioot@

ALU

流水寄存器保证了流水线中不同段的指令不会相互影 响。每个时钟周期结束之后,该段的所有执行结果都 保存在流水段寄存器中,在下一个时钟周期开始作为 下一个段的输入。

采用定向技术消除上例中的相关 DSUB操作是在DADD操作产生了结果之后才使

用该结果的,考虑将DADD的结果从EX/MEM寄 存器移到DSUB需要的地方,也就是ALU的输入 锁存器,则不需要引入停顿。

计算机科学与技术系

yangruioot@

时间(时钟周期) 1 DADD R1,R2,R3 IM 2 Reg 3 4 DM 5 Reg 6

计算机科学与技术系

yangruioot@

时间(时钟周期) 1 load M 2 Reg 3 4 M 5 Reg 6 7 8

ALU

ALU

指令 i+1

M

Reg

M

Reg

ALU

指令 i+2

MIPS指令五级流水CPU设计资料

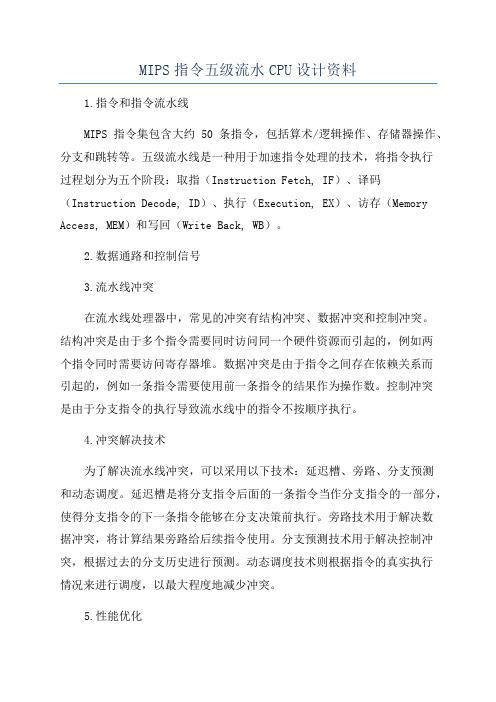

MIPS指令五级流水CPU设计资料1.指令和指令流水线MIPS指令集包含大约50条指令,包括算术/逻辑操作、存储器操作、分支和跳转等。

五级流水线是一种用于加速指令处理的技术,将指令执行过程划分为五个阶段:取指(Instruction Fetch, IF)、译码(Instruction Decode, ID)、执行(Execution, EX)、访存(Memory Access, MEM)和写回(Write Back, WB)。

2.数据通路和控制信号3.流水线冲突在流水线处理器中,常见的冲突有结构冲突、数据冲突和控制冲突。

结构冲突是由于多个指令需要同时访问同一个硬件资源而引起的,例如两个指令同时需要访问寄存器堆。

数据冲突是由于指令之间存在依赖关系而引起的,例如一条指令需要使用前一条指令的结果作为操作数。

控制冲突是由于分支指令的执行导致流水线中的指令不按顺序执行。

4.冲突解决技术为了解决流水线冲突,可以采用以下技术:延迟槽、旁路、分支预测和动态调度。

延迟槽是将分支指令后面的一条指令当作分支指令的一部分,使得分支指令的下一条指令能够在分支决策前执行。

旁路技术用于解决数据冲突,将计算结果旁路给后续指令使用。

分支预测技术用于解决控制冲突,根据过去的分支历史进行预测。

动态调度技术则根据指令的真实执行情况来进行调度,以最大程度地减少冲突。

5.性能优化为了提高CPU的性能,可以采取一些优化技术,例如流水线分段、超标量和超流水线。

流水线分段将指令流水线划分为多个段,使得每个段可以并行工作,提高指令的吞吐量。

超标量技术引入多个功能单元来同时执行多条指令,提高指令的并行度。

超流水线技术则进一步增加流水线的级数,以提高指令的处理速度。

总结:MIPS指令五级流水线CPU是一种高效的处理器设计,它采用五级流水线来加速指令处理,并通过解决流水线冲突来提高指令执行的效率。

该CPU的设计需要考虑数据通路和控制信号,以及解决冲突的技术和性能优化的方法。

基于MIPS架构的多周期CPU设计

2018 年软件2018,V〇1.39,N o. 8第 39 卷第 8 期COMPUTER ENGINEERING&SOFTWARE国际IT 传媒品牌基金项玛办文基于M IPS架构的多周期CPU设计柳成,荣静(扬州大学广陵学院,江苏扬州225000)摘要:为了提高多周期C P U流水线的效率,在指令存储器和数据存储器的数据读取中设计发送地址在上升 沿、读取数据在下降沿,从而实现译码和访存在一个周期内完成。

在取指级不再单独设置加法器,把PC+4放在ALU 中完成。

通过大量的多路选择器与数据交互总线来进行数据联通。

采用VerilogHDL语言设计出CPU,并在VIVADO 平台上实现仿真,最后通过龙芯公司的LS-CPU-EXB-002试验箱来进行验证,结果表明所设计的多周期C P U的有 效性。

关键词:流水线;V e r ilo g H D L;多周期C PU; L S-C P U-E X B-002试验箱中图分类号:TP332 文献标识码:A D O I: 10.3969/j.issn.l003-6970.2018.08.009本文著录格式:柳成,荣静•基于M IP S架构的多周期C P U设计[J].软件,2018, 39 (8):40-44Design of Multi-cycle CPU Based on MIPS ArchitectureLIU Cheng, RONG Jing(Guangling College ofYangzhou University, Yangzhou225000)【Abstract】:In order to improve the efficiency of the multi-cycle CPU pipeline,the designation of the sending ad-dress is on the rising edge and the reading data is on the falling edge in the data reading of the instruction memory and the data memory,so that the decoding and the access are completed in one cycle.The adder is no longer set separately at the fetch level,and PC+4 is placed in the ALU.Data communication is performed through a large number of multiplexers and data exchange buses.The CPU was designed using Verilog HDL language,and the simulation was implemented on the VIVADO platform.Finally,the verification was performed by the companyf s LS-CPU-EXB-002 test box.The results showed the effectiveness of the designed multi-cycle CPU.【Key words】:Pipeline;Verilog HDL;Multi-cycle CPU;LS-CPU-EXB-002 test box0引言M IPS架构是为流水线而生,每条M IPS指令的 执行分为五个部分,每一个部分为一个流水级。

64位MIPS指令处理器的流水线设计

64位MIPS指令处理器的流水线设计

李明刚

【期刊名称】《现代电子技术》

【年(卷),期】2005(28)3

【摘要】介绍了一种采用64位MIPS指令集CPU的流水线设计.作为SOC的核心,CPU的性能主要取决于指令的执行效率,而采用流水线方式大大增加了指令的执行速度,提高了CPU的性能.该CPU使用五级流水线设计,文中对影响流水线正常执行的各种因素进行了分析,以及在实际设计中采用相应的控制机制,从而完成对一个具有较高性能的CP U核的流水线控制的设计.

【总页数】3页(P98-100)

【作者】李明刚

【作者单位】合肥工业大学,理学院,安徽,合肥,230009

【正文语种】中文

【中图分类】TP332

【相关文献】

1.基于MIPS指令集的流水线CPU设计与实现 [J], 刘秋菊;张光照;王仲英

2.基于 MIPS 指令集的超标量和超长指令字混合架构处理器设计 [J], 李源;马海林;何虎

3.MIPS全64位超级流水线RISC R400处理器 [J], 赵信

4.超级流水线处理器MIPS R4000的结构设计及其特征 [J], 郑飞

5.基于FPGA的六级流水线MIPS处理器设计 [J], 孙巧稚;施慧彬

因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于MIPS32指令系统的三级流水线CPU设计方法[发明专利]

![一种基于MIPS32指令系统的三级流水线CPU设计方法[发明专利]](https://img.taocdn.com/s3/m/16886e235e0e7cd184254b35eefdc8d376ee149c.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 202010958681.8(22)申请日 2020.09.14(71)申请人 西北工业大学地址 710072 陕西省西安市友谊西路127号(72)发明人 唐家祺 画佳恒 王硕 马可 刘耀坤 王澍 王喜平 何成骋 姚远 (74)专利代理机构 西北工业大学专利中心61204代理人 刘新琼(51)Int.Cl.G06F 30/32(2020.01)G06F 9/30(2006.01)G06F 9/32(2006.01)(54)发明名称一种基于MIPS32指令系统的三级流水线CPU设计方法(57)摘要本发明涉及一种基于MIPS32指令系统的三级流水线CPU设计方法,其中在三级流水线实现的过程中,提出了一个新颖的逻辑结构使得三级流水线正常工作与运行,其通过取值、移码与执行三个阶段,并使用插入其中的流水线寄存器控制与记录每一级产生的新的信息,相比于五级流水线来说,其逻辑结构更为简单,使得其具有更快的时钟频率。

同时,由于只需要对极少的指令冒险和数据冒险,所以旁路设计逻辑简单,可以一定程度上提升指令的处理器的时钟频率和运行速度。

权利要求书1页 说明书26页 附图5页CN 112182999 A 2021.01.05C N 112182999A1.一种基于MIPS32指令系统的三级流水线CPU设计方法,其特征在于:三级流水线由两个流水线寄存器和在其三个流水级中插入的模块构成;三级流水线CPU的运行过程由取指令、译码和执行三级组成;其流水情况为:CLK 12345INS1IF DECODE EXEINS2 IF DECODE EXEINS3 IF DECODE EXE其中:IF——取指令DECODE——译码EXE——执行CLK——时钟节拍数INS——指令所述的取指令过程:首先由多路选择器模块MUX1选择适合的PC值,将其PC值发送给对应的PC模块,PC模块再将对应的地址转送给指令存储器,进行取地址操作,除此之外,再将地址存入下一级流水线寄存器中;当指令存储器收到指令对应的地址时,进行取指令操作,将这一拍取出的指令存入下一级流水线寄存器中;所述的译码过程:指令被送译码器中,根据所拥有的指令不同生成不同的控制信号,这些控制信号将帮助执行指令时保证指令正常运行,构成了指令的控制通路,将这些信号存入下一级流水线寄存器中;同时,指令信号被分段传输入寄存器文件中,这些信号是寄存器的索引,通过索引读出数据,将数据存入下一级流水线寄存器中;同时,还有部分信号和数据是直接在指令中包含的,通过前一级的流水线寄存器将其取出,然后导入下一级流水线寄存器中;所述的执行过程:流水线寄存器发出所有的数据信号和控制信号,他们将完成指令最终的操作,并将结果传回PC模块中;在直接跳转单元中,指令完成的是跳转地址的计算与选择操作,将最终地址传回多路选择器MUX1后,通过控制信号选择接下来的地址传入PC中;在算数逻辑运算单元模块ALU中,完成的是算数计算指令和逻辑运算指令,根据信号,将结果写回寄存器文件中;指令运行时可能发生异常,当异常发生时,异常处理模块将会改写指令的控制信号,使指令按照异常发生的控制信号进行运作,ALU或流水线寄存器将遇到的异常提交到协处理器单元CP0中,然后CPU会将这些进行处理;在Branch模块中,判断指令是否为分支跳转指令,视情况将不同的指令地址送入;流水线最后的多路选择器MUX2将选择何种数据写入寄存器文件;而多路选择器MUX3作用是判断是写入哪个寄存器文件中的寄存器。

流水线技术--MIPS R4000流水线计算机简介

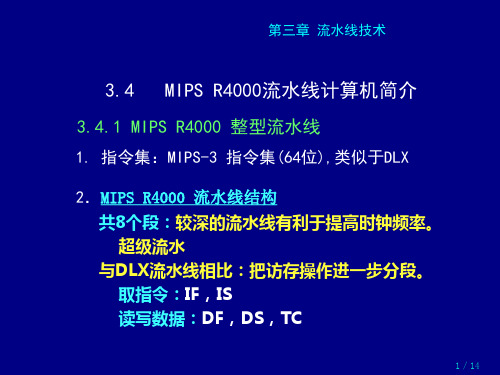

3.4 MIPS R4000流水线计算机简介

3. R4000浮点流水线是一种多功能非线性流水线 4. 双精度浮点操作指令的延迟、启动间隔以及 流水段的使用情况 (表3.9)

虚拟存储器的特点

13/14

表3.9

浮点指令 延 迟

初始化 间隔 3

4 35 111 1 1

使用的流水段

加、减

乘 除 求平方根 取反 求绝对值

虚拟存储器的特点

7/14

虚拟存储器的特点

3.4 MIPS R4000流水线计算机简介

◆ 采用单周期延迟分支

◆ 预测分支:失败分支

◆ 处理分支指令的时空图

虚拟存储器的特点

9/14

虚拟存储器的特点

3.4 MIPS R4000流水线计算机简介

3.4.2 MIPS R4000 浮点流水线

1. R4000浮点部件 ◆ 1个浮点除法器 ◆ 1个浮点乘法器 ◆ 1个浮点加法器

4

8 36 112 2 2

U,S+A,A+R,R+S

U,E+M,M,M,M,N,N+A,R U,A,R,D28,D+A,D+R,D+A,D+R,A,R U,E,(A+R) 108,A,R U,S U,S

浮点比较

3

2

U,A,R

虚拟存储器的特点

虚拟存储器的特点 1/14

3.4 MIPS R4000流水线计算机简介

3. 流水线中各段的功能

虚拟存储器的特点

2/14

4.指令序列在流水线中的重叠执行过程

虚拟存储器的特点

3.4 MIPS R4000流水线计算机简介

5. 载入延迟为两个时钟周期

基于MIPS的流水线处理器设计

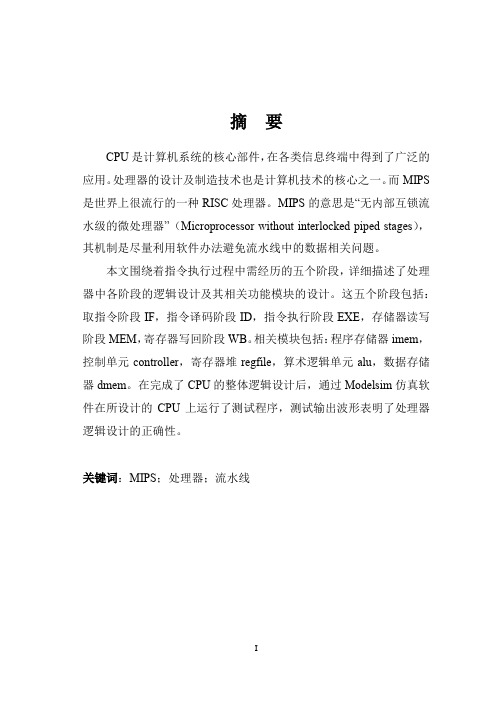

摘要CPU是计算机系统的核心部件,在各类信息终端中得到了广泛的应用。

处理器的设计及制造技术也是计算机技术的核心之一。

而MIPS 是世界上很流行的一种RISC处理器。

MIPS的意思是“无内部互锁流水级的微处理器”(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

本文围绕着指令执行过程中需经历的五个阶段,详细描述了处理器中各阶段的逻辑设计及其相关功能模块的设计。

这五个阶段包括:取指令阶段IF,指令译码阶段ID,指令执行阶段EXE,存储器读写阶段MEM,寄存器写回阶段WB。

相关模块包括:程序存储器imem,控制单元controller,寄存器堆regfile,算术逻辑单元alu,数据存储器dmem。

在完成了CPU的整体逻辑设计后,通过Modelsim仿真软件在所设计的CPU上运行了测试程序,测试输出波形表明了处理器逻辑设计的正确性。

关键词:MIPS;处理器;流水线AbstractThe Central Processing Unit (CPU) is the key part of a computer, which has been widely used in various information terminals.Also, the design and manufacturing technology of the processor is one of the cores of the computer technology. And, as a RISC processor, MIPS is very popular in the world. MIPS means “microprocessor without interlocked piped stages”, the mechanism of it is to avoid the data-related problems in the pipeline as much as possible by software.Around the five stages of the instruction execution, the article describes the logic designs of the processor and it’s related functional modules in detail.The five stages include: the instruction fetch stage IF, the instruction decode stage ID, the instruction execution stage EXE, the memory read/write stage MEM, and the register write back stage WB. The related modules include: the instruction memory imem, the control unit controller, the register file regfile, the arithmetic logic unit alu, and the data memory dmem.Upon the completion of the whole logic designs, running the test programs by the Modelsim, the correctness of the logic designs is proved by the output waveform.Keywords: MIPS, CPU, Pipeline目录摘要 (I)Abstract (II)目录.............................................................................................. I II 第1章MIPS体系结构概述.. (1)1.1 流水线技术 (1)1.2 RISC技术 (2)1.3 MIPS简介 (4)1.4 MIPS指令集 (5)1.5 本章小结 (10)第2章MIPS处理器的实现 (11)2.1 MIPS CPU顶层结构 (11)2.2 IF级 (13)2.3 ID级 (14)2.4 EXE级 (16)2.5 MEM级 (17)2.6 WB级 (19)2.7 外部数据输入中断 (19)2.8 本章小结 (20)第3章流水线CPU的仿真 (21)3.1 流水线CPU的指令仿真 (21)3.2 本章小结 (37)第4章总结和展望 (38)参考文献 (39)致谢 (40)附录1 英文文献 (41)附录2 中文译文 (48)附录3 主要模块代码 (54)第1章MIPS体系结构概述1.1 流水线技术在任一条指令的执行过程中,各个功能部件都会随着指令执行的进程而呈现出时忙时闲的现象。

(完整word版)MIPS流水线CPU的verilog实现

(完整word版)MIPS流水线CPU的verilog实现一、实验目的1.了解提高CPU性能的方法。

2.掌握流水线MIPS微处理器的工作原理。

3.理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

4.掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下:1.至少运行下列MIPS32指令。

(1)算术运算指令:ADD、ADDU、SUB、SUBU、ADDI、ADDIU。

(2)逻辑运算指令:AND、OR、NOR、XOR、ANDI、ORI、XORI、SLT、SLTU、SLTI、SLTIU。

(3)移位指令:SLL、SLLV、SRL、SRLV、SRA。

(4)条件分支指令:BEQ、BNE、BGEZ、BGTZ、BLEZ、BLTZ。

(5)无条件跳转指令:J、JR。

(6)数据传送指令:LW、SW。

(7)空指令:NOP。

2.采用5级流水线技术,对数据冒险实现转发或阻塞功能。

3.在XUP Virtex-Ⅱ Pro 开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz。

三、实验原理1.总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用于高档CPU的架构中。

根据MIPS处理器的特点,将整体的处理过程分为取指令(IF)、指令译码(ID)、执行(EX)、存储器访问(MEM)和寄存器会写(WB)五级,对应多周期的五个处理阶段。

如图3.1所示,一个指令的执行需要5个时钟周期,每个时钟周期的上升沿来临时,此指令所代表的一系列数据和控制信息将转移到下一级处理。

图3.1 流水线流水作业示意图由于在流水线中,数据和控制信息将在时钟周期的上升沿转移到下一级,所以规定流水线转移变量命名遵守如下格式:名称_流水线级名称例如:在ID级指令译码电路(Decode)产生的寄存器写允许信号RegWrite在ID级、EX级、MEM级和WB级上的命名分别为RegWrite_id、RegWrite_ex、RegWrite_mem和RegWrite_wb。

经典的MIPS五级流水介绍

无

第二个ALU操作数来自第 二个寄存器堆的输出(读 出数据2) PC的值替换为计算PC+4 的加法器的输出

PCSrc MemRead M器写数据的 输入值

三种流水线冒险

结构冒险 如果由于资源争夺导致几条指令 不能在同一时钟周期内执行,就称处理器 中含有结构冒险。 阻塞(stall)也叫气泡(bubble),解决结 构冒险的一种方式。

op op

rs

rt

constant or address

address

五种寻址模式:

1)寄存器寻址,操作数是寄存器 2)基址或偏移寻址,操作数在内存中,其地址是指令中 基址寄存器和常数的和。 3)立即数寻址,操作数是指令中的常数. 4)PC相对寻址,地址是PC计数器和指令中常数的和。 5)伪直接寻址,跳转地址是指令中26位和PC计数器的高 位相连而成

○

三种流水线冒险

数据冒险 一个操作必须等待另一个操作完成后才 能进行时,流水线必须停顿,我们称这种情况为 数据冒险。 转发(forward) 也叫旁路(bypass)。上一个 操作的结果产生以后不必写回寄存器,直接转发 给下一条指令。可以消除部分数据冒险。 阻塞(stall)当一条指令试图读取一个寄存器而 它前一条指令是load指令,并且该load指令写入 的是同一寄存器时,必须采用相应的机制阻塞流 水线。

引入流水线寄存器图

流水线每级的工作

流水线中的控制

一共9条控制线,根据流水线的五个步骤将 控制线分为五组: 1)取指令:读取指令内存和写PC的控制信 号总是确定的,没特别需控制的。 2)指令译码/读取寄存器:每个时钟周期内 这个步骤所完成的工作都是相同的,不需 设置控制线。

3)指令执行/地址计算:设置的控制线有RegDst、 ALUOp和ALUSrc。根据这些信号选择结果寄存器, 确定ALU的操作,同时读取数据2或经过符号扩展后 得到的立即数。 4)内存访问:设置的控制线有Branch、MemRead 和MemWrite,这些控制信号分别由相等分支、取和 存指令设定。除非控制信号指示这是一条分支指令 同时ALU输出为0,将选择线性地址中的下一条指令 作为PCSrc信号。 5)写回:两条控制线分别是MemtoReg和RegWrite, 前者决定是将ALU结果还是将内存数据传送寄存器堆, 后者记录所要写入的数据。

经典MIPS五级流水介绍

信号名称

设为0时的效果

设为1时的效果

RegDst

egWrite ALUSrcR

写入寄存器的目标编号来 自rt字段(20:16)

写入寄存器的目至写入寄 存器输入对应的寄存器 第二个ALU操作数为已符号化扩 展的指令低16位 PC的值置为计算分支目标地址的 加法器的输出 输入地址对应的数据内存的内容 放置到读出数据的输出 输入地址对应的数据内存的内容 替换为写入数据的输入 数据内存提供寄存器写数据的输 入值

○

三种流水线冒险

数据冒险 一个操作必须等待另一个操作完成后才 能进行时,流水线必须停顿,我们称这种情况为 数据冒险。 转发(forward) 也叫旁路(bypass)。上一个 操作的结果产生以后不必写回寄存器,直接转发 给下一条指令。可以消除部分数据冒险。 阻塞(stall)当一条指令试图读取一个寄存器而 它前一条指令是load指令,并且该load指令写入 的是同一寄存器时,必须采用相应的机制阻塞流 水线。

三种流水线冒险

分支冒险 也叫控制冒险。每周期都取指令, 但对与分支指令,必须等到MEM阶段才能 确定是否执行分支。这种为了确定预取正 确的指令导致的延迟叫做分支冒险。 静态预测 阻塞直到分支发生完毕的速度实 在太慢。比较普遍的提高分支阻塞速度的 方法是假设分支不发生,继续执行;或者 假定分支发生 ,跳到转移地址执行。可以 将分支冒险的代价减半。

引入流水线寄存器图

流水线每级的工作

流水线中的控制

一共9条控制线,根据流水线的五个步骤将 控制线分为五组: 1)取指令:读取指令内存和写PC的控制信 号总是确定的,没特别需控制的。 2)指令译码/读取寄存器:每个时钟周期内 这个步骤所完成的工作都是相同的,不需 设置控制线。

922116-计算机组成与实现-CH6--流水线CPU

流水线执行指令的详细过程

示例:lw―第3个时钟周期

ID/EX驱动ALU计算,结果写入EX/MEM

寄存器被写入 组合逻辑正在工作

25:00

PC

IM

AD

NPC

PC

IMM PC4

RA NPC

PC4F

25:21 20:16

A1 RF

A2 RD1

20:16 15:11

0 1

A3

1F

2

RD2

M1

WD

PC4D

由于寄存器值的保存与传递是分析要点,以及简化分析过程,不单独记录组合 逻辑计算结果

垂直方向:每行代表各寄存器在某个时钟上升沿后各自存入的值

CL1

CL2

CLK R1

R2

R3

1 XXX100

2 100200 101

3 100200 201

102

4

301

202

5

302

4

计算机组成与实现

回顾:MIPS数据通路的5个阶段

回写

MEM

WB

计算机组成与实现

流水线执行特点

理论上,流水线每时钟周期都可以从IM中读取一条新指令,同时 将已在流水线里的指令同时向前推进一个阶段

多条指令同时工作,但占用不同的资源(即处于不同阶段)

时钟周期

1

2

3

4

5

6

7

8

9

指令N 取指令 读操作数 执行

访存

回写

指 令 指令N+1 序 列 指令N+2

M1

WD

PC4D

15:00

EXT

IF/ID

IF 取指令

ID 译码/读操作数

流水线分析例题

流⽔线分析例题例1:MIPS 流⽔线,后半拍写 GPRs。

求阻塞法处理 RAW 冒险时的执⾏时间。

ADD R4,R5,R6SUB R7,R4,R6OR R8,R4,R6SW R6,20(R4)LW R9,20(R8)I1-I2 冒险,停 3 拍。

此时 I1-I3, I1-I4 均已消除。

I3-I5 冒险,停 2 拍。

故执⾏时间为 5+4+3+2=14拍。

例2:MIPS 流⽔线,前半拍写 GPRs。

求转发法处理 RAW 冒险时的执⾏时间。

假设存在 EX-EX,MEM-EX 的转发线路。

ADD R4,R5,R6SUB R7,R4,R6OR R8,R4,R6SW R6,20(R4)LW R9,20(R8)I1-I2 冒险,利⽤ EX-EX 线路转发,停 0 拍。

I1-I3 冒险,利⽤ MEM-EX 线路转发,停 0 拍。

I1-I4 冒险,同拍内 GPRs 先写后读,停 0 拍。

I3-I5 冒险,利⽤ MEM-EX 线路转发,停 0 拍。

故执⾏时间为 5+4=9 拍。

例3:MIPS 流⽔线,前半拍写 GPRs。

求转发法处理 RAW 冒险时的执⾏时间。

假设仅存在 EX-EX 的转发线路。

ADD R4,R5,R6SUB R7,R4,R6OR R8,R4,R6SW R6,20(R4)LW R9,20(R8)I1-I2 冒险,利⽤ EX-EX 线路转发,停 0 拍。

I1-I3 冒险,⽆法转发,停 1 拍(注意不是 2 拍!)。

此时 I1-I4 冒险已经消除。

I3-I5 冒险,⽆法转发,停 1 拍。

故执⾏时间为 5+4+1+1=11 拍。

例4:MIPS 流⽔线,后半拍写 GPRs。

求转发法处理 RAW 冒险时的执⾏时间。

假设仅存在 EX-EX 的转发线路。

ADD R4,R5,R6SUB R7,R4,R6OR R8,R4,R6SW R6,20(R4)LW R9,20(R8)I1-I2 冒险,利⽤ EX-EX 线路转发,停 0 拍。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本科实验报告课程名称:计算机组成与设计实验姓名:学院:信息与电子工程学院专业:电子科学与技术学号:314010指导教师:屈民军、唐奕2016年1 月7 日一、实验目的1.了解提高CPU性能的方法。

2.掌握流水线MIPS微处理器的工作原理。

3.理解数据冒险、控制冒险的概念以及流水线冲突的解决方法。

4.掌握流水线MIPS微处理器的测试方法。

二、实验任务设计一个32位流水线MIPS微处理器,具体要求如下:1.至少运行下列MIPS32指令。

(1)算术运算指令:ADD、ADDU、SUB、SUBU、ADDI、ADDIU。

(2)逻辑运算指令:AND、OR、NOR、XOR、ANDI、ORI、XORI、SLT、SLTU、SLTI、SLTIU。

(3)移位指令:SLL、SLLV、SRL、SRLV、SRA。

(4)条件分支指令:BEQ、BNE、BGEZ、BGTZ、BLEZ、BLTZ。

(5)无条件跳转指令:J、JR。

(6)数据传送指令:LW、SW。

(7)空指令:NOP。

2.采用5级流水线技术,对数据冒险实现转发或阻塞功能。

3.在XUP Virtex-Ⅱ Pro 开发系统中实现MIPS微处理器,要求CPU的运行速度大于25MHz。

三、实验原理1.总体设计流水线是数字系统中一种提高系统稳定性和工作速度的方法,广泛应用于高档CPU的架构中。

根据MIPS处理器的特点,将整体的处理过程分为取指令(IF)、指令译码(ID)、执行(EX)、存储器访问(MEM)和寄存器会写(WB)五级,对应多周期的五个处理阶段。

一个指令的执行需要5个时钟周期,每个时钟周期的上升沿来临时,此指令所代表的一系列数据和控制信息将转移到下一级处理。

由于在流水线中,数据和控制信息将在时钟周期的上升沿转移到下一级,所以规定流水线转移变量命名遵守如下格式:名称_流水线级名称例如:在ID级指令译码电路(Decode)产生的寄存器写允许信号RegWrite在ID级、EX级、MEM级和WB级上的命名分别为RegWrite_id、RegWrite_ex、RegWrite_mem和RegWrite_wb。

在顶层文件中,类似的变量名称有近百个,这样的命名方式起到了很好的识别作用。

1)流水线中的控制信号(1)IF级:取指令级。

从ROM中读取指令,并在下一个时钟沿到来时把指令送到ID 级的指令缓冲器中。

该级控制信号决定下一个指令指针的PCSource信号、阻塞流水线的PC_IFwrite信号、清空流水线的IF_flush信号。

(2)ID级:指令译码器。

对IF级来的指令进行译码,并产生相应的控制信号。

整个CPU的控制信号基本都是在这级上产生。

该级自身不需任何控制信号。

流水线冒险检测也在该级进行,冒险检测电路需要上一条指令的MemRead,即在检测到冒险条件成立时,冒险检测电路产生stall信号清空ID/EX寄存器,插入一个流水线气泡。

(3)EX级:执行级。

该级进行算术或逻辑操作。

此外LW、SW指令所用的RAM访问地址也是在本级上实现。

控制信号有ALUCode、ALUSrcA、ALUScrB和RegDst,根据这些信号确定ALU操作、选择两个ALU操作数A、B,并确定目标寄存器。

另外,数据转发也在该级完成。

数据转发控制电路产生ForwardA和ForwardB两组控制信号。

(4)MEM级:存储器访问级。

只有在执行LW、SW指令时才对存储器进行读写,对其他指令只起到一个周期的作用。

该级只需存储器写操作允许信号MemWrite。

(5)WB级:写回级。

该级把指令执行的结果回写到寄存器文件中。

该级设置信号MemtoReg和寄存器写操作允许信号RegWrite,其中MemtoReg决定写入寄存器的数据来自于MEM级上的缓冲值或来自于MEM级上的存储器。

2)数据相关与数据转发如果上一条指令的结果还没有写入到寄存器中,而下一条指令的源操作数又恰恰是此寄存器的数据,那么,它获得的将是原来的数据,而不是更新后的数据。

这样的相关问题称数据相关。

在设计中,采用数据转发和插入流水线气泡的方法解决此类相关问题。

(1)三阶数据相关与转发转发条件为:(操作数A、B同时满足)①WB级指令是写操作,即RegWrite_wb=1;②WB级指令写回的目标寄存器不是$0,即RegWriteAddr_wb≠0;③WB级指令写回的目标寄存器与在ID级指令的源寄存器是同一寄存器,即RegWriteAddr_wb=RsAddr_id 或RegWriteAddr_wb=RtAddr_id。

(2)二阶数据相关与转发(MEM冒险)转发条件:①WB级指令是写操作,即RegWrite_wb=1;②WB级指令写回的目标寄存器不是$0,即RegWriteAddr_wb≠0;③WB级指令写回的目标寄存器与在EX级指令的源寄存器是同一寄存器,即RegWriteAddr_wb=RsAddr_ex 或RegWriteAddr_wb=RtAddr_ex;④EX冒险不成立,即RegWriteAddr_mem≠RsAddr_ex 或RegWriteAddr_mem=RtAddr_ex。

(3)一阶数据相关与转发(EX冒险)转发条件ForwardA、ForwardB作为数据选择器的地址信号,转发条件不成立时,ALU 操作数从ID/EX流水线寄存器中读取;转发条件成立时,ALU操作数取自数据旁路。

转发条件:①MEM级指令是写操作,即RegWrite_mem=1;②MEM级指令写回的目标寄存器不是$0,即RegWriteAddr_mem≠0;③MEM级指令写回的目标寄存器与在EX级指令的源寄存器是同一寄存器,即RegWriteAddr_mem=RsAddr_ex 或RegWriteAddr_mem=RtAddr_ex。

3)数据冒险与数据转发这类冒险不同于数据相关冒险,需要单独一个“冒险检测单元(Hazard Detector)”,它在ID级完成。

冒险成立的条件为:①上一条指令是lw指令,即MemRead_ex=1;②在EX级的lw指令与在ID级的指令读写的是同一个寄存器,即RegWriteAddr_ex=RsAddr_id 或RegWriteAddr_ex=RtAddr_id。

冒险的解决:为解决数据冒险,我们引入流水线阻塞。

当Hazard Detector检测到冒险条件成立时,在lw指令和下一条指令之间插入阻塞,即流水线气泡(bubble),使后一条指令延迟一个时钟周期执行,这样就将该冒险转化为二阶数据相关,可用转发解决。

如图所示流水线气泡的引入需要注意的是,如果处于ID级的指令被阻塞,那么处于IF级的指令也必须阻塞,否则,处于ID级的指令就会丢失。

防止这两条指令继续执行的方法是:保持PC寄存器和IF/ID流水线寄存器不变,同时插入一个流水线气泡。

具体实现方法如下:在ID级检测到冒险条件时,HazardDetector输出两个信号:Stall与PC_IFWrite。

Stall信号将ID/EX流水线寄存器中的EX、MEM和WB级控制信号全部清零。

这些信号传递到流水线后面的各级,由于控制信号均为零,所以不会对任何寄存器和存储器进行写操作,高电平有效。

PC_IFWrite信号禁止PC寄存器和IF/ID流水线寄存器接收新数据,低电平有效。

2.3)分支冒险还有一类冒险是包含分支的流水线冒险流水线每个时钟周期都得取指令才能维持运行,但分支指令必须等到MEM级才能确定是否执行分支。

这种为了确定预取正确的指令而导致的延迟叫做控制冒险或分支冒险。

一种比较普遍的提高分支阻塞速度的方法是假设分支不发生,并继续执行顺序的指令流。

如果分支发生的话,就丢弃已经预取并译码的指令,指令的执行沿着分支目标继续。

由于分支指令直到MEM级才能确定下一条指令的PC,这就意味着为了丢弃指令必须将流水线中的IF、ID和EX级的指令都清除掉(flush)。

这种优化方法的代价较大,效率较低。

如果我们能在流水线中提前分支指令的执行过程,那么就能减少需要清除的指令数。

这是一种提高分支效率的方法,降低了执行分支的代价。

因此我们采用提前分支指令的方法解决分支冒险。

提前分支指令需要提前完成两个操作:①计算分支的目的地址:②判断分支指令的跳转条件:在提前完成以上两个操作之外,我们还需丢弃IF级的指令。

具体做法是:加入一个控制信号IF_flush,做为IF/ID流水线寄存器的清零信号。

当分支冒险成立,即Z=1,则IF_flush=1,否则IF_flush=0,故IF_flush = Z。

考虑到本系统还要实现的无条件跳转指令:J和JR,在执行这两个指令时也必须要对IF/ID流水线寄存器进行清空,因此,IF_flush的表达式应表示为:IF_flush = Z || J || JR。

2.MIPS指令格式1)R型指令格式本实验要实现的R型指令有:①算术逻辑运算指令:ADD、ADDU、SUB、SUBU、AND、OR、NOR、XOR 、SLT、SLTU②移位指令:SLLV、SRLV、SRA V、SLL、SRL、SRA③寄存器跳转指令:JR2)I型指令格式本实验要实现的I型指令有:①存储器访问指令:LW、SW②立即数算术逻辑运算指令:ADDI、ADDIU、ANDI、ORI、XORI、SLTI、SLTIU③分支指令:BEQ、BNE、BGEZ、BGTZ、BLEZ、BLTZ3)J型指令格式本实验要实现的I型指令有:无条件跳转指令:J3.ID的设计指令译码模块的主要作用是从机器码中解析出指令,并根据解析结果输出各种控制信号。

ID模块主要有指令译码(Decode)、寄存器堆(Registers)、冒险监测、分支检测和加法器等组成。

ID模块的接口信息如下表所示:(1)指令译码(Decode)子模块的设计Decode控制器的主要作用是根据指令确定各个控制信号的值,是一个组合电路。

我们将指令分成八类:R_type1:ADD、ADDU、SUB、SUBU、AND、OR、NOR、XOR 、SLT、SLTU、SLLV、SRLV、SRAV R型指令R_type2:SLL、SRL、SRAJR_type:JRJ_type:J J型指令I_type:ADDI、ADDIU、ANDI、ORI、XORI、SLTI、SLTIUBranch:BEQ、BNE、BGEZ、BGTZ、BLEZ、BLTZ I型指令LW:LWSW:SWDecode输出的九组控制信号:①RegWrite决定是否对寄存器(Registers)进行写操作。

当RegWrite高电平有效时,将数据写入指定的寄存器中。

需要写回寄存器的指令有:LW、R_type1、R_type2和I_type,则RegWrite_id= LW || R_type1 || R_type2 || I_type②RegDst决定目标寄存器是rt还是rd。