L结构处理器高速接口设计指导

讲解cpu设计的书籍

讲解cpu设计的书籍

关于CPU设计的书籍有很多,以下是一些经典和值得推荐的书籍:

《计算机体系结构量化研究方法》(中文名,作者John L. Hennessy / David A. Patterson)。

这本书是计算机体系结构方面的经典之作,适合入门者阅读。

《自己动手写CPU》(作者:雷思磊)。

这本书以MIPS32处理器为例,

讲解了处理器设计的基本原理和实现过程。

《教你设计CPU——RISC-V处理器》(作者:胡振波)。

这本书介绍了RISC-V指令集结构,并讲解了一个开源的RISC-V核的实现原理。

《深入理解计算机系统》(作者:Randal E. Bryant / David O'Hallaron)。

这本书涵盖了计算机体系结构的各个方面,包括CPU设计、内存管理、指

令集架构等,适合对计算机系统有较深了解的读者阅读。

《计算机组成与设计:硬件/软件接口》(作者:David A. Patterson / John L. Hennessy)。

这本书是计算机组成与设计的经典教材,详细介绍了计算机的各个部件以及它们之间的接口和通信。

这些书籍的难度和侧重点各不相同,读者可以根据自己的需求和兴趣选择适合自己的书籍进行阅读和学习。

同时,也可以结合在线课程、博客、论坛等资源,加深对CPU设计的理解。

MIPI高速数据接口的研究与实现

MIPI高速数据接口的研究与实现摘要:MIPI-DSI是MIPI联盟面对移动终端提供的一种高速度、低能耗的串行通讯接口,能够满足高分辨率显示,减少显示输出能耗的需要。

本文设计了作用于显示驱动芯片MIPI接口的高速接收电路,包含可校正输入终端电阻、带输入失衡补偿的高速度比较器还有串行转并行模块。

仿真分析显示,单通道数据传输速率达到了1Gbps。

关键词:MIPI;数据接口;差分传输技术移动行业处理器接口MIPI主要是为移动应用处理器建立标准协议,致力于为移动终端里面的高清摄像头、显示器、射频/基带等提供规范化的接口。

MIPI 技术不仅可以显著改善网络的带宽和性能,同时也具备节省成本、减少复杂度、降低功耗、抑制电磁干扰等优势。

可以说,MIPI不只是一种接口或协议,更是一套全面的、多样的、高质量的协议与标准。

一、MIPI接口技术概念及应用1、概念MIPI接口技术是一种基于串行数据传输的高性能技术,具有传输速度快、功耗低、尺寸小、可靠性高以及灵活性等优点。

MIPI利用高速差分传输技术,通过多个数据通道和时钟信号实现高速、可靠且低功耗的数据传输。

与传统的并行接口技术相比,MIPI接口具有更小的体积,可以有效地满足小型设备的设计要求。

此外,MIPI接口技术具有出色的抗干扰和抗噪声能力,使得数据传输更加可靠。

同时还具有极大的灵活性,可以满足多种应用场景以及多种设备的连接要求。

2、应用随着技术的发展,MIPI接口技术已经成为各种设备的标配,从智能手机到平板电脑,从汽车到医疗设备,都被广泛地用于图像和视频传输。

例如,手机和平板电脑的屏幕显示是我们日常生活中必不可少的一部分,而且,拍照、录像等多媒体功能也是不可或缺的。

这些功能的实现,需要高速的MIPI接口,以及更加快速的数据传输。

MIPI接口的出色性能使得手机拍照、录像和屏幕显示的效果大幅提升,可以实现高速传输,并且可以将拍摄的图像和视频数据实时显示在屏幕上,从而实现高帧率、高分辨率的拍照和录像体验,同时还能够有效地降低设备的能耗。

高速数据采集系统的新型接口设计

De i n o e t p fi e f c o i h s e d d t c i ii n sg f n w y e o nt r a e f r h g — p e a a a qu s to

在高速数 据采 集 系统 中, 字信 号 处 理 器 ( S ,it 数 DPd a 西 l

s ml mcs ) i emr往往 不能适应 A/ g p D芯 片的工作 速率 。为 了

C L 向 A D 发控制 命令 ;2 对采 集到 的信 息进行 处理 。 PD / ()

1 1 主要 器件 介绍 . 表 1 具体器件 列表 型号

Ab ta t sr c :Tr d t n l a a a q iiin s s e awa s u e u l l g o a ff l f g o F a n e r p e u s i n l a i o a t c u s t y t m l y s sa f l f rh l u l l f i d o a - a FI O si t r u tr q e tsg a sg LTh s p p r i to u e h e i t ra e d sg i r i a e n r d c s t e n w n e fc e i n,wh c h ih t e CPL wo k s t e lg c c n r l c r ,a d u e t D r s a h o i o t o o e n s s i s i t r u t n m o u e t fe h e u s in 1 o v h s u s t a h a a b i g s o a e n t ma c i g wih t e n e r p i d l o o f r t e r q e t sg a.S le t e is e h t t e d t en t r g o t h n t h o c p b l y o F F a a i t f I O.Th s e i n n t n y i r v s h p e o a a a q i i o e fc i e y b t lo a i i d sg o o l mp o e t e s e d f d t c u st n fe tv l , u as h s ma y i n a v n a e ,s c s wi i l i t ra e cr u t u i e s l y e s o t a s ln , a d o h r f a u e h t c n b d a t g s u h a t a smp e n e f c ic i, n v r a i , a y t r n p a t n t e e t r s t a a e h t e t n ie y u e n c mm u ia i n n ma ea q ii o L x e sv l s d i o n c to sa d i g c u st r i

RTL8019型控制器与DSP芯片TMS320F206的接口设计及编程技巧

RTL8019型控制器与DSP芯片TMS320F206的接口设计及编程技巧基于美国TI公司的高速数字信号处理器(DSP),详细描述RTL8019型以太网控制器的性能特点和引脚功能。

同时给出DSP与RTL8019的硬件电路接口设计方法及DSP控制RTL8019进行网络传输的相应软件编程方法。

1 引言数字信号处理器(DSP)具有先进的并行处理结构,特别适合于信号处理,已经越来越多地应用于工业控制领域和各类仪器仪表的开发设计。

互联网络硬件和软件的迅猛发展使得网络用户呈指数增长,在使用计算机进行网络互联的同时,各种家电设备、仪器仪表以及工业生产中的数据采集与控制设备逐步走向网络化,以便共享网络中庞大的信息资源。

在电子设备日趋网络化的背景下,利用高速数字信号处理器控制RTL8019实现以太网通讯具有十分重要的意义。

TMS320F206是TI公司生产的16-bit定点DSP,它有l条程序总线和3条数据总线,采用了改进的哈佛结构,内含高度并行的32-bit算术逻辑单元、16×16-bit并行硬件乘法器、片内存储器和片内外设,配备了高度专业化的指令集,功耗相当低,特别适合于信号处理。

RTL8019采用100引脚POFP封装,性能优良,价格低。

它支持PnP自动探测.符合EthernetⅡ与IEEE802.3(10Base5、10Base2、10BoseT)标准,内嵌16 KB SRAM,有全双工通信接口,可以通过交换机在双绞线上同时发送和接收数据,使带宽从10MHz增加到20MHz,是进行以太网通信的理想器件。

本文即结合DSP处理器的特点,详细介绍Realtek公司生产的RTL8019型以太网控制器的硬件电路设计方法及编程技巧。

2 RTL8019的主要引脚功能·AEN(34):地址使能引脚,决定电路被分得的地址空间:·INT0-INT7(97~100,1~4):中断请求引脚;·IOCHRDY(35):读/写命令准备引脚;·IOCSl6B(96):8位/16位数据选择引脚,高电平选择16位数据总线,低电平选择8位数据总线;·IORB,IOWB(29,30):I/O端口读命令、写命令;·SMEMRB,SMEMWB(3l,32):寄存器读命令、写命令;·RSTDRV(33):复位信号;·SD0-SDl5(36~43,87,88,90~96):数据线;·SA0-SDl9(5,7~13,15,16,18~27):地址线;·X1(50):20 MHz晶体振荡器或外部晶体振荡器输入引脚;·LEDBNC,LEDO,LEDl,LED2(60~63):网卡状态指示;·TPOUT+、TPOUT-、TPIN-、TPIN+(45,46,58,59);数据发送和接收引脚。

深大计算机408复试参考书目

一、《计算机网络》第7版,作者:谢希仁1. 本书是深圳大学计算机专业重点推荐教材,全面系统地介绍了计算机网络的基本概念、技术和应用,包括网络体系结构、传输介质、网络协议、网络管理等内容,适合深入学习计算机网络方面的同学参考。

2. 书中内容详实、权威性强,作者谢希仁是我国计算机网络领域的资深专家,他的研究成果被广泛应用在国内外的网络技术领域,该书拥有很高的参考价值。

二、《计算机组成与设计:硬件/软件接口》第5版,作者:DavidA.Patterson, John L.Hennessy1. 该书是计算机体系结构领域的经典教材,主要介绍了计算机系统的各个方面,包括指令级并行、处理器设计、存储系统、I/O系统、并行系统、网络互连等内容,适合对计算机硬件感兴趣的同学参考。

2. 书中涉及的内容丰富多样,涵盖了从传统的计算机系统结构、性能评价到现代的并行计算机体系、多核处理器等前沿技术,对于深入理解计算机组成与设计具有重要的指导意义。

三、《C++ Primer》第5版,作者:Stanley B.Lippman, Josée Lajoie, Barbara E.Moo1. 作为一本权威的C++编程语言教材,该书从基本概念到高级应用都进行了全面覆盖,包括语法、面向对象编程、模板、异常处理、STL 库等内容,适合对C++编程语言感兴趣的同学参考。

2. 本书在国际上获得广泛的赞誉,被誉为C++语言领域的经典之作,对于学习和掌握C++语言的同学来说,是不可多得的宝藏教材。

四、《算法导论(原书第3版)》,作者:Thomas H.Cormen, Charles E.Leiserson, Ronald L.Rivest, Clifford Stein1. 该书是计算机算法领域的经典教材,系统地介绍了算法分析与设计的基本原理,包括递归、排序与顺序统计量、数据结构、图算法、算法问题复杂性等内容,适合对算法与数据结构感兴趣同学参考。

soc设计知识点总结

soc设计知识点总结SOC(System on Chip)指的是在一个芯片上集成了一系列功能模块,包括处理器、存储器、I/O接口等,使得整个系统可以在一个单一的芯片上完成。

SOC设计是现代集成电路设计的重要领域,本文将对SOC设计的关键知识点进行总结。

一、SOC设计概述SOC设计是一项综合性工程,涉及到多个学科和技术领域。

在SOC设计过程中,需要考虑以下几个核心要素:1. 系统架构设计:确定系统的功能需求和整体结构,包括处理器的选择、总线结构、存储器层次结构等。

2. IP核集成:选择合适的IP核并进行集成,对SOC的功能和性能起到关键作用。

IP核可以是自己设计的,也可以是从第三方获取的。

3. 性能优化:通过对系统进行优化,提升其性能表现。

优化可能涉及到处理器架构、存储器等方面。

4. 功耗管理:SOC设计中功耗管理是一个重要的问题,需要采取适当的手段减少功耗,以实现低能耗的设计。

5. 验证和调试:验证设计的正确性和性能是否满足需求,并进行调试修复问题。

二、SOC设计中的关键技术1. 处理器架构:SOC设计中处理器的选择和架构设计是一个重要的决策。

常见的处理器架构有ARM、MIPS等,选择适合应用场景的处理器架构可以提高系统性能。

2. 存储器层次结构:SOC设计中存储器的选择和层次结构的设计对系统性能有着重要影响。

常见的存储器包括寄存器、高速缓存、SDRAM等,通过合理的存储器层次结构设计可以提高系统的存取速度。

3. 总线设计:SOC中各个模块之间的通信需要通过总线来实现。

总线设计需要关注带宽、延迟、支持的传输协议等方面,合理的总线设计可以提高系统的性能。

4. 通信接口设计:SOC设计中的I/O接口设计对于系统的外部通信起到重要作用。

常见的接口包括UART、SPI、I2C等,通过设计高效的接口可以提高系统的数据传输速率。

5. 时钟和时序设计:SOC设计中需要考虑各个模块之间的时钟同步和时序关系。

合理的时钟和时序设计可以确保系统正常工作,避免由于时序问题而引起的故障。

PCI接口设计及PCI9054

种:(1)单独的PCI接口芯片a(2)基于CPLD(Complex PTo掣a蚴ableLogicalDevice)

或FI'GA(Field ProgrammableGateArray)设计PCI接口。本文分别介绍了这两种 方法。

在论文前半部分分析和讨论了PCI规范的基本数据传输过程,并在此基础上 设计开发了一个基于PCI总线接口的数字信号处理系统。首先在论文第一部分论 述了PCI总线规范中基本传输过程及其终止的实现思想。然后主要分析和介绍使 用PLX公司的PCI9054芯片实现数字信号处理系统PCI接口的硬件设计。特别是 对PCI9054内部寄存器值的设定方式做了较为详尽的论述。接着实现了基于 PCI9054接口芯片的驱动程序及与主机的系统通信。

CPU(Central Processing Unit)的飞速发展,ISA/EISA(Extended Industry StandardArchitecture)逐渐显现出疲态,跟不上时代的步伐。当时CPU的速度甚 至还高过总线的速度,造成硬盘、显示卡还有其它的外围设备只能通过慢速并且 狭窄的瓶颈来发送和接收数据,使得整机的性能受到严重的影响。为了解决这个 问题,1992年Intel在发布486处理器的时候,也同时提出了32.bit的PCI总线。

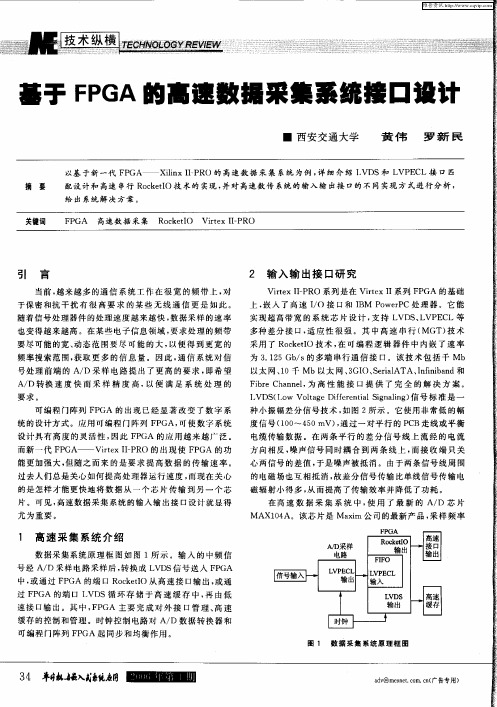

基于FPGA的高速数据采集系统接口设计

级差分输出幅度( 率) 制和可编 程 的四级输 出预加重 摆 控

模块 。R ceI ok t O的原始设计 是 比较 复杂 的, 幸运 的是 , 但 Xl x 司提 供 了大 量 成熟 的 和高 效 的 I Itlcu l i 公 i n P(ne eta l

Po et) rp r 核来 使 用 。如 果 能 够 很 好地 掌握 该 工 具 的使 y 用, 将会 极大 地缩 短设计 的进 度 , 减少 开发 和调试 时 问。

维普资讯

基于 F G P A的高速数 掘采集系统接 口设计

■ 西安交 通大学 黄 伟 罗 新 民

关键词

F GA P

高速 数 据 采 集 Ro k tO VitxI— RO e el re IP

引 言

当前 , 越来越 多的通信 系统 工作在 很宽 的频带 上 , 对 于保密和抗干 扰有 很 高要 求 的某些 无 线通 信 更是 如此 。

I S L w V l g iee t l in l g 信 号 标 准 是 一 VD ( o ot eDf rni g ai ) a f aS n 种 小 振 幅差 分 信 号技 术 , 图 2 示 。它 使 用非 常 低 的幅 如 所 度 信 号 (0 ~ 4 0mV)通 过 一 对平 行 的 P B走 线 或 平 衡 1 0 5 , C

码器 、 先进先出缓 冲器 F F 物理 介质接人 提供 与外部媒 IO;

体 的模 拟 接 口 , 中 包 括 :O倍 时 钟 倍 频 器 、 送 端 时 钟 其 2 发

生成器 、 发送缓 冲器 、 串化器 、 接收 端 的时钟恢 复 电路 、 接 收缓 冲器 、 串器 、 解 可变速率 的全双工收发器 、 编程 的五 可

STM32F207和DM9161A的高速以太网接口设计

S 邶 2 F 2 0 7和 D M9 1 6 1 A 的高速 以太 网接 口设计

党武松 , 范寒 柏 。 胡 杨

( 华 北 电力 大 学 电气 与 电 子 T 程学 院 , 保定 0 7 1 0 0 3 )

摘 要 :本 文 以微 处 理 器 S TM3 2 F 2 0 7和 网络 接 口芯 片 DM9 1 6 1 A为核心 , 并 在 此 硬 件 平 台上 添 加 了 网络 变 压 器 HS 9 0 1 6 。

s ou r c e c o de .

Key wor ds:Et he r ne t ; ST M 3 2 F2 07; Lw I P pr ot oc ol

引 言

本文 主 要 阐 述 了 基 于 S TM3 2 F 2 0 7微 处 理 器 和 DM9 1 6 1 A 网 络接 口芯 片 的 以 太 网 方 案 , 能 够 实 现 对 谐 波 的监狈 4 , 很 好 地 解 决 了谐 波 对 电 网 所 造 成 污 染 这 一 问 题 。

① MI I一 个 端 口 需 要 l 4根 数 据 线 , RMI I 一个 端 口 需 要 7根数 据 线 。

MA X 3 2 3 2 接 口 电路等 几 个 部分 。系 统框 图结 构 如 图 1

所示 。

② MI I 的数 据 传 输 需 要 4根 线 , RMI I 的 数 据 传 输 需

要 2根 线 。

S T M3 2 F 2 O 7内部 集 成 了 MA C ( Me d i a A c c e s s C o n t r o 1 )

Et h er n e t l n t er f a c e Ba s e d o n STM 3 2F 2 0 7 a n d DM9 1 6 1 A鲞

龙芯 3C5000L 处理器 数据手册说明书

龙芯3C5000L处理器数据手册V1.2龙芯中科技术股份有限公司[键入文字]I 版权声明本文档版权归龙芯中科技术股份有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术股份有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村环保科技示范园龙芯产业园2号楼Building No.2, Loongson Industrial Park,Zhongguancun Environmental Protection Park, Haidian District, Beijing电话(Tel):************传真(Fax):************阅读指南《龙芯3C5000L处理器数据手册》主要介绍龙芯3C5000L处理器接口结构,特性,电气规范,以及硬件设计指导。

修订历史文档更新记录文档名: 龙芯3C5000L 处理器 数据手册 版本号:V1.2 创建人:芯片研发部 创建日期 : 2021-11-26更新历史序号更新日期 版本号 更新内容12021-2-20 V1.0 初稿 2 2021-8-20 V1.1 调整分级,处理器核等相关信息3 2021-11-26 V1.2 第一章,修改概述2.4节,修改SYSCLK 要求2.5节,修改I2C 描述2.6节,修改中断描述2.9节,修改CLKSEL 说明2.10节,修改引脚名称3.3节,修改HT 描述4.3节,修改复位描述6.5.1节,修改电源描述 手册信息反馈:*******************也可通过问题反馈网站/ 向我司提交芯片产品使用过程中的问题,并获取技术支持。

高速接口设计调试

在某 型号接收机 中内部数据 的接收和整机对外部数据 的传送 中转 采用 主控板来实现 , 接收机 的设计 要求 : 主控板对数字信号处理板 的数 据接 收要 做到高可靠性 、 实时性 、 传输的数据量大 、 数据 口多 。 2 . 数据传输 方案的选 择 在进行数据 传输 的时候 考虑 了多种 数据传输 的方案 : 串 口、 双 口、 C P C I 、 G P I O、 自定义 高速 口等 , 并对 几种 传输方 案 的优缺 点进 行 了分 析, 对 可行性 进行了论证。 串 口: 采用串 口进行传输 的优 点是 , 根据前期项 目的经验 和从 项 目 的继 承性上 , 数据 的传输最初考 虑用串 口的形式 , 采用 串口有前期 的经 验 可以借鉴 , 从项 目的延续性上讲 , 如果采用 串口在数据 的接 收上 可以 采 用前期项 目的方 案 , 采用 C P C I 的处理器 和多串 口卡来实现数据 的接 收, 不需要 自己开发 主控板 , 相对 硬件设计 的工作量小 , 系统实现相对 简单, 连线 少 , 调试方 便。缺点是 串 口的传输 速率相对较低 , 一般 的处 理器只能到 1 1 5 2 0 0 b p s , 即使 采 用前 期 项 目的成 功 经 验也 只能 做 到 4 0 6 8 0 0 b p s , 况且前 期 的项 目只有 6个 串口 , C P C I 处理 器处理起 来 已经 相 当紧张 , 目 前 的系统有 2 0 个 串口 , 原方案很难满足 现在的使用要求 , 数 据传输 的时效性得不 到保证 , 且从 项 目的总体上考虑需 要各个数字 信号 处理板同源 、 需要有对各个 数字信 号处理板 同步 的一些控制信 号 , 目 前 的现有 的 C P C I 处理器满足不 了使用要求 。故不考虑采用 C P C I 配 合 多串 口卡的方案。 双口: 采用双 口的优点是 数据 的传输是 并行 的 , 数 据 的传 输速率 高, 可 以按 照约定 的协议 双方进行数 据通信 , 实现相对 简单 , 缺点是 连 线多, 需要 多根地址线 、 数据线 以及 读写片选控 制线等 , 从 而导致 主控 板上 的连接线过多 , 总线底板上 的信号走线变得复杂 , 线路 实现 的可靠 性得 不到有效保证。 C P C I : 采用C P C I 的优点是 C P C I 是标准的总线 , 采用前插板 的形 式 , 显得 整机结构简洁 、 可对板 子进行 热插 拔 , 相对来说维护起来方便 。缺 点 是从设 计实 现上 就要求 所有 的数字信 号处理 板与 主控板都 必须 是 C P C I 接 口的 , 根据整机 4 U的结 构要 求 , 就需要把板卡设计成标准 3 U的 板卡, 标准 3 U的板卡实现数字信号处理板 与主控板 的功能从尺 寸上来 说 无法实现 , 且 因为 主控板 与数 字信号处理板间有 同步控制信 号线 , 需 要 定做 C P C I 的底板。故放弃该方案 。 G P I O: 采用 G P I O的优点是 G P I O数据 的传 输速率 高 , 缺点 是 G P I O 的布线要 求高 , 鉴于整机 的结构 复杂 , G P I O的信 号流 向要 经过数 字信 号 处 理板 、 总线 底 板 、 主 控板 等板 卡 , 布 线 实现 比较 困难 , 难 以保 证 G P I O的正常工作 , 风险较大。故放弃该方案。 自定义总线 : 采用 自定 义总线的优点是实现灵活 , 可 以根据 系统的 实际需要 , 减 少布线风险 、 电路板 的尺寸不像 C P C I 板卡受 限 , 设计 得当 可以用较少的信号线 , 可 以做到相 当高 的数据传输速率 。 3 . 高 速 口的 实 现 与 调 试 通过 对 目前 几种 常用 的数据传 输方 案的 比较结 合项 目的实 际要 求, 采用高速 自 定义口 板 内的数据传输 , 根据 系统实 际和数字信号处理 板、 主控板板上资源情 况 , 实现时采用异步通信 , 增加 同步头和帧尾 , 采 用异步 3 2位数据后 , 单板 的数据传输 时间不到 1 0 ms , 在 主控板对 数据 进行接 收时采用 多路数据 的并行接 收 , 用F P GA来 同时接收 1 0 个 数字 信号处理板的数据 , 在D S P 对F P G A 进行数据读取 时 , 通过 D S P 和F P G A 接 口时序 的优化 , 实现在 5 m s 内对接 收到的 1 O 块数 字信号处理 板数据 的依次读取 , 保证 数据传 输的实时性 , 为后面 的设计 实现预留充足的时 间, 保证 了整机对外进行数据传输 的实 时f 生 要求 。 因 为 采 用 自定 义 口 , 在 调 试 过 程 中 出现 了各 种 各 样 的 问 题 , 如 主 控 板收不 到数 据 、 收到的数 据有 丢 、 多、 错的现象 , 单 口到多 口扩充 移植 等, 下面就调试过程 中几个 比较突 出的问题进行一个 简要 的描述。 ( 1 ) 发送 的最后一个字节收不 到 在主控板进行数 据接收时 , 为 了验证接收 到数据 的正确性 , 测试采 用数字 信号处理 板单 口发送 、 主控板接 收 , 固定数据 包 的大小 , 手动连 续发送 的办法 , 分 别统计发送和正确接收 的数据包 , 发现两边的数据包 始终差一包 , 从数 据的第一包就开始差 , 单 步发送 一个数据包发现主控 板收不 到本包 的最后一个数 据 , 反复试 验多次 , 现象 一致 , 经过 分析排 除 了数字信号处 理板发送问题 , 定位到 主控板 的接收异常 , 异常 的原 因 有逻辑 和软件两个方 面 , 首先排 除软 件问题 , 重点 对 F P G A的逻辑设计 进行排查 , 依据接 收信号的流程逐步对收 到的数 据进 行排查 , 对设计 的 逻辑进行时序仿真 , 发现确实存在最后一个数据不能正 确读 出的问题 。 在仿 真 的 时序 图形 中可 以看 到 , 在F P G A的逻 辑设 计 中 , D S P对 F P G A的读数信号 已经有效 , 但是读 F P G A内部 的存贮单元 的读 信号滞 后D S P对 F P G A的读数信 号 , 导 致本次 读 出的是前 一个读 信号读 出的 F P G A 存贮 单元 的内容 , 而不 是本 次实际要 读的数据 , 所 以本次读 信号 读 不到本 次数 据 , 而 当下一包数据 到来时 , F P G A把数据 收下来存贮 到 内部的寄存器 , D S P 对F P G A进行读 操作时 , 读 出来 的是上 一包 的最后 个字, 然后 才是本包 的数据 , 按 照这样 的流程 进行下去 , 本包 的最后 个数据依 然没有读取 。

基于FPGA的高速Link接口收发器设计

文章编号 : 1 6 7 3 . 1 . 1 3 1 ( 2 0 1 4) 0 8 — 0 0 4 7 — 0 3

Hi g h— s pe e d Li nk Po r t Tr a ns mi t t e r/Re c e i v e r Ba s e d o n FPGA

p r o c e s s i n g s y s t e m wa s g r e a t l y r e s t r i c t e d b y d a t a t r a n s mi t t i n g r a t e b e t we e n DS P a n d F P GA. T h e r e f o r e , h i g h — r a t e , wi d e d a t a b a n ・

2 0 1 4 年 第 8 期 ( 总第 1 4 0期 )

信 息 通 信

I N FO R M A TI ON & C 0M M UN I CATI ON S

24 0 )

基于 F P G A的高速 L i n k 接 口收发器设计

陈 捷。 卢汉平

d wi d t h d a a t r e a l — t i me t r a n s c e i v e r b e c o me t h e v i t a l p a r t o f mo d e m s i g n a l p r o c e s s i n g s y s t e m. I n t h i s p a p e r , a h i g h — r a t e t r a n s c e i v e r

LON节点采用查询方式的主从处理器SPI接口设计

的一种完全开放 的现场总线技术 , 是用于开发监控 网 络 系统 的一 个完整的技术平台。 o wok 的核心技 L n rs

速、 全双工、 同步的串行通信总线s I P连接节点的主从 处理器 , 具有电路简单、 速度快、 通信可靠等优点。

制, 因而其应用处理能力相对较弱, 对于复杂的应用常

使 用主 从 处 理器 结 构 。 处 理 器 完成 应 用程 序 处 理 , 主

1 e rn u0 芯片禾 L r a N 口 01 l ]k _

技术探讨

T C NC LE P O A I E H lA X L R TON

L oN苇点采用查询方式的

主 从 处 理器 S I P 接口设 计 ห้องสมุดไป่ตู้

De i n O n e f C _rL Sg fSPI t rl e f ON d s d l a 0 N0 e Ba e O C i C u e O s / a e Pr c S O ig l q i d n Ar ht t r fHO tSIV O e s rUsn n U r MO e e y

杨 帅 薛 岚 徐 建俊 高安 邦 江 苏电子产品装备 制造工程 技 术研 究开发中心 ( 江苏淮安 2 3 0 ) 2 0 3

摘

要: 为增 强L n rs o wok 节点控 制 能 力 ,采 用单 片机作 为L n rs o Wok 节点 的 主处 理 器 ,Nern 片作 为从 处 uo 芯 理 器; 主从 处理 器采 用S I P 通信 接 口;利 用Nern 片 中声 明的Nerwi 对 象和 A 8 s 1 片机 中 uo 芯 uo r e T 9 5单

基于S3C2440的LXI总线高速数据采集模块的设计

A /D c n e t r F F s h a h e o y 8 C 4 0 a h a n p o e s r P D a o p o e s r t e l z h o v r e , I O a t e c c e m m r , 3 2 4 s t e m i r c s o ,C L s a c — r c s o o r a i e t e

具体 的数据采 集控制过程可 以分 为以下步骤 : ( )系统 的初始化 : i aFF . I O复位控制 :I T 2 7在使用前需复位 ,其低 电平 D 70 复位最 小时间需大于 2 n , 5 s 写入数据 O O O H时, I O复位 xOO FF

信 号 变 为低 电 平 , 复 位 F F ;¥ C 4 0内部 程 序 延 迟 一 段 时 IO 3 2 4

将 I T 2 7数 据 输 出 到 ¥ C 4 0的数 据 总 线 L A A 5 D70 32 4 D T I  ̄

LAA D T O上 去 。

开 始

成的 以太 网控制模块 , 需要一个 与之 匹配 的 D 9 0 M 0 0控制芯片

差 分 输 入 或 者 单 端 输 入 ,而 且 可 以 灵 活 的选 择 输 入 范 围 和 偏

移 。该 A D芯片 的采集速 率可 以向下兼容, 过改变其输入采 通 样 时钟的频率既可 以实现其极 限速 率的高速 采样也可 以进行 低 速的采样 ,所 以选择 A 9 2 以保证采样速度 的灵活性 。 D 2 4可

IT 2 7输 出/ F的 半满 信 号 ,并 在 C L D70 H P D内 部产 生 ¥ C 4 0 324 中 断 请 求 信 号 IQ A 。 R_ D ( )响 应 中 断 及 查 询 中断 源 :¥C 4 0响 应 中 断 后 ,当 5 324 nC 5 为 低 ,地 址 为 中 断源 查询 地址 时 , 读 取 数 据 总 线 上 对 GS 应 的 数 据 位 来 查 询 中断 源 。 ( ) 读 取 数 据 : 若 ¥ C 4 0查 询 到 的 是 F F 生 的半 6 324 IO产 满 ( H )信 号产 生 的 中 断 请 求 ,则 即 将 n C 5为 低 ,地 址 为 /F GS

TMS320C55x硬件设计实例

04

使用触发器或延迟链技术,实

现精确的时序控制。

05

通过仿真和测试,验证时序优

化效果并调整参数。

06

06

TMS320C55x常见问题 与解决方案

启动问题

启动问题

在TMS320C55x硬件设计过程中,有 时会出现启动失败的问题,这可能是 由于电源不稳定、复位电路故障、启 动配置错误等原因造成的。

解决方案

04扩Biblioteka 板设计扩展板是为了满足特定应用需 求而设计的,可以添加额外的

功能模块和接口。

扩展板的设计需要考虑与核心 板的接口匹配,以及与其他扩

展板的互操作性。

扩展板上的元件布局和布线同 样要合理,以确保信号完整性 和减小电磁干扰。

扩展板的尺寸和重量也需要考 虑,以满足实际应用的需求。

接口板设计

接口板是用于连接外部设 备的板卡,如串口、并口、 USB等。

详细描述

TMS320C55x系列DSP具有高速的运算能力和高效的数字信号 处理算法,能够快速处理大量的图像数据。通过使用 TMS320C55x,可以实现高效的图像压缩、图像增强和图像识 别等功能。

信号处理

总结词

TMS320C55x系列DSP在信号处理领域具有出色的实时信号处理能力和高效的算法,适用于通信信号 处理、雷达信号处理、振动信号处理等应用。

低功耗

TMS320C55x采用低功耗设计, 能够在保证性能的同时降低功耗, 延长设备的使用时间。

集成度高

TMS320C55x集成了丰富的外设 接口,如串口、GPIO等,方便与 其他硬件设备进行连接和控制。

应用领域

音频处理

TMS320C55x强大的数字信号处理能力使其成为音频处理领域的 理想选择,如音频编解码、音频效果处理等。

高速铁路设计规范(最新版)

11 总则1.0.1 为统一高速铁路设计技术标准,使高速铁路设计符合安全适用、技术先进、经济合理的要求,制定本规范。

1.0.2 本规范适用于旅客列车设计行车速度250~350km/h 的高速铁路,近期兼顾货运的高速铁路还应执行相关规范。

1.0.3 高速铁路设计应遵循以下原则:(1)贯彻“以人为本、服务运输、强本简末、系统优化、着眼发展”的建设理念;(2)采用先进、成熟、经济、实用、可靠的技术;(3)体现高速度、高密度、高安全、高舒适的技术要求;(4)符合数字化铁路的需求。

1.0.4 高速铁路设计速度应按高速车、跨线车匹配原则进行选择,并应考虑不同速度共线运行的兼容性。

1.0.5 高速铁路设计年度宜分近、远两期。

近期为交付运营后第十年;远期为交付运营后第二十年。

对铁路基础设施及不易改、扩建的建筑物和设备,应按远期运量和运输性质设计,并适应长远发展要求。

易改、扩建的建筑物和设备,可按近期运量和运输性质设计,并预留远期发展条件。

随运输需求变化而增减的运营设备,可按交付运营后第五年运量进行设计。

1.0.6 高速铁路建筑限界轮廓及基本尺寸应符合图1.0.6 的规定,曲线地段限界加宽应根据计算确定。

27250550040002440170017501250650③①②④⑤1700251250①轨面②区间及站内正线(无站台)建筑限界③有站台时建筑限界④轨面以上最大高度⑤线路中心线至站台边缘的距离(正线不适用)图1.0.6 高速铁路建筑限界轮廓及基本尺寸(单位:mm)1.0.7 高速铁路列车设计活载应采用ZK 活载。

ZK 活载为列车竖向静活载,ZK 标准活载如图1.0.7-1 所示,ZK 特种活载如图1.0.7-2 所示。

图1.0.7-1 ZK 标准活载图式图1.0.7-2 ZK 特种活载图式31.0.8 高速铁路应按全封闭、全立交设计。

1.0.9 高速铁路设计应执行国家节约能源、节约用水、节约材料、节省用地、保护环境等有关法律、法规。

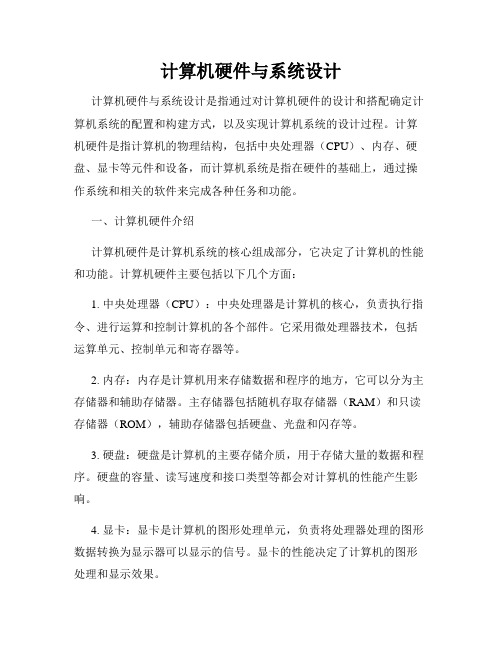

计算机硬件与系统设计

计算机硬件与系统设计计算机硬件与系统设计是指通过对计算机硬件的设计和搭配确定计算机系统的配置和构建方式,以及实现计算机系统的设计过程。

计算机硬件是指计算机的物理结构,包括中央处理器(CPU)、内存、硬盘、显卡等元件和设备,而计算机系统是指在硬件的基础上,通过操作系统和相关的软件来完成各种任务和功能。

一、计算机硬件介绍计算机硬件是计算机系统的核心组成部分,它决定了计算机的性能和功能。

计算机硬件主要包括以下几个方面:1. 中央处理器(CPU):中央处理器是计算机的核心,负责执行指令、进行运算和控制计算机的各个部件。

它采用微处理器技术,包括运算单元、控制单元和寄存器等。

2. 内存:内存是计算机用来存储数据和程序的地方,它可以分为主存储器和辅助存储器。

主存储器包括随机存取存储器(RAM)和只读存储器(ROM),辅助存储器包括硬盘、光盘和闪存等。

3. 硬盘:硬盘是计算机的主要存储介质,用于存储大量的数据和程序。

硬盘的容量、读写速度和接口类型等都会对计算机的性能产生影响。

4. 显卡:显卡是计算机的图形处理单元,负责将处理器处理的图形数据转换为显示器可以显示的信号。

显卡的性能决定了计算机的图形处理和显示效果。

5. 输入输出设备:输入输出设备包括键盘、鼠标、显示器、打印机、扫描仪等,它们用于与计算机进行交互和数据的输入输出。

二、计算机系统设计原则在进行计算机系统设计时,需要考虑以下几个原则,以确保系统的稳定性和高效性:1. 全局优化:要从整体上考虑系统的设计,确保硬件和软件的搭配是协调和高效的,避免出现瓶颈和冲突。

2. 模块化设计:将计算机系统划分为多个模块,每个模块负责不同的功能,以便更好地进行管理和维护。

3. 可扩展性:要考虑系统的可扩展性,即在未来需要增加硬件配置或扩展功能时,能够方便地进行升级和扩展。

4. 可靠性:计算机系统的可靠性非常重要,需要选择可靠的硬件元件,采取适当的备份和容错机制,以确保系统的稳定性和可用性。

基于P2020处理器的高速数据总线接口设计_陈崇森

基于P2020处理器的高速数据总线接口设计※陈崇森(广州海格通信集团股份有限公司,广州510663)摘要:通过以Freescale公司的P2020双核处理器为核心的嵌入式硬件平台,介绍了CPU与FPGA的基于Local Bus接口设计具备DMA传输功能及环形缓冲的高速数据总线接口方法,以及基于Linux3.0内核开发此接口的驱动程序的实现方法。

该技术已在某宽带高速设备上应用,实际测试,其实时稳定性、数据吞吐量、链路稳定性均满足设计要求,对同类型嵌入式平台的高速数据总线接口设计及开发有借鉴意义。

关键词:P2020;Local Bus;DMA;环形缓冲中图分类号:TP311 文献标识码:AHigh-speed Data Bus Interface Based on P2020※Chen Chongsen(Guangzhou Haige Communications Group Incorporated Company,Guangzhou 510663,China)Abstract:Taking the embedded platform using Freescale P2020dual-core processor as the example,the high-speed data bus interface de-sign based on the local bus between CPU and FPGA is introduced,which has DMA transfer function and the ring buffer.The implemen-tation method of the driver for the interface based on Linux3.0kernel is also introduced.The technology has been applied in a wide bandhigh speed device.The test results show that the stability,data throughput and link stability all meet the design requirements.The designhas reference significance to the same type of embedded platform.Key words:P2020;Local Bus;DMA;ring buffer引 言QorIQ P2平台是Freescale公司推出的高性能低功耗系列处理器,包括P2020双核以及P2010单核两款产品。

(完整版)TMS320C6455高速SRIO接口设计

TMS320C6455高速SRIO接口设计引言数字信号处理技术已广泛应用于通信、雷达、声纳、遥感、图形图像处理和语音处理等领域。

随着现代科技的发展,尤其是半导体工艺的进入深亚微米时代,新的功能强劲的高性能数字信号处理器(DSP)也相继推出,如ADI(美国模拟器件)公司的TigerSHARC系列和TI(德州仪器)公司的C6000系列,但是,要实现对运算量和实时性要求越来越高的DSP 算法,如对基于分数阶傅立叶变换的Chirp信号检测与估计,合成孔径雷达(SAR)成像,高频地波雷达中的自适应滤波和自适应波束形成等算法,单片DSP 仍然显得力不从心。

这些挑战主要涉及两个主题:一是计算能力,指设备、板卡和系统中分别可用的处理资源。

采用多DSP、多FPGA系统,将是提高运算能力的一个有效途径。

二是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移。

对于一些复杂的信息系统,对海量数据传输的实时性提出了苛刻的要求,多DSP之间、DSP与高速AD采集系统、DSP与FPGA间的高速数据传输,是影响信号处理流程的主要瓶颈之一。

TI公司最新推出的高性能TMS320C6455(下文称C6455)处理器,具有高速运算能力的同时集成了高速串行接口SRIO,方便多DSP以及DSP与FPGA之间的数据传输,在一定程度上满足了高速实时处理和传输的要求。

本文在多DSP+FPGA通用信号处理平台的基础上,深入研究了多DSP间,DSP与FPGA间的SRIO 的数据通信和加载技术的软硬件设计与实现。

这些技术包括了目前SRIO接口的各种应用方式,可作为SRIO接口及C6455开发提供参考[1-3]。

1 C6455特性及SRIO标准介绍C6455是目前单片处理能力最强的新型高性能定点DSP,它是TI 公司基于第三代先进VeloviTI VLIW(超长指令字)结构开发出来的新产品。

最高主频为1.2GHz,16位定点处理能力为9600MMAC/s。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

¾ 使用说明

64K双端口SRAM方案

¾ 原理框图

GPIO[m] GPIO[n]

LSEM# LCS# LOE# LA[15:0] LD[15:0]

RSEM# RCS# ROE# RA[15:0] RD[15:0]

LSSP

W#/R OE# A[15:0] D[15:0]

LW#/R DP SRAM RW#/R

GPIO[13:0] A[15:0] D[15:0]

用 户 电 路

双端口SRAM外存扩充方案

¾ 设计说明

GPIO[13:0]都可以作为双端口SRAM的高位扩展地址,外存容量 可增加到229×64K×16bits,用户可根据需要选择; 其他设计和仲裁与双端口64K外存SRAM扩展方案相同; 用户用DPSRAM的另一个端口。 在BLT操作之前,程序应将外存的高位地址置入GPIO[x:y] ; 在BLT操作之后,程序应将GPIO[x:y] 置为输入; 在BLT操作之前或之后,CS#和SEM#由程序确定; DPSRAM中的旗语协议可以支持更多的操作。

64K单端口SRAM外存方案

¾ 原理框图

LSSP

W#/R OE# A[15:0] D[15:0] CS# SRAM W#/R OE# A[15:0] D[15:0]

User Arbitrator

User Logic

64K单端口SRAM外存方案

¾外部Arbitrator算法

¾ 使用说明

Non_SRAM方案

¾ 原理框图

LSSP

E[i] GPIO[13:0] W#/R OE# D[15:0]

User Logic

Non_SRAM方案

¾ 设计说明

Non_SRAM方案可以理解LSSP配置了无穷大的外存; GPIO[13:0]都可以作为控制微码,用户可以根据需要选择; EV[i]作为送往LSSP的数据有效标志。

LSSP对SRAM的访问的优先最高; CS#=0,也可以如图中虚线可控; W#/R=0时,LSSP对外部写; W#/R=1,OE# =0时,LSSP从外部读; A[15:0]为访问地址输出; BLT操作完成后,程序可以将D[15:0]设为三态; SRAM接口时序请参阅“L结构处理器使用说明”。

单端口SRAM外存扩充方案

¾ 原理框图

LSSP

W#/R OE# GPIO[13:0] A[15:0] D[15:0] CS# SRAM W#/R OE# A[29:16] A[15:0] D[15:0]

User Arbitrator

User Logic

单端口SRAM外存扩充方案

¾ 设计说明

GPIO[13:0]都可以作为SRAM的高位扩展地址,外存容 量可增加到229×64K×16bits,用户可根据需要选择; 其他设计和仲裁与64K外存SRAM方案的相同。 在BLT操作之前,程序应将外存的高位地址置入 GPIO[x:y] ; 在BLT操作之后,程序应将GPIO[x:y] 置为输入。

¾ 使用说明

双端口SRAM外存扩充方案

¾ 原理框图

GPIO[m] GPIO[n] LSEM# LCS# RSEM# RCS#

LSSP

W#/R OE#

LW#/R DP SRAM RW#/R ROE# LOE# LA[29:16] LA[15:0] LD[15:0] RA[29:16] RA[15:0] RD[15:0]

用 户 电 路

64K双端口SRAM方案

¾ 设计说明

Biblioteka 用GPIO[n]作为DPSRAM的CS#控制(其中n为 13:0); 用GPIO[m]作为DPSRAM的SEM#的控制(其中m为 13:0,n≠m); 用户使用DPSRAM的另一个端口。 DPSRAM中的旗语协议可以支持更多的操作; 在BLT操作之前或之后,CS#和SEM#由程序确定。

¾ 使用说明

输出操作

在BLT操作之前,程序应确定微码GPIO[x:y]; 用户逻辑根据微码确定当前BLT写数据的属性。

输入操作

当E[i]有效,读GPIO[x:y]微码,并发起BLT读,同时根据微码确定输 入数据的属性; OE#由低变高表示LSSP完成数据接收。

L结构处理器(LSSP) 高速数据接口设计指导

崔向东

2006年12月

前言

¾ LSSP内置16K×16bits的数据SRAM; ¾ LSSP设置一个高速SRAM接口,用于内存和外部电路之 间的数据交换; ¾ 块传送(BLT)机制执行数据交换的操作; ¾ BLT内存寻址空间为16K,外部寻址空间为64K; ¾ 每次BLT的操作长度为1~16K; ¾ 用GPIO作为扩展地址,可以实现LSSP更大的外部访问空 间; ¾ 关于LSSP的BLT的操作时序请参阅《L结构处理器使用说 明》。