CAT1026ZI-25-GT3中文资料

CAT4139TD-GT3;中文规格书,Datasheet资料

CAT413922 V High Current Boost White LED DriverDescriptionThe CAT4139 is a DC/DC step−up converter that delivers an accurate constant current ideal for driving LEDs. Operation at a fixed switching frequency of 1 MHz allows the device to be used with small value external ceramic capacitors and inductor. LEDs connected in series are driven with a regulated current set by the external resistor R1. The CAT4139 is ideal for driving parallel strings of up to five white LEDs in series or up to 22 V.LED dimming can be done by using a DC voltage, a logic signal, or a pulse width modulation (PWM) signal. The shutdown input pin allows the device to be placed in power−down mode with “zero”quiescent current.In addition to thermal protection and overload current limiting, the device also enters a very low power operating mode during “Open LED” fault conditions. The device is housed in a low profile (1mm max height) 5−lead TSOT−23 package for space critical applications. Features•Switch Current Limit 750 mA•Drives LED Strings up to 22 V•Up to 87% Efficiency•Low Quiescent Ground Current 0.6 mA•1 MHz Fixed Frequency Low Noise Operation•Soft Start “In−rush” Current Limiting•Shutdown Current Less than 1 m A•Open LED Overvoltage Protection•Automatic Shutdown at 1.9 V (UVLO)•Thermal Overload Protection•TSOT−23 5−Lead (1 mm Max Height)•These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS CompliantApplications•GPS Navigation Systems•Portable Media Players•Handheld DevicesTSOT−23TD SUFFIXCASE 419AEPIN CONNECTIONSMARKING DIAGRAMDevice Package Shipping ORDERING INFORMATIONCAT4139TD−GT3(Note 1)TSOT−23(Pb−Free)3,000/Tape & Reel TP = Specific Device CodeY = Production Year (Last Digit)M = Production Month (1−9, A, B, C)(Top View)VINSHDNSWGNDFB1TPYM1.NiPdAu Plated Finish (RoHS−compliant)Figure 1. Typical Application Circuit9 strings at D: Central CMSH1−40 (rated 40 V)Table 1. ABSOLUTE MAXIMUM RATINGSParametersRatings Units VIN, FB Voltage −0.3 to +7V SHDN Voltage −0.3 to +7V SW Voltage−0.3 to +40V Storage Temperature Range −65 to +160_C Junction Temperature Range −40 to +150_C Lead Temperature300_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Table 2. RECOMMENDED OPERATING CONDITIONS (Typical application circuit with external components is shown above.)ParametersRange Units VINup to 5.5V SW pin voltage0 to 22V Ambient Temperature Range (Note 2)−40 to +85_C2.TSOT23−5 package thermal resistance q JA = 135°C/W when mounted on board over a ground plane.Table 3. DC ELECTRICAL CHARACTERISTICS(V IN = 3.6 V, ambient temperature of 25°C (over recommended operating conditions unless otherwise specified))Symbol Parameter Test Conditions Min Typ Max UnitsI Q Operating Current V FB= 0.2 VV FB= 0.4 V (not switching)0.60.11.50.6mAI SD Shutdown Current V SHDN = 0 V0.11m A V FB FB Pin Voltage9 x 3 LEDs, I OUT = 180 mA285300315mV I FB FB pin input leakage1m AI LED Programmed LED Current R1 = 10 WR1 = 3 W 28.53010031.5mAV IH V IL SHDN Logic HighSHDN Logic LowEnable Threshold LevelShutdown Threshold Level0.40.80.71.5VF SW Switching Frequency0.8 1.0 1.3MHzI LIM Switch Current Limit V IN = 3.6 VV IN = 5 V 600750mAR SW Switch “On” Resistance I SW = 100 mA 1.0 2.0W I LEAK Switch Leakage Current Switch Off, V SW = 5 V15m A T SD Thermal Shutdown150°C T HYST Thermal Hysteresis20°C V UVLO Under−voltage lock out (UVLO) Threshold 1.9V V OV−DET Over−voltage detection threshold2324V V OCL Output Clamp voltage“Open LED”29VDC Maximum duty cycleMinimum duty cycle 9216%Figure 2. Quiescent Current vs. V IN(Not Switching)Figure 3. Quiescent Current vs. V IN(Switching)INPUT VOLTAGE (V)INPUT VOLTAGE (V)501001502005.04.54.03.53.000.51.01.52.0Figure 4. FB Pin Voltage vs. TemperatureFigure 5. FB Pin Voltage vs. Output CurrentTEMPERATURE (°C)OUTPUT CURRENT (mA)10015050−5029729830130230320018016014012010080290295300305310Figure 6. Switching Frequency vs. SupplyVoltage Figure 7. Switch ON Resistance vs.Input VoltageINPUT VOLTAGE (V)4.0 4.53.53.00.80.91.01.11.2Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )F B P I N V O L T A G E (m V )F B P I N V O L T AG E (m V )S W I T C H I N G F R E Q U E N C Y (M H z )INPUT VOLTAGE (V)4.54.05.03.53.000.51.01.52.0S W I T C H R E S I S T A N C E (W )5.5299300 5.0 5.55.5Figure 8. Output Current vs. Input VoltageFigure 9. Output Current RegulationINPUT VOLTAGE (V)INPUT VOLTAGE (V)5.04.54.03.53.0100120140160180200 5.55.14.94.74.5−2.0−0.500.52.0Figure 10. Efficiency vs. Output Current Figure 11. Efficiency vs. Input VoltageOUTPUT CURRENT (mA)INPUT VOLTAGE (V)2001801601201008075808590957580859095Figure 12. Power −up at 180 mA Figure 13. Switching WaveformL E D C U R R E N T (m A )I O U T V A R I A T I O N (%)E F F I C I E N C Y (%)E F F I C I E N C Y (%)5.3140 5.5−1.0−1.51.01.5Figure 14. Maximum Output CurrentFigure 15. Shutdown VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)501001502503000.20.61.0Figure 16. Switch Current LimitINPUT VOLTAGE (V)600650750800900M A X O U T P U T C U R R E N T (m A )S H U T D O W N V O L T A G E (V )S W I T C H C U R R E N T L I M I T (m A )0.40.8200700850VIN is the supply input for the internal logic. The device is compatible with supply voltages down to 2.8 V and up to 5.5V. It is recommended that a small bypass ceramic capacitor (4.7 m F) be placed between the VIN and GND pins near the device. If the supply voltage drops below 1.9 V, the device stops switching.SHDN is the shutdown logic input. When the pin is tied to a voltage lower than 0.4 V, the device is in shutdown mode, drawing nearly zero current. When the pin is connected to a voltage higher than 1.5 V, the device is enabled.GND is the ground reference pin. This pin should be connected directly to the ground plane on the PCB.SW pin is connected to the drain of the internal CMOS power switch of the boost converter. The inductor and the Schottky diode anode should be connected to the SW pin. Traces going to the SW pin should be as short as possible with minimum loop area. An over−voltage detection circuit is connected to the SW pin. When the voltage reaches 24V, the device enters a low power operating mode preventing the SW voltage from exceeding the maximum rating.FB feedback pin is regulated at 0.3 V. A resistor connected between the FB pin and ground sets the LED current according to the formula:I LED+0.3VR1The lower LED cathode is connected to the FB pin.Table 4. PIN DESCRIPTIONSPin #Name Function 1SW Switch pin. This is the drain of the internal power switch.2GND Ground pin. Connect the pin to the ground plane.3FB Feedback pin. Connect to the last LED cathode.4SHDN Shutdown pin (Logic Low). Set high to enable the driver.5VIN Power Supply input.The CAT4139 is a fixed frequency (1 MHz), low noise, inductive boost converter that provides a constant current with excellent line and load regulation. The device uses a high−voltage CMOS power switch between the SW pin and ground to energize the inductor. When the switch is turned off, the stored energy in the inductor is released into the load via the Schottky diode.The on/off duty cycle of the power switch is internally adjusted and controlled to maintain a constant regulated voltage of 0.3 V across the feedback resistor connected to the feedback pin (FB). The value of the resistor sets the LED current accordingly (0.3 V/R1).During the initial power−up stage, the duty cycle of the internal power switch is limited to prevent excessive in−rush currents and thereby provide a “soft−start” mode of operation.In the event of an “Open LED” fault condition, where the feedback control loop becomes open, the output voltage will continue to increase. Once this voltage exceeds 24 V, an internal protection circuit will become active and place the device into a very low power safe operating mode. Thermal overload protection circuitry has been included to prevent the device from operating at unsafe junction temperatures above 150°C. In the event of a thermal overload condition the device will automatically shutdown and wait till the junction temperatures cools to 130°C before normal operation is resumed.Application Information External Component SelectionCapacitorsThe CAT4139 only requires small ceramic capacitors of 4.7m F on the input and 1 m F on the output. Under normal condition, a 4.7 m F input capacitor is sufficient. For applications with higher output power, a larger input capacitor of 10 m F may be appropriate. X5R and X7R capacitor types are ideal due to their stability across temperature range.InductorA 22 m H inductor is recommended for most of the CAT4139 applications. In cases where the efficiency is critical, inductances with lower series resistance are preferred. Inductors with current rating of 800mA or higher are recommended for most applications. Sumida CDRH6D28−220 22 m H inductor has a rated current of 1.2A and a series resistance (D.C.R.) of 128 m W typical. Schottky DiodeThe current rating of the Schottky diode must exceed the peak current flowing through it. The Schottky diode performance is rated in terms of its forward voltage at a given current. In order to achieve the best efficiency, this forward voltage should be as low as possible. The response time is also critical since the driver is operating at 1MHz. Central Semiconductor Schottky rectifier CMSH1−40 (1A rated) is recommended for most applications.LED Current SettingThe LED current is set by the external resistor R1 connected between the feedback pin (FB) and ground. The formula below gives the relationship between the resistor and the current:R1+0.3VLED currentTable 5. RESISTOR R1 AND LED CURRENTLED Current (mA)R1 (W)20152512301010033001Open LED ProtectionIn the event of an “Open LED” fault condition, the CAT4139 will continue to boost the output voltage with maximum power until the output voltage reaches approximately 24 V . Once the output exceeds this level, the internal circuitry immediately places the device into a very low power mode where the total input power is limited to about 6 mW (about 1.6 mA input current with a 3.6V supply). The SW pin clamps at a voltage below its maximum rating of 40 V . There is no need to use an external zener diode between VOUT and the FB pin. A 35 V rated C2 capacitor is required to prevent any overvoltage damage in the open LED condition.Figure 18. Open LED Protection CircuitSchottky 40 V (Central CMSH05−4)V Figure 19. Open LED Disconnect and ReconnectFigure 20. Open LED DisconnectFigure 21. Open LED Supply Current Figure 22. Open LED Output VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)5.55.04.54.03.53.01.01.52.02.55.55.04.54.03.53.01520253035I N P U T C U R R E N T (m A )O U T P U T V O L T A G E (V )Dimming ControlThere are several methods available to control the LED brightness.PWM Signal on the SHDN PinLED brightness dimming can be done by applying a PWM signal to the SHDN input. The LED current is repetitively turned on and off, so that the average current is proportional to the duty cycle. A 100% duty cycle, with SHDN always high, corresponds to the LEDs at nominal current. Figure23 shows a 1 kHz signal with a 50% duty cycle applied to the SHDN pin. The recommended PWM frequency range is from 100Hz to 2 kHz.Figure 23. Switching Waveform with 1 kHzPWM on SHDN Filtered PWM SignalA filtered PWM signal used as a variable DC voltage can control the LED current. Figure 24 shows the PWM control circuitry connected to the CAT4139 FB pin. The PWM signal has a voltage swing of 0 V to 2.5 V. The LED current can be dimmed within a range from 0 mA to 20 mA. The PWM signal frequency can vary from very low frequency and up to 100 kHz.Figure 24. Circuit for Filtered PWM Signal0 V2.5 VW PWMSignalVA PWM signal at 0 V DC, or a 0% duty cycle, results in a max LED current of about 22 mA. A PWM signal with a 93% duty cycle or more, results in an LED current of 0mA.Figure 25. Filtered PWM Dimming (0 V to 2.5 V)LEDCURRENT(mA)2520151050102030405060708090100PWM DUTY CYCLE (%)分销商库存信息: ONSEMICAT4139TD-GT3。

热回收转轮 操作和维护手册说明书

热回收转轮操作和维护手册DTR-VS-ver.5.0 (09.2017)IEC/EN 60439-1 +AC Low voltage switchgears and controllersVTS 保留非预先通知而修改的权利目录1. 介绍 (2)2. 技术数据 (3)2.1. 驱动单元基本参数 (3)2.1.1. 结构 (3)2.1.2. 驱动器操作 (3)2.2. 技术规范 (4)2.2.1. 结构 (4)2.2.2. 操作参数 (4)2.2.3. 元器件的额定参数 (4)2.3. 驱动单元的安装和配置 (5)2.4. 含变频器和VTS自控的驱动单元安装和配置 (5)2.4.1. 热回收转轮驱动回路的接线图 (5)2.4.2. 驱动单元的安装和配置 (6)2.4.3. 电机防护 (7)2.5. 自控系统的驱动单元安装和配置 (7)2.5.1. 热回收转轮驱动回路的接线图 (7)2.5.2. 热回收转轮驱动单元的控制 (8)2.5.3. 变频器配置例子 (8)2.5.4. 电机保护 (9)2.6. 系统中带有EC调速器的驱动单元安装和配置 (10)2.6.1. EC调节器的ModBus RTU/RS485参数 (11)2.6.2. 通过MODBUS设置旋转速度 (12)2.7. 安装建议 (13)3. 保存和运输 (14)4. 启动 (14)5. 维护 (15)5.1. 热回收转轮和驱动皮带 (15)5.2. 转轮密封 (16)1. 介绍本文档描述了关于热回收转轮的参数、运输、保管和服务内容。

●在进行任何动作前,务必详细阅读本文档。

2. 技术数据2.1. 驱动单元基本参数2.1.1. 结构本驱动单元是每个热回收转轮的完整部件。

基本构成如下:●变频器/EC电机控制器(取决于不同的版本或区域)●热回收轮芯●轮芯驱动皮带传动装置●电机减速器-马达带有减速齿轮2.1.2. 驱动器操作驱动单元用于启动并平缓地控制热回收转轮,使得速度在3-10rpm范围内。

CAT4104V-GT3;CAT4104VP2-GT3;中文规格书,Datasheet资料

CAT4104700 mA Quad ChannelConstant Current LED DriverDescriptionThe CAT4104 provides four matched low dropout current sinks to drive high −brightness LED strings up to 175 mA per channel. The LED channel current is set by an external resistor connected to the RSET pin. The LED pins are compatible with high voltage up to 25 V supporting applications with long strings of LEDs.The EN/PWM logic input supports the device enable and high frequency external Pulse Width Modulation (PWM) dimming control.Thermal shutdown protection is incorporated in the device to disable the LED outputs whenever the die temperature exceeds 150°C.The device is available in the 8−pad TDFN 2 mm x 3 mm package and the SOIC 8−Lead 150 mil wide package.Features•4 Matched LED Current Sinks up to 175 mA •Up to 25 V Operation on LED Pins•Low Dropout Current Source (0.4 V at 175 mA)•LED Current Set by External Resistor•High Frequency PWM Dimming via EN/PWM •“Zero” Current Shutdown Mode •Thermal Shutdown Protection•TDFN 8−pad 2 x 3 mm and SOIC 8−lead Packages•These Devices are Pb −Free, Halogen Free/BFR Free and are RoHS CompliantApplications•Automotive Lighting•General and Architectural Lighting •LCD BacklightFigure 1. Typical Application Circuit768 WONOFFSOIC −8V SUFFIX CASE 751BD PIN CONNECTIONSMARKING DIAGRAMSCAT4104V = CAT4104VHC = CAT4104VP2SOIC 8−lead (Top View)Device Package Shipping ORDERING INFORMATIONCAT4104V −GT3(Note 1)SOIC −8(Pb −Free)3,000/Tape & Reel 1.Lead Finish is NiPdAuCAT4104V TDFN −8VP SUFFIX CASE 511AKCAT4104VP2−GT3(Note 1)TDFN −8(Pb −Free)3,000/Tape & ReelGNDVIN RSET LED4LED3LED2LED11EN/PWM GNDVINRSET LED4LED3LED2LED1EN/PWM TDFN 8−pad (Top View)HC1Table 1. ABSOLUTE MAXIMUM RATINGSParameter Rating Unit VIN, RSET, EN/PWM Voltages−0.3 to 6V LED1, LED2, LED3, LED4 Voltages−0.3 to 25V Storage Temperature Range−65 to +160_C Junction Temperature Range−40 to +150_C Lead Temperature300_C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Table 2. RECOMMENDED OPERATING CONDITIONSParameter Rating Unit VIN 3.0 to 5.5V Voltage applied to LED1 to LED4, outputs off up to 25V Voltage applied to LED1 to LED4, outputs on up to 6 (Note 2)V Ambient Temperature Range−40 to +85_CI LED per LED pin10 to 175mA2.Keeping LEDx pin voltage below 6 V in operation is recommended to minimize thermal dissipation in the package.NOTE:Typical application circuit with external components is shown on page 1.Table 3. ELECTRICAL OPERATING CHARACTERISTICS (Min and Max values are over the recommended operating conditions= 25°C.)unless specified otherwise. Typical values are at VIN = 5.0 V, TTable 4. RECOMMENDED EN/PWM TIMING (Min and Max values are over the recommended operating conditions unless specified otherwise. Typical values are at VIN = 5.0 V, T AMB = 25°C.)Symbol NameConditions MinTyp MaxUnits T PS Turn −On time, EN/PWM rising to I LED from shutdownI LED = 175 mA I LED = 80 mA 1.51.3m s T P1Turn −On time, EN/PWM rising to I LED I LED = 175 mA 600ns T P2Turn −Off time, EN/PWM falling to I LED I LED= 175 mA I LED = 80 mA 400300ns T R LED rise time I LED = 175 mA I LED = 80 mA 700440ns T F LED fall time I LED = 175 mA I LED = 80 mA360320ns T LO EN/PWM low time 1m s T HI EN/PWM high time5m s T PWRDWNEN/PWM low time to shutdown delay48msFigure 2. CAT4104 EN/PWM TimingEN/PWM OperationThe EN/PWM pin has two primary functions. One function enables and disables the device. The other function turns the LED channels on and off for PWM dimming control. The device has a very fast turn −on time (from EN/PWM rising to LED on) and allows “instant on” when dimming LED using a PWM signal.Accurate linear dimming is compatible with PWM frequencies from 100 Hz to 5 kHz for PWM duty cycle down to 1%. PWM frequencies up to 50 kHz can be supported for duty cycles greater than 10%.When performing a combination of low frequencies and small duty cycles, the device may enter shutdown mode.This has no effect on the dimming accuracy, because the turn −on time T PS is very short, in the range of 1 m s.To ensure that PWM pulses are recognized, pulse width low time T LO should be longer than 1 m s. The CAT4104enters a “zero current” shutdown mode after a 4 ms delay (typical) when EN/PWM is held low.Figure 3. Quiescent Current vs. Input Voltage(RSET Open)Figure 4. Quiescent Current vs. RSET CurrentINPUT VOLTAGE (V)RSET CURRENT (mA)5.55.04.54.03.53.00.40.60.81.01.22.01.51.00.5002468Figure 5. Quiescent Current vs. Input Voltage(Full Load)Figure 6. LED Dropout vs. LED Pin VoltageINPUT VOLTAGE (V)LED PIN VOLTAGE (V)5.55.04.54.03.53.05.05.56.06.57.0 1.00.80.60.40.2004080120160200Figure 7. LED Line RegulationFigure 8. LED Current Change vs.TemperatureVIN (V)TEMPERATURE (°C)5.55.04.54.03.53.00408012016020012080400−4004080120160200Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )L E D C U R R E N T (m A )L E D C U R R E N T (m A )L E D C U R R E N T (m A )No LoadFull LoadFigure 9. LED Current vs. RSET ResistorFigure 10. LED Current vs. LED Pin VoltageRSET (k W )LED PIN VOLTAGE (V)1010.1101001000654321004080120160200Figure 11. RSET Pin Voltage vs. Input VoltageFigure 12. RSET Pin Voltage vs. TemperatureINPUT VOLTAGE (V)TEMPERATURE (°C)5.55.04.54.03.53.01.101.151.201.251.3012080400−401.101.151.201.251.30Figure 13. LED Off Current vs. LED PinVoltageLED PIN VOLTAGE (V)0.20.40.60.81.0L E D C U R R E N T (m A )L E D C U R R E N T (m A )R S E T V O L T A G E (V )R S E T V O L T A G E (V )L E D O F F C U R R E N T (m A )Figure 14. EN/PWM Pull −down Current vs.V EN/PWMFigure 15. EN/PWM Threshold vs. VINENABLE VOLTAGE (V)INPUT VOLTAGE (V)54321005101520250.40.60.81.01.21.4Figure 16. Power Up from Shutdown Figure 17. Power DownFigure 18. PWM 200 Hz, 1% Duty CycleE N A B L E C U R R E N T (m A )E N A B L E T H R E S H O L D (V )Table 5. PIN DESCRIPTIONSNamePinSOIC 8−LeadPinTDFN 8−Lead FunctionLED111LED1 cathode terminalLED222LED2 cathode terminalLED333LED3 cathode terminalLED444LED4 cathode terminalGND5 5 and TAB Ground referenceEN/PWM66Device enable input and PWM control VIN77Device supply pinRSET88LED current set pin for the LED channels Pin FunctionVIN is the supply pin for the device. A small 0.1 m F ceramic bypass capacitor is optional for noisy environments. Whenever the input supply falls below the under−voltage threshold, all LED channels are automatically disabled. EN/PWM is the enable and one wire dimming input for all LED channels. Guaranteed levels of logic high and logic low are set at 1.3 V and 0.4 V respectively. When EN/PWM is initially taken high, the device becomes enabled and all LED currents are set at a gain of 100 times the current in RSET. To place the device into zero current shutdown mode, the EN/PWM pin must be held low for 4 ms typical.LED1 to LED4 provide individual regulated currents for each of the LED cathodes. There pins enter a high impedance zero current state whenver the device is placed in shutdown mode.RSET pin is connected to an external resistor to set the LED channel current. The ground side of the external resistor should be star connected to the GND of the PCB. The pin source current mirrors the current to the LED sinks. The voltage at this pin is regulated to 1.2 V.GND is the ground reference for the device. The pin must be connected to the ground plane on the PCB.TAB (TDFN 8−Lead Only) is the exposed pad underneath the package. For best thermal performance, the tab should be soldered to the PCB and connected to the ground plane.Block DiagramFigure 19. CAT4104 Functional Block Diagram4 Current Sink RegulatorsVINBasic OperationThe CAT4104 has four tightly matched current sinks to regulate LED current in each channel. The LED current in the four channels is mirrored from the current flowing through the RSET pin according to the following formula:I LED ^1001.2V R SETTable 6 shows standard resistor values for RSET and the corresponding LED current.Table 6. RSET RESISTOR SETTINGSLED Current [mA]RSET [k W ]20 6.3460 2.10100 1.271750.768Tight current regulation for all channels is possible over a wide range of input voltages and LED voltages due to independent current sensing circuitry on each channel.Each LED channel needs a minimum of 400 mV headroom to sink constant regulated current up to 175 mA.If the input supply falls below 2 V , the under −voltage lockout circuit disables all LED channels. Any unused LED channels should be left open.For applications requiring more than 175 mA current,LED channels can be tied together to sink up to a total of 700 mA from the one device.The LED channels can withstand voltages up to 25 V . This makes the device ideal for driving long strings of high power LEDs from a high voltage source.Application InformationSingle 12 V SupplyThe circuit shown in Figure 20 shows how to power the LEDs from a single 12 V supply using the CA T4104. Three external components are needed to create a lower voltage necessary for the VIN pin (below 5.5 V). The resistor R2 and zener diode Z provide a regulated voltage while the quiescent current runs through the N −Channel transistor M.The recommended parts are ON Semiconductor MM3Z6V2zener diode (in SOD −323 package), and 2N7002L N −Channel transistor (in SOT23).Figure 20. Single Supply Driving 12 LEDsDaylight DetectionThe circuit in Figure 21 shows how to use CA T4104 in an automatic light sensor application. The light sensor allows the CAT4104 to be enabled during the day and disabled during the night. Two external components are required to configure the part for ambient light detection and conserve power. Resistor R1 sets the bias for the light sensor. The recommended part is Microsemi LX1972 light sensor. For best performance, the LED light should not interfere with the light sensor.Figure 21. Daylight DetectionNightlight DetectionThe circuit shown in Figure 22 illustrates how to use the CAT4104 in an automatic night light application. The light sensor allows the CA T4104 to be disabled during the day and enabled during the night. Five external components are needed to properly configure the part for night detection.Resistor R3 limits the quiescent current through the N −Channel transistor M. Resistors R1 and R2 act as a voltage divider to create the required voltage to turn ontransistor M, which disables the CAT4104. The recommended parts are ON Semiconductor 2N7002L N −Channel transistor (in SOT23) and the Microsemi LX1972 light sensor. For best performance, the LED light should not interfere with the light sensor.Figure 22. Nightlight DetectionLED Current DeratingThe circuit shown in Figure 23 provides LED temperature derating to avoid over −driving the LED under high ambient temperatures, by reducing the LED current to protect the LED from over −heating. The positive thermo coefficient (PTC) thermistor RPTC is used for temperature sensing and should be located near the LED. As the temperature of RPTC increases, the gate voltage of the MOSFET M1decreases. This causes the transistor M1 on −resistance to increase which results in a reduction of the LED current. The circuit is powered from a single VCC voltage of 5 V . The recommended parts are Vishay 70°C thermistor PTCSS12T071DTE and ON Semiconductor 2N7002L N −Channel transistor (in SOT23).The PCB and heatsink for the LED should be designed such that the LED current is constant within the normal temperature range. But as soon as the ambient temperature exceeds a max threshold, the LED current drops to protect the LEDs from overheating.Figure 23. LED Current DeratingPower DissipationThe power dissipation (P D) of the CAT4104 can be calculated as follows:P D+(V IN I IN))S(V LEDN I LEDN)where V LEDN is the voltage at the LED pin, and I LEDN is theLED current. Combinations of high V LEDN voltage and high ambient temperature can cause the CAT4104 to enter thermal shutdown. In applications where V LEDN is high, a resistor can be inserted in series with the LED string to lower the power dissipation P D.Thermal dissipation of the junction heat consists primarily of two paths in series. The first path is the junction to the case (q JC) thermal resistance which is defined by the package style, and the second path is the case to ambient (q CA) thermal resistance, which is dependent on board layout. The overall junction to ambient (q JA) thermal resistance is equal to:q JA+q JC)q CAFor a given package style and board layout, the operating junction temperature T J is a function of the power dissipation P D, and the ambient temperature, resulting in the following equation:T J+T AMB)P D(q JC)q CA)+T AMB)P D q JA When mounted on a double−sided printed circuit board with two square inches of copper allocated for “heat spreading”, the resulting q JA is about 90°C/W for the TDFN−8 package, and 160°C/W for the SOIC−8 package. For example, at 60°C ambient temperature, the maximum power dissipation for the TDFN−8 is calculated as follow: P Dmax+T Jmax*T AMBq JA+150*6090+1WRecommended LayoutA small ceramic capacitor should be placed as close as possible to the driver VIN pin. The RSET resistor should have a Kelvin connection to the GND pin of the CAT4104. The board layout should provide good thermal dissipation through the PCB. In the case of the CAT4104VP2 in the TDFN package, a via can be used to connect the center tab to a large ground plane underneath as shown on Figure 24.Figure 24. CAT4104 Recommended Layout分销商库存信息:ONSEMICAT4104V-GT3CAT4104VP2-GT3。

atc精选中文手册

A T24C256中文资料2009-11-1509:43特性与1MHzI2C总线兼容到伏工作电压范围低功耗CMOS技术写保护功能当WP为高电平时进入写保护状态64字节页写缓冲器自定时擦写周期100,000编程/擦写周期可保存数据100年8脚DIPSOIC封装温度范围商业级工业级和汽车级概述CAT24WC256是一个256K位串行CMOSE2PROM内部含有32768个字节每字节为8位CATALYST公司的先进CMOS技术实质上减少了器件的功耗CAT24WC256有一个64字节页写缓冲器该器件通过I2C总线接口进行操作极限参数工作温度工业级-55+125商业级0+75贮存温度-65+150各管脚承受电压+Vcc管脚承受电压+封装功率损耗Ta=焊接温度(10秒)300口输出短路电流100mA功能描述CAT24WC256支持I2C总线数据传送协议I2C总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL串行时钟CAT24WC256串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP写保护当WP脚连接到Vcc所有内存变成写保护只能读当WP引脚连接到Vss或悬空允许器件进行读/写操作A0A1器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4个CAT24WC256器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C总线协议I2C总线协议定义如下1只有在总线空闲时才允许启动数据传送2在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8位从器件地址的高5位固定为10100见图5接下来的2位A1A0为器件的地址位最多可以连接4个器件到同一总线上这些位必须与硬连线输入脚A1A0相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA线CAT24WC256再根据读写控制位R/W的状态进行读或写操作应答信号I2C总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9个时钟周期时将SDA线拉低表示其已收到一个8位数据CAT24WC256在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8位字节之后响应一个应答信号当CAT24WC256工作于读模式时在发送一个8位数据后释放SDA线并监视一个应答信号一旦接收到应答信号CAT24WC256继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W位置0给从器件在从器件送回应答信号后主器件发送两个8位地址字写入CAT24WC256的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256最多可以写入64个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63个字节每发送一个字节后CAT24WC256将响应一个应答位且内部低6位地址加1高位地址保持不变如果主器件在发送停止信号之前发送大于64个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256正在进行内部写操作将不会发送应答信号如果CAT24WC256已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256读操作的初始化方式和写操作时一样仅把R/W位置为1有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1也就是说如果上次读/写的操作地址为N则立即读的地址从地址N+1开始如果N=E此处E=32767则计数器将翻转到0且继续输出数据CAT24WC256接收到从器件地址信号后R/W位置1它首先发送一个应答信号然后发送一个8位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256应答之后主器件重新发送起始信号和从器件地址此时R/W位置1CAT24WC256响应并发送应答信号然后输出所要求的一个8位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256发送完一个8位字节数据后主器件产生一个应答信号来响应告知CAT24WC256主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256将发送一个8位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256输出的数据按顺序由N到N+1输出读操作时地址计数器在CAT24WC256整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E此处E=32767计数器将翻转到零并继续输出数据字节。

深圳市数冠电子科技有限公司PT2559B L2光敏三极管说明书

产品说明书侧面感光双晶NPN光敏三极管PT2559B/L2⏹描述PT2559B/L2是一款高速高灵敏度双晶NPN型光敏三极管侧面感光结构,采用黑色环氧材料封装,使产品适用于红外波段的感光,对可见光有滤波作用。

⏹特点●快速响应●高感光灵敏度●无铅环保⏹应用●电机测速●计数器●鼠标●红外传感应用系统⏹封装尺寸感光面芯片尺寸和排列发射极 A集电极发射极 B注: 1. 所有尺寸单位位毫米(括号内单位为英寸)2. 未标明误差的精度为± 0.25毫米(.01英寸)⏹极限参数(Ta=25℃)参数名称符号参考值单位集电极-发射极电压V CEO60V发射极-集电极电压V ECO6V集电极电流Ic20mA焊接温度*1Tsol260℃工作温度Topr-20~+85℃存储温度Tstg-40~+85℃说明:*1:焊接时间≦5seconds.⏹光电参数(Ta=25℃)参数名称符号最小典型最大单位测试条件频谱范围λ0.5840--1100nm感光峰值波长λP--940--nm集电极–发射极击穿电压BV CEO60----VIc=500μA,Ib=0发射极-集电极击穿电压BV ECO6----V Ic=50μA,Ib=0集电极暗电流ICEO----50nA V CE=10V, H=0mw/cm2集电极-发射极饱和电压V CE(S)---0.2VIc=5mA,I B=1mA集电极电流I C(on)0.7 1.5--mA Ee=1mW/cm2, V CE=5V直流电流放大倍数HFE1200--1800V CE=5V, IC=2mA上升/下降时间t r/t f--15/15μS V CE=5V, I C=1mA R L=1000ΩAmbient Temperature Ta(°C)C o l l e c t o r P o w e rD i s s i p a t i o n (m W )40100020406080100-20-40608020300Ambient Temperature Ta(°C)R e l a t i v e C o l l e c t o r C u r r e n t (%)40608060100160Vce=5V204080120140Ee=1mW/cm 2102050701008060200600Wavelength(nm)R e l a t i v e S p e c t r a l S e n s i t i v i t y (%)Ta=25°407008009001000110012001Irradiance Ee(mW/cm )C o l l e c t o r C u r r e n t I c (m A )1.530.51010101010210Vce=5VT =25 Ca °2 特性曲线图图.1集电极耗散功率与环境温度图.2相对频谱灵敏度图.3相对集电极电流与环境温度图.4集电极电流与辐照度25Ambient Temperature (°C)C o l l e c t o rD a r k C u r r e n t IC E O(n A )50751000.1110100Vce=20V 0Collector-Emitter Voltage V CE (V)C o l l e c t o r C u r r e n t I c (m A )12340.51.01.52.02.53.03.5Ee=0.5mW/cm2Ee=0.75mW/cm 2Ee=1.0mW/cm 2Ee=1.25mW/cm 2Ee=1.5mW/cm2图.5集电极暗电流与环境温度图.6集电极电流与集射电压注意事项:1.我公司保留更改产品材料和以上说明书的权利,更改以上产品说明书恕不另行通知。

CAT6219-285TD-GT3中文资料

GND is the ground reference for the LDO. The pin must be connected to the ground plane on the PCB.

BYP is the reference bypass pin. An optional 0.01μF capacitor can be connected between BYP pin and GND to reduce the output noise and enhance the PSRR at high frequency.

VOUT is the LDO regulator output. A small 2.2μF ceramic bypass capacitor is required between the VOUT pin and ground. For better transient response, its value can be increased to 4.7μF.

The capacitor should be located near the device. For the SOT23-5 package, a continuous 500mA output current may turn-on the thermal protection. A 250Ω internal shutdown switch discharges the output capacitor in the no-load condition.

CAT2300VP2-GT3;中文规格书,Datasheet资料

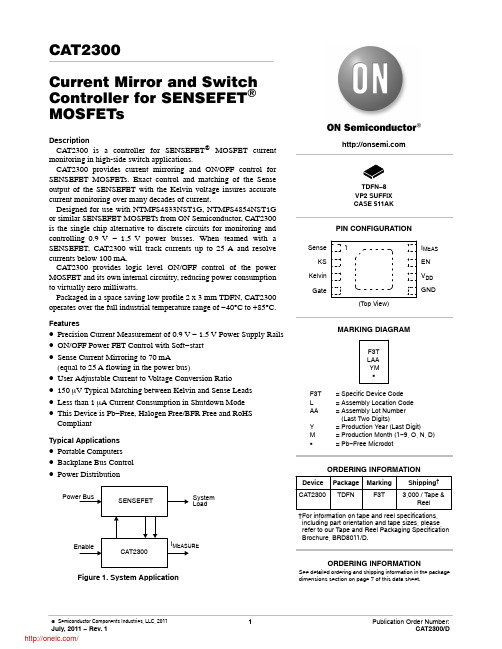

CAT2300Current Mirror and Switch Controller for SENSEFET )MOSFETsDescriptionCAT2300 is a controller for SENSEFET ® MOSFET current monitoring in high-side switch applications.CAT2300 provides current mirroring and ON/OFF control for SENSEFET MOSFETs. Exact control and matching of the Sense output of the SENSEFET with the Kelvin voltage insures accurate current monitoring over many decades of current.Designed for use with NTMFS4833NST1G, NTMFS4854NST1G or similar SENSEFET MOSFETs from ON Semiconductor, CA T2300is the single chip alternative to discrete circuits for monitoring and controlling 0.9 V − 1.5 V power busses. When teamed with a SENSEFET, CAT2300 will track currents up to 25 A and resolve currents below 100 mA.CAT2300 provides logic level ON/OFF control of the power MOSFET and its own internal circuitry, reducing power consumption to virtually zero milliwatts.Packaged in a space saving low profile 2 x 3 mm TDFN, CAT2300operates over the full industrial temperature range of −40°C to +85°C.Features •Precision Current Measurement of 0.9 V − 1.5 V Power Supply Rails •ON/OFF Power FET Control with Soft −start •Sense Current Mirroring to 70 mA (equal to 25 A flowing in the power bus)•User Adjustable Current to V oltage Conversion Ratio•150 m V Typical Matching between Kelvin and Sense Leads •Less than 1 m A Current Consumption in Shutdown Mode •This Device is Pb −Free, Halogen Free/BFR Free and RoHS CompliantTypical Applications•Portable Computers •Backplane Bus Control •Power DistributionFigure 1. System ApplicationSystem LoadSee detailed ordering and shipping information in the package dimensions section on page 7 of this data sheet.ORDERING INFORMATIONPIN CONFIGURATIONTDFN −8VP2 SUFFIX CASE 511AKSense KS Kelvin Gate1GNDV DD EN I MEAS (Top View)MARKING DIAGRAMF3T = Specific Device Code L = Assembly Location Code AA = Assembly Lot Number (Last Two Digits)Y = Production Year (Last Digit)M = Production Month (1−9, O, N, D)G= Pb −Free MicrodotF3T LAA YM GDevice Package Shipping †ORDERING INFORMATIONCAT2300TDFN3,000 / Tape &ReelMarking F3T†For information on tape and reel specifications,including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.SenseKSKelvin Gate ENFigure 2. Simplified Block DiagramI MEASV DDTable 1. PIN FUNCTION DESCRIPTIONPin No.Pin Name Function1Sense Connects to Sense pin of SENSEFET and directs sensed current to IMEAS output.2KS Kelvin Sense; a Kelvin connection for the current mirror control amplifier. This connection must be made directly to Sense on the SENSEFET package. Do not share any trace length with CAT2300’s Sense lead.3Kelvin Connects to Kelvin pin of the SENSEFET. Serves as the reference point for Sense lead biasing.4Gate Connects to Gate of the SENSEFET and controls SENSEFET operation.5GND Electrical ground for IC.6V DD External voltage supply for driving the gate of the SENSEFET and power supply for CAT2300 internal circuitry via an internal voltage regulator.7EN Enable: High true logic input. Turns ON SENSEFET and CAT2300’s internal circuitry. A logic LOW on EN grounds Gate, shutting off the SENSEFET and shuts down the internal current source and mirroring circuitry.8I MEASSensed current output. A resistor between I MEAS and ground develops a voltage proportional to the current flowing through the SENSEFET.PADBackside paddle is internally connected to GND. This pad may be left floating but if connected with PCB it must be to the ground plane of circuitry which is also grounded.Table 2. ABSOLUTE MAXIMUM RATINGS (Note 1)ParameterSymbol Value Unit V DD V DD6.5V Gate±15mA V K , EN, Sense, KS, Kelvin, I MEAS 6.5V Junction Temperature150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Guaranteed by design.Table 3. RECOMMENDED OPERATING CONDITIONSParameterSymbol Value Unit V K V K 0.9 to 1.5V V DDV DD 5V Maximum Junction Temperature T JUNCTION 125°C Ambient Temperature RangeT AMBIENT−40 to +85°CTable 4. PACKAGE THERMAL PERFORMANCEPackage Symbol Test Conditions Min Typ Max UnitTDFN−8q JA1 oz Copper Thickness, 100 mm2160°C/W q JC35SOIC−8q JA1 oz Copper Thickness, 100 mm2160°C/W q JC25Table 5. DC ELECTRICAL CHARACTERISTICS(V K = 0.9 – 1.5 V; V DD = +5 V; T AMBIENT =−40°C to +85°C, T JUNCTION =−40°C to +125°C, unless otherwise specified.)Parameter Symbol Test ConditionsLimitsUnits Min Typ MaxKelvin voltage V K0.9 1.5V Gate Drive input voltage V DD 4.5 5.5V Supply Current on V DD pin I VDD EN = logic 01m AEN = logic 16577100m A Gate drive Sourcing I GATE V GATE = V DD– 1 V−235−280−330m A Gate drive Sinking V GATE = 0.6 V79.613mA Offset Voltage V OS V OS = V KELVIN− V SENSEV K = 0.9 V to 1.5 V±150±300m VInput Bias Current;Kelvin and KS inputsI K100150nA Power Supply Rejection Ratio PSRR70db I MEAS output current I MEAS070mA Output voltage of I MEAS amplifier V O_IM0V K – 0.1V LOGICLow level input voltage V IL EN0.9 1.1 1.26V High level input voltage V IH EN 1.4 1.65 1.9V Hysteresis0.55V Low level input current I IL EN, V DD = 0 V or 5.5 V2m A High level input current I IH EN, V DD = 0 V or 5.5 V2m A Table 6. AC OPERATING CHARACTERISTICS(V K = 0.9 V – 1.5 V; V DD = 5 V; T AMBIENT =−40°C to +85°C, T JUNCTION =−40°C to +125°C, unless otherwise specified.)Parameter Symbol Test ConditionsLimitsUnits Min Typ MaxI MEAS output rise time t R 20 W, 100 pF, V K = 1.5 VI SENSE : 2 mA – 70 mA 38m sI MEAS output fall time t F33m s I MEAS Settling time t S EN = Logic 0³1, I SENSE = 1 mA30m sEN = Logic 0³1, I SENSE = 70 mA50m sTYPICAL PERFORMANCE CHARACTERISTICSFigure 3. Load Step: 1 A – 10 A50 m s / divI BusV MEASPIN DESCRIPTIONSenseSense connects directly to the SENSEFET’s Sense pin and directs the sensed current to the I MEAS output. Sense is controlled by an amplifier with a FET follower stage to maintain Sense at exactly the Kelvin voltage, thus insuring accuracy of the SENSEFET’s mirror current.KSKS = Kelvin Sense; a Kelvin connection for the mirroring amplifier. Current measurement accuracy is dependent upon the voltage match between the SENSEFET’s Sense and Kelvin leads. To minimize voltage losses in the PCB trace between CA T2300 and the SENSEFET, a Kelvin connection for the control amplifier is provided. KS must be a dedicated connection, shared by no other circuitry , and tied directly to the Sense pin on of the SENSEFET.Figure 4. Current SenseSENSEFETSENSEFETSENSEFETCareful layout is critical in achieving full SENSEFET perfomance. PCB trace resistance can no longer be ignored as it can be in typical low current circuit designs. Microvolt offsets (m V) produce meaningful errors in current ratio tracking. A few milliohms of trace resistance carrying a few milliamps of current produces microvolts of potential difference between CAT2300 and the SENSEFET. To circumvent this error CA T2300 provides a Kelvin lead (KS)for monitoring the SENSEFET’s Sense pin. Under no circumstances should the KS connection share any portion of the current path between the sense pins of CAT2300 and the SENSEFET. Doing so will degrade measurement accuracy.KelvinKelvin connects directly to the SENSEFET’s Kelvin pin and acts the reference voltage for CAT2300’s mirroring circuit. It too must be a dedicated connection, shared by no other circuitry.GateGate connects to the SENSEFET’s Gate pin and controls the SENSEFET’s operation. Gate is controlled by EN: a logic 1 turns the SENSEFET ON, a logic 0 turns it OFF.When ON, voltage is applied to the SENSEFET’s gate via a current source inside CAT2300.By controlling the gate drive current a controlled turn-ON is achieved. Faster turn-on times can be done by adding a supplemental current source to augment the internal current source. Placing a resistor between V DD and Gate will provide extra current and boost turn-on speeds.For a softer turn-on characteristic, add capacitance between the SENSEFET’s Gate and Source pins;approximately 1 nF for every ms of increased delay.When switching OFF the SENSEFET, Gate provides a strong pull-down, 7.5 mA typical, so the SENSEFET will be switched off quickly.V DDV DD provides gate drive for the SENSEFET and power for CAT2300’s internal circuitry and must be +5 V .I MEAS I MEAS is the mirror current output. Placing a resistor between I MEAS and ground produces a voltage proportional to I BUS . The maximum voltage producible at IMEAS is the Kelvin voltage (V K ) – 0.1 V . This sets a limitation on the maximum value of R MEAS .R MEAS +ǒV K *0.1V ǓI SENSE+CSRǒV K *0.1V ǓI buswhere:CSR = Current Sensing Ratio taken from the SENSEFET data sheet.I bus = Max current through the SENSEFET.ENEnable is a high true logic input controlling the SENSEFET’s ON/OFF state. A logic high on EN turns the switch ON; a logic low turns it OFF.Bus turn-ON time is controlled by the FET’s input gate capacitance and the drive current applied to the gate.To minimize power consumption EN disables the internal gate drive current source and current mirroring circuitry whenever the SENSEFET is OFF.ENFigure 5. Typical ApplicationV DDV MEASPACKAGE DIMENSIONSTDFN8, 2x3CASE 511AK −01ISSUE ATOP VIEW SIDE VIEW BOTTOM VIEWFRONT VIEWA1Notes:(1) All dimensions are in millimeters.(2) Complies with JEDEC MO-229.SYMBOLMIN NOM MAX A 0.700.750.80A10.000.020.05A30.20 REFb 0.200.250.30D 1.90 2.00 2.10D2 1.30 1.40 1.50E 3.00E2 1.201.30 1.40e 2.900.50 TYP3.10L0.200.300.40A20.450.550.65Example of Ordering Information (Notes 2 − 5)Prefix Device #Suffix ORDERING INFORMATIONPart Number Temperature Range Package Quantity per Reel (Note 6)Package MarkingCAT2300VP2−GT3−40°C to +85°CTDFN3,000F3T2.All packages are RoHS −compliant (Lead −free, Halogen −free).3.The standard lead finish is NiPdAu pre −plated (PPF).4.The device used in the above example is a CAT2300VP2−GT3 (TDFN, NiPdAu, Tape & Reel, 3,000).5.For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.6.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.SENSEFET is a registered trademark of Semiconductor Components Industries, LLCPUBLICATION ORDERING INFORMATION分销商库存信息: ONSEMICAT2300VP2-GT3。

DPtech LSW2300系列以太网交换机安装手册v1.2

DPtech LSW2300系列以太网交换机 安装手册

i

DPtech LSW2300系列以太网交换机安装手册

杭州迪普科技股份有限公司为客户提供全方位的技术支 持。 通过杭州迪普科技股份有限公司代理商购买产品的用 户,请直接与销售代理商联系;直接向杭州迪普科技股 份有限公司购买产品的用户,可直接与公司联系。 杭州迪普科技股份有限公司 地址: 杭州市滨江区通和路68号中财大厦6层 邮编:310052

1.1 产品概述 .................................................................................................................................. 1-1 1.2 产品型号及规格介绍 .............................................................................................................. 1-1 1.3 前后面板介绍 .......................................................................................................................... 1-3 1.3.1 LSW2300-8T4GP-I/LSW2300-8T4GP-I-DC产品外观 ....................................................... 1-3 1.3.2 LSW2300-8GT4GP-I/LSW2300-8GT4GP-I-DC产品外观.................................................. 1-7 1.3.3 LSW2300-16GT2GP-I/ LSW2300-16GT2GP-I-DC 产品外观 .......................................... 1-11 1.4 端口介绍 ................................................................................................................................ 1-14 1.4.1 CONSOLE口 ......................................................................................................................... 1-14 1.4.2 百兆/千兆以太网电接口 .................................................................................................... 1-15 1.4.3 SFP口 .................................................................................................................................. 1-17

CAT4238TD-GT3;中文规格书,Datasheet资料

CAT4238High Efficiency 10 LED Boost ConverterDescriptionThe CAT4238 is a DC/DC step−up converter that delivers an accurate constant current ideal for driving LEDs. Operation at a fixed switching frequency of 1 MHz allows the device to be used with small value external ceramic capacitors and inductor. LEDs connected in series are driven with a regulated current set by the external resistor R1. LED currents up to 40 mA can be supported over a wide range of input supply voltages up to 5.5 V, making the device ideal for battery−powered applications. The CAT4238 high−voltage output stage is perfect for driving mid−size and large panel displays containing up to ten white LEDs in series.LED dimming can be done by using a DC voltage, a logic signal, or a pulse width modulation (PWM) signal. The shutdown input pin allows the device to be placed in power−down mode with “zero”quiescent current.In addition to thermal protection and overload current limiting, the device also enters a very low power operating mode during “Open LED” fault conditions. The device is housed in a low profile (1mm max height) 5−lead thin SOT23 package for space critical applications.Features•Drives High V oltage LED Strings (38 V)•Up to 87% Efficiency•Low Quiescent Ground Current 0.6 mA•Adjustable Output Current•1 MHz Fixed Frequency Low Noise Operation•Soft Start “In−rush” Current Limiting•Shutdown Current Less than 1 m A•Open LED Overvoltage Protection•Automatic Shutdown at 1.9 V (UVLO)•Thermal Overload Protection•Thin SOT23 5−lead (1 mm Max Height)•These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS CompliantApplications•GPS Navigation Systems•Portable Media Players•Handheld Devices, Digital Cameras•Portable Game MachinesTSOT−23TD SUFFIXCASE 419AEPIN CONNECTIONSMUYMMARKING DIAGRAMDevice Package Shipping ORDERING INFORMATIONCAT4238TD−GT3TSOT−23(Pb−Free)Green*3,000/Tape & Reel MU = Specific Device CodeY = Production Year (Last Digit)M = Production Month (1−9, A, B, C)(Top View)VINSHDNSWGNDFB1* Lead Finish NiPdAuFigure 1. Typical Application CircuitL: Sumida CDC5D23B −470D: Central CMDSH05−4C2: Taiyo Yuden UMK212BJ224 (rated 50 V)Table 1. ABSOLUTE MAXIMUM RATINGSParametersRatings Units V IN , FB voltage −0.3 to +7V SHDN voltage −0.3 to +7V SW voltage (Note 1)up to 60V Storage Temperature Range −65 to +160_C Junction Temperature Range −40 to +150_C Lead Temperature300_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.The SW pin voltage is rated up to 39 V for external continuous DC voltage.Table 2. RECOMMENDED OPERATING CONDITIONSParametersRange Units V INup to 5.5V SW pin voltage0 to 38V Ambient Temperature Range −40 to +85_CNOTE:Typical application circuit with external components is shown above.Table 3. DC ELECTRICAL CHARACTERISTICS(V IN = 3.6 V, ambient temperature of 25°C (over recommended operating conditions unless otherwise specified))Symbol Parameter Test Conditions Min Typ Max UnitsI Q Operating Current V FB= 0.2 VV FB= 0.4 V (not switching)0.60.11.50.6mAI SD Shutdown Current V SHDN = 0 V0.11m A V FB FB Pin Voltage10 LEDs with I LED = 20 mA285300315mV I FB FB pin input leakage1m AI LED Programmed LED Current R1 = 10 WR1 = 15 WR1 = 20 W 28.51914.2530201531.52115.75mAV IH V IL SHDN Logic HighSHDN Logic LowEnable Threshold LevelShutdown Threshold Level0.40.80.71.5VF SW Switching Frequency0.8 1.0 1.3MHzDC Maximum Duty Cycle VIN = 3 V92%I LIM Switch Current Limit350450600mAR SW Switch “On” Resistance I SW = 100 mA 1.0 2.0WI LEAK Switch Leakage Current Switch Off, V SW = 5 V15m AThermal Shutdown150°CThermal Hysteresis20°C V UVLO Undervoltage Lockout (UVLO) Threshold 1.9V V OV-SW Overvoltage Detection Threshold40V V OCL Output Voltage Clamp“Open LED” with VIN = 5 V434548VPin DescriptionVIN is the supply input for the internal logic. The device is compatible with supply voltages down to 2.8 V and up to 5.5V. It is recommended that a small bypass ceramic capacitor (4.7 m F) be placed between the VIN and GND pins near the device. If the supply voltage drops below 1.9 V, the device stops switching.SHDN is the shutdown logic input. When the pin is tied to a voltage lower than 0.4 V, the device is in shutdown mode, drawing nearly zero current. When the pin is connected to a voltage higher than 1.5 V, the device is enabled.GND is the ground reference pin. This pin should be connected directly to the ground place on the PCB.SW pin is connected to the drain of the internal CMOS power switch of the boost converter. The inductor and the Schottky diode anode should be connected to the SW pin. Traces going to the SW pin should be as short as possible with minimum loop area. An over-voltage detection circuit is connected to the SW pin. When the voltage reaches 40V, the device enters a low power operating mode preventing the SW voltage from exceeding the maximum rating.FB feedback pin is regulated at 0.3 V. A resistor connected between the FB pin and ground sets the LED current according to the formula:I LED+0.3VR1The lower LED cathode is connected to the FB pin.Table 4. PIN DESCRIPTIONSPin #Name Function 1SW Switch pin. This is the drain of the internal power switch.2GND Ground pin. Connect the pin to the ground plane.3FB Feedback pin. Connect to the last LED cathode.4SHDN Shutdown pin (Logic Low). Set high to enable the driver.5VIN Power Supply input.Block DiagramDevice OperationThe CAT4238 is a fixed frequency (1 MHz), low noise,inductive boost converter that provides a constant current with excellent line and load regulation. The device uses a high-voltage CMOS power switch between the SW pin and ground to energize the inductor. When the switch is turned off, the stored energy in the inductor is released into the load via the Schottky diode.The on/off duty cycle of the power switch is internally adjusted and controlled to maintain a constant regulated voltage of 0.3 V across the feedback resistor connected to the feedback pin (FB). The value of the resistor sets the LED current accordingly (0.3 V/R 1).During the initial power-up stage, the duty cycle of the internal power switch is limited to prevent excessive in-rush currents and thereby provide a “soft-start” mode of operation.While operating from a Li −Ion battery, the device can deliver 20mA of load current into a string of up to 10 white LEDs. For higher input voltages, the LED current can be increased.In the event of an “Open LED” fault condition, where the feedback control loop becomes open, the output voltage will continue to increase. Once this voltage exceeds 40 V , an internal protection circuit will become active and place the device into a very low power safe operating mode where only a small amount of power is transferred to the output.This is achieved by pulsing the switch once every 6 m s and keeping it on for about 1 m s.Thermal overload protection circuitry has been included to prevent the device from operating at unsafe junction temperatures above 150°C. In the event of a thermal overload condition the device will automatically shutdown and wait till the junction temperatures cools to 130°C before normal operation is resumed.Light Load OperationUnder light load condition (under 2 mA) and with input voltage above 5.0 V , the CAT4238 driving 10 LEDs, the driver starts pulse skipping. Although the LED current remains well regulated, some lower frequency ripple may appear.Figure 3. Switching Waveform V IN = 5.0 V,I LED = 1.5 mAFigure 4. Quiescent Current vs. V IN(Not Switching)Figure 5. Quiescent Current vs. V IN(Switching)INPUT VOLTAGE (V)INPUT VOLTAGE (V)50751001251505.04.54.03.53.000.51.01.52.0Figure 6. FB Pin Voltage vs. TemperatureFigure 7. FB Pin Voltage vs. Output CurrentTEMPERATURE (°C)OUTPUT CURRENT (mA)150100500−50297298299300301302303290295300305310Figure 8. Switching Frequency vs. SupplyVoltageFigure 9. Switching WaveformsINPUT VOLTAGE (V)500 ns/div5.04.55.54.03.53.00.80.91.01.11.2Q U I E S C E N T C U R R E N T (m A )Q U I E S C E N T C U R R E N T (m A )F B P I N V O L T AG E (m V )F B P I N V O L T AG E (m V )S W I T C H I N G F R E Q U E N C Y (M H z )SW 20V/divInductor Current 100mA/divVOUT AC coupled 500mV/div5.5Figure 10. LED Current vs. Input VoltageFigure 11. LED Current Regulation (10 mA)INPUT VOLTAGE (V)INPUT VOLTAGE (V)−1.0−0.50.51.0Figure 12. Efficiency vs. Load Current(10 LEDs)Figure 13. Efficiency vs. Input Voltage(10 LEDs)LED CURRENT (mA)INPUT VOLTAGE (V)6070809010060708090100Figure 14. Power −up with 10 LEDs at 20 mAFigure 15. Switch ON Resistance vs. InputVoltageINPUT VOLTAGE (V)5.55.04.54.03.53.000.51.01.52.0L E D C U R R E N T (m A )L E D C U R R E N T V A R I A T I O N (%)E F F I C I E N C Y (%)E F F I C I E N C Y (%)S W I T C H R E S I S T A N C E (W )Figure 16. Maximum Output Current vs. InputVoltageFigure 17. Shutdown Voltage vs. Input VoltageINPUT VOLTAGE (V)INPUT VOLTAGE (V)1020304050600.20.40.60.81.0O U T P U T C U R R E N T (m A )S H U T D O W N V O L T A G E (V )Application InformationExternal Component Selection CapacitorsThe CAT4238 only requires small ceramic capacitors of 4.7m F on the input and 0.22 m F on the output. Under normal condition, a 4.7 m F input capacitor is sufficient. For applications with higher output power, a larger input capacitor of 10 m F may be appropriate. X5R and X7R capacitor types are ideal due to their stability across temperature range.InductorA 47 m H inductor is recommended for most of the CAT4238 applications. In cases where the efficiency is critical, inductances with lower series resistance are preferred. Inductors with current rating of 300 mA or higher are recommended for most applications. Sumida CDC5D23B −470 47 m H inductor has a rated current of 490mA and a series resistance (D.C.R.) of 420 m W typical.Schottky DiodeThe current rating of the Schottky diode must exceed the peak current flowing through it. The Schottky diode performance is rated in terms of its forward voltage at agiven current. In order to achieve the best efficiency, this forward voltage should be as low as possible. The response time is also critical since the driver is operating at 1MHz.Central Semiconductor Schottky diode CMDSH05−4(500mA rated) is recommended for most applications.LED Current SettingThe LED current is set by the external resistor R 1connected between the feedback pin (FB) and ground. The formula below gives the relationship between the resistor and the current:R 1+0.3VLEDcurrent Table 5. RESISTOR R 1 AND LED CURRENTLED Current (mA)R 1 (W )56010301520201525123010Open LED ProtectionIn the event of an “Open LED” fault condition, the CAT4238 will continue to boost the output voltage with maximum power until the output voltage reaches approximately 40 V . Once the output exceeds this level, the internal circuitry immediately places the device into a very low power mode where the total input power is limited to about 6 mW (about 1.6 mA input current with a 3.6 V supply). The SW pin clamps at a voltage below its maximum rating of 60 V . There is no need to use an external zener diode between V out and the FB pin. A 50 V rated C 2 capacitor is required to prevent any overvoltage damage in the open LED condition.Figure 18. Open LED Protection without ZenerSchottky 100 V(Central CMSH1−100)V INV OUTFigure 19. Open LED Switching Waveforms withoutZener2 m s/divS W 10 V /d i vFigure 20. Open LED Supply Current vs. V IN withoutZenerINPUT VOLTAGE (V)5.04.54.03.53.002.01.04.05.0S U P P L Y C U R R E N T (m A )5.53.0Figure 21. Open LED Output Voltage vs. V IN withoutZenerINPUT VOLTAGE (V)5.04.54.03.53.035404550O U T P U T V O L T A G E (V )5.555Dimming ControlThere are several methods available to control the LED brightness.PWM Signal on the SHDN PinLED brightness dimming can be done by applying a PWM signal to the SHDN input. The LED current is repetitively turned on and off, so that the average current is proportional to the duty cycle. A 100% duty cycle, with SHDN always high, corresponds to the LEDs at nominal current. Figure 22shows a 1kHz signal with a 50% duty cycle applied to the SHDN pin. The recommended PWM frequency range is from 100Hz to 2kHz.Figure 22. Switching Waveform with 1 kHz PWM onSHDN Filtered PWM SignalA filtered PWM signal used as a variable DC voltage can control the LED current. Figure 23 shows the PWM control circuitry connected to the CAT4238 FB pin. The PWM signal has a voltage swing of 0 V to 2.5 V . The LED current can be dimmed within a range from 0 mA to 20 mA. The PWM signal frequency can vary from very low frequency up to 100 kHz.Figure 23. Circuit for Filtered PWM Signal0 V2.5 V PWM Signal WA PWM signal at 0 V DC, or a 0% duty cycle, results in a max LED current of about 22 mA. A PWM signal with a 93% duty cycle or more, results in an LED current of 0mA.Figure 24. Filtered PWM Dimming (0 V to 2.5 V)L E D C U R R E N T (m A )2520151050102030405060708090100PWM DUTY CYCLE (%)Board LayoutThe CAT4238 is a high−frequency switching regulator. The traces that carry the high−frequency switching current have to be carefully layout on the board in order to minimize EMI, ripple and noise in general. The thicker lines on Figure25 show the switching current path. All these traces have to be short and wide enough to minimize the parasitic inductance and resistance. The loop shown on Figure25 corresponds to the current path when the CA T4238 internal switch is closed. On Figure 26 is shown the current loop,when the CAT4238 switch is open. Both loop areas should be as small as possible.Capacitor C1 has to be placed as close as possible to the V IN pin and GND. The capacitor C2 has to be connected separately to the top LED anode. A ground plane under the CAT4238 allows for direct connection of the capacitors to ground. The resistor R1 must be connected directly to the GND pin of the CA T4238 and not shared with the switchingcurrent loops and any other components. Figure 25. Closed−switch Current Loop Figure 26. Open−switch Current LoopFigure 27. Recommended PCB Layout分销商库存信息: ONSEMICAT4238TD-GT3。

CAT24C256WI-GT3中文资料

256-Kb I 2C CMOS Serial EEPROMCAT24C256PIn COnfIguRATIOn funCTIOnAl SyMbOlfEATuRESn Supports Standard and fast I 2C Protocol n 1.8 V to 5.5 V Supply Voltage Range n 64-byte Page Write buffern Hardware Write Protection for entire memory n Schmitt Triggers and noise Suppression filterson I 2C bus Inputs (SCl and SDA).n low power CMOS technology n 1,000,000 program/erase cycles n 100 year data retention n Industrial temperature rangen RoHS-compliant 8-pin PDIP and SOIC packagesPDIP (l)SOIC (W, X)VSSSD ASCL WPA 2, A 1, A 0DEVICE DESCRIPTIOnThe CAT24C256 is a 256-Kb Serial CMOS EEPROM, internally organized as 5 2 pages of 64 bytes each, for a total of 32,768 bytes of 8 bits each.It features a 64-byte page write buffer and supports both the Standard ( 00 kHz) as well as Fast (400 kHz) I 2C protocol.Write operations can be inhibited by taking the WP pin High (this protects the entire memory).External address pins make it possible to address up to eight CAT24C256 devices on the same bus.8765V CC WP SCL SDAA 2A 0A 1V SS1234For the location of Pin , please consult the corresponding package drawing.PIn funCTIOnSA 0, A, A 2Device Address SDA Serial Data SCL Serial Clock WP Write Protect V CC Power Supply V SSGround* Catalyst carries the I 2C protocol under a license from the Philips Corporation.for Ordering Information details, see page 13.CAT24C256AbSOluTE MAXIMuM RATIngS(1)Storage Temperature-65°C to + 50°C Voltage on Any Pin with Respect to Ground(2)-0.5 V to +6.5 VRElIAbIlITy CHARACTERISTICS(3)Symbol Parameter Min unitsN END(4)Endurance ,000,000Program/ Erase Cycles T DR Data Retention 00YearsD.C. OPERATIng CHARACTERISTICSV CC = .8 V to 5.5 V, T A = -40°C to 85°C, unless otherwise specified.Symbol Parameter Test Conditions Min Max unitsI CC Supply Current Read or Write at 400 kHz mAI SB Standby Current All I/O Pins at GND or V CC µAI L I/O Pin Leakage Pin at GND or V CC µAV IL Input Low Voltage-0.5V CC x 0.3V V IH Input High Voltage V CC x 0.7V CC + 0.5V V OL Output Low Voltage V CC > 2.5 V, I OL = 3.0 mA0.4V V OL2Output Low Voltage V CC > .8 V, I OL = .0 mA0.2VPIn IMPEDAnCE CHARACTERISTICST A = 25°C, f = 400 kHz, V CC = 5 VSymbol Parameter Conditions Min Max unitsC IN(3)SDA I/O Pin Capacitance V IN = 0 V8pFC IN(3)Input Capacitance (other pins)V IN = 0 V6pFnotes:( ) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.(2) The DC input voltage on any pin should not be lower than -0.5 V or higher than V CC + 0.5 V. During transitions, the voltage on any pin mayundershoot to no less than - .5 V or overshoot to no more than V CC + .5 V, for periods of less than 20 ns.(3) These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q 00and JEDEC test methods.(4) Page Mode, V CC = 5 V, 25°CCAT24C256A.C. CHARACTERISTICS(1)V CC = .8 V to 5.5 V, T A = -40°C to 85°C, unless otherwise specified.Symbol Parameter1.8 V - 5.5 V2.5 V - 5.5 Vunits Min Max Min MaxF SCL Clock Frequency 00400kHzT I(2)Noise Suppression Time Constant atSCL, SDA Inputs0. 0. µst AA SCL Low to SDA Data Out 3.50.9µs t BUF(2)Time the Bus Must be Free Before aNew Transmission Can Start4.7 .3µst HD:STA Start Condition Hold Time40.6µs t LOW Clock Low Period 4.7 .3µs t HIGH Clock High Period40.6µs t SU:STA Start Condition Setup Time 4.70.6µs t HD:DAT Data In Hold Time00µs t SU:DAT Data In Setup Time0.250. µs t R(2)SDA and SCL Rise Time 0.3µs t F(2)SDA and SCL Fall Time0.30.3µs t SU:STO Stop Condition Setup Time40.6µs t DH Data Out Hold Time0. 0. µs t WR Write Cycle Time55ms t PU(2), (3)Power-up to Ready Mode ms notes:( ) Test conditions according to “A.C. Test Conditions” table.(2) Tested initially and after a design or process change that affects this parameter.(3) t PU is the delay between the time V CC is stable and the device is ready to accept commands.A.C. TEST COnDITIOnSInput Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Times≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Levels0.5 x V CCOutput Load Current Source: I OL = 3 mA (V CC≥ 2.5 V); I OL = mA (V CC < 2.5 V); C L = 00 pFCAT24C256PIn DESCRIPTIOnSCl:The Serial Clock input pin accepts the Serial Clock generated by the Master.SDA: The Serial Data I/O pin receives input data and transmits data stored in EEPROM. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.A0, A1 and A2: The Address pins accept the device ad-dress. These pins have on-chip pull-down resistors. WP: The Write Protect input pin inhibits all write op-erations, when pulled HIGH. This pin has an on-chip pull-down resistor.funCTIOnAl DESCRIPTIOnThe CAT24C256 supports the Inter-Integrated Circuit (I2C) Bus data transmission protocol, which defines a device that sends data to the bus as a transmitter and a device receiving data as a receiver. Data flow is controlled by a Master device, which generates the serial clock and all START and STOP conditions. The CAT24C256 acts as a Slave device. Master and Slave alternate as either transmitter or receiver. Up to 8 devices may be connected to the bus as determined by the device ad-dress inputs A0, A , and A2.I2C buS PROTOCOlThe I2C bus consists of two ‘wires’, SCL and SDA. The two wires are connected to the V CC supply via pull-up resistors. Master and Slave devices connect to the 2-wire bus via their respective SCL and SDA pins. The transmitting device pulls down the SDA line to ‘transmit’ a ‘0’ and releases it to ‘transmit’ a ‘ ’.Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics).During data transfer, the SDA line must remain stable while the SCL line is HIGH. An SDA transition while SCL is HIGH will be interpreted as a START or STOP condition (Figure ).STARTThe START condition precedes all commands. It consists of a HIGH to LOW transition on SDA while SCL is HIGH. The START acts as a ‘wake-up’ call to all receivers. A bsent a START, a Slave will not respond to commands. STOPThe STOP condition completes all commands. It consists of a LOW to HIGH transition on SDA while SCL is HIGH. The STOP starts the internal Write cycle (when follow-ing a Write command) or sends the Slave into standby mode (when following a Read command).Device AddressingThe Master initiates data transfer by creating a START condition on the bus. The Master then broadcasts an 8-bit serial Slave address. The first 4 bits of the Slave address are set to 0 0, for normal Read/Write opera-tions (Figure 2). The next 3 bits, A2, A and A0, select one of 8 possible Slave devices. The last bit, R/W, specifies whether a Read (1) or Write (0) operation is to be performed.AcknowledgeAfter processing the Slave address, the Slave responds with an acknowledge (ACK) by pulling down the SDA line during the 9th clock cycle (Figure 3). The Slave will also acknowledge the byte address and every data byte presented in Write mode. In Read mode the Slave shifts out a data byte, and then releases the SDA line during the 9th clock cycle. If the Master acknowledges the data, then the Slave continues transmitting. The Master terminates the session by not acknowledging the last data byte (NoACK) and by sending a STOP to the Slave. Bus timing is illustrated in Figure 4.CAT24C256figure 3. Acknowledge Timingfigure 2. Slave Address bitsfigure 1. Start/Stop Timingfigure 4. bus TimingSCLSDA INSDA OUTCAT24C256WRITE OPERATIOnSbyte WriteIn Byte Write mode the Master sends a START, followed by Slave address, two byte address and data to be written (Figure 5). The Slave acknowledges all 4 bytes, and the Master then follows up with a STOP, which in turn starts the internal Write operation (Figure 6). During internal Write, the Slave will not acknowledge any Read or Write request from the Master.Page WriteThe CAT24C256 contains 32,768 bytes of data, arranged in 5 2 pages of 64 bytes each. A two byte address word, following the Slave address, points to the first byte to be written. The most significant bit of the address word is ‘don’t care’, the next 9 bits identify the page and the last 6 bits identify the byte within the page. Up to 64 bytes can be written in one Write cycle (Figure 7).The internal byte address counter is automatically in-cremented after each data byte is loaded. If the Master transmits more than 64 data bytes, then earlier bytes will be overwritten by later bytes in a ‘wrap-around’ fashion (within the selected page). The internal Write cycle starts immediately following the STOP.Acknowledge PollingAcknowledge polling can be used to determine if the CAT24C256 is busy writing or is ready to accept com-mands. Polling is implemented by interrogating the device with a ‘Selective Read’ command (see READ OPERATIONS).The CAT24C256 will not acknowledge the Slave address, as long as internal Write is in progress.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is pro-tected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the operation of the CAT24C256.CAT24C256 figure 5. byte Write Timingfigure 6. Write Cycle Timingfigure 7. Page Write TimingCAT24C256READ OPERATIOnSImmediate Address ReadIn standby mode, the CAT24C256 internal address counter points to the data byte immediately following the last byte accessed by a previous operation. If that ‘previ-ous’ byte was the last byte in memory, then the address counter will point to the st memory byte, etc. When, following a START, the CAT24C256 is presented with a Slave address containing a ‘ ’ in the R/W bit position (Figure 8), it will acknowledge (ACK) in the 9th clock cycle, and will then transmit data being pointed at by the internal address counter. The Master can stop further transmission by issuing a NoACK, followed by a STOP condition.Selective ReadThe Read operation can also be started at an address different from the one stored in the internal address counter. The address counter can be initialized by per-forming a ‘dummy’ Write operation (Figure 9). Here the START is followed by the Slave address (with the R/W bit set to ‘0’) and the desired two byte address. Instead of following up with data, the Master then issues a 2nd START, followed by the ‘Immediate Address Read’ se-quence, as described earlier.Sequential ReadIf the Master acknowledges the st data byte transmitted by the CAT24C256, then the device will continue trans-mitting as long as each data byte is acknowledged by the Master (Figure 0). If the end of memory is reached during sequential Read, then the address counter will ‘wrap-around’ to the beginning of memory, etc. Sequential Read works with either ‘Immediate Address Read’ or ‘Selective Read’, the only difference being the starting byte address.CAT24C256 figure 8. Immediate Address Read Timingfigure 9. Selective Read Timingfigure 10. Sequential Read TimingCAT24C2568-lEAD 300 MIl WIDE PlASTIC DIP (l)notes:( ) Complies with JEDEC Standard MS00 .(2) All dimensions are in millimeters.(3) Dimensioning and tolerancing per ANSI Y 4.5M- 982ecSYMBOLA A1b b2D E E1e eB LMIN 0.380.369.027.626.09 6.357.872.923.81NOM 0.46 1.771.147.872.54 BSCMAX 4.57A2 3.05 3.810.56c 0.210.260.3510.168.257.119.65For current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfPACKAgE OuTlInESCAT24C256Doc No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-lEAD 150 MIl WIDE SOIC (W)notes:(1) Complies with JEDEC specification MS-012 dimensions.(2) All linear dimensions are in millimeters.SyMbOl A A b C D E E h L MIn 0. 0 .350.334.805.803.800.250.40nOM 0.250. 9MAX 0.25 .750.5 5.006.204.00e .27 BSC0.50 .27Ө10°8°eFor current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfCAT24C2562Doc. No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-lEAD 208 MIl WIDE SOIC, EIAJ (X)notes:(1) Complies with EIAJ specification.(2) All linear dimensions are in millimeters.θcSYMBOLA1A b c D E E1e L MIN 0.050.365.137.755.130.51NOM 0.250.19 1.27 BSCMAX 0.252.030.485.338.265.380.76θ10°8°For current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfCAT24C2563Doc No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeORDERIng InfORMATIOnNotes:( ) All packages are RoHS-compliant (Lead-free, Halogen-free). (2) The standard lead finish is NiPdAu.(3) The device used in the above example is a CAT24C256WI-GT3 (SOIC-JEDEC, Industrial Temperature, NiPdAu, Tape & Reel). (4) For SOIC, EIAJ (X) package the standard lead finish is Matte-Tin. This package is available in 2000 pcs/reel, i.e. CAT24C256XI-T2. (5) For additional package and temperature options, please contact your nearest Catalyst Semiconductor Sales office.Catalyst Semiconductor, Inc.Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054Phone: 408.542. 000Fax: 408.542. Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following: Beyond Memory™, DPP™, EZDim™, MiniPot™, and Quad-Mode™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.CATALYST SEMICONDUCTOR MAKES NO WARRANTY , REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled “Advance Information” or “Preliminary” and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.Publication #: 04Revison: D Issue date: 0 / 2/07REVISIOn HISTORyDate Revision Comments0/07/05A Initial Issue/ 6/05B Update Ordering Information Add Tape and Reel Specifications 02/02/06CUpdate Ordering Information0 / 2/07DUpdate Package Outlines. Add SOIC, EIAJ Package Outlines Update A.C. Characteristics. Add A.C. Test ConditionsUpdate Figures , 3 and 4Delete Package Marking. Deleted Tape and Reel Updated Ordering Information。

E2SCA18-7.999M中文资料(ECLIPTEK)中文数据手册「EasyDatasheet - 矽搜」

(5 DigitsMaximum + Decimal)

HC-49/UP

规格如有更改,恕不另行通知.

CR44

.

08/08

包装选择

空白=散装,TR =卷带式

频率

负载电容

S =串联谐振 XX = XXpF并联谐振

动作模式 /水晶切割 A =基本/ AT, B =三次泛音/ AT D =基本/ BT

外形尺寸 ALL DIMENSIONS IN MILLIMETERS

建议焊盘布局 ALL DIMENSIONS IN MILLIMETERS

电气特性

频率范围频率ຫໍສະໝຸດ 差 /稳定性在工作温 度范围

工作温度范围

老化( 25°C)

存储温度范围

并联电容

绝缘电阻

驱动电平

负载电容(C

)

3.579545MHz为50.000MHz

为±50ppm /±100ppm(标准),±30ppm/为±50ppm(AT切割只),±15ppm/±30ppm(AT切割只),

环境/机械特性

PARAMETER

ESD敏感性

精细泄漏测试 可燃性 总泄漏测试 机械冲击 耐湿性 湿度敏感度 耐焊接热 抗溶剂 可焊性 温度循环 振荡

SPECIFICATION

MIL-STD-883,方法3015,1级,HBM:1500V MIL-STD-883,方法1014,条件A UL94-V0 MIL-STD-883,方法1014,条件C MIL-STD-202,方法213,条件C MIL-STD-883,法1004 J-STD-020, MSL1 MIL-STD-202,方法210,满足条件K MIL-STD-202,方法215 MIL-STD-883,方法2003 MIL-STD-883,方法1010,条件B MIL-STD-883,方法2007条件A

家庭常用英语

家庭常用英语第一天:该起床了1.It's Time to Get up该起床了A:Li Na,It's time to get up. 李娜,该起床了。

B:Oh,I'm afraid I'll be late. 噢,恐怕要迟到了吧。

A:Don't worry. It's still early. It's just half past six.不用着急,还早呢,才六点半.B:Would you please help me get my breakfast ready when I wash my face and brush my teeth?I'm on duty today.我洗漱时您能不能帮我准备好早饭?今天我值日。

A:That's OK. 行啊.B:Thank you,Mum. 谢谢,妈妈。

今天下午有大雨第二天:今天下午有大雨2.There Will Be a Heavy Rain this AfternoonA:Mum,it's raining now. 妈,下雨了。

B:The weatherman says there will be a heavy rain this afternoon. 天气预报说今天下午还有大雨呢。

A:Then I'll have to take my raincoat, won't I?那我得带雨衣吧?B:Of course,you will. But be careful when you ride with your raincoat on. Don't forget to take it back after school.当然得带了。

可是你穿着雨衣骑车一定要小心,放学以后别忘了把雨衣带回来。

A:No,I won't. 我不会忘的。

第三天:我找不到我的毛衣了3.I Can't Find My Sweater我找不到毛衣了A:It's very cold this morning. You must put on more clothes. 今天早晨很冷,你必须多穿衣服。

CAT1026WI-25-GT3中文资料