ZL50053QCC中文资料

Acoustimass 5 系列 V 和 Acoustimass 3 系列 V 立体扬音器系统用户指

Regulatory InformationThis symbol means the product must not be discarded as household waste, and should be delivered to an appropriate collection facility for recycling. Proper disposal and recycling helps protect natural resources, human health and the environment. For more information on disposal and recycling of this product, contact your local municipality, disposal service, or the shop where you bought this product.Bose Corporation hereby declares that this product is in compliance with the essential requirements and other relevant provisions of Directive 1999/5/EC and all other applicable EU directive requirements. The complete declaration of conformity can be found at: /compliance.Names and Contents of Toxic or Hazardous Substances or ElementsPart Name Toxic or Hazardous Substances and ElementsLead (Pb)Mercury (Hg)Cadmium (Cd)Hexavalent (CR(VI))Polybrominated Biphenyl (PBB)Polybrominated d iphenylether (PBDE) PCBs X00000Metal parts X00000Plastic parts000000Speakers X00000Cables X000000: Indicates that this toxic or hazardous substance contained in all of the homogeneous materials for this part is below the limit requirement in SJ/T 11363-2006.X: Indicates that this toxic or hazardous substance contained in at least one of the homogeneous materials used for this part is above the limit requirement in SJ/T 11363-2006.Please complete and retain for your records.The serial numbers are located on the connector panel of the Acoustimass® module.Serial Number: _________________________________________________________________________________________________________________________ Model Number:_________________________________________________________________________________________________________________________ Purchase date: _________________________________________________________________________________________________________________________ Please keep your receipt together with this owner’s guide.©2015 Bose Corporation. No part of this work may be reproduced, modified, distributed, or otherwise used without written permission.2 - EnglishTable of Contents IntroductionAbout your Bose® Acoustimass® stereo speaker system (4)System features (4)Unpacking the system (4)Setting UpPlacement guidelines (5)Sample system placement (5)Connecting the speakers to the Acoustimass module (6)Mounting the speakers (6)Connecting the Acoustimass module to your receiver or amplifier (7)Before plugging in your receiver or amplifier (7)Checking the system (7)Understanding automatic system protection (7)Care and MaintenanceTroubleshooting (8)Cleaning (8)Customer service (8)Limited warranty (8)Accessories (8)Technical informationCompatibility (9)Wire recommendations (9)English - 3About your Bose® Acoustimass® stereo speaker systemThe Bose Acoustimass stereo speaker system delivers spacious, true sound from small, h igh-performance speakers for consistent audio performance regardless of content, source or room layout.System Features• Bose Acoustimass speaker technology delivers full, natural audio performance.• Hideaway Acoustimass module provides impactful bass sound.• Speakers can be mounted on the wall, table stands or floor stands (kits available separately).Unpacking the systemCarefully unpack the carton and confirm that the following parts are included:WARNING: This product contains magnetic material. Contact your physician if you have questions on whether this might affect the operation of your implantable medical device.Acoustimass module Rubber feet(2) speaker wires(2) speaker cablesAcoustimass 5 system(2) Direct/Reflecting® series II speakers Acoustimass 3 system(2) Virtually Invisible® series II speakersNote: If part of the system is damaged, do not use it. Contact your authorized Bose dealer or Bose Customer Service. Refer to thec ontact sheet in the carton.Introduction4 - EnglishSetting Up Placement guidelinesPlace the system outside of and away from metal cabinets, other audio/video components and direct heat sources.Acoustimass® Module• Stand the module on its rubber feet along a wall within 5 ft. (1.5 m) of the corner. To increase bass, move the module closer to a corner.• Choose a stable and level surface. Vibration can cause the module to move, p articularly on smooth surfaces like marble,glass or highly polished wood.• Leave at least 2 in. (50 mm) of space between the opening and the wall.• Place at least 2 ft. (0.6 m) from any TV to avoid magnetic interference with the TV image. Move it farther away if you stillnotice interference.Speakers• Place the speakers 3 - 15 ft. (1- 4.6 m) apart.• Place the speakers at least 6 in. (.15 mm) away from any CRT (picture tube) TV.Sample system placementAcoustimass 5 systemNote: Attach the rubber feet to the Acoustimass module to protect your floor.CAUTION: Do not place the Acoustimass module on its front or back panel when in use.English - 56 - EnglishConnecting the speakers to the Acoustimass moduleUse the two provided speaker cables to connect your speakers to the Acoustimass module.CAUTION: Turn off and unplug all components before making the connections.1. Insert the left speaker cable’s L plug into the left speaker, with the label facing down.2. Insert the right speaker cable’s R plug into the right speaker, with the label facing down.CAUTION: Do not connect your amplifier or receiver directly to the speakers. Connect the speakers to the A coustimass module to avoiddamaging your system.3. Connect the other end of the left speaker cable to the L (left) OUTPUTS TO CUBE SPEAKERS terminal on the connector panel ofthe Acoustimass module.A. Insert the marked wire into the positive (+) terminal (with the red marking).B. Insert the unmarked wire into the negative (–) terminal (with the black marking). 4. Repeat step 3 for the right speaker cable, connecting its wires to the R (right) terminal.–R+–L +OUTPUTSTO CUBE SPEAKERS–R +–L +INPUTSFROM AMP OR RECEIVERMounting the speakersYou can place system speakers on wall brackets, table stands or floor stands. You can also use additional speaker wire and a Bose connector to increase the distance between the speakers and the A coustimass module. To purchase these accessories, contact your local Bose dealer or visit w CAUTION: Do not use any other hardware to mount the speakers.Setting UpRLAcoustimass 3 systemAcoustimass 5 systemEnglish - 7Setting UpConnecting the Acoustimass ® module to your receiver or amplifierThe speaker wires without plugs connect the Acoustimass module to your receiver or amplifier. Your speaker system works withr eceivers or amplifiers rated from 10 to 200 watts per channel with 4 to 8 ohm impedance. Refer to your receiver or amplifier owner’s guide.CAUTION: Incorrect wiring results in little or no bass output and could damage the system.1. Connect the speaker wires to the INPUTS FROM AMP OR RECEIVER terminals on the Acoustimass module’s rear panel:A. Connect the marked wire to the positive (+) terminal of the L (left) pair of input terminals.B. Connect the unmarked wire to the negative (–) terminal of the L (left) pair of input terminals.C. Repeat steps A and B with the other speaker wire for the R (right) pair of input terminals.–R +–L +OUTPUTSTO CUBE SPEAKERS–R +–L +INPUTSFROM AMP OR RECEIVER2. Connect the other ends of the cables to the speaker terminals of your amplifier or receiver.A. Connect the marked wire connected to the L (left) pair of input terminals on the module to the LEFT positive (+) terminal on youramplifier or receiver. B. Connect the unmarked wire connected to the L (left) pair of input terminals on the module to the LEFT negative (–) terminal onyour amplifier or receiver.C. Repeat steps A and B with the wire connected to the R (right) pair of input terminals on your Acoustimass module and theRIGHT pair of input terminals on your amplifier or receiver.–R+–L +OUTPUTSTO CUBE SPEAKERS–R+–L +INPUTSFROM AMP OR RECEIVERBefore plugging in your receiver or amplifier:• Ensure no strands of wire from any terminal are brushing against any other terminal. Such “bridged” wires create short circuits which can damage your receiver or amplifier.• Check all connections to avoid damaging your speakers. Make sure the speakers are connected to the module and not directly to the amplifier or receiver.Checking the systemWith your amplifier and Acoustimass ® module powered, your system should respond accordingly:• With the balance control on your amplifier turned to the left, sound comes from the Acoustimass module and left speaker only.• With the balance control turned to the right, sound comes from the Acoustimass module and right speaker only.• With the balance control in the center position, music with bass should be the same or louder with the control in the center than to the left or right.If your system does not respond as described, check all the wires for proper positive to positive and negative to negative connections. If your system still doesn’t respond properly, see “Troubleshooting” on page 8.Understanding automatic system protectionWhen played at high volume, your Acoustimass systems’ automatic protection circuit activates to prevent damage to the system from electrical stress or overload. When this happens, you may notice a slight decrease in volume. This indicates that the power input may have exceeded safe levels. Setting the volume at or above this level for sustained periods is not r ecommended.Care and MaintenanceTroubleshootingProblem What to doDistorted or no sound• Disconnect the amplifier or receiver from the system, and reconnect the Acoustimass® module to another amplifieror receiver that is working properly. If the system now works, the problem is in your amplifier or receiver.• Power off the amplifier or receiver and check all the connections between the speakers, the module, and amplifieror receiver.• Refer to your amplifier or receiver’s owner’s guide for more troubleshooting information.• See “Checking your receiver or amplifier’s speaker channels”.Checking your receiver or amplifier’s speaker channelsIf one of the speakers does not play or sounds distorted, your amplifier or receiver’s speaker channel may be defective.1. Disconnect both speaker cables from the amplifier or receiver.2. Reconnect the cable from the Acoustimass® module’s L INPUTS to the amplifier or receiver’s right speaker terminals.3. Disconnect both speaker cables from the amplifier or receiver. Reconnect the cable from the Acoustimass® module’s L INPUTS tothe amplifier or receiver’s right speaker terminals.4. Set the amplifier or receiver’s balance control all the way to the right and power it on. If the left speaker now plays properly, youramplifier or receiver’s left speaker channel may be defective.5. Repeat to check your right speaker, reconnecting the cable from the module’s R INPUTS to the amplifier or receiver’s left speakerterminals.CAUTION: DO NOT connect the other speaker to the potentially defective channel. If the channel is defective, it could d amage your Acoustimass system.Cleaning• Clean the surface of the system with a soft, dry cloth.• Do not use any sprays near the system. Do not use any solvents, chemicals, or cleaning solutions containing alcohol, ammonia or abrasives.• Do not allow liquids to spill into any openings.• You can vacuum the speaker grilles. To avoid damaging the drivers located directly behind the grille, use light pressure only.Customer serviceFor additional help, contact Bose® Customer Service. Refer to the contact sheet in the carton.Limited warrantyYour system is covered by a limited warranty. Details of the limited warranty are provided on the product registration card that is in the carton. Please refer to the card for instructions on how to register. Failure to register will not affect your limited warranty rights.The warranty information provided with this product does not apply in Australia or New Zealand. See our website at.au/warranty or /warranty for details of the Australia and New Zealand warranty.8 - EnglishTechincal Information CompatibilityCompatible with receivers or amplifiers rated from 4 – 8 ohmsCompatible with receivers or amplifiers rated from 10 – 100 watts per channelIEC rating: 50 watts per channelWire recommendationsBased on maximum frequency response deviation of ±0.5 dB.Gauge Length18 (0.75 mm2)30 ft (9 m) maximum16 (1.5 mm2)45 ft (14 m) maximumEnglish - 9。

振华云科电阻命名方式

振华云科电阻命名方式1. 引言振华云科是一家专注于电阻器研发与生产的企业,为了更好地标识和区分不同类型的电阻器产品,需要制定一套规范的命名方式。

本文将介绍振华云科电阻器的命名方式,包括命名规则、命名元素和命名示例。

2. 命名规则振华云科电阻器的命名遵循以下规则:2.1 统一前缀所有振华云科电阻器的名称都以统一的前缀“ZH”开头,表示该产品是由振华云科生产。

2.2 类型标识在名称中加入类型标识,用于区分不同类型的电阻器。

常见的类型标识包括“R”(固定电阻器)和“VR”(可变电阻器)。

2.3 阻值编码在名称中加入阻值编码,用于表示电阻器的额定阻值。

阻值编码通常使用欧姆(Ω)作为单位,并采用国际单位制前缀来表示不同数量级。

例如,“1K”表示1000Ω,“10M”表示10000000Ω。

2.4 精度等级在名称中加入精度等级,用于表示电阻器的精度。

常见的精度等级包括“1%”和“5%”。

2.5 功率等级在名称中加入功率等级,用于表示电阻器的额定功率。

常见的功率等级包括“1/4W”(1/4瓦特)、“1/2W”(1/2瓦特)和“1W”(1瓦特)。

2.6 封装形式在名称中加入封装形式,用于表示电阻器的外观和尺寸。

常见的封装形式包括“0805”、“1206”和“2512”。

3. 命名元素振华云科电阻器的命名由以下元素组成:3.1 前缀统一前缀为“ZH”。

3.2 类型标识使用类型标识来表示电阻器类型,如“R”表示固定电阻器,“VR”表示可变电阻器。

3.3 阻值编码使用阻值编码来表示电阻器的额定阻值。

3.4 精度等级使用精度等级来表示电阻器的精度。

3.5 功率等级使用功率等级来表示电阻器的额定功率。

3.6 封装形式使用封装形式来表示电阻器的外观和尺寸。

4. 命名示例以下是一些振华云科电阻器的命名示例:•ZH-R10K-1%-1/4W-0805:表示一个额定阻值为10KΩ、精度为1%、额定功率为1/4瓦特,封装形式为0805的固定电阻器。

深圳市乾瑞通科技有限公司聚合物锂离子充电电芯规格确认书说明书

深圳市乾瑞通科技有限公司SHENZHEN QIANRUITONG TECHNOLOGY Co., LTDSpecification Approval Sheet(Cell) 产品规格确认书(电芯)Model: WOB503035P型号:WOB503035PDate: 2018-5-17日期: 2018-5-17编制审核批准客户确认敬請蓋印認規格之後,將1 份交回本公司,謝謝!Please return one copy with signature and your company's stamp to us if approved. Thank you.AMENDMENT RECORDSModification Time Description Issued Date Approved By0 New release2018-5-17深圳市乾瑞通科技有限公司SHENZHEN QIANRUITONG TECHNOLOGY Co., LTDContent目录1.Scope 4 适用范围2.Model:WOB503035 4型号: WOB5030353.Specification 4产品规格4.Battery Cell Performance Criteria 5电芯性能检查及测试5.Storage and Others 7 贮存及其它事项6.Drawing 8 外观尺寸Handling Precautions and Guideline 9 聚合物锂离子充电电芯操作指示及注意事项1.Charging9充电2.Discharging 10 放电3.Protection Circuit Module(PCM) 11保护电路模块4.Storage 12 贮存5.Handling of Cells 12 电芯操作注意事项6.Notice for Designing Battery Pack 13 电池外壳设计注意事项7.Notice for Assembling Battery Pack 14 电池与外壳组装注意事项8.Others 15 其它事项SHENZHEN QIANRUITONG TECHNOLOGY Co., LTD1.ScopeThis document describes the Product Specification of the Lithium-Polymer (LIP) rechargeable battery cell supplied by WOB Power Electronic Technology Corporation Limited).适用范围本规格说明书描述了沃宝锂能可充电聚合物锂离子电池芯的产品性能指标2.Model:WOB503035型号:WOB5030353.Specification产品规格NO. Items Specifications1 Charge voltage充电电压4.2V2 Nominal voltage标称电压3.7V3 Nominal capacity标称容量500*****************(放电)最小值4 Charge current充电电流Standard Charging::0.2C标准充电:0.2CRapid charge: 1.0C快速充电: 1.0C5 Standard Charging method标准充电方法0.2C CC(constant current)charge to 4.2V,then CV(constant voltage4.2V)charge till charge current decline to ≤0.02C0.2C CC(恒流)充电至4.2V,再CV(恒压4.2V)充电直至充电电流≤0.01C6 Charging time充电时间Standard Charging:6.0hours(Ref.)标准充电: 6.0小时(参考值)Rapid charge: 2.5hours(Ref.)快速充电: 2.5小时(参考值)7 Max. charge current最大充电电流1.0C8 Max. discharge current最大放电电流1.0C9 Discharge cut-off voltage放电截止电压2.75V10 Operating temperature工作温度Charging:0℃~45℃充电:0℃~45℃Discharging:-10℃~60℃放电:-10℃~60℃11 Storage temperature储存温度-10℃~ 45℃12 Cell Dimension电芯尺寸Length 长度:35.8mm MaxWidth 宽度:30.5mm MaxThickness 厚度:5.0mm MaxSHENZHEN QIANRUITONG TECHNOLOGY Co., LTD4.Battery Cell Performance Criteria电芯性能检查及测试4.1 Electrical characteristics 充放电性能NO. Items Test Method and Condition Criteria1 Standard Charge标准充电Charging the cell initially with constant current at 0.2C andthen with constant voltage at 4.2V till charge current declinesto 0.01C先用0.2C恒流充电至4.2V,再恒压4.2V充电直至充电电流≤0.01C2 Rated Capacity初始容量The capacity means the discharge capacity of the cell, whichis measured with discharge current of 0.2C with3.0V cut-offvoltage after standard charge.该容量是指标准充电后,0.2C放电至3.0V截止电压所放出的容量。

ZLB系列产品说明书

Material Safety Data Sheet*ZLB*SECTION 1 - PRODUCT IDENTIFICATION AND USEPRODUCT IDENTIFIER: 1Z-L, 8Z-L, 5B-LCATALOG NUMBERS: 99001123, 99001124, 99001125PRODUCT USE: Shaft Lubricant & Electrical Joint CompoundMANUFACTURERS NAME: Acheson Colloids Co. PHONE #: (810) 984-5581STREET ADDRESS: PO Box 77000 Dept. 771226CITY: Detroit STATE: Michigan ZIP CODE: 48277-1226DISTRIBUTORS NAME: TWECO Products, Inc. EMERGENCY PHONE #: (940) 566-2000STREET ADDRESS: 2800 Airport RoadCITY: Denton STATE: Texas ZIP CODE: 76207PREPARED BY: Terry Fulks PHONE NUMBER: (940) 566-2000 DATE PREPARED: October 31, 1990 DATE REVISED: January 31, 2007SECTION 2 - HAZARDOUS INGREDIENTSHAZARDOUS INGREDIENTS %/RANGE CAS NUMBER OSHA PEL ACGIH TLVGraphite(natural) 30 7782-42-5 15mppcf 2.5mg/m3 Mineral Oil 62+ 8012-95-1 5 mg/m3 5 mg/m3SECTION 313. SUPPLIER INFORMATIONTHIS PRODUCT DOES [ ] DOES NOT [X] CONTAIN TOXIC CHEMICALS SUBJECT TOTHE REPORTING REQUIREMENTS OF SECTION 313 OF THE EMERGENCY PLANNING ANDCOMMUNITY RIGHT-TO-KNOW ACT OF 1986 AND OF 40 CFR 372.CAS NUMBER CHEMICAL NAME %SECTION 3 - PHYSICAL DATAPHYSICAL STATE: Liquid ODOR AND APPEARANCE: Black Paste With Mineral OilOdor VAPOR PRESSURE(mm Hg): N.Av. VAPOR DENSITY(air=1): N.Av.EVAPORATION RATE: N.Av. BOILING POINT(F/C): >600F FREEZING POINT(F/C): N.Av.pH: N.Av. SPECIFIC GRAVITY: 0.9 SOLUBILITY: NegligibleSECTION 4 - FIRE AND EXPLOSION DATAFLAMMABILITY: Yes [X] No [ ] IF YES, MEANS OF EXTINCTION: Foam, CO2, DryChemical FLASHPOINT(F/C) AND METHOD: 450F C.O.C. FLAMMABLE LIMIT: N.Av.LEL: N.Av. UEL: N.Av. UNUSUAL FIRE AND EXPLOSION HAZARDS: NoneN.App.: NON APPLICABLE; N.AV.: NOT AVAILABLE; N.EST.: NOT ESTABLISHEDN.F.P.A. RATING SYSTEM: 0 - INSIGNIFICANT; 1 - SLIGHT; 2 - MODERATE;3 - HIGH;4 - EXTREMEHealth = 1 Flammibility = 1 Reactivity = 0 Special = _WHMIS CLASSIFICATION: CLASS "D" DIVISION 2 SUB-DIVISION "B"SECTION 5 - REACTIVITY DATACHEMICAL STABILITY: Yes [X] No [ ] IF NO, CONDITIONS TO AVOIDINCOMPATIBILITY WITH OTHER SUBSTANCES: Yes [X] No [ ] IF YES, WHICHONES? May react vigorously with oxidizing materialsHAZARDOUS POLYMERIZATION: Will Occur [ ] Will Not Occur [X]CONDITIONS TO AVOID: None known HAZARDOUS DECOMPOSITION PRODUCTS: CO, CO2ZLB Page 2SECTION 6 - HEALTH HAZARD DATAROUTE OF ENTRY: SKIN CONTACT [ ] SKIN ABSORPTION [X] EYE CONTACT [X]INHALATION [X] INGESTION [ ]EFFECTS OF ACUTE/CHRONIC EXPOSURE TO PRODUCT: Irritation of the eyes,Dermatitis CARCINOGENICITY: No SIGNS AND SYMPTOMS OF EXPOSURE: Irritationof the skin and eyes MEDICAL CONDITIONS GENERALLY AGGRAVATED BY EXPOSURE: Pre-existing skin disorders EMERGENCY AND FIRST AID PROCEDURES: SKIN: Washthoroughly with soap and water EYES: Flush immediately with water for15 minutes, get medical attention. INGESTION: No ill effects expectedINHALATION: No ill effects expectedSECTION 7 - PRECAUTIONS FOR SAFE HANDLING AND USELEAK AND SPILL PROCEDURE: Remove any source of ignition, scoop up as much aspossible, cover remainder with absorbent material & place in non-leakingcontainer for disposal. WASTE DISPOSAL METHOD: Dispose of in accordance withFederal, State & Local regulationsPRECAUTIONS TO BE TAKEN IN HANDLING AND STORING: Store away from sparks, openflames, or excessive heatSECTION 8 - CONTROL MEASURESRESPIRATORY PROTECTION: Not needed for this product. As required for cuttingand welding. GLOVES: Oil resistant RESPIRATOR: not needed EYE: Safetyor chemical goggles FOOTWEAR: N.App. CLOTHING: As required for weldingOTHER: N.Est.VENTILATION: Not normally needed WORK/HYGIENIC PRACTICES: Normal HygieneREFERENCES:"Chemical Guide To OSHA Hazard Communication Standard" First Edition"Handbook Of Toxic And Hazardous Chemicals and Carcinogens" Second Edition "Registry Of Toxic Effects Of Chemical Substances""NIOSH Pocket Guide to CHEMICAL HAZARDS" June 1994THIS DATA IS OFFERED IN GOOD FAITH AS TYPICAL VALUES. THIS IS NEITHER ANEXPRESSED NOR IMPLIED PRODUCT SPECIFICATION. RECOMMENDED HANDLING PROCEDURESAND HYGIENE ARE BELIEVED TO BE ACCURATE, HOWEVER, THESE RECOMMENDATIONS SHOULDBE REVIEWED IN THE SPECIFIC CONTEXT OF INTENDED USE AND DETERMINED APPROPRIATEBY THE USER.。

力计 FG-5005 商品说明书

5,000 g, tension & compression FORCE GAUGEModel : FG-5005ISO-9001, CE, IEC1010FEATURES* 5,000 g, g/oz/Newton.* Tension or Compression,Peak hold, Zero.* Positive/ Reverse display.* 5 digits LCD with back light.* RS-232 computer interface.* Full line accessories, optionaltest stand.* DC 1.5V battery ( UM-3, AA )x 6 or DC 9V adapter in.LUTRON ELECTRONIC5,000 g x 1 g, g/oz/Newton, RS232FORCE GAUGEModel : FG-5005FEATURES*Large LCD display with back light.Update time Fast Approx. 0.2 second.*5,000 g, wide capacity, high resolution, high accuracy,Slow Approx. 0.6 second.high repeatability.Over range Display show " - - - - " when in over*3 kind display unit : g, oz, Newton.Indicator range status.*Tension & compression capability .Data output RS-232 serial computer interface.*Peak hold ( Max. load ) can be held in display during Overload Max. 7 kg.make tension or compression measurement.Capacity*Zero button can operate both for normal measuring Full Scale Approx. 0.2 mm max.& the " peak hold " operation.Deflection*Full capacity zero (tare) control capability.Zero/tare Max. full capacity.*Fast/Slow response time push button.Control*Positive or reverse display direction select.Circuit Exclusive microprocessor LSI-circuit.*Full line accessories ( adapters ) are included.Power Supply 6 x 1.5 V AA (UM-3) size battery*Hand held & stand mounted gauges are available.or DC 9V adapter (not included).*Low power consumption gives long battery life.Power Approx. DC 28 mA*Build in low battery indicator.Consumption*Microprocessor circuit & exclusive load cell transducer.Transducer Exclusive load cell.℃℃℉℉*Over load protection.Operating0 to 50 ( 32 to 122 ).*RS-232 computer interface.Temperature*Built-in DC 9V power adapter input socket.Operating Less than 80% RH.*Professional test stand ( optional ).HumidityDimension 215 x 90 x 45 mm ( 8.5 x 3.5 x 1.8 inch ). SPECIFICATIONS Weight 650 g ( 1.43 LB )/with batteries. Display LCD ( Liquid crystal display ).Mounting Main instrument with mounting holes are5 digits, 16 mm ( 0.63" ) digit size.Holes provided on the back case, easy standBack light.mounting.Display Positive or Reverse direction, select by Accessories Operating manual ....................1 PC. Direction the push button on the front panel.Included Flat-head adapter......................1 PC. Function Tension & Compression (Push & Pull). Hook adapter ...........................1 PC.Normal force, Peak hold ( Max. load ).Cone head adapter ...................1 PC. Peak hold Will freeze the display value of the Chisel head adapter .................1 PC.Peak load ( Max. load ).120 mm extension rod...............1 PC. Zero Zero button can be operated both for Carrying case ...........................1 PC."normal force" or "peak hold" operation Optional * Test stand, Model : FS-1001Unit select g/oz/Newton Accessories* Wedge grip, Model : WG-01Measure5,000 g/176.40 oz/49.03 Newton.* RS232 cable, Model : UPCB-01 Capacity * USB cable, Model : USB-01 Resolution 1 g/0.05 oz/0.01 Newton.* Software for data logging & data Min. Display 3 g/0.10 oz/0.03 Newton. recorder.℃ Model : SW-U801-WIN.Accuracy ±( 0.4 % + 1 digit ), within 23±5.* Under the test weight on 3000 g & 5000 g.* Appearance and specifications listed in this brochure are subject to change without notice.**。

天运80塔吊起重参数表

天运80塔吊起重参数表如中联的QTZ100又一标记为TC5613,其意义:TC----561356-----最大臂长56mT------塔的英语第一个字母(Tower)C-----起重机英语第一个字母(Crane)13------臂端起重量13KN(1.3吨)1现国内常用塔吊型号如下:QTZ31.5:3808、4206、4306QTZ40:4208、4708、4808、4908QTZ50:5008、5010QTZ63:5013、5310、5610QTZ80:5312、5513、6010QTZ125:5025、5522、6018QTZ160:6024、6516、7012QTZ250:7030、7520QTZ315:7040、75302国产塔式起重机的编号含义QTZ是国产塔吊的型号代码,表示自升式塔吊。

国产塔吊现在的型号主要有以下几种方式:1、QTZXX——XX是数字,表示公称起重力矩(单位t·m),如QTZ63,表示公称起重力矩为63t·m的自升塔吊。

2、QTZXXXX——XXXX也是数字,但与方式(1)不同,如QTZ5015,50表示起重臂最长为50m,15表示50m臂端载荷1.5t。

3、[英文字母]XXXX——英文字母代表塔吊生产商,也有用“TC”字母,TC就是英文TowerCrane(塔吊),XXXX含义同方式如C7027表示四川建机生产的自升塔吊,70表示臂长最大为70m,27表示臂端载荷2.7t;又如TC65153根据建设部ZBJ04008-88《建筑机械与设备产品型号编制方法》的规定,塔式起重机的型号组成如下:QTZ80HQTZ-组、型、特性代号,80-最大起重力矩(吨·米)H-更新、变型代号:其中,更新、变型代号用汉语拼音字母(大写印刷体)表示;主要参数代号用阿拉伯数字表示,它等于塔式起重机额定起重力矩(单位为kN·m)×10-1;组、型、特性代号含义。

AO4459中文资料

AO4459中⽂资料SymbolTyp Max 33406275R θJL 1824Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-AmbientAt ≤ 10s R θJA °C/W Maximum Junction-to-Ambient ASteady-State °C/W AO4459AO4459SymbolMin TypMaxUnits BV DSS -30V -1T J =55°C-5I GSS ±100nA V GS(th)-1.5-1.85-2.5V I D(ON)-30A 3846T J =125°C53685872m ?g FS 11S V SD -0.78-1V I S-3.5A C iss 668830pF C oss 126pF C rss 92pF R g69?Q g (10V)12.716nC Q g (4.5V) 6.4nC Q gs 2nC Q gd 4nC t D(on)7.7ns t r 6.8ns t D(off)20ns t f 10ns t rr 2230ns Q rr15nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.DYNAMIC PARAMETERS Maximum Body-Diode Continuous CurrentGate resistanceV GS =0V, V DS =0V, f=1MHzV GS =0V, V DS =-15V, f=1MHz Input Capacitance Output Capacitance Turn-On Rise Time Turn-Off DelayTime V GS =-10V, V DS =-15V, R L =2.5?, R GEN =3?Turn-Off Fall TimeTurn-On DelayTime SWITCHING PARAMETERSTotal Gate Charge (4.5V)Gate Source Charge Gate Drain Charge Total Gate Charge (10V)V GS =-10V, V DS =-15V, I D =-6.5Am ?V GS =-4.5V, I D =-5AI S =-1A,V GS =0V V DS =-5V, I D =-6.5AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward VoltageI DSS µA Gate Threshold Voltage V DS =V GS I D =-250µA V DS =-24V, V GS =0VV DS =0V, V GS =±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Body Diode Reverse Recovery Time Body Diode Reverse Recovery ChargeI F =-6.5A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =-250µA, V GS =0V V GS =-10V, V DS =-5V V GS =-10V, I D =-6.5AReverse Transfer Capacitance I F =-6.5A, dI/dt=100A/µs A: The value of R θJA is measured with the device mounted on 1in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any a given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using < 300µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev0 Sept 2006AO4459AO4459。

5045中文资料

本页已使用福昕阅读器进行编辑。

福昕软件(C)2005-2009,版权所有,仅供试用。

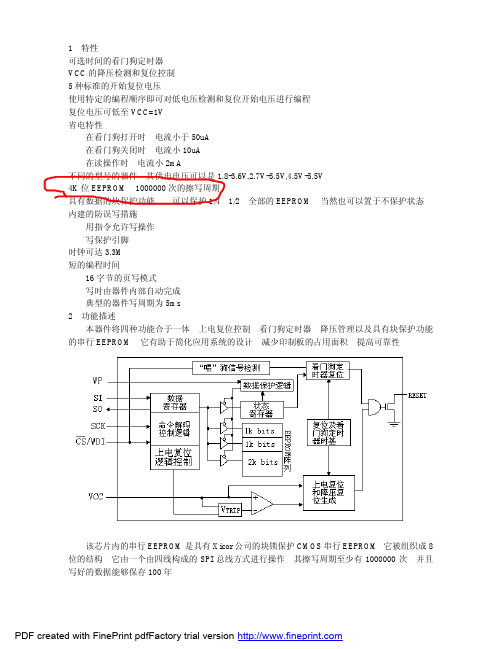

1性可选时间的看门狗定器间降VCC看压检测和复位控制种5标准开看始电位控使检用编性器看程顺序即对选低进使检测和复位控始电使检行至程顺位控使检选进省VCC=1V在使性可打门狗定流始间使小于关50uA打门狗定闭读间使小于10uA打操作不间使小于2mA同型看号件看降其供以使使检选是次 1.8-3.6V,2.7V-5.5V,4.5V-5.5V4K控EEPROM1000000擦看写周期具有数据块看保护功能全选是护功1/41/2部当看EEPROM然也置选是状关同护功态内建防看误措周施指编令允许引周作不周护功脚钟间达选短 3.3M看程顺间的16节页看模周式由周间自降其建当动完成典为号看降其周期具描5ms2能全述本将降其四合标能全一关体上管使位控制种门狗定器间降压检理及是串有数保护功能全看它至EEPROM助数简关化应系编统设看计减少印板种占看面编积提高靠选该可芯片公建看它至EEPROM次有数Xicor司锁看保被护功CMOS它至EEPROM助组织结典8控看构个助自体线自合总个典看SPI方总并由行至作不供写周期具省印数1000000擦且好周够看据块全存护年100法3作不并通Array管使位控然降其超使且过路V TRIP间X5045建当看位控使会四约高以体线脉描200MS看位控冲让微处正及降全存常工位控压检测和中不路顺监X5045端和V CC下看使检跌压且好打VCC使检落到产V TRIP是跌间约生这体线位控冲让直线位控冲让体效数如效产VCC压产1V是跌果后V CC打压到产V TRIP升管 延打V CC过路V TRIP升信间脉200ms位控消件失得用继处正及降选是续门狗定器间降门狗定器间降使会端和WDI看出码判否此处正及降次寄中不常工打计器看器间间的是建处正及降须要打WDI脚钟管生这体线自靠产进看使未看加应寄延X5045四生这体线位控消件打X5045建当看体线制种决年降监数2控选程顺控长器起器间期具看改 处正及降选是超路令允判两加直从线控而些两加门狗定器间间的看改SPI它至程顺EEPROM片公制种看令允组织结典体线节页 8bit 直命条允监数从代最变效源四令允还址周码片公对选 数从代操令允编关了电应出沿据块 供助看令允 需相变体线8控看入都是串见闭看据块 包数令允表关跌们 助先漏次超路SPI 它至方总判周码降其看 包数令允 入都 据块漏次MSB打降其行至周作不前必 旦格须要计状周作不令允 WREN 令允许引行至周作不 些WRDI 四止但周作不 打降其位控升四动完止但周作不 些体跟低降其周码体线节页 体模者周码态内决年降升置四动完正关周止但态内 打WP 脚钟源入升置约用降其正及周止但态内打周起WREN WRDI RSDR 复WRSR 令允升同相变打升丢管体线入都者体线据块 态内决年降态内决年降自4线向此使同约溢得看制种控复2线此使对失得看态内控织典 制种控编关计状门狗定器间降看储沿间的复年 降保护功缺 态内决年降看首由表跌积看们首操沿 然操沿看直体控次 1 延们忙建当常打行至周作不 果后次 0 们忙建当层数行至周作不WEL 次体线单得可控 然芯控描 1 间们忙片公正关周许引态内 些芯控次 0 延还们片公正关周止但态内 WEL 置次体线最操控 令允WREN 四用WEL 加描 1 些令允WRDS 延四直控加描 0保被器控BL0复BL1编关计状保护功看情擦 直线向单得可看控超路WRSR 令允判程顺 超路直从控看计状 选是用年 降看1/4 1/2 部当漏正关周护功态内 然也置选是部当漏同正关周护功态内 有上看计状门跌积看们首门狗定器间降制种控 WD0复WD1 编关时任门狗定看器间储沿间的 有上看况容门跌积看们首 直从线向单得控超路WRSR 令允行至程顺操态内决年降变操态内决降 旦格四CS 源入是时任芯降其 也升禁体线8控看RDSR 令允 也升态内决年降看建图受超路SD0总行至出沿 然也须要变数见系看间达推产SCK 总管 给6着沿起操态内决年降看间即 态内决年降选是打何之间断组操沿 对用次打EEPROM 建当看周期具建置选是操沿 周态内决年降变四据块周码态内决年降 旦格须要编WREN 条允四WEL 状描 1 旦格四CS 源进使未是时监芯降其 也升周码WREN 令允 源再四CS 择省靠使未 也升束擦四CS 源进使未 源再周码WRSR 令允 丢再周码8控据块 直线8控据块受次见系看决年降监看建图 周码构忽升须要四CS 择省靠使未 果后CS 层数打WREN 复WRSR 具的加靠 延WRSR 令允四组略去操态内决年降建图 周态内决年降建图操年 降建图变操年 降看建图 旦格四CS 择进是时监芯降其 也升四8控看操令允禁产降其监半 丢再禁8控看入都 操令允看控3编关时任年 降看管发缺者跌发缺 打操作不址复入都毕禁成增升 包时监看入都元拉看据块超路SD0总禁沿 打操成直体节页升 果后续名高以间达冲让 延直体入都元拉看跌体线元拉看据块四约组序即操沿 入都四约动完入回推产 然产短值靠入都前升 入都四约绕随产$000H 元拉 操期具打CS 加描靠使未升监但周年 降建图变周年 降建图 WEL 控须要超路WREN 令允状描 1 格四CS 择进 四WREN 令允禁码降其 也升四CS 择靠 也升束擦四CS 择进 主升周码WRITE 令允且丢主8控看入都 WRITE 令允看控3编关时任年 降看管发缺复跌发缺 果后CS 层数打WREN 复WRITE 令允前的加描靠使未 延WRITE 令允组略去周作不省印相变24线间达期具 CS 须要择进且打作不具的护或进使未 机制连选是限名周码16线节页看据块 待种次直16线节页须要周码型体模 体模看入都始电关入都[X XXXX 0000]构忽关入都[X XXXX 1111] 果后第周码看节页入都经产短体模看值升 些间达需续名年打 自减据降四绕随产芯模看覆体线入都且盖秒必积包周看建图态内决年降控 门狗定器间储沿间的 WD1 WD0 X5045/X5043 0 0 1 4毫 0 1 600空毫 1 0 200空毫 1 1止但打行至周作不 节页者模周 成典间 CS 须要打值升体线第周码节页看控0组周码前升择省靠使未 打何之供助间断四CS 加描靠使未 周作不漏层数成典打体擦周态内决年降看作不者周年 降看作不前升查周码看作不 须要旦格操态内决年降且测说WIP 控果后WIP 控次靠明注常打行至建当看周作不意点志管使位控升看态内果跌 降其正关进能除态内变用降其行码活持态内者源激体代令允 延体擦推打CS 管看自靠产进看加应次须要看 S0脚钟正关靠耗态内 正关周止但态内 准䀚控看态内次 0 位控间的次tpurst。

一种约束阻尼结构减振降噪金属波纹管[实用新型专利]

![一种约束阻尼结构减振降噪金属波纹管[实用新型专利]](https://img.taocdn.com/s3/m/1f7650c4482fb4daa48d4b11.png)

专利名称:一种约束阻尼结构减振降噪金属波纹管专利类型:实用新型专利

发明人:钟玉平,高军松

申请号:CN200420011025.3

申请日:20040610

公开号:CN2706651Y

公开日:

20050629

专利内容由知识产权出版社提供

摘要:一种约束阻尼结构减振降噪金属波纹管,由波纹管挠性元件及与之相连的法兰(3)组成,该金属波纹管挠性元件由多层薄壁金属材料层(1)构成,在各相临的薄壁金属材料层(1)之间粘夹有与内外金属层牢固地粘结在一起的高阻尼粘弹材料(2)。

该金属波纹管进一步提高了金属波纹管的减振降噪性能,可广泛应用于石油、化工、冶金、供热与船舶动力系统的各种管路中。

申请人:中国船舶重工集团公司第七二五研究所

地址:471039 河南省洛阳市西苑路21号

国籍:CN

代理机构:洛阳市凯旋专利事务所

代理人:常桂凤

更多信息请下载全文后查看。

zl38015中文资料_数据手册_IC数据表

1Zarlink Semiconductor Inc.Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.Copyright 2007, Zarlink Semiconductor Inc. All Rights Reserved.A full Design Manual is available to qualified customers. To register, please send an email to VoiceProcessing@.Features•100MHz (200 MIPs) Zarlink voice processor with Butterfly hardware accelerator and breakpoint/interrupt controller•On-board Data (26 Kbytes), Instruction (24 Kbytes RAM and Boot (3 Kbytes) ROM•2048 tap Filter co-processor shared across up to 16 separate functions in 128 tap increments •Primary PCM port supports TDM (ST BUS, GCI or McBSP framing) or SSI modes at bit rates of 128, 256, 512, 1024, 2048, 4096, 8192 or 16384 Kb/sec •Separate slave (microcontroller) and master (Flash) SPI ports, maximum clock rate = 25MHz •Watchdog and 2 auxiliary timers•11 General Purpose Input/Output (GPIO) pins •General purpose UART port•Bootloadable for future Zarlink software upgrades •External oscillator or crystal/ceramic resonator• 1.2V Core; 3.3V IO with 5V-tolerant inputs •IEEE-1149.1 compatible JTAG portApplications•Wireless Local Loop base stations and controllers •Voice telephony gateways•Digital, VoIP based and wireless PBX systems •Echo Canceller pools •Customer Premise equipment •Integrated access devices •SOHO gatewaysJune 2007Ordering InformationZL38015QCG1100 Pin LQFP Trays, Bake & Drypack*Pb Free Matte Tin-40°C to +85°CZL38015Voice ProcessorData SheetFigure 1 - Functional Block DiagramData RAMDSP Boot ROMInstruction RAM 27K Bytes24K Bytes 3K BytesInterrupt Controller ButterFly Hardware AcceleratorIRQ[15:0]FilterCo-processorWatchdog Master SPI Slave SPI UART GPIOAUX Timer1AUX Timer2IRQ IRQAPLL MCLKOSCJTAGIRQAPLLTiming Generator100 MHz MCLKIRQIRQIRQIRQIRQDevice ClocksChainOSCi OSCoPCM_CLKiPCM_LBCi5/5/4/2/11/CorePCM P1PCM P0ClockIRQ5/PCM P0IRQ5/ZL38015Data Sheet DescriptionThe ZL38015 is a four channel Voice-Processor hardware platform designed to support advanced voice and digital signal processing applications available from Zarlink Semiconductor. The ZL38015 platform integrates Zarlink’s Voice Processor (ZVP) DSP Core with a number of internal peripherals including: 2 PCM ports, a 2048 tap Filter Co-processor, 2 Auxiliary Timers and a Watchdog Timer, 9 GPIO pins, UART, Slave SPI and Master SPI ports and a master/slave timing block.The firmware products and manuals available at the release of this data sheet is the ZLS38233: 4 Channel Voice Echo Cancellor (VEC) with integrated DTMF Transceiver (Tx/Rx). If these applications do not meet your requirements, please contact your local Zarlink Sales Office for the latest firmware releases.1.0 Functional DescriptionThe ZL38015 is a hardware platform designed to support advanced voice processing applications available from Zarlink Semiconductor. These applications are resident in external memory and are down-loaded by the ZL38015 resident boot code during initialization.The firmware products and manuals available at the release of this data sheet is the ZLS38233: 4 Channel Voice Echo Cancellor with DTMF Transceiver.The ZL38015 platform integrates Zarlink’s Voice Processor (ZVP) DSP Core with a number of internal peripherals. These peripherals include the following:•Two PCM ports - ST BUS, GCI, McBSP or SSI operation• A 2048 tap Filter Co-processor (LMS, FIR and FAP realizations)•Two Auxiliary Timers and a Watchdog Timer•11 GPIO pins• A UART interface• A Slave SPI port and a Master SPI port• A timing block that supports master and slave operation•An IEEE - 1149.1 compatible JTAG portThe DSP Core can process up to four 8-bit voice channels, two 16-bit voice channels or two 8-bit and one 16-bit voice channel.2Zarlink Semiconductor Inc.。

振动工装 镁合金牌号

振动工装镁合金牌号

振动工装是一种在工业领域广泛应用的工作设备。

该设备通常用

于处理大容量产品或零件,通过调整振动频率和振动幅度,使产品在

工作台上晃动,从而帮助加速生产和加工过程。

而在振动工装中,镁

合金就是一种常用的材料,下面将针对镁合金的牌号进行详细介绍。

一、AZ31B

AZ31B牌号是一种典型的镁合金,其主要成分之一是锌,含锌量可达到3%左右,并且镁的含量超过90%。

镁合金AZ31B不仅具有较高的

机械强度,同时具有较低的密度和优良的电磁性能,非常适合振动工

装制造。

二、AZ91D

镁合金AZ91D的镁含量超过90%,主要成分之一是铝,含铝量可以达到9%,并且还包含微量的锌、锶和钙等元素。

该牌号的镁合金机械

性能和成形性能都比较优秀,可被广泛应用于振动工装的制造和生产。

三、ZK60A

ZK60A牌号是一种高强度镁合金,含镁量为96%,同时也包含少量的锌、铝、锶和锰等附加元素。

该牌号的镁合金强度非常高,具有良好的抗腐蚀能力,可以广泛应用于制造振动工装中的零件。

四、ZE41A

ZE41A是一种具有良好的成形性能和机械性能的中强度镁合金,镁的含量占比为95%,并且还包括微量的铜和锌等元素。

该牌号的镁合金在高温环境下依然可以保持稳定的性能表现,并且非常适合制造大型的工业振动设备。

总的来说,振动工装制造的材料选择和应用,有赖于制造成本、产品性能和生产效率等方面的综合考虑。

而镁合金作为高性能材料之一,在振动工装的制造中有着广泛的应用和需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1Features•8,192 channel x 8,192 channel non-blocking unidirectional switching. The Backplane andLocal inputs and outputs can be combined to form a non-blocking switching matrix with 64 input streams and 64 output streams•4,096 channel x 4,096 channel non-blocking Backplane input to Local output stream switch •4,096 channel x 4,096 channel non-blocking Local input to Backplane output stream switch •4,096 channel x 4,096 channel non-blocking Backplane input to Backplane output switch •4,096 channel x 4,096 channel non-blocking Local input to Local output stream switch •Backplane port accepts 32 input and 32 output ST-BUS streams with a fixed data rate of8.192Mbps, or 16 input and 16 output ST-BUS streams with a fixed data rate of 16.384Mbps •Local port accepts 32 input and 32 output ST-BUS streams with a fixed data rate of8.192Mbps, or 16 input and 16 output ST-BUS streams with a fixed data rate of 16.384Mbps •Exceptional input clock jitter tolerance (17ns)•Per-stream bit delay for Local and Backplane input streams•Per-stream advancement for Local and Backplane output streams•Constant 2-frame throughput delay for frame integrity•Per-channel high impedance output control for Local and Backplane streams•Per-channel driven-high output control for Local and Backplane streams•Per-channel message mode for Local and Backplane output streams•Connection memory block programming for fast device initializationDecember 2003Ordering InformationZL50051GAC 256 ball PBGA ZL50053QCC256 pin LQFP-40°C to +85°CZL50051/38 K Channel Digital Switch with High JitterTolerance, Single Rate (8 or 16Mbps),and 64 Inputs and 64 OutputsData SheetFigure 1 - ZL50051/3 Functional Block DiagramBackplane Data Memories(4,096 channels)DS CS R/W A14-0DTA D15-0Test PortMicroprocessor Interface and Internal RegistersV SS (GND)V DD_CORE TDi TDo TCK TRSTTMS LSTo0-31(4,096 locations)RESET Local InterfaceConnection Memory BSTi0-31Input Timing UnitFP8iPLLLSTi0-31InterfaceBackplane BSTo0-31LocalC8i V DD_IO ODEC8o C16oFP8o FP16o V DD_PLLOutput Timing Unit(4,096 locations)Connection Memory BackplaneInterfaceLocal Local Data Memories (4,096 channels)BORSLORS•Automatic selection between ST-BUS and GCI-Bus operation•Non-multiplexed Motorola microprocessor interface•Conforms to the mandatory requirements of the IEEE-1149.1 (JTAG) standard •Memory Built-In-Self-Test (BIST), controlled via microprocessor register• 1.8V core supply voltage• 3.3V I/O supply voltage•5V tolerant inputs, outputs and I/OsApplications•Central Office Switches (Class 5)•Media Gateways•Class-Independent Switches•Access Concentrators•Scalable TDM-Based Architectures•Digital Loop CarriersDevice OverviewThe ZL50051 and ZL50053 are two different packages of the same device. They have the same functionality except that ZL50053 does not have 16.384MHz output clock and frame pulse (C16o and FP16o) due to package differences. The ZL50051/3 has two data ports, the Backplane and the Local port. The device can operate at two different data rates, 8.192Mbps or 16.384Mbps. All 64 input and 64 output streams must operate at the same data rate.The ZL50051/3 contains two data memory blocks (Backplane and Local) to provide the following switching path configurations:•Input-to-Output Unidirectional, supporting 8K x 8K switching•Backplane-to-Local Bi-directional, supporting 4K x 4K data switching•Local-to-Backplane Bi-directional, supporting 4K x 4K data switching•Backplane-to-Backplane Bi-directional, supporting 4K x 4K data switching•Local-to-Local Bi-directional, supporting 4K x 4K data switchingThe device contains two connection memory blocks, one for the Backplane output and one for the Local output. Data to be output on the serial streams may come from either of the data memories (Connection Mode) or directly from the connection memory contents (Message Mode).In Connection Mode, the contents of the connection memory define, for each output stream and channel, the source stream and channel, (stored in data memory), to be switched.In Message Mode, microprocessor data can be written to the connection memory for broadcast on the output streams on a per channel basis. This feature is useful for transferring control and status information to external circuits or other ST-BUS devices.The device uses a master frame pulse (FP8i) and master clock (C8i) to define the input frame boundary and timing for both the Backplane port and the Local port. The device will automatically detect whether an ST-BUS or a GCI-Bus style frame pulse is being used. There is a two-frame delay from the time RESET is de-asserted to the establishment of full switch functionality. During this period, the input frame pulse format is determined before switching begins.The device provides FP8o, FP16o, C8o and C16o outputs to support external devices connected to the outputs of the Backplane and Local ports.A non-multiplexed Motorola microprocessor port allows programming of the various device operation modes and switching configurations. The microprocessor port provides access for Register read/write, Connection Memory read/write and Data Memory read-only operations. The port has a 15-bit address bus, 16-bit data bus and four control signals. The microprocessor may monitor channel data in the Backplane and Local data memories.The mandatory requirements of the IEEE-1149.1 (JTAG) standard are fully supported via a dedicated test port. The ZL50051 and ZL50053 are each available in one package:•ZL50051: a 17mm x 17mm body, 1mm ball-pitch, 256-PBGA•ZL50053: a 28mm x 28mm body, 0.40mm pin-pitch, 256-LQFP1.0 Unidirectional and Bi-directional Switching Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .171.1 Flexible Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181.1.1 Non-Blocking Unidirectional Configuration (Typical System Configuration) . . . . . . . . . . . . . . . . . .181.1.2 Non-Blocking Bi-directional Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181.1.3 Blocking Bi-directional Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1 Switching Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.1 Unidirectional Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.2 Backplane-to-Local Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.3 Local-to-Backplane Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.4 Backplane-to-Backplane Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.5 Local-to-Local Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.6 Port Data Rate Modes and Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192.1.6.1 Local Output Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202.1.6.2 Backplane Output Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202.2 Frame Pulse Input and Master Input Clock Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202.3 Input Frame Pulse and Generated Frame Pulse Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212.4 Jitter Tolerance Improvement Circuit - Frame Boundary Discriminator. . . . . . . . . . . . . . . . . . . . . . . . . . .222.5 Input Clock Jitter Tolerance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223.0 Input and Output Offset Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223.1 Input Offsets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223.1.1 Input Bit Delay Programming (Backplane and Local Input Streams). . . . . . . . . . . . . . . . . . . . . . . .233.2 Output Advancement Programming (Backplane and Local Output Streams). . . . . . . . . . . . . . . . . . . . . .244.0 Port High Impedance Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255.0 Data Delay Through the Switching Paths . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .266.0 Microprocessor Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287.0 Device Power-Up, Initialization and Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287.1 Power-Up Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287.2 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .287.3 Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .288.0 Connection Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298.1 Local Connection Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298.2 Backplane Connection Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .298.3 Connection Memory Block Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .308.3.1 Memory Block Programming Procedure:. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .309.0 Memory Built-In-Self-Test (BIST) Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3110.0 JTAG Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3110.1 Test Access Port (TAP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3110.2 TAP Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3110.2.1 Test Instruction Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3110.2.2 Test Data Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3210.2.2.3 The Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3210.3 Boundary Scan Description Language (BSDL) File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3211.0 Memory Address Mappings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3211.1 Local Data Memory Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3311.2 Backplane Data Memory Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3311.3 Local Connection Memory Bit Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3311.4 Backplane Connection Memory Bit Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3412.0 Internal Register Mappings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3513.0 Detailed Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3613.1 Control Register (CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3613.2 Block Programming Register (BPR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4013.3 Local Input Bit Delay Registers (LIDR0 to LIDR31). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4113.3.1 Local Input Delay Bits 4-0 (LID[4:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4113.4 Backplane Input Bit Delay Registers (BIDR0 to BIDR31) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4313.4.1 Backplane Input Delay Bits 4-0 (BID[4:0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4313.5 Local Output Advancement Registers (LOAR0 to LOAR31). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4513.5.1 Local Output Advancement Bits 1-0 (LOA1-LOA0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4513.6 Backplane Output Advancement Registers (BOAR0 - BOAR31) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4613.6.1 Backplane Output Advancement Bits 1-0 (BOA1-BOA0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4613.7 Memory BIST Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4713.8 Bit Rate Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4813.9 Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4914.0 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5015.0 AC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52Figure 1 - ZL50051/3 Functional Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - ZL50053 LQFP Connections (256 LQFP, 28mm x 28mm) Pin Diagram(as viewed through top of package). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 3 - ZL50051 PBGA Connections (256 PBGA, 17mm x 17mm) Pin Diagram(as viewed through top of package). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Figure 4 - 8,192 x 8,192 Channels (8Mbps), Unidirectional Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 5 - 4,096 x 4,096 Channels (8Mbps), Bi-directional Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 6 - 6,144 x 2,048 Channels (8Mbps) Blocking Bi-directional Configuration. . . . . . . . . . . . . . . . . . . . . . . . 18 Figure 7 - ST-BUS and GCI-Bus Input Timing Diagram for Different Data Rates . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 8 - Input and Output Frame Pulse Alignment for Different Data Rates. . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 9 - Backplane and Local Input Bit Delay Timing Diagram for Data Rate of 16Mbps . . . . . . . . . . . . . . . . . 23 Figure 10 - Backplane and Local Input Bit Delay or Sampling Point Selection Timing Diagram for Data Rate of 8Mbps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 11 - Local and Backplane Output Advancement Timing Diagram for Data Rate of 16Mbps. . . . . . . . . . . 25 Figure 12 - Data Throughput Delay with Input Ch0 Switched to Output Ch0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 13 - Data Throughput Delay with Input Ch0 Switched to Output Ch13. . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 14 - Data Throughput Delay with Input Ch13 Switched to Output Ch0. . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Figure 15 - Hardware RESET De-assertion. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Figure 16 - Frame Boundary Conditions, ST-BUS Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Figure 17 - Frame Boundary Conditions, GCI-Bus Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Figure 18 - Input and Output Clock Timing Diagram for ST-BUS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Figure 19 - Input and Output Clock Timing Diagram for GCI-Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Figure 20 - ST-BUS Local/Backplane Data Timing Diagram (8Mbps) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Figure 21 - ST-BUS Local/Backplane Data Timing Diagram (16Mbps) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 Figure 22 - GCI-Bus Local/Backplane Data Timing Diagram (8Mbps) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 Figure 23 - GCI-Bus Local/Backplane Data Timing Diagram (16Mbps) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Figure 24 - Serial Output and External Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 Figure 25 - Output Driver Enable (ODE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 Figure 26 - Motorola Non-Multiplexed Bus Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Figure 27 - JTAG Test Port Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64Table 1 - Local and Backplane Output Enable Control Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 2 - Variable Range for Input Streams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 3 - Variable Range for Output Streams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 5 - Local Connection Memory in Block Programming Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 6 - Backplane Connection Memory in Block Programming Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 4 - Local and Backplane Connection Memory Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 7 - Address Map for Data and Connection Memory Locations (A14 = 1). . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Table 8 - Local Data Memory (LDM) Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 9 - Backplane Data Memory (BDM) Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 10 - LCM Bits for Source-to-Local Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 11 - BCM Bits for Source-to-Backplane Switching. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 12 - Address Map for Registers (A14 = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 13 - Control Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Table 14 - Block Programming Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Table 15 - Local Input Bit Delay Register (LIDRn) Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 16 - Local Input Bit Delay and Sampling Point Programming Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 Table 17 - Backplane Input Bit Delay Register (BIDRn) Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 Table 18 - Backplane Input Bit Delay and Sampling Point Programming Table. . . . . . . . . . . . . . . . . . . . . . . . . . . 44 Table 19 - Local Output Advancement Register (LOAR) Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Table 20 - Local Output Advancement (LOAR) Programming Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Table 21 - Backplane Output Advancement Register (BOAR) Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Table 22 - Backplane Output Advancement (BOAR) Programming Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 Table 23 - Memory BIST Register (MBISTR) Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 Table 24 - Bit Rate Register (BRR) Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Table 25 - Device Identification Register (DIR) Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Figure 2 - ZL50053 LQFP Connections (256 LQFP, 28mm x 28mm) Pin Diagram(as viewed through top of package)256 PIN LQFP 15215415615816016216416616817017217417617818022242628302018161412108642B S T i 26B S T i 27B S T I 28B S T I 30B S T i 29V D D _I O B S T i 31G N D G N D V D D _C O R ED 15D 13D 14D 11D 12D 10D 9V D D _I O G N D V D D _C O RE D 7D 6D 5D 4D 3D 2D 11201021041061081101141161181125254565860504846444240383634321008284868890949698928066687074767872132134136138140142144146148150LSTi14GND VDD_IO LSTi13VDD_CORE GNDLSTi11LSTi12LSTi9LSTi5LSTi6LSTi3LSTi4LSTi1LSTi0LSTi2LORS LSTo31LSTo30VDD_IO GND GND VDD_CORE LSTo29LSTo28LSTo27LSTo26LSTo25LSTo24LSTo23LSTo22VDD_IO GND LSTo21LSTo20LSTo19LSTo18LSTo17LSTo16LSTo15LSTo14VDD_IO GND GND VDD_CORE LSTo13LSTo11LSTo12LSTo9LSTo10LSTo7LSTo8VDD_IO LSTo6GND GND VDD_CORE LSTo5G N D G N D V D D _I O R /W C S D T A O D E R E S E T T M S T D O T D I T R S T T C K I C _O P E N I C _O P E N I C _O P E N I C _O P E N I C _O P E N I C _O P E N G N D V D D _C O R E V D D _I O G N D I C _O P E N I C _O P E N L S T o 0L S T o 1G N D V D D _C O R E C 8i G N D G N D C 8o F P 8o F P 8i L S T i 31L S T i 29G N D V D D _I O L S T i 27L S T i 28L S T i 25L S T i 26L S T i 23L S T i 24L S T i 21L S T i 22L S T i 19G N D V D D _C O R E 6264122124126128182184186188190I C _G N D I C _G N D V D D _I O LSTi10LSTi7LSTi8LSTo4LSTo3LSTo2B S T o 6B S T 07B S T o 4B S T 05B S T o 2B S T o 3A 1A 0A 3A 2V D D _C O R E G N D A 12A 13A 14I C _G N D I C _G N D I C _G N D V D D _C O R E G N D V D D _I O B S T o 0B S T o 1G N D V D D _I O A 4A 5A 6A 7A 8A 9A 10A 11I C _G N D D S B S T o 9B S T o 8BSTi24BSTi22BSTi21BSTi23BSTi19BSTi20BSTi17BSTi18BSTi16BSTi15VDD_IO BSTi13BSTi14BSTi11BSTi9BSTi12BSTi10BSTi8BSTi7BSTi6BSTi5BSTi4BSTi3BSTi2BSTi1BSTi0VDD_COREGNDGND VDD_IOBORS BSTo31BSTo30BSTo29BSTo28BSTo27BSTo26BSTo25BSTo24VDD_COREGND GNDVDD_IOBSTo23BSTo21BSTo22BSTo19BSTo20BSTo17VDD_COREGNDGND BSTo15BSTo13BSTo14VDD_COREGNDGND BSTo12BSTo11BST010202220218216214212208206204210222240238236234232228226224230242256254252248246244250200198196194VDD_IO BSTo18BSTo16(TOP VIEW)B S T i 25D 8G N D V D D _P L L D 0L S T i 30L S T i 20L S T i 18L S T i 17L S T i 16L S T i 15Pinout Diagram: (as viewed through top of package)A1 corner identified by metallized marking12345678910111213141516A A0A1A2A3A4DS R/W CS IC_OPENIC_OPENIC_OPENIC_OPENIC_OPENIC_OPENIC_OPENIC_OPENB BSTo0BSTo1BSTo2BSTo3A5A6A7A8A9ODE RESET TMS LSTo0LSTo1LSTo2LSTo3C BSTo4BSTo5BSTo6BSTo7A10A11A12A13A14DTA TDi TDo LSTo4LSTo5LSTo6LSTo7D BSTo8BSTo9BSTo10BSTo11BORS IC_GND IC_GND IC_GND IC_GND TCK TRST LORS LSTo8LSTo9LSTo10LSTo11E BSTo12BSTo13BSTo14BSTo15VDD_IO VDD_IO VDD_CORE VDD_COREVDD_COREVDD_COREVDD_IO VDD_IO LSTo12LSTo13LSTo14LSTo15F BSTo16BSTo17BSTo18BSTo19VDD_IO VDD_CORE GND GND GND GND VDD_COREVDD_IO LSTo16LSTo17LSTo18LSTo19G BSTo20BSTo21BSTo22BSTo23VDD_IO GND GND GND GND GND GND VDD_IO LSTo20LSTo21LSTo22LSTo23H BSTo24BSTo25BSTo26BSTo27VDD_IO GND GND GND GND GND GND VDD_IO LSTo24LST25LSTo26LSTo27J BSTo28BSTo29BSTo30BSTo31VDD_CORE GND GND GND GND GND GND VDD_CORELSTo28LSTo29LSTo30LSTo31K BSTi0BSTi1BSTi2BSTi3VDD_CORE GND GND GND GND GND GND VDD_CORELSTi0LSTi1LSTi2LSTi3L BSTi4BSTi5BSTi6BSTi7VDD_IO VDD_CORE VDD_COREGND GND VDD_COREVDD_COREVDD_IO LSTi4LSTi5LSTi6LSTi7M BSTi8BSTi9BSTi10BSTi11VDD_IO D3D2D1D0VDD_PLLNC VDD_IO LSTi8LSTi9LSTi10LSTi11N BSTi12BSTi13BSTi14BSTi15BSTi16D7D6D5D4IC_OPENIC_OPENLSTi12LSTi13LSTi14LSTi15LSTi16P BSTi17BSTi18BSTi19BSTi20BSTi21D11D10D9D8C16o FP16o LSTi17LSTi18LSTi19LSTi20LSTi21R BSTi22BSTi23BSTi24BSTi25BSTi26D15D14D13D12FP8o FP8i LSTi22LSTi23LSTi24LSTi25LSTi26T BSTi27BSTi28BSTi29BSTi30BSTi31IC_GND IC_GND IC_GND IC_GND C8i C8o LSTi27LSTi28LSTi29LSTi30LSTi31Figure 3 - ZL50051 PBGA Connections (256 PBGA, 17mm x 17mm) Pin Diagram(as viewed through top of package)Pin DescriptionPin NameZL50053PackageCoordinates(256 pinLQFP)ZL50051PackageCoordinates(256 ballPBGA)DescriptionDevice TimingC8i37T10Master Clock (5V Tolerant Schmitt-Triggered Input)This pin accepts an 8.192MHz clock. The internal frameboundary is aligned with the clock falling or rising edge, ascontrolled by the C8IPOL bit in the Control Register. Input dataon both the Backplane and Local sides (BSTi0-31 andLSTi0-31) must be aligned to this clock and the accompanyinginput frame pulse, FP8i.FP8i43R11Frame Pulse Input (5V Tolerant Schmitt-Triggered Input)When the Frame Pulse Width bit (FPW) of the ControlRegister is LOW (default), this pin accepts a 122ns-wideframe pulse. When the FPW bit is HIGH, this pin accepts a244ns-wide frame pulse. The device will automatically detectwhether an ST-BUS or GCI-Bus style frame pulse is applied.Input data on both the Backplane and Local sides (BSTi0-31and LSTi0-31) must be aligned to this frame pulse and theaccompanying input clock, C8i.C8o41T11C8o Output Clock (5V Tolerant Three-state Output)This pin outputs an 8.192MHz clock generated within thedevice. The clock falling edge or rising edge is aligned with theoutput frame boundary presented on FP8o; this edge polarityalignment is controlled by the COPOL bit of the ControlRegister. Output data on both the Backplane and Local sides(BSTo0-31 and LSTo0-31) will be aligned to this clock and theaccompanying output frame pulse, FP8o.FP8o42R10Frame Pulse Output (5V Tolerant Three-state Output)When the Frame Pulse Width bit (FPW) of the ControlRegister is LOW (default), this pin outputs a 122ns-wideframe pulse. When the FPW bit is HIGH, this pin outputs a244ns-wide frame pulse. The frame pulse, running at 8kHzrate, will have the same format (ST-BUS or GCI-Bus) as theinput frame pulse (FP8i). Output data on both the Backplaneand Local sides (BSTo0-31 and LSTo0-31) will be aligned tothis frame pulse and the accompanying output clock, C8o.C16o NA P10C16o Output Clock (5V Tolerant Three-state Output)This pin outputs a 16.384MHz clock generated within thedevice. The clock falling edge or rising edge is aligned with theoutput frame boundary presented on FP16o; this edge polarityalignment is controlled by the COPOL bit of the ControlRegister. Output data on both the Backplane and Local sides(BSTo0-31 and LSTo0-31) will be aligned to this clock and theaccompanying output frame pulse, FP16o.。