SPI时序分析和基础知识总结解析

SPI接口扫盲SPI定义SPI时序(CPHACPOL)

SPI接⼝扫盲SPI定义SPI时序(CPHACPOL)SPI接⼝扫盲douqingl@为何要写这篇⽂档?百度上找出来的SPI接⼝中⽂描述都说的太过简略,没有⼀篇⽂档能够详尽的将SPI介绍清楚的。

wikipedia英⽂版[注释1]中,SPI接⼝介绍的很好,但是毕竟是英⽂版,读起来终究不如母语舒服,所以我结合⾃⼰的⼯作经验,对其进⾏了汉化、整理。

个⼈SPI接⼝相关经验:1. 参与过国产某芯⽚SPI接⼝样品验证、SPI接⼝服务DEMO开发(C语⾔)。

2. 使⽤国产某芯⽚GPIO接⼝模拟SPI接⼝(C语⾔)。

3. 使⽤STM32芯⽚的SPI MASTER/SLAVE(C语⾔)。

SPI接⼝是什么?SPI ( Serial Peripheral Interface,串⾏外设接⼝)是⼀种同步、串⾏通讯接⼝规格,常⽤于短距离通讯,主要是在嵌⼊式系统中。

此接⼝由Mototola公司推出,已成为⼀种事实标准(没有统⼀的协议规范,但是基于其⼴泛的使⽤,根据实际使⽤中⼤家通⽤的习惯形成了⼀个类似⾏规的标准)。

SPI典型的应⽤场景包括SD卡(SD接⼝中包含SPI接⼝)和液晶显⽰。

SPI是⼀种⾼速的,全双⼯,同步的通信总线。

分为主(master)、从(slave)两种模式,⼀个SPI通讯系统需要包含⼀个(且只能是⼀个)maser(主设备),⼀个或多个slave(从设备)。

SPI接⼝的读写操作,都是由master发起。

当存在多个从设备时,通过各⾃的⽚选(slave select)信号进⾏管理。

硬件开发⼈员设计、提供的SPI接⼝,其实只是⼀个数据读写通道,具体读写数据所代表的意义需要在应⽤中定义。

不像SD接⼝那样,对于命令有着明确详细的定义。

SPI接⼝都包含哪些IO线?除了供电、接地两个模拟连接以外,SPI总线定义四组数字信号:- 接⼝时钟SCLK(Serial Clock,也叫SCK、CLK),master输出⾄slave的通讯时钟。

SPI协议详解

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

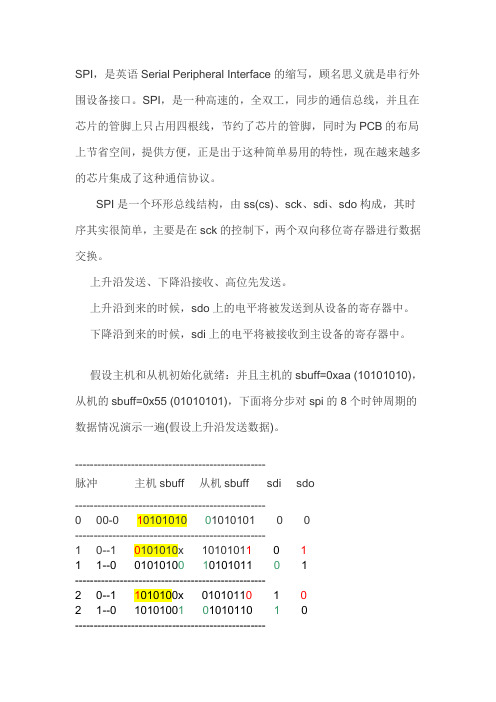

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

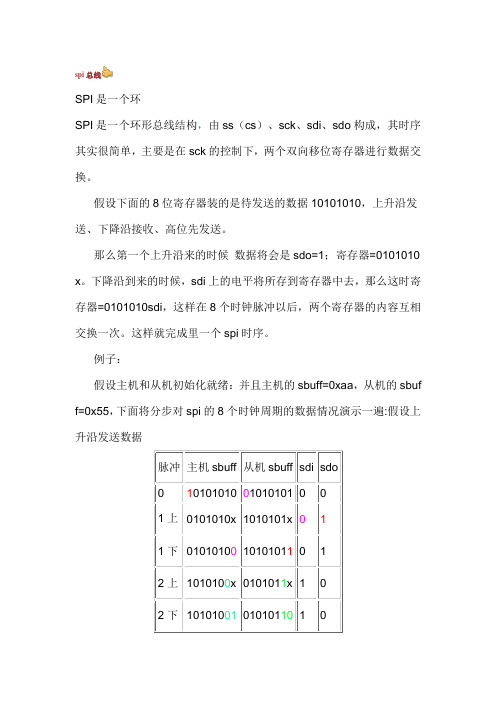

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 101010110 11 1--0 0101010010101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 1010100101010110 10---------------------------------------------------3 0--1 0101001x 101011010 13 1--0 0101001010101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 1010010101011010 10---------------------------------------------------5 0--1 0100101x 101101010 15 1--0 0100101010110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 1001010101101010 10---------------------------------------------------7 0--1 0010101x 110101010 17 1--0 0010101011010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 0101010110101010 10---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

spi时序图怎么看?spi时序图详解分析

spi时序图怎么看?spi时序图详解分析https:///is/ecFhoa5/我做产品的时候,最怕就是做IIC和SPI的通信。

这两种协议时序哪怕是延时时间有误差,都有可能导致通信不上。

出现问题的时候,如果没设备也很难排查问题到底出在哪⾥。

有时候这个产品写好的时序程序,换⼀个单⽚机⽤同⼀个程序移植过去就不⾏了。

⽽且很多公司都没有设备可以调试这些协议,⼤多数时候都是完全靠蒙。

今天就拿新⼿⽐较头痛的SPI来进⾏时序图的分析和讲解,看不懂你打我!我记得第⼀次SPI通讯的时候,完全是照抄⽹络上的程序,因为芯⽚⼿册的时序图看起来太可怕了,根本看不懂。

后⾯各种模拟时序写多了,才有了经验,然后⽤经验去理解数据⼿册以及⽹络上的教程。

很多新⼿看各种数据⼿册和教程被吓到了,其实很多时候不是你的问题,⽽是数据⼿册和教程写得太学术化了。

举个例⼦,就像SPI协议⽤CPOL和CPHA真值表来选择不同的模式。

因为在很多SPI接⼝芯⽚的数据⼿册根本没提CPOL和CPHA这两个东西,那要怎么知道芯⽚的通讯模式?其实是要我们⾃⼰根据芯⽚⼿册的时序图去分析模式的,⽽不会直接告诉你是⽤的哪个模式。

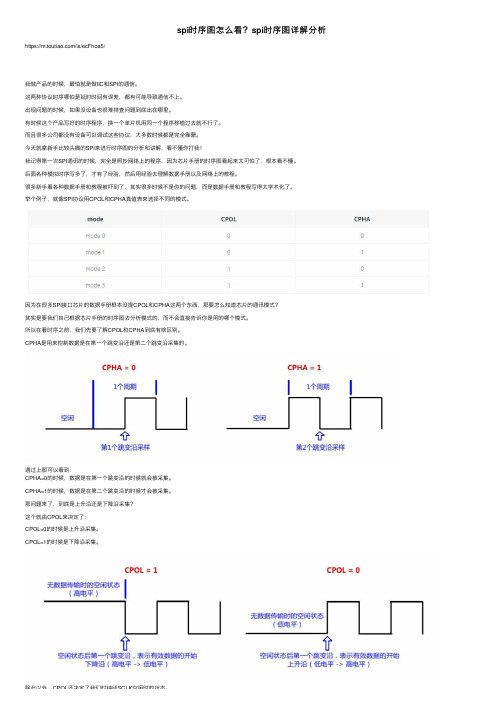

所以在看时序之前,我们先要了解CPOL和CPHA到底有啥区别。

CPHA是⽤来控制数据是在第⼀个跳变沿还是第⼆个跳变沿采集的。

通过上图可以看到:CPHA=0的时候,数据是在第⼀个跳变沿的时候就会被采集。

CPHA=1的时候,数据是在第⼆个跳变沿的时候才会被采集。

那问题来了,到底是上升沿还是下降沿采集?这个就由CPOL来决定了:CPOL=0的时候是上升沿采集。

CPOL=1的时候是下降沿采集。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

除此以外,CPOL还决定了我们时钟线SCLK空闲时的状态。

CPOL=0的时候表⽰SCLK在空闲时为低电平。

CPOL=1的时候表⽰SCLK在空闲时为⾼电平。

Ok,明⽩了这个,我们再分析4种模式的时序图。

1. 模式0(CPOL=0 CPOL=0)CPOL = 0:时钟线空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 0:数据在第1个跳变沿(上升沿)采样时序图如下:2.模式1(CPOL=0 CPOL=1)CPOL = 0:空闲时是低电平,第1个跳变沿是上升沿,第2个跳变沿是下降沿CPHA = 1:数据在第2个跳变沿(下降沿)采样时序图如下:3.模式2(CPOL=1 CPOL=0)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 0:数据在第1个跳变沿(下降沿)采样时序图如下:4.模式3(CPOL=1 CPOL=1)CPOL = 1:空闲时是⾼电平,第1个跳变沿是下降沿,第2个跳变沿是上升沿CPHA = 1:数据在第2个跳变沿(上升沿)采样时序图如下:这样看是不是对4种模式的区别⽐较清晰了?下⾯,我们再拿OLED的驱动芯⽚SSD1306的时序图来作为实战讲解。

SPI知识收集

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCK(时钟),CS(片选)。

(1)SDO –主设备数据输出,从设备数据输入(2)SDI –主设备数据输入,从设备数据输出(3)SCLK –时钟信号,由主设备产生(4)CS –从设备使能信号,由主设备控制其中CS是控制芯片是否被选中的,也就是说只有片选信号为预先规定的使能信号时(高电位或低电位),对此芯片的操作才有效。

这就允许在同一总线上连接多个SPI设备成为可能。

接下来就负责通讯的3根线了。

通讯是通过数据交换完成的,这里先要知道SPI 是串行通讯协议,也就是说数据是一位一位的传输的。

这就是SCK时钟线存在的原因,由SCK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。

数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。

完成一位数据传输,输入也使用同样原理。

这样,在至少8次时钟信号的改变(上沿和下沿为一次),就可以完成8位数据的传输。

要注意的是,SCK信号线只由主设备控制,从设备不能控制信号线。

同样,在一个基于SPI的设备中,至少有一个主控设备。

这样传输的特点:这样的传输方式有一个优点,与普通的串行通讯不同,普通的串行通讯一次连续传送至少8位数据,而SPI允许数据一位一位的传送,甚至允许暂停,因为SCK时钟线由主控设备控制,当没有时钟跳变时,从设备不采集或传送数据。

也就是说,主设备通过对SCK时钟线的控制可以完成对通讯的控制。

SPI还是一个数据交换协议:因为SPI的数据输入和输出线独立,所以允许同时完成数据的输入和输出。

不同的SPI 设备的实现方式不尽相同,主要是数据改变和采集的时间不同,在时钟信号上沿或下沿采集有不同定义,具体请参考相关器件的文档。

模拟IIC和SPI的时序分析

模拟IIC和SPI的时序分析IIC(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

它是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。

在CPU 与被控IC之间、IC与IC之间进行双向传送(半双工),高速IIC 总线一般可达400kbps以上。

I2C总线在传送数据过程中共有三种类型信号,它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。

CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。

若未收到应答信号,由判断为受控单元出现故障。

这些信号中,起始信号是必需的,结束信号和应答信号,都可以不要。

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

数据传送格式:字节传送与应答:每一个字节必须保证是8位长度。

数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。

字节传送与应答:4、在总线的一次数据传送过程中,可以有以下几种组合方式:a、主机向从机发送数据,数据传送方向在整个传送过程中不变:也就是主机写方式注:有阴影部分表示数据由主机向从机传送,无阴影部分则表示数据由从机向主机传送。

A表示应答,A非表示非应答(高电平)。

S表示起始信号,P表示终止信号。

b、主机在第一个字节后,立即从从机读数据.也就是主机读方式c、在传送过程中,当需要改变传送方向时,起始信号和从机地址都被重复产生一次,但两次读/写方向位正好反相。

模拟IIC和SPI的时序分析

模拟IIC和SPI的时序分析IIC(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。

它是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。

在CPU 与被控IC之间、IC与IC之间进行双向传送(半双工),高速IIC 总线一般可达400kbps以上。

I2C总线在传送数据过程中共有三种类型信号,它们分别是:开始信号、结束信号和应答信号。

开始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。

//产生IIC开始信号void IIC_Start(void){SDA_OUT();//sda线输出IIC_SDA=1;IIC_SCL=1;delay_us(4);IIC_SDA=0;//START:when CLK is high,DATA change form high to lowdelay_us(4);IIC_SCL=0;//钳住I2C总线,准备发送或接收数据}结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。

//产生IIC停止信号void IIC_Stop(void){SDA_OUT();//sda线输出IIC_SCL=0;IIC_SDA=0;//STOP:when CLK is high DATA change form low to highdelay_us(4);IIC_SCL=1;IIC_SDA=1;//发送I2C总线结束信号delay_us(4);}应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。

CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。

若未收到应答信号,由判断为受控单元出现故障。

//产生ACK应答void IIC_Ack(void){IIC_SCL=0;SDA_OUT();IIC_SDA=0;delay_us(2);IIC_SCL=1;IIC_SCL=0;delay_us(2);}这些信号中,起始信号是必需的,结束信号和应答信号,都可以不要。

SPI通讯方式

SPISPI总线协议及SPI时序图详解SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

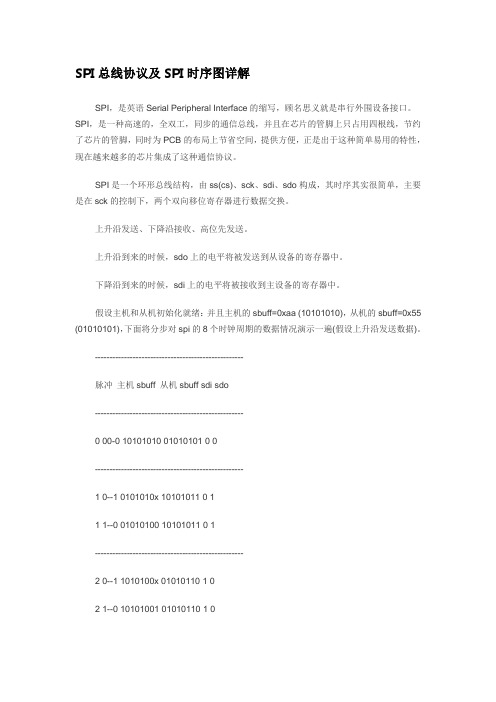

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 101010110 11 1--0 0101010010101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 1010100101010110 10---------------------------------------------------3 0--1 0101001x 101011010 13 1--0 0101001010101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 1010010101011010 10---------------------------------------------------5 0--1 0100101x 101101010 15 1--0 0100101010110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 1001010101101010 10---------------------------------------------------7 0--1 0010101x 110101010 17 1--0 0010101011010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 0101010110101010 10---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

SPI总线协议及SPI时序图详解

SPI总线协议及SPI时序图详解SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 10101011 0 11 1--0 01010100 10101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 10101001 01010110 1 0---------------------------------------------------3 0--1 0101001x 10101101 0 13 1--0 01010010 10101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 10100101 01011010 1 0---------------------------------------------------5 0--1 0100101x 10110101 0 15 1--0 01001010 10110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 10010101 01101010 1 0---------------------------------------------------7 0--1 0010101x 11010101 0 17 1--0 00101010 11010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 01010101 10101010 1 0---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

万变不离其宗之SPI总线要点总结

万变不离其宗之SPI总线要点总结[导读] 前面总结了UART/I2C的技术要点,SPI相对I2C而言,比较简单。

本文来总结一下SPI总线个人认为比较重要的一些技术要点。

什么是SPI?SPI(Serial Peripheral Interface)是一种嵌入式系统中应用广泛的同步串行通信、主从架构式总线接口。

80年代由摩托罗拉开发,已成为事实标准。

这句话里有几个关键要点:•同步•串行•通信•主从•总线要理解这些要点,先上图,一图胜千言:常见的SPI接口有这样几个引脚:•SCLK: 串行时钟,总是主端负责输出(Master)。

总是由主端控制该信号,从端为输入采样。

•MOSI:主出从入(Master Output Slave Input)。

总是由主端控制该信号,从端为输入采样。

•MISO:主入从出(Master Input Slave Output)。

总是由从端控制该信号,主端为输入采样。

•:从选择信号(Slave Select)。

总是由主端控制该信号,从端为输入采样。

要理解上面这几个信号引脚的内涵,结合时序图,就比较容易理解了:数字电路中,同步电路是一种通过时钟信号同步存储元件状态变化的数字电路。

•主端>从端:o:主端发送低电平先选通从芯片,上面加帽表示低有效。

啥意思呢?就是这个脚低电平期间选中从设备,主设备发送的时序报文对选中的从设备有效,其他挂载在总线上的设备忽略总线报文。

o SCLK/SCK:发送同步移位时钟。

o MOSI:将数据按照SCLK移位时钟周期,将数据移位发送至该引脚。

被选中的从设备依照SCLK/SCK上升沿或者下降沿,按位采样,一般字节的高位在前,具体须遵从芯片手册时序定义。

从端依赖SCK/SCLK对MOSI上的信号逐位采样,采样的位依次进入接收移位寄存器,完成对字节的重组。

当字节接收完成,再由后续数字电路进行处理。

后续处理芯片实现各异,如是一个单片机则可能引发中断请求,如是特定功能数字芯片,则依据接收报文完成相应的功能处理。

串行外设接口(SPI)总线时序详解

串行外设接口(SPI)总线时序详解SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB 的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI 是一个环形总线结构,由ss(cs)、sck、sdi、sdo 构成,其时序其实很简单,主要是在sck 的控制下,两个双向移位寄存器进行数据交换。

SPI 总线是Motorola 公司推出的三线同步接口,同步串行3 线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU 与各种外围器件进行全双工、同步串行通讯。

SPI 主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI 总线有四种工作方式(SP0,SP1,SP2,SP3),其中使用的最为广泛的是SPI0 和SPI3 方式。

SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI 主模块和与之通信的外设音时钟相位和极性应该一致。

SPI 时序详解---SPI 接口在模式0 下输出第一位数据的时刻SPI 接口有四种不同的数据传输时序,取决于CPOL 和CPHL 这两位的组合。

图1 中表现了这四种时序,时序与CPOL、CPHL 的关系也可以从图中看出。

时序分析基础知识

时序分析基础知识在当今数据驱动的世界中,时序分析成为了理解和预测数据随时间变化趋势的重要工具。

无论是经济领域的股票价格波动、气象学中的气候变化,还是工业生产中的设备故障预测,时序分析都发挥着关键作用。

那么,什么是时序分析?它又包含哪些基础知识呢?让我们一起来揭开它神秘的面纱。

首先,我们来理解一下什么是时序数据。

简单来说,时序数据就是按照时间顺序排列的数据点的集合。

这些数据点可以是每小时的气温、每天的销售额、每分钟的网络流量等等。

与普通的数据不同,时序数据具有明显的时间依赖性,即后面的数据点往往受到前面数据点的影响。

时序分析的一个重要概念是趋势。

趋势反映了数据在长期时间内的总体走向,可以是上升、下降或者保持平稳。

例如,一家公司的销售额在过去几年中持续增长,这就是一个上升的趋势。

识别趋势对于预测未来的发展方向至关重要。

除了趋势,季节性也是时序分析中的常见特征。

季节性是指数据在固定的时间间隔内呈现出相似的模式。

比如,零售业在每年的圣诞节期间销售额会大幅增加,这就是季节性的表现。

了解季节性可以帮助我们更好地规划生产和库存。

接下来,让我们聊聊周期性。

周期性与季节性有些相似,但周期的时间间隔通常不那么固定。

经济的繁荣与衰退往往呈现出周期性的特点。

在进行时序分析时,我们还需要关注噪声。

噪声是指数据中的随机波动,它可能由测量误差、突发事件或者其他不可预测的因素引起。

处理噪声是时序分析中的一个挑战,因为它可能会掩盖数据中的真实模式。

移动平均是时序分析中常用的一种方法。

它通过计算一定时间段内数据的平均值来平滑数据,从而更清晰地显示出趋势和季节性。

例如,我们可以计算过去 5 天的股票价格平均值,来减少每日价格波动带来的干扰。

指数平滑是另一种重要的方法。

它给予近期数据更高的权重,使得预测更能反映当前的变化情况。

自回归模型(AR)是基于数据自身的历史值来预测未来值的方法。

它假设当前值与过去的若干个值之间存在线性关系。

移动平均自回归模型(ARMA)则结合了自回归和移动平均的特点,能够更全面地捕捉数据的特征。

SPI总线信号质量及完整性的检测方法与规范

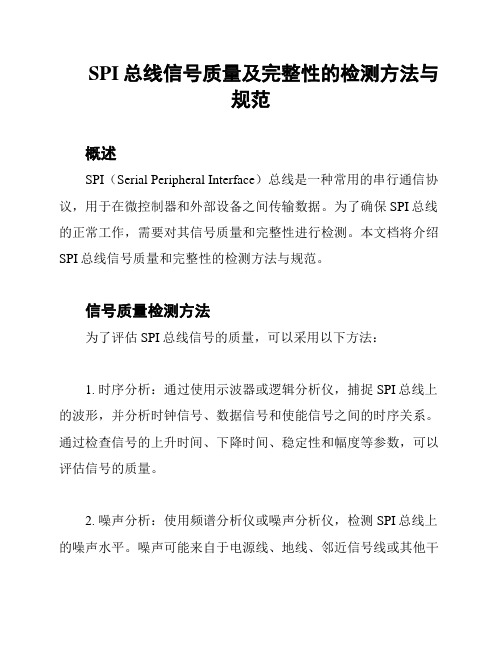

SPI总线信号质量及完整性的检测方法与规范概述SPI(Serial Peripheral Interface)总线是一种常用的串行通信协议,用于在微控制器和外部设备之间传输数据。

为了确保SPI总线的正常工作,需要对其信号质量和完整性进行检测。

本文档将介绍SPI总线信号质量和完整性的检测方法与规范。

信号质量检测方法为了评估SPI总线信号的质量,可以采用以下方法:1. 时序分析:通过使用示波器或逻辑分析仪,捕捉SPI总线上的波形,并分析时钟信号、数据信号和使能信号之间的时序关系。

通过检查信号的上升时间、下降时间、稳定性和幅度等参数,可以评估信号的质量。

2. 噪声分析:使用频谱分析仪或噪声分析仪,检测SPI总线上的噪声水平。

噪声可能来自于电源线、地线、邻近信号线或其他干扰源。

通过分析噪声的频谱特征,可以确定是否存在噪声问题,并采取相应的措施进行抑制。

3. 眼图分析:通过使用高速示波器,捕捉SPI总线上的多个数据传输周期,并绘制眼图。

眼图可以显示信号的稳定性和噪声干扰情况,从而评估信号的质量。

通过调整信号的驱动能力、阻抗匹配和布线等措施,可以改善信号的质量。

完整性检测方法为了确保SPI总线数据的完整性,可以采用以下方法:1. 数据校验:在SPI总线上进行数据传输时,可以使用CRC (循环冗余校验)或其他校验算法对数据进行校验。

接收端可以通过计算接收到的数据的校验值,与发送端发送的校验值进行比较,以验证数据的完整性。

2. 电气特性检测:通过检测SPI总线上的电平、噪声和干扰情况,可以评估数据传输的完整性。

例如,检测信号的上升时间和下降时间是否在规定范围内,检测信号的幅度是否稳定等。

3. 容错设计:在设计SPI总线的系统时,可以采用容错技术,以提高数据传输的完整性。

例如,增加冗余数据、使用纠错码等方法,可以在一定程度上纠正传输过程中的错误。

规范要求为了确保SPI总线信号的质量和数据的完整性,应遵循以下规范要求:1. 时序规范:定义SPI总线上时钟信号、数据信号和使能信号的时序要求,包括上升时间、下降时间、保持时间等。

(转)SPI时序详解

(转)SPI时序详解1、什么是SPI? SPI是串⾏外设接⼝(Serial Peripheral Interface)的缩写,是 Motorola 公司推出的⼀ 种同步串⾏接⼝技术,是⼀种⾼速的,全双⼯,同步的通信总线。

2、SPI优点 ⽀持全双⼯通信 通信简单 数据传输速率块3、缺点 没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议⽐较在数据 可靠性上有⼀定的缺陷。

4、特点 (1):⾼速、同步、全双⼯、⾮差分、总线式 (2):主从机通信模式5、SPI 电路连接 (1):SPI的通信原理很简单,它以主从⽅式⼯作,这种模式通常有⼀个主设备和⼀个或多 个从设备,需要⾄少4根线,事实上3根也可以(单向传输时)。

也是所有基于SPI的设备共 有的,它们是SDI(串⾏数据输⼊ Serial Digital IN)、SDO(串⾏数据输出 Serial Digital OUT)、SCLK(时钟)、CS(⽚选)。

(2):SDO/MOSI – 主设备数据输出,从设备数据输⼊ (3):SDI/MISO – 主设备数据输⼊,从设备数据输出 (4):SCLK – 时钟信号,由主设备产⽣; (5):CS/SS – 从设备使能信号,由主设备控制。

当有多个从设备的时候,因为每个从设 备上都有⼀个⽚选引脚接⼊到主设备机中,当我们的主设备和某个从设备通信时将需要将 从设备对应的⽚选引脚电平拉低或者是拉⾼。

6、SPI通信模式分析 SPI通信有4种不同的模式,不同的从设备可能在出⼚是就是配置为某种模式,这是不能改变的, 但我们的通信双⽅必须是⼯作在同⼀模式下,所以我们可以对我们的主设备的SPI模式进⾏配置, 通过CPOL(时钟极性)和CPHA(时钟相位)来控制我们主设备的通信模式。

具体模式具体如下: Mode0:CPOL=0,CPHA=0 Mode1:CPOL=0,CPHA=1 Mode2:CPOL=1,CPHA=0 Mode3:CPOL=1,CPHA=1 时钟极性CPOL是⽤来配置SCLK的电平出于哪种状态时是空闲态或者有效态,时钟相位CPHA 是⽤来配置数据采样是在第⼏个边沿 CPOL=0,表⽰当SCLK=0时处于空闲态,所以有效状态就是SCLK处于⾼电平时 CPOL=1,表⽰当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时 CPHA=0,表⽰数据采样是在第1个边沿,数据发送在第2个边沿 CPHA=1,表⽰数据采样是在第2个边沿,数据发送在第1个边沿 SPI主模块和与之通信的外设通信时,两者的时钟相位和极性应该保持⼀致。

SPI的时序

SPI传输数据格式的学习SPI用CPHA和CPOL控制时钟SCK。

CPOL控制空闲时,SCK的电平状态。

CPOL=0,SCK空闲时是低电平;CPOL=1, SCK空闲时是电平。

CPOL对SPI传输的格式没有影响。

CPAH用来选择两种不同的传输格式。

CPAH=0,时钟的前沿用来发送数据(最先发送的位,在前沿到来之前在数据线上已经准备好了),CPAH=1,时钟的前沿用来准备数据,后沿用来发送数据。

以下是由STM32F103RC的SPI配置成4中不同格式得到的时序图。

图中黄色的是SCK,蓝色的是MOSI。

1.CPHA=0,CPOL=0。

CPOL=0,空闲时SCK是低电平,CPHA=0前沿(上升沿)到来之前,MOSI 的数据已经准备好,所以前沿就把数据发送出去,后沿(下降沿)准备好下一个要发送的bit。

发送的数据是0xA5。

2.CPHA=0,CPOL=1。

CPOL=1,空闲时SCK是高电平,CPHA=0前沿(下降沿)到来之前,MOSI的数据已经准备好,所以前沿就把数据发送出去,后沿(上升沿) 准备好下一个要发送的bit。

发送的数据是0x65。

3.CPHA=1,CPOL=0。

CPOL=0,空闲时SCK是低电平,CPHA=1前沿(上升沿)到来之后,准备MOSI要发送的数据,后沿(下降沿) 把数据发送出去。

发送的数据是0x65。

4.CPHA=1,CPOL=1。

CPOL=1,空闲时SCK是高电平,CPHA=1前沿(下降沿)到来之后,准备MOSI要发送的数据,后沿(上升沿) 把数据发送出去。

发送的数据是0x65。

小结:CPOL用来决定闲时SCK是高电平还是低电平,CPHA用来决定是前沿传输数据还是后沿传输数据。

可以看出用SPI来驱动74HC595的时候选择CPHA=1,CPOL=1或者CPHA=0,CPOL=0都是可以的。

SPI协议学习心得

SPI协议学习心得SPI协议学习心得一、SPI1、掌握SPI通信协议2、了解W25Q64芯片读写操作3、STM32SPI寄存器配置介绍4、SPI操作FLASH程序分析二、知识点1、SPI协议:时序分析在数据手册,这里主要对应IIC进行比较说明注意:一个是时序,一个是和外设的连接(4条SPI线)SPI与IIC对比:1)速度SPI 4M 高速25MIIC 100K 高速400K2)硬件接口SPI 数据线2根收发分开,一根时钟线,一根片选线,一共4根线IIC 两线制,SDA双向数据线,时钟线3)外部引脚SPI 外部不需要上拉,接也可以IIC 外部一定要上拉4)寻址方式/拓扑结构SPI 多主多从寻址方式不同:SPI通过片选线确定哪个芯片通信每个设备一根片选线,一般低电平选中,所以SPI不适合接太多从设备,从设备增加,需要用到的IO就增加(译码器)IIC 多主多从IIC通过发送设备地址,确定哪个设备通信主从设备增加,不需要增加IO5)数据帧格式SPI 一次能传输的位数理论上不限制,一般8位、16位,不存在起始信号、停止信号和应答信号,纯粹是普通的二进制数据流IIC 有特定的帧格式,起始信号+地址+方向+数据,每次传输一个字节(固定),每个字节后面加一个应答位,传输结束是停止标志(停止位)6)创造者SPI MOTOIIC 飞利浦7)应用领域SPI 大数据传输方面,对速度要求高的场合IIC 少量数据传输场合8)时序IIC 起始信号,停止信号数据阶段:一个始终传输一个位,只有唯一一种时序SPI 全是数据阶段时序,没有其他信号,一个时钟传输一个位时序有4种,由极性和相位决定时序类型CPOL CPHA极性相位时序类型(SCK时钟线)0 0 00 1 11 0 21 1 3对SPI来讲,配置时序是重点,配置时序由所驱动的器件的时序决定9)SPI主机IO称呼MISO:当作主机时,为输入,从机时为输出方向MOSI:当作主机时,为输出,从机时为输入方向SCK:同步时钟信号,决定了SPI速度nCS:从机片选(片选线),可以使用普通IO口,一般是低电平选中,用来选择通信的目标从设备2、FLASH 1001 0011 FLASH的组成:页(page)-扇区(sector)-块(block)-片(chip) 1001 0011flash写数据之前要擦除,擦除最小单位为扇区(有的操作是块擦除),擦除后,所有字节全部为1,也就是写操作时候只能把1改为03、W25Q64W25Q64是华邦公司推出的大容量SPI FLASH产品,W25Q64的容量为64Mb,该系列还有W25Q80/16/32等。

SPI

spi总线SPI是一个环SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

假设下面的8位寄存器装的是待发送的数据10101010,上升沿发送、下降沿接收、高位先发送。

那么第一个上升沿来的时候数据将会是sdo=1;寄存器=0101010 x。

下降沿到来的时候,sdi上的电平将所存到寄存器中去,那么这时寄存器=0101010sdi,这样在8个时钟脉冲以后,两个寄存器的内容互相交换一次。

这样就完成里一个spi时序。

例子:假设主机和从机初始化就绪:并且主机的sbuff=0xaa,从机的sbuf f=0x55,下面将分步对spi的8个时钟周期的数据情况演示一遍:假设上升沿发送数据这样就完成了两个寄存器8位的交换,上面的上表示上升沿、下表示下降沿,sdi、sdo相对于主机而言的。

其中ss引脚作为主机的时候,从机可以把它拉底被动选为从机,作为从机的是时候,可以作为片选脚用。

根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个8位时钟周期才把数据读回来!看大家明白没有!!!!!SPI总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。

外围设置FLASHRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。

SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,需要至少4根线,事实上3根也可以(用于单向传输时,也就是半双工方式)。

SPI时钟极性与时钟相位关系根本剖析

SPI时钟极性与时钟相位关系根本剖析----2011年11月21日有感而发⑴时钟极性:SCK空闲状态为低电平(时钟周期中第一个时钟沿也为低电平)①时钟相位:数据采样从第一个时钟沿开始1、如果MSB先发送,则MOSI空闲状态与最高位相同2、如果LSB先发送,则MOSI空闲状态与最低位相同②时钟相位:数据采样从第二个时钟沿开始1、如果MSB先发送,则MOSI空闲状态与最低位相同2、如果LSB先发送,则MOSI空闲状态与最高位相同⑴时钟极性:SCK空闲状态为高电平(时钟周期中第一个时钟沿也为高电平)①时钟相位:数据采样从第一个时钟沿开始1、如果MSB先发送,则MOSI空闲状态与最高位相同2、如果LSB先发送,则MOSI空闲状态与最低位相同②时钟相位:数据采样从第二个时钟沿开始1、如果MSB先发送,则MOSI空闲状态与最低位相同2、如果LSB先发送,则MOSI空闲状态与最高位相同2011年12月3日理解更本质如果CPOL = 0,且CPHA = 0,则一个时钟周期是先低电平,再高电平如果CPOL = 0,且CPHA = 1,则一个时钟周期是先高电平,再低电平如果CPOL = 1,且CPHA = 0,则一个时钟周期是先高电平,再低电平如果CPOL = 1,且CPHA = 1,则一个时钟周期是先低电平,再高电平上述简而言之就是:CPHA = 0,时钟周期第一个沿与空闲状态相同,CPHA = 1,时钟周期第一个沿与空闲状态相反。

如下图所示:网友言论:SPI总线小结SPI接口的全称是"Serial Peripheral Interface",意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,地位在后,为全双工通信,数据传输速度总体来说比I2C总线要快,速度可达到几Mbps。

STM32学习重点spi剖析

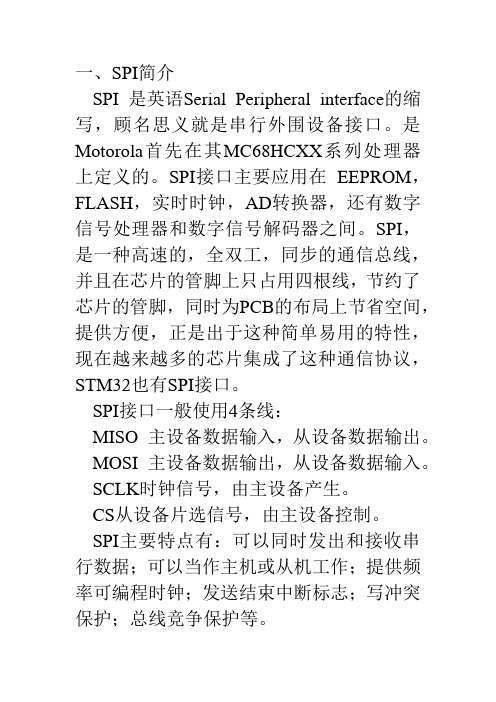

一、SPI简介SPI 是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。

是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议,STM32也有SPI接口。

SPI接口一般使用4条线:MISO 主设备数据输入,从设备数据输出。

MOSI 主设备数据输出,从设备数据输入。

SCLK时钟信号,由主设备产生。

CS从设备片选信号,由主设备控制。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线四种工作方式SPI 模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设备时钟相位和极性应该一致。

不同时钟相位下的总线数据传输时序见下图:二、STM32的SPI介绍STM32的SPI功能很强大,SPI时钟最多可以到18Mhz,支持DMA,可以配置为SPI协议或者I2S协议。

本节,我们将利用STM32的SPI来读取外部SPI FLASH芯片(W25X16),这节,我们使用STM32的SPI1的主模式,STM32的主模式配置步骤如下:1)配置相关引脚的复用功能,使能SPI1时钟。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI接口是一种事实标准,并没有标准协议,大部分厂家都是参照Motorola的SPI 接口定义来设计的。但正因为没有确切的版本协议,不同家产品的SPI接口在技术 上存在一定的差别,容易引起歧义,有的甚至无法直接互连(需要软件进行必要的 修改)。

SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化 。如图1所示,其使用的4条信号线分别为: 1) SCLK:串行时钟,用来同步数据传输,由主机输出; 2) MOSI:When master, out line; when slave, in line。主机输出从机输入数据线; 3) MISO:When master, in line; when slave, out line。主机输入从机输出数据线; 比如MOSI,该线上数据一定是Master流向Slave的。因此在电路板上,Master的 MOSI引脚应与Slave的MOSI引脚连接在一起。双方的MISO也应该连在一起,而不是 一方的MOSI连接另一方的MISO。 Motorola的经典命名是MOSI和MISO,这是站在信号线的角度来命名的。 不过,也有一些产家(比如Microchip)是按照类似SDI,SDO的方式来命名,这是 站在器件的角度根据数据流向来定义的。 SDI:串行数据输入 SDO:串行数据输出 在这种情况下,当Master与Slave连接时,就应该用一方的SDO连接另一个方的 SDI。 4) SS:Slave Select, 片选线,用于选择激活某Slave设备,低有效,由Master驱动输 出。只有当SS-信号线为低电平时,对应Slave设备的SPI接口才处于工作状态。

一主多从的SPI传输模式

SPI总线添加从器件:每个器件需要一个单独的从选择信号。总信号数最终为 n+3 个,其中 n 是总线上从器件的数量。在 SPI 总线上添加新的从器件也不方便。 对于额外添加的每个从器件,都需要一条新的从器件选择线。

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产 生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。如下图所示,在 SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

SPI也支持多Slave应用。多个Slave共享时钟线、数据线,可以直接并接在一起; 而各Slave的片选线SS则单独与Master连接,受Master控制。在一段时间内,Master 只能通过某根SS线激活一个Slave,进行数据传输,而此时其他Slave的时钟线和数据 线端口则都应保持高阻状态,以免影响当前数据传输的进行。 SPI接口采用主从模式(Master Slave)架构;支持多slave模式应用,一般仅支持 单Master。主机通过片选线来确定要通信的从机。这就要求从机的MISO口具有三态特 性,使得该口线在器件未被选通时表现为高阻抗。 SPI的时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在 后(MSB first);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率 可达几Mbps的水平。

在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位 (CPHA或UCCKPH)。时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和 发送数据的时钟沿。 主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了 保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。

在一个SPI时钟周期内,会完成如下操作: 1) 主机通过MOSI线发送1位数据,从机通过该线读取这1位数据; 2) 从机通过MISO线发送1位数据,主机通过该线读取这1位数据。 这是通过移位寄存器来实现的。如下图所示,主机和从机各有一个移位寄存器,且 二者连接成环。随着时钟脉冲,数据按位传输,高位在前,低位在后(MSB first), 依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄 存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

SPI时序分析和基础知识总结

一、SPI总线的历史 二、SPI总线接口定义 三、SPI总线的工作方式和传输时序 四、SPI与I2C的异同点 五、SPI总线的优缺点 六、SPI总线的设置 七、SPI与SD卡信号

八、关于QSPI

Байду номын сангаас

SPI ( Serial Peripheral Interface )串行外设接口总线,最早由Motorola提出,出现 在其M68系列单片机中,由于其简单实用,又不牵涉到专利问题,因此许多厂家的 设备都支持该接口,广泛应用于外设控制领域。

在主设备这边配置SPI接口时钟的时候一定要弄清楚从设备的时钟要求,因为主设 备这边的时钟极性和相位都是以从设备为基准的 。 SPI总线有四种工作方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示);

四种工作方式时序分别为:

时序详解:

CPOL:时钟极性选择,为0时SPI总线空闲为低电平,为1时SPI总线空闲为高电平 CPHA:时钟相位选择,为0时在SCK第一个跳变沿采样,为1时在SCK第二个跳变沿采样 工作方式1: 当CPHA=0、CPOL=0时SPI总线工作在方式1。MISO引脚上的数据在第一个SPSCK沿跳变 之前已经上线了,而为了保证正确传输,MOSI引脚的MSB位必须与SPSCK的第一个边沿同步, 在SPI传输过程中,首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收方捕捉位信号 ,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字 节的8位信号传输结束。 工作方式2: 当CPHA=0、CPOL=1时SPI总线工作在方式2。与前者唯一不同之处只是在同步时钟信号的 下降沿时捕捉位信号,上升沿时下一位数据上线。 工作方式3: 当CPHA=1、CPOL=0时SPI总线工作在方式3。MISO引脚和MOSI引脚上的数据的MSB位 必须与SPSCK的第一个边沿同步,在SPI传输过程中,在同步时钟信号周期开始时(上升沿)数据 上线,然后在同步时钟信号的下降沿时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束 时(上升沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。 工作方式4: 当CPHA=1、CPOL=1时SPI总线工作在方式4。与前者唯一不同之处只是在同步时钟信号的 上升沿时捕捉位信号,下降沿时下一位数据上线。