MC1DU128NDCA-0QC00中文资料

莫克8口无管理以太网开关产品说明书

EDS-308Series8-port unmanaged Ethernet switchesFeatures and Benefits•Relay output warning for power failure and port break alarm •Broadcast storm protection•-40to 75°C operating temperature range (-T models)CertificationsIntroductionThe EDS-308Ethernet switches provide an economical solution for your industrial Ethernet connections.These 8-port switches come with a built-in relay warning function that alerts network engineers when power failures or port breaks occur.In addition,the switches are designed for harsh industrial environments,such as the hazardous locations defined by the Class 1Div.2and ATEX Zone 2standards.The switches comply with FCC,UL,and CE standards and support either a standard operating temperature range of 0to 60°C or a wide operating temperature range of -40to 75°C.All switches in the series undergo a 100%burn-in test to ensure that they fulfill the special needs of industrial automation control applications.The EDS-308switches can be installed easily on a DIN rail or in a distribution box.SpecificationsInput/Output InterfaceAlarm Contact Channels1relay output with current carrying capacity of 1A @24VDCEthernet Interface10/100BaseT(X)Ports (RJ45connector)EDS-308/308-T:8EDS-308-M-SC/308-M-SC-T/308-S-SC/308-S-SC-T/308-S-SC-80:7EDS-308-MM-SC/308-MM-SC-T/308-MM-ST/308-MM-ST-T/308-SS-SC/308-SS-SC-T/308-SS-SC-80:6All models support:Auto negotiation speed Full/Half duplex modeAuto MDI/MDI-X connection100BaseFX Ports (multi-mode SC connector)EDS-308-M-SC:1EDS-308-M-SC-T:1EDS-308-MM-SC:2EDS-308-MM-SC-T:2100BaseFX Ports (multi-mode ST connector)EDS-308-MM-ST:2EDS-308-MM-ST-T:2100BaseFX Ports (single-mode SC connector)EDS-308-S-SC:1EDS-308-S-SC-T:1EDS-308-SS-SC:2EDS-308-SS-SC-T:2100BaseFX Ports (single-mode SC connector,80km)EDS-308-S-SC-80:1EDS-308-SS-SC-80:2Standards IEEE802.3for10BaseTIEEE802.3u for100BaseT(X)and100BaseFXIEEE802.3x for flow controlOptical Fiber800Typical Distance4km5km40km80kmWavelen-gthTypical(nm)130013101550TX Range(nm)1260to13601280to13401530to1570 RX Range(nm)1100to16001100to16001100to1600Optical PowerTX Range(dBm)-10to-200to-50to-5 RX Range(dBm)-3to-32-3to-34-3to-34 Link Budget(dB)122929 Dispersion Penalty(dB)311Note:When connecting a single-mode fiber transceiver,we recommend using anattenuator to prevent damage caused by excessive optical power.Note:Compute the“typical distance”of a specific fiber transceiver as follows:Linkbudget(dB)>dispersion penalty(dB)+total link loss(dB).DIP Switch ConfigurationEthernet Interface Port break alarmSwitch PropertiesMAC Table Size2kbitsPacket Buffer Size768KProcessing Type Store and ForwardPower ParametersInput Current EDS-308/308-T:0.07A@24VDCEDS-308-M-SC/S-SC Series,308-S-SC-80:0.12A@24VDCEDS-308-MM-SC/MM-ST/SS-SC Series,308-SS-SC-80:0.15A@24VDC Connection1removable6-contact terminal block(s)Operating Voltage9.6to60VDCInput Voltage Redundant dual inputs,12/24/48VDCReverse Polarity Protection SupportedOverload Current Protection SupportedPhysical CharacteristicsHousing MetalIP Rating IP30Dimensions53.6x135x105mm(2.11x5.31x4.13in)Weight790g(1.75lb)Installation DIN-rail mounting,Wall mounting(with optional kit) Environmental LimitsOperating Temperature Standard Models:-10to60°C(14to140°F)Wide Temp.Models:-40to75°C(-40to167°F) Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsHazardous Locations ATEX,Class I Division2EMI CISPR32,FCC Part15B Class AMaritime DNV-GLEMC EN55032/24Vibration IEC60068-2-6EMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1MHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:1kVIEC61000-4-5Surge:Power:2kV;Signal:2kVIEC61000-4-6CS:10VIEC61000-4-8PFMFSafety UL508,UL60950-1,CSA C22.2No.60950-1 Shock IEC60068-2-27Freefall IEC60068-2-32MTBFTime255,528hrsStandards MIL-HDBK-217FWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x EDS-308Series switchInstallation Kit1x cap,plastic,for SC fiber port2x cap,plastic,for SC fiber port(-SC models)2x cap,plastic,for ST fiber port(-ST models) Documentation1x quick installation guide1x warranty cardDimensionsOrdering InformationModel Name 10/100BaseT(X)PortsRJ45Connector100BaseFX PortsMulti-Mode,SCConnector100BaseFX PortsMulti-Mode,STConnector100BaseFX PortsSingle-Mode,SCConnectorOperating Temp.EDS-3088–––0to60°CEDS-308-T8–––-40to75°C EDS-308-M-SC71––0to60°CEDS-308-M-SC-T71––-40to75°C EDS-308-MM-SC62––0to60°CEDS-308-MM-SC-T62––-40to75°C EDS-308-MM-ST6–2–0to60°CEDS-308-MM-ST-T6–2–-40to75°C EDS-308-S-SC7––10to60°CEDS-308-S-SC-T7––1-40to75°C EDS-308-SS-SC6––20to60°CEDS-308-SS-SC-T6––2-40to75°C EDS-308-S-SC-807––10to60°CEDS-308-SS-SC-806––20to60°C Accessories(sold separately)Power SuppliesDR-120-24120W/2.5A DIN-rail24VDC power supply with universal88to132VAC or176to264VAC input byswitch,or248to370VDC input,-10to60°C operating temperatureDR-452445W/2A DIN-rail24VDC power supply with universal85to264VAC or120to370VDC input,-10to50°C operating temperatureDR-75-2475W/3.2A DIN-rail24VDC power supply with universal85to264VAC or120to370VDC input,-10to60°C operating temperatureMDR-40-24DIN-rail24VDC power supply with40W/1.7A,85to264VAC,or120to370VDC input,-20to70°Coperating temperatureMDR-60-24DIN-rail24VDC power supply with60W/2.5A,85to264VAC,or120to370VDC input,-20to70°Coperating temperatureWall-Mounting KitsWK-46Wall-mounting kit,2plates,8screws,46.5x66.8x1mmRack-Mounting KitsRK-4U19-inch rack-mounting kit©Moxa Inc.All rights reserved.Updated Jan30,2019.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

MC1DU128NDVA-0QC00中文资料

MultiMediaCard SpecificationVersion : Ver. 0.9Date 4 – June - 2004Samsung Electronics Co., LTDSemiconductor Flash Memory Product Planning & Applications1 Introduction to the MultiMediaCard ----------------------------------------------------------- 51.1 System Features ----------------------------------------------------------------------------------------- 5-------------------------------------------------------------------------------------- 51.2 ProductModel2 Function Description ------------------------------------------------------------------------------- 72.1 Flash Technology Independence ------------------------------------------------------------------ 72.2 Defect and Error Management --------------------------------------------------------------------- 72.3 Endurance ----------------------------------------------------------------------------------------------- 72.4 Automatic Sleep Mode ------------------------------------------------------------------------------- 72.5 Hot Insertion -------------------------------------------------------------------------------------------- 82.6 MultiMediaCard Mode -------------------------------------------------------------------------------- 82.6.1 MultiMediaCard Standard Compliance ----------------------------------------------------------- 82.6.2 Negotiation Operation Conditions ----------------------------------------------------------------- 82.6.3 Card Acquisition and Identification ---------------------------------------------------------------- 82.6.4 Card Status ---------------------------------------------------------------------------------------------- 82.6.5 Memory Array Partitioning --------------------------------------------------------------------------- 92.6.6 Read and Write Operations ------------------------------------------------------------------------- 92.6.7 Data Transfer Rate ------------------------------------------------------------------------------------102.6.8 Data Protection in the Flash Card -----------------------------------------------------------------10-----------------------------------------------------------------------------------------------------10 2.6.9 Erase2.6.10 Write Protection ----------------------------------------------------------------------------------------102.6.11 Copy Bit ------------------------------------------------------------------------------------------------- 102.6.12 The CSD Register ------------------------------------------------------------------------------------ 112.7 SPI Mode ----------------------------------------------------------------------------------------------- 112.7.1 Negotiating Operation Conditions ---------------------------------------------------------------- 112.7.2 Card Acquisition and Identification --------------------------------------------------------------- 112.7.3 Card Status --------------------------------------------------------------------------------------------- 112.7.4 Memory Array Partitioning -------------------------------------------------------------------------- 112.7.5 Read and Write Operations ------------------------------------------------------------------------- 112.7.6 Data Transfer Rate ------------------------------------------------------------------------------------ 112.7.7 Data Protection in the MultiMediaCard ----------------------------------------------------------- 1212-----------------------------------------------------------------------------------------------------2.7.8 Erase2.7.9 Write Protection ---------------------------------------------------------------------------------------- 123 Product Specifications ----------------------------------------------------------------------------- 133.1 Recommended Operating Conditions ------------------------------------------------------------------------- 133.2 Operating Characteristis ----------------------------------------------------------------- 143.3 System Environmental Specifications ----------------------------------------------------------------- 153.4 System Reliability and Maintenance -------------------------------------------------------------- 153.5 Physical Specifications ------------------------------------------------------------------------------- 164 MultiMediaCard Interface Description --------------------------------------------------------- 174.1 Pin Assignments in MultiMediaCard Mode ------------------------------------------------------- 174.2 Pin Assignments in SPI Mode ---------------------------------------------------------------------- 184.3 MultiMediaCard Bus Topology ---------------------------------------------------------------------- 184.4 SPI Bus Topology -------------------------------------------------------------------------------------------------- 194.4.1 SPI Interface Concept ------------------------------------------------------------------------------------------- 194.4.2 SPI Bus Topology ------------------------------------------------------------------------------------------------ 1920------------------------------------------------------------------------------------------------- 4.5 Registers4.5.1 Operation Condition Register (OCR) ---------------------------------------------------------------------------204.5.2 Card Identification (CID) ------------------------------------------------------------------------------214.5.3 Relative Card Address (RCA) ----------------------------------------------------------------------- 21 4.5.4 Card Specific Data (CSD) ---------------------------------------------------------------------------- 22 4.6 MultiMediaCard Communication -------------------------------------------------------------------- 3030----------------------------------------------------------------------------------------------- 4.6.1 Commands4.7 Read, Write and Erase Time-out Conditions ----------------------------------------------------- 33 4.8 Card Identification Mode ------------------------------------------------------------------------------ 34 4.8.1 Operating Voltage Range Validation --------------------------------------------------------------- 35 4.9 Data Transfer Mode ------------------------------------------------------------------------------------ 35 4.9.1 Block Read ----------------------------------------------------------------------------------------------- 37 4.9.2 Block Write ----------------------------------------------------------------------------------------------- 3738------------------------------------------------------------------------------------------------------ 4.9.3 Erase4.9.4 Write Protect Management -------------------------------------------------------------------------- 38 4.9.5 Card Lock/Unlock Operation ------------------------------------------------------------------------ 38----------------------------------------------------------------------------------------------- 41 4.9.6 Responses4.9.7 Status ------------------------------------------------------------------------------------------------------ 42 4.9.8 Command Response Timing ------------------------------------------------------------------------ 4448 4.9.9 Reset------------------------------------------------------------------------------------------------------ 4.10 SPI Communication ----------------------------------------------------------------------------------- 49 4.10.1 Mode Selection ----------------------------------------------------------------------------------------- 49 4.10.2 Bus Transfer Protection ------------------------------------------------------------------------------ 49 4.10.3 Data Read Overview ---------------------------------------------------------------------------------- 50 4.10.4 Data Write Overview ---------------------------------------------------------------------------------- 51 4.10.5 Erase and Write Protect Management ----------------------------------------------------------- 52 4.10.6 Reading CID/CSD Registers ------------------------------------------------------------------------ 53 4.10.7 Reset Sequence --------------------------------------------------------------------------------------- 53 4.10.8 Error Conditions ---------------------------------------------------------------------------------------- 53 4.10.9 Memory Array Partitioning --------------------------------------------------------------------------- 53 4.10.10 Card Lock/Unlock -------------------------------------------------------------------------------------- 53 4.10.11 Commands ----------------------------------------------------------------------------------------------- 54 4.10.12 Responses ----------------------------------------------------------------------------------------------- 56 4.10.13 Data Tokens --------------------------------------------------------------------------------------------- 58 4.10.14 Data Error Token --------------------------------------------------------------------------------------- 59 4.10.15 Clearing Status Bits ------------------------------------------------------------------------------------ 60 4.11 SPI Bus Timing ----------------------------------------------------------------------------------------- 61 4.12 Error Handling ------------------------------------------------------------------------------------------ 64 4.12.1 Error Correction Code (ECC) ----------------------------------------------------------------------- 64 4.12.2 Cyclic Redundancy Check (CRC) ----------------------------------------------------------------- 642 Function Description2.1 Flash Technology IndependenceThe 512 byte sector size of the MultiMediaCard is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host computer software simply issues a Read or Write command to the MultiMediaCard. This command contains the address and the number of sectors to write/read. The host software then waits for the command to complete. The host software does not get involved in the details of how the flash memory is erased, programmed or read. This is extremely important as flash devices are expected to get more and more complex in the future. Because the MultiMediaCard uses an intelligent on-board controller, the host system software will not require changing as new flash memory evolves. In other words, systems that support the MultiMediaCard today will be able to access future MultiMediaCards built with new flash technology without having to update or change host software.2.2 Defect and Error ManagementMultiMediaCards contain a sophisticated defect and error management system. This system is analogous to the systems found in magnetic disk drives and in many cases offers enhancements. For instance, disk drives do not typically perform a read after write to confirm the data is written correctly because of the performance penalty that would be incurred. MultiMediaCards do a read after write under margin conditions to verify that the data is written correctly (except in the case of a Write without Erase Command). In the rare case that a bit is found to be defective, MultiMediaCards replace this bad bit with a spare bit within the sector header. If necessary, MultiMediaCards will even replace the entire sector with a spare sector. This is completely transparent to the host and does not consume any user data space.The MultiMediaCards soft error rate specification is much better than the magnetic disk drive specification. In the extremely rare case a read error does occur, MultiMediaCards have innovative algorithms to recover the data. This is similar to using retries on a disk drive but is much more sophisticated. The last line of defense is to employ powerful ECC to correct the data. If ECC is used to recover data, defective bits are replaced with spare bits to ensure they do not cause any future problems.These defect and error management systems coupled with the solid-state construction give MultiMediaCards unparalleled reliability2.3 EnduranceMultiMediaCards have an endurance specification for each sector of 1,000,000 writes (reading a logical sector is unlimited). This is far beyond what is needed in nearly all applications of MultiMediaCards. Even very heavy use of the MultiMediaCard in cellular phones, personal communicators, pagers and voice recorders will use only a fraction of the total endurance over the typical device’s five year lifetime. For instance, it would take over 100 years to wear out an area on the MultiMediaCard on which a files of any size (from 512 bytes to capacity) was rewritten 3 times per hour, 8 hours a day, 365 days per year.With typical applications the endurance limit is not of any practical concern to the vast majority of users.2.4 Automatic Sleep ModeAn important feature of the MultiMediaCard is automatic entrance and exit from sleep mode. Upon completion of an operation, the MultiMediaCard will enter the sleep mode to conserve power if no further commands are received within 5 msec The host does not have to take any action for this to occur. In most systems, the MultiMediaCard is in sleep mode except when the host is accessing it, thus conserving power. When the host is ready to access the MultiMediaCard and it is in sleep mode, any command issued to the MultiMediaCard will cause it to exit sleep and respond. The host does not have to issue a reset first. It may do this if desired, but it is not needed. By not issuing the reset, performance is improved through the reduction of overhead.2.5 Hot InsertionSupport for hot insertion will be required on the host but will be supported through the connector. Connector manufacturers will provide connectors that have power pins long enough to be powered before contact is made with the other pins. Please see connector data sheets for more details. This approach is similar to that used in PCMCIA to allow for hot insertion. This applies to both MultiMediaCard and SPI modes.2.6 MultiMediaCard Mode2.6.1 MultiMediaCard Standard ComplianceThe MultiMediaCard is fully compliant with MultiMediaCard standard specification V3.31.The structure of the Card Specific Data (CSD) register is compliant with CSD structure V1.2.2.6.2 Negotiating Operation ConditionsThe MultiMediaCard supports the operation condition verification sequence defined in the MultiMediaCard standard specifications. The MultiMediaCard host should define an operating voltage range that is not supported by the MultiMediaCard. It will put itself in an inactive state and ignore any bus communication. The only way to get the card out of the inactive state is by powering it down and up again. In addition the host can explicitly send the card to the inactive state by using the GO_INACTIVE_STATE command.2.6.3 Card Acquisition and IdentificationThe MultiMediaCard bus is a single master (MultiMediaCard host) and multi-slaves (cards) bus. The host can query the bus and find out how many cards of which type are currently connected. The MultiMediaCard’s CID register is pre-programmed with a unique card identification number which is used during the acquisition and identification procedureIn addition, the MultiMediaCard host can read the card’s CID register using the READ_CID MultiMediaCard command. The CID register is programmed during the MultiMediaCard testing and formatting procedure, on the manufacturing floor. The MultiMediaCard host can only read this register and not write to it.2.6.4 Card StatusMultiMediaCard status is stored in a 32 bit status register which is sent as the data field in the card respond to host commands. Status register provides information about the card’s current state and completion codes for the last host command. The card status can be explicitly read (polled) with the SEND_STATUS command.2.6.7 Data Protection in the Flash CardEvery sector is protected with an Error Correction Code (ECC). The ECC is generated (in the memory card) when the sectors are written and validated when the data is read. If defects are found, the data is corrected prior to transmission to the host.The MultiMediaCard can be considered error free and no additional data protection is needed. However, if an application uses additional, external, ECC protection, the data organization is defined in the user writeable section of the CSD register2.6.8 EraseThe smallest erasable unit in the MultiMediaCard is a erase group. In order to speed up the erase procedure, multiple erase groups can be erased in the same time. The erase operation is divided into two stages.Tagging - Selecting the Sectors for ErasingTo facilitate selection, a first command with the starting address is followed by a second command with the final address, and all erase groups within this range will be selected for erase.Erasing - Starting the Erase ProcessTagging can address erase groups. An arbitrary selection of erase groups may be erased at one time. Tagging and erasing must follow a strict command sequence (refer to the MultiMediaCard standard specification for details).2.6.9 Write ProtectionThe MultiMediaCard erase groups are grouped into write protection groups. Commands are provided for limiting and enabling write and erase privileges for each group individually. The current write protect map can be read using SEND_WRITE_PROT command.In addition two, permanent and temporary, card levels write protection options are available.Both can be set using the PROGRAM_CSD command (see below). The permanent write protect bit, once set, cannot be cleared.The One Time Programmable (OTP) characteristic of the permanent write protect bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.10 Copy BitThe content of an MultiMediaCard can be marked as an original or a copy using the copy bit in the CSD register. Once the Copy bit is set (marked as a copy) it cannot be cleared.The Copy bit of the MultiMediaCard is programmed (during test and formatting on the manufacturing floor) as a copy. The MultiMediaCard can be purchased with the copy bit set (copy) or cleared, indicating the card is a master.The One Time Programmable (OTP) characteristic of the Copy bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.11 The CSD RegisterAll the configuration information of the MultiMediaCard is stored in the CSD register. The MSB bytes of the register contain manufacturer data and the two least significant bytes contains the host controlled data - the card Copy and write protection and the user ECC register.The host can read the CSD register and alter the host controlled data bytes using the SEND_CSD and PROGRAM_CSD commands.2.7 SPI ModeThe SPI mode is a secondary (optional) communication protocol offered for MultiMediaCard. This mode is a subset of the MultiMediaCard protocol, designed to communicate with an SPI channel, commonly found in Motorola’s (and lately a few other vendors’) microcontrollers.2.7.1 Negotiating Operation ConditionsThe operating condition negotiation function of the MultiMediaCard bus is not supported in SPI mode. The host must work within the valid voltage range (2.7 to 3.6 volts) of the card.2.7.2 Card Acquisition and IdentificationThe card acquisition and identification function of the MultiMediaCard bus is not supported in SPI mode. The host must know the number of cards currently connected on the bus. Specific card selection is done via the CS signal.2.7.3 Card StatusIn SPI mode only 16 bits (containing the errors relevant to SPI mode) can be read out of the MultiMediaCard status register.2.7.4 Memory Array PartitioningMemory partitioning in SPI mode is equivalent to MultiMediaCard mode. All read and write commands are byte addressable.2.7.5 Read and Write OperationsIn SPI mode, only single block read/write mode is supported.2.7.6 Data Transfer RateIn SPI mode only block mode is supported. The typical access time (latency) for each data block, in read operation, is 1.5mS. The write typical access time (latency) for each data block, in read operation, is 1.5mS. The write block operation is done in handshake mode. The card will keep DataOut line low as long as the write operation is in progress and there are no write buffers available.2.7.7 Data Protection in the MultiMediaCardSame as for the MultiMediaCard mode.2.7.8 EraseSame as in MultiMediaCard mode2.7.9 Write ProtectionSame as in MultiMediaCard modeFigure 3-1 Timing Diagram of Data Input and Output3.5 Physical SpecificationsDimensions of Normal MMC(24mm x 32mm x 1.4mm)Dimensions of RS-MMC(24mm x 18mm x 1.4mm)rising and falling edges). If the host does not allow the switchable R OD implementation, a fix R CMD can be used. Consequently the maximum operating implementation, a fix R CMD can be used. Consequently the maximum operating frequency in the open drain mode has to be reduced in this case.4.4 SPI Bus Topology4.4.1 SPI Interface ConceptThe Serial Peripheral Interface (SPI) is a general-purpose synchronous serial interface originally found on certain Motorola micro-controllers. The MultiMediaCard SPI interface is compatible with SPI hosts available on the market. As any other SPI device the MultiMediaCard SPI channel consists of the following 4 signals:- CS : Host to card chip select signal- CLK : Host to card clock signal- DataIn : Host to card data signal- DataOut : Card to host data signalAnother SPI common characteristic, which is implemented in the MultiMediaCard card as well, is byte transfers. All data tokens are multiples of 8 bit bytes and always byte aligned to the CS signal. The SPI standard defines the physical link only and not the complete data transfer protocol. The MultiMediaCard uses a subset of the MultiMediaCard protocol and command set.4.4.2 SPI Bus TopologyThe MultiMediaCard card identification and addressing algorithms are replaced by hardware Chip Select (CS) signal. There are no broadcast commands. A card (slave) is selected, for every command, by asserting (active low) the CS signal (see Figure 4-3). The CS signal bust is continuously active for the duration of the SPI transaction (command, response and data). The only exception is card-programming time. At this time the host can de-assert the CS signal without affecting the programming process. The bi-directional CMD and DAT lines are replaced by unidirectional dataIn and dataOut signals. This eliminates the ability of executing commands while data is being read or written and, therefore, eliminates the sequential and multi block read/write operations. The SPI channel supports only single block read/write.Figure 4-3 SPI Bus SystemReadThe read access time is defined as the sum of the two times given by the CSD parameters TAAC and NSAC (refer to Table “Card Specific Data (CSD)”). These card parameters define the typical delay between the end bit of the read command and the start bit of the data block. This number is card dependent and should be used by the host to calculate throughput and the maximal frequency for stream read.WriteThe R2W_FACTOR field in the CSD is used to calculate the typical block program time obtained by multiplying the read access time by this factor. It applies to all write/erase commands (e.g. SET(CLEAR)_WRITE_PROTECT, PROGRAM_CSD(CID) and the block write commands). It should be used by the host to calculate throughput.EraseThe duration of an erase command will be (order of magnitude) the number of sectors to be erased multiplied by the block write delay.4.8 Card Identification ModeAll the data communication in the card identification mode uses only the command line (CMD). MultiMediaCard State Diagram (Card Identification Mode)Figure 4-2 MultiMediaCard State Diagram (Card Identification Mode)The host starts the card identification process in open drain mode with the identification clock rate f OD(generated by a push pull driver stage). The open drain driver stages on the CMD line allow the parallel card operation during card identification. After the bus is activated the host will request the cards to send their valid operation conditions with the command SEND_OP_COND (CMD1). Since the bus is in open drain mode, as long as there is more than one card with operating conditions restrictions, the host gets in the response to the CMD1 a “wired or” operation condition restrictions of those cards. The host then must pick a common denominator for operation and notify the application that cards with out of range parameters (from the host perspective) are connected to the bus. Incompatible cards go into Inactive State (refer to also Chapter “Operating Voltage Range Validation”). The busy bit in the CMD1 response can be used by a card to tell the host that it is still working on its power-up/reset procedure (e.g. downloading the register information from memory field) and is not ready yet for communication. In this case the host must repeat CMD1 until the busy bit is cleared. After an operating mode is established, the host asks all cards for their unique card identification (CID) number with the broadcast command ALL_SEND_CID (CMD2).All not already identified cards (i.e. those which are in Ready State) simultaneously start sending their CID numbers serially, while bit-wise monitoring their outgoing bitstream. Those cards, whose outgoing CID bits do not match the corresponding bits on the command line in any one of the bit periods, stop sending their CID immediately and must wait for the next identification cycle (cards stay in the Ready State). There should be only one card which successfully sends its full CID-number to the host. This card then goes into the Identification State. The host assigns to this card (using CMD3, SET_RELATIVE_ADDR) a relative card address (RCA, shorter than CID), which will be used to address the card in future communication (faster than with the CID). Once the RCA is received the card transfers to the Standby State and does not react to further identification cycles. The card also switches the output drivers from the open-drain to the push-pull mode in this state. The host repeats the identification process as long as it receives a response (CID) to its identification command (CMD2). When no card responds to this command, all cards have been identified. The time-out condition to recognize this, is waiting for the start bit for more than 5 clock periods after sending CMD24.8.1 Operating Voltage Range ValidationThe MultiMediaCard standards operating range validation is intended to support reduced voltage range MultiMediaCards. The MultiMediaCard supports the range of 2.7 V to 3.6V supply voltage. So the MultiMediaCard sends a R3 response to CMD1 which contains an OCR value of 0x80FF8000 if the busy flag is set to “ready” or 0x00FF8000 if the busy flag is active (refer to Chapter “Responses”). By omitting the voltage range in the command, the host can query the card stack and determine the common voltage range before sending out-of-range cards into the Inactive State. This bus query should be used if the host is able to select a common voltage range or if a notification to the application of non usable cards in the stack is desired. Afterwards, the host must choose a voltage for operation and reissue CMD1 with this condition sending incompatible cards into the Inactive State.4.9 Data Transfer ModeWhen in Standby State, both CMD and DAT lines are in the push-pull mode. As long as the content of all CSD registers is not known, the f PushPull clock rate is equal to the slow f OpenDrain clock rate. SEND_CSD (CMD9) allows the host to get the Card Specific Data (CSD register), e.g. ECC type, block length, card storage capacity, maximum clock rate etc..。

第2章MC9S12DG128的结构与工作原理

2.1 MC9S12DG128的内部结构

2.1.1 CPU12内核(Star Core)

(2)间址/变址寄存器(Index Register) X、Y

❖ CPU12内部有两个16位地址寄存器IX和IY,称为间接寻址寄 存器,简称间址寄存器或变址寄存器。一般情况下作为指针 寄存器,用于多种寻址方式下的地址计算,也可用于临时存 放数据或参与一些运算,只能按照16位方式访问。

❖ 若把一个16位数据存入累加器D中,则高8位在A寄存器中,低8位在B 寄存器中。与此相对应,若把D寄存器中的一个16位数据存入存储器, 则高8位在存储器的低位地址,低8位在存储器的高位地址。

❖ 注意,任何Motorola (Freescale)公司独立设计的16位、32位CPU中, 寄存器与存储器字节的对应关系都是高位数据存放于低位地址,低位数 据占用高位地址,这与Intel公司的CPU数据存放格式正好相反。

2.1 MC9S12DG128的内部结构

2.1.1 CPU12内核(Star Core)

❖ SP主要用于堆栈管理,用于中断和子程序调用时保存系统地址信息,也 可以存储临时信息,一般不做他用。

❖ 在不影响其内容的前提下,也可替补用作所有变址寻址方式下的变址寄 存器,通常不参与运算。

❖ 惟一例外的是,在符号扩展指令中用作目的寄存器。此外,还具有自身 的加、减1指令。

(Program State Word),但不同的是,它还可以参与控制CPU的行为。 ❖ 条件码寄存器中各位的定义:

CCR中的各位包括两部分: ➢5个算术特征位(Arithmetic Flag Bit) ,即H、N、Z、V、C,它们反映上一条指令执 行结果的特征(状态); ➢3个MCU控制位,即中断屏蔽位X、I和STOP指令控制位,这3位通常由软件设定, 以控制CPU的行为。复位后,X、I两位默认状态为1,屏蔽系统中断。CCR是真正的 专用寄存器,除了C、H位以外,其他各位不参与任何运算。

六讲MCS单片机IO接口和功能模块

使用PORTJ中断口功能旳例子,本例旳原理是: 设置A口为输出口,PTA旳第6脚跟PTJ旳第6脚 硬件相连,PTB输出,用来控制8个LED灯, PTJ开中断,而且设置为上升沿触发。首先PTA 初始化为0,PTB为0xFF,此时等灭。在大循环 冲设置PTA第6位为高电平,产生中断,灯低4 个亮,高4个不亮。使用单步运营查看效果。

数据旳格式,一共有8种情况。 SCAN:连续转换队列旳模式。此位定义了A/D 转换是连续进行

还是只进行一次。1=连续队列转换;0=单次队列转换。 MULT:当这位为0 时,ATD 旳队列控制器只从指定旳输入通道

进行采样,能够使用ATDCTL5寄存器中旳CC、CB 和CA 三位来 指定需要采样旳模拟量输入通道。当这位为1 时,则对多种旳通 道进行采样,每次采样旳通道数量由S8C、S4C、S2C 和S1C 控制 位来指定,第一种采样通道由CC、CB 和CA 控制位来指定,其 他采样通道由通道选择码CC、CB 和CA 旳增长来决定。 CC、CB、CA:模拟输入通道选择码。和MULT配合使用。

设置方向寄存器(DDRx)为输入(0X00) 随时读取I/O口旳数据寄存器(PORTx)

I/O口作为输出使用

设置方向寄存器(DDRx)为输出(0XFF) 设置驱动能力寄存器(非必须) 拉电阻选择(非必须) 随时写入I/O口数据寄存器(PORTx)

1、通用I/O接口

I/O口作为外部中断接受使用

MC9S12DG128B单片机I/O口

PORTA

连接按键

PORTB

连接发光二极管

PORTE

特殊功能

PORTJ

中断输入,没有PJ0-PJ5

PORTP

中断输入,没有PP6

PORTM

通讯设备MCi中文手册与指令手册

SrvprofieId是服务配置ID,可以建立0-9共10个配置ID,比如说可以用AT^SISS将配置0作socket,配置1作HTTP,配置2作FTP等,然后要启用哪个服务,就用AT^SISO=0或1或2打开哪个服务,要关掉哪个服务就用AT^SISC=0或1或2关闭哪个服务。一般的数据传输用的都是socket服务;SISS指令里的ConID是指当前服务调用哪个连接配置ID(conProfileId),连接配置ID可以设定6个,可以用AT^SICS=0,apn,cmnet或者AT^SICS=1,apn,cmwap设定不同的APN,根据不同的应用,调用不同的连接配置。

at^sics=0,conType,GPRS0//设置GPRS工作模式

at^sics=0,user,cm//用户名称

at^sics=0,pass0,apn,cmnet//网络接入点名称

at^siss=1,srvType,socket//设置服务类型为socket

通讯设备MCi中文手册与指令手册

继TC35i/mc39i/mc55后,siemens/cinterion又推出了mc37i/mc52i/mc55i。

MC52i包括了MC35i,MC39i,Tc35i的所有功能,引脚和指令完全兼容MC55/MC56。

MC52i和MC55i的区别

MC52i和MC55i是内部自带协议栈的两个GPRS模块,他们支持以下Internet服务:

AT^SISS:2,"srvType",""//第2个服务平台

AT^SISS:3,"srvType",""//第3个服务平台

AT^SISS:4,"srvType",""//第4个服务平台

W25Q128BV中文版

在唤醒过程中,当电压VCC升到高于Vwi时,编程和擦除的相关指令仍然要等待一段时间 tpuw, 这些指令包括写使能,页写,擦除扇区,擦除块,擦除整个芯片和写状态寄存器。上 电过程中,/CS 必须踪电压 VCC,直到电压达到 VCC_min后再延迟 tvsl 时间。可以在/CS管 脚上加一个上拉电阻来实现。

Sector 14 (4KB)

xxEFFFh •

xxE0FFh

xxDF00h •

xxD000h

Sector 13 (4KB)

xxDFFFh •

xxD0FFh

• • •

xx2F00h •

xx2000h

xx1F00h •

xx1000h

xx0F00h •

xx0000h

Sector 2 (4KB) Sector 1 (4KB) Sector 0 (4KB)

9.1.4,顶部/底部块保护(TB)、 非易失性的 TB 位,可以控制 BP 是从顶部开始还是底部开始。TB=0,从顶部开始,TB=1 从底部开始。默认的是从 TB=0 顶部开始的。TB 位是可以通过写状态寄存器指令来操作 的。

SPI 总线操作模式 0 和模式 3 都是被支持的。模式 0 与模式3 的最大区别在于,当 SPI 总 线的主设备处在待机状态,并且没有数据传输到串行 FLASH 时的 CLK 的信号状态。对模式 0 来说,当/CS 在上升沿和下降沿的时候,CLK 总是在处在低电平。在模式 3 的时候,当/ CS 处在上升沿和下降沿的时候 ,CLK 总是处在高电平。

High Voltage Generators

ATmega128L单片机的Micro+SD卡读写

机开始所有的总线传输。数据从单片机的MOSI引脚同 步输入Micro SD卡的DI引脚,并由Micro SD卡的D0线 同步输入单片机的MISO引脚,数据在CLK信号的上升 沿同步输入和输出。在每个数据传输的结尾还必须提供 8个额外的时钟,以允许Micro SD卡完成任何未完结的 操作。由于Micro SD卡的电压为3.3 V,所以选择需要支 持3.3 V的I/O端口输出的ATmegal28L单片机。另 外,使用SPI模式时,为了防止在无卡接人或卡驱动器呈 高阻态时总线悬空,根据SD卡规范,这些信号需要在主 机端用10 kfl ̄lOO kQ的上拉电阻。其硬件连接电路如图 1所示。

模式选择信息,因为卡选择(CS)引脚在该命令和其他所

有SPI命令传送过程中都保持为低电平。Micro SD卡以

Rl作为响应。空闲状态位被置为高电平,此时Micro SD

卡进入空闲状态,此阶段的SPI时钟频率不能超过400

kHz(将SPCR寄存器设置为0x53)。Micro SD卡进入

SPI模式后,主机应该先发一条初始化指令CMDl。此时

//打开文件

if(FAT_Delltem(&FileInfo))return 1,//删除文件记录项

return 0;

}

结语

本设计将Micro SD卡的存储方式应用到电脑横机控 制系统中,简化了花型文件数据存储设计,减小了系统的 尺寸,提高了系统的可靠性,使得花型文件的读出和存取 简单易行,裁剪了FAT32实现了嵌入式文件系统,提高了 系统的存储能力。采用ATmegal28L高性能单片机的串 行外设接口sPI,满足访问Micro SD卡的功能要求,加快 了整个系统的设计进程。实践证明,该文件系统读取Mi— cro SD卡上花型文件的速度满足该控制系统的要求。该 嵌入式文件系统只需对底层驱动进行简单修改就可移植

飞思卡尔MC9S12XS128单片机重点模块讲解

�

这一点和 51 单片机的 I/O 口有区别,在典型的 51 单片中 P0 口内部没有上拉电阻,但作为 I/O 口使用时需要外接排阻。其他 P1-P3 口则可以直接作为双向口使用,51 单片在上电复位 后端口被默认的置 1.在 51 单片中端口的某一位置 0 时端口作为输出口使用,置 1 时作为输 入口使用。例如如果我们想把 P1 作为输出口使用时我们可以在程序开始时写 P1=0x00; 如果 我们想把 P1 口作为输入口使用时我们可以写 P1=0xff; 这一点正好和飞思卡尔的 128 单片机 相反,另外 128 单片有专门的数据方向寄存器 DDRA 或者 DDRB 等来管理各个端口的输入 输出选择,51 单片没有。如果我们想把端口 A 作为输入口使用,我们只需写 DDRA=0x00; 即所有位都置 0,如果我们想把端口 A 作为输出口使用,我们只需要写 DDRA=0xff; 即所有 位都置 1 ,而如 果我们想要 把端口 A 的高四 位做输入口 ,低 4 位做输 出口时我们 就 写 DDRA=0x0f; 当我们需要将该端口的某一位做输出或者输入口使用时只需要将该端口对应的 方向位置 1 或者置 0 即可。例如我们想把 A3 口作输入口, A4 口作输出口使用时我们只需 要写: DDRA_DDRA3=0; DDRA_DDRA4=1; 即可。 � � 对于数据方向寄存器的使用只要记住:置 1——输出 置 0——输入 PORTA 数据寄存器也是由 8 位组成,任何时候都可以对它进行读写操作。

#define uchar unsigned char //数据类型宏替换 #define uint unsigned int /*------------------------延时函数--------------------------------------*/ void delay(uint a) { uint i,j; for(i=0;i<a;i++) for(j=0;j<a;j++) ; } /*--------------------------指示灯闪烁函数-------------------------------*/ void light() { while(INPUT) { PORTB=0x3f; delay(500); PORTB=0x00; delay(500); } } //6 只灯全点亮 //延时一段时间 //6 只灯全熄灭 //延时一段时间 //判断输入电平的高低

潍柴天然气伍德沃德电脑版针脚定义

^0000000000000000 ^0000000(^——I I I 1=^>000000000000000*0000000,I I ------ -------------- . IJ2-A三、线束原理图OH2.0 PCM128-HD 针脚定义、OH2.0 PCM128-HD、接插件定义0H2.0 PCM128-HDJ1-C J1-B J1-A^oo 0000000 (>0)OOOOOOQOOO已??000000?9J2-B-nn^HsfI I IIJl-C Jl-B Jl-AJ* nPCM128,HD-QH2.2arsi wwrn H iin鬟=^Hxxyulinuoon^oaeeeeee o••❷••••••••••••J2-B J2-Aas sxii.t K TDMMns) ATDO4 M or nc CM M M300 W AW trw«um*^<TTE»-£FEQ£»C£CX JI dKATSM WMUALB26312 FTO d GUCO.DCSmraea SCMEHATCCS THAT ME LAILED GOCWC 3 7即 vnw EACH APFlKATgA DUAL FlXDOml I/O ZhoMLY ox njrcnoiMJTv CMK: saxcrco、▲ ) ।―•eeeaoeoPT 口CXHHJ X C M T UH^TIES DU7 * L A BLEDV0QIIW4AD 亚ACCUMTE REP«ESCMTATaJ«,<TTDSMELtt $HM.O BC MMOCD KT THEPOt-iaaMD CHASSIS GWI)o o 0墟QiQgi由目壮姓线以Tirra-CTOi 'Ogc m uxi *nx< ^wr^nv cunw P>M <em. Mfi•W0*^ —■»,««MMO —C «B0aU <■■,1 —H <M«^> 3,3«AC M 31U;,SM CABLE TfH TlLyGlL•num* voii crow cxi iMyirdrO-GiL(G*Ywral Purpow CCOM CX)3D£ SQE TH …CXUDK j SAXHX O4.V?ECD^€NBED 3 STAMDAfiUJ12W. JH 组J2202IM£SS OTHWBE SRIflTEJ. MMOtSIDfiARE . MJ€i MkwoppWAfcB您客MJD^y—ETVCGR0CC-20C60£C-200eDIAGRAM-PLANT WIRINGPCN128HlhDH22 x406 SDEC - FMV9971-13802NTS 1 OF 2四、针脚定义1、J1-A接插件®0(2)(S)@(S)(2)©(g)®<2、J1-B接插件(§)⑥⑤卷)@)感)。

资料:MC9S12XS128中文资料

飞思卡尔智能汽车竞赛XS128主要模块实验指导书第一章端口整合模块端口A,B和K为通用I/O接口端口E 整合了IRQ,XIRQ中断输入端口T 整合了1个定时模块端口S 整合了2个SCI模块和1个SPI模块端口M 整合了1个MSCAN端口P 整合了PWM 模块,同时可用作外部中断源输入端口H 和J 为通用I/O接口,同时可用作外部中断源输入端口AD 整合了1个16位通道ATD模块大部分I/O引脚可由相应的寄存器位来配置选择数据方向、驱动能力,使能上拉或下拉式装置。

当用作通用IO口时,所有的端口都有数据寄存器和数据方向寄存器。

对于端口T, S, M, P, H, 和J 有基于每个针脚的上拉和下拉控制寄存器。

对于端口AD 有基于每个针脚的上拉寄存器。

对于端口A、B、E 和K,有一个基于端口的上拉控制寄存器。

对于端口T, S, M, P, H, J, 和AD,有基于每个针脚的降额输出驱动控制寄存器。

对于端口A, B, E, 和K,有一个基于端口的降额输出驱动控制寄存器。

对于端口S、M,有漏极开路(线或)控制寄存器。

对于端口P、H 和J,有基于每个针脚的中断标志寄存器。

纯通用IO端口共计有41个,分别是:PA[7:0]PB[7:0]PE[6:5]PE[3:2]PK[7,5:0]PM[7:6]PH[7:0] (带中断输入)PJ[7:6] (带中断输入)PJ[1:0] (带中断输入)第二章脉冲宽度调制模块XS128具有8位8通道的PWM,相邻的两个通道可以级联组成16位的通道。

PWME:PWM通道使能寄存器。

PWMEx=1将立即使能该通道PWM波形输出。

若两个通道级联组成一个16位通道,则低位通道(通道数大的)的使能寄存器成为该级联通道的使能寄存器,高位通道(通道数小的)的使能寄存器和高位的波形输出是无效的。

PWMPOL:PWM极性寄存器。

PPOLx=1,则该通道的周期初始输出为高电平,达到占空比后变为低电平;相反,若PPOLx=0,则初始输出为低电平,达到占空比后变为高电平。

美国MCC数据采集卡选型手册A-ProductSelGuide-CHINESE-Simple

高性价比的数据采集设备

方案

应用范围广 最优性价比

USB | 温度 | OEM | 记录器 | PCI/PCIe | 高级传感器测量 | 软件

2

我们不仅销售DAQ产品—我们设计创新方案以解决世界各地的工程师、 科学家、 OEM、 技术人员和学生面临的问 题。 MCC新型USB-1608G系列树立了高速度、 低成本USB数据采集产品行业新基准。 新型USB-2408系列是现有成本 最低的24位多功能数据采集仪器, 可采集温度和电压信号。 两款产品都提供了开箱即用的软件, 同时提供多种应用程 序和编程接口。

USB | 温度 | OEM | 记录器 | PCI/PCIe | 高级传感器测量 | 软件

5

高速BNC多功能模块

USB-1602HS和USB-1604HS系列

• 1.33 MS/s或2 MS/s同步采样 • 32路数字I/O, 计数器/定时器 • 包含软件和驱动

多功能温度和电压采集模块

USB-2408系列

最高2mss采样率数字io和计数器定时器包括正交编码器性价比高众多型号可选usb软件mccdaqcom高性价比的数据采集设备usbdaq16位高速多功能模块usb1608g系列采样率从250kss到500kss包含windowslinuxmac系统的软件和驱动高速16位多功能模块usb1616hs系列包含软件和驱动低价位高速模块usb1208hs系列包含的软件和驱动低价位多功能模块usb120814081608系列最高500kss采样率包含软件和驱动电压温度和基于电桥的输入模块usb2404系列4路通用模拟输入usb2404ui最高50kss采样率最大输入范围60包含软件和驱动无操作系统依赖的daq模块usb7000系列daqflex最高200kss采样率包含软件和驱动usb软件mccdaqcom高性价比的数据采集设备usbdaq16位同步采集模块usb1608hs系列每通道250kss同步采样包含软件和驱动多功能温度和电压采集模块usb2408系列最高1kss采样率包含windowslinux和mac的软件和驱动高速多功能板卡usb2500系列24路数字io4个计数器可配置为正交编码器包含软件和驱动低成本温度和电压采集模块usbtemp和tc系列包含软件和驱动高精度多功能usb2416系列包含软件和驱动高速bnc多功能模块usb1602hs和usb1604hs系列133mss或2mss同步采样包含软件和驱动usb软件mccdaqcom高性价比的数据采集设备usbdaq固态数字io模块usbssr系列使用标准oac5odc5iac5idc5模块单独出售包含软件和驱动24通道数字io模块usb1024系列包含软件和驱动数字io板卡和模块usbdio24系列和dio96h包含软件和驱动模拟输出模块usb3100系列包含软件和驱动正交编码器模块usbquad0810mhz计数器12v输入范围包含软件和驱动机电继电器模块usberb系列在240vac28vdc电压下可通过6a的电流包含软件和驱动usb软件mccdaqcom高性价比的数据采集设备温度在线查看更多产品

科迈10 通讯协议

40030 8627 L2发电特性 Char 1 - - - 发电机

40021 8528 发电无功L2 kVAr Integer 2 0 - - 发电机

40022 8529 发电无功L3 kVAr Integer 2 0 - - 发电机

40005 9628 发电12线压 V Unsigned 2 0 - - 发电机

40006 9629 发电23线压 V Unsigned 2 0 - - 发电机

40058 8759 (N/A)

40052 10124 (N/A)

40053 10603 D+ V Integer 2 1 - - 控制器 I/O

40009 8199 发电电流 L2 A Unsigned 2 0 - - 发电机

40010 8200 发电电流 L3 A Unsigned 2 0 - - 发电机

40031 8628 L3发电特性 Char 1 - - - 发电机

40032 8565 发电千伏安 kVA Integer 2 0 - - 发电机

40025 8534 发功率因数L2 Integer 1 2 - - 发电机

40026 8535 发功率因数L3 Integer 1 2 - - 发电机

40056 8229 燃油位 % Integer 2 0 - - 控制器 I/O

40057 8978 (N/A)

40001 8192 发电压1 V Unsigned 2 0 - - 发电机

40002 8193 发电压2 V Unsigned 2 0 - - 发电机

40033 8530 发电千伏安L1 kVA Integer 2 0 - - 发电机

麦格纳电子设备公司XR系列2U程控直流电源说明书

XR 系列2U 程控直流电源 • 可靠电流馈电式功率处理工艺概述2U XR系列通过在2 kW,4 kW,6 kW,8 kW,8 kW和10 kW的2U封装中提供高电压(大于1500 VDC)和高电流(大于250 ADC)模型,从而补充了1U SL系列。

XR系列具有Magna-Power产品产品中最高的电压范围,最多10,000 VDC和高电流型号高达600 ADC,所有这些型号都利用了公司的签名电流喂养的功率处理来提供强大的电源转换。

此外,高精度编程和监视水平使电源测量值有信心,从而消除了对外部电力计的需求。

主要特性•高精度测量•主从式操作功能•远地感应•37-pin外部模拟量I/O接口•RS232接口•可选配以太网接口和GPIB接口•0-10V外部模拟输入•可编程设置保护限值•快速瞬态响应•远程接口软件•NI LabVIEW和IVI驱动器•联锁功能迅速切断输入•在美国设计和制造可用选项•高转换速率输出(+HS)•IEEE-488 GPIB通信(+GPIB)•LXI TCP/IP以太网通信(+LXI)•增强冲击震动标准(+RUG)1标准型号规定纹波。

对于具有高转换速率输出(+HS)的型号,纹波更高。

详情请参考选项页。

第 10 页麦格纳电子设备公司第 11 页数据表 (4.5.1)MagnaDC 程控直流电源规格交流输入隔离±2500 Vdc,对地最大输入电压通过 RoHS 认证是后支撑轨包括在内GPIB: IEEE-488注:参数如有更改,恕不另行通知。

输入电压规格为两线间规格。

(8.89 x 48.26 x 60.96 cm)第 12 页麦格纳电子设备公司XR 系列2U 程控直流电源 • 可靠电流馈电式功率处理工艺产品图前面板Models with Output Voltage Rating ≤1000 Vdc onlyRefer to “DC Output Bus Connections”3/8-16 Threaded Insert, Qty (2)High Voltage Mating Cable Provided直流输出总线直流输出总线直流输出总线高压输出电缆包含于额定电压大于3,000 Vdc的型号RS232 (JS3)37-PIN EXTERNAL USER I/O (JS1)IEEE-488 GPIB (JS4)TCP/IP ETHERNET (JS5)RS232 (JS3)37-PIN EXTERNAL USER I/O (JS1)LAN RST背面IEEE-488 GPIB (+GPIB) 选项背面LXI TCP/IP 以太网 (+LXI) 选项第 13 页数据表 (4.5.1)MagnaDC 程控直流电源1电源开关:在未接通输出时接通控制电路4通过集成机械接触器接通和断开总电源5用无级旋钮设定电压和电流8REM SEN远地感应:远地感应启用 INT CTL内部:前面板启动/停止/启用清除 EXT CTL外部:外部启动/停止/启用清除 ROTARY旋转:前面板旋钮输入 EXT PGM外部:外部模拟电压电流控制 REMOTE远程:远程计算机控制2POWER电源:显示电源接通 STANDBY待机:待机状态7诊断警报 LOC:联锁 PGL:外部输入电压超限 THL:超高温条件 OVT过压跳闸:过压保护跳闸 OCT过流跳闸:过流保护跳闸6仪表显示输出电压/电流、电压/电流设定点、过压/过流跳闸3功能键MENU菜单:选择功能 ITEM项目:选择功能内的项目 V/I DIS V/I显示器:显示电压和电流设置 TRIP DIS跳闸显示器:显示过压/过流跳闸设置 CLEAR清除:清除设置或重置故障 ENTER进入:选择项目C 版前面板–空白前面板概述(15) XR系列电源,选配+CAB3选件产品选件阻流二极管 (+BD)集成阻塞二极管(+BD)选项在MagnaDC程控直流电源的正输出端提供一个外部散热保护二极管。

MC9S12XS128单片机简介

MC9S12XS128 单片机简介1、HCS12X 系列单片机简介Freescale 公司的16 位单片机主要分为HC12 、HCS12、HCS12X 三个系列。

HC12核心是16 位高速CPU12 核,总线速度8MHZ;HCS12 系列单片机以速度更快的CPU12 内核为核心,简称S12 系列,典型的S12 总线速度可以达到25MHZ。

HCS12X 系列单片机是Freescale 公司于2005 年推出的HCS12 系列增强型产品,基于S12 CPU 内核,可以达到25MHz 的HCS12 的2-5 倍性能。

总线频率最高可达40 MHz。

S12X 系列单片机目前又有几个子系列:MC9S12XA 系列、MC9S12XB 系列、MC9S12XD 系列、MC9S12XE 系列、MC9S12XF系列、MC9S12XH 系列和MC9S12XS 系列。

MC9S12XS128 就是S12X 系列中的一个成员。

2、MC9S12XS128 性能概述MC9S12XS128 是16 位单片机,由16 位中央处理单元(CPU12X)、128KB 程序Flash(P-lash)、8KB RAM、8KB 数据Flash(D-lash)组成片内存储器。

主要功能模块包括:内部存储器内部PLL 锁相环模块2 个异步串口通讯SCI1 个串行外设接口SPIMSCAN 模块1 个8 通道输入/输出比较定时器模块TIM周期中断定时器模块PIT16 通道A/D 转换模块ADC1 个8 通道脉冲宽度调制模块PWM输入/输出数字I/O 口3、输入/输出数字I/O 口MC9S12XS128 有3 种封装,分别为64 引脚、80 引脚、112 引脚封装。

其全名分别为MC9S12XS128MAE、MC9S12XS128MAA、MC9S12XS128MAL。

MC9S12XS 系列具有丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ 和PORTAD 共11 个端口。

MC9S12DG128实验系统使用手册

MC9S12DG128实验系统使用手册目录第一章系统概述 (2)第二章硬件电路原理 (4)2.1子板硬件原理 (4)2.1.1、MCU引脚接口部分 (5)2.1.2、串口通信部分 (5)2.1.3、电源部分 (6)2.1.4、复位电路部分 (6)2.1.5、I/O端口电路部分 (7)2.1.6、晶振电路与BDM插头部分 (7)2.2母板硬件原理 (8)2.2.1、电源部分 (8)2.2.2、MC9S12DG128开发板与各接口部分 (9)2.2.3、串口通信部分 (11)2.2.4、LED数码管显示部分 (12)2.2.5、8位数字量输入输出部分 (13)2.2.6、红外发射接收部分 (14)2.2.7、LCD显示部分 (15)2.2.8、模拟量输入部分 (15)2.2.9、蜂鸣器和喇叭部分 (15)2.2.10、键盘输入部分 (16)2.2.11、继电器部分 (16)2.2.12、打印机部分 (17)2.2.13、CAN总线部分 (17)第三章 MC9S12DG128教学平台快速入门 (18)3.1硬件连接 (18)3.2软件应用 (20)第一章系统概述天津工业大学Freescale MCU/DSP研发中心开发的DG128实验系统,其功能基本上和美国MCUSLK系统相同,而且根据中国的教学情况重新设计了一些功能、力求达到更好的实验效果。

DG128实验系统由主板和独立的MCU子板构成。

DG128实验系统的主板插槽和美国的MCUSLK 系统相互兼容,主板的插槽可以插包括S12、S08、 HC08各系列MCU子板。

MCU子板可以单独调试运行,也可以插在主板上调试,充分利用主板丰富的硬件资源。

MC9S12DG128具有16位中央处理器(HCS12 CPU)、128KB Flash EEPROM、8KB RAM、2KB EEPROM,以及定时器通道、键盘中断和A/D通道等接口。

MC9S12DG128实验系统可以直接与CodeWarrior相连,具有下载程序、在线单步运行、断点调试、连续运行、修改寄存器和存储单元等特点,可以很方便的进行教学。

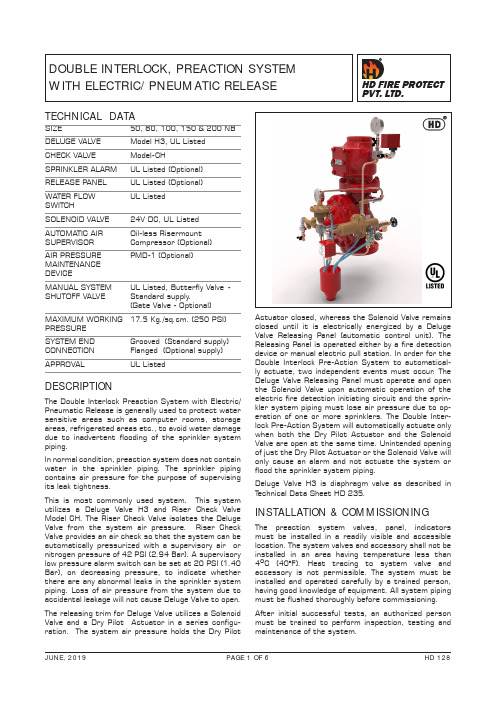

HD 128页双锁防火保护设备系列说明书

DOUBLE INTERLOCK, PREACTION SYSTEM WITH ELECTRIC/PNEUMATIC RELEASESIZE50, 80, 100, 150 & 200 NB DELUGE VAL VE Model H3, UL Listed CHECK VAL VE Model-CHSPRINKLER ALARM UL Listed (Optional)RELEASE PANEL UL Listed (Optional)WATER FLOW UL ListedSWITCHSOLENOID VAL VE 24V DC, UL Listed AUTOMATIC AIR Oil-less RisermountSUPERVISOR Compressor (Optional)AIR PRESSURE PMD-1 (Optional) MAINTENANCEDEVICEMANUAL SYSTEM UL Listed, Butterfly Valve - SHUTOFF VAL VE Standard supply.(Gate Valve - Optional)MAXIMUM WORKING 17.5 Kg./sq.cm. (250 PSI)PRESSURE SYSTEM END Grooved (Standard supply) CONNECTION Flanged (Optional supply)APPROVALUL ListedTECHNICAL DATADESCRIPTIONThe Double Interlock Preaction System with Electric/Pneumatic Release is generally used to protect water sensitive areas such as computer rooms, storage areas, refrigerated areas etc., to avoid water damage due to inadvertent flooding of the sprinkler system piping.In normal condition, preaction system does not contain water in the sprinkler piping. The sprinkler piping contains air pressure for the purpose of supervising its leak tightness.This is most commonly used system. This system utilizes a Deluge Valve H3 and Riser Check Valve Model CH. The Riser Check Valve isolates the Deluge Valve from the system air pressure. Riser Check Valve provides an air check so that the system can be automatically pressurized with a supervisory air or nitrogen pressure of 42 PSI (2.94 Bar). A supervisory low pressure alarm switch can be set at 20 PSI (1.40 Bar), on decreasing pressure, to indicate whether there are any abnormal leaks in the sprinkler system piping. Loss of air pressure from the system due to accidental leakage will not cause Deluge Valve to open.The releasing trim for Deluge Valve utilizes a Solenoid Valve and a Dry Pilot Actuator in a series configu-ration. The system air pressure holds the Dry PilotActuator closed, whereas the Solenoid Valve remains closed until it is electrically energized by a Deluge Valve Releasing Panel (automatic control unit). The Releasing Panel is operated either by a fire detection device or manual electric pull station. In order for the Double Interlock Pre-Action System to automatical-ly actuate, two independent events must occur . The Deluge Valve Releasing Panel must operate and open the Solenoid Valve upon automatic operation of the electric fire detection initiating circuit and the sprin-kler system piping must lose air pressure due to op-eration of one or more sprinklers. The Double Inter-lock Pre-Action System will automatically actuate only when both the Dry Pilot Actuator and the Solenoid Valve are open at the same time. Unintended opening of just the Dry Pilot Actuator or the Solenoid Valve will only cause an alarm and not actuate the system or flood the sprinkler system piping.Deluge Valve H3 is diaphragm valve as described in T echnical Data Sheet HD 235.INSTALLATION & COMMISSIONINGThe preaction system valves, panel, indicators must be installed in a readily visible and accessible location. The system valves and accessory shall not be installed in an area having temperature less than 4o C (40oF). Heat tracing to system valve and accessory is not permissible. The system must be installed and operated carefully by a trained person, having good knowledge of equipment. All system piping must be flushed thoroughly before commissioning. After initial successful tests, an authorized person must be trained to perform inspection, testing and maintenance of the system.RECOMMENDED SEQUENCE OF INSTALLATIONSIn planning the installation, consideration must also be given to the disposal of relatively large quantities of water that may be associated with draining of the system or performing flow test.1.Install the Deluge Valve on Riser in vertical position.2. Install the Riser Check Valve above Deluge Valveas shown in installation drawing.3.On completion of system piping, install all the trims as per the trim drawing. Care must be taken to ensure that Check Valves, Strainers, Valves etc. are installed with the flow arrows in the proper direction.4. Connect all drain piping as shown in the drawing.5. All unused opening on valve or trim parts mustbe plugged.6. Connect air supply line.7. Connect all electrical to control panel as perwiring drawing.8. Make sure that all the nut bolts, fittings arescrewed properly.9. Follow the valve resetting and test procedure.10. The pipe fittings and nipple must be cleaned. Usethread sealent on male threads only.11. For common drain piping a check valve to beprovided interconnecting main dran and the funnel.12. The drain tubing to be drip funnel must be installedwith smooth bends that will restrict flow.13. The drain piping must be free-flow and care mustbe taken to direct the drain in proper area to avoid damage due to release of system.14. A supervisory air or nitrogen supply is to beinstalled as given in the data sheet. An air dryer , if specified, needs tobe installed as per authority having jurisdiction.15. The electric connection through conduit is to bemade as per authority having jurisdiction.RESETTING PROCEDUREa. Close the upstream side stop valve of the Deluge Valve.b. Open drain valves and allow water to drain (if water flow was establish) & close drain valve when water flow has ceased.c. Check all release devices are closed. Inspect the release devices if system was subject to fire condition.d. Open the air supply line and check the pressure is maintained up to 42 PSI (2.94 Bar). and Control Panel is kept on.e. Open the priming line so that the diaphragm chamber reads the system water pressure. Open the manual release station partly to vent the air& then close it.f. Open the upstream side of stop valve to read the Deluge Valve Inlet water supply pressure. The Deluge Valve is set.g. Check all the trim parts for possible leak.INSPECTION AND MAINTENANCEInspection and testing is to be carried out only by an authorized and trained personnel. DO NOT TURN OFF the water supply or close any valve to make repair(s) or test the valve, without placing a roving fire patrol in the area covered by the system. Also inform the local security personal and central alarm station, so that there is no false alarm signal. It is recommended to carry out physical inspection of the system at least twice a week. The inspection should verify that no damage has taken place to any components and check for following normal condition of the system. The owner is responsbile for maintaining the pre-action system.NORMAL CONDITIONa. A ll main valves are open and sealed with tamper proof seal.b. All drain valves are in closed condition.c. No leak or drip is detected from drip valve.d. All water gauge of deluge valve, should show the required pressure.e. No leak in any trim or other piping.f. Release panel is on and no abnormal indication are seen.g. All testing procedure to be verified.Procedure outlined below will result in operation of associated alarm. Concerned authorities to be in-formed about the tests before conducting the tests.QUATERLY TESTWATER FLOW ALARM TESTOpen the sprinkler alarm gong test valve, the water will flow through sprinkler alarm and/or water flow switch. On satisafctory observation close the alarm test valve.SOLENOID VALVE TESTa. Close the inlet valve of Deluge Valve and open themain drain valve.b. Close the air supply valve and drain the airpressure by opening drain valve of check valve.c. Activate the solenoid valve through detector(zone-1) or manual release zone-2.d. Observe water flow through solenoid valve outlet.e. Deactivate solenoid valve deactivating theinitiating zone (zone-1/ zone-2).f. Reset the system as resetting procedure.AIR SUPPERVISORY LOW PRESSURE ALARM TESTRelease air pressure gradually through valve provided on check valve. When air pressure drops to 20 PSI (1.40 Bar), the supervisory low pressure alarm must be observed. Close the valve & observe that air pressure has been established to 42 PSI (2.94 Bar), the supervisory air pressure alarm must come to normal condition. If required reset the release panel.ANNUAL OPERATION TESTT esting valve operation without causing water upply to the deluge valve.a. Close the main system valve controlling water supply to the deluge valve.b. Open the main drain valve provided on deluge inletside and allow water to drain. When water flow from drain valve has stopped, crack open the main system valve and close the main drain valve partly allowing the water pressure at inlet of deluge valve to raise up to 1.4 Kg. / Sq. Cm.(20 PSI) and no more pressure is rising.c. Actuate the solenoid valve from control panel as per instruction of control panel manufacturer . Deluge Valve must open and water flow must be noticed through drip valve and through solenoid valve. Close the main supply control valve immediately and allow water to drain fromdrain valve.d. When water flow has stopped, reset the deluge valve as per resetting procedure.The steps b & c must be performed very quickly to prevent water flow to riser .NOTE: For abnormal condition of deluge valve refer the data sheet No. HD235.CAUTIONThe system must be inspected, tested and main-tained as instructed above, in addition to the requirement of NFPA or as per requirement of authority having jurisdiction. The owner is responsible for the inspection, testing and maintenance of the system and devices.DOUBLE INTERLOCK PREACTION SYSTEM WITH ELECTRIC/PNEUMATIC RELEASEPART LISTPREACTION TRIM SIZE QUANTITY PER PREACTION TRIM ITEM NO CODE NO DESCRIPTION SIZE/ MAKE200 NB150 NB100 NB80 NB50 NB1BFV WAFER TYPE GEAR OPRT.WITH TAMPER SWITCH *2”, HD MAKE(MODEL NO.HDMW300)1111126458DELUGE VAL VE FLANGE END 2”, HD MAKE (MODEL NO.DV-H3)----1 26455DELUGE VAL VE FLANGE END3”, HD MAKE (MODEL NO.DV-H3)---1-26454DELUGE VAL VE FLANGE END4”, HD MAKE (MODEL NO.DV-H3)--1--26453DELUGE VAL VE FLANGE END6”, HD MAKE (MODEL NO.DV-H3)-1---26457DELUGE VAL VE FLANGE END8”, HD MAKE (MODEL NO.DV-H3)1----31563DRY PILOT ACTUATOR1/2” HD MAKE (MODEL NO. H1)11111 41951EMERGENCY RELEASE STATION1/2” HD MAKE (MODEL NO.ERS-1)11111 59392ANGLE VAL VE1-1/4”---22 59394ANGLE VAL VE2”222--69423PRIMING VAL VE1/2”11111 7-RESTRICTED CHECK VAL VE1/2”11111 81825ANTI RESET VAL VE (ARV-1)1/2”11111 93569CHECK VAL VE - FLANGE TO GROOVE2”, HD MAKE (MODEL NO. CH)----1 9114345CHECK VAL VE - FLANGE TO GROOVE3”, HD MAKE (MODEL NO. CH)---1-9114346CHECK VAL VE - FLANGE TO GROOVE4”, HD MAKE (MODEL NO. CH)--1--9114343CHECK VAL VE - FLANGE TO GROOVE6”, HD MAKE (MODEL NO. CH)-1---9114347CHECK VAL VE - FLANGE TO GROOVE8”, HD MAKE (MODEL NO. CH)1----101674PRESSURE MAINTENANCE DEVICE*1/2” (PMD-1)11111 11114071PRESSURE GAUGE0-300 PSI, UL LISTED33333 121416SPRINKLER ALARM (GONG BELL)*HD MAKE (TYPE-A)11111 13-PRESSURE SWITCH POTTER MAKE, UL LISTED22222 14-SOLENOID VAL VE PARKER MAKE, UL LISTED11111 15DV RELEASING PANEL *POTTER MAKE, UL LISTED11111 16TRIM FITTINGS11111 17AUTOMATIC SPRINKLER **-----18HEAT DETECTOR/ SMOKE DETECTOR**-----19SPLASH PROOF FUNNEL11111* OPTIONAL SUPPLL Y** NOT SUPPLLIED BY HD FIRENOTES:DELUGE VAL VE END CONNECTION (OPTIONAL - G X G/ F X F) F = FLANGE ENDCHECK VAL VE END CONNECTION (OPTIONAL - G X G/ F X G / F X F)G = GROOVE ENDBUTTERFL Y VAL VE END CONNECTION (OPTIONAL - G X G/ WAFER TYPE / LUG TYPE)PRESSURE GAUGE (OPTIONAL - HDP-1 / HDP-2)OPTIONAL TRIM SUPPL Y - LOOSE / SEMI ASSEMBLED)SHAPE OF FITTINGS / VAL VES MAY CHANGE.SYSTEM PIPING, SPRINKLER, DETECTOR NOT SUPPLIED BY HD FIREPRIMING LINE BY OTHERSLIMITED WARRANTYHD FIRE PROTECT PVT. L TD. hereby referred to as HD FIRE warrants to the original purchaser of the fire protection products manufactured by HD FIRE and to any other person to whom such equipment is transferred, that such products will be free from defect in material and workmanship under normal use and care, for two (2) years from the date of shipment by HD FIRE. Products or Components supplied or used by HD FIRE, but manufactured by others, are warranted only to the extent of the manufacturer’s warranty. No warranty is given for product or components which have been subject to misuse, improper installation, corrosion, unauthorized repair , alteration or un-maintained. HD FIRE shall not be responsible for system design errors or improper installation or inaccurate or incomplete information supplied by buyer or buyer’s representatives.HD FIRE will repair or replace defective material free of charge, which is returned to our factory, transportation charge prepaid, provided after our inspection the material is found to have been defective at the time of initial shipment from our works. HD FIRE shall not be liable for any incidental or consequential loss, damage or expense arising directly or indirectly from the use of the product including damages for injury to person, damages to property and penalties resulting from any products and components manufactured by HD FIRE. HD FIRE shall not be liable for any damages or labour charges or expense in making repair or adjustment to the product. HD FIRE shall not be liable for any damages or charges sustained in the adaptation or use of its engineering data & services. In no event shall HD Fire’s product liability exceed an amount equal to the sale price.The foregoing warranty is exclusive and in lieu of all other warranties and representation whether expressed, implied, oral or written, including but not limited to, any implied warranties or merchantability or fitness for a particular purpose. All such other warranties and representations are hereby cancelled.NOTICE :The equipment presented in this bulletin is to be installed in accordance with the latest publication standards of NFPA or other similar organisations and also with the provision of government codes or ordinances wherever applicable.The information provided by us is to the best of our knowledge and belief, and consist of general guidelines only. Site handling and installation control is not in our scope. Hence we give no guarantee for result and take no liability for damages, loss or penalties whatsoever , resulting from our suggestion, information, recommendation or damages due to our product.Product development is a continuous programme of HD FIRE PROTECT PVT. L TD. and hence the right to modify any specification without prior notice is reserved with the company.D-6/2, ROAD NO. 34, WAGLE INDUSTRIAL ESTATE, THANE 400 604, INDIA.• TEL: + (91) 22 2158 2600 • FAX: +(91) 22 2158 2602•EMAIL:***************• WEB: HD FIRE PROTECT PVT . LTD.Protecting What Matters Most to YouXXXXSize 150265380410051506200Actuation Device DP Double InterlockPre-action sytem with Electric/ Pneumatic ReleaseAir MaintenanceDevice N None 1PMD-12Nitrogen Air Maintenance DeviceControl Panel N None AIncludedCompressor *N None 11/6 HP 21/3 HP 31/2 HP 43/4 HP 5 1 HP 61-1/2 HPXXXCompressor Pressure H42 PSI*Compressor standard supply is 50 Hz., 60 Hz is optional supply.。

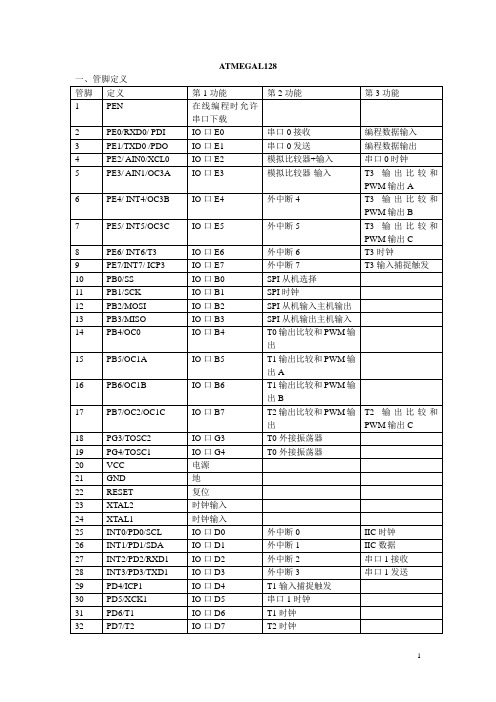

Atmegal128单片机寄存器

ATMEGAL128二、寄存器I=1:允许全局中断C=0:禁止全局中断(2)T:位复制存储将寄存器某一位复制到T,或将T复制到寄存器某一位(3)H:半进位标志位H=1:低4位向高4位有进位H=0:低4位向高4位无进位(4)S:符号位S=N异或V(5)V:2进制补码溢出标志V=1:2进制补码有溢出V=0:2进制补码无溢出(6)N:负数标志位N=1:结果是负数N=0:结果是正数(7)Z:零标志Z=1:结果是零Z=0:结果不是零(二、三)SPH,SPL:堆栈指针堆栈区的初地址,SPL是低8位,SPH是高8位(1)SRE:外部扩展时能SRE=1:允许外部扩展,三总线扩展SRE=0:禁止外部扩展(2)SE休眠模式使能SE=1:允许休眠模式SE=0:禁止休眠模式(3)SM2,SM1,SM0:休眠模式选择(4)IVSEL:中断向量选择IVSEL=1:中断向量地址选择Boot区起始地址IVSEL=0:中断向量地址选择Flash区起始地址(5)IVCE:中断向量选择使能IVCE=1:使能中断向量选择IVCE=0:禁止中断向量选择(五)XMCRA:外部存储器控制A低地址(六)XMCRB:外部存储器控制B(1)XMBK外部存储器总线保持使能:XMBK=1:总线AD0~AD7口线上的总线保持功能XMBK=0:禁止总线保持使能(七)MCUCSR:复位标志(1)JTD:JTAG测试使能JTD=1:JTAG测试使能JTD=0:禁止JTAG测试(2)JTRF:JTAG测试复位标志JTRF=1:JTAG复位JTRF=0:JTAG没复位(3)WDRF:看门狗复位标志WDRF=1:看门狗复位WDRF=0:看门狗没复位(4)BORF:掉电检测复位标志BORF=1:掉电检测复位BORF=0:没掉电(5)EXTRF:外部引脚复位标志EXTRF=1:外部引脚复位EXTRF=0:外部引脚没复位(6)PORF:上电复位标志PORF=1:上电复位PORF=0:没上电复位TMS=1:寄存器PSR0和PSR321保持其数据直到被更新。

智能小车概述

51单片机、AVR单片机或DSP

51单片机、AVR单片机或DSP 均为大众组比赛认可的主控芯 片类型 51单片机适宜用于入门(便宜 功能也很不错)

最重要

备注

• 定时器

• 中断

• 输入捕捉

• PWM(脉宽调制)

• 内部存储器 ○ 学习单片机注意的模块 ○ 学习C51请注意 ○ 建议看郭天祥的网上视频 ○ 自己尝试模块的使用与制作 ○ 切勿心急 ○ 增强动手能力

学做智能车

从五个方面来说 1)硬件 2)机械 3)控制策略 4)软件 5)打酱油

硬件

何为硬件?

硬件就是基于底层电路 的设计与开发

硬件

2)硬件需要掌握的知识

一、基本的模电知识:二极管、三极管、C-MOS工艺、DA/AD、运放……

二、基本的数电知识:逻辑转换、延迟与时序控制……

三、CPU/MCU接口技术:外围的与程序接口例如:IIC总线、SPI总线……

最后献上一句 话,祝大家成功!

01 添加标题 Stay hungr y,

02 添加标题 Stay foolish!

03 添加标题 From Steven Jobs

总体介绍

汽车动态分析

车速控制系统

方向控制系统

赛道检测系统

电子控制系统

策略规划系统

行为决策系统

路况记忆系统

数据传输系统

MCU

MC9S12XS128 DSC

组委会规定比赛主控芯片为 MC9S12XS128

DSC(Digital Signal Controller)

单片机(类似于CPU)及大家 所熟悉的冯诺依曼体系,包括 接受数据,储存数据,处理数 据,发送数据

01 解剖智能车

一.Laser 二.CCD/CMOS 三.electromagnetism

IND560BC操作技术手册

本手册版权归梅特勒-托利多(常州)称重设备系统有限公司所有,未经许可不得翻 印、修改或引用! METTLER TOLEDO 为梅特勒-托利多公司的注册商标!

警告

1、请专业人员调试、检测和维修系统。 2、请保持本设备良好接地。

注意

1、 严禁带电插拔。 2、 请先切断电源,再进行电气设备连接,检修。

2 操作.. .................................................................................................................5

2.1 面板布局 ................................................................................................................................ 5 2.2 状态与标识定义 .................................................................................................................... 5 2.3 常用功能键说明 .................................................................................................................... 6 2.4 基本操作 ................................................................................................................................ 8 2.5 快速配置控制系统 .............................................................................................................. 10

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。