EDA模板

EDA复习资料

1.VHDL最基本的结构是什么?其作用各是什么?库(LIBRARY)声明:列出了当前设计中需要用到的所有库文件,如ieee,std和work 等。

实体(ENTITY):定义了电路的输入/输出引脚。

构造体(ARCHITECTURE):所包含的代码描述了电路要实现的功能。

2.in、inout 、buffer有何异同?IN 含义:输入INOUT 含义:说明该端口是双向的,可以输出也可以输入BUFFER 含义:说明该端口可以输出信号且在构造体内部可以使用该输出信号。

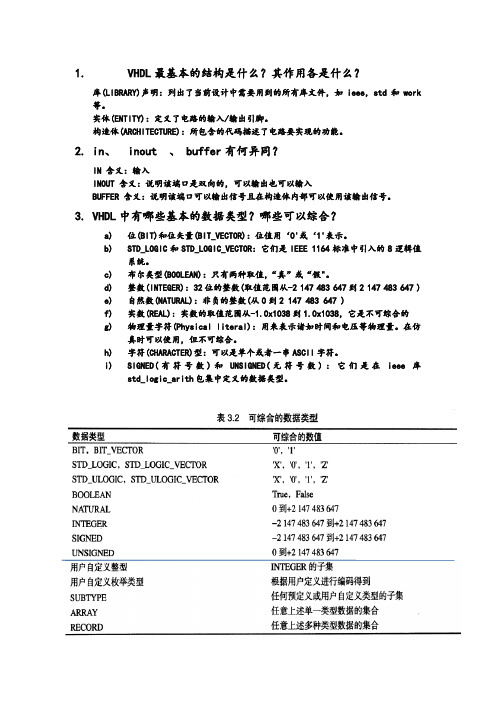

3.VHDL中有哪些基本的数据类型?哪些可以综合?a)位(BIT)和位矢量(BIT_VECTOR):位值用‘0'或‘1'表示。

b)STD_LOGIC和STD_LOGIC_VECTOR:它们是IEEE 1164标准中引入的8逻辑值系统。

c)布尔类型(BOOLEAN):只有两种取值,“真”或“假"。

d)整数(INTEGER):32位的整数(取值范围从-2 147 483 647到2 147 483 647 )e)自然数(NATURAL):非负的整数(从0到2 147 483 647 )f)实数(REAL): 实数的取值范围从-1.0x1038到1.0x1038,它是不可综合的g)物理量字符(Physical literal):用来表示诸如时间和电压等物理量。

在仿真时可以使用,但不可综合。

h)字符(CHARACTER)型:可以是单个或者一串ASCIl字符。

i)SIGNED(有符号数)和UNSIGNED(无符号数):它们是在ieee库std_logic_arith包集中定义的数据类型。

4.包集中定义了哪些数据类型转换函数?它们的适用范围是什么?在ieee库的包集std_logic_arith中提供的数据类型转换函数:a.conv_integer(p):将数据类型为INTEGER,UNSIGNED,SIGNED,STD_ULOGIC或STD_LOGIC的操作数P转换成INTEGER类型。

标准D0KA模板在小浪底工程中的使用

标准D0KA模板在小浪底工程3#导流洞中闸室126区施工中的运用1 概述国际公开招标的黄河小浪底水利枢纽,是集防洪、发电、根治“黄患"、治理黄河为一体的综合性工程。

它位于河南省孟津县小浪底,是我国在建“水字1号,,工程,1994年开工,1997年10月28日实施截流,2000年1月首台机组发电。

导流洞施工是由中外联合公司(有三家外国公司)承包的,在工期严重滞后的情况下,由水电一、三、四、十四工程局联合组成0TFF(取英文第一个字母)联营体,分包3个导流泄洪洞的开挖和混凝土衬砌工程。

施工条件是塌方严重,要在20个月里追回11个月工期,确保1997年10月截流,在如此条件下,我局承担了3号导流洞施工。

3号导流洞全长1l00m,剩余开挖工程10.2万多m3,混凝土10万m3,钢筋制安8000多t.而在导流洞施工中控制工期是中闸室的施工,为了加快施工进度,增加施工面,将中闸室119和126区用环形格梁分开,这样119区、126区可以同时施工;126区(洞室)的混凝土衬砌由环形钢格梁做为支撑进行施工。

表1为126区的工程量。

2 中闸室126区施工特点(1)中闸室地板(119区)设计高程为140.40m,而126区环形钢梁的顶面高程164.45m,即126区第一层混凝土底高程。

126区最高高程为181.45m,所以126区施工最大高度为41.0m。

这样D0KA模板系统起吊安装就有很大的困难。

根据施工需要,第一、二、三、四层D0KA模板用桥吊安装,第五、六、七层D0KA模板由移动吊车拆装(采用KA-TO40t轮式加长臂吊车)。

(2)126区是在119区边墙没有施工前开始施工,126区垂直高度41m,施工交通非常困难,为此采用外方提供的组装式塔梯,解决人员施工交通问题,虽然施工交通得到解决,但塔梯占据中闸室有限的有效空间,给D0KA模板安装运输带来不可避免的困难。

这些困难将在施工中得到解决。

(3)126区边墙衬砌设计厚度2.0m,实际衬砌厚度平均2.3m;第1、2层衬砌高度为1.5m,其余为3.0m一层,第1、2层主要是考虑环形梁承载能力和设计需要。

eda 工具对整个集成电路产业的重要作用和意义

eda 工具对整个集成电路产业的重要作用和意义集成电路产业是现代信息社会的核心和基石,它广泛应用于手机、计算机、通信设备、家电以及各种智能设备中。

对于集成电路产业的发展和创新,EDA(Electronic Design Automation,电子设计自动化)工具起着至关重要的作用。

EDA工具是一种软件系统,它通过提供设计、仿真、验证和布局等功能,加速了集成电路设计的过程,提高了设计效率和可靠性。

下面将会详细探讨EDA工具在整个集成电路产业中的重要作用和意义。

首先,EDA工具可以加速集成电路设计的过程。

在传统的集成电路设计方式中,设计师需要手工绘制电路原理图和布局图,这个过程既繁琐又复杂。

而有了EDA工具,设计师可以利用其提供的功能快速绘制电路原理图,并且可以通过自动布局和布线功能得到高质量的布局图。

这样,设计师可以在短时间内完成设计,大大加快了产品研发的速度。

其次,EDA工具能够提高集成电路设计的可靠性。

在电路设计中,引入误差和不确定因素是难以避免的,而EDA工具通过提供仿真和验证功能,能够对设计进行全面的测试和验证。

设计师可以在EDA工具中搭建电路模型并进行仿真,评估电路的性能和可靠性。

如果设计存在问题,设计师可以通过仿真结果进行相应的修改和优化。

通过这种方式,EDA工具可以帮助设计师提前发现和解决潜在问题,降低产品研发过程中的风险。

此外,EDA工具还能够提供丰富的设计资源和库,帮助设计师实现创新。

随着集成电路的不断发展,设计复杂度不断提高,设计师面临的挑战也越来越多。

而EDA工具中的设计资源和库,包括电路元件、信号处理算法和设计模板等,可以帮助设计师快速实现设计想法,克服技术难题。

此外,EDA工具还可以提供智能优化功能,通过自动化算法和优化策略,帮助设计师优化电路性能和功耗。

这些功能和资源的提供,不仅能够降低设计的复杂度,还有助于激发创新思维,推动集成电路设计的发展。

此外,EDA工具在提高集成电路产业的竞争力方面发挥了重要的作用。

数字集成电路后端设计简历模板

数字集成电路后端设计简历模板随着数字电子产品的不断发展,数字集成电路后端设计工程师成为了电子行业中不可或缺的重要角色。

作为数字集成电路后端设计工程师,必须具备扎实的电子学和数字电路知识,熟练掌握EDA工具,具备良好的团队合作和沟通能力,能够针对项目需求进行电路设计和验证,为电子产品的研发提供技术支持。

下面是一个数字集成电路后端设计工程师的简历模板,希望能够为求职者提供参考。

一、个人信息尊称:XXX性别:男/女学历:本科/硕士/博士专业:电子信息工程/集成电路设计与集成系统毕业院校:XXX大学通信方式:手机/电流信箱二、教育背景1. 本科/硕士/博士就读学校:XXX大学2. 主修专业:电子信息工程/集成电路设计与集成系统3. 获得学位:本科学士/硕士研究生/博士研究生4. 在校经历:获得过国家奖学金/获得过优秀毕业生称号/担任过学生会干部三、项目经历1. 项目名称:数字集成电路后端设计项目描述:负责XXX芯片的后端设计与验证工作工作内容:使用EDA工具完成电路原理图绘制和版图设计,进行时序分析和功耗优化,参与验证测试和故障分析取得成果:成功实现XXX芯片的设计与验证,并投入生产使用2. 项目名称:数字信号处理芯片设计项目描述:参与XXX系列数字信号处理芯片的设计与优化工作内容:参与电路架构设计和功能模块拓展,完成时序闭环和时钟树设计,协助仿真验证和性能评估取得成果:提高了XXX系列芯片的性能和稳定性,获得了公司的技术创新奖四、技能专长1. 扎实掌握数字电路原理和逻辑设计基础知识2. 熟练使用Verilog/VHDL等HDL语言进行电路的RTL描述和综合3. 精通EDA工具,如Cadence/Mentor/Synopsys等,熟练使用Design Compiler等工具进行综合和布局布线4. 熟悉时序分析,功耗优化和故障分析等后端设计相关技术5. 具备良好的团队协作和沟通能力,能够与项目组成员高效配合,完成项目任务五、实习经历1. 公司名称:XXX科技有限公司实习岗位:数字集成电路后端设计工程师实习描述:参与XXX系列芯片的后端设计与验证工作,完成时序分析和布局布线优化实习成果:成功独立完成了一个芯片的布局设计,并取得了良好的性能指标2. 公司名称:XXX集成电路设计研究所实习岗位:数字电路设计工程师实习描述:参与数字信号处理芯片的电路设计和验证工作,完成功能模块的逻辑设计和仿真验证实习成果:熟练掌握了数字电路设计流程,为后续工作打下了坚实的基础六、获奖情况1. 获得XXX大学优秀毕业生称号2. 获得XXX科技有限公司年度优秀员工奖3. 获得XXX大学“三好学生”称号4. 参与完成XXX项目,获得公司技术创新奖七、自我评价本人作为一名数字集成电路后端设计工程师,具备扎实的数字电路和EDA工具应用能力,有丰富的项目经验和团队合作经历。

配置管理计划模板

配置管理计划模板一、引言。

配置管理是软件开发过程中至关重要的一环,它涉及到软件产品的版本控制、变更管理、发布管理等方面,对于保证软件产品的质量和稳定性具有重要作用。

本文档旨在为项目团队提供一个配置管理计划模板,以便在软件开发过程中规范和管理配置管理工作。

二、背景。

在软件开发过程中,随着项目规模的扩大和开发人员的增多,配置管理变得愈发重要。

良好的配置管理可以确保团队成员之间的协作顺畅,减少因配置错误导致的问题,提高软件开发的效率和质量。

三、配置管理目标。

1. 确保软件产品的版本控制,避免因为版本混乱导致的问题。

2. 管理软件产品的变更,确保变更的合理性和有效性。

3. 控制软件产品的发布,保证发布过程的规范和稳定。

四、配置管理计划。

1. 配置标识。

为软件产品的每个版本和变更进行唯一标识,以便进行管理和追溯。

2. 配置控制。

管理软件产品的变更,包括变更的提出、评审、批准和实施。

3. 配置审计。

对软件产品的配置进行定期审计,确保配置的合规性和完整性。

4. 配置发布。

控制软件产品的发布过程,包括发布计划的制定、发布包的准备和发布过程的监控。

五、配置管理工具。

在配置管理过程中,我们将使用以下工具进行支持:1. 版本控制工具,Git、SVN等。

2. 缺陷跟踪工具,JIRA、Redmine等。

3. 发布管理工具,Jenkins、Docker等。

六、配置管理流程。

1. 变更管理流程。

变更提出,团队成员可以通过指定渠道提出变更请求。

变更评审,由配置管理团队对变更进行评审,评估变更的合理性和影响。

变更批准,对通过评审的变更进行批准,确定变更实施的时间和方式。

变更实施,按照变更计划对变更进行实施,并记录变更的过程和结果。

2. 发布管理流程。

发布计划制定,根据项目进度和需求制定发布计划。

发布包准备,准备发布所需的软件包和文档。

发布过程监控,监控发布过程中的各项指标,确保发布的稳定性和质量。

七、配置管理责任。

1. 配置管理员,负责配置管理计划的执行和管理。

EDA(电子设计自动化)模板

EDA(电子设计自动化)模板项目名称:EDA(电子设计自动化)模板1. 项目简介:本项目是一个用于电子设计自动化的模板,旨在提供一个可靠、高效的电子设计自动化框架,以帮助电子工程师快速完成电路设计、仿真和验证工作。

2. 功能特点:- 电路设计:提供基本的电路元件库,支持通过拖拽方式构建电路图,并自动生成对应的电路连接。

- 电路仿真:集成常用的电路仿真工具,例如SPICE仿真,以验证电路的性能和功能。

- 电路布局与布线:提供丰富的布局和布线工具,支持生成PCB (印制电路板)的设计文件。

- 线束与信号完整性分析:集成线束设计与信号完整性分析工具,帮助工程师解决电路布线时可能遇到的问题。

- 可扩展性:支持自定义电路元件库、仿真模型和布局规则,以满足不同项目的需求。

3. 技术实现:- 前端框架:使用HTML、CSS和JavaScript实现界面的搭建和交互功能。

- 后端开发:使用Python或Java等编程语言构建后端逻辑,处理用户请求和数据存储。

- 数据库:使用MySQL或MongoDB等数据库管理电路设计的相关信息。

- 仿真工具集成:集成常用的电路仿真工具,例如PSPICE、LTspice等。

- 布局与布线工具:集成AutoCAD、Altium Designer等工具,实现电路布局和布线功能。

4. 使用步骤:1) 登录系统或注册新用户。

2) 创建项目并命名。

3) 在项目中添加电路元件,连接电路图。

4) 进行电路仿真,验证电路性能。

5) 根据仿真结果进行电路布局和布线。

6) 分析电路线束与信号完整性,解决布线中的问题。

7) 导出PCB设计文件或打印电路图。

5. 预期成果:本项目的目标是提供一个完整的电子设计自动化框架,简化电子工程师的设计流程,提高工作效率。

预期成果包括:- 一个稳定可靠的EDA模板,满足基本的电子设计需求。

- 提供可扩展性,允许用户根据具体项目需求进行定制。

- 提供详细的文档和示例,帮助用户快速上手使用和定制模板。

立创eda设计规则设置

立创eda设计规则设置立创EDA是一种电子设计自动化工具,为电子设计师提供了快速、高效的设计、验证和生产流程。

设计规则设置是立创EDA中的一个重要环节,它决定了设计的可行性、可靠性和制造的可行性。

本文将详细介绍立创EDA设计规则设置的一些基本概念和具体步骤。

设计规则是指在设计电路时,所需要遵循的一系列规定,以满足电路功能和性能要求,并确保电路在制造和生产中能够正常工作。

设计规则设置是指将这些规则应用于电路设计中的过程。

在立创EDA中,设计规则设置包括以下几个方面。

1.尺寸规则设置:包括物理布局的尺寸规则、器件形状与间距的规则等。

在设置尺寸规则时,需要注意电路板的实际制造限制,如最小线宽线距、最小孔径等。

合理设置尺寸规则可以保证电路设计的可行性和可靠性。

2.电性规则设置:包括信号传输线的设计、电源和接地的布局、阻抗匹配等电性特性方面的规则。

合理设置电性规则可以优化电路性能,并减少电磁干扰和信号损耗。

3.材料规则设置:包括板材选择、焊盘尺寸、焊盘间距、焊盘控制等材料特性方面的规则。

在设置材料规则时,需要考虑材料的可靠性和可获得性,以确保电路设计符合制造和生产的要求。

4.DRC(设计规则检查)设置:DRC是立创EDA中的一个功能模块,用于检查设计是否符合所设定的规则。

在进行DRC设置时,需要根据具体的设计要求和制造要求,选择相应的检查规则。

通过合理设置DRC规则,可以提高设计的准确性和可靠性。

5.ERC(电器规则检查)设置:ERC是立创EDA中的另一个功能模块,用于检查设计中的电气问题。

在进行ERC设置时,需要关注电路的连通性、电压和电流的正常传输等电气特性。

通过合理设置ERC规则,可以降低电路设计中出现的电气问题。

基于以上几个方面,下面是立创EDA设计规则设置的一般步骤。

第一步是确定设计要求和制造要求。

在进行设计规则设置之前,首先需要明确设计的目标和要求,如电路的功能、性能、可靠性要求等,以及制造的要求,如最小线宽线距、最小孔径等。

东北石油大学课程设计任务书模板

东北石油大学课程设计任务书课程EDA技术课程设计题目闹钟系统的设计专业姓名学号主要内容、基本要求、主要参考资料等主要内容:设计并制作一个带闹钟功能的24小时计时器。

它包括以下几个组成部分:1、显示屏, 由4 个七段数码管组成, 用于显示当前时间(时: 分)或设置的闹钟时间;2、数字键, 实现‘0’—‘9’的输入, 用于输入新的时间或新的闹钟时间;3、TIME(时间)键, 用于确定新的时间设置;4、ALARM(闹钟)键, 用于确定新的闹钟时间设置, 或显示已设置的闹钟时间;5、扬声器, 在当前时钟时间与闹钟时间相同时, 发出蜂鸣声基本要求:1、计时功能: 这是本计时器设计的基本功能, 每隔一分钟计时一次, 并在显示屏上显示当前时间。

2、闹钟功能: 如果当前时间与设置的闹钟时间相同, 则扬声器发出蜂鸣声。

3、设置新的计时器时间: 用户用数字键输入新的时间, 然后按"TIME"键确认。

在输入过程中, 输入数字在显示屏上从右到左依次显示。

例如, 用户要设置新的时间12: 34, 则按顺序输入”1”, ”2”, ”3”, ”4”, 与之对应, 显示屏上依次显示的信息为: ”1”, ”12”, ”123”, ”1234"。

如果用户在输入任意几个数字后较长时间内, 例如5 s, 没有按任何键, 则计时器恢复到正常的计时显示状态。

主要参考资料:[1] 潘松著.EDA技术实用教程(第二版). 北京: 科学出版社, .[2] 康华光主编.电子技术基础模拟部分. 北京: 高教出版社, .[3] 阎石主编.数字电子技术基础. 北京: 高教出版社, .完成期限 .3.20指导教师专业负责人3月16日东北石油大学课程设计任务书课程EDA技术课程设计题目交通灯控制器专业姓名学号主要内容、基本要求、主要参考资料等主要内容:设计一个交通信号灯控制器, 由一条主干道和一条支干道汇合成十字路口, 在每个入口处设置红、绿、黄三色信号灯, 红灯亮禁止通行, 绿灯亮允许通行, 黄灯亮则给行驶中的车辆有时间停在禁行线外。

EDA实验报告模板

EDA上机实验一

实

验

报

告

班级:电信科1002班

成员:王佳鹏、刘甲易、李启迪

一、实验目的:熟悉并了解软件QuartusII的应用

二、实验过程:

1、创建工程

(1)打开当前工程

(2)将设计文件加入到工程中

(3)选择目标期间

(4)选择综合器和仿真器

(5)结束设置

2、设计输入

(1)新建文本文件

(2)编辑文本文件

3、项目编译

(1)编译前的设置

(2)编译

(3)查看编译结果

4、仿真验证

(1)打开波形编译器

(2)输入信号节点

(3)编辑输入信号波形

(4)仿真参数设置

(5)观察仿真结果

三、实验程序:简单的与门设计

1、程序

2、波形

3、延时分析

4、电路图

四、实验结果

通过此次上机学习及操作,我们小组成员都能基本掌握QuartusII 的使用,达到了初期的实验目的,为以后的上机实验打上了良好的基础。

EDA cadance软件使用

ORCAD

对于引脚比较多的元件,可采用阵列放置的方式快速放置引脚;

第8页

新建多部件元件

一般IC的引脚为了便于识别,需要修改引脚编号;

ORCAD

第9页

新建多部件元件

在属性编辑窗口可对引脚名称等属性进行快速编辑

ORCAD

第10页

新建多部件元件

ORCAD

按快捷键Ctrl+N进入下一部件的绘制,绘制完成后按View——Package可 全局查看该元件;

第29页

输出gerber文件

点击Manufacture——Artwork,打开gerber设置窗口;

Allegro

第30页

检查电路上件资料

Allegro

1、打开从Orcad输出的BOM;将没带“@”的元件删掉(可将其排序后快 速删除);

2、把剩下的带“@”的元件位号复制到新建的文本文件,将文本文件后 续改为“.lst”;

EDA软件使用

第1页

目录

一、Orcad 1、建立元件库 (1)建立单部件元件 (2)建立多部件元件 (3)建立其他模型 2、绘制原理图 (1)设置绘图环境 (2)放置元件、走线 (3)常用操作 (4)查找对象 (5)自动编号 (6)输出BOM表

第2页

二、Allegro 1、查看图层 2、查找对象 3、常用工具栏 4、转换低版本 5、导出位号图 6、导出坐标图 7、自定义快捷键 8、输出gerber 9、检查电路上件资料

建立元件库

依次点击File——News——Library,即可建立库文件;

ORCAD

第3页

建立单部件元件

ORCAD

选中上图项目管理器中的库文件,点击New part,打开新建元器件窗口;

engineering optimization 模板

engineering optimization 模板the question and provide a detailed explanation. Please keep in mind that the optimal word count for this article will be between 3000-6000 words.Title: Engineering Optimization: Unleashing Efficiency and InnovationIntroduction (300 words)Engineering optimization plays a pivotal role in driving efficiency, innovation, and sustainability in various industries. By systematically defining and solving complex problems, engineers can optimize design parameters, achieve cost-effective solutions, and create groundbreaking products. In this article, we will delve into the world of engineering optimization, exploring its principles, methodologies, and its diverse applications across different domains.1. Understanding Engineering Optimization (500 words)1.1 Definition and Basic Concepts1.2 Objectives of Engineering Optimization1.3 The Importance of Engineering Optimization2. Optimization Algorithms (1000 words)2.1 Deterministic Algorithms2.1.1 Gradient-based Methods2.1.2 Direct Search Methods2.1.3 Evolutionary Algorithms2.2 Stochastic Algorithms2.2.1 Simulated Annealing2.2.2 Particle Swarm Optimization2.2.3 Genetic Algorithms2.3 Comparison of Optimization Algorithms3. Mathematical Modeling in Engineering Optimization (1000 words) 3.1 Problem Formulation3.2 Objective Function and Constraints3.3 Design Variables and Parameters3.4 Response Surface Modeling3.5 Sensitivity Analysis4. Applications of Engineering Optimization (1500 words)4.1 Mechanical Engineering4.1.1 Structural Optimization4.1.2 Material Selection4.2 Aerospace Engineering4.2.1 Wing Design Optimization4.2.2 Trajectory Optimization4.3 Civil Engineering4.3.1 Optimization in Structural Design4.3.2 Traffic Flow Optimization4.4 Electrical Engineering4.4.1 Power System Optimization4.4.2 Circuit Design Optimization4.5 Environmental Engineering4.5.1 Waste Management Optimization4.5.2 Renewable Energy System Optimization5. Challenges and Future Trends in Engineering Optimization (500 words) 5.1 Complex and Multi-Objective Optimization Problems5.2 Uncertainty and Robust Optimization5.3 Hybrid Optimization Techniques5.4 Evolutionary Computing and Artificial Intelligence5.5 Big Data and OptimizationConclusion (200 words)Engineering optimization is a powerful tool that empowers engineers to address and solve complex problems across diverse industries. Byleveraging optimization algorithms, mathematical modeling techniques, and advanced technologies, engineers can achieve efficient and sustainable solutions, reduce costs, and foster innovation. However, the field still faces challenges related to complex problem formulations, robustness, and the utilization of emerging technologies. The future of engineering optimization holds great promise as researchers and practitioners continue to push the boundaries and explore novel techniques to tackle real-world problems.Note: The word count of this template is approximately 3,800 words. Please feel free to add or remove content to meet the desired word count requirement.。

EDA 第3章 VHDL语言 3.3全加器的VHDL描述

3.3 全加器的VHDL描述

3.3.2 CASE语句

1. CASE语句

CASE <表达式> IS When <选择值或标识符> => <顺序语句>; ... ; <顺序语句> ; When <选择值或标识符> => <顺序语句>; ... ; <顺序语句> ; ...

WHEN OTHERS => <顺序语句>;

component元件名port端口名表endcomponent文件名33vhdl333例化语句在组件映射部分其中的端口名是在元件组件定义语句中的端口名表中已定义好的元件端口的名字或者说是顶层文件中待连接的各个元件本身的端口名

3.3 全加器的VHDL描述

目的:进一步学习VHDL的语法

重点:1、CASE语句的用法

3.3 全加器的VHDL描述

【例3-17】 LIBRARY IEEE ; --或门逻辑描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS PORT (a, b :IN STD_LOGIC; c : OUT STD_LOGIC ); END ENTITY or2a; ARCHITECTURE one OF or2a IS BEGIN c <= a OR b ; END ARCHITECTURE one ;

3.3 全加器的VHDL描述

3.3.1 半加器描述 –真值表描述方法

【例3-16】 LIBRARY IEEE; --半加器描述(2):真值表描述方法 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS PORT (a, b : IN STD_LOGIC; co, so : OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE fh1 OF h_adder is SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; --定义标准逻辑位矢量数据类型 BEGIN abc <= a & b ; --a相并b,即a与b并置操作 PROCESS(abc) BEGIN CASE abc IS --类似于真值表的CASE语句 WHEN "00" => so<='0'; co<='0' ; WHEN "01" => so<='1'; co<='0' ; WHEN "10" => so<='1'; co<='0' ; WHEN "11" => so<='0'; co<='1' ; WHEN OTHERS => NULL ; END CASE; END PROCESS; END ARCHITECTURE fh1 ;

北航EDA课件06_03_003

3.2 Verilog HDL基本结构

一、简单的Verilog HDL例子

[例3.2.1] 8位全加器

模块名(文件名)

端口定义 module adder8 ( cout,sum,a,b,cin ); output cout; // 输出端口声明 output [7:0] sum; input [7:0] a,b; // 输入端口声明 input cin; assign {cout,sum}=a+b+cin; 功能描述 endmodule

15

3.2 Verilog HDL基本结构 三、逻辑功能定义

在Verilog 模块中有3种方法可以描述电路的逻辑功能: (1)用assign 语句 连续赋值语句 assign x = ( b & ~c );

常用于描述 组合逻辑

(2)用元件例化(instantiate)

and myand3( f,a,b,c);

模块元件例化——顶层模块(trist1)调用由某子模块 (mytri)定义的实例元件(tri_inst)来实现某功能。

13

3.2 Verilog HDL基本结构

Verilog HDL程序是由模块构成的。每个模块嵌套在module和 endmodule声明语句中。模块是可以进行层次嵌套的。 每个Verilog HDL源文件中只准有一个顶层模块,其他为子模块。 每个模块要进行端口定义,并说明输入输出端口,然后对模块的 功能进行行为逻辑描述。

3.2 Verilog HDL基本结构

二、Verilog HDL模块的结构

Verilog的基本设计单元是“模块 (block) ‖ 。 Verilog 模块的结构由在module和endmodule关键词 之间的4个主要部分组成:

《集成电路模板》课件

通过将多个芯片垂直堆叠,实现更高 效、更高速的集成电路。

市场发展趋势

物联网和5G技术的推动

随着物联网和5G技术的普及,集成电路市场将迎来新的增长点。

人工智能和数据中心的需求

人工智能和数据中心的建设将进一步拉动集成电路市场的需求。

汽车电子的快速发展

随着汽车智能化程度的提高,汽车电子市场对集成电路的需求也在 不断增长。

集成电路定义

集成电路是将多个电子元件集成在一块衬底上,完成一定的电路或系统功能的微 型电子部件。

它采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布 线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个 管壳内,成为具有所需电路功能的微型结构。

集成电路发展历程

1993年

甚大规模集成电路 的出现。

集成电路应用领域

通信领域

如手机、电话、传真机、交换机等。

消费电子领域

如电视、音响、摄像机等。

计算机领域

如个人电脑、服务器、笔记本电脑等。

汽车电子领域

如发动机控制、安全气囊等。

集成电路应用领域

通信领域

如手机、电话、传真机、交换机等。

消费电子领域

如电视、音响、摄像机等。

将不同类型的芯片和器件集成在同一 封装内,实现更复杂、更高效的系统 级集成。

通过将多个芯片垂直堆叠,实现更高 效、更高速的集成电路。

技术发展趋势

摩尔定律的延续

随着制程工艺的不断进步,集成电路 上的晶体管数量持续增加,性能不断 提升。

3D集成技术的发展

异构集成

将不同类型的芯片和器件集成在同一 封装内,实现更复杂、更高效的系统 级集成。

测试技术

功能测试

软件授权问询函回复模板

软件授权问询函回复模板根据申报及回复材料:(1)发行人 EDA 软件授权业务包括永久授权和固定期限授权两类,两类业务中都存在合同约定验收条款的情形;(2)对于永久授权业务,发行人以合同/订单签订日与合同/订单约定的授权开始日孰晚时点确认收入,对于固定期限业务按授权期限直线法分摊确认收入。

请发行人说明:区分永久授权和固定期限授权业务,分析合同明确约定验收条款的情况下,收入确认不考虑验收条款的原因及是否符合《企业会计准则》要求,并模拟匡算按验收时点确认收入对报告期各期的影响。

请申报会计师对上述事项进行核查并发表明确意见。

回复:一、发行人说明(一)区分永久授权和固定期限授权业务,分析合同明确约定验收条款的情况下,收入确认不考虑验收条款的原因及是否符合《企业会计准则》要求,并模拟匡算按验收时点确认收入对报告期各期的影响1、区分永久授权和固定期限授权业务,分析合同明确约定验收条款的情况下,收入确认不考虑验收条款的原因及是否符合《企业会计准则》要求公司永久授权和固定期限授权软件产品销售业务,除授权期限和后续的质量保证服务内容存在不同外,两者所销售的软件产品的功能、特性和质量标准不存在差异。

永久授权软件产品销售,属于在某一时点履行的履约义务,公司以合同/订单签订日与合同/订单约定的授权开始日孰晚时点确认收入;固定期限授权软件产品销售,属于在某一时段履行的履约义务,公司以合同/订单签订日与合同/订单约定的授权开始日孰晚作为开始确认收入的时点,并于软件授权期限内按照直线法确认收入。

(1)公司 EDA 软件系经过国际领先客户多年验证的标准化产品,客户对其试用主要系基于相应产品是否适合自身需求,或尝试其不同功能模块的组合,应用于并支撑其集成电路设计和制造流程,并非对EDA 软件本身是否符合某种质量标准的判断公司EDA 软件经过国际领先客户多年验证,系标准化产品,客户无需再次对标准化软件产品本身是否符合行业标准进行技术测试和行业标准论证。

Cadence软件介绍【范本模板】

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面.下面主要介绍其产品线的范围.1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具.(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具(NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统.可以说,spw包括了matlab的很多功能,连demo都有点象.它是面向电子系统的模块化设计、仿真和实现的环境.它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备.在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境.它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一.包括仿真、库和分析扩展部分。

可以进行spw的定点分析行为级和rtl级的代码生成.C、Mutimedia多媒体(Multimedia Design Kit)它可以进行多媒体应用的设计,包括电视会议系统、数字电视等等以及任何种类的图象处理系统的设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 Multisim 2001基本操作应用(黑体小三)

盐 城 师 范 学 院

EDA 技术实验报告

物电 学院 09(5)班 姓名 XXX 学号 092234XX 实验日期 2011-3-18 课程名称 EDA 技术基础教程 实验名称:Multisim 2001基本操作应用 实验地点 逸夫楼428-430

实验内容(目的,要求、任务、过程、结果等) 实验目的 (仿宋四号)

1、学会设置设计界面;(宋体小四,前面空两格,段落行距为1.5倍行距)

2、学会创建电路、选取仪器、放置文本、处理标题;

3、熟悉电路仿真和分析的方法。

实验仪器

电脑一台(宋体小四,前面空两格,段落行距为1.5倍行距)

实验内容

(宋体小四,前面空两格,段落行距为1.5倍行距)

图1-1所示是一方波倍频器电路,其输入为方波信号、频率为1 kHz 、幅度为2.5V ,占空比为50%。

要求仿真测量输入和输出信号,并观察调整R2与输出信号占空比变化情况。

(图形要居中)

R1

2.2ohm R3

2.2ohm 50%

Key = a

1M_LIN

R2

C1

2.2nF

C3

2.2nF

C2

1.0nF

D1

1N4148

D3

1N4148

U1A

74HC04N

2

1

U1B

74HC04N

4

3

U1C

74HC04N

6

5

V 1

5V

126

6

10

9

8

2

图1-1 方波倍频器电路(宋体5号居中)

1. 创建电路

R1

2.2ohm R2

2.2ohm 50%

Key = a

1M_LI N

R3

C1

2.2nF

C2

2.2nF

C3

1.0nF A

B

T

G XSC1

D1

1N4148

D2

1N4148

U1A

74HC04N

2

1

U1B

74HC04N

4

3

U1C

74HC04N

6

5

5V

V CC V 1

5V

XFG 1

325

10

6

8

7

1

图1-15 方波倍频器仿真电路

2 电路仿真和分析 (1). 选择并启动瞬态分析

图1-16 瞬态分析设置对话框

2

图1-17 Output Variables页设置

实验结果

1.创建电路

(宋体小四,前面空两格,段落行距为1.5倍行距)

按照实验内容选取适当元器件创建如图1-1的电路

图1 设计图

2.启动仿真

按实验要求选择所需节点进行仿真,得出仿真电路图如下:

思考题

1.如何仿真模拟电子技术实验三?

(宋体小四,前面空两格,段落行距为1.5倍行距)

答:模拟电子技术实验三用Protel进行仿真。

实验小结

(宋体小四,前面空两格,段落行距为1.5倍行距)

此为实验报告模板,做实验报告时把红色说明文字去除,要求2-3页为实验原理部分,另外2-3页为自己完成部分(包括小结)。