采用TMS320C3x集成的汽车信号处理及音频系统

TMSVC系统的硬件设计

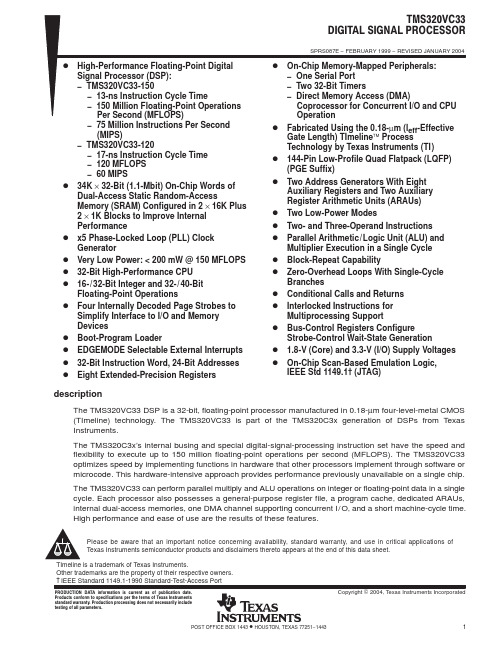

封面作者:Pan Hongliang仅供个人学习The Hardware Design of TMS320VC33 SystemAbstract:This paper introduces the hardware design method of the minimal system about TMS320VC33 which is the float DSP chip, according to its structure. It also introduces the circuits about Timing、Res et、JTAG Emulation and Memory Interfacing combining with practical application.Key words:Reset, Timing, JTAG Emulation, Boot.摘要:本文针对浮点DSP芯片TMS320VC33芯片的结构特点,介绍了该芯片最小系统硬件电路设计的方法,并结合实际应用情况,介绍了相关的时钟电路、复位电路、JTAG仿真接口电路、外围存储器接口电路以及Boot的设计。

关键词:复位,时钟,JTAG仿真,Boot。

引言TMS320C3X系列是隶属TMS320家族的一个低价位32位浮点DSP。

目前主要应用于数字化音频、视频会议、工控和机器人技术等方面,还可应用于电力系统在线监测方面。

其中VC33的最高处理速度为150 MFLOPS,其主要特点和组成有:(1)高品质的浮点DSP,指令周期为13ns\17ns,处理速度为150MFLOP S\120MFLOPS。

(2)低功耗(<200mw@150MFLOPS) (3)×5 PLL时钟发生器(4) 34K×32bit片内RAM (5) 32位指令字,24位地址线(6)支持Bootloader,一个串口,两个32位定时器和DMA。

DSP的160个经典问题

[原创]做DSP最应该懂得157个问题(回答)做DSP最应该懂得157个问题(回答)一.DSP系统设计100问一、时钟和电源问:DSP的电源设计和时钟设计应该特别注意哪些方面?外接晶振选用有源的好还是无源的好?答:时钟一般使用晶体,电源可用TI的配套电源。

外接晶振用无源的好。

问:TMS320LF2407的A/D转换精度保证措施。

答:参考电源和模拟电源要求干净。

问:系统调试时发现纹波太大,主要是哪方面的问题?答:如果是电源纹波大,加大电容滤波。

问:请问我用5V供电的有源晶振为DSP提供时钟,是否可以将其用两个电阻进行分压后再接到DSP的时钟输入端,这样做的话,时钟工作是否稳定?答:这样做不好,建议使用晶体。

问:一个多DSP电路板的时钟,如何选择比较好?DSP电路板的硬件设计和系统调试时的时序问题?答:建议使用时钟芯片,以保证同步。

硬件设计要根据DSP芯片的时序,选择外围芯片,根据时序设定等待和硬件逻辑。

二.干扰与板的布局问:器件布局应重点考虑哪些因素?例如在集中抄表系统中?答:可用TMS320VC5402,成本不是很高。

器件布局重点应是存贮器与DSP的接口。

问:在设计DSP的PCB板时应注意哪些问题?答:1.电源的布置;2.时钟的布置;3.电容的布置;4.终端电路;5.数字同模拟的布置。

问:请问DSP在与前向通道(比如说AD)接口的时候,布线过程中要注意哪些问题,以保证AD采样的稳定性?答:模拟地和数字地分开,但在一点接地。

问:DSP主板设计的一般步骤是什么?需要特别注意的问题有哪些?答:1.选择芯片;2.设计时序;3.设计PCB。

最重要的是时序和布线。

问:在硬件设计阶段如何消除信号干扰(包括模拟信号及高频信号)?应该从那些方面着手?答:1.模拟和数字分开;2.多层板;3.电容滤波。

问:在电路板的设计上,如何很好的解决静电干扰问题。

答:一般情况下,机壳接大地,即能满足要求。

特殊情况下,电源输入、数字量输入串接专用的防静电器件。

DSP应用技术-DSP及其应用概述

① C55xTM DSP内核可以为高达600 MIPS的性能提供300 MHz;

② 目前TMS320C5510 DSP已经开始投产,TMS320C5509 DSP 可提供样片;

③ 在整个C5000TM DSP平台上可实现软件兼容。

(2) 应用:功能丰富的便携产品,2G、2.5G、3G手机与基站, 数字音频播放器,数码相机,电子图书,语音识别,GPS接收器, 指纹/模式识别,无线调制解调器,耳机,生物辨识。

③ 高达7 MB的片上内存;

④ 两个多通道缓冲串行端口(McBSP)(三个用于C6202与 C6203 DSP的McBSP);

⑤ 16位主机端口接口(HPI)(32位用于C6202、C6203与C6204 DSP的扩展总线);

⑥ 两个32位定时器;

⑦ 300 MHz时速率高达2400 MIPS(C6203 DSP)。

(6) 具有软、硬件等待功能,能与各种存取速度的存储器接 口。

(7) 针对滤波、相关和矩阵运算等需要大量乘法累加运算的 特点,DSP芯片大多配有独立的乘法器和加法器,使得在同一 时钟周期内可以完成乘、累加两个运算。

(8) 低功耗,DSP一般为0.5~4 W,而采用低功耗技术的 DSP芯片只有0.1 W,可用电池供电。

(2) 特性:OMAP5910双内核处理器同时包括。 ① 150 MHz的TI增强ARM925微处理器: * 16 KB指令高速缓冲存储器以及8 KB数据缓冲器; * 数据与指令MMU; * 32位与16位指令集。

② 150 MHz TMS320C55xTM DSP内核: * 24 KB指令高速缓冲存储器; * 160 KB SRAM; * 用于视频算法的硬件加速器。

(3) 特性:高级自动电源管理;可配置的空闲域,以延长电 池寿命;缩短调制过程,从而加快产品上市进程。

DSP芯片型号,DSP芯片选型

DSP芯片型号,DSP芯片选型现在市面上的DSP产品很多,定点DSP有200多种,浮点DSP有100多种。

主要生产:TI 公司、AD公司、Lucent、Motorola和LSI Logic公司。

主导产品:TI 公司的TMS320C54xx(16bit 定点)、TMS320C55xx(16bit 定点)、TMS320C62xx(32bit 定点)、TMS320C67xx(16bit 浮点)、Motorola公司的DSP68000系列。

我们在DSP选型时需要注意什么?1、DSP芯片概述16bit定点DSP:最早以TMS320C10/C2X为代表,现在以TM320C2XX/C54XX为代表。

32 bit浮点DSP:代表产品ADSP21020、TMS320C3X通用DSP芯片的代表性产品包括TI公司的TMS320系列、AD公司ADSP21xx系列、MOTOROLA公司的DSP56xx系列和DSP96xx系列、AT&T公司的DSP16/16A 和DSP32/32C等单片器件。

TI的三大主力DSP产品系列为C2000系列主要用于数字控制系统;C5000(C54x、C55x)系列主要用于低功耗、便携的无线通信终端产品;C6000系列主要用于高性能复杂的通信系统。

C5000系列中的TMS320C54x系列DSP芯片被广泛应用于通信和个人消费电子领域。

在DSP系统的设计流程中,选择合适的器件非常重要,在确定了系统功能需求之后,通过先期的算法确定及性能模拟,我们要选择性价比最高的器件才能够为下一步开发提供便利。

DSP系统的设计流程图2,DSP芯片的选择方法一般而言,定点DSP芯片的价格较便宜,功耗较低,但运算精度稍低。

而浮点DSP芯片的优点是运算精度高,且C语言编程调试方便,但价格稍贵,功耗也较大。

例如TI 的TMS320C2XX/C54X系列属于定点DSP芯片,低功耗和低成本是其主要的特点。

而TMS320C3X/C4X/C67X属于浮点DSP芯片,运算精度高,用C语言编程方便,开发周期短,但同时其价格和功耗也相对较高。

做DSP最应该懂得157个问题(回答)

做DSP最应该懂得157个问题(回答)四.5V/3.3V如何混接?TIDSP的发展同集成电路的发展一样,新的DSP都是3.3V的,但目前还有许多外围电路是5V的,因此在DSP系统中,经常有5V和3.3V的DSP混接问题。

在这些系统中,应注意:1)DSP输出给5V的电路(如D/A),无需加任何缓冲电路,可以直接连接。

2)DSP输入5V的信号(如A/D),由于输入信号的电压>4V,超过了DSP的电源电压,DSP的外部信号没有保护电路,需要加缓冲,如74LVC245等,将5V信号变换成3.3V的信号。

3)仿真器的JTAG口的信号也必须为3.3V,否则有可能损坏DSP。

五.为什么要片内RAM大的DSP效率高?目前DSP发展的片内存储器RAM越来越大,要设计高效的DSP系统,就应该选择片内RAM较大的DSP。

片内RAM同片外存储器相比,有以下优点:1)片内RAM的速度较快,可以保证DSP无等待运行。

2)对于C2000/C3x/C5000系列,部分片内存储器可以在一个指令周期内访问两次,使得指令可以更加高效。

3)片内RAM运行稳定,不受外部的干扰影响,也不会干扰外部。

4)DSP片内多总线,在访问片内RAM时,不会影响其它总线的访问,效率较高。

六.为什么DSP从5V发展成3.3V?超大规模集成电路的发展从1um,发展到目前的0.1um,芯片的电源电压也随之降低,功耗也随之降低。

DSP也同样从5V发展到目前的3.3V,核心电压发展到1V。

目前主流的DSP 的外围均已发展为3.3V,5V的DSP的价格和功耗都价格,以逐渐被3.3V的DSP取代。

七如何选择DSP的电源芯片?TMS320LF24xx:TPS7333QD,5V变3.3V,最大500mA。

TMS320VC33: TPS73HD318PWP,5V变3.3V和1.8V,最大750mA。

TMS320VC54xx:TPS73HD318PWP,5V变3.3V和1.8V,最大750mA;TPS73HD301PWP,5V变3.3V和可调,最大750mA。

DSP小知识

我是已经从事DSP开发有几年了,看到许多朋友对DSP的开发非常感兴取,我结合这几年对DSP的开发写一写自己的感受,一家之言,欢迎指教。

我上研究生的第一天起根据老板的安排就开始接触DSP,那时DSP开发在国内高校刚刚开始,一台DSP开发器接近一万还是ISA总线的,我从206开始240、2407A都作过产品,对5402、2812、5471在产品方案规划制定和论证时也研究过。

由于方向所限对6X、8X系列没有接触。

我发现在国内无论在公司或高校许多地方为了加快开发周期往往把一个产品开发分为硬件和软件两个相对独立部分,由不同的人完成。

这在具有一定技术和管理基础的公司,由总设计师统一规划协调,分任务并行完成的情况下是可行的,也是符合现代产品开发规律的。

但是在高校人员的流动很大,研究生的有效科研时间很短、基础差(许多研究生起步时对电熔、电阻、三极管的分类和选型都很困难,我也是这样过来的)更不用说系统规划设计了,况且许多老板自己也不太懂,师兄有自己的任务,他们搞明白时也毕业了。

在许多高校做DSP就是找一个算法加到自己的主程序里,在板子上跑一下,基本达到效果就可以了,至于可靠性是次要的,产业化无从谈起,这已经算不错的了。

其实我觉得一个系统的完成,系统的规划是最重要的,在规划时对硬件设计的知识和认识是决定性的,它可以让你知道什么是可行的,什么是不可行的,当你同时具有软件设计能力时,就可以合理的分配系统功能,完成使用VHDL进行系统行为描述-—系统功能划分——系统子结构设计这样的自顶向下的设计规划流程,成为系统设计专家、项目经理,否则只是硬件工程师、软件工程师。

无论作51、196、还是DSP都是这样。

下面分别谈谈我对硬件和软件设计的感受硬件设计是系统设计的关键,国内和国外产品的差距往往是硬件设计水平高低决定的,任何软件设计思想没有可靠的物理载体都是空中楼阁,纸上谈兵。

学校的研究生很多都想避开硬件设计,对于一个全新的设计与其说不屑不如说不敢。

航盛维修手册统一版

www. hangsheng- sh. com

3.3.2.3 车内部半球摄像头................................................................28 3.3.2.3.1 车内部半球摄像头参数.....................................................28 3.3.2.3.2 车内部半球摄像头尺寸图.................................................28 3.3.2.3.3 车内部半球摄像头接口定义.............................................29 3.3.3 连接线参数 .............................................................................. 29 3.3.4 控制盒尺寸 .............................................................................. 29 3.3.5 系统连接总成图....................................................................... 29 3.4 故障排除指导 ..................................................................................... 30 3.5 注意事项 ............................................................................................ 30 影音类 ............................................................................................................... 31 4 高清播放器(固态存储).......................................................................... 31 4.1 功能描述 ............................................................................................. 31 4.2 系统组成 ............................................................................................. 31 4.2.1 产品图示 .................................................................................. 31 4.2.2 系统组成图 .............................................................................. 32 4.2.3 整机接线图 .............................................................................. 32 4.3 技术参数 ............................................................................................. 33 4.3.1 性能及技术参数....................................................................... 33 4.3.2 面板及定义 .............................................................................. 33 4.4 故障排除及维护指导.......................................................................... 34 4.4.1 故障排除 ................................................................................. 34 4.4.2 日常维护保养.......................................................................... 34 5 液晶显示器 ................................................................................................. 35 5.1 功能描述 ............................................................................................. 35 5.1.1 功能介绍:.............................................................................. 35 5.2 系统组成 ............................................................................................. 35

TMS320系列DSP芯片介绍

● 4.程序存储器寻址

● 使用程序计数器(PC)寻址,但是,对于一些指令需要用到绝对寻址。

● 5.中断

● 54X支持软件中断(如INTR,TRAP,RESET)和硬件中断,中断 可分为可屏蔽中断(如TINT,INT0等)和不可屏蔽中断(如 RESET和NMI),其中RESET的优先级最高,不可屏蔽中断的优 先级高于可屏蔽中断的优先级,硬件中断的优先级则高于软件中断 的优先级。

● 9.片上的外设

● 可软件编程的等待状态发生器,使得与速度较慢的设备通讯更加方 便;

● 片上的锁相环时钟发生器可以对外部时钟信号进行倍频或分频,从 而得到自己所需要的时钟频率,当分频时还可节省系统的功耗;

● 可以禁止对外部数据总线,地址总线以及控制信号的控制; ● 可以软件编程的定时器;

● 一些特殊的端口:标准的同步全双工串行口和时分复用(TDM)串 行口,自动缓冲串行口(auto-BSP),多通道缓冲串行口 (MCBSP),直接内存访问(DMA)控制器和与外部处理器通信 的HPI(Host Port Interface)接口。每一个型号的芯49.1标准的边界扫描逻辑 接口,即JTAG扫描逻辑电路,用于仿真和测试,可以实现在线仿真。

TMS320C54X的BOOT设计

● 由于直接将程序写入DSP芯片非常困难,所以TMS320C54X DSP 芯片都在片内设置有BOOT程序,它的主要作用是在开机时将用户 程序从外部装入到程序存储器。

。在一般形式的FIR滤波

器中,乘法是DSP的重要组成部分。在TMS320系列中,由于具有 专用的硬件乘法器,乘法可以在一个指令周期内完成。这样可以大 量降低FIR的计算时间。

特殊的DSP指令 ● 4.

。在TMS320系列中有一些特

DSP芯片的基本结构

DSP芯片的基本结构DSP芯片的基本结构包括:1.哈佛结构;2.流水线操作;3.专用的硬件乘法器;4.特殊的DSP指令;5.快速的指令周期。

哈佛结构哈佛结构的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

与两个存储器相对应的是系统中设置了程序总线和数据总线,从而使数据的吞吐率提高了一倍。

由于程序和存储器在两个分开的空间中,因此取指和执行能完全重叠。

流水线与哈佛结构相关,DSP芯片广泛采用流水线以减少指令执行的时间,从而增强了处理器的处理能力。

处理器可以并行处理二到四条指令,每条指令处于流水线的不同阶段。

CLLOUT1,取指N N-1 N-2,译码N-1 N N-2,执行N-2 N-1 N,专用的硬件乘法器,乘法速度越快,DSP处理器的性能越高。

由于具有专用的应用乘法器,乘法可在一个指令周期内完成。

特殊的DSP指令DSP芯片是采用特殊的指令。

快速的指令周期哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令再加上集成电路的优化设计可使DSP芯片的指令周期在200ns以下。

DSP芯片的选择方法一般而言,定点DSP芯片的价格较便宜,功耗较低,但运算精度稍低。

而浮点DSP芯片的优点是运算精度高,且C语言编程调试方便,但价格稍贵,功耗也较大。

例如TI的T MS320C2XX/C54X系列属于定点DSP芯片,低功耗和低成本是其主要的特点。

而TMS320C3X/C4X/C67X属于浮点DSP芯片,运算精度高,用C语言编程方便,开发周期短,但同时其价格和功耗也相对较高。

DSP应用系统的运算量是确定选用处理能力为多大的DSP芯片的基础。

运算量小则可以选用处理能力不是很强的DSP芯片,从而可以降低系统成本。

相反,运算量大的DSP系统则必须选用处理能力强的DSP芯片,如果DSP芯片的处理能力达不到系统要求,则必须用多个DSP芯片并行处理。

DSP选型和介绍

DSP简介DSP数字信号处理(DIGITAL Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

德州仪器、FREESCALE等半导体厂商在这一领域拥有很强的实力。

DSP的发展DSP的发展历史大致可以分成四个阶段:萌芽阶段、成长阶段、成熟阶段、突破阶段。

萌芽阶段:1982年以前在这段时期里为解决Von Neumann结构在进行数字信号处理时总线和存储器之间的瓶颈效应,许多公司投入大量人力和物力开展了很多探索性的工作,研制出了一些DSP的雏形,如AMI的S2811、INTEL的2920、AT&T的DSP-1和NEC的uPD7720。

但这些产品的运算速度都太慢,而且开发工具严重不足,无法进行大规模的开发工作,还不能称作真正意义上的DSP。

第一片DSP是1982年TI公司出品的TMS320C10,它是—个16位的定点DSP,采用了哈佛(Harvard)结构,有一个乘加器和一个累加器。

TMS320C10完成—次乘加操作需要390ns,即在一秒钟的时间内可以完成250万次左右的乘加运算。

或许正是因为生产出了第一个DSP,TI公司在此后的三十几年中一直是DSP界的领军人物。

成长阶段:1982-1987年这段时间内各公司相继研制出了自己的DDSP并不断地改进。

如1985年,TI推出了TMS320C20,它具备单指令循环的硬件支持,寻址空间达到64K字,有专门的地址寄存器,一次乘加运算只需耗时200ns。

1987年,MOTOROLA公司推山了DSP56001,采用24位的数据和指令,有专门的地址寄存器,可以循环寻址,累加器有保护位,一坎乘加运算只需耗时75ns。

TMS320C3X

【 关键 词 】 数字 信 号 处 理器

一

软件 模 拟器

有源 电力 滤 波器

( )模 拟外 设 , 速缓 存 及 流 水线 . 时 等功 能 ; 3 高 定

( )可 以设 置断 点 ; 4

Байду номын сангаас

、

引 言

数 字 信号 处 理 ( gtl in l oes g 芯 片 . Dii ga csi ) aS Pr n 由于 内部 采用 先进 的 总 线 结 构 和 单 周 期 的 乘 法 器 , 持 并 支 行 操 作 和 流水 线 操作 , 得 其 运 算 性 能 大 大 提 高 , 实 使 能 时快 速 进 行 各 种 数 字 信 号 处 理 算 法 . 此 在 很 多 领 域 因

拟 :用 户 利用 它 可 “模 拟 外 部 I O—I 3中 断 , NT NT 这

一

公 司 的第 三代 D P产 品 . 是 第 一 代 浮 点 D P 由 于 S 也 S。 其优 越 的浮 氟处 理 功 能 . 泛 地 应 用 于 实 时 数 字 信 号 广

处理 领 域 。 在用 DS P硬 件仿 真 系 统 进 行 软 件 开 发 时 , 须 得 必

合其 在 有源 电力 滤波 器 ( t eP 呵 F lr设 计 中的应 Ac v ∞ i ie) t

=

壶 噩酉二

[苗 墼 题

[ 窭 麴 [ j丑 蔓

<

用, 详细 介绍 了软件 模拟 器 的使 用方 法 及注 意 事项 :

二 、 MS 2 C X软 件 模 拟 器 简 介 T 30 3

这 样 . 了进 行 直 观 的 分 析 , 要 扩 展 A/ 为 需 D或 D/ 设 A 备 , 无疑 又增 加 了开 发 成 本 。 这

流水灯实践学习心得体会

流水灯实践学习心得体会-精品2020-12-12【关键字】方案、方法、进展、空间、领域、文件、运行、传统、问题、系统、有效、深入、继续、充分、平稳、快速、执行、统一、发展、加深、建立、提出、掌握、了解、研究、特点、突出、稳定、成果、基础、需要、环境、工程、资源、能力、方式、特色、作用、标准、规模、结构、任务、速度、设置、增强、分析、调控、形成、整合、管理、强化、支持、发挥、解决、优化、完善、取决于、方向、适应、实现、提高、改进、专业化、重要性篇一:对LED流水灯的学习总结单片机的学习总结第一个实验:一、从点亮一个发光二极管到实现流水灯的操作实验报告实验目的:(1)知道单片机最小系统和典型系统(2)知道如何建立一个工程,完成一个点亮发光二极管的编译和烧写实验器件以及基础知识描述:(1)LED发光二极管是一种半导体二极管,可以把电能转换成光能,有一个PN结构成。

(2)晶振:全称为晶体振荡器,其作用是产生原始的时钟频率,这个频率晶振经过频率发生器的放大或缩小后就成为了电脑中各种不同的总线频率。

(3)IO端口的驱动能力:每个I/O端口允许的做大20mA 的灌电流,可以直接驱动LED和继电器;高电平输出时一般对负载提供电流其提供的电流叫“拉电流”;低电平输出时一般是要吸收负载的电流,其吸收的电流叫“灌电流”。

(4)P1.0---P1.7:准双向接口(内置上拉电阻),端口P1的数据寄存器用P1表示,端口置一表示高电平,设置为0表示输出低电平。

(5)如何进行程序烧写:5.1、用传统的并行烧写器5.2采用目前流行的IAP在线下载程序,STC的单片机可以不要编程器,通过USB或串口下载程序(6)延时函数:每条指令都占有一定的时间,如果让机器什么都不干机器就会延时,外加循环此数一个完整的点亮LED源代码程序如下:#includeSbit LED=P1^0;void main(){LED=1;LED=0;While(1)}有这一个简单的程序实现使p1^0端口控制的LED灯点亮,如果要实现多个灯同时点亮呢?可以定义多个端口,使之输出低电平即可://实现第1、3、5、7个LED灯点亮#includesbit LED0=P1^0;sbit LED2=P1^2;sbit LED4=P1^4;sbit LED6=P1^6;main(void){LED0=0;LED2=0;LED4=0;LED6=0;while(1){}}实现了控制灯亮暗后,程序中添加一段延时程序即可实现灯的闪烁:延时函数分为有参延时和无参延时;//一个简单的有参延时函数:void delay(unsigned int t){While(--t);}//无参延时函数:void delay(){for(int i=1000;i>0;i++)for(int j=1000;j>0;j++);}或者: void delay(){Unsigned int i=300;While(--i);}通过进一步的分析可以进行流水灯的设计:设计目的:从实际工程出发,在理论和实践上掌握流水灯系统的基础组成,工作原理。

TMS320C3x DSP

分 类号 :P 6 T 8 文献标识 码 : A 文章 编号 :0 6 97 20 )4一 !2 —0 10 —67 (0 20 ( 3 3 O

D P芯 片的开 发包 括 硬件开 发 和软件 开发 两个 s 方面, 就软 件开 发而 言 , 用汇 编语言 编写 程序是 一件

导 功能 (otae) Boodr,从 而 使 其程 序 可 以从低 速 B l

比较 繁琐 的事 情 ,因为不 同类型 芯片 的汇 编语言有

所 不 同.其可 读性 和可移植 性较差 且需较 长 的开发 周期 , 而一旦 开发完毕 , 要再 对其修 改 和升级将 非常 困难 。用 c语 言开 发 D P程 序将使 其开 发速度 大大 S

加 快 , 且可 读性 和可移植 性都大 大增加 , 序修改 而 程 也极为方 便 但 在某些 情况 下 , c代码 的效率还 是无 法 与手工 编写 的汇 编代码 的效率 相 比 ,如 F 程序 n’ 等, 而且一 些硬 件控 制功能 也不 如汇 编语言方 便 , 而

维普资讯

2一 4

《 国外 电子元器 ̄)02 t2e 年第 4 期

2O 年 4月 02

编程序 也可以调用 c函数或 访问 c程 序中定义 的变 量 。以下是互相访 问变 量的编程实例。 例 h c程序中访问 . s 在 b 定义 的汇编程序变量: s

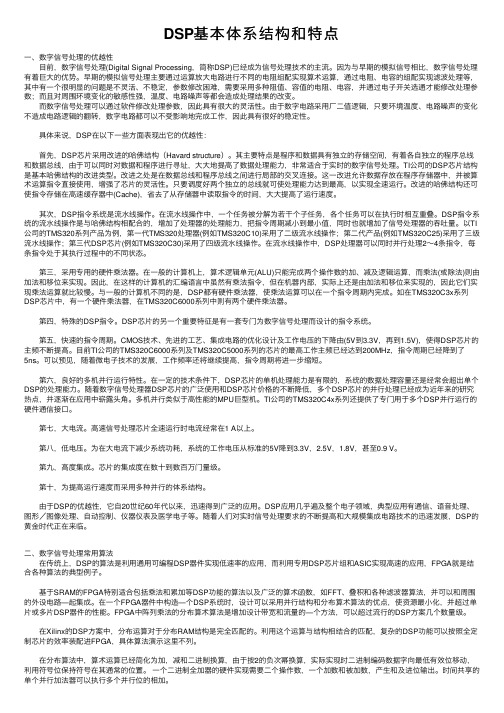

DSP基本体系结构和特点

DSP基本体系结构和特点⼀、数字信号处理的优越性 ⽬前,数字信号处理(Digital Signal Processing,简称DSP)已经成为信号处理技术的主流。

因为与早期的模拟信号相⽐,数字信号处理有着巨⼤的优势。

早期的模拟信号处理主要通过运算放⼤电路进⾏不同的电阻组配实现算术运算,通过电阻、电容的组配实现滤波处理等,其中有⼀个很明显的问题是不灵活、不稳定,参数修改困难,需要采⽤多种阻值、容值的电阻、电容,并通过电⼦开关选通才能修改处理参数;⽽且对周围环境变化的敏感性强,温度、电路噪声等都会造成处理结果的改变。

⽽数字信号处理可以通过软件修改处理参数,因此具有很⼤的灵活性。

由于数字电路采⽤⼚⼆值逻辑,只要环境温度、电路噪声的变化不造成电路逻辑的翻转,数字电路都可以不受影响地完成⼯作,因此具有很好的稳定性。

具体来说,DSP在以下⼀些⽅⾯表现出它的优越性: ⾸先,DSP芯⽚采⽤改进的哈佛结构(Havard structure)。

其主要特点是程序和数据具有独⽴的存储空间,有着各⾃独⽴的程序总线和数据总线,由于可以同时对数据和程序进⾏寻址,⼤⼤地提⾼了数据处理能⼒,⾮常适合于实时的数字信号处理。

TI公司的DSP芯⽚结构是基本哈佛结构的改进类型。

改进之处是在数据总线和程序总线之间进⾏局部的交叉连接。

这⼀改进允许数据存放在程序存储器中,并被算术运算指令直接使⽤,增强了芯⽚的灵活性。

只要调度好两个独⽴的总线就可使处理能⼒达到最⾼,以实现全速运⾏。

改进的哈佛结构还可使指令存储在⾼速缓存器中(Cache),省去了从存储器中读取指令的时间,⼤⼤提⾼了运⾏速度。

其次,DSP指令系统是流⽔线操作。

在流⽔线操作中,⼀个任务被分解为若⼲个⼦任务,各个任务可以在执⾏时相互重叠。

DSP指令系统的流⽔线操作是与哈佛结构相配合的,增加了处理器的处理能⼒,把指令周期减⼩到最⼩值,同时也就增加了信号处理器的吞吐量。

以TI 公司的TMS320系列产品为例,第⼀代TMS320处理器(例如TMS320C10)采⽤了⼆级流⽔线操作;第⼆代产品(例如TMS320C25)采⽤了三级流⽔线操作;第三代DSP芯⽚(例如TMS320C30)采⽤了四级流⽔线操作。

航盛维修手册统一版

上海航盛实业有限公司售后服务部

上海航盛维修指导手册

所有权声明

该文档及其所含信息是 HSAE(上海航盛实业有限公司)的财产。该文档及其所含信息的复制、使用及披露必须 得到 HSAE(上海航盛实业有限公司)的书面授权。

www. hangsheng- sh. com

售后服务部 赵强

2013-10-18

上海航盛实业有限公司售后服务部

故障录波装置原理详细介绍

变电站故障录波装置的设计及介绍曲春辉,张新国,焦彦军(华北电力大学,河北保定071003)摘要:电力系统的发展对变电站故障录波装置提出了更高的要求,计算机软硬件技术的飞速发展,全球定位系统(GPS)、以太网络、数字信号处理器(DSP)、嵌入式计算机等硬件技术及面向对象编程(OOP)的软件技术,为微机型故障录波装置的性能改善提供了必要条件。

本文介绍了一种基于当前先进的计算机技术的高性能的变电站故障录波装置的设计方案,较详细地分析说明了其软硬件结构和功能。

关键词:变电站故障录波GPS 以太网PC/1040引言随着电力网络的扩大复杂化和区域互联趋势的到来,电力系统的行为也将越来越复杂。

一些原有的假设条件和简化模型的适用性都将接受进一步的挑战与检验。

在此情况下丰富详尽的现场实测数据,尤其是故障或非正常状态下的数据,无疑将具有越来越重要的价值。

它们不仅是分析故障原因检验继电保护动作行为的依据,也为电力工作者研究了解复杂系统的真实行为,发现其规律提供宝贵的资料,因此故障录波装置作为电力系统暂态过程的记录设备,电力系统对其要求也越来越高了,计算机技术的不断突飞猛进,为微机型故障录波装置进一步扩大信息量,提高可靠性、准确性、灵活性、实时性以及共享信息资源提供了必要的有利条件。

本文提出了一种利用当前先进的计算机技术实现微机型故障录波装置的方案,以提高故障录波装置的性能,使之更好地适应电力系统发展的需要。

1故障录波器的整体结构该系统以网络为核心,把各个单元连接成为一个有机整体,作为一个分布式的系统,它采用多CPU并行工作方式构成。

主要可以分为三大部分:下位机单元、中层通讯管理单元、上位机单元。

下层采集卡相互独立,中层管理单元负责与上位机的通讯及保存掉电后可能丢失的数据,上位机负责人机接口及与其他系统通过网络通信。

结构如图1所示。

1.1下位机单元(数据采集系统)数据采集系统,包括开关量采集系统和模拟量采集系统。

装置中可插入开关量采集板4块,模拟量采集板6块,每块开关量采集板可监测32路开关量,每块模拟量采集板可监测16路模拟量。

TI公司DSP系列概述解析

下一步可能的应用 ...

互联网相关: 智能电冰箱等

高速, 高密度磁盘驱动 数字视频

Internet 服务器

高精度的加工工艺

高效的 电动汽车

C2000系列DSP

子系列

C2xx子系列:16位定点DSP、20MIPS

➢代表器件:TMS320F206PZ C24x子系列:16位定点DSP、20MIPS

Memory Sub-System

Fast program execution out of both RAM and Flash memory

▪ 110-120 MIPS with Flash Acceleration Technology ▪ 150 MIPS out of RAM for time-critical code CCoonnttrrooll PPoerrtispherals

C6000™ DSP

Personal DSP

TI C55x™ DSP 核心: 世界上最低功耗性能比

mW/MIPS的DSPs

• 以达到0.05mW/MIPs的最低

功耗性能比而具有最长的电池 寿命。

• 最佳的代码密度 • 兼容C54x™ DSP软件

Broadband Infrastructure DSP

MIPS MEMORY

Flash ROM RAM Boot ROM EVENT MGR GP Timers CMP/PWM CAP/QEP 10-BIT ADC Channels Conv. Time COMMS SCI (UART) SPI CAN

GPIO

WATCHDOG

EMIF

VOLTAGE

PACKAGING

PRODUCTION Yr 2000 10Ku Pricing

TMS320VC33DSP芯片说明书

D On-Chip Memory-Mapped Peripherals:

− One Serial Port − Two 32-Bit Timers − Direct Memory Access (DMA) Coprocessor for Concurrent I/O and CPU Operation Fabricated Using the 0.18-µm (leff-Effective Gate Length) TImeline Process Technology by Texas Instruments (TI ) 144-Pin Low-Profile Quad Flatpack (LQFP) (PGE Suffix) Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs) Two Low-Power Modes Two- and Three-Operand Instructions Parallel Arithmetic / Logic Unit (ALU) and Multiplier Execution in a Single Cycle Block-Repeat Capability Zero-Overhead Loops With Single-Cycle Branches Conditional Calls and Returns Interlocked Instructions for Multiprocessing Support Bus-Control Registers Configure Strobe-Control Wait-State Generation 1.8-V (Core) and 3.3-V (I/O) Supply Voltages On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1† (JTAG)

《广州市车联网先导区建设总体技术规范》

B.1 一般要求 ................................................................................................. 57 B.2 功能及性能要求.................................................................................... 57 参考文献 ......................................................................................................... 62

4

3GPP TS 36.306(Release 14) 演进通用陆地无线接入系统:用 户 设 备 射 频 接 入 能 力 (Evolved Universal Terrestrial Radio Access (E-UTRA); User Equipment (UE) radio access capabilities)

II

广州市车联网先导区建设总体技术规范

1 范围 本文件主要规定了广州市车联网先导区的整体目标、技术架构、

建设内容及其技术要求等。 本文件共分7章,分别为总则、规范性引用文件、术语及定义、

缩略语、总体要求、基础设施建设技术要求、应用场景建设技术要求 等。

本文件适用于广州市车联网先导区建设,其它地区可参照执行。 2 规范性引用文件

下列术语和定义适用于本文件。 3.1 区域子系统 regional subsystem

区域子系统是特定区域的路侧协同设施的数据汇聚点,提供交 通预测、交通监管、安全预警、以及域内车辆管理等服务。 3.2 中心子系统 central subsystem

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Copyright © 1997, Texas Instruments Incorporated

Contents

ABSTRACT............................................................................................................................ 1 INTRODUCTION .................................................................................................................. 2 HARDWARE DESCRIPTION ............................................................................................... 5 SOFTWARE DESCRIPTION ................................................................................................ 7 Hands-Free Cellular Phone Mode...................................................................................... 7 Adaptive-Active Noise Control Mode ................................................................................. 9 EXPERIMENTAL SETUP AND RESULTS........................................................................ 11 Hands-Free Cellular Phone Mode.................................................................................... 11 Adaptive-Active Noise Control Mode ............................................................................... 12 SUMMARY .......................................................................................................................... 23 REFERENCES .................................................................................................................... 24 APPENDIX A-----Flow Charts for System Software............................................................. 25 APPENDIX B-----INTSYS.ASM Program............................................................................. 29

Literature Number: SPRA095 March 1997

Printed on RecFra bibliotekcled Paper

IMPORTANT NOTICE Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current. TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements. Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage (“Critical Applications”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office. In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Integrated Automotive Signal Processing and Audio System Using the TMS320C3x

Uday Gupta, Micheal Bychowsky, and Dr. Sen M. Kuo Department of Electrical Engineering Northern Illinois University Dekalb, IL 60115