L9925;中文规格书,Datasheet资料

R12I05资料

Electrical Specifications (measured at TA = 25°C, at nominal input voltage and rated output current unless otherwise specified)

Input Voltage Range VIN (continuous operation) Reflected Ripple Current (depending on the type) Voltage Set Point Accuracy Line Regulation (high VIN to low VIN) Load regulation (depending on the type) Ripple and Noise (BW=DC to 20MHz) (depending on the type) Isolation Voltage (flash tested for 1 second) Test Voltage (50Hz, 10 seconds) Resistance (Viso = 500V) Switching Frequency Package Weight Storage Temperature Range Operating Temperature Range (all output types) Case Temperature Above Ambient (depending on the type) MTTF 1) (depending on the type) –40°C +25°C +85°C SIP types 5V types 12V types 4.5VDC min. / 5.5VDC max. 10.8VDC min. / 13.2VDC max. 23 mA p-p min. to 38 mA p-p max. see Tolerance Envelope 1.0% min. / 1.2% max. of VIN 3.7% min. / 8.5% max. 45mVp-p min. / 200mVp-p max. 1000VDC min. 1000 Vpk min. 10 GΩ min. 90kHz typ. 2.0 g –50°C to +130°C –40°C min. to +85°C max. (see graph) +36°C min. / +45°C max. 417kHrs min. / 3970kHrs max. 328kHrs min. / 2327kHrs max. 222kHrs min. / 934kHrs max.

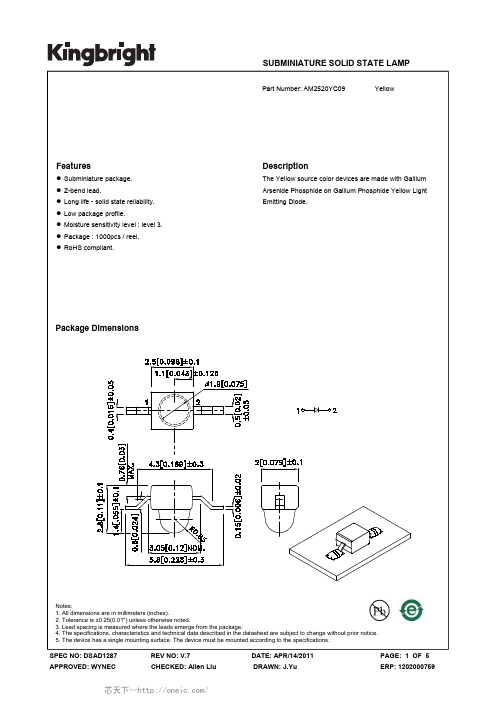

AM2520YC09, 规格书,Datasheet 资料

Part Number: AM2520YC09 Yellow

Features

Subminiature package. Z-bend lead. Long life - solid state reliability. Low package profile. Moisture sensitivity level : level 3. Package : 1000pcs / reel. RoHS compliant.

REV NO: V.7 CHECKED: Allen Liu

DATE: APR/14/2011 DRAWN: J.Yu

PAGE: 5 OF 5 ERP: 1202000759

芯天下--/

Part No. Dice Lens Type Iv (mcd) [2] @ 20mA Min. AM2520YC09 Yellow (GaAsP/GaP) Water Clear 20 Typ. 50 Viewing Angle [1] 2θ1/2 20°

Notes: 1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 of the optical peak value. 2. Luminous intensity/ luminous Flux: +/-15%.

Notes: 1.Wavelength: +/-1nm. 2. Forward Voltage: +/-0.1V.

Absolute Maximum Ratings at TA=25°C

Parameter Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating Temperature Storage Temperature

FGA25N120FTD;中文规格书,Datasheet资料

@ TC = 25oC @ TC = 100oC

Diode continuous Forward current Maximum Power Dissipation Maximum Power Dissipation Operating Junction Temperature

@ TC = 100oC @ TC = 25oC @ TC = 100oC

Symbol

Parameter

Test Conditions

VFM

Diode Forward Voltage

IF = 25A

TC = 25oC TC = 125oC

trr

Diode Reverse Recovery Time

TC = 25oC TC = 125oC

Irr

Diode Reverse Recovery Time

©2009 Fairchild Semiconductor Corporation

1

FGA25N120FTD Rev. A1

G

E

Ratings

1200 ± 25 50 25 75 25 313 125 -55 to +150 -55 to +150 300

Units

V V A A A A W W oC oC

Applications

• Induction heating and Microvewave oven • Soft switching applications

February 2009

tm

General Description

Using advanced field stop trench technology, Fairchild’s 1200V trench IGBTs offer superior conduction and switching performances, and easy parallel operation with exceptional avalanche ruggedness. This device is designed for soft switching applications.

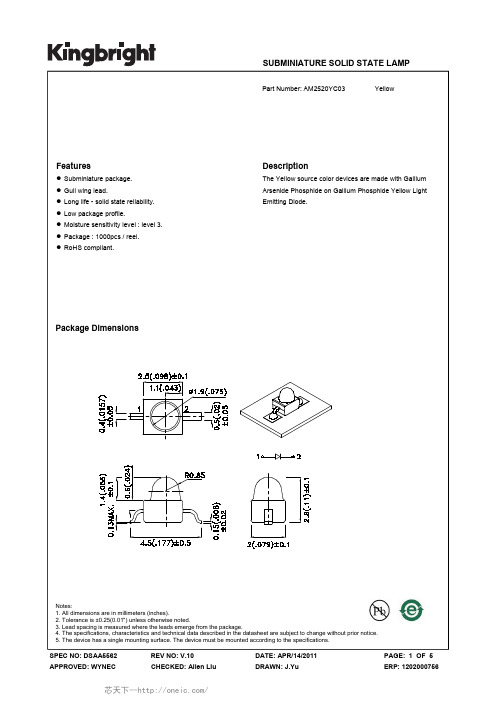

AM2520YC03, 规格书,Datasheet 资料

SPEC NO: DSAA5562 APPROVED: WYNEC

REV NO: V.10 CHECKED: Allen Liu

DATE: APR/14/2011 DRAWN: J.Yu

PAGE: 1 OF 5 ERP: 1202000756

芯天下--/

Selection Guide

Part No. Dice Lens Type Iv (mcd) [2] @ 20mA Min. AM2520YC03 Yellow (GaAsP/GaP) Water Clear 20 Typ. 50 Viewing Angle [1] 2θ1/2 20°

Notes: 1. θ1/2 is the angle from optical centerline where the luminous intensity is 1/2 of the optical peak value. 2. Luminous intensity/ luminous Flux: +/-15%.

Note: 1. 1/10 Duty Cycle, 0.1ms Pulse Width.

Yellow 75 30 140 5 -40°C To +85°C -40°C To +85°C

Units mW mA mA V

SPEC NO: DSAA5562 APPROVED: WYNEC

REV NO: V.10 CHECKED: Allen Liu

Notes: 1.Wavelength: +/-1nm. 2. Forward Voltage: +/-0.1V.

Absolute Maximum Ratings at TA=25°C

Parameter Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating Temperature Storage Temperature

RER125-1912NG;中文规格书,Datasheet资料

Nominal data

Type RER 125-19/12 NG VDC VDC min-1 W °C °C m3/h B 12 7 .. 15 2650 5 -30 75 110 5.7

Nominal voltage Nominal voltage range Speed Power input Min. ambient temperature Max. ambient temperature Air flow Sound power level

RER 125-19/12 NG

DC centrifugal compact fan

single inlet

ebm-papst St. Georgen GmbH & Co. KG Hermann-Papst-Straße 1 D-78112 St. Georgen Phone +49 7724 81-0 Fax +49 7724 81-1309 info2@

0 10 20 30 40 50 60 CFM m³/h

VS

•

20

40

60

80

100

Web data sheet XI · Page 4 of 4 ebm-papst St. Georgen GmbH & Co. KG · Hermann-Papst-Straße 1 · D-78112 St. Georgen · Phone +49 7724 81-0 · Fax +49 7724 81-1309 · info2@ ·

/

RER 125-19/12 NG

DC centrifugal compact fan

single inlet

19665;中文规格书,Datasheet资料

Dual-Wire Dual-Operator Programmable Monitor DescriptionThe patented* Desco Dual-Wire Dual-OperatorProgrammable Monitor monitors two operators and two ESD work worksurfaces eliminating the need for periodic Figure 1. Desco 19665 Dual-Wire Dual-Operator Programmable MonitorFeatures and ComponentsTECHNICAL BULLETIN TB-3019Made in theUnited States of AmericaFigure 2. Dual-Wire Dual-Operator Programmable CBDE FG H I J K LFRONT VIEWBACK VIEWOperation1. Monitoring of the operators will remain in the STANDBY condition until a wrist cord is plugged into the operator remote. STANDBY mode is indicated by a blinking yellow operator LED.10mm snap needs to pierce and clinch bottom side of mat. Snap needs to be at least 12" apart or 72" max. 10mm snap needs to pierce and clinch bottom side of mat. Snap needs to be at least 12" apart or 72" max.OPERATOR 1WORKSURFACEOPERATOR 2WORKSURFACE10mm PUSH & CLINCH SNAP10mm PUSH & CLINCH SNAPBENCH GROUNDMAT 1 WIRING WHITE CABLEMAT 2 WIRING BLACK CABLEWRIST STRAP MONITORWRIST STRAP MONITORELECTRIC GROUNDOPERATOR 2REMOTE JACK BLACK CABLEOPERATOR 2REMOTE JACK WHITE CABLE Screw allows ground cord to be bolted to mat; keeps cord from disconnecting.Figure 3. Installing the Dual-Wire Dual-Operator Programmable MonitorororFigure 4. Connecting a dual-wire wrist strap to the operator remoteSETTING THE OPERATOR TEST VOLTAGE AND TEST LIMITThe Dual-Wire Dual-Operator Monitor’s operator test voltage and high test limit can be set to different values. The operator test voltage can be set to either +5V or +8V, and the operator high test limit can be set to either 10 megohms or 35 megohms. The default voltage is +8V, and the default operator high test limit is 10 megohms. These settings are controlled by a set of 3 switches located inside the monitor’s enclosure.NOTE: Desco recommends re-calibration of the monitor should either setting be changed. See the “Calibration” section for more information.To gain access to these switches, remove the monitor’s cover and position the monitor so the PCB matches the orientation shown in Figure 5. Switches SW1 and SW2 control the operator test voltage. Switch SW3 controls the operator high test limit.Operator Test Voltage+5VSW1 Position: RIGHTSW2 Position: LEFT+8VSW1 Position: LEFTSW2 Position: RIGHTOperator High Test Limit10 megohmsSW3 Position: RIGHT35 megohmsSW3 Position: LEFTCalibrationFrequency of recalibration should be based on the critical nature of those ESD sensitive items handled and the risk of failure for the ESD protective equipment and materials. In general, Desco recommends that calibration be performed annually.Use the EMIT 50524 Limit Comparator for Dual-Wire Monitors to perform periodic testing (once every 6-12 months) of the Dual-Wire Dual-Operator Programmable Monitor. The Limit Comparator can be used on the shop floor within a few minutes virtually eliminating downtime, verifying that the monitor is operating within tolerances. See TB-6542 for more information.Figure 5. Switches SW1, SW2 and SW3 inside the monitor’s enclosure Figure 6. EMIT 50524 Limit Comparator for Dual-Wire MonitorsNIST CalibrationDesco provides a basic, National Institute of Standardsand Technology (NIST) traceable calibration for theproducts that we manufacture. This is sometimesreferred to as a Level 1 calibration.For more on National Institute of Standards andTechnology see:/index.htmlFor more information on the calibration that Desco’sprovides for products that we manufacture see:/Calibration.aspxSpecificationsOperating Voltage 12 VDCOperating Temperature 32°F - 104°F (0 - 40°C)Monitor Dimensions 4.4" x 4.7" x 2.1"(11.2cm x 11.9cm x 5.3cm)Monitor Weight 1.1 lbs (0.5 kg)TEST VOLTAGESOperator +8 V** or +5 VWorksurface 200 mVTEST LIMITSOperator Low Fail: < 1.72 megohmsPass: 2 - 9 megohms**High Fail: > 11.5 megohms**orPass: 2 - 30 megohmsHigh Fail: > 40 megohmsWorksurface Pass: < 3.5 megohmsFail: > 3.8 megohms**DefaultFigure 7. Operator Remote dimensionsReplacement remotes are available as EMIT itemnumbers 50525 and 50526.分销商库存信息: DESCO19665。

BUK9277-55A,118;中文规格书,Datasheet资料

1.Product profile1.1General descriptionLogic level N-channel enhancement mode Field-Effect Transistor (FET) in a plasticpackage using TrenchMOS technology. This product has been designed and qualified to the appropriate AEC standard for use in automotive critical applications.1.2Features and benefitsQ101 compliantSuitable for logic level gate drive sourcesSuitable for thermally demanding environments due to 175 °C rating1.3Applications12 V and 24 V loadsAutomotive and general purpose power switchingMotors, lamps and solenoids1.4Quick reference dataBUK9277-55AN-channel TrenchMOS logic level FETRev. 3 — 17 May 2011Product data sheetTable 1.Quick reference data Symbol Parameter ConditionsMin Typ Max Unit V DS drain-source voltage T j ≥25°C; T j ≤175°C --55V I D drain current V GS =5V; T mb =25°C; see Figure 1; see Figure 4--18A P tottotal power dissipation T mb =25°C; see Figure 2--51WStatic characteristics R DSondrain-source on-state resistanceV GS =10V; I D =10A;T j =25°C -5969m ΩV GS =4.5V; I D =10A; T j =25°C --86m ΩV GS =5V; I D =10A; T j =25°C; see Figure 13-6577m ΩAvalanche ruggedness E DS(AL)Snon-repetitive drain-sourceavalanche energyI D =18A;V sup ≤55V; R GS =50Ω; V GS =5V; T j(init)=25°C; unclamped--33mJ2.Pinning information3.Ordering informationTable 2.Pinning information Pin Symbol Description Simplified outline Graphic symbol1G gate SOT428 (DPAK)2D drain 3S sourcembDmounting base; connected to drain32mb1Table 3.Ordering informationType numberPackage NameDescriptionVersion BUK9277-55ADPAKplastic single-ended surface-mounted package (DPAK); 3 leads (one lead cropped)SOT4284.Limiting values[1]Maximum value not quoted. Repetitive rating defined in avalanche rating figure.[2]Single-pulse avalanche rating limited by maximum junction temperature of 175 °C.[3]Repetitive avalanche rating limited by an average junction temperature of 170 °C.[4]Refer to application note AN10273 for further information.Table 4.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditionsMin Max Unit V DS drain-source voltage T j ≥25°C; T j ≤175°C -55V V DGR drain-gate voltage R GS =20k Ω-55V V GS gate-source voltage -1515V I Ddrain currentT mb =25°C; V GS =5V;see Figure 1; see Figure 4-18A T mb =100°C; V GS =5V; see Figure 1-13A I DM peak drain current T mb =25°C; pulsed; t p ≤10µs; see Figure 4-73A P tot total power dissipation T mb =25°C; see Figure 2-51W T stg storage temperature -55175°C T j junction temperature -55175°C Source-drain diodeI S source current T mb =25°C-18A I SM peak source current pulsed; t p ≤10µs; T mb =25°C -73A Avalanche ruggednessE DS(AL)S non-repetitive drain-source avalanche energy I D =18A; V sup ≤55V; R GS =50Ω; V GS =5V;T j(init)=25°C; unclamped -33mJ E DS(AL)Rrepetitive drain-source avalanche energysee Figure 3[1][2][3][4]--JSingle-pulse and repetitive avalanche rating; avalanche current as a function of avalanche time5.Thermal characteristicsTable 5.Thermal characteristics Symbol ParameterConditions Min Typ Max Unit R th(j-mb)thermal resistance from junction to mounting base-- 2.93K/W R th(j-a)thermal resistance from junction to ambientsee Figure 5-71.4-K/W6.CharacteristicsTable 6.CharacteristicsSymbol Parameter Conditions Min Typ Max Unit Static characteristicsV(BR)DSS drain-source breakdownvoltage I D=0.25mA;V GS=0V; T j=25°C55--V I D=0.25mA;V GS=0V; T j=-55°C50--VV GS(th)gate-source threshold voltage I D=1mA; V DS=V GS; T j=-55°C;see Figure 12-- 2.3VI D=1mA; V DS=V GS; T j=25°C;see Figure 121 1.52VI D=1mA; V DS=V GS; T j=175°C;see Figure 120.5--VI DSS drain leakage current V DS=55V;V GS=0V; T j=175°C--500µAV DS=55V;V GS=0V; T j=25°C-0.0510µA I GSS gate leakage current V GS=15V;V DS=0V; T j=25°C-2100nAV GS=-15V;V DS=0V; T j=25°C-2100nAR DSon drain-source on-stateresistance V GS=10V;I D=10A;T j=25°C-5969mΩV GS=4.5V; I D=10A; T j=25°C--86mΩV GS=5V;I D=10A;T j=175°C;see Figure 13--154mΩV GS=5V;I D=10A;T j=25°C;see Figure 13-6577mΩDynamic characteristicsQ G(tot)total gate charge I D=10A;V DS=44V;V GS=5V;see Figure 14-11-nCQ GS gate-source charge- 1.6-nC Q GD gate-drain charge-5-nCC iss input capacitance V GS=0V;V DS=25V; f=1MHz;T j=25°C;see Figure 15-440643pFC oss output capacitance-90110pF C rss reverse transfer capacitance-6093pFt d(on)turn-on delay time V DS=30V;R L=1.2Ω; V GS=5V;R G(ext)=10Ω; T j=25°C -10-nst r rise time-47-ns t d(off)turn-off delay time-28-ns t f fall time-33-ns L D internal drain inductance meausured from drain lead frompackage to centre of die; T j=25°C- 2.5-nHL S internal source inductance measured from source lead frompackage to source bond pad;T j=25°C-7.5-nHSource-drain diodeV SD source-drain voltage I S=15A;V GS=0V; T j=25°C;see Figure 16-0.85 1.2Vt rr reverse recovery time I S=20A;dI S/dt=-100A/µs;V GS=-10V;V DS=30V; T j=25°C -33-nsQ r recovered charge-60-nC分销商库存信息: NXPBUK9277-55A,118。

LP395ZNOPB;中文规格书,Datasheet资料

LP395LP395 Ultra Reliable Power TransistorLiterature Number: SNOSBF3BLP395Ultra Reliable Power TransistorGeneral DescriptionThe LP395is a fast monolithic transistor with completeoverload protection.This very high gain transistor has in-cluded on the chip,current limiting,power limiting,and ther-mal overload protection,making it difficult to destroy fromalmost any type of overload.Available in an epoxy TO-92transistor package this device is guaranteed to deliver100mA.Thermal limiting at the chip level,a feature not available indiscrete designs,provides comprehensive protection againstoverload.Excessive power dissipation or inadequate heatsinking causes the thermal limiting circuitry to turn off thedevice preventing excessive die temperature.The LP395offers a significant increase in reliability whilesimplifying protection circuitry.It is especially attractive as asmall incandescent lamp or solenoid driver because of itslow drive requirements and blowout-proof design.The LP395is easy to use and only a few precautions needbe observed.Excessive collector to emitter voltage can de-stroy the LP395as with any transistor.When the device isused as an emitter follower with a low source impedance,itis necessary to insert a4.7kΩresistor in series with thebase lead to prevent possible emitter follower oscillations.Also since it has good high frequency response,supplyby-passing is recommended.Areas where the LP395differs from a standard NPN transis-tor are in saturation voltage,leakage(quiescent)current andin base current.Since the internal protection circuitry re-quires voltage and current to function,the minimum voltageacross the device in the on condition(saturated)is typically1.6Volts,while in the off condition the quiescent(leakage)current is typically200µA.Base current in this device flowsout of the base lead,rather than into the base as is the casewith conventional NPN transistors.Also the base can bedriven positive up to36Volts without damage,but will drawcurrent if driven negative more than0.6Volts.Additionally,ifthe base lead is left open,the LP395will turn on.The LP395is a low-power version of the1-Amp LM195/LM295/LM395Ultra Reliable Power Transistor.The LP395is rated for operation over a−40˚C to+125˚Crange.Featuresn Internal thermal limitingn Internal current and power limitingn Guaranteed100mA output currentn0.5µA typical base currentn Directly interfaces with TTL or CMOSn+36Volts on base causes no damagen2µs switching timeConnection DiagramTO-92Package00552501Order Number LP395ZSee NS Package Z03ATypical ApplicationsFully Protected Lamp Driver00552503©2005National Semiconductor Corporation Collector to Emitter Voltage36VCollector to Base Voltage36V Base to Emitter Voltage(Forward)36V Base to Emitter Voltage(Reverse)10V Base to Emitter Current(Reverse)20mA Operating Temperature Range−40˚C to+ Storage Temperature Range−65˚C to+ Lead Temp.(Soldering,10seconds)Electrical CharacteristicsTested Design Symbol Parameter Conditions Typical Limit Limit((Note3)(Note4)V CE Collector to Emitter0.5mA≤I C≤100mA3636V Operating Voltage(Note2)I CL Collector Current Limit V BE=2V,V CE=36V452520m(Note5)V BE=2V,V CE=15V906050mV BE=2V,2V≤V CE≤6V130100100m I B Base Current0≤I C≤100mA−0.3−2.0−2.5µI Q Quiescent Current V BE=0V,0≤V CE≤36V0.240.500.60m V CE(SAT)Saturation Voltage V BE=2V,I C=100mA 1.82 2.00 2.10V BV BE Base to Emitter Break-0≤V CE≤36V,I B=2µA3636V down Voltage(Note5)V BE Base to Emitter Voltage I C=5mA0.690.790.90V (Note6)I C=100mA(Note5) 1.02 1.40V t S Switching Time V CE=20V,R L=200Ω2V BE=0V,+2V,0VθJA Thermal Resistance0.4"leads soldered to150180 Junction to Ambient printed circuit board0.125"leads soldered to130160printed circuit boardNote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the functional,but do not guarantee specific performance limits.Note2:Parameters identified with boldface type apply at temp.extremes.All other numbers,unless noted apply at+25˚C.Note3:Guaranteed and100%production tested.Note4:Guaranteed(but not100%production tested)over the operating temperature and supply voltage ranges.These limits are not used to calculate quality levels.Note5:These numbers apply for pulse testing with a low duty cycle.Note6:Base positive with respect to emitter.Simplified Circuit005525052one in which the filament resistance drops to a very low value before it actually blows out.This is especially rough on most solid-state lamp drivers and in most cases a lamp failure of this type will also cause the lamp driver to fail.descent lamps.Additionally,the current limiting characteris-tics of the LP395are advantageous as it serves to limit the cold filament inrush current,thus increasing lamp life.Typical Performance Characteristics5Volt Transfer Function36Volt Transfer Function0055251000552511Collector Characteristics Available Collector Current0055251200552513Quiescent Collector Current Saturation Voltage00552514005525153Collector Current Threshold00552509Typical ApplicationsLamp Flasher(Short Circuit Proof)Optically IsolatedSwitch0055250600552507 Two TerminalCurrent Limiter Composite PNP0055250800552502 4Order Number LP395ZNS Package Z03ANational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.For the most current product information visit us at .LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systemswhich,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform whenproperly used in accordance with instructions for useprovided in the labeling,can be reasonably expected to resultin a significant injury to the user.2.A critical component is any component of a life supportdevice or system whose failure to perform can be reasonablyexpected to cause the failure of the life support device orsystem,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification(CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National SemiconductorAmericas CustomerSupport CenterEmail:new.feedback@Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improveme and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products a sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work rig or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rma published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanie by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptiv business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids a express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasona be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their product and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may b provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely a the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such us TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communications Amplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotive Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated分销商库存信息: NATIONAL-SEMICONDUCTOR LP395Z/NOPB。

AD9265BCPZ-105;AD9265BCPZ-125;AD9265BCPZ-80;AD9265BCPZRL7-80;中文规格书,Datasheet资料

16-Bit, 125 MSPS/105 MSPS/80 MSPS,1.8 V Analog-to-Digital ConverterAD9265Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2009–2010 Analog Devices, Inc. All rights reserved.FEATURESSNR = 79.0 dBFS @ 70 MHz and 125 MSPS SFDR = 93 dBc @ 70 MHz and 125 MSPS Low power: 373 mW @ 125 MSPS 1.8 V analog supply operation 1.8 V CMOS or LVDS output supply Integer 1-to-8 input clock divider IF sampling frequencies to 300 MHz−154.3 dBm/Hz small signal input noise with 200 Ω input impedance @ 70 MHz and 125 MSPS Optional on-chip ditherProgrammable internal ADC voltage reference Integrated ADC sample-and-hold inputsFlexible analog input range: 1 V p-p to 2 V p-pDifferential analog inputs with 650 MHz bandwidth ADC clock duty cycle stabilizer Serial port controlUser-configurable, built-in self-test (BIST) capability Energy-saving power-down modesAPPLICATIONSCommunicationsMultimode digital receivers (3G)GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, and TD-SCDMA Smart antenna systemsGeneral-purpose software radios Broadband data applications Ultrasound equipmentPRODUCT HIGHLIGHTS1. On-chip dither option for improved SFDR performance with low power analog input.2. Proprietary differential input that maintains excellent SNR performance for input frequencies up to 300 MHz.3.Operation from a single 1.8 V supply and a separate digital output driver supply accommodating 1.8 V CMOS or LVDS outputs.4.Standard serial port interface (SPI) that supports various product features and functions, such as data formatting (offset binary, twos complement, or gray coding), enabling the clock duty cycle stabilizer, DCS, power-down, test modes, and voltage reference mode.5.Pin compatibility with the AD9255, allowing a simple migration from 16 bits down to 14 bits.FUNCTIONAL BLOCK DIAGRAMDRVDD (1.8V)D15 TO D0DCODITHER CLK+CLK–SYNCVCM VREF VIN+VIN–DFS DCSOR08502-001Figure 1.AD9265Rev. A | Page 2 of 44TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Product Highlights ........................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 General Description ......................................................................... 3 Specifications ..................................................................................... 4 ADC DC Specifications ............................................................... 4 ADC AC Specifications ................................................................. 5 Digital Specifications ................................................................... 6 Switching Specifications ................................................................ 8 Timing Specifications .................................................................. 9 Absolute Maximum Ratings .......................................................... 10 Thermal Characteristics ............................................................ 10 ESD Caution ................................................................................ 10 Pin Configurations and Function Descriptions ......................... 11 Typical Performance Characteristics ........................................... 15 Equivalent Circuits ......................................................................... 23 Theory of Operation ...................................................................... 25 ADC Architecture ...................................................................... 25 Analog Input Considerations .................................................... 25 Voltage Reference ....................................................................... 28 Clock Input Considerations ...................................................... 29 Power Dissipation and Standby Mode .................................... 31 Digital Outputs ........................................................................... 32 Timing ......................................................................................... 32 Built-In Self-Test (BIST) and Output Test .................................. 33 Built-In Self-Test (BIST) ............................................................ 33 Output Test Modes ..................................................................... 33 Serial Port Interface (SPI) .............................................................. 34 Configuration Using the SPI ..................................................... 34 Hardware Interface ..................................................................... 34 Configuration Without the SPI ................................................ 35 SPI Accessible Features .............................................................. 35 Memory Map .................................................................................. 36 Reading the Memory Map Register Table ............................... 36 Memory Map Register Table ..................................................... 37 Memory Map Register Descriptions ........................................ 39 Applications Information .............................................................. 40 Design Guidelines ...................................................................... 40 Outline Dimensions ....................................................................... 41 Ordering Guide .. (41)REVISION HISTORY1/10—Rev. 0 to Rev. AChanges to Worst Other (Harmonic or Spur) Parameter,Table 2 ................................................................................................ 5 Changes to Figure 77 ...................................................................... 29 Changes to Input Clock Divider Section ..................................... 30 Changes to Table 17 ........................................................................ 37 Updated Outline Dimensions . (41)10/09—Revision 0: Initial VersionAD9265Rev. A | Page 3 of 44GENERAL DESCRIPTIONThe AD9265 is a 16-bit, 125 MSPS analog-to-digital converter (ADC). The AD9265 is designed to support communications applications where high performance combined with low cost, small size, and versatility is desired.The ADC core features a multistage, differential pipelined architecture with integrated output error correction logic to provide 16-bit accuracy at 125 MSPS data rates and guarantees no missing codes over the full operating temperature range. The ADC features a wide bandwidth differential sample-and-hold analog input amplifier supporting a variety of user-selectable input ranges. It is suitable for multiplexed systems that switch full-scale voltage levels in successive channels and for sampling single-channel inputs at frequencies well beyond the Nyquist rate. Combined with power and cost savings over previously available ADCs, the AD9265 is suitable for applications in communications, instrumentation and medical imaging. A differential clock input controls all internal conversion cycles. A duty cycle stabilizer provides the means to compensate for vari-ations in the ADC clock duty cycle, allowing the converters to maintain excellent performance over a wide range of input clock duty cycles. An integrated voltage reference eases design consid-erations.The ADC output data format is either parallel 1.8 V CMOS or LVDS (DDR). A data output clock is provided to ensure proper latch timing with receiving logic.Programming for setup and control is accomplished using a 3-wire SPI-compatible serial interface. Flexible power-down options allow significant power savings, when desired. An optional on-chip dither function is available to improve SFDR performance with low power analog input signals.The AD9265 is available in a Pb-free, 48-lead LFCSP and is speci-fied over the industrial temperature range of −40°C to +85°C.AD9265Rev. A | Page 4 of 44SPECIFICATIONSADC DC SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , SVDD = 1.8 V , maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS enabled, unless otherwise noted. Table 1.Parameter Temp AD9265BCPZ-801AD9265BCPZ-1051 AD9265BCPZ-1251 Unit Min Typ Max Min Typ Max Min Typ Max RESOLUTION Full 16 16 16 Bits ACCURACY No Missing Codes Full Guaranteed Guaranteed Guaranteed Offset Error Full ±0.05 ±0.25 ±0.05 ±0.25 ±0.05 ±0.25 % FSR Gain Error Full ±0.2 ±2.5 ±0.2 ±2.5 ±0.4 ±2.5 % FSRDifferential Nonlinearity (DNL)2Full −1.0 +1.25 −1.0 +1.25 −1.0 +1.25 LSB 25°C ±0.6 ±0.65 ±0.7 LSBIntegral Nonlinearity (INL)2Full ±2.5 ±3.5 ±4.5 LSB 25°C ±1.5 ±2.0 ±3.0 LSB TEMPERATURE DRIFT Offset Error Full ±2 ±2 ±2 ppm/°CG ain Error Full ±15 ±15 ±15 ppm/°CINTERNAL VOLTA G E REFERENCE Output Voltage Error (1 V Mode) Full +8 ±12 +8 ±12 +8 ±12 mV Load Regulation @ 1.0 mA Full 3 3 3 mV INPUT REFERRED NOISE VREF = 1.0 V 25°C 2.17 2.26 2.17 LSB rmsANALOG INPUTInput Span, VREF = 1.0 V Full 22 2 V p-pInput Capacitance 3 Full 88 8 pFInput Common-Mode Voltage Full 0.90.9 0.9 VREFERENCE INPUT RESISTANCE Full 66 6 kΩPOWER SUPPLIES Supply Voltage AVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V DRVDD Full 1.7 1.8 1.9 1.7 1.8 1.9 1.7 1.8 1.9 V SVDD Full 1.7 3.5 1.7 3.5 1.7 3.5V Supply CurrentIAVDD 2Full 126131169176 194 202 mA IDRVDD 21.8 V CMOS Full 1420 24 mA 1.8 V LVDS Full 4346 49 mA POWER CONSUMPTION DC Input Full 241258323343 373 392 mWSine Wave Input 2DRVDD = 1.8 V CMOS Output Mode Full 254341 394 mW LVDS Output Mode Full 308391 439 mWStandby Power 4 Full 5454 54 mWPower-Down Power Full 0.050.150.050.15 0.05 .015 mW1 The suffix following the part number refers to the model found in the Ordering Guide section.2Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit. 3Input capacitance refers to the effective capacitance between one differential input pin and AGND. 4Standby power is measured with a dc input, the CLK pins (CLK+, CLK−) inactive (set to AVDD or AGND).AD9265Rev. A | Page 5 of 44ADC AC SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , SVDD = 1.8 V , maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS enabled, unless otherwise noted. Table 2.Parameter 1 Temp AD9265BCPZ-802 AD9265BCPZ-1052 AD9265BCPZ-1252Unit Min Typ Max Min Typ Max Min Typ Max SI G NAL-TO-NOISE-RATIO (SNR)f IN = 2.4 MHz 25°C 80.2 79.7 79.0 dBFS f IN = 70 MHz 25°C 79.7 79.2 79.0 dBFS Full 78.7 78.2 77.3 dBFS f IN = 140 MHz 25°C 78.4 78.3 77.5 dBFS f IN = 200 MHz 25°C 77.1 76.9 75.6 dBFSSIGNAL-TO-NOISE-AND DISTORTION (SINAD)f IN = 2.4 MHz 25°C 79.6 79.4 78.7 dBFS f IN = 70 MHz 25°C 79.6 78.8 78.7 dBFS Full 78.6 77.9 77.0 dBFS f IN = 140 MHz 25°C 77.3 77.5 77.0 dBFSf IN = 200 MHz 25°C 76.0 75.7 74.4 dBFSEFFECTIVE NUMBER OF BITS (ENOB)f IN = 2.4 MHz 25°C 12.912.9 12.8 Bits f IN = 70 MHz 25°C 12.912.8 12.8 Bits f IN = 140 MHz 25°C 12.512.6 12.5 Bits f IN = 200 MHz 25°C 12.312.3 12.1Bits WORST SECOND OR THIRD HARMONICf IN = 2.4 MHz 25°C −88 −90 −88 dBc f IN = 70 MHz 25°C −94 −89 −93 dBc Full −92 −88 −85 dBc f IN = 140 MHz 25°C −82 −86 −89 dBc f IN = 200 MHz 25°C −81 −81 −80 dBcSPURIOUS-FREE DYNAMIC RANGE (SFDR)f IN = 2.4 MHz 25°C 88 90 88 dBc f IN = 70 MHz 25°C 94 89 93 dBc Full 92 88 85 dBc f IN = 140 MHz 25°C 82 86 89 dBc f IN = 200 MHz 25°C 81 81 80 dBcSPURIOUS-FREE DYNAMIC RANGE (SFDR) Without Dither (AIN @ −23 dBFS)f IN = 2.4 MHz 25°C 103 98 96 dBFS f IN = 70 MHz 25°C 103 96 98 dBFS f IN = 140 MHz 25°C 104 96 98 dBFS f IN = 200 MHz 25°C 102 101 97 dBFSWith On-Chip Dither (AIN @ −23 dBFS)f IN = 2.4 MHz 25°C 110 108 108 dBFS f IN = 70 MHz 25°C 110 109 110 dBFS f IN = 140 MHz 25°C 110 109 109 dBFS f IN = 200 MHz 25°C 110 109 109 dBFSAD9265Rev. A | Page 6 of 44Parameter 1 Temp AD9265BCPZ-802 AD9265BCPZ-1052 AD9265BCPZ-1252Unit Min Typ Max Min Typ Max Min Typ Max WORST OTHER (HARMONIC OR SPUR)Without Dither f IN = 2.4 MHz 25°C −106 −105 −101 dBc f IN = 70 MHz 25°C −106 −104 −103 dBc Full −97 −95 −92 dBc f IN = 140 MHz 25°C −104 −103 −104 dBc f IN = 200 MHz 25°C −102 −103 −100 dBc With On-Chip Dither f IN = 2.4 MHz 25°C −106 −105 −102 dBc f IN = 70 MHz 25°C −106 −105 −103 dBc Full −97 −99 −98 dBc f IN = 140 MHz 25°C −104 −103 −104 dBc f IN = 200 MHz 25°C −101 −101 −100 dBc TWO-TONE SFDR Without Dither f IN = 29 MHz (−7 dBFS ), 32 MHz (−7 dBFS ) 25°C 9390 95 dBcf IN = 169 MHz (−7 dBFS ), 172 MHz (−7 dBFS ) 25°C 8078 79 dBcANALOG INPUT BANDWIDTH 25°C 650 650 650 MHz1 See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation , for a complete set of definitions.2The suffix following the part number refers to the model found in the Ordering Guide section.DIGITAL SPECIFICATIONSAVDD = 1.8 V , DRVDD = 1.8 V , SVDD = 1.8 V , maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, and DCS enabled, unless otherwise noted. Table 3.Parameter Temperature Min Typ Max Unit DIFFERENTIAL CLOCK INPUTS (CLK+, CLK−) Logic Compliance CMOS/LVDS/LVPECL Internal Common-Mode Bias Full 0.9 V Differential Input Voltage Full 0.3 3.6 V p-p Input Voltage Range Full AGND AVDD V Input Common-Mode Range Full 0.9 1.4 V High Level Input Current Full −100 +100 μA Low Level Input Current Full −100 +100 μA Input Capacitance Full 4 pF Input Resistance Full 8 10 12 kΩ SYNC INPUT Logic Compliance CMOS Internal Bias Full 0.9 V Input Voltage Range Full AGND AVDD V High Level Input Voltage Full 1.2 AVDD V Low Level Input Voltage Full AGND 0.6 V High Level Input Current Full −100 +100 μA Low Level Input Current Full −100 +100 μA Input Capacitance Full 1 pF Input Resistance Full 12 16 20 kΩAD9265Rev. A | Page 7 of 44Parameter Temperature Min Typ Max UnitLOGIC INPUT (CSB)1High Level Input Voltage Full 1.22 SVDD V Low Level Input Voltage Full 0 0.6 V High Level Input Current Full −10 +10 μA Low Level Input Current Full 40 132 μA Input Resistance Full 26 kΩ Input Capacitance Full 2 pF LOGIC INPUT (SCLK/DFS)2 High Level Input Voltage Full 1.22 SVDD V Low Level Input Voltage Full 0 0.6 V High Level Input Current (VIN = 1.8 V) Full −92 −135 μA Low Level Input Current Full −10 +10 μA Input Resistance Full 26 kΩ Input Capacitance Full 2 pF LOGIC INPUT/OUTPUT (SDIO/DCS)1 High Level Input Voltage Full 1.22 SVDD V Low Level Input Voltage Full 0 0.6 V High Level Input Current Full −10 +10 μA Low Level Input Current Full 38 128 μA Input Resistance Full 26 kΩ Input Capacitance Full 5 pF High Level Output Voltage Full 1.70 V Low Level Output Voltage Full 0.2 V LOGIC INPUTS (OEB, PDWN, DITHER, LVDS, LVDS_RS)2 High Level Input Voltage Full 1.22 2.1 V Low Level Input Voltage Full 0 0.6 V High Level Input Current (VIN = 1.8 V) Full −90 −134 μA Low Level Input Current Full −10 +10 μA Input Resistance Full 26 kΩ Input Capacitance Full 5 pF DIGITAL OUTPUTS (DRVDD = 1.8 V) CMOS Mode High Level Output Voltage I OH = 50 μA Full 1.79 V I OH = 0.5 mA Full 1.75 V Low Level Output Voltage I OL = 1.6 mA Full 0.2 V I OL = 50 μA Full 0.05 V LVDS Mode ANSI Mode Differential Output Voltage (V OD ) Full 290 345 400 mV Output Offset Voltage (V OS ) Full 1.15 1.25 1.35 V Reduced Swing Mode Differential Output Voltage (V OD ) Full 160 200 230 mV Output Offset Voltage (V OS ) Full 1.15 1.25 1.35 V1 Pull-up.2Pull-down.AD9265Rev. A | Page 8 of 44SWITCHING SPECIFICATIONS−1.0 dBFS differential input, 1.0 V internal reference, and DCS enabled, unless otherwise noted. Table 4.AD9265BCPZ-801 AD9265BCPZ-1051 AD9265BCPZ-1251 Parameter Temp Min Typ Max Min Typ Max Min Typ Max Unit CLOCK INPUT PARAMETERS Input Clock Rate Full 625 625 625 MHz Conversion Rate 2 DCS Enabled Full 20 80 20 105 20 125 MSPS DCS Disabled Full 10 80 10 105 10 125 MSPS CLK Period—Divide-by-1 Mode (t CLK ) Full 12.5 9.5 8 ns CLK Pulse Width High (t CH ) Divide-by-1 Mode, DCS Enabled Full 3.75 6.25 8.75 2.85 4.75 6.65 2.4 4 5.6 ns Divide-by-1 Mode, DCS Disabled 5.9 6.25 6.6 4.5 4.75 5.0 3.8 4 4.2 nsDivide-by-3 Mode, Divide-by-5 Mode, andDivide-by-7 Mode, DCS Enabled 3Full 0.8 0.8 0.8 ns Divide-by-2 Mode, Divide-by-4 Mode, Divide-by-6 Mode and Divide-by-8 Mode, DCSEnabled or DCS Disabled 3 Full 0.8 0.8 0.8 ns Aperture Delay(t A ) Full 1.0 1.0 1.0 ns Aperture Uncertainty (Jitter, t J ) Full 0.07 0.07 0.07 ps rms DATA OUTPUT PARAMETERS CMOS Mode Data Propagation Delay (t PD ) Full 2.4 2.8 3.4 2.4 2.8 3.4 2.4 2.8 3.4 nsDCO Propagation Delay (t DCO )4Full 2.7 3.4 4.2 2.7 3.4 4.2 2.7 3.4 4.2 ns DCO to Data Skew (t SKEW ) Full 0.3 0.6 0.9 0.3 0.6 0.9 0.3 0.6 0.9 ns Pipeline Delay (Latency) Full 12 12 12 Cycles LVDS Mode Data Propagation Delay (t PD ) Full 2.6 3.4 4.2 2.6 3.4 4.2 2.6 3.4 4.2 nsDCO Propagation Delay (t DCO )4Full 3.3 3.8 4.3 3.3 3.8 4.3 3.3 3.8 4.3 ns DCO to Data Skew (t SKEW ) Full −0.3 0.4 1.2 −0.3 0.4 1.2 −0.3 0.4 1.2 ns Pipeline Delay (Latency) Full 12.5 12.5 12.5 CyclesWake-Up Time 5Full 500 500 500 μs OUT-OF-RAN G E RECOVERY TIME Full 2 2 2 Cycles1 The suffix following the part number refers to the model found in the Ordering Guide section. 2Conversion rate is the clock rate after the divider. 3See the Input Clock Divider section for additional information on using the DCS with the input clock divider. 4Additional DCO delay can be added by writing to Bit 0 through Bit 4 in SPI Register 0x17 (see Table 17). 5Wake-up time is defined as the time required to return to normal operation from power-down mode.AD9265Rev. A | Page 9 of 44TIMING SPECIFICATIONSTable 5.ParameterConditions Min Typ Max Unit SYNC TIMING REQUIREMENTSt SSYNC SYNC to rising edge of CLK setup time 0.30 ns t HSYNCSYNC to rising edge of CLK hold time 0.40 ns SPI TIMING REQUIREMENTSt DS Setup time between the data and the rising edge of SCLK 2 ns t DH Hold time between the data and the rising edge of SCLK 2 ns t CLK Period of the SCLK40 ns t S Setup time between CSB and SCLK 2 ns t H Hold time between CSB and SCLK 2 ns t HIGH SCLK pulse width high 10 ns t LOW SCLK pulse width low10 ns t EN_SDIO Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge10 ns t DIS_SDIOTime required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge10nsTiming Diagrams08502-002NOTES1. DEx DENOTES EVEN BIT.2. DOx DENOTES ODD BIT.Figure 2. LVDS (DDR) and CMOS Output Mode Data Output TimingSYNC08502-104Figure 3. SYNC Input Timing RequirementsAD9265Rev. A | Page 10 of 44ABSOLUTE MAXIMUM RATINGSTable 6.Parameter RatingElectricalAVDD to AGND −0.3 V to +2.0 VDRVDD to AGND −0.3 V to +2.0VSVDD to AGND −0.3 V to +3.6 VVIN+, VIN− to AGND −0.3 V to AVDD + 0.2 V CLK+, CLK− to AGND −0.3 V to AVDD + 0.2 V SYNC to AGND −0.3 V to AVDD + 0.2 V VREF to AGND −0.3 V to AVDD + 0.2 V SENSE to AGND −0.3 V to AVDD + 0.2 V VCM to AGND −0.3 V to AVDD + 0.2 V RBIAS to AGND −0.3 V to AVDD + 0.2 V CSB to AGND −0.3 V to SVDD +0.3 V SCLK/DFS to AGND −0.3 V to SVDD +0.3 V SDIO/DCS to AGND −0.3V to SVDD + 0.3 V OEB to AGND −0.3 V to DRVDD + 0.2 V PDWN to AGND −0.3 V to DRVDD + 0.2 V LVDS to AGND −0.3 V to AVDD + 0.2 V LVDS_RS to AGND −0.3 V to AVDD + 0.2 V DITHER to AGND −0.3 V to AVDD + 0.2 V D0 through D15 to AGND −0.3 V to DRVDD + 0.2 V DCO to AGND −0.3 V to DRVDD + 0.2 V EnvironmentalOperating Temperature Range(Ambient)−40°C to +85°C Maximum Junction TemperatureUnder Bias150°C Storage Temperature Range(Ambient)−65°C to +150°CStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stressrating only; functional operation of the device at these or anyother conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affectdevice reliability. THERMAL CHARACTERISTICSThe exposed paddle must be soldered to the ground plane for the LFCSP package. Soldering the exposed paddle to the customer board increases the reliability of the solder joints and maximizes the thermal capability of the package.Typical θJA is specified for a 4-layer PCB with a solid ground plane. As shown, airflow improves heat dissipation, which reduces θJA . In addition, metal in direct contact with the package leads from metal traces, through holes, ground, and power planes, reduces the θJA . Table 7. Thermal ResistancePackage Type Airflow Velocity(m/s) θJA 1, 2 θJC 1, 3 θJB 1, 4 Unit 48-Lead LFCSP (CP-48-8)0 24.5 1.3 12.7 °C/W 1.0 21.4 °C/W 2.5 19.2 °C/W1Per JEDEC 51-7, plus JEDEC 25-5 2S2P test board.2Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air). 3Per MIL-Std 883, Method 1012.1. 4Per JEDEC JESD51-8 (still air).ESD CAUTION分销商库存信息:ANALOG-DEVICESAD9265BCPZ-105AD9265BCPZ-125AD9265BCPZ-80AD9265BCPZRL7-80AD9265BCPZRL7-105AD9265BCPZRL7-125 AD9265-125EBZ AD9265-105EBZ AD9265-80EBZ。

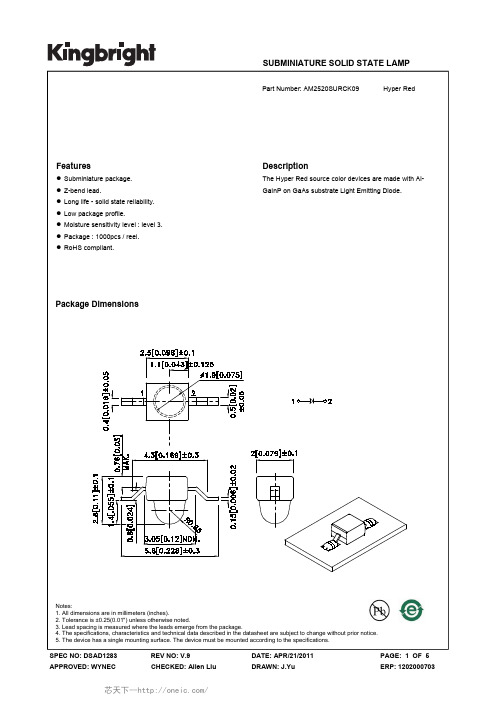

AM2520SURCK09, 规格书,Datasheet 资料

Recommended Soldering Pattern (Units : mm; Tolerance: ± 0.1)

Reel Dimension

Tape Dimensions (Units : mm)

SPEC NO: DSAD1283 APPROVED: WYNEC

REV NO: V.9 CHECKED: Allen Liu

SUBMINIATURE SOLID STATE LAMP

Part Number: AM2520SURCK09 Hyper Red

Features

Subminiature package. Z-bend lead. Long life - solid state reliability. Low package profile. Moisture sensitivity level : level 3. Package : 1000pcs / reel. RoHS compliant.

DATE: APR/21/2011 DRAWN: J.Yu

PAGE: 2 OF 5 ERP: 1202000703

芯天下--/

Hyper Red

AM2520SURCK09

SPEC NO: DSAD1283 APPROVED: WYNEC

REV NO: V.9 CHECKED: Allen Liu

DATE: APR/21/2011 DRAWN: J.Yu

PAGE: 3 OF 5 ERP: 1202000703

芯天下--/

AM2520SURCK09

Reflow soldering is recommended and the soldering profile is shown below. Other soldering methods are not recommended as they might cause damage to the product.

BFT92W,115;中文规格书,Datasheet资料

2

45 o

MLB548

1.0

90 o

VCE = 10 V; IC = 15 mA.

Fig.10 Common emitter input reflection coefficient (s11), typical values.

90 o

135 o

45 o

180 o

40 MHz 50 40 30 20 10 3 GHz

Fig.6

Gain as a function of collector current, typical values.

Fig.7

Gain as a function of collector current, typical values.

50 gain (dB) 40 G UM 30 MSG

MLB546

1 C re (pF) 0.8

6 fT (GHz) 4 V CE = 10 V 5V

MLB543

0.6

0.4

2

0.2

0 0 4 8 12 16 20 VCB (V)

0 1 10 I C (mA) 10 2

IC = 0; f = 1 MHz.

f = 500 MHz; Tamb = 25 C.

Fig.4

DISCRETE SEMICONDUCTORS

DATA SHEET

BFT92W PNP 4 GHz wideband transistor

Product specification May 1994

/

NXP Semiconductors

Product specification

0 0 10 20 I C (mA) 30

VCE = 10 V; Tj = 25 C.

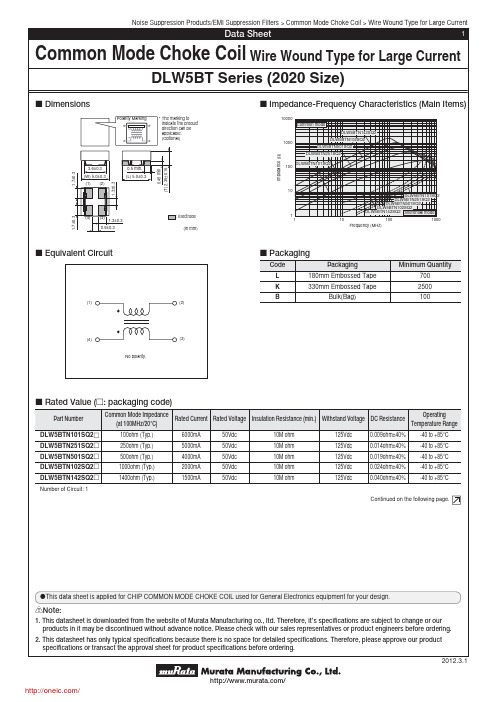

DLW5BTN142SQ2L;DLW5BTN102SQ2L;DLW5BTN101SQ2L;DLW5BTN251SQ2L;DLW5BTN501SQ2L;中文规格书,Datasheet资料

Operating

(at 100MHz/20°C)

Temperature Range

DLW5BTN101SQ2p DLW5BTN251SQ2p DLW5BTN501SQ2p DLW5BTN102SQ2p DLW5BTN142SQ2p Number of Circuit: 1

100ohm (Typ.) 250ohm (Typ.) 500ohm (Typ.) 1000ohm (Typ.) 1400ohm (Typ.)

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

Data Sheet

1

Common Mode Choke Coil Wire Wound Type for Large Current

2012.3.1

/

/

Noise Suppression Products/EMI Suppression Filters > Common Mode Choke Coil > Wire Wound Type for Large Current

0.5 min. (L) 5.0±0.3

0.45 min. (T) 2.35±0.15

1.3±0.3

1.7±0.3

(4) (3) 1.3±0.3 0.9±0.3

: Electrode (in mm)

c Impedance-Frequency Characteristics (Main Items)

10000 Common mode

Notice Solderability of Tin plating termination chip might be deteriorated when low temperature soldering profile where peak solder temperature is below the Tin melting point is used. Please confirm the solderability of Tin plating termination chip before use.

ISL99201IRTCZ-TK,ISL99201IRTCZ-TK,ISL99201IRTDZ-TK,ISL99201IRTDZ-TK, 规格书,Datasheet 资料

ISL99201IRTDZ-TK (Notes 1, 2) 201D ISL99201IIAZ-T (Notes 1, 3, 4) 201A

ISL99201IIAZ-TK (Notes 1, 3, 4) 201A ISL99201IIBZ-T (Notes 1, 3, 4) 201B

ISL99201IIBZ-TK (Notes 1, 3, 4) 201B ISL99201IICZ-T (Notes 1, 3, 4) 201C

Features

• Filterless Class D with Efficiency > 86% at 400mW • Click-Pop Suppression • Slew Rate Control • Spread Spectrum Switching • Optional SYNC Pin for Master/Slave Operation Without Interface (Only in TDFN) • 1.4W into 8Ω with Less than 1% THD+N • 2.4V to 5.5V Single Supply Voltage • Built-in Resistors to Reduce Board Component Count • Only One External Component Required (Fixed Gain Mode) • Short Circuit and Thermal Protection • Gain Programmable 6dB, 9.6dB, 12dB and User Programmable • Pb-Free (RoHS compliant)

ISL99201IICZ-TK (Notes 1, 3, 4) 201C ISL99201IIDZ-T (Notes 1, 3, 4) ISL99201IIDZ-TK (Notes 1, 3, 4) NOTES: 1. Please refer to TB347 for details on reel specifications. 201D 201D

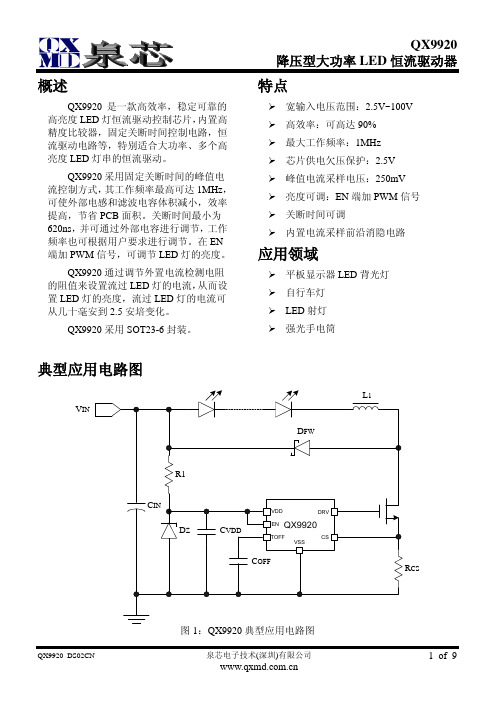

QX9920中文规格书

L1 > 4VLED ∗TOFF ∗ RCS

系统工作频率

系统工作频率FS由下式确定:

FS

=

VIN VIN

− VLED ∗ TOFF

QX9920_DS02CN

泉芯电子技术(深圳)有限公司

7 of 9

封装信息

SOT23-6 封装尺寸图:

QX9920 降压型大功率 LED 恒流驱动器

本产品主要应用于消费类电子产品中,如果客户将本产品应用于医疗、军事、航天等要求 极高质量、极高可靠性的领域的产品中,其潜在失败风险所造成的人身伤害、财产损失等 情况,泉芯公司不承担任何责任。

本规格书所包含的信息仅作为泉芯产品的应用指南,没有任何专利和知识产权的许可暗示, 如果客户侵犯了第三方的专利和知识产权,泉芯公司不承担任何责任。

VDD

TOFF

关断时间 控制电路

EN 带隙基准 250mV

SQ RQ

250mV

DRV CS

QX9920_DS02CN

VSS

图 2:QX9920 内部电路方框图

泉芯电子技术(深圳)有限公司

3 of 9

QX9920 降压型大功率 LED 恒流驱动器

极限参数(注 1)

参数

符号

9 of 9

描述

最小值 最大值 单位

电压

VMAX

VDD 最大电压

VMIN_MAX EN、DRV、CS 和 TOFF 脚电压

-0.3

7

V

VDD+0.3

V

最大功耗 温度

PSOT23-6

SOT23-6 最大功耗

TJ

结温范围

-20

TA

工作温度

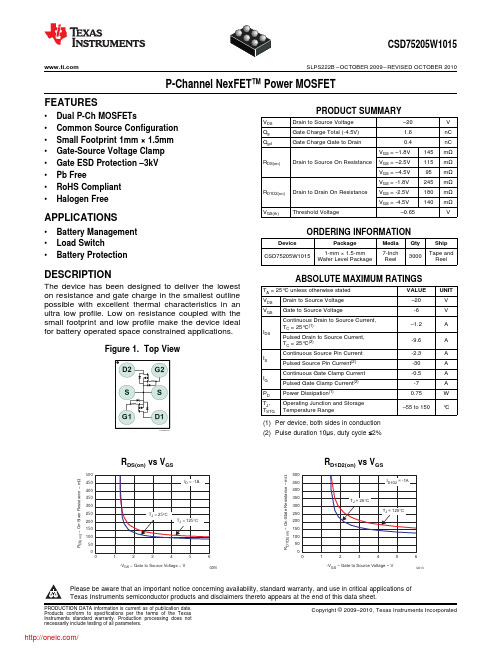

CSD75205W1015;中文规格书,Datasheet资料

VDS = –10V, IDS = –1A

VDS = –10.25V, VGS = 0V

VDS = –10V, VGS = –4.5V, IDS = –1A, RG = 10Ω

IDS = –1A, VGS = 0V Vdd = –10.25V, IF = –1A, di/dt = 200A/μs Vdd = –10.25V, IF = –1A, di/dt = 200A/μs

td(on)

Turn On Delay Time

tr

Rise Time

td(off)

Turn Off Delay Time

tf

Fall Time

Diode Characteristics

VSD

Diode Forward Voltage

Qrr

Reverse Recovery Charge

trr

Reverse Recovery Time

TJ = 25°C

TJ = 125°C

1

2

3

4

5

-VGS − Gate to Source Voltage − V

6

G006

500 450 400 350 300 250 200 150 100

50 0 0

RD1D2(on) vs VGS

ID1D2 = -1A

TJ = 25°C

TJ = 125°C

1

RDS(on) Drain to Source On Resistance

RD1D2(on) Source to Drain On Resistance

gfs

Transconductance

PDR5K-13;中文规格书,Datasheet资料

5A GLASS PASSIVATED RECTIFIERPowerDI ®5Features• Glass Passivated Die Construction • Low Leakage Current • Lead Free Finish, RoHS Compliant (Note 1) • "Green" Molding Compound (No Br, Sb)Mechanical Data• Case: PowerDI ®5• Case Material: Molded Plastic, “Green” Molding Compound.UL Flammability Classification Rating 94V-0 • Moisture Sensitivity: Level 1 per J-STD-020 • Terminals: Finish – Matte Tin annealed over Copper leadframe.Solderable per MIL-STD-202, Method 208 • Polarity: See Diagram • Marking Information: See Page 3 • Ordering Information: See Page 3 • Weight: 0.096 grams (approximate)Maximum Ratings @T A = 25°C unless otherwise specifiedSingle phase, half wave, 60Hz, resistive or inductive load. For capacitance load, derate current by 20%.Characteristic Symbol Value UnitPeak Repetitive Reverse VoltageWorking Peak Reverse Voltage DC Blocking Voltage V RRM V RWMV R750 V Average Rectified Output Current I O5 A Non-Repetitive Peak Forward Surge Current8.3ms Single Half Sine-Wave Superimposed on Rated Load I FSM160 AThermal CharacteristicsCharacteristic Symbol Value UnitTypical Thermal Resistance Junction to Lead R θJL3 °C/W Typical Thermal Resistance Junction to Ambient (Note 3) R θJA28 °C/W Operating and Storage Temperature Range T J , T STG-65 to +175 °CElectrical Characteristics @T A = 25°C unless otherwise specifiedCharacteristic Symbol Min Typ Max Unit TestConditionForward Voltage V F⎯⎯ 0.91 ⎯ 0.99 0.87 V I F = 5A, T S = 25°C I F = 5A, T S = 125°CReverse Leakage Current (Note 2) I R⎯ ⎯ ⎯ ⎯ 10 0.3 μAmA V R = 750V, T J = 25°C V R = 750V, T J = 125°CTypical Reverse Recovery Time t rr ⎯ 3 ⎯μs I F = 0.5A, I R = 1.0A,I rr = 0.25ANotes:1. EU Directive 2002/95/EC (RoHS). All applicable RoHS exemptions applied. Please visit our website at /products/lead_free.html.2. Short duration pulse test used to minimize self-heating effect.3. Device mounted on Polymide PCB, with 16X recommended pad layout.Top View Bottom ViewLEFT PIN RIGHT PINNote: Pins Left & Right must be electrically connected at the printed circuit board.BOTTOMSIDE HEAT SINKFig. 1 Forward Power Dissipation I , AVERAGE FORWARD CURRENT (A)F(AV)P , P O W E R D I S S I P A T I O N (W )D V , INSTANTANEOUS FORWARD VOLTAGE (V)Fig. 2 Typical Forward CharacteristicsF10I , I N S T A N T A N E O U S F O R W A R D C U R R E N T (A )FV , INSTANTANEOUS REVERSE VOLTAGE (V)Fig. 3 Typical Reverse CharacteristicsR I I N S T A N T A N E O U S R E V E R S E C U R R E N T (µA )R ,101001,000Fig. 4 Total Capacitance vs. Reverse VoltageV , DC REVERSE VOLTAGE (V)R C , T O T A L C A P A C I T A N C E (p F )T56I A V E R A G E F O R W A R D C U R R E NT (A )F (A V ),T , AMBIENT TEMPERATURE (C)Fig. 5 Forward Current Derating CurveA °02004006008001,000Fig. 6 Operating T emperature DeratingV , DC REVERSE VOLTAGE (V)R T , D E R A T E D A M B I E N T T E M P E R A T U R E (°C )AOrdering Information (Note 4)Part Number CasePackaging PDR5K-13 PowerDI ®55000/Tape & ReelNotes: 4. For packaging details, go to our website at /datasheets/ap02007.pdf.Marking InformationPackage Outline DimensionsSuggested Pad LayoutPowerDI ®5 Dim Min Max A 1.05 1.15 A2 0.33 0.43 b1 0.80 0.99 b2 1.70 1.88 D 3.90 4.05 D2 3.054 Typ E6.40 6.60 e 1.84 TypE1 5.30 5.45 E2 3.549 Typ L 0.75 0.95 L1 0.50 0.65 W 1.101.41 All Dimensions in mmDimensionsValue (in mm)Z 6.6 X11.4 X2 3.6 Y1 0.8 Y2 4.7 C3.87 E1 0.9R5K = Product Type Marking Code = Manufacturers’ code marking YYWW = Date code markingYY = Last two digits of year (ex: 09 for 2009) WW = Week code 01 to 52 K = Factory DesignatorYYWWKR5KIMPORTANT NOTICEDIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.LIFE SUPPORTDiodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:A. Life support devices or systems are devices or systems which:1. are intended to implant into the body, or2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in thelabeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.Copyright © 2009, Diodes Incorporated分销商库存信息: DIODESPDR5K-13。

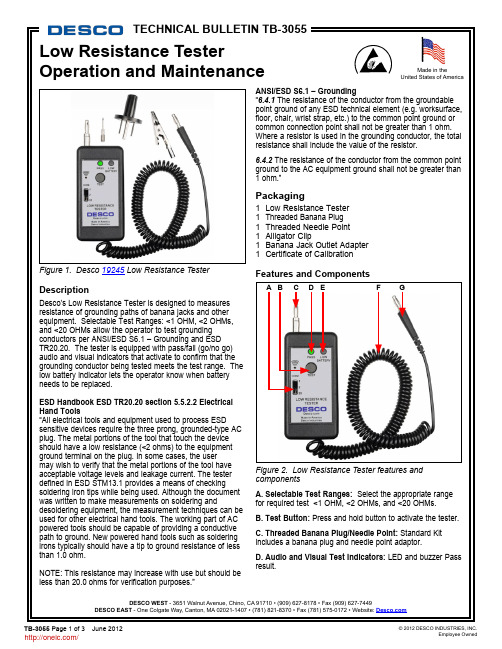

19245;中文规格书,Datasheet资料

Made in theUnited States of AmericaDescriptionDesco’s Low Resistance Tester is designed to measures resistance of grounding paths of banana jacks and other equipment. Selectable Test Ranges: <1 OHM, <2 OHMs, and <20 OHMs allow the operator to test grounding Figure 1. Desco 19245 Low Resistance TesterANSI/ESD S6.1 – GroundingThe resistance of the conductor from the groundable point ground of any ESD technical element (e.g. worksurface, floor, chair, wrist strap, etc.) to the common point ground or common connection point shall not be greater than 1 ohm. Where a resistor is used in the grounding conductor, the total Figure 2. Low Resistance Tester features and componentsA. Selectable Test Ranges: Select the appropriate range for required test <1 OHM, <2 OHMs, and <20 OHMs.B. Test Button: Press and hold button to activate the tester.BCD EGFE. Low Battery LED: LED illuminates when the battery needs to be replaced.F. 6 Foot Coiled Cord: Insulation black color PVCG. Banana Plug: Industrial Standard .175 “(4.4 mm) Banana Plug, fits banana jack ≥ .157”.OperationUSING THE TESTER 1. Select test range.2. Connect coil cord banana plug end to known ground. Use adaptors where needed. Note: The Desco Low Resistance Tester may be used with an outlet polarity checker, such as Desco’s 19219, to determine a knownground.3. Connect or touch tester end to banana jack or other equipment that is being tested for resistance to ground.4. Press and hold test button.5. An audio and visual indication will activate for Pass result6. No audio or visual indication will indicate a Fail resultFigure 3. Testing banana jacks with 19245 tester.Example of Test Range Uses<1 OHM Range- ESD Technical element Grounding Conductors: Banana Jacks, Grounding Blocks, Mat Ground Cords ANSI/ESD S6.1 Grounding, sections 6.4 Technical Elements, 6.4.1, 6.4.2 and 6.4.3 - New AC Powered Hand ToolsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools<2 OHM- Soldering IronsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools- Other AC Powered Hand ToolsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools<20 OHM- Soldering iron verificationESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools- Auxiliary grounds (ground rods) ANSI/ESD S20.20** ANSI/ESD S20.20 requires <25 ohms from the Auxiliary Ground to the Equipment Grounding Conductor. Desco’s Low Resistance Tester only tests to <20 ohms. In cases of a no pass result with the Low Resistance Tester when testing an Auxiliary Ground, an Ohm meter should used to determine the actual resistance from the Auxiliary Ground to the Equipment Grounding ConductorFigure 4. Testing soldering iron with 19245 tester.Figure 6. Testing auxiliary ground with 19245 tester.Remove the 2 screws located at the back of the tester.Remove and turn over the circuit board.4. Locate and replace the battery (3 Volt; Model CR2032).5. Re-assemble the tester.First, place battery under prongsNext, press here to snap battery in place分销商库存信息: DESCO19245。

L9825中文资料

THERMAL DATA

Symbol

Parameter

Thermal shutdown

TJSC Thermal shutdown threshold

Thermal resistance Rthjc-one Single output (junction case) Max. Rthjc-all All outputs (junction case) Max.

V

-0.3 to 7

V

IIN

Protection diodes current 1)

(T ≤ 1ms)

-20 to 20

mA

Outputs (Out1 ... Out8)

VOUTc Continuous output voltage

-1.0 to 45

V

IOUT

Output current 2)

-3 to 2.05

9

CLK serial clock

10

GND device ground

11

GND device ground

12

NON2 control input 2

13

VCC supply voltage

14

Out 2 output 2

15

Out 4 output 4

16

Out 6 output 6

17

Out 8 output 8

BLOCK DIAGRAM

VCC

NON1

VCC

1

3

2

Q1

S Latch / Driver

R

OUT1 IOL

Diag1

NON2 NCS

VCC

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 INDEPENDENTLY CONTROLLEDH-BRIDGESR DS,ON <0.9Ω @ T amb = 25°C, V S = 14V 0.8A DC CURRENT WITHOUT HEAT SINK LOW QUIESCENT MODE I q <200µA THEMAL PROTECTIONCROSS CONDUCTION PROTECTION SUPPLY VOLTAGE UP TO 40V CMOS COMPATIBLE INPUTSOUTPUT SHORT-CIRCUIT PROTECTIONDESCRIPTIONThe L9925 is a dual full bridge driver for stepper motor applications. Realized in BCD (Bipolar,CMOS & DOS) techology, logic circuits, precise linear blocks and power transistors are combined to optimize circuit performance and minimize off chip components. Schmitt triggers are used for all input stages and are fully compatible with 5V CMOS logic levels. When both enable signals are low, the IC is commanded to a low quiescent cur-rent state and will draw less than 200µA from the battery.The charge pump is integrated on chip; no exter-nal components are required. Full performance is maintaned for 9V <V S <16V. Extended ranges of 6V <<V S <9V and 16V <V S <40V yields full func-tionally but with relaxed performance. Over tem-perature protection and ESD protection to all pins ensures relability and reduces system integration failures................................................................................................................................................................................................................March 1999®CHARGE PUMP TEMP OUT1VS1OUT2IN2PGND1VS2OUT3OUT4IN1EN1GNDEN2IN3IN42nd FULL BRIDGE1st FULL BRIDGE 5VREGULATOREN1EN1EN1EN240V7V7V 7VT1T1T2T2T1T2CHARGE PUMPD99AT423BLOCK DIAGRAMSO28ORDERING NUMBER: L9925L9925DMOS DUAL FULL BRIDGE DRIVER1/9Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) O b s o le t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond whih damage to the device may occur. Functional operation under these condition isn’t implied.For voltages and currents applied externally to the device:Symbol ParameterValue Unit V VSDC Dc Supply Voltage-0.3 to 26V V VSP Supply Voltage Pulse (T ≤400ms) (1)40V I OUT DC Output Load Current±1.2A I OUT MAXDC Output Current: for VOUT > VVS +0.3V or VOUT < -0.3V the internal DMOS reverse and/or substrate diode become conductive and the applied current should not exceed the specified limit.±1.8AV IN1,2DC Input Voltage -0.3 to 7VV EN Enable Input Voltage-0.3 to 7VT stg , T jStorage and Junction Temperature-40 to 150°C P totTotal Power Dissipation (T pins = 80°C)(T amb = 70°C no copper area on PCB) (T amb =70°C 8cm 2 copper area on PCB)51.232W W W(1) Device may be overstressed if pulsed simultaneous with short circuit at one or more of the outputs will be present.THERMAL DATASymbol Parameter Value Unit T jTS Thermal Shut-down junction temperature min.150°C T jTSH Thermal Shut-down thereshold hysteresis typ.25°CR th j-amb Thermal Resistance Junction-ambient (2)50°C/W R th j-pinsThermal Resistance Junction-pins15°C/W(2)With 6cm 2 on board heat sink areaPGND IN1EN1N.C.N.C.GND OUT1GND OUT3VS2GND GND N.C.VS1N.C.OUT2IN2N.C.1324567892625242322202119271028N.C.N.C.D88AT424N.C.EN2IN3IN4OUT4N.C.1112131816171514PGNDN.C.PIN CONNECTIONO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) ELECTRICAL CHARACTERISTICS (V S = 9 to 16V; T j = -40 to 150°C (3), unless otherwise specified.)Symbol ParameterTest ConditionMin.Typ.Max.Unit I SQuiescent CurrentEN1 = EN2 =0V; T j = 85°C200µA EN1 = EN2 =5V; I load = 0A512mAR ds Switch on Resistance T j = 25°C; V S = 14V; I o =300mA 0.750.8ΩT j = 125°C; V S = 6V; I o =300mA 1.5 1.9ΩT d-on Turn-on delay See Fig 11050µs T d-SB Standby setting time See Fig 150200µs T d-off Turn-off delaySee Fig 11050µs t rise Output rise time (10 to 90%)See Fig 10.5520µs t fall Output fall time (90 to 10%)See Fig 10.5520µs IL oOutput leakage current EN = 0V; V o =V S or GND -1010mAINx, ENx Logic Input Low voltage -0.31.5V Logic Input High voltage 3.56V Hysteresis0.51.02.0VIbias Input bias current -50300µAThe voltage refered to GND and currents are assumed positive, when the current flows into the pin.(3) Tested up to 125°C, parameter guaranted by correlation up to 150°CPIN FUNCTIONS Function1PGND1Ground for DMOS sources in bridge 12IN1Digital Input from motor controller for bridge 13EN1Logic enable/disable for bridge 1 (active high)4, 5NC No connect6OUT1Output of one half of bridge 17, 8GND Ground9OUT3Output of one half of bridge 210, 11NC No connect12EN2Logic enable/disable for bridge 2 (active high)13IN3Digital Input from motor controller for bridge 214PGND2Ground for DMOS sources in bridge 215NCNo connect16IN4Digital Input from motor controller for bridge 217OUT4Output of one half of bridge 218, 19NCNo connect 20VS2Supply Voltage for bridge 221, 22GNDGround23VS1Supply Voltage for bridge 124, 25NCNo connect26OUT2Output of one half of bridge 127IN2Digital Input from motor controller for bridge 128NCNo connectO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) Logic LevelsAll inputs are positive, non inverting logicLogic StateVoltage Range 0-0.3 to 1.5V 13.5 to 6.0VTruth Table Enable/ DisableEN1EN0Bridge 1Bridge 2Iq 00Disabled Disabled<200µA 01DisabledEnabled <12mA 10Enabled Disabled<12mA11Enabled Enabled <12mAGeneral OperationWith the bridge enabled, each input INx, maps di-rectly to the corresponding output OUTx.The output voltage will be equal to the difference between the supply rail and the product of the load current ad the on resistance of the output switch.V out = V supply - (R DS,ON ⋅ I LOAD ). Sourced load currents are positive.IN1OUT1IN2OUT2IN3OUT3IN4OUT4000000001V S1V S1VS1VSt r t ft ft r 10%t dSB OUT1IN2IN1EN1EN2OUT2t dSBt dSBD99AT425STANDBY MODE OPERATING MODE OVERTEMPERATURE STANDBY MODEt dOFF t dOFF t dSB t dON t dON90%50%TristateTristate Tristate TristateTristateTristateFigure 1. Timing Diagram-4012D99AT426RON (Ω)V VS =6V V VS =12V-20020406080100120140160T(˚C)Figure 2. Typical R ON - Characteristics of Sourceand Sink Stage61.50.750.91.9D99AT427RON (Ω)max for T J ≤125˚CI OUT1/2=±0.3Atyp. for T J =25˚C1216.5V VS (V)Figure 3. ON - Resistance vs Supply VoltageO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) Figure 4 shows a typical application diagram for DC motor driving. To assure the safety of the cir-cuit in the reverse battery condition a reverse pro-tetion diode D 1 is necessary. The transient pro-tection diode D 2 must assure that themaximum supply voltage V S during the transients at the V BAT line will be limited to a value lower than the absolute maximu ratings for V VSP . The capacities C B are used to lower V S -EMR and its values de-pend on the driving load.The resistance feedback loop realized by R o lim-ited to the µP power supply line by the diode D o allows open load detection. To protect the device at the outputs against EMI or ESD > 2KV external capacitors C ex may be used.CIRCUIT DESCRIPTIONL9925 is a dual full bridge IC designed to drive DC motors, stepper motors and other inductive loads. Eah bridge has 4 power DMOS transistor with R DSon = 0.75Ω and the relative protection and control circuitry (see fig. 5). Tthe 4 half bridges can be controlled independently by means of the 4 inputs IN1, IN3, IN4 and 2 enable inputs ENABLE1 and ENABLE2.LOGIC DRIVE (true table for the two full bridges)INPUTSOUTPUT MOSFETSIN1IN3IN2IN4EN1 = EN2 = HL L H HL H L H Sink 1, Sink2Sink1, Source2Source1, Sink2Source1, Source2@Tj > 150°C X X All transistors turned OFF EN1 = EN2 = L XXAll transistors turned OFFL = Low; H = High; X = Don’t careCROSS CONDUCTIONThe device guarantees the absence of cross-con-duction by watching internal gate-source voltage of the driving power DMOS.TRANSISTOR OPERATION ON STATEWhen one of POWER DMOS transistors is ON it can be considered as a resistor R DS(ON) = 0.75Ωat a junction temperature of 25°CCHARGEPUMPTEMPOUT1VS1OUT2IN2PGND1VS2OUT3OUT4IN1EN1GNDEN2O O OI/OI/O I/OD 0D 1D 240VR 010K ΩR 010K ΩC B 100nFC B 40V 100µFD 0+5VO OIN3IN42nd FULL BRIDGE1st FULL BRIDGE 5VREGULATOREN1µP EN1EN1EN240V7V7V7VT1T1T2T2T1T2CHARGE PUMPPGND2D99AT423C EN 100nFC EN 100nFC EX 100nFC EX 100nFABSTEPPER MOTORFigure 4. Application DiagramO b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) In this condition the dissipated power is ginen by:P ON = R DS(ON) ⋅ I DS 2The low R DS(ON) of the Multipower BCD process can provide high currents with low power dissipa-tion.OFF STATEWhen one of the POWER DMOS transistor is OFF the V DS voltage is equal to the supply volt-age and only the leakage current I DSS flows.The power dissipation during this period is given by:P OFF = V S ⋅ I DSSTRANSITIONSLike all MOS power transistors the DMOS POWER transistors have an intrinsic diode be-tween their source and drain that can operate as a fast freewheeling diode in switched mode appli-cations. During recirculation with the ENABLE in-put is low, the POWER MOS is OFF and the di-ode voltage it is clamped to its characteristics.When the ENABLE input is low, the POWER MOS is OFF and the diode carries all of the recir-culation current. The power dissipated in the tran-sitional times in the cycle depends upon the volt-age and current waveforms in the application.P trans = I DS (t) ⋅ V DS (t)Figure 5a. Two phase choppingFigure 5b. One phase choppingFigure 5c. Enable choppingENIN1 = HIN2 = L EN1 = HIN1IN2D99AT429ENIN1 = L IN2 = H EN1 = HIN1IN2D99AT430EN IN1 = H IN2 = L EN1 = HIN1IN2D99AT431ENIN1 = H IN2 = H EN1 = HIN1IN2D99AT432EN IN1 = H IN2 = L EN1 = HIN1IN2D99AT433ENIN1 = X IN2 = X EN1 = LIN1IN2D99AT434O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )Ob s o l e t e P r o d uc t (s ) - O b s o l e t e P r od u c t (s ) THERMAL PROTECTIONA thermalprotection circuit has been included that will disable the device if the junction temperature reaches 150°C. When the temperature has fallen to a safe level the device restarts under the con-trol of the input and enable signals.APPLICATION INFORMATION RECIRCULATIONDuring recirculationwith the ENALBE input high,the voltage drop across the transistor is R DS(ON).for voltages less than 0.6V and is clamped at a voltages depending on the characteristics of the source-drain diode for greater voltages. Although the device is protected against cross conduction.POWER DISSIPATION each bridgeIn order to achieve the high performance provided by the L9925 some attention must be paid t en-sure that it has an adequate PCB area to dissi-pate the heat. The forst stage of any thermal de-sign is to calculate the dissipated power in the application, for this example the half step opera-tion shown in Fig. 6 is considered.RISE TIME T RWhen an arm of the half bridge is turned on cur-rent begins to flow in the inductive load until the maximum current I L is reached after a time T R ,The dissipated energy E OFF/ON .E OFF/ON = [R DS(ON) ⋅ I L 2 ⋅ T R ] ⋅23ON TIME T ONDuring this time the energy dissipated is due to the ON resistance of the transistors E ON and thecommutation E COM . As two of the POWER DMOS transistors are ON E ON is given by:E ON = I L 2 ⋅ R DS(ON) ⋅ 2 ⋅ T ONIn the commutation the energy dissipated is:E CON = V S ⋅ I L ⋅ T COM ⋅ f SWITCH ⋅ T ONWhere:T COM = Communication Time and it is assumed that:;T COM = t rise = t fall ≤ 20µsT SWITCH = Chopper frequencyFALL TIME T FFor this example it is assumed that the energy dissipated in this part of the cycle takes the same form as that shown for the rise time:E OFF/ON = [R DS(ON) ⋅ I L 2 ⋅ TF ] ⋅23QUIESCENT ENERGYThe last contribution of the energy dissipation is due to the quiescrent supply current and is given by:E QUIESCENT = I QUIESCENT ⋅ V S ⋅ TTOTAL ENERGY PER CYCLEE TOT = (2 ⋅ E OFF/ON + E ON + E COM ) bridge1++ (2 ⋅ E OFF/ON + E ON + E COM ) bridg2 + E QUIESCENTThe total power dissipation P DIS is simply:P DIS =E tot TT R = Rise time T ON = ON time T F = Fall time T OFF = OFF time T = PeriodT = T R + T ON + T F + T OFFT switchT R T ON T OFFT F I LD99AT435Figure 6.O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )l e t e Pr o du ct(s)-O bs ol e te Pr o du ct(s)SO28DIM.mm inchMIN.TYP.MAX.MIN.TYP.MAX.A 2.650.104 a10.10.30.0040.012 b0.350.490.0140.019 b10.230.320.0090.013 C0.50.020c145° (typ.)D17.718.10.6970.713 E1010.650.3940.419 e 1.270.050e316.510.65F7.47.60.2910.299 L0.4 1.270.0160.050 S8° (max.)OUTLINE AND MECHANICAL DATAO b s ol e te Pr o du ct(s)-O bs ol e te Pr o du ct(s)O bs oObs o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s ) Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequencesof use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics © 1999 STMicroelectronics – Printed in Italy – All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.O b s o l e t e P r o d u c t (s ) - O b s o l e t e P r o d u c t (s )分销商库存信息: STML9925。