APPSA04-41SGWA中文资料

APPSA04-41SYKWA中文资料

Absolute Maximum Ratings at TA=25°C °

P ar am et er Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating/Storage Temperature

Note: 1. 1/10 Duty Cycle, 0.1ms Pulse Width.

Su p er B r ig h t Yello w 125 30 175 5 -40° C To +85°C

Un its mW mA mA V

SPEC NO:DSAB3096 APPROVED : J. Lu

REV NO: V.3 CHECKED: Joe Lee

Electrical / Optical Characteristics at TA=25°C °

Sy m b o l λpeak λD ∆λ1/2 C VF IR P ar am et er Peak Wavelength Dominate Wavelength Spectral Line Half-width Capacitance Forward Voltage Reverse Current D ev i c e Super Bright Yellow Super Bright Yellow Super Bright Yellow Super Bright Yellow Super Bright Yellow Super Bright Yellow Ty p . 590 590 20 20 2.0 2.5 10 Max . Un its nm nm nm pF V uA Tes t Co n d it io n s I F =20mA I F =20mA I F =20mA VF=0V;f=1MHz I F =20mA V R = 5V

AD2S80A中文手册

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

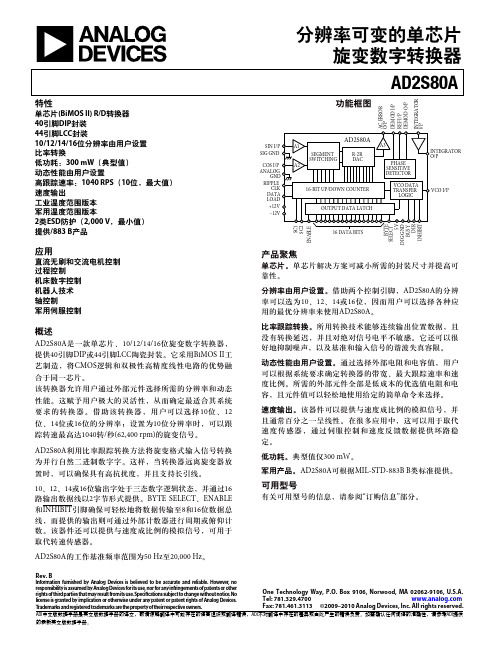

分辨率可变的单芯片 旋变数字转换器 AD2S80A

单芯片(BiMOS ll) R/D转换器 40引脚DIP封装 44引脚LCC封装 10/12/14/16位分辨率由用户设置 比率转换 低功耗:300 mW(典型值) 动态性能由用户设置 高跟踪速率:1040 RPS(10位,最大值) 速度输出 工业温度范围版本 军用温度范围版本 2类ESD防护(2,000 V,最小值) 提供/883 B产品

弧分 弧分 弧分 代码 代码

% FSD % FSD mV µV/°C % FSD V % rm s O /P kΩ V mA

1 mA负载 均值 过压保护 短路输出保护 10、12、14和16 双向自然二进制 逻辑LO至INHIBIT 逻辑LO使能位置 输出。逻辑HI输出处于 高阻抗状态 MS Byte DB1–DB8、 LS Byte DB9–DB16 LS Byte DB1–DB8、 LS Byte DB9–DB16 内部拉高 (100 kΩ)至+VS 10位 12位 14位 16位

AO4803A;中文规格书,Datasheet资料

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

Gate-Source Voltage

VGS

Continuous Drain

TA=25°C

Current

TA=70°C

Pulsed Drain Current C

Avalanche Current C

Avalanche energy L=0.1mH C

ID

IDM IAS, IAR EAS, EAR

TA=25°C Power Dissipation B TA=70°C

PD

Junction and Storage Temperature Range

TJ, TSTG

Maximum -30 ±20 -5 -4 -30 17 14 2 1.3

AK4311A-VM资料

2's complement MSB-first data is input on this pin.

9 LRCK

I L/R Clock Pin

10 CDATA

I Control Data Input Pin

Must be tied to "H" or "L" if this pin is not used.

11 CCLK

I Control Clock Input Pin

Must be tied to "H" or "L" if this pin is not used.

12 CS

I Chip Select Pin

Must be tied to "H" if this pin is not used.

13 TST2

6 CLKO

O Clock Buffer Output Pin, Inverting clock output of XTI

7 BICK

I Serial Bit Input Clock Pin

This clock is used to latch audio data.

8 SDATA

I Audio Data Input Pin

Symbol

min

AVDD

-0.3

DVDD

-0.3

IIN

-

VIND

-0.3

Ta

-10

Tstg

-65

[AK4311A]

max 6.0 AVDD+0.3 ±10 AVDD+0.3 70 150

Units V V mA V °C °C

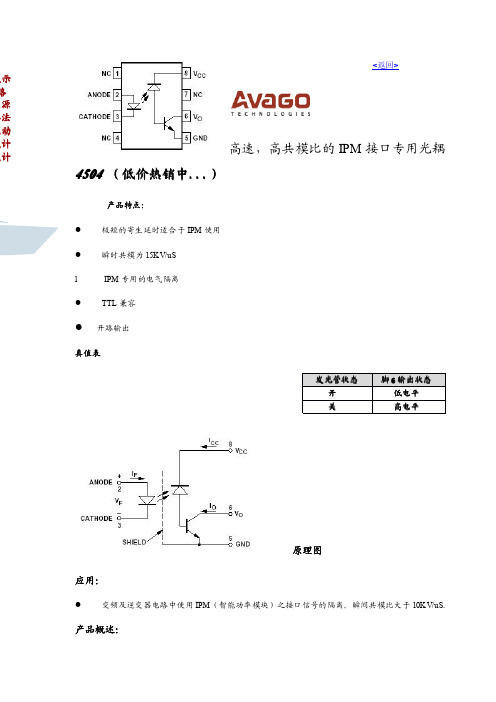

A4504中文资料

上图是典型的功率器件接口电路以及时序图;

众所周知,当功率管IPM开关工作时,原则上是绝对不能使上下两臂同时导通的。

即使在高下稍有交迭也会潜在威胁功率管和周遍电路,特别是在大电流状态下。

防止这一现象的办法是一只的时候必须确保他的对管已经完全关闭。

在此加入了一段小小的延时,被称之为“死区”。

如何缩是工程师的一项重要的课题。

“开通”IPM延时时间取决于光耦的寄生延时数据又要参照IPM的驱动电路,其中重要的是参大和最小延时时间,上图的LED是输入电压,OUT是输出电压。

大多数设计应用是:当输入为高电打开。

那么根据图上下输入的需要延时的时间至少应该是(tPLHmax-tPHLmin),此数据在手册上大多数情况下,IPM数据手册给定的死区时间是大于光耦所规定的最少要求延时的。

HCPL-4504高速光耦与IPM连接的例图:

设计注意:

1:7脚8脚需要短路连接;

2:IPM功率越大上拉电阻值越小;

3:光耦副边的引线须尽量小于2cm;

1)与DIP-IPM连接原理图:(见DIP-IPM设计手册)

2)与通用IPM连接原理图:

<返回>

上海嘉尚电子科技有限公司版权所有@2005咨询热线:021-********,54420290传真:021-********。

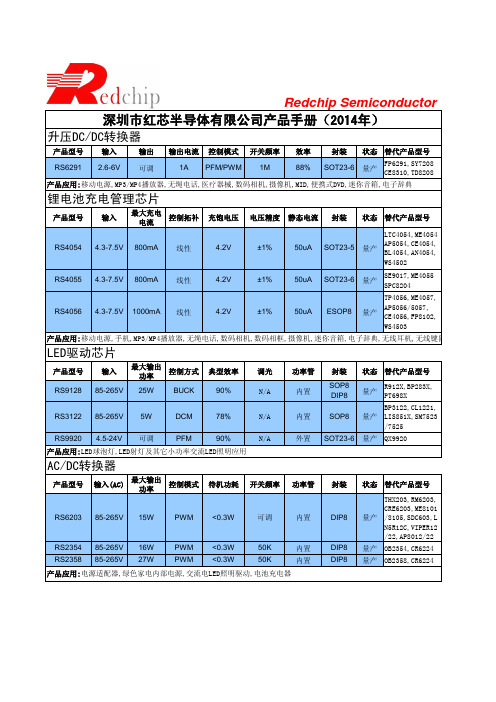

红芯半导体产品手册2014

量产 OB2358,CR6224

产品应用:电源适配器,绿色家电内部电源,交流电LED照明驱动,电池充电器

Redchip Semiconductor 深圳市红芯半导体有限公司产品手册(2014年)

马达驱动芯片

产品型号 输入 驱动电流 静态电流 待机电流

热保护

RS117/118 1.8-7.2V 1.5A 300uA 0.1uA

±1%

50uA

ESOP8

量产

TP4056,ME4057, AP5056/5057, CE4056,FP8102, WS4503

产品应用:移动电源,手机,MP3/MP4播放器,无绳电话,数码相机,数码相框,摄像机,迷你音箱,电子辞典,无线耳机,无线键鼠

LED驱动芯片

产品型号

最大输出

输入

控制方式 典型效率

产品型号输入输出输出电流控制模式开关频率效率封装状态替代产品型号rs6291266v可调1apfmpwm1m88sot236量产fp6291sy7208ce8310td8208产品型号输入最大充电电流控制拓补充饱电压电压精度静态电流封装状态替代产品型号rs40544375v800ma线性42v150uasot235量产ltc4054me4054ap5054ce4054bl4054an4054ws4502rs40554375v800ma线性42v150uasot236量产se9017me4055spc8204rs40564375v1000ma线性42v150uaesop8量产tp4056me4057ap50565057ce4056fp8102ws4503产品型号输入最大输出功率控制方式典型效率调光功率管封装状态替代产品型号rs912885265v25wbuck90内置sop8dip8量产r912xbp283xpt698xrs312285265v5wdcm78内置sop8量产bp3122cl1221lis851xsm75237525rs99204524v可调pfm90外置sot236量产qx9920产品型号输入ac最大输出功率控制模式待机功耗开关频率功率管封装状态替代产品型号rs620385265v15wpwm03w可调内置dip8量产thx203rm6203cre6203me81018105sdc603ln5r12cviper1222ap801222rs235485265v16wpwm03w50k内置dip8量产ob2354cr6224rs235885265v27wpwm03w50k内置dip8量产ob2358cr6224redchipsemiconductor深圳市红芯半导体有限公司产品手册2014年升压dcdc转换器产品应用

sg-004a使用手册

sg-004a使用手册摘要:一、sg-004a使用手册概述二、sg-004a的功能与特点三、sg-004a的安装与配置1.准备工作2.安装步骤3.配置步骤四、sg-004a的使用方法1.基本操作2.高级功能五、sg-004a的维护与故障排除1.日常维护2.常见故障排除六、sg-004a的软件升级与更新七、结论正文:sg-004a使用手册sg-004a是一款功能强大的设备,本手册将详细介绍sg-004a的使用方法、功能特点以及维护技巧。

一、sg-004a使用手册概述sg-004a使用手册旨在为用户提供一个详细的操作指南,帮助用户更好地了解sg-004a的功能、安装、配置和使用方法。

通过本手册,用户可以掌握sg-004a的操作技巧,确保设备稳定运行,提高工作效率。

二、sg-004a的功能与特点sg-004a具有以下主要功能和特点:1.高性能处理器,处理速度快,响应迅速;2.大容量内存,满足多种应用场景需求;3.丰富的接口,可连接多种外部设备;4.稳定的系统,保证长时间运行不断电;5.节能环保,低功耗设计,节省能源。

三、sg-004a的安装与配置1.准备工作在开始安装前,请确保设备已经验收合格,并准备好相关工具和配件,如螺丝刀、螺丝等。

2.安装步骤(1)首先,将sg-004a放置在合适的位置,确保地面平整,避免设备摇晃。

(2)然后,将设备底部的螺丝拧下,拆开底盖。

(3)接着,按照图纸连接电源线、数据线等,注意接线顺序和颜色对应。

(4)最后,将底盖重新安装,拧紧螺丝。

3.配置步骤(1)打开设备电源,待设备启动后,进入配置界面。

(2)根据需求设置设备参数,如时钟、网络配置等。

(3)配置完成后,保存设置,并重启设备。

四、sg-004a的使用方法1.基本操作(1)接通电源,启动设备。

(2)根据需求,连接外部设备。

(3)运行相关应用程序,开始工作。

2.高级功能(1)设备管理:查看设备状态、性能等信息。

(2)数据备份与恢复:定期备份数据,防止数据丢失。

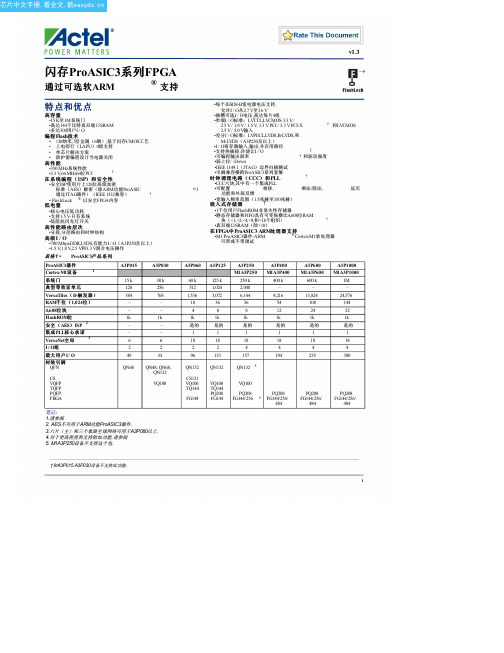

M1A3P250-1FG144中文资料(microsemi)中文数据手册「EasyDatasheet - 矽搜」

以ProASIC3器件做出参考也适用于ARM功能ProASIC3器件.该ARM功能部件号开始与M1(Cortex-M1).

IV

v1.3

芯片中文手册,看全文,戳

1 - ProASIC3器件系列简介

概述

超出ProASIC功能

PLUS® 家庭.非易失性闪存技术使ProASIC3

设备是安全,低功耗,单芯片解决方案,上电即行(LAPU)优势.ProASIC3再编程,提供时间将

表 2•

ProASIC3 FPGA包装规格尺寸

包

QN48 CS121

长 ×宽 (毫米 \毫米)

6×6

6×6

标称面产品

(mm 2)

36

36

间距( mm)

0.4

0.5

高度( mm)

0.90

0.99

QN68 8×8

64

0.4 0.90

QN132 8×8

VQ100 14 × 14

28 × 28

低电量

•核心电压低功耗

•支持1.5 V-只有系统

•低阻抗闪光灯开关

高性能路由层次

•分段,分层路由和时钟结构

高级I / O

•700 MbpsDDR,LVDS,有能力I / O(A3P250及以上)

•1.5 V,1.8 V,2.5 V和3.3 V混合电压操作

表格 1 • ProASIC3产品系列

ProAS IC3器 件

ProASIC3器件支持ARM Cortex-M1处理器. ARM设备有开头M1A3P(Cortex-M1)和不支持 AES解密Actel订购数量.

闪存优点

降低购置成本

优点设计师超出低单位成本,性能和易用性.不比 基于SRAMFPGA,以Flash为基础ProASIC3器件允许所有功能是住在电;没有外部引导PROM是必需.上 电路板安全机制防止访问所有节目安排信息并启用FPGA逻辑安全远程更新.设计人员 可以进行安全远程在系统编程,以支持未来设计迭代和现场升级与信心,有价值知识产 权(IP)不能被复制或受到威胁.安全ISP可以使用行业标准AES算法来执行. ProASIC3系 列器件结构减轻需要在更高用户容量ASIC移植.这使得ProASIC3系列具有成本效益ASIC替代 解决方案,尤其是在消费类,网络/通信,计算,和航空电子市场应用程序.

OPA132UAG4资料

PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

OPEN-LOOP GAIN Open-Loop Voltage Gain

RL = 10kΩ, VO = –14.5V to +13.8V RL = 2kΩ, VO = –13.8V to +13.5V RL = 600Ω, VO = –12.8V to +12.5V

FREQUENCY RESPONSE Gain-Bandwidth Product Slew Rate Settling Time: 0.1%

ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

OPA132 op amps are easy to use and free from phase inversion and overload problems often found in common FET-input op amps. Input cascode circuitry provides excellent common-mode rejection and maintains low input bias current over its wide input voltage range. OPA132 series op amps are stable in unity gain and provide excellent dynamic behavior over a wide range of load conditions, including high load capacitance. Dual and quad versions feature completely independent circuitry for lowest crosstalk and freedom from interaction, even when overdriven or overloaded.

ZM4741A中文资料(vishay)中文数据手册「EasyDatasheet - 矽搜」

8.5

40

1000

0.25

ZM4752A

33

7.5

45

1000

0.25

ZM4753A

36

7

50

1000

0.25

ZM4754A

39

6.5

60

1000

0.25

ZM4755A

43

6

70

1500

0.25

ZM4756A

47

5.5

80

1500

0.25

ZM4757A

51

5

95

1500

0.25

ZM4758A

56

4.5

绝对最大额定值

Tamb = 25℃,除非另有说明

参数

齐纳电流(见表"特色")

功耗

注意:

1) 有效规定,电极被防护持在环境温度.

热特性

Tamb = 25℃,除非另有说明

参数 热阻结到环境空气 结温 储存温度

注意:

1) 有效规定,电极被防护持在环境温度.

测试条件 测试条件

18315

符号

值

单元

Ptot

1 1)

18317

6.50 (0.256) ref.

min. 3.00 (0.118)

芯片中文手册,看全文,戳

法律免责声明

免责声明

所有产品规格及数据如有更改,恕不另行通知. Vishay Intertechnology,Inc.宣布,其附属公司,代理商和员工,以及代表及其或其各自所有人(统称为" Vishay"),对本文包含任何错误,不准确或不完整或以任何其他方式披露不承担任何责任有关任何产品.

SCX25A_v4_04161 中文版

SCX25A 录音室电容话筒概览SCX25A 是专业的录音室电容话筒,有着优雅的设计,专利话筒头悬吊系统。

独特的防震安装在机械精制的铜环中,SCX25A 话筒头完全与话筒身和电路隔离开来。

能够将声学反射和衍射最小化,SCX25A 提供纯净而开放的声音,拥有出色的细节和真实感。

SCX25A 具有平稳均匀的20 Hz - 20 kHz 频率响应, SCX25A 对于轴向和离轴信号的响应都能保持十分稳定一致,并表现出优秀的相位一致性能,邻近效应影响达到最低。

SCX25A 具有宽心型指向模式,能够让音响工程师将乐器声音或人声与房间声协调混合。

其他特性包括一个1英寸(25 mm )蒸汽镀金话筒头,小型化的电子元件以及极小的体积。

SCX25A 可以处理超过135 dB 的声压级并提供高达20 dB 的环境噪声抑制。

对于较低输出的选项,SCX25ALO 型号有着150 dB 的声压级限制和4.9 mV/Pa 的灵敏度。

除人声以外,SCX25A 还理想适用于捕捉原声乐器的声音,如钢琴、吉他、颤音琴、木管乐器、铜管乐器、打击乐器、鼓组overhead 、合唱队、管弦乐团和交响乐乐器组。

SCX25A 具有工艺精湛的黄铜制外壳,创新的话筒头悬吊系统,钢制网罩,黑色多层A 级液体表面处理,以及镀金XLR 接头。

产品型号SCX25ALO – 低输出的 SCX25ASCX25AMP – 搭配成对SCX25APS – 钢琴拾音话筒套装提供附件配合 3/8” 话筒架的金属适配器 CASEWOOD – 泡沫内衬木盒 DCLIP - 重型尼龙铸造卡扣夹可选附件APS2 - 两通道48 V 幻象电源。

110 V 可切换为240 V 。

可拆卸电源线。

DFLEX -双轴鼓框安装夹,带超宽蝶形夹。

STANDKD -短基座支架,带伸缩臂臂架。

SMT25 -外观低调的防震架带尼龙线和指旋螺丝用于定位。

PD133 - 可选的两层防喷网罩用于控制爆破音。

ZXRE4041FN8TC中文资料(Diodes)中文数据手册「EasyDatasheet - 矽搜」

IR =8 Ato 100 A F = 10Hz到10kHz的

1 10 0.2 0.6

60

mV mV

V (rms)

5 4

3

2

反向电流(mA)

1

T A =-40c T O +85C

0 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4

芯片中文手册,看全文,戳

SOT 23微 功 耗 1.225V电 压 基 准

ZXRE4041

说明

该ZXRE4041是一个带隙电路设计

实现精密微功耗电压基准

1.225伏.该装置是在小外形可用 SOT23表面贴装封装,非常适合应用中节省空间是非常 重要的.

SOT23公差可为0.5%,C级 精密应用.卓越的性能 保持在30 A到12毫安工作电流

MIN TYP MAX

IR=100 A

1.214 1.225 1.226 C‡

V

1.208 1.225 1.232 D

1.196 1.225 1.244 E

1.183 1.225 1.257 F

30

A

0.03

12

mA

I 到我 R(min)

R(m ax)

20 75

PPM /℃,

IR=30 Ato 1mA IR =1mAto 12mA

(V) 1.0

R

V 0.5

0 10

(inA) 0 I

10 A 20m A

0

40பைடு நூலகம்

80

时间(s)

瞬态响应

120 140

80 70

60 50 40

翻译(中文)

PeakSwitch™设计指南AN-41应用指南介绍PeakSwitch产品系列是高度集成的单片离线式开关电源IC,它专门针对需要短时间内提供峰值输出功率的电源应用,例如喷墨打印机、音频放大器和DVR。

当负载有峰值功率要求时,其等效开关频率会达到277 kHz,从而可以使用一个较小的变压器。

PeakSwitch具有很多创新的专利技术,比如自适应的开关周期导通时间控制、自适应的流限调整、AC线电压检测及快速AC复位。

这些技术大大简化了设计,同时也缩短了工程设计周期,降低了系统成本,使得整系统具有完善的保护功能及可靠的系统性能。

该系列中的每个产品都在一个硅片上集成了一个高压功率MOSFET及控制器。

内部连接到漏极的高压电流源在启动阶段提供偏置电流,从而省去了外部启动电路元件。

内部振荡器具有频率调制(抖动)特性可以降低EMI。

此外,IC还集成了一些功能用于系统级的保护。

自动重启动功能过载、输出短路及开环故障情况下降低了MOSFET、变压器及输出二极管的功耗,自动恢复迟滞关断功能在出现温度故障时会禁止MOSFET开关。

导通时间延长技术使得电源在低交流输入电压时能够输送更多的功率,同时延长了维持时间。

无论何时出现故障触发了自动重启动,智能的AC线电压检测及欠压保护(UVLO)功能都会将IC关断,并且在AC重新上电后实现很快的复位。

Power Integrations公司的EcoSmart® 技术令使用PeakSwitch产品系列的电源空载功率<300 mW,从而满足各类能效标准要求,比如加州能源委员会(CEC)、欧盟及能源之星的标准。

范围此应用指南用于帮助工程师使用PeakSwitch系列产品设计隔离的AC-DC反激式开关电源。

工程师可以利用本文所述的指导方法快速选择所需的关键元件并完成合适的变压器设计。

为方便起见,本文直接参考了PI Xls变压器设计表格。

该设计表格为PI Expert ™电源设计软件包的一部分。

AD7401A中文资料

7/08—Revision 0: Initial Version

Terminology .................................................................................... 13 Theory of Operation ...................................................................... 14

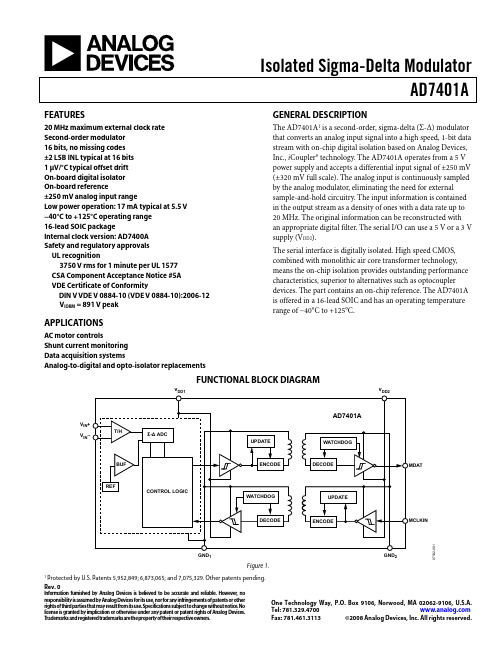

The serial interface is digitally isolated. High speed CMOS, combined with monolithic air core transformer technology, means the on-chip isolation provides outstanding performance characteristics, superior to alternatives such as optocoupler devices. The part contains an on-chip reference. The AD7401A is offered in a 16-lead SOIC and has an operating temperature range of −40°C to +125°C.

APPLICATIONS

GENERAL DESCRIPTION

The AD7401A1 is a second-order, sigma-delta (Σ-Δ) modulator that converts an analog input signal into a high speed, 1-bit data stream with on-chip digital isolation based on Analog Devices, Inc., iCoupler® technology. The AD7401A operates from a 5 V power supply and accepts a differential input signal of ±250 mV (±320 mV full scale). The analog input is continuously sampled by the analog modulator, eliminating the need for external sample-and-hold circuitry. The input information is contained in the output stream as a density of ones with a data rate up to 20 MHz. The original information can be reconstructed with an appropriate digital filter. The serial I/O can use a 5 V or a 3 V supply (VDD2).

泽耀科技 A32-S400A22S1a 产品手册说明书

A32-S400A22S1a 产品手册基于SX126X 带屏蔽盖的433/470/490MHz,156mW,LoRa 扩频,IPEX 接口的射频收发模块版本:Spec_ A32-S400A22S1a _V1.0 日期:2021-05 状态:受控状态LoRa扩频,IPEX接口的射频收发模块 一 、产品概述A32-S400A22S1a是一款433/470/490MHz(中国频段),约156mW,高速,高稳定性,工业级的,集无线收发于一体的射频收发模块。

模块采用了SEMTECH原装SX126X射频芯片,工作在410~525MHz的ISM频段,带有金属屏蔽罩,抗干扰性能强。

该模块发射功率足,频谱特性优异,谐波非常小,频道串扰小,体积小,部分器件达到了军品级标准。

二 、产品特征●SX126X射频芯片●高性能IPEX天线接口和邮票口,传输距离可达5.0km[ 1 ]●超低功耗处理,最低功耗≤1uA●工作频段410~525MHz频率可调,信道间隔可调GFSK、FSK、MSK、GMSK、LORA、OOK调制●256 byte buffer●通信接口4-Pin硬件SPI通信接口推荐速率4Mbps,最大速率可达10Mbps●宽范围空中速率[ 2 ]可调空中速率,0.018-62.5kbps(LORA模式)●功率可调,最大功率约22dBm[ 3 ]●四种工作模式[ 4 ]睡眠模式(sleep down)待机模式(standby)发送模式(send)接收模式(receive)●供电电压范围[ 5 ]2.0V~3.6VDC●发射电流在发射功率为22dbm下,测得的发射电流约为108mA●接收灵敏度低至-148dBm●超小体积,贴片封装19.65*16mm模块重量约1.5gLoRa扩频,IPEX接口的射频收发模块备注:[ 1 ]晴朗空旷,无障碍物干扰;最大功率、高度2m、空中速率2.4kbps[ 2 ]空速越高,传输距离越近;空速越低,传输距离越远。

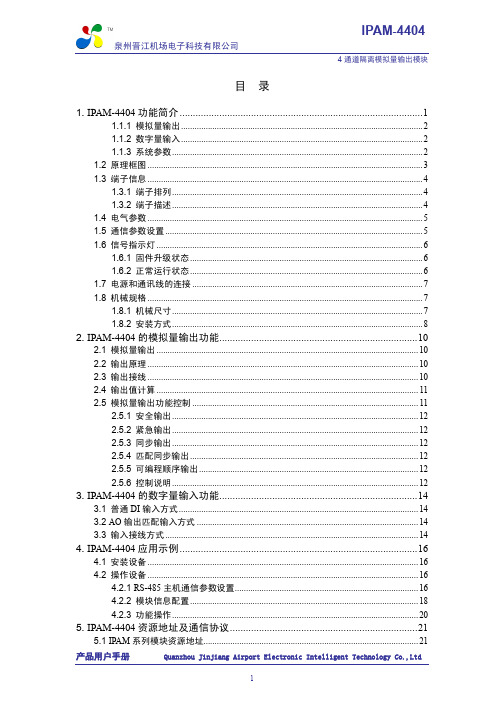

IPAM-4404 输出4路的模拟量 模拟量输出模块 用户手册

5. IPAM-4404 资源地址及通信协议 .......................................................................21

5.1 IPAM 系列模块资源地址................................................................................................ 21 产品用户手册

1.2 1.3

1.4 1.5 1.6

1.7 1.8

2. IPAM-4404 的模拟量输出功能...........................................................................10

2.1 2.2 2.3 2.4 2.5

3. IPAM-4404 的数字量输入功能...........................................................................14

4. IPAM-4404 应用示例 ..........................................................................................16

4.1 安装设备 ......................................................................................................................... 16 4.2 操作设备 ......................................................................................................................... 16 4.2.1 RS-485 主机通信参数设置.................................................................................. 16 4.2.2 模块信息配置 ...................................................................................................... 18 4.2.3 功能操作 .............................................................................................................. 20

安普德科技产品简介

间接认证·PCI

• 安普德科技完成了针对PCI安全标准涉及Wireless技术的标准制定 • Blue Guard技术是安普德科技拥有独立自主知识产权且符合PCI标准的无线安全加密技术 • Blue Guard技术应用于BT53H模组

PCI SSC维护的标准 PCI数据安全标准 ---- PCI-DSS PCI支付应用数据安全标准 ---- PCI PA-DSS PCI PIN传输安全 ---- PCI PTS PCI点对点加密 ---- PCI P2PE PCI取证调查程序 ---- PC

ACC1340是安普德科技针对 IOT 市场开发的一款高性能 WiFi 射频芯片产品,支持802.11 a/b/g/n,支持WiFi Direct、 Soft AP以及STA/AP 模式共存。具有高速性、稳定性和传输距 离远等特点,可以高度匹配音视频流媒体传输。2016 Q4已量 产。

安普德产品 • 芯片

• 2.4G/5G 双模Wi-Fi 芯片

• 协议栈

• 可支持Linux 和嵌入式 RTOS系统 • 自有Wi-Fi协议栈 • 自有蓝牙协议栈 • Apple Air Play协议栈 • Amazon Alexa协议栈

• 嵌入式音频处理软件

• SRI-独有的智能语音唤醒功能 • 独有的回声消除&降噪功能 • 自有Sonic ART音频技术 • 支持音频压缩 • 独有的Blue guard无线加密技术

26.9mm x 15.2mm

WiFi特性: • 支持802.11b/g/n • 支持2.4GHz和5GHz双频段 • 支持WiFi Direct、Soft AP和STA/AP 模式共存 • 支持WiFi音、视频传输

蓝牙特性: • TI CC2564双模蓝牙方案 • 支持蓝牙4.1版本,可实现经典蓝牙与BLE同时传输 • 可升级至蓝牙4.2版本,提升安全加密特性 • 支持蓝牙音、视频传输

AD404M41RLA-5资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SURFACE MOUNT DISPLAY

APPSA04-41SGWA SUPER BRIGHT GREEN

Features

!0.4

Description

The Super Bright Green source color devices are made with Gallium Phosphide Green Light Emitting Diode.

PAGE: 3 OF 5

元器件交易网

APPSA04-41SGWA SMT Reflow Soldering Instructions

Number of reflow process shall be less than 2 times and cooling process to normal temperature is required between first and second soldering process.

Spectral Line Half-width Super Bright Green Capacitance Forward Voltage Reverse Current Super Bright Green Super Bright Green Super Bright Green

Absolute Maximum Ratings at TA=25°C °

PAGE: 2 OF 5

元器件交易网

Super Bright Green

APPSA04-41SGWA

SPEC NO: DSAB3091 APPROVED : J. Lu

REV NO: V.3 CHECKED : Joe Lee

DATE:MAR/31/2003 DRAWN:Y.H.LI

P ar am et er Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating/Storage Temperature

Note: 1. 1/10 Duty Cycle, 0.1ms Pulse Width.

Recommended Soldering Pattern (Units : mm)

SPEC NO: DSAB3091 APPROVED : J. Lu

REV NO: V.3 CHECKED : Joe Lee

DATE:MAR/31/2003 DRAWN:Y.H.LI

PAGE: 4 OF 5

元器件交易网

INCH CHARACTER HEIGHT. CURRENT OPERATION. CONTRAST AND LIGHT OUTPUT. MOUNTING ON P.C. BOARDS OR SOCKETS. FOR LUMINOUS INTENSITY. RUGGED.

!LOW ! HIGH

! EASY

° Electrical / Optical Characteristics at TA=25°C

Sy m b o l λpeak λD ∆λ1/2 C VF IR P ar am et er Peak Wavelength Dominate Wavelength D ev i c e Super Bright Green Super Bright Green Ty p . 565 568 30 15 2.2 2.5 10 Max . Un its nm nm nm pF V uA Tes t Co n d it io n s I F =20mA I F =20mA I F =20mA VF=0V;f=1MHz I F =20mA V R = 5V

!CATEGORIZED

!MECHANICALLY ! GRAY

FACE, WHITE SEGMENT. : 800PCS / REEL.

! PACKAGE

Package Dimensions & Internal Circuit Diagram

D i g i t a l l y s i

Notes: 1. All dimensions are in millimeters (inches), Tolerance is ±0.25(0.01")unless otherwise noted. 2. Specifications are subject to change without notice.

Tape Specifications (Units : mm)

SPEC NO: DSAB3091 APPROVED : J. Lu

REV NO: V.3 CHECKED : Joe Lee

DATE:MAR/31/2003 DRAWN:Y.H.LI

PAGE: 5 OF 5

Su p er B r ig h t Gr een 105 25 140 5 -40°C To +85°C

Un its mW mA mA V

SPEC NO: DSAB3091 APPROVED : J. Lu

ቤተ መጻሕፍቲ ባይዱ

REV NO: V.3 CHECKED : Joe Lee

DATE:MAR/31/2003 DRAWN:Y.H.LI

SPEC NO: DSAB3091 APPROVED : J. Lu

REV NO: V.3 CHECKED : Joe Lee

DATE:MAR/31/2003 DRAWN:Y.H.LI

PAGE: 1 OF 5

元器件交易网

Selection Guide

P ar t N o . Dic e L en s Ty p e Iv (u c d ) @ 10 m A Min . APPSA04-41SGWA SUPER BRIGHT GREEN(GaP) WHITE DIFFUSED 1900 Ty p . 7500 Common Anode,Rt. Hand Decimal D es c r i p t i o n