一种LED数码管显示控制器的VHDL设计

LED显示程序设计实验

实验二LED数码管驱动显示程序实验一、实验目的1、初步学习和了解VHDL语言编程方式2、学习和掌握七段数码显示译码器的设计方法3、学习和掌握VHDL的多层设计方法二、实验要求1、根据硬件设计的思维方式,编制LED七段码的显示程序2、要求是一位LED以定位方式显示3、完成LED七段码波形分析的显示功能4、在EDA实验箱上按要求显示三、实验设备1、计算机一台2、EDA——Ⅳ实验箱一台四、实验原理1、七段码是用一种纯组合的逻辑电路,通常是用小型专用的IC门电路组成,数字输入与输出表达均未16进制,处理一般较复杂,而用FPGA/CPLD来实现较为简单。

2、七段码输入与输出的原理与真值表关系。

(a)输入:七段码输入为四个输入信号,用来表示为“0000”到“1111”,即表示为十六进制的“0”到“F”。

(b)输出:七段码输出为七个输出信号,分别用“A、B、C、D、E、F、G”七个符号来表示。

一般规定,输出信号为“1”时,它所控制的发光二极管为点亮状态,输出信号为“0”时,它所控制的发光二极管为熄灭状。

本实验使用的七段数码管为共阴极组,其电路如图2.1所示。

图2.1 共阴极数码管及其电路(c)输入与输关系为四位二进制代码组成十六进制代码,将其代码显示,其对应关系如表2.1所示。

(d)显示方式是通过选位的方式进行,是将FPGA/CPLD的三位二进制的信号输出,通过外部三——八译码器硬件电路,选中一路LED信号为输出,故选择一位LED数码管显示,本实验是采取选相应的一个指定位置进行LED显示。

3、输入是通过外部的四个按键操作而组成一位十六进制。

其连接到FPGA/CPLD的对应的引脚上,需进行引脚分配。

4、编写译码程序,生成底层组件,组合成底层文件。

表2-1 七段字符显示真值表五、实验步骤1、 在D 盘建立自己的文件目录,D: \ EX \ Z04** \ you*\ex*;2、 在Max+Pluse Ⅱ的界面下,自己的文件目录下,建立项目文件 File \ Project \ 文件名A ;3、 在自己的文件目录下,建立文本文件 File \ New \ 文件名B.vhd ;4、 保存此文件并划归到项目文件内, File \ Project \ Set Project current File ,其中文本文件名B 必须和实体名一致;5、 输入程序,保存文件“文件名B.vhd ”,File \ Save As “文件名B.vhd ”(注意后缀,如保存默认文件名时,其后缀通常为“*.tdf ”文件,必须删除后缀为“*.tdf ”文件名;6、 单击编译器快捷方式按钮,对文本文件进行编译,观察是否有原则错误;7、 如有修改则修改程序中错误,若无错误则可做以下工作; 8、 建立底层器件的封装,File \ Create Default Symbol ;9、 建立图形文件,File \ New \ 文件名C.gdf 并化归到项目内。

基于VHDL的数码显示驱动器的设计

2 0 1 3年第 2期

朱志平 : 基于V H D L的数码 显示驱动 器的设计

表 1 二 一十进制译码器的真值表

・ 2 7・

根据真值表中输入、 输 出信号的变化关系 , 我们可以用硬件描述语言编写出满足数码显示驱动所需要 的代 码程 序 .

图. 这种设计方法 的优点就是使用综合工具对电路整体结构先进行组合优化 、 编译 , 删繁取 真 , 再利用仿 真工具对其进行 波 形仿真 , 检验 电路 的正确性和可靠性. 通过这样 的设计方式 , 设计人员无需多长时间 , 就能设计 出性能稳定 、 运行可靠 、 满足

实际需求的优质电路 .

数码显示 已在整个工农业生产、 航空业 、 交通运输 、 医疗卫生、 仪器仪表以及军民融合技术产业中有了 广泛的用途… , 给人们的视觉带来 了不可置疑的效果, 是现代社会发展过程中不可或缺的部分. 数码显示 驱 动 的控制方 式通 常情 况下可 分为 两类 J : 一 是 直接 利 用微 处 理 器 以静 态 或 动态 扫 描 方式 实 现 ; 二 是 利

X : out

—

一 一一四输入

s t dl o g i c

_ —

v e c t o r ( 6 d o w n t o 0 ) ) ; 一一一 七输出

e n d D P: a r c h i t e c t u r e b e h a v e o f DP i s b e g i n wi t h d s e l e c t

L I B RAC 1 1 6 4. ALL;

— 一

e n t i t y DP i s

p o r t ( d :i n s t d _ l o g i c _ v e c t o r ( 3 d o w n t o 0 ) ;

项目六 数码管显示译码器的VHDL设计

四、项目实施——1. QuartusⅡ VHDL设计输入法

(3) 项目编译

分析综合

点击Quartus Ⅱ软件工具条上的快捷按钮 进行分析综合。

,对抢答器工程

根据提示信息,处理错误,直至无误为止。

四、项目实施——1. QuartusⅡ VHDL设计输入法

四、项目实施

硬件平台准备

微机一台(Windows XP系统、安装好 Quartus Ⅱ5.0等相关软件)

EDA学习开发板一块 USB电源线一条 ISP下载线一条。

四、项目实施——1. QuartusⅡ VHDL设计输入法

(1) 创建工程

在D:\altera\Quartus50\example\seg7下建立项目seg7 选择EPM240T100C5作为目标器件

三、项目分析

VHDL源程序

--****************************************************** --seg7.vhd library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; --********************************************** entity seg7 is

输入端 ABCD 0000 0001 0010 0011 0100 0101 0110 0111

输出端 abcdefgh 11111100 01100000 11110010 11110010 01100110 10110110 10111110 11100000

(VHDL实验报告)数码管显示(一位数码管显示0-9,八位数码管显示学号后八位)

(1)一位数码管显示0-9:

(2)八位数码管显示学号后八位:

9、用下载电缆通过JTAG 口将对应的sof 文件加载到FPGA 中。观察实验 结果是否与自己的编程思想一致。

六、实验现象及结果 以设计的参考示例为例,当设计文件加载到目标器件后,将数字

四、 实验内容

本实验要求完成的任务是在时钟信号的作用下,使一位数码管显示输出 0-9,使八位数码管显示学号后八位。在实验中时,数字时钟选择 1KHZ作为 扫描时钟,实验箱中的拨动开关与 FPGA 的接口电路,以及拨动开关 FPGA 的

管脚连接在实验一中都做了详细说明,这里不在赘述。以下两图分别是数码 管显示模块的电路原理和其数码管的输入与FPGA的管脚连接表。

电子科技大学成都学院学院

标准实验报告

(实验)课程名称 数字电路 EDA 设计与应用

姓名 乱弹的枇杷 学号 专业 指导教师

一、 实验名称 数码管显示(一位数码管显示 0-9,八位数码管显示学号

后八位)

二、 实验目的 1、了解数码管的工作原理。 2、学习七段数码管显示译码器的设计。 3、掌握 VHDL 的 CASE 语句及多层次设计方法。

七段码管位选输入信号 七段码管位选输入信号 七段码管位选输入信号

五、 实验步骤

1、打开 QUARTUSII 软件,新建一个工程。 2、建完工程之后,再新建一个VHDL File,打开VHDL 编辑器对话框。 3、按照实验原理和自己的想法,在VHDL 编辑窗口编写VHDL 程序。其 程序如下所示:

(1)一位数码管显示0-9:

(2)八位数码管显示学号后八位:

vhdl按键控制数码管显示

vhdl按键控制数码管显示

在传统的硬件电路设计中,主要的设计文件是电路原理图,而采用HDL 设计系统硬件电路时主要使用HDL编写源程序。

VHDL的主要优点有:

(1)VHDL支持自顶至下的和基于库的设计方法,而且支持同步电路、异步电路、现场可编程门阵列器件FPGA(field programmable gate array)以及其他随机电路的设计。

(2)VHDL语句的行为描述能力和程序结构决定了它具有支持大规模设计的分解和已有设计再利用的功能,它支持系统的数学模型直到门级电路的描述,并且高层次的行为描述与低层次的门级电路描述、结构描述可以混合使用。

(3)VHDL的硬件描述与具体的工艺技术和硬件结构无关,当门级或门级以上的描述通过仿真检验后,再利用相应的工具将设计映射成不同的工艺,因此电路的设计与工艺的改变是相互独立的。

彼此的改变不会产生不良影响,并且VHDL硬件描述语言的实现目标器件的选择范围广泛,可使用各系列的CPLD、FPGA及各种门阵列器件。

应用VHDL语言设计A_D和LED显示控制器

应用 VHDL 语言设计 A/ D 和 LED 显示控制器

De signing A/ D and LED Display Controller by Using VHDL Language

李 锋 卢 佩 费春国 刘成臣

(天津科技大学自动化系 ,天津 300222)

0 引言

在工业测量和控制中 ,A/ D 器件和 LED 显示是不 可缺少的 。LED 显示器的驱动多采用通用的 TTL 或 CMOS 集成电路 ,如 8279 ,MAX7219 等 。传统的 A/ D 转 换器件的控制多采用单片机来完成 ,但在一些特殊应 用场合 ,例如高速 、强电磁干扰等恶劣条件下 ,单片机 的速度和可靠性往往满足不了系统的要求 。VHDL 语 言作为 IEEE 的标准 ,是一种功能强大 、通用的硬件描 述语言 ,得到各种 EDA 工具的支持 。本文将介绍利用 VHDL 语言 采 用 自 顶 向 下 的 方 法 在 一 片 ALTERA 的 CPLD( EPM7160SLC84 - 10) 上设计实现一种高速 A/ D 和 LED 显示控制器 。

输入的是内部 ram 的地址 ;当 a0 是 0 时 db - in 输入的 是要显示的数据 。Data - out 进程以 clk 为敏感信号 , 取出 ram 中的数据作为段码输出 : Scan - out 进程同样 以 clk 为敏感信号通过内部的计数器控制输出扫描 码 。Scan - out 进程的 VHDL 代码如下 :

41

《自动化仪表》第 24 卷第 6 期 2003 年 6 月

② 通过 EDA 软件采用自顶向下的设计方法对系 统进行设计缩短了开发周期 ,大大提高了设计效率 ;

VHDL语言实例

VHDL 语言实例例1:设计一七段显示译码器,用它来驱动七段发光管 到9和字母A 到F 。

LED 显示数码管为共阳极。

LIBRARY ieee;USE ieee.std_logic_1164.all; ENTITY HEX2LED ISP ORT(LED : OUT std_logic_vector(6 TO图例1七段显示译码器实体ARCHITECTURE HEX2LED_arc OF HEX2LED IS BEGIN--HEX-TO-SEVEN-SEGMENT DECODER --SEGMENT ENCODING--5 | |1-- — — — — --4 | |20);HEX2LEDHEX :IN std_logic_vector(3 DOWNTO HEXES. . 0]"0) );LED 显示十六进制数字0ENDHEX2LED;WITH HEX SELECTLED<= "1111001" when "0001","0100100" when "0010","0110000" when "0011","0011001" when "0100","0010010" when "0101","0000010" when "0110","1111000" when "0111","0000000" when "1000","0010000" when "1001","0001000" when "1010","0000011" when "1011","1000110" when "1100","0100001" when "1101","0000110" when "1110","0001110" when "1111","1000000" when others;END HEX2LED_arc;例 2 :设计一个八选一数据选择器1)s 是通道选择信号,d0,d1,d2,d3,d4,d5,d6,d7 数据输入out1 是数据输出ENTITY sels ISP ORT(d0,d1,d2,d3,d4,d5,d6,d7:IN BIT;s :INTEGERRANGE0 TO 7;END sels;ARCHITECTURE sels_arc OF sels IS BEGINWITH s SELECTout1 <= d0 WHEN 0, d1 WHEN 1, d2 WHEN 2, d3 WHEN 3,d4 WHEN 4,d5 WHEN 5, d6 WHEN 6, d7 WHEN 7;END sels_arc;LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux8 ISPORT(IO,I1,I2,I3,I4,I5,I6,I7,A,B,C:IN std_logic; END mux8;sels图例2 (a)八选一数据选择器实体图例2 (b)八选一数据选择器实体out1 :OUT BIT);2)A,B,C 是通道选择信号,据输出10,11,12,13,14,15,16,17数据输入 Q 是数Q :OUT std_logic);ARCHITECTURE mux8_arc OF mux8 ISSIGNAL sel :INTEGER ;BEGINQ <= 10 AFTER 10 ns WHEN sel= 0 ELSE11 AFTER 10 ns WHEN sel= 1 ELSE 12 AFTER 10 ns WHEN sel= 2 ELSE 13 AFTER 10 ns WHEN sel= 3 ELSE 14 AFTER 10 ns WHEN sel= 4 ELSE 15 AFTER 10 ns WHEN sel= 5 ELSE 16 AFTER 10 ns WHEN sel= 6 ELSE 17 AFTER 10 ns ;sel <= 0 WHEN A=‘ 0' AND B= ‘ 0' AND C= ‘ 0' ELSE1 WHEN A= '1' AND B= ‘ 0'AND C='0' ELSE2 WHEN A='0' AND B=‘1' AND C= '0' ELSE3 WHEN A='1' AND B=‘1' AND C='0' ELSE4 WHEN A='0' AND B=‘ 0'AND C= '1' ELSE5 WHEN A='1' AND B=‘ 0'AND C= '1' ELSE6 WHEN A='0' AND B=‘ 0'AND C= '1' ELSE7;END mux8_arc;例3:设计一 D 触发器 d 是输入端,clk 是时钟信号控制端,q 是触发器的输出端。

基于VHDL语言的数码管闪烁控制的实现

在上位机调试时 , 最重要 的是顺序的处理数据 , 因为

不 同的数据在转化 时会乘 以不同的权 ,所 以如果数据顺

序不正确 , 将得不到预期的效果。当输入一个方波时 , 现

象如 图 7 示 。 所

[ 刘皖, 4 ] 何道君’ 谭明. G F A设计与应用[ ] P M. 北京: 清华大学

出版社, 0 , . 2 66 0 0

[赵宇 玲. 于 F G 5 ] 基 P A的信号采集 与处理 系统设计 与实

现[】 D. 南京: 京理工大学, 0 ,: — 3 南 2 8 2 2. 0 62

1 4

_

w e ” 1” > au =h m ( ; h n 0 = do t su g ) 1 < 3

w e ”0 ” > au< su g ) h n 10= do t=h m ( ; 4 w e ”0 ” > au =h m ( ; h n 1 1= do t su g ) < 5 w e ” ” > au =h m ( ; h n 10= do t su g ) 1 < 6

基 于 V D 语 言的数码管闪烁控制的实现 HL

电子 质 量 ( 1第 0 期) 22 7 0

为数码管闪烁的基准时钟 , 用于控制数字 闪烁 的快慢 , 从

而达到调速的 目的。

S 4:

W HEN 3 >F S = LOW ER2 = 3CURRENT S < FF ; TAT : E<

的 显示 。

END CAS E; END I F;

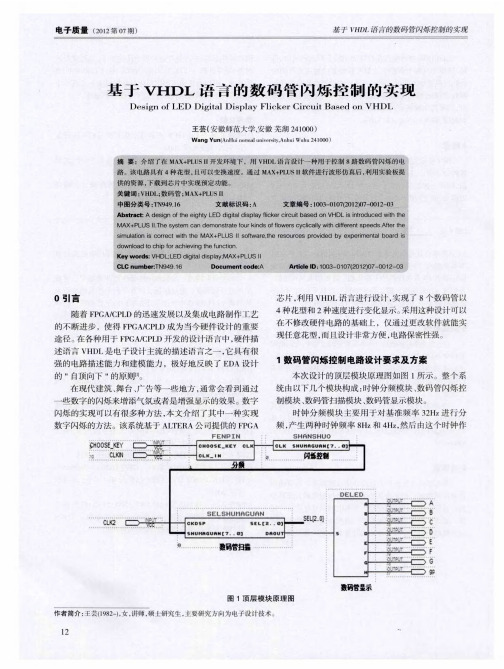

2各模块设计

21分频模块 。 该模块主要用 V D H L语言实现四分频 和八分频。设

计时主要用 到计数器。主要代码如下 :

I I I GE C K I )HEN FR SNG ED fL NT

基于VHDL的彩灯控制器的设计

基于VHDL的彩灯控制器的设计作者:尚肖肖刘言实来源:《科技视界》2017年第13期【摘要】彩灯对于美化、亮化城市有着重要的作用。

而彩灯控制器作为彩灯的一个重要部分更是备受关注。

传统的彩灯控制电路一般是由数字电路组成,因此结构复杂、成本较高且功率损耗大,而且电路的老化以及机械元件的变化将会导致触发电路电源开关的不稳定,最终使得彩灯经常发生故障。

本文设计了一种基于VHDL的彩灯控制器。

与传统的设计相比,该设计具有速度快、体积小,重量轻的优点。

【关键词】彩灯控制器;VHDL0 引言彩灯对于美化、亮化城市有着不可轻视的重要工作。

因此作为城市装饰的彩灯需求量越来越大,人们此时开始关注彩灯的花型、创意等元素,而彩灯控制器作为彩灯的一个重要部分更是备受关注。

基于传统的机械和纯电路的控制方式有着十分严重的弊端,传统的彩灯控制电路一般是由数字电路组成,这种彩灯控制器电路结构复杂、成本高、损耗大,电路一旦老化以及机械元件的变化将导致触发电路电源开关不稳定,使得彩灯经常发生故障。

本设计是基于VHDL的彩灯控制器设计,实现对LED彩灯的控制。

主要是以FPGA的最小系统作为主控核心与发光二极管、电阻、开关等组成电路,利用软件编译实现彩灯花型变换的效果,可以有效地弥补原来传统的彩灯控制电路的缺点和不足。

1 硬件设计彩灯控制器的硬件部分可分为两个模块:主控核心和外围电路。

通过这两个模块就可以实现整个彩灯控制器的设计。

本着简化设计、缩小设计成本的想法,本设计的彩灯控制器的主控核心选择的是Altera公司的FPGA最小系统它搭载的是Cyclone Ⅱ系列的芯片EP2C5Q208C8N。

外围电路分为LED显示电路、开关控制电路两个部分。

LED显示模块电路为8个LED发光二极管,8个300欧姆的电阻,电阻一端接排针,一端与发光二极管相连,发光二极管另一端直接接地。

开关控制电路部分电路由四个四脚轻触无锁开关和四个10K欧姆的电子组成,开关一脚接地对脚接电阻,其余两脚悬空处理,电阻的另一端接上另一个排针即可。

基于VHDL语言的数码管闪烁控制的实现

基于VHDL语言的数码管闪烁控制的实现王芸【期刊名称】《电子质量》【年(卷),期】2012(000)007【摘要】介绍了在MAX+PLUSⅡ开发环境下,用VHDL语言设计一种用于控制8路数码管闪烁的电路。

该电路具有4种花型,且可以变换速度。

通过MAX+PLUSⅡ软件进行波形仿真后,利用实验板提供的资源,下载到芯片中实现预定功能。

%A design of the eighty LED digital display flicker circuit based on VHDL is introduced with the MAX+PLUS II.The system can demonstrate four kinds of flowers cyclically with different speeds.After the simulation is correct with the MAX+PLUS II software,the resources provided by experimental board is download to chip for achieving the function.【总页数】3页(P12-14)【作者】王芸【作者单位】安徽师范大学,安徽芜湖241000【正文语种】中文【中图分类】TN949.16【相关文献】1.VHDL语言实现FIFO存储控制 [J], 郑波祥;陈笑;齐晋2.控制系统中用数码管显示实时数据的实现方法 [J], 宋洪柱3.基于VHDL语言的交通信号控制器的设计与实现 [J], 林涛4.基于S7-200 smart型PLC的彩灯闪烁控制系统实现 [J], 张松宇;胡春芳5.汽车车灯控制系统的VHDL语言实现 [J], 郑应民因版权原因,仅展示原文概要,查看原文内容请购买。

基于VHDL的LCD控制器的设计与实现

第2期2009年2月工矿自动化Industr y and M ine AutomationNo.2 Feb.2009收稿日期:2008-10-29作者简介:周 雷(1985-),男,中国矿业大学信号与信息处理专业2006级硕士研究生,研究方向为EDA 技术应用。

E 2mail:zhoul35@文章编号:1671-251X(2009)02-0093-02基于VHDL 的LCD 控制器的设计与实现周 雷, 付慧生, 熊建伟(中国矿业大学信电学院,江苏徐州 221008)摘要:文章介绍了基于VH DL 语言状态机的LCD 控制器的设计方法,说明了字符型液晶显示器显示的基本原理,给出了显示字符的方法及实现LCD 控制器的部分VH DL 语言程序。

基于VH DL 设计的LCD 控制器具有很好的移植性,稍加改动就可以应用到不同场合。

关键词:LCD 控制器;VH DL;字符显示 中图分类号:TP312 文献标识码:B 参考文献:[1] 高丽珍.新型矿用本质安全型电源的设计与研究[J].机械工程与自动化,2006(3):125~127.[2] 杨智敏,侯传教,刘 霞.单片式开关稳压器LM2576-ADJ 及其应用[J ].移动电源与车辆,2004(1):34~36.[3] 张乃国.电源技术[M].北京:中国电力出版社,1998.[4] 崔保春,王 聪,卢其威,等.矿用本质安全开关电源的研究[J].中国煤炭,2006(3):49~51.0 引言传统的LCD 控制器通常由单片机组成,具有集成电路复杂、移植性差等缺点。

随着可编程逻辑器件的发展,以FPGA(现场可编程门阵列)为平台,采用硬件编程语言来实现LCD 控制器,具有易于集成到片上系统、方便修改、适应不同液晶显示器等优点。

本文设计的LCD 控制器是一种基于FPGA 的液晶显示控制器,它采用VH DL 语言实现控制器的编程设计,这种设计方法稍加改动就可以应用于常见的LCD 接口电路中[1]。

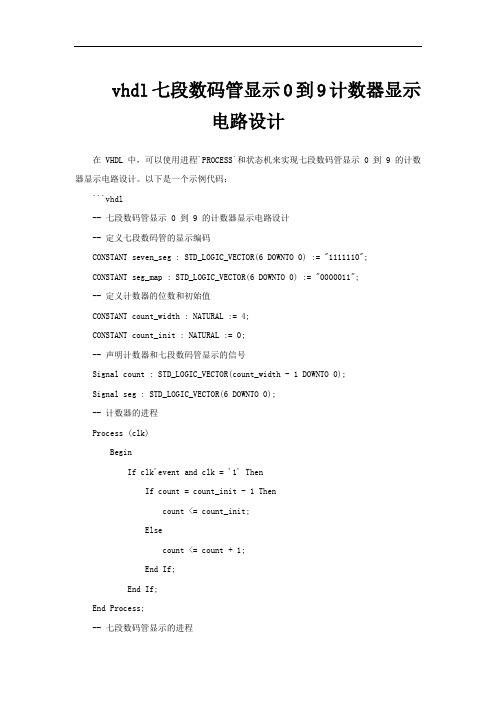

vhdl七段数码管显示0到9计数器显示电路设计

vhdl七段数码管显示0到9计数器显示电路设计在 VHDL 中,可以使用进程`PROCESS`和状态机来实现七段数码管显示 0 到 9 的计数器显示电路设计。

以下是一个示例代码:```vhdl-- 七段数码管显示 0 到 9 的计数器显示电路设计-- 定义七段数码管的显示编码CONSTANT seven_seg : STD_LOGIC_VECTOR(6 DOWNTO 0) := "1111110";CONSTANT seg_map : STD_LOGIC_VECTOR(6 DOWNTO 0) := "0000011";-- 定义计数器的位数和初始值CONSTANT count_width : NATURAL := 4;CONSTANT count_init : NATURAL := 0;-- 声明计数器和七段数码管显示的信号Signal count : STD_LOGIC_VECTOR(count_width - 1 DOWNTO 0);Signal seg : STD_LOGIC_VECTOR(6 DOWNTO 0);-- 计数器的进程Process (clk)BeginIf clk'event and clk = '1' ThenIf count = count_init - 1 Thencount <= count_init;Elsecount <= count + 1;End If;End If;End Process;-- 七段数码管显示的进程Process (count)BeginCase count IsWhen count_init - 1 => seg <= seven_seg;When count_init => seg <= seg_map;When count_init + 1 => seg <= seven_seg;When count_init + 2 => seg <= seg_map;When count_init + 3 => seg <= seven_seg;When count_init + 4 => seg <= seg_map;When count_init + 5 => seg <= seven_seg;When count_init + 6 => seg <= seg_map;When count_init + 7 => seg <= seven_seg;When count_init + 8 => seg <= seg_map;When count_init + 9 => seg <= seven_seg;When Others => seg <= seven_seg;End Case;End Process;-- 连接计数器和七段数码管显示的信号Output seg;```上述代码中,使用了两个进程`PROCESS`来实现计数器和七段数码管的显示。

数码管vhdl设计

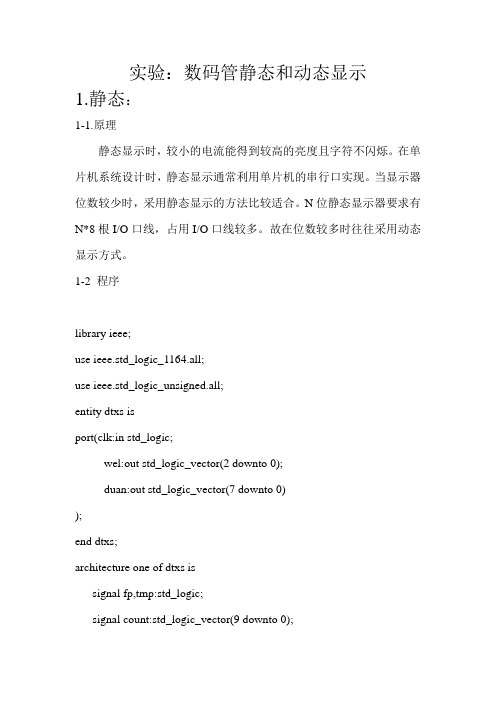

实验:数码管静态和动态显示1.静态:1-1.原理静态显示时,较小的电流能得到较高的亮度且字符不闪烁。

在单片机系统设计时,静态显示通常利用单片机的串行口实现。

当显示器位数较少时,采用静态显示的方法比较适合。

N位静态显示器要求有N*8根I/O口线,占用I/O口线较多。

故在位数较多时往往采用动态显示方式。

1-2 程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dtxs isport(clk:in std_logic;wel:out std_logic_vector(2 downto 0);duan:out std_logic_vector(7 downto 0));end dtxs;architecture one of dtxs issignal fp,tmp:std_logic;signal count:std_logic_vector(9 downto 0);signal sl:std_logic_vector(2 downto 0); beginprocess(clk)beginif(clk'event and clk='1')thenif(count="1111100111")thencount<=(others=>'0');tmp<=not tmp;elsecount<=count+1;end if;end if;fp<=tmp;end process;process(fp)beginif(fp'event and fp='1')thenif(sl="111")thensl<="000";elsesl<=sl+1;end if;end if;end process;wel<=sl;process(sl)begincase sl iswhen"111"=>duan<="00111111";when"110"=>duan<="01100110";when"101"=>duan<="01011011";when"100"=>duan<="01111101";when"011"=>duan<="00000110";when"010"=>duan<="01101101";when"001"=>duan<="01001111";when"000"=>duan<="00000111";when others=>null;end case;end process;end one;1-3.仿真图注意事项:注意分频模块,同时,位选由三个位选择控制;2.动态:1-1.原理所谓动态显示就是一位一位地轮流点亮显示器的各个位(扫描〕,对于显示器的每一位来说,每隔一段时间点亮一次。

vhdl共阴极数码显示电路

vhdl共阴极数码显示电路VHDL共阴极数码显示电路数码显示器是一种常见的电子显示设备,它能够将数字信息以可视化的方式呈现给用户。

VHDL共阴极数码显示电路是一种使用VHDL 语言设计的共阴极数码显示器电路。

本文将详细介绍VHDL共阴极数码显示电路的原理和设计过程。

共阴极数码显示器是一种常见的数码显示器类型,它由多个共阴极数码管组成。

每个共阴极数码管由7个LED灯组成,可显示0到9的数字。

共阴极数码管的工作原理是,当给定特定的电压时,相应的LED灯会点亮,形成所需的数字。

其中,共阴极表示数码管的阴极端口是连接在一起的,而阳极端口则是分别连接的。

VHDL语言是一种用于描述数字系统的硬件描述语言,它可以对数字电路进行建模和仿真。

使用VHDL语言进行设计,可以使得电路的功能更加清晰明了,并且可以方便地进行验证和修改。

在设计VHDL共阴极数码显示电路时,首先需要定义输入和输出信号。

输入信号通常包括一个4位的二进制数,用于表示要显示的数字。

输出信号是连接到共阴极数码管的引脚,用于控制数码管的亮灭。

接下来,需要编写VHDL代码来描述共阴极数码显示电路的行为。

代码主要包括两部分:数码管驱动模块和顶层模块。

数码管驱动模块是用来控制数码管显示的核心模块。

它根据输入的二进制数,将对应的数字显示在数码管上。

在这个模块中,需要定义一个包含数字对应的真值表,以便根据输入的二进制数选择对应的数字。

顶层模块是将数码管驱动模块和输入输出信号连接起来的模块。

它负责接收输入信号,将其传递给数码管驱动模块,并将输出信号连接到数码管的引脚上。

设计完成后,可以使用VHDL仿真工具对设计的电路进行验证。

通过输入不同的二进制数,观察数码管上显示的数字是否与预期相符。

如果一切正常,可以将设计的电路下载到FPGA或其他可编程逻辑器件中进行实际的硬件测试。

VHDL共阴极数码显示电路具有简单、可靠、易于实现等优点。

它在数字电子系统中得到广泛应用,例如计数器、时钟、测量仪器等。

开关控制数码管的VHDL程序的设计与实现

开关控制数码管的VHDL程序的设计与实现摘要本设计是利用所学过的电子线路课程知识,利用Quartus II软件,结合所学知识设计一个,具有使用开关控制数码管功能。

文章分析了整个电路的工作原理,还说明了各程序模块的功能,并对最终结果就行了总结。

通过此次设计加深了对课程的理解,掌握了一些基本逻辑器件的功能和使用方法。

本设计通过软件设计电路,方便快捷,避免了硬件布线的繁琐,提高了效率。

关键词开关;数码管; VHDL程序Abstract Th is design is to use the learned electronic circuit course knowledge, use Quartus II software, combined with the design of a knowledge, which has the function of digital switch control tube. This paper analyzes the whole electric circuit principle of work, also that the apps modules of the system, and the final results will do summary. Through this design deepened to the understanding of the course and master the basic logic devices of some function and use. This design convenient and quick, avoid the hardware wiring trival, improve efficiency through the software design circuit.Keyword Switch;Digital tube;VHDL program1 前言VHDL是一种应用广泛的硬件描述语言,设计者可以通过它编写代码,通过模拟器仿真验证其功能,完成逻辑综合与逻辑优化,最后通过下载到相应的可编程逻辑器件(如FPGA)中来实现设计。

VHDL 彩灯控制电路的设计与实现

VHDL 彩灯控制电路的设计与实现一、实验目的1.进一步了解时序电路设计方法2.熟悉状态机的设计方法二、实验所用仪器及元器件1、计算机2、直流稳压电源3、数字系统与逻辑设计实验开发板三、实验内容用VHDL语言设计并实现一个彩灯控制(8个发光二极管)电路,仿真并下载验证其功能。

彩灯有两种工作模式,可以通过拨码开关或者按键进行切换。

(1)单点移动模式:一个点在8个发光二极管上来回的亮(2)幕布模式:从中间两个点,同时向两边一次点亮直至全亮,然后再向中间点灭,依次往复四、设计思路与过程根据实验要求,需要实现在拨码开关或者按键的控制下实现两种状态机的转换。

首先,确定输入输出变量:输入:拨码开关a:实现两种模式的转换;时钟clk::提供有效时钟沿;输出:8维向量b:连接8个发光二极管。

其次,确定电路工作状态因为在单点移动模式和幕布模式都要满足灯来回亮,共计工作状态23种:a=0时,实现单点移动模式,工作状态有s0~s13共14种状态;a=1时,实现幕布模式,工作状态有s14~s22共9种状态。

再次,大致确定VHDL编写思路确定好输入输出变量和电路状态后,考虑结构体中需要的进程需要完成以下两个功能——分频和实现状态机,故我使用了4个进程。

其功能分别如下:P0:分频,将实验板上提供的50MHz的时钟信号,即输入clk分为频率为1Hz的低频信号clk_out,以便观察现象;P1:为当前状态储存的下一状态;P2:当时钟有效沿到来时,当前状态转入下一状态;(P1、P2共同实现状态机的转换)P3:控制LED灯的输出,达到实验要求效果具体程序如下。

五、VHDL程序library ieee;use ieee.std_logic_1164.all;entity light isport (clk: in std_logic;a: in std_logic;b:out std_logic_vector(7 downto 0));end light;architecture light_1 of light istype state_type is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16,s17,s18,s19,s20,s21,s22); signal current_state,next_state: state_type;signal clk_out:std_logic;signal tmp: integer range 0 to ;beginp0:process(clk) --分频器,把50MHz的时钟clk分为1Hz的时钟clk_out beginif clk'event and clk='1' thenif tmp= thentmp<=0;elsetmp<=tmp+1;end if;if tmp= thenclk_out<='1';elseclk_out<='0';end if;end if;end process;p1:process(current_state,a) --当前状态在开关函数a作用下所储存的下一状态begincase current_state iswhen s0=> if(a='0') then next_state<=s1;else next_state<=s14; end if;when s1=> if(a='0') then next_state<=s2;else next_state<=s14; end if;when s2=> if(a='0') then next_state<=s3;else next_state<=s14; end if;when s3=> if(a='0') then next_state<=s4;else next_state<=s14; end if;when s4=> if(a='0') then next_state<=s5;else next_state<=s14; end if;when s5=> if(a='0') then next_state<=s6;else next_state<=s14; end if;- 1 -when s6=> if(a='0') then next_state<=s7;else next_state<=s14; end if;when s7=> if(a='0') then next_state<=s8;else next_state<=s14; end if;when s8=> if(a='0') then next_state<=s9;else next_state<=s14; end if;when s9=> if(a='0') then next_state<=s10;else next_state<=s14; end if;when s10=> if(a='0') then next_state<=s11;else next_state<=s14; end if;when s11=> if(a='0') then next_state<=s12;else next_state<=s14; end if;when s12=> if(a='0') then next_state<=s13;else next_state<=s14; end if;when s13=> if(a='0') then next_state<=s0;else next_state<=s14; end if;when s14=> if(a='1') then next_state<=s15;else next_state<=s0; end if;when s15=> if(a='1') then next_state<=s16;else next_state<=s0; end if;when s16=> if(a='1') then next_state<=s17;else next_state<=s0; end if;when s17=> if(a='1') then next_state<=s18;else next_state<=s0; end if;when s18=> if(a='1') then next_state<=s19;else next_state<=s0; end if;when s19=> if(a='1') then next_state<=s20;else next_state<=s0; end if;when s20=> if(a='1') then next_state<=s21;else next_state<=s0; end if;when s21=> if(a='1') then next_state<=s22;else next_state<=s0; end if;when s22=> if(a='1') then next_state<=s14;else next_state<=s0; end if;end case;end process;p2:process(clk_out) --时钟clk_out作用下的状态转换函数beginif(clk_out'event and clk_out='1') thencurrent_state<=next_state;end if;end process;p3:process(current_state) --当前状态所对应的输出函数begincase current_state is- 2 -when s0=>b<="";when s1=>b<="";when s2=>b<="";when s3=>b<="";when s4=>b<="";when s5=>b<="";when s6=>b<="";when s7=>b<="";when s8=>b<="";when s9=>b<="";when s10=>b<="";when s11=>b<="";when s12=>b<="";when s13=>b<="";when s14=>b<="";when s15=>b<="";when s16=>b<="";when s17=>b<="";when s18=>b<="";when s19=>b<="";when s20=>b<="";when s21=>b<="";when s22=>b<="";end case;end process;end light_1;六、仿真波形说明:为了仿真需要,在进行仿真事,将分频部分p0去掉,直接用clk作用进程p2其中:- 3 -End time=2msa period time=60usclk period time=2us七、故障及问题分析本次实验整体比较顺利,但仍旧出现了几个问题:开始并未设置分频器,clk的频率为50MHz,这个频率过高,若是直接用于提供时钟,不但不能看清现象,还会因为周期过短(可能会短于电路的延迟时间),导致输出错误。

基于vhdl语言的二进制转十进制并用数码管显示的设计

河南科技学院机电学院VHDL课程设计报告题目:八位数码管显示专业班级:电气工程及其自动化102姓名:周迎接学号:20100344214指导教师:付广春完成日期:2012年12月27 日目录1 引言 (2)2 总体设计方案 (2)2.1 输入引脚数目的计算 (3)2.2 二进制转为十进制部分程序设计 (3)2.3 数码管显示部分程序设计 (4)3 仿真显示 (5)3.1 显示3仿真图 (5)3.2显示96的仿真图 (5)4 心得体会 (6)参考文献 (6)附录1 (7)摘要随着当今社会电子技术的快速发展,单凭借硬件已不再能满足广大人民的需求,这时候软件就显示除了他们突出的优点。

与其他编程语言相比,VHDL语言以其超强的硬件描述能力,良好的可读性和可移植性,以及其良好的用户自定义性受到了广大用户的青睐。

VHDL语言在最近几年的发展及其迅猛,由此可以看出其用途已经变的越来越广泛。

一个VHDL程序由5个部分组成,包括实体(ENTITY)、结构体(architecture)、配置(coxnfiguration)、包(package)和库(library)。

实体和结构体两大部分组成程序设计的最基本单元。

图2.2表示的是一个VHDL 程序的基本组成。

配置是用来从库中选择所需要的单元来组成该系统设计的不同规格的不同版本,VHDL和Verilog HDL已成为IEEE的标准语言,使用IEEE提供的版本。

包是存放每个设计模块都能共享的设计类型、常数和子程序的集合体。

库是用来存放已编译的实体、结构体、包和配置。

在设计中可以使用ASIC芯片制造商提供的库,也可以使用由用户生成的IP库。

今天我所要设计的是基于VHDL语言的8位数码管显示电路,其要实现的功能是把输入的二进制数转换为对应的十进制数,并通过数码管显示出来。

其过程大致可以分为通过程序将输入的二进制数先转换为对应的十进制数,然后再把对应的十进制数与数码管的管脚对应起来,使其显示在数码管上。

vhdl七段数码管显示0到9计数器显示电路设计 -回复

vhdl七段数码管显示0到9计数器显示电路设计-回复如何设计一个能够显示0到9的计数器的七段数码管显示电路。

文章长度:1500-2000字一、引言(100字左右)计数器是数字电路中非常常见的一个组件,而七段数码管则是用于显示数字的一种常用装置。

本文将详细介绍如何设计一个能够实现0到9的计数器,并利用七段数码管进行显示的电路。

二、理论基础(200字左右)在开始设计电路之前,我们需要掌握一些基本的理论知识。

七段数码管是由七个LED组成的,每个LED被称为一个段,分别用a、b、c、d、e、f、g表示。

通过控制七个段的亮灭可以显示不同的数字。

例如,要显示数字0,将a、b、c、d、e、f亮起,而要显示数字1,则只需将b、c 亮起。

三、设计电路(600字左右)1. 确定计数范围根据题目要求,我们需要设计一个能够显示0到9的计数器。

因此,计数范围为0到9,共有10个数字需要显示。

2. 确定计数位数根据题目要求,我们需要设计的是一个十进制计数器,因此需要三个计数位。

每个计数位都是一个0到9的计数器。

3. 设计逻辑电路我们可以使用JK触发器作为计数器的基本构建模块。

JK触发器有两个输入和两个输出,分别称为J、K和Q、~Q。

其中,J和K分别用于控制触发器状态的跳变,而Q和~Q是触发器的两个状态。

我们可以使用三个JK触发器构建一个三位的二进制计数器。

具体电路如下:第一个JK触发器的CLK输入连接计数器电路的时钟信号,J、K和第二个JK触发器的CLK端连接在一起,第二个JK触发器的Q输出连接第三个触发器的J输入,第一个触发器的Q输出连接了第三个触发器的K输入。

这样的设计将会实现三个触发器之间的互动。

4. 连接七段数码管根据七段数码管的布局,我们需要将七段的对应输入连接到计数器的输出。

根据计数器的输出值,我们可以设定哪些段需要亮起或熄灭。

连接七段数码管的具体方法可以参考其数据手册或规格说明。

四、测试与调试(400字左右)完成电路的设计之后,我们需要进行测试和调试,以确保电路能够正常显示0到9的数字。

数码管显示VHDL

数码管显示library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY smgdt ISPORT (clk : IN std_logic;rst : IN std_logic;dataout : OUT std_logic_vector(7 DOWNTO 0); --各段数据输出en : OUT std_logic_vector(7 DOWNTO 0)); --COM使能输出END smgdt;ARCHITECTURE arch OF smgdt ISsignal cnt_scan : std_logic_vector(15 downto 0 );signal data4 : std_logic_vector(3 downto 0);signal dataout_xhdl1 : std_logic_vector(7 downto 0);signal en_xhdl : std_logic_vector(7 downto 0);begindataout<=dataout_xhdl1;en<=en_xhdl;process(clk,rst)beginif(rst='0')thencnt_scan<="0000000000000000";elsif(clk'event and clk='1')thencnt_scan<=cnt_scan+1; --把时钟分频end if;end process;process(cnt_scan(15 downto 13))begin --001 0000 0000 0000 0000--001 1111 1111 1111 1111 y--010 0000 0000 0000 0000--010 1111 1111 1111 1111 z--011 0000 0000 0000 0000 w--011 1111 1111 1111 1111 case cnt_scan(15 downto 13) iswhen"000"=> en_xhdl<="01111111";when"001"=> en_xhdl<="10111111";when"010"=> en_xhdl<="11011111";when"011"=> en_xhdl<="11101111";when"100"=> en_xhdl<="11110111";when"101"=> en_xhdl<="11111011";when"110"=> en_xhdl<="11111101";when"111"=> en_xhdl<="11111110";when others=> en_xhdl<="11111110";end case;end process;process(en_xhdl)begincase en_xhdl iswhen "11111110"=> data4<="0000";when "11111101"=> data4<="0001";when "11111011"=> data4<="0010";when "11110111"=> data4<="0011";when "11101111"=> data4<="0100";when "11011111"=> data4<="0101";when "10111111"=> data4<="0110";when "01111111"=> data4<="0111";when others => data4<="1000";end case;end process;process(data4)begincase data4 isWHEN "0000" =>dataout_xhdl1 <= "11000000";WHEN "0001" =>dataout_xhdl1 <= "11111001";WHEN "0010" =>dataout_xhdl1 <= "11111001";WHEN "0011" =>dataout_xhdl1 <= "10110000";WHEN "0100" =>dataout_xhdl1 <= "11000000";WHEN "0101" =>dataout_xhdl1 <= "10000000";WHEN "0110" =>dataout_xhdl1 <= "11111001";WHEN "0111" =>dataout_xhdl1 <= "10011001";WHEN "1000" =>dataout_xhdl1 <= "11111001";WHEN "1001" =>dataout_xhdl1 <= "00011001";WHEN "1010" =>dataout_xhdl1 <= "00010001";WHEN "1011" =>dataout_xhdl1 <= "11000001";WHEN "1100" =>dataout_xhdl1 <= "01100011";WHEN "1101" =>dataout_xhdl1 <= "10000101";WHEN "1110" =>dataout_xhdl1 <= "01100001";WHEN "1111" =>dataout_xhdl1 <= "01110001";WHEN OTHERS =>dataout_xhdl1 <= "00000011";END CASE;END PROCESS;end arch;。

vhdl设计实例

vhdl设计实例VHDL设计实例:数字电子钟引言:数字电子钟是一种常见的电子设备,用于显示当前时间。

本文将介绍如何使用VHDL设计一个简单的数字电子钟。

一、设计概述数字电子钟由时钟模块、数码管显示模块和控制模块组成。

时钟模块用于生成计时脉冲,数码管显示模块用于将时钟模块输出的计时脉冲转换为对应的数字显示,控制模块用于调整时钟和设置时间。

二、时钟模块设计时钟模块是整个电子钟的核心,它需要能够精确地生成计时脉冲。

使用VHDL语言,可以使用计数器和时钟分频器实现时钟模块。

计数器用于计数,时钟分频器用于将计数器的输出分频为1秒钟一次的脉冲。

三、数码管显示模块设计数码管显示模块用于将时钟模块输出的计时脉冲转换为数字显示。

在数码管显示模块中,每个数码管对应一个数字显示,通过切换不同的数码管,可以实现显示小时、分钟和秒钟。

使用VHDL语言,可以使用多路复用器和BCD转换器实现数码管显示模块。

四、控制模块设计控制模块用于调整时钟和设置时间。

通过增加按钮和减少按钮,可以实现调整时钟的功能。

通过设置按钮,可以进入设置时间的模式,并通过增加按钮和减少按钮设置小时、分钟和秒钟。

使用VHDL语言,可以使用状态机实现控制模块。

五、测试与验证在设计完成后,需要进行测试和验证。

可以使用仿真工具对设计的各个模块进行仿真,验证其功能是否正常。

同时,还可以将设计烧录到FPGA开发板上进行实际测试,确保数字电子钟能够正常工作。

六、总结本文以VHDL设计实例为题,详细介绍了数字电子钟的设计过程。

通过时钟模块、数码管显示模块和控制模块的设计,实现了一个简单的数字电子钟。

通过测试和验证,确保了设计的正确性和可靠性。

希望本文对读者理解VHDL设计实例并进行创作有所帮助。

通过自己的实践和研究,不断探索和创新,可以设计出更多实用的数字电子设备。

让我们一起努力,推动数字电子技术的发展!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计与制造一种L ED数码管显示控制器的V HDL设计邬杨波1,李小海2(11宁波大学信息科学与工程学院,浙江宁波 315211;21江东区科学技术局,浙江宁波 315040)摘 要: 本文给出了一种L ED数码管显示控制器的设计。

该显示控制器具有三线串行接口、多种工作模式;可以最多控制8位7段L ED数码管的显示或者64个单独的发光二极管;利用数控脉宽调制电路实现32级灰度控制。

用V HDL描述了整个设计,并在Altera公司的EPF10K10LC84 -3器件实现了该数码管显示控制器。

关键词: L ED数码管;V HDL;FL EX10K;显示控制中图分类号:TN364+11 文献标识码:A 文章编号:1008-0147(2003)02-30-05 Design of7-Segment Numeric L ED Display Driver by VH DLWU Yang-bo1,L I Xiao-hai2(1.Faculty of Inf orm ation S&T,N i ngbo U niversity,N i ngbo Zhejiang,315211;2.N i ngbo Jiangdong S&T B ureau,N i ngbo Zhejiang,315040,Chi na)Abstract:A design of7-segment numeric L ED display driver is proposed.The display driver with3 -wire serial interface and several work modes can drive8bits7-segment numeric L ED’s display in2 dividually(or64L EDs).32level control of grey scale is provided with a pulse-width modulatr.The structure of the driver is expressed in V HDL,and it is implemented in EPF10K10LC84-3.K eyw ords:Numeric L ED;V HDL;FL EX10K;Display driver1 引 言发光二极管(L ED)无论在工业生产、交通运输、还是仪器仪表上都有广泛的用途。

不仅可以用来表示测量值,也可以用来表示系统的各种状态。

V HDL是一种面向设计、多层次的标准化硬件描述语言,并已经被广泛接受为描述、验证和设计数字系统的最重要的标准语言之一[1]。

V HDL使设计者可以不依赖冯・诺依曼结构,即不仅仅是时序机的设计,而允许设计是真正并行的,从而为设计者提供了一种全新的数字系统的设计途径。

使用V HDL语言不只是意味着代码的编写,更是为了便于建立层次结构和元件结构的设计。

利用V HDL 编写的电路模块可被重复利用。

故可以简化设计者的设计工作,大大缩短设计时间,提高工作效率。

本文利用V HDL语言对L ED数码管控制器进行设计和描述,并在Altera公司的EPF10K10LC84-3器件实现了该数码管控制器。

第31卷,第2期Vol.31,No.2微 电 子 技 术MICR OE L ECTR ONIC TECHN OLOG Y总第150期2003年4月收稿日期:20022082132 L ED 数码管控制器的总体结构该L ED 数码管显示控制器具有同步串行接口,用三个端子(DIN 、CL K 、LOAD )与外接控制器相连接;能同时控制8位共阴极数码管或64个发光二极管。

根据控制寄存器的内容,该显示控制器可以实现多种工作模式:睡眠模式、显示测试模式、正常模式;实现扫描位数的控制:且利用数控脉宽调制电路实现32级灰度控制[2];实现BCD 译码/不译码数字控制。

在控制器内部具有8×8双口RAM 和一个控制寄存器组,均可独立寻址,可在不需要重写整个显示器的情况下,对每位数字单独控制并刷新,或改变工作状态。

此外,该控制器还提供复位信号。

L ED 数码管显示控制器的总体结构如图1所示。

该控制器由同步串行接口电路、地址译码器、8×8双口RAM 、控制寄存器组、数控脉宽调制电路、动态扫描电路构成。

图1 数码管显示控制器的总体结构图 同步串行接口电路:主要实现与外接微控制器的接口;地址译码器:对输入的串行地址进行地址译码:8×8双口RAM :用于保存对应数码管的显示内容,每一个存储单元均可单独寻址,即对每位数字可以单独控制并刷新;控制寄存器组:用于寄存显示控制器的各个控制字;数控脉宽调制电路:用于实现对数码管显示的灰度控制:动态扫描电路:根据双口RAM 、控制寄存器组中的内容最终实现对数码管的显示控制。

表1 数据帧格式D15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0××××地 址MSB数 据L SB图2 数据传送时序图 第2期 邬杨波,李小海:一种L ED 数码管显示控制器的VHDL 设计313 显示控制器各功能模块的设计311 同步串行接口电路同步串行接口电路由16位串入并出的移位寄存器构成。

在时钟信号CL K 的上升沿串行数据从DIN 移入内部的16位移位寄存器,以16位数据作为一个数据帧,数据帧的格式如表1所示;在信号Load 的上升沿将移位寄存器中D0~D7的数据存入地址D8~D11对应的存储单元中。

数据传送的时序图如图2所示。

312 8×8双口RAM 和控制寄存器组8×8双口RAM 电路结构如图3所示,主要由8个8位的寄存器及3-8的多路选择器构成。

寄存器:用来作为构成8×8双口RAM 的基本存储单元,带有使能端(EN )、锁存端(LA TCH )和复位端(RST );使能信号高电平有效,在使能信号有效时,利用锁存信号的上升沿,将输入数据锁存。

使能信号由4-16线地址译码器提供,双口RAM 地址空间为:0000~0111。

复位信号高电平有效,复位信号将寄存器清零。

图3 8×8双口RAM 电路多路选择器:根据输入的读地址信号(rdaddr[2..0])将RAM 中的数据输出。

控制寄存器组由几个于RAM 中相同的寄存器构成,其使能信号由4-16线地址译码器提供,其地址空间为:1000~1111;由于控制寄存器组由5个寄存器组成,因此只占用其地址空间中的5个地址,余下3个保留。

控制寄存器的输出送入动态扫描电路,决定显示控制器的工作模式及功能。

313 数控脉宽调制电路这是一个输出频率不变的脉宽数控调制电路,其频率决定数码管的扫描频率。

此电路由可预置计数器、原码/反码变换电路和T 触发器构成其原理图如图4所示。

图4 数控脉宽调制电路原码/反码变换电路:将输入的预置信号根据控制信号作相应变换。

datain[4..0]为五位预置数输入信号;ct1为原码/反码变换电路的控制信号,当ct1=‘0’时输出为原码信号,当ct1=‘1’输出为反码信号。

可预置计数器:这是一个可预置的5位二进制计数器;over 为计数溢出信号,load 预置数装载信号。

T 触发器:每来一个时钟脉冲输出翻转一次。

所谓反码,即对原来的二进制数(原码)按位取反,所得到的新的二进制数为(2n -x ),这里n 是二进制数的位数,x 是原来的二进制数。

或者说,原码加反码等于该二进制数的最大数2n 。

例如,当原码为“10011”(十进制19)时,它的反码为“01100”(十进制12),原码加反码二者之和为“11111”(十进制31)。

在5位的可预置计数器中,如果设预置数为原码19,则计数器从19开始计数,计数到溢出时,共计数了12个。

若此时将预置数取反后重新装载计数,则取反后预置数为12,计数器从12开始计数,计数到溢出时,共计数19个。

两次计数之和为31。

不论预置数如何变化,两次计数之和是不会改变的,这样就保证了PWM 输出的频率恒定不变。

图4电路的工作原理是:当有脉冲输入后,计数器从所预置的数开始计数,计数满时,计数器输出 32 微 电 子 技 术over 产生一个正脉冲,接计数器的置数端Load ,使计数器重新装载,同时经T 触发器产生PWM 输出(使低电平变为高电平,或使高电平变为低电平)。

PWM 输出pout 同时反馈到原码/反码变换电路的控制端,使预置数在输出pout 为低电平时为原码,在高电平时为反码。

如果原码代表输出高电平(脉冲宽度)的时间,则反码就代表了输出低电平的时间。

这样,在第一次溢出脉冲到来时,PWM 输出高电平,计数器按原码计数,同时预置数由原码变为反码,计数满时达到所需的脉冲宽度,产生第二次溢出脉冲,PWM 输出低电平,计数器按反码计数,同时预置数由反码变为原码,计数满时完成一个PWM输出的周期,产生第三次溢出脉冲,PWM 输出高电平……如此循环往复,按预置数产生所需宽度的脉冲。

预置数可以在任何时刻按需要改变,从而产生可变宽度的脉冲输出,其频率为:f =f <(2n +3)(由于计数器的溢出信号采用同步输出,故在每次利用溢出信号装载预置数时会额外占用3个时钟周期,因此输出PWM 信号的频率的计算作了修改)。

该电路仿真时序图如图5所示。

图5 数控脉宽调制电路仿真时序图图6 显示工作方式流程图图7 数码管动态扫描电路逻辑框图314 动态扫描电路该电路能够根据控制寄存器的设定值完成各种模式的扫描显示功能:根据设定值扫描1-8位数码管,根据设定值进行睡眠模式(SHU TDOWN )、测试模式(TEST )、正常模式(NORMOL E )显示;其工作流程如图6所示。

该电路由显示状态机、位选译码电路及显示模式控制电路构成,其结构如图7所示。

显示状态机由一个模可变的计数器构成,对扫描时钟进行计数,其计数输出作为显示状态,同时也作为双口RAM 的读地址。

位选译码电路对显示状态机的输出进行位选译码,其输出控制数码管选通与否。

显示模式控制电路根据控制寄存器的内容实现各种模式的显示控制。

动态扫描电路各信号功能及意义如下:(1)reset 位复位信号,复位以后输出信号seecodeout 为“0000-0000”,addrout =“000”。

(2)clk 扫描时钟信号,扫描频率在1024-4096之间。

(3)shutdown 睡眠显示模式控制信号,高电平有效。

该信号有效时进入睡眠显示模式。

(4)test 测试显示模式控制信号,高电平有效。

该信号有效时进入测试显示模式。

(5)bcdslt BCD 译码控制信号,高电平有效。