中原工学院计算机组成原理试卷

计算机组成原理试题及答案

计算机组成原理试题及答案一、选择题。

1. 下列哪个是计算机组成原理的基本概念?A. 数据结构。

B. 操作系统。

C. 计算机体系结构。

D. 算法。

答案,C。

2. 计算机组成原理的核心是什么?A. 中央处理器。

B. 内存。

C. 输入输出设备。

D. 总线。

答案,A。

3. 下列哪个不是计算机组成原理中的主要部件?A. 控制单元。

B. 运算器。

C. 存储器。

D. 输入设备。

答案,D。

4. 计算机组成原理中,数据和指令在内存中是以什么形式存储的?B. 十进制。

C. 八进制。

D. 十六进制。

答案,A。

5. 计算机组成原理中,控制单元的主要功能是什么?A. 控制数据传输。

B. 进行运算。

C. 存储数据。

D. 输入输出。

答案,A。

1. 计算机组成原理中,CPU的作用是进行数据处理和______。

答案,控制。

2. 内存是计算机中的______存储器。

答案,临时。

3. 计算机组成原理中,总线是连接各个部件的______。

答案,通信线路。

4. 控制单元的主要功能是______。

答案,控制数据传输和处理。

5. 计算机组成原理中,运算器负责进行______运算。

答案,算术和逻辑。

1. 简述计算机组成原理中的冯·诺依曼结构。

答,冯·诺依曼结构是一种计算机体系结构,主要包括存储器、运算器、控制器、输入设备和输出设备等五大部分。

其中存储器用于存储数据和指令,运算器用于进行算术和逻辑运算,控制器用于控制数据传输和处理,输入设备用于接收数据输入,输出设备用于显示处理结果。

2. 什么是指令周期?它与时钟周期有什么关系?答,指令周期是指计算机执行一条指令所需的时间,它包括取指令周期、执行周期和访存周期。

时钟周期是CPU中时钟脉冲的时间间隔,它决定了CPU的工作速度。

指令周期与时钟周期的关系在于,时钟周期是指令周期的基本单位,指令周期是由若干个时钟周期组成的。

四、综合题。

1. 简述计算机组成原理中的存储器层次结构。

答,计算机存储器层次结构包括寄存器、高速缓存、内存和外存等多个层次。

2022年中原工学院网络工程专业《计算机组成原理》科目期末试卷B(有答案)

2022年中原工学院网络工程专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、某计算机主存按字节编址,由4个64M×8位的DRAM芯片采用交叉编址方式构成,并与宽度为32位的存储器总线相连,主存每次最多读写32位数据。

若double型变量x 的主存地址为80400lAH,则读取x需要的存储周期数是()。

A.1B.2C.3D.42、有如下C语言程序段:for(k=0;k<1000;k++)a[k]=a[k]+32;若数组a及变量k均为int型,int型数据占4B,数据Cache采用直接映射方式、数据区大小为1KB,块大小位16B,该程序段执行前Cache为空,则该程序段执行过程中访问数组a的Cache缺失率约为()。

A.1.25%B.2.5%C.12.5%D.25%3、假定编译器对高级语言的某条语句可以编译生成两种不同的指令序列,A、B和C三类指令的CPl和执行两种不同序列所含的三类指令条数见下表。

则以下结论错误的是()。

I.序列一比序列二少l条指令Ⅱ.序列一比序列二的执行速度快Ⅲ.序列一的总时钟周期数比序列二多1个Ⅳ.序列一的CPI比序列二的CPI大A.I、llB.1、ⅢC. ll、1VD.Ⅱ4、完整的计算机系统应该包括()。

A.运算器、存储器、控制器B.外部设备和主机C.主机和应用程序D.主机、外部设备、配套的软件系统5、在计算机系统中,作为硬件与应用软件之间的界面是()。

A.操作系统B.编译程序C.指令系统D.以上都不是6、在计数器定时查询方式下,正确的描述是()。

A.总线设备的优先级可变B.越靠近控制器的设备,优先级越高C.各设备的优先级相等D.对硬件电路故障敏感7、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

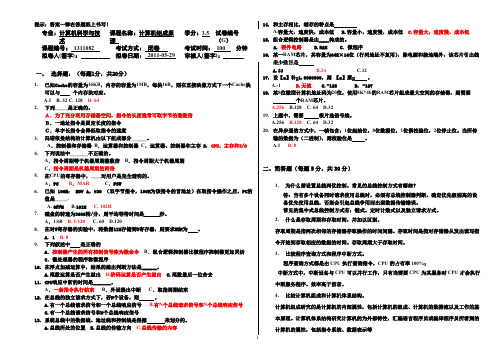

计算机组成原理试卷A卷.doc

计算机组成原理试卷A卷、选择题(共20题,每题2分,共40分,将答案写在下列表格中)。

1A -(2,4-1)B -(215-1)C -(2I5+1)D -(2,4+1)2、交叉存储器实质上是一种多模块存储器,它用()方式执行多个独立的读写操作。

A资源重复B资源共享C流水式并行D顺序3、某DRAM芯片,具存储容量为2MX16位,该芯片的地址线和数据线的数目是()。

A 20, 16B 16, 2C 2, 16D 21, 164、常用的虚拟存储系统由()两级存储器组成,其中辅存是大容屋的磁表面存储器。

A通用寄存器-cache B cache-辅存C主存■辅存 D cache-主存5、用于对某个寄存器中操作数的寻址方式为()。

A寄存器直接B间接C寄存器间接D直接6、程序控制类的指令功能是()。

A进行算术运算和逻辑运算B进行主存与CPUZ间的数据传送C进行CPU和I/O设备Z间的数据传送D改变程序执行的顺序7、在集中式总线仲裁中,()方式响应时间最快。

A计数器定时查询方式B电路故障C独立请求方式D菊花链方式8、某计算机字长16位,其存储容量为256MB,若按单字编址,它的寻址范围是()。

A 0—128MB B 0—64MBC 0—64MD 0—128M9、岂接映射cache的主要优点是实现简单。

这种方式的主要缺点是()。

A cache中的块数随著主存容量增大而线性增加B它的存取时间人于其它cache映射方式C如果使用屮的2个或多个块映射到cache同一行,命屮率则下降D它比其他cache映射方式价格更贵10、主存贮器和CPU之间增加cache的目的是()。

A扩大主存贮器容量B既扩大主存贮器容量,乂扩大CPU中通用奇存器的数量C扩•大CPU屮通用寄存器的数量D解决CPU和主存之间的速度匹配问题11、浮点数加、减运算过程一般包括对阶、尾数运算、规格化、舍入和判溢出等步骤。

设浮点数的阶码和尾数均采用补码表示,H•位数分别为5位和7位(均含2位符号位)。

计算机组成原理试题答案及解析

计算机组成原理试题答案及解析一、单选题1. What is the primary function of the control unit in a computer?A. Performing arithmetic calculationsB. Managing the execution of instructionsC. Storing data for future useD. Controlling the input/output devicesAnswer: BExplanation: The control unit is responsible for managing the execution of instructions in a computer. It coordinates the activities of all the other components and ensures that instructions are executed in the correct sequence.2. Which of the following is an example of a volatile memory?A. Hard disk driveB. Solid-state driveC. Flash memoryD. Random-access memory (RAM)Answer: DExplanation: Random-access memory (RAM) is an example of volatile memory, which means that its contents are lost when the power to thecomputer is turned off. Unlike permanent storage devices like hard disk drives or solid-state drives, RAM is used for temporary data storage during program execution.3. What is the purpose of the arithmetic logic unit (ALU) in a computer?A. Storing program instructionsB. Executing arithmetic and logic operationsC. Controlling the input/output devicesD. Managing the memory hierarchyAnswer: BExplanation: The arithmetic logic unit (ALU) is responsible for performing arithmetic and logic operations in a computer. It can perform operations such as addition, subtraction, multiplication, division, and logical comparisons.4. Which of the following is not a valid addressing mode in computer architecture?A. Immediate addressingB. Direct addressingC. Indirect addressingD. Parallel addressingAnswer: DExplanation: Parallel addressing is not a valid addressing mode in computer architecture. The other three options (immediate, direct, and indirect addressing) are commonly used in programming to access memory locations or operands.5. Which of the following is not a characteristic of a reduced instruction set computer (RISC)?A. Simple instructionsB. Large instruction setC. Load/store architectureD. Fixed instruction lengthAnswer: BExplanation: A reduced instruction set computer (RISC) is characterized by its simple instructions, load/store architecture (data must be loaded into registers before operations can be performed), and fixed instruction length. The term "reduced" in RISC refers to the reduced complexity of the instructions, not the size of the instruction set.二、多选题1. Which of the following are examples of secondary storage devices? (Select all that apply)A. Hard disk drive (HDD)B. Random-access memory (RAM)C. Solid-state drive (SSD)D. Optical disc drive (ODD)Answer: A, C, DExplanation: Secondary storage devices are used for long-term storage and include hard disk drives (HDDs), solid-state drives (SSDs), and optical disc drives (ODDs). Random-access memory (RAM) is a type of primary storage, not secondary storage.2. Which of the following components are part of the von Neumann architecture? (Select all that apply)A. Central processing unit (CPU)B. Control unit (CU)C. Input/output devicesD. MemoryAnswer: A, B, DExplanation: The von Neumann architecture includes the central processing unit (CPU), control unit (CU), and memory. Input/output devices are not considered part of the von Neumann architecture.3. Which of the following are advantages of a pipelined processor? (Select all that apply)A. Increased throughputB. Decreased latencyC. Simpler designD. Reduced power consumptionAnswer: A, B, DExplanation: Pipelining allows for increased throughput (more tasks completed per unit of time), decreased latency (each task takes less time to complete), and reduced power consumption (as tasks are divided into smaller stages and can be executed concurrently).4. Which of the following statements about cache memory is true? (Select all that apply)A. It is faster than primary memory.B. It is smaller than primary memory.C. It stores frequently used data.D. It is volatile.Answer: A, B, CExplanation: Cache memory is faster than primary memory (such as RAM), smaller in size, and stores frequently used data to reduce the access time for the CPU. However, cache memory is not volatile - it retains its contents even when the power is turned off.5. Which of the following are examples of input devices? (Select all that apply)A. KeyboardB. MonitorC. MouseD. PrinterAnswer: A, CExplanation: Input devices are used to enter data or commands into a computer system. Examples of input devices include keyboards and mice, which allow users to input text or interact with software. Monitors and printers are output devices.三、解析1. Control unit: The control unit is an essential component of a computer system. Its primary function is to manage the execution of instructions and coordinate the activities of other hardware components. It ensures that instructions are fetched, decoded, and executed in the correct sequence. The control unit communicates with the arithmetic logic unit (ALU), memory, and input/output devices to carry out the instructions provided by the program.2. Volatile memory: Volatile memory, like random-access memory (RAM), is a type of computer memory that loses its contents when the power is turned off. Unlike permanent storage devices such as hard disk drives or solid-state drives, volatile memory is used for temporary data storage during program execution. RAM allows data to be quickly read from and written to, making it ideal for storing active program instructions and data.3. Arithmetic logic unit (ALU): The arithmetic logic unit (ALU) is responsible for performing arithmetic and logic operations in a computer. Itcan perform operations such as addition, subtraction, multiplication, division, and logical comparisons. The ALU receives inputs from registers within the central processing unit (CPU) and performs calculations based on these inputs. The result of the operation is then stored back in the registers for further processing or output.4. Addressing modes: Addressing modes are used in computer architecture to specify how to access memory locations or operands in an instruction. Some common addressing modes include immediate addressing (data is directly specified in the instruction), direct addressing (the operand is specified by its memory address), and indirect addressing (the memory address of the operand is stored in a register). These addressing modes allow for efficient retrieval and manipulation of data during program execution.5. Reduced instruction set computer (RISC): A reduced instruction set computer (RISC) is a type of computer architecture that emphasizes simplicity and efficiency in instruction execution. RISC processors use a small set of simple instructions, with each instruction typically performing a single operation. This simplifies the design of the processor and allows for faster instruction execution. RISC processors often employ techniques such as pipelining to further enhance performance and efficiency. The term "reduced" in RISC refers to the reduced complexity of the instructions, not the size of the instruction set.总结:本文回答了一系列与计算机组成原理相关的试题,并对每个问题进行了解析和解答。

2022年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)

2022年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、某计算机使用4体交叉编址存储器,假定在存储器总线上出现的主存地址(十进制)序列为8005,8006,8007,8008,8001,8002,8003,8004,8000,则可能发生访存冲突的地址对是()。

A.8004和8008B.8002和8007C.8001和8008D.8000和80042、采用八体并行低位交叉存储器,设每个体的存储容量为32K×16位,存储周期为400ns,下述说法中正确的是()。

A.在400ns内,存储器可向CPU提供2位二进制信息B.在l00ns内,每个体可向CPU提供27位二进制信息C.在400ns内,存储器可向CPU提供2位二进制信息D.在100ns内,每个体可向CPU提供2位二进制信息3、假设机器字长为16位,用定点补码小数表示时,一个字所能表示的范围是()。

A.0~(1-2-15)B.-(1-2-15)~(1-2-15)C.-1~1D.-1~(1-2-15)4、下列关于各种移位的说法中正确的是()。

I.假设机器数采用反码表示,当机器数为负时,左移时最高数位丢0,结果出错;右移时最低数位丢0,影响精度Ⅱ在算术移位的情况下,补码左移的前提条件是其原最高有效位与原符号位要相同Ⅲ.在算术移位的情况下,双符号位的移位操作中只有低符号位需要参加移位操作()A. Ⅲ、ⅡB.只有ⅡC.只有ⅢD.全错5、并行加法器中,每位全和的形成除与本位相加两数数值位有关外,还与()有A.低位数值大小B.低位数的全和C.高位数值大小D.低位数送来的进位6、为协调计算机系统各部件的工作,需要一种器件来提供统一的时钟标准,这个器件,是()。

A.总线缓冲器B.总线控制器C.时钟发生器D.以上器件都具备这种功能7、总线宽度与下列()有关。

A.控制线根数B.数据线根数C.地址线根数D.以上都不对8、程序P在机器M上的执行时间是20s,编译优化后,P执行的指令数减少到原来的70%,而CPl增加到原来的1.2倍,则P在M上的执行时间是()。

(完整)计算机组成原理试卷(含答案),推荐文档

机指令字长 16 位,每

个操作数的地址码为 5 位。指令分为零地址码、一地址码和二地址码三种格式。若二地址码

指令有 a 种,零地址有 b 种,如操作码长度固定,则一地址码最多有几种?若操作码长度可

变,则一地址码最多允许有几种?

设一地址码 x 种。

固定长度操作码:26-a-b

(5 分)

操作码长度可变:x=(26-a)*25-b*2-5 (5 分)

与技术

成原理

3.5

(A)

课程编号: 133102 考试方式: 闭卷 考试时间: 分钟

更多的专业资料给更多有 拟卷人(签字):

拟卷日期: 2006- 审核人(签字): 12-5

5. 已知一 CPU 内部

的数据通路

5. 取指令:(5 分)

如下图所示。 指令 STA X (设该指令为单字节, X 为直接地址)的功能是 A (X)。请写出指令 STA X 的

C.取指周期结束 。

中断服务程序。效率高于前者。 4. 比较计算机组成和计算机体系结构。

A.有一个总线请求信号和一个总线响应信号 B.有N个总线请求信号和N个总线响应信号

C.有一个总线请求信号和N个总线响应信号

13. 系统总线中的数据线、地址线和控制线是根据

来划分的。

计算机组成研究的是计算机的内部属性,包括计算机的组成、计算机的数据流以及工作的基 本原理。计算机体系结构研究计算机的为外部特性,汇编语言程序员或编译程序员所看到的

B.外部设备一旦发出中断请求,CPU 应立即响应。

3. 微型计算机的发展通常以

为技术标志。

C.中断方式一般用于处理随机出现的服务请求。

A.操作系统

B.磁盘

C.软件

D.微处理器

计算机组成原理试题集(含答案)

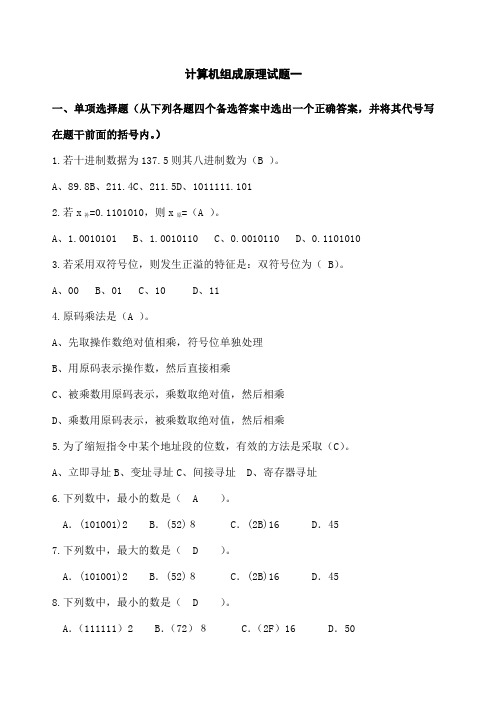

计算机组成原理试题二

一、选择题(共20分,每题1分)

1.CPU响应中断的时间是_C_____。

A.中断源提出请求;B.取指周期结束;C.执行周期结束;D.间址周期结束。

2.下列说法中___c___是正确的。

A.加法指令的执行周期一定要访存;B.加法指令的执行周期一定不访存;

C.指令的地址码给出存储器地址的加法指令,在执行周期一定访存;

24.异步控制常用于(A)作为其主要控制方式。

A.在单总线结构计算机中访问主存与外围设备时 B.微型机的CPU控制中

C.组合逻辑控制的CPU中 D.微程序控制器中

25.为了缩短指令中某个地址段的位数,有效的方法是采取(C)。

A、立即寻址

B、变址寻址

C、间接寻址

D、寄存器寻址

二、判断题(判断下列各题的正误。对的打“√”,错的打“×”,若错误必须加以改正。每题1分,计10分)

7、主存储器中采用双译码结构的主要目的是提高存取速度。×

8、集中式总线控制中,定时查询方式下,各设备的优先级是固定不变的。×

9、引入虚拟存储系统的目的是提高存储速度。×

10、DMA方式进行外设与主机交换信息时,不需要向主机发出中断请求。×

11、CPU以外的设备都称外部设备。×

12、第三代计算机所用的基本器件是晶体管。×

1、存储单元是存放一个二进制信息的存贮元。×

2、计算机辅助设计简称CAD。√

3、集中式总线控制中,定时查询方式的响应速度最快。×

4、主程序运行时何时转向为外设服务的中断服务程序是预先安排好的。×

5、时序电路用来产生各种时序信号,以保证整个计算机协调地工作。√

6、采用下址字段法控制微程序执行顺序的微程序控制器中,一定要有微程序计数器。×

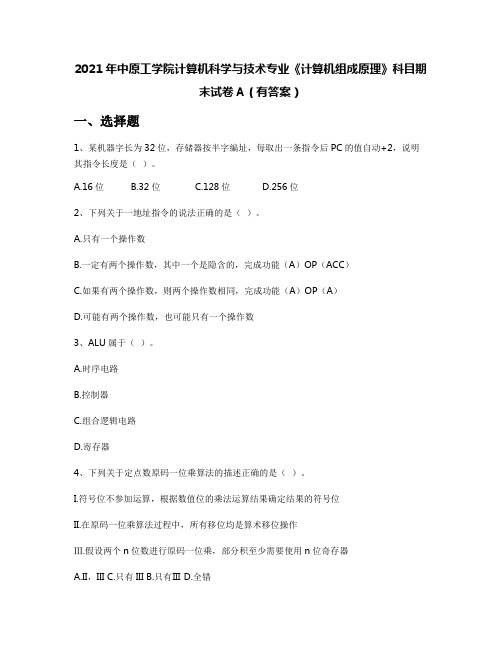

2021年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某机器字长为32位,存储器按半字编址,每取出一条指令后PC的值自动+2,说明其指令长度是()。

A.16位B.32位C.128位D.256位2、下列关于一地址指令的说法正确的是()。

A.只有一个操作数B.一定有两个操作数,其中一个是隐含的,完成功能(A)OP(ACC)C.如果有两个操作数,则两个操作数相同,完成功能(A)OP(A)D.可能有两个操作数,也可能只有一个操作数3、ALU属于()。

A.时序电路B.控制器C.组合逻辑电路D.寄存器4、下列关于定点数原码一位乘算法的描述正确的是()。

I.符号位不参加运算,根据数值位的乘法运算结果确定结果的符号位II.在原码一位乘算法过程中,所有移位均是算术移位操作Ⅲ.假设两个n位数进行原码一位乘,部分积至少需要使用n位奇存器A.II,III C.只有IIIB.只有Ⅲ D.全错5、假设寄存器的内容为00000000,若它等于-128,则该机器采用了()。

A.原码B.补码C.反码D.移码6、下列关于页式虚拟存储器的论述,正确的是()。

A.根据程序的模块性,确定页面大小B.可以将程序放置在页面内的任意位置C.可以从逻辑上极大地扩充内存容量,并且使内存分配方便、利用率高D.将正在运行的程序全部装入内存7、Cache用组相联映射,一块大小为128B,Cache共64块,4块分一组,主存有4096块,主存地址共需()位。

A.19B.18C.17D.168、指令寄存器的位数取决()。

A.存储器的容量B.指令字长C.机器字长人D.存储字长9、下列选项中,能缩短程序执行时间的措施是()。

1.提高CPU时钟频率Ⅱ.优化数据通路结构ll.对程序进行编译优化A.仪I、ⅡB.仅I、ⅢC.仅Ⅱ、ID.I、Ⅱ、Ⅲ10、在计数器定时查询方式下,正确的描述是()。

A.总线设备的优先级可变B.越靠近控制器的设备,优先级越高C.各设备的优先级相等D.对硬件电路故障敏感11、某同步总线采用数据线和地址线复用方式,其中地址/数据线有32根,总线时钟频率为66MHz,每个时钟周期传送两次数据(上升沿和下降沿各传送一次数据),该总线的最大数据传输率(总线带宽)是()。

2021年中原工学院数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年中原工学院数据科学与大数据技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、对36位虚拟地址的页式虚拟存储系统,每页8KB,每个页表项为32位,页表的总容量为()。

A.1MBB.4MBC.8MBD.32MB2、若单译码方式的地址输入线为6,则译码输出线有()根,那么双译码方式有输出线()根。

A.64,16B.64,32C.32,16D.16,643、某计算机字长为32位,按字节编址,采用小端(Litle Endian)方式存放数据。

假定有一个double型变量,其机器数表示为1122334455667788H,存放在00008040H开始的连续存储单元中,则存储单元00008046H中存放的是()。

A.22HB.33HC.66HD.77H4、假设有7位信息码010101,则低位增设偶校验位后的代码和低位增设奇校验位后的代码分别为()。

A.01101010 01101010B.0101010 01101011C.01101011 01101010D.01101011 011010115、某机器字长为8位,采用原码表示法(其中一位为符号位),则机器数所能表示的范围是()。

A.-127~+127B.-127~+128C.-128~+127D.-128~+1286、在集中式总线控制中,响应时间最快的是()。

A.链式查询B.计数器定时查询C.独立请求D.分组链式查询7、关于同步控制说法正确的是()。

A.采用握手信号B.由统一时序电路控制的方式C.允许速度差别较大的设备一起接入工作D.B和C8、计算机硬件能够直接执行的是()。

1.机器语言程序IⅡ.汇编语言程序Ⅲ.硬件描述语言程序入A.仅IB.仅I、ⅡC.仅I、ⅢD. I、Ⅱ 、Ⅲ9、冯·诺依曼型计算机的设计思想主要有()。

1.存储程序Ⅱ.二进制表示Ⅲ.微程序方式Ⅳ.局部性原理A. I,ⅢB.Ⅱ,ⅢC.IⅡ,IⅣD.I,IⅡ10、下列关于指令流水线数据通路的叙述中,正确的是()。

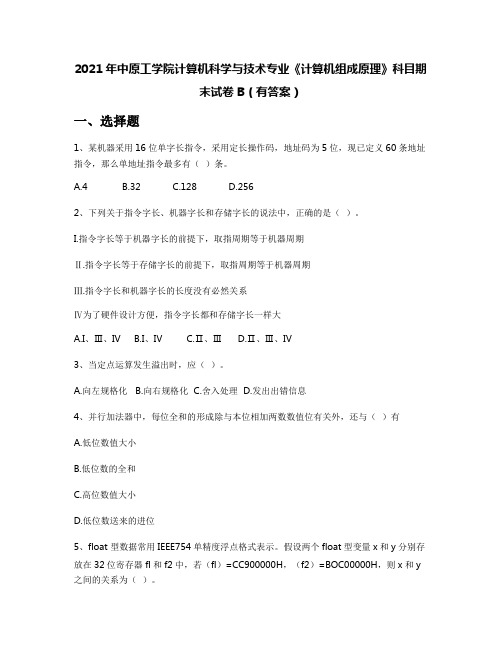

2021年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)

2021年中原工学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、某机器采用16位单字长指令,采用定长操作码,地址码为5位,现已定义60条地址指令,那么单地址指令最多有()条。

A.4B.32C.128D.2562、下列关于指令字长、机器字长和存储字长的说法中,正确的是()。

I.指令字长等于机器字长的前提下,取指周期等于机器周期Ⅱ.指令字长等于存储字长的前提下,取指周期等于机器周期Ⅲ.指令字长和机器字长的长度没有必然关系Ⅳ为了硬件设计方便,指令字长都和存储字长一样大A.I、Ⅲ、IVB.I、ⅣC.Ⅱ、ⅢD.Ⅱ、Ⅲ、Ⅳ3、当定点运算发生溢出时,应()。

A.向左规格化B.向右规格化C.舍入处理D.发出出错信息4、并行加法器中,每位全和的形成除与本位相加两数数值位有关外,还与()有A.低位数值大小B.低位数的全和C.高位数值大小D.低位数送来的进位5、float 型数据常用IEEE754单精度浮点格式表示。

假设两个float型变量x和y分别存放在32位寄存器fl和f2中,若(fl)=CC900000H,(f2)=BOC00000H,则x和y 之间的关系为()。

A.x<y且符号相同B.x<y符号不同C.x>y且符号相同D.x>y且符号不同6、在全相联映射、直接映射和组相联映射中,块冲突概率最小的是()。

A.全相联映射B.直接映射C.组相联映射D.不一定7、在对破坏性读出的存储器进行读/写操作时,为维持原存信息不变,必须辅以的操作是()。

A.刷新B.再生C.写保护D.主存校验8、下列关于配备32位微处理器的计算机的说法中,正确的是()。

该机器的通用寄存器一般为32位Ⅱ.该机器的地址总线宽度为32位Ⅲ.该机器能支持64位操作系统IV.一般来说,64位微处理器的性能比32位微处理器的高A.I、ⅡB.I、ⅢC.I、ⅣD.I、IⅡ、Ⅳ9、程序P在机器M上的执行时间是20s,编译优化后,P执行的指令数减少到原来的70%,而CPl增加到原来的1.2倍,则P在M上的执行时间是()。

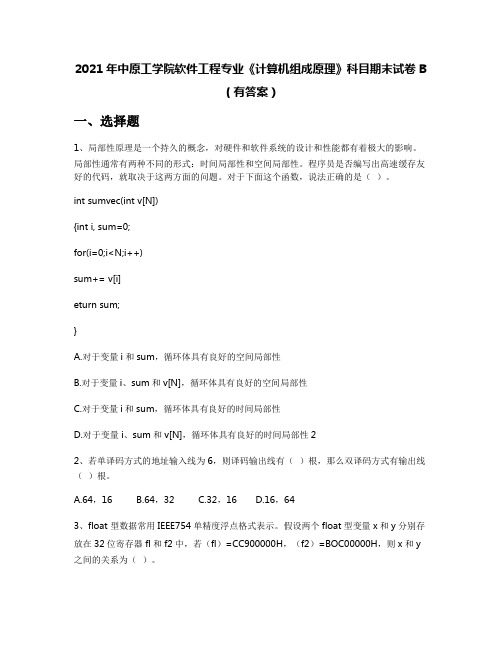

2021年中原工学院软件工程专业《计算机组成原理》科目期末试卷B(有答案)

2021年中原工学院软件工程专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、局部性原理是一个持久的概念,对硬件和软件系统的设计和性能都有着极大的影响。

局部性通常有两种不同的形式:时间局部性和空间局部性。

程序员是否编写出高速缓存友好的代码,就取决于这两方面的问题。

对于下面这个函数,说法正确的是()。

int sumvec(int v[N]){int i, sum=0;for(i=0;i<N;i++)sum+= v[i]eturn sum;}A.对于变量i和sum,循环体具有良好的空间局部性B.对于变量i、sum和v[N],循环体具有良好的空间局部性C.对于变量i和sum,循环体具有良好的时间局部性D.对于变量i、sum和v[N],循环体具有良好的时间局部性22、若单译码方式的地址输入线为6,则译码输出线有()根,那么双译码方式有输出线()根。

A.64,16B.64,32C.32,16D.16,643、float 型数据常用IEEE754单精度浮点格式表示。

假设两个float型变量x和y分别存放在32位寄存器fl和f2中,若(fl)=CC900000H,(f2)=BOC00000H,则x和y 之间的关系为()。

A.x<y且符号相同B.x<y符号不同C.x>y且符号相同D.x>y且符号不同4、当满足下列()时,x>-1/2成立。

A.x1必须为l,x2~x4至少有一个为1B.x1必须为1,x2~x4任意C.x1必须为0,x2~x4至少有一个为1D.x1必须为0,X2~x4任意5、假设编译器规定int 和shot类型长度分别为32位和16位,若有下列C语言语句:unsigned short x=65530;unsigned int y=x;得到y的机器数为()。

A.00007FFAHB.0000 FFFAHC.FFFF 7FFAHD.FFFF FFFAH6、某总线共有88根信号线,其中数据总线为32根,地址总线为20根,控制总线36根,总线工作频率为66MHz、则总线宽度为(),传输速率为()A.32bit 264MB/sB.20bit 254MB/sC.20bit 264MB/sD.32bit 254MB/s7、假设某存储器总线采用同步通信方式,时钟频率为50MHz,每个总线事务以突发方式传输8个字,以支持块长为8个字的Cache行读和Cache行写,每字4B.对于读操作,方式顺序是1个时钟周期接收地址,3个时钟周期等待存储器读数,8个时钟周期用于传输8个字。

计算机组成原理期末考试试题及答案

计算机组成原理期末考试试题及答案一、选择题1、完整的计算机系统应包含______。

DA. 运算器、存储器和操纵器B. 外部设备和主机C. 主机和有用程序D. 配套的硬件设备和软件系统2、计算机系统中的存储器系统是指______。

DA.RAM存储器B.ROM存储器C. 主存储器D. 主存储器和外存储器3、冯·诺依曼机工作方法的根本特点是______。

BA. 多指令流单数据流B. 按地址访问并顺序执行指令C. 堆栈操作D. 存储器按内部选择地址4、以下说法中不正确的选项是______。

DA. 任何可以由软件完成的操作也可以由硬件来完成B. 固件就功能而言类似于软件,而从形态来说又类似于硬件C. 在计算机系统的层次结构中,微程序级属于硬件级,其他四级都是软件级D. 面向高级语言的机器是完全可以完成的5、在以下数中最小的数为______。

CA. (101001)2B. (52)8C. (101001)BCDD. (233)166、在以下数中最大的数为______。

BA. (10010101)2B. (227)8C. (143)5D. (96)167、在机器中,______的零的表示形式是唯一的。

BA. 原码B. 补码C. 反码D. 原码和反码9、针对8位二进制数,以下说法中正确的选项是______。

BA.–127的补码为10000000B.–127的反码等于0的移码BC.+1的移码等于–127的反码D.0的补码等于–1的反码9、一个8位二进制整数采纳补码表示,且由3个“1〞和5个“0〞组成,则最小值为______。

BA. –127B. –32C. –125D. –310、计算机系统中采纳补码运算的目的是为了______。

CA. 与手工运算方法保持一致B. 提高运算速度C. 简化计算机的设计D. 提高运算的精度11、假设某数x的真值为–,在计算机中该数表示为,则该数所用的编码方法是______码。

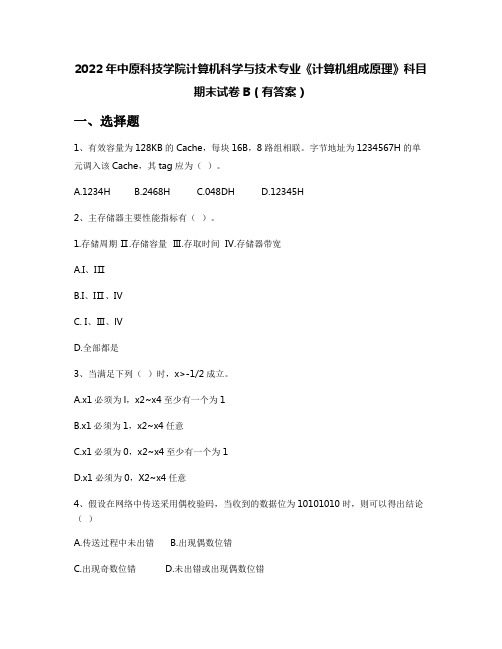

2022年中原科技学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)

2022年中原科技学院计算机科学与技术专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、有效容量为128KB的Cache,每块16B,8路组相联。

字节地址为1234567H的单元调入该Cache,其tag应为()。

A.1234HB.2468HC.048DHD.12345H2、主存储器主要性能指标有()。

1.存储周期Ⅱ.存储容量Ⅲ.存取时间Ⅳ.存储器带宽A.I、IⅡB.I、IⅡ、IVC. I、Ⅲ、lVD.全部都是3、当满足下列()时,x>-1/2成立。

A.x1必须为l,x2~x4至少有一个为1B.x1必须为1,x2~x4任意C.x1必须为0,x2~x4至少有一个为1D.x1必须为0,X2~x4任意4、假设在网络中传送采用偶校验码,当收到的数据位为10101010时,则可以得出结论()A.传送过程中未出错B.出现偶数位错C.出现奇数位错D.未出错或出现偶数位错5、在补码加减交替除法中,参加操作的数和商符分别是()。

A.绝对值的补码在形成商值的过程中自动形成B.补码在形成商值的过程中自动形成C.补码由两数符号位“异或”形成D.绝对值的补码由两数符号位“异或”形成6、内部总线(又称片内总线)是指()。

A.CPU内部连接各寄存器及运算部件之间的总线B.CPU和计算机系统的其他高速功能部件之间互相连接的总线C.多个计算机系统之间互相连接的总线D.计算机系统和其他系统之间互相连接的总线7、总线的半同步通信方式是()。

A.既不采用时钟信号,也不采用握手信号B.只采用时钟信号,不采用握手信号C.不采用时钟信号,只采用握手信号D.既采用时钟信号,又采用握手信号8、已知计算机A的时钟频率为800MHz,假定某程序在计算机A上运行需要12s。

现在硬件设计人员想设计计算机B,希望该程序在B上的运行时间能缩短为8s,使用新技术后可使B的时钟频率大幅度提高,但在B上运行该程序所需要的时钟周期数为在A上的1.5倍。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本试卷共2页,此页为B 卷第1页(注:参加重修考试者请在重修标识框内打钩)中原工学院2008~2009学年第1学期计算机专业计算机组成原理课程期末试卷一、填空:(19分)1、[x]补=1.01011,则x 的真值为,[-x]补=,[x/2]补

=。

2、动态存储器的刷新是按方式进行刷新的,常用的刷新方式

有,,。

3、一个组相联映射的Cache ,有128块,每组4块,主存共有16384块,

每块64个字,则主存地址共位,其中主存字块标记应为位,

组地址应为__位,Cache 地址共位。

4、CPU 从主存取出一条指令并执行该指令的时间叫,它通常包

含若干个,而后者又包含若干个。

5、微命令编码方法通常有,,

三种方法。

6、实现n ×n 位运算的不带符号阵列乘法器需要__________个全加器和__________与门。

二、选择:(10分)

1、使用74LS181这种器件来构成一个16位的ALU ,需要使用()

片74LS181。

A 、2

B 、4

C 、8

D 、162、主存储器与CPU 之间增加Cache 的目的是()A 、解决CPU 与主存之间的速度匹配问题。

B 、扩大主存储器的容量。

C 、扩大CPU 中通用寄存器的数量。

D 、降低主存储器的成本。

3、下列因素中,与Cache 的命中率无关的是()A 、主存的存取时间。

B 、块的大小。

C 、地址映射方式。

D 、Cache 的容量。

4、某机器字长32位,存储容量是1MB ,若字编址,其寻址范围是()A 、0~1M B、0~512KB C、0~256K D、0~256KB

题号一二三四五六七八九十总分5、微程序控制器中,机器指令与微指令的关系是

()

A、一条机器指令是由一条微指令来解释执行。

B、一条机器指令是由一段用微指令编成的微程

序来解释执行。

C、一段机器指令组成的程序是由一条微指令来解释执行。

D、一条微指令是由若干条机器指令组成。

三、名词解释:(10分)

1、(5分)DMA :

2、(5分)虚拟存储器:

四、简答:(24分)

1、(8分)提高主存速度有哪些具体措施?试简述之。

2、(8分)试述后续微地址的形成方法并指出其优缺

点。

B 卷√

A 卷重修标识

本试卷共2页,此页为B卷第2页

3、(8分)简要说明页式虚拟存储器的地址变换过程。

五、计算:(20分)

1、(12分)某机器浮点数的阶码为3位,尾数为6

位,均不包括符号位,试按补码浮点数的计算步骤,计算x+y。

已知x=2101×(-0.100010),y=2100×(+0.010110)。

2、(8分)设存储器容量为128M字,字长64位,模块数m=8,分别用顺序方式和交叉方式进行组织。

存储周期T=200ns,数据总线宽度为64位,总线传送周期50ns

τ=。

问顺序存储器和交叉存储器的带宽各是多少?六、分析与设计:(17分)

1、(10分)下图为双总线结构机器的数据通路,图中带有小圆圈标注

的地方表示有控制信号,无标注的地方不受控制。

试画出指令ADD R1,R2的指令周期流程图,并列出相应微操作控制信号序列,假设该指令的地址已存入在PC中。

ADD R1,R2;(R1)+(R2)→R1

2、(7分)设某机器指令长度为20位,具有双地址,单地址,无地址三种指令类型,若每个地址码用6位表示。

试问:如果操作码采用变长编码,对于已设计出m条双地址指令,n条无地址指令,最多还可以设计出多少条单地址指令?。