第10章《低功耗设计》2008年秋季

《微处理器系统结构与嵌入式系统设计》课程教案

《微处理器系统结构与嵌入式系统设计》课程教案第一章:微处理器概述1.1 微处理器的定义与发展历程1.2 微处理器的组成与工作原理1.3 微处理器的性能指标1.4 嵌入式系统与微处理器的关系第二章:微处理器指令系统2.1 指令系统的基本概念2.2 常见的指令类型及其功能2.3 指令的寻址方式2.4 指令执行过程第三章:微处理器存储系统3.1 存储器的分类与特点3.2 内存管理单元(MMU)3.3 存储器层次结构与缓存技术3.4 存储系统的性能优化第四章:微处理器输入/输出系统4.1 I/O 接口的基本概念与分类4.2 常见的I/O 接口技术4.3 直接内存访问(DMA)4.4 interrupt 与事件处理第五章:嵌入式系统设计概述5.1 嵌入式系统的设计流程5.2 嵌入式处理器选型与评估5.3 嵌入式系统硬件设计5.4 嵌入式系统软件设计第六章:嵌入式处理器架构与特性6.1 嵌入式处理器的基本架构6.2 嵌入式处理器的分类与特性6.3 嵌入式处理器的发展趋势6.4 嵌入式处理器选型considerations 第七章:数字逻辑设计基础7.1 数字逻辑电路的基本概念7.2 逻辑门与逻辑函数7.3 组合逻辑电路与触发器7.4 微处理器内部的数字逻辑设计第八章:微处理器系统设计与验证8.1 微处理器系统设计流程8.2 硬件描述语言(HDL)与数字逻辑设计8.3 微处理器系统仿真与验证8.4 设计实例与分析第九章:嵌入式系统软件开发9.1 嵌入式软件的基本概念9.2 嵌入式操作系统与中间件9.3 嵌入式软件开发工具与环境9.4 嵌入式软件编程实践第十章:嵌入式系统应用案例分析10.1 嵌入式系统在工业控制中的应用10.2 嵌入式系统在消费电子中的应用10.3 嵌入式系统在医疗设备中的应用10.4 嵌入式系统在其他领域的应用案例分析第十一章:嵌入式系统与物联网11.1 物联网基本概念与架构11.2 嵌入式系统在物联网中的应用11.3 物联网设备的硬件与软件设计11.4 物联网安全与隐私保护第十二章:实时操作系统(RTOS)12.1 实时操作系统的基本概念12.2 RTOS的核心组件与特性12.3 常见的实时操作系统及其比较12.4 实时操作系统在嵌入式系统中的应用第十三章:嵌入式系统功耗管理13.1 嵌入式系统功耗概述13.2 低功耗设计技术13.3 动态电压与频率调整(DVFS)13.4 嵌入式系统的电源管理方案第十四章:嵌入式系统可靠性设计14.1 嵌入式系统可靠性概述14.2 故障模型与故障分析14.3 冗余设计技术与容错策略14.4 嵌入式系统可靠性评估与测试第十五章:现代嵌入式系统设计实践15.1 现代嵌入式系统设计挑战15.2 多核处理器与并行处理15.3 系统级芯片(SoC)设计与集成15.4 嵌入式系统设计的未来趋势重点和难点解析第一章:微处理器概述重点:微处理器的定义、发展历程、组成、工作原理、性能指标。

宏晶科技STC12C5410AD系列单片机器件手册说明书

STC12C5410AD系列单片机器件手册 --- 1个时钟/机器周期8051 ---无法解密 ---低功耗,超低价 ---高速,高可靠 ---强抗静电,强抗干扰STC12C5412, STC12C5412ADSTC12C5410, STC12C5410ADSTC12C5408, STC12C5408ADSTC12C5406, STC12C5406ADSTC12C5404, STC12C5404ADSTC12C5402, STC12C5402ADSTC12LE5412,STC12LE5412ADSTC12LE5410,STC12LE5410ADSTC12LE5408,STC12LE5408ADSTC12LE5406,STC12LE5406ADSTC12LE5404,STC12LE5404ADSTC12LE5402,STC12LE5402AD技术支援:宏晶科技(深圳) www.MCU-Memory.com support@MCU-Memory.comUpdate date: 2006-4-15 (请随时注意更新)宏晶科技:专业单片机/存储器供应商 www.MCU-Memory.com STC12C5410AD系列 1T 8051单片机中文指南2领导业界革命 覆盖市场需求宏晶科技是新一代增强型8051单片机标准的制定者,致力于提供满足中国市场需求的世界级高性能单片机技术,在业内处于领先地位,销售网络覆盖全国。

在保证质量的基础上,以极低的价格和完善的服务赢得了客户的长期信赖。

在广受欢迎的STC89C51全系列单片机的基础上,现全力推出“1个时钟/机器周期”的单片机,全面提升8051单片机性能。

欢迎海内外厂家前来洽谈合作!新客户请直接联系深圳,以获得更好的技术支持与服务。

STC 12C5410AD系列 1T 8051 单片机 新客户请直接联系深圳以获得更好的技术支持和服务 欢迎海内外厂家前来洽谈合作 传真至深圳申请STC单片机 样片及ISP下载线/编程工具●高速:1个时钟/机器周期,RISC型8051内核,速度比普通8051快12倍●宽电压:5.5~3.4V,2.0~3.8V(STC12LE5410AD系列)●低功耗设计:空闲模式,掉电模式(可由外部中断唤醒)●工作频率:0~35MHz,相当于普通8051:0~420MHz ---实际可到48MHz,相当于8051: 0~576MHz●时钟:外部晶体或内部RC振荡器可选,在ISP下载编程用户程序时设置●12K/10K/8K/6K/4K/2K字节片内Flash程序存储器,擦写次数10万次以上●512字节片内RAM数据存储器●芯片内E2PROM功能●ISP / IAP,在系统可编程/在应用可编程,无需仿真器●10位ADC,8通道,STC12C2052AD系列为8位ADC●4通道捕获/比较单元(PWM/PCA/CCU),STC12C2052AD系列为2通道 ---也可用来再实现4个定时器或4个外部中断(支持上升沿/下降沿中断)●2个硬件16位定时器,兼容普通8051的定时器。

第10章-数字集成电路物理设计方法

20

功耗分析

• 静态功耗分析

– 利用时序库提供的器件功耗数据进行计算 – 利用物理库提供的金属物理工艺数据分析电压降和电迁移效应 – 能提供平均功耗的预估值,迅速简洁

• 动态功耗分析

– 需要提供设计的仿真数据 – VCD文件(Value Change Format):文件太大造成使用不便 – TCF文件(Toggle Count Format):结果比较粗糙,与实际情况存在差异 – CPF文件(Common Power Format):适用于功能验证、RTL综合、形式 验证、布局布线约束

7

数字集成电路物理设计流程

• 250nm工艺物理设计流程

– Timing-Driven Design, TDD – Timing-Driven Routing – Power Grid – Zero Skew

– Static Timing Analysis, STA

– Worst Case, WC – Best Case, BC – In-Place Optimization, IPO – Design Rule Violation, DRV

– Standard Design Constraints, SDC

13

展平式物理设计

自底向上的展平式设计流程及调用关系

14

硅虚拟原型设计

• 布图

– 考虑将整个设计进行分割

• 布线

– 采用快速近似的实验布线(Trial Routing)

– 所需时间约为详细布线的1/10

– 与最终结果在性能上的差距为5%~10% – 快速的设计收敛评估

– Design for Testability, DFT

– On-Chip Variation, OCV

低功耗产品开发宝典,下一个风口,必读深度好文

低功耗产品开发宝典,下一个风口,必读深度好文从2017-2018年开始,在消费类IPC还在铺天盖地增长时,悄然间在北美诞生了另一个新的消费类IPC品类,就是低功耗摄像头&门铃,海外叫Battery Camera,代表品牌有Alro ,Ring,Blink等,产品的核心变化是由常供电变成电池供电,这又是一个很大的技术革新,彻底解决了布线的问题。

因为要电池供电首先要解决的就是长时间续航问题,所以IPC在不工作时就需要处于休眠状态,而当有人走过时,要快速的从休眠状态到正常工作状态。

举个例子来说,现在我们的手机,电视,电脑等电子产品,开机时间一般也要个十秒八秒,而低功耗摄像头必须在1s 以内完成开机并录制视频,严格来讲需要在300毫秒-500毫秒内开机正常工作,要不等设备启动开始录像的时候人早就已经不在画面里了,如何实现快速启动就成为研发低功耗产品研发门槛之一。

低功耗产品由三大核心技术构成:1、快速开机,涉及主控芯片。

2、云服务器&心跳保活服务器,涉及云平台3、低功耗WIFI技术,涉及Wifi模块。

除了以上三大核心技术以外,剩下其他的就是常用IPC的软件架构逻辑了。

首先来讲下快速开机,一般情况下Linux的开机时间基本要10秒以上,目前可以支持快速开机的开源系统是Freertos,但是Freertos 系统目前行业内开发人员能熟练运用的研发人员很少,所以这个难题就只有交给芯片原厂来解决了,最早解决这个问题的芯片原厂是行业龙头海思,他们在Linux基础上开发了一套Liteost系统,开机时间可以控制在500毫秒以内,让行业内的研发人员可以继续用熟悉的Linux 方式来开发低功耗产品。

其次是芯片原厂北京君正,他们直接优化Linux内核起动速度,也可以达到500毫秒内快速启动,另外一家就是Realtek(瑞昱),用Freertos系统可以在200毫秒完成设备启动,但Freertos开发门槛相当高。

第10章最小功耗系统设计

、断开操作。要考虑电源投切过程中过渡态对 断开操作。 程 序运行的影响,要保证有充分的时序余度。 序运行的影响,要保证有充分的时序余度。

♂

§10.1 概述

●有效运行是指单片机在完成规定任务的操作运行。

§10.1 概述

二. 应用系统的功耗分析

1.系统中的有效运行与无谓等待 1.系统中的有效运行与无谓等待 ⑵有效运行的时域占空比 单片机高速运行,许多操作任务瞬间完成。 ●单片机高速运行,许多操作任务瞬间完成。相对 外围设备、人机交互、物理参数采集、 外围设备、人机交互、物理参数采集、控制执行 机构等响应周期很长。 机构等响应周期很长。 CPU执行有效运行后处于长期的无谓等待 占空比。 执行有效运行后处于长期的无谓等待— ●CPU执行有效运行后处于长期的无谓等待—占空比。

♂

§10.1 概述

三. 最小功耗系统设计内容

最小功耗系统设计包括本质低功耗、 最小功耗系统设计包括本质低功耗、功耗管理及 供电管理的软件及硬件设计。 供电管理的软件及硬件设计。 1.系统的本质低功耗设计 1.系统的本质低功耗设计

●本质功耗是指系统在有效运行状态下的功耗。 本质功耗是指系统在有效运行状态下的功耗。

♂

§10.1 概述

一. 最小低功耗系统设计的意义

2.促进便携化发展 2.促进便携化发展 最小功耗设计技术利于电子系统向便携化发展。 最小功耗设计技术利于电子系统向便携化发展。 便携式电脑、笔记本电脑是最小功耗设计的成果。 便携式电脑、笔记本电脑是最小功耗设计的成果。 3.诱人的可靠性效益 3.诱人的可靠性效益 最小功耗设计使电路全CMOS CMOS化 CMOS电路噪声容 ●最小功耗设计使电路全CMOS化,CMOS电路噪声容 可靠性提高。 限较大。--可靠性提高 限较大。--可靠性提高。 最小功耗设计方法就是要功耗管理。常采用休闲、 ●最小功耗设计方法就是要功耗管理。常采用休闲、 掉电、睡眠、关断及电源关闭等方式。--系统对 掉电、睡眠、关断及电源关闭等方式。--系统对 外界噪声失敏, 外界噪声失敏,大大减小噪声干扰产生的出错概 提高了可靠性。 率,提高了可靠性。

低功耗设计方法

低功耗设计方法《低功耗设计方法》第一章绪论1.1 什么是低功耗设计低功耗设计是一种在满足设计要求的同时,将系统耗电量降至最低的一种技术。

它采取特定的设计技巧,在软件,硬件和系统上实现降功耗,以提高系统的能效比。

1.2 低功耗设计的重要性由于现代设备的日益发展,不断的功耗需求限制了其应用范围。

因此,低功耗设计日益受到重视,在移动器件的设计,尤其是电池供电的产品中,低功耗设计变得越来越重要。

低功耗设计的应用可以提高芯片的运行效率,减少耗电和热量的产生,使产品更加可靠和可维护。

第二章软件层低功耗设计2.1 指令优化指令优化是软件设计中最重要的一项,是用来减少存储器的访问次数,减少指令的数量,从而降低总的电源消耗。

指令的优化分析可以通过提高指令的执行速度和改善指令的执行顺序,减少内存的访问,以及改变指令编译器优化或减少指令的数量来实现。

2.2 其他软件层优化软件层的优化不仅仅是指令的优化,而且包括其他优化方法,如编译器优化、算法优化、芯片和(OS)操作系统内核的优化等。

其中,最关键的就是OS内核的优化,因为它涉及到整个系统的管理和控制。

第三章硬件层低功耗设计3.1 器件选择硬件层的低功耗设计是通过合理地合适器件来实现的。

包括最小化芯片面积,减少晶体管的数量,选择符合低功耗设计要求的低功耗元件,改善行宽号,缩小指令周期,选择最佳工作频率等。

3.2 供电电路设计供电电路设计是重要的低功耗设计之一,主要涉及电源的管理、供电等级变换、供电识别、供电补偿等技术。

如果能够使用一些电源芯片,可以减少系统的供电电路的复杂度,减少功耗损耗,提高系统的效率。

第四章小结低功耗设计是一种利用硬件及软件设计技术降低系统功耗的一项技术。

它采用特定的设计技巧,在软件,硬件,系统上实现降功耗,以达到提高系统能效比的目的。

在软件设计中,采用指令优化,编译器优化,算法优化,芯片优化等方法实现降功耗。

硬件设计方面,主要是器件选择及供电设计。

低功耗设计技术解读

Copyright©博看网. All Rights Reserved.

张伟等:连铸机扇形段连铸辊轴承受力分析

2022年增刊(1)

最大程度鼓肚时铸坯与支撑辊在某点接触,其示意图如图

4所示。

-

2

'

' '

'

图 4 发生最大鼓肚时铸坯对二分节辊辊列的

作用力示意图 当发生最大鼓肚时,通过受力分析可以得到:

— 88—

t= Vl; 式中:l—从 结 晶 器 液 面 到 6段 第 七 根 辊 子 处 的 弧 线 长

度,m; V—铸坯速度,m/min; l—取 15528,V取 18。 则有 t=1515828=8627min。

δ=K槡t=27槡t=27槡8627=793mm; A = 0335(1100 ×102 -2 ×793) ×10-3 = 0323m2; Q = 7040 × 98 × 10858 × 0323 = 241964N =24186kN; 则轴承最大受力为 F2 =399%Q=24196×399% =965kN。 如果考虑到比 1100mm宽断面的铸坯,可以乘以系数 i=13,得到: F2`=F2 ×i=965×13=1255kN; 此处的轴承型号为 NSK24030.MB.C4,由轴承生产厂 家提供的数据可知 24030S.MB.C4的承载能力: F承 =C0 ×e=950kN×03=285kN; 比较后可知理想条件状态下轴承不会出现超载情况。 3 铸坯鼓肚 铸坯鼓肚是连铸生产中一种特有的现象,铸坯在凝固 过程中,钢水静压力的作用,使两个辊之间的坯壳向外凸 起,所以,在凝固末端之前形成铸坯鼓肚是必然的。在浇 注过程中,鼓肚的形态在相邻两辊之间呈“面包状”,即中 间区域较两边以及与辊列的接触区域高,其差值称之为鼓 肚量,如图 3所示。

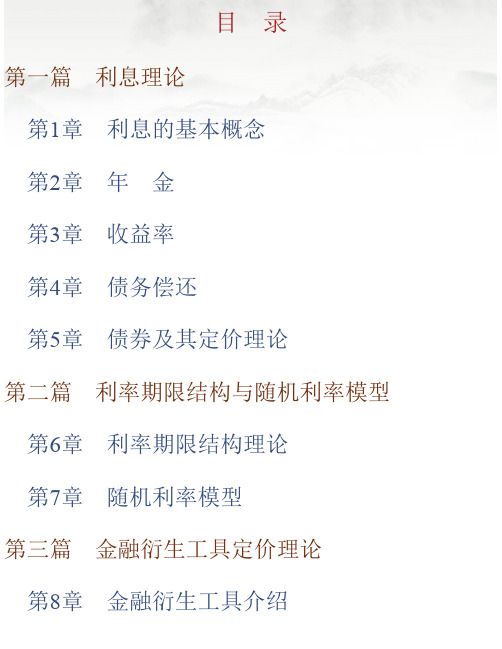

2020年春季中国精算师《金融数学》过关必做1000题(含历年真题)

目 录第一篇 利息理论第1章 利息的基本概念第2章 年 金第3章 收益率第4章 债务偿还第5章 债券及其定价理论第二篇 利率期限结构与随机利率模型第6章 利率期限结构理论第7章 随机利率模型第三篇 金融衍生工具定价理论第8章 金融衍生工具介绍第9章 金融衍生工具定价理论第四篇 投资组合理论第10章 投资组合理论第11章 CAPM和APT附 录 2011年秋季中国精算师考试《金融数学》真题及详解第一篇 利息理论第1章 利息的基本概念单项选择题(以下各小题所给出的5个选项中,只有一项最符合题目要求,请将正确选项的代码填入括号内)1.已知在未来三年中,银行第一年按计息两次的名义年利率10%计息,第二年按计息四次的名义年利率12%计息,第三年的实际年利率为6.5%。

某人为了在第三年末得到一笔10000元的款项,第一年年初需要存入银行( )元。

[2011年秋季真题]A.7356B.7367C.7567D.7576E.7657【答案】C【解析】由名义年利率和实际年贴现因子的等价关系,可得:每年的贴现因子分别为,,。

因此,第三年末10000元的款项在第一年初的现值为:。

2.已知0时刻在基金A中投资1元到2t时的积累值为(3t+1)元,在基金B中投资1元到3t时的积累值为元。

假设在T时基金B的利息强度为基金A的利息强度的两倍,则0时刻在基金中B投资1000元在5T时的积累值为( )元。

[2011年秋季真题]A.27567B.27657C.27667D.27676E.27687【答案】C【解析】由题得,0时刻在基金A中投资1元到t时的积累值为(1.5t+1)元,即积累因子,利息强度在基金B中投资1元到3t时的积累值为元,因此在基金B中投资1元到t时的积累值为元,因此。

当时,即,解得,因此0时刻在基金中B投资1000元在5T时的积累值为元。

3.已知某基金的积累函数a(t)为三次函数,每三个月计息一次,第一季度每三个月计息一次的年名义利率为10%,第二季度每三个月计息一次的年名义利率为12%,第三季度每三个月计息一次的年名义利率为15.2%,则为( )。

《系统级芯片(SoC)设计》课程思政案例

《系统级芯片(SoC)设计》课程思政案例(一)教学设计:《系统级芯片(SoC)设计》课程在大四第一学期讲授,教学过程中遇到如下问题:(1)课程难度较高,与考研复习冲突,在学习过程中,学生存在较大的畏难情绪,学习的内生动力不足;(2)课程需要用到学生前三年学习的基础知识,但由于各部分内容分散在不同时间段,学生综合运用这些理论知识解决复杂工程问题的能力不强;(3)为追求学业成绩,大部分学生陷于理论知识的学习,参与实践的意愿不强烈,动手实践和创新能力较弱。

根据《系统级芯片(SoC)设计》的课程特点,在课堂讲授、实验、课后作业、课程设计大作业等环节,从系统级芯片的世情、国情、行情以及设计方法论等层面,深入挖掘课程的思政元素,建设课程思政案例5个,拓展专业课程的广度和深度,教学设计形成以下特色:(1)充分结合中美贸易战、芯片“卡脖子”的时事以及集成电路产业链现状分析,激发学生的学习兴趣与科技报国的家国情怀和使命担当。

(2)以解决系统级芯片设计面临的挑战为主线,分析研讨设计技术的原理,把设计方法论和科学精神的培养结合起来,提高学生正确认识问题、分析问题和解决问题的能力。

(3)在课堂教学和实验环节,融入国内外系统级芯片设计技术的最新进展,在增强民族自豪感的同时,意识到精益求精的重要性,培养学生的工匠精神。

(4)校企协同,将华为课程资源--昇腾310 AI推理SoC作为案例,介绍SoC架构的特点,使学生切身体会到我国集成电路行业的先进技术。

(一)案例名称:SoC低功耗设计(二)案例教学目标理解CMOS电路的功耗来源,掌握低功耗设计技术的原理;了解国内外超级计算机的发展现状,使学生感受我国科技和经济实力的快速发展,增强民族自豪感,培养精益求精的工匠精神。

(三)案例教学实施过程第一节概述为了讲解低功耗技术,首先让学生了解针对不同的应用领域(超级计算机/数据中心,消费类电子设备,移动电子设备,生物芯片等),芯片功耗的区间不同,低功耗的概念是相对的。

【浙江省自然科学基金】_低功耗设计_期刊发文热词逐年推荐_20140811

2013年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

科研热词 霍尔效应 运算放大器(op-amp) 超低功耗设计 绝热多米诺电路 电动助力转向 有源器件并联 无线抄表 数据转换器 开关信号理论 多值逻辑 低噪声放大器 低功耗 传感器 交叉耦合 zigbee技术 t运算电路 delta-sigma调制器 cc2430

推荐指数 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2010年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

科研热词 推荐指数 低功耗 2 风能发电机 1 门控时钟 1 量子细胞自动机 1 通用阈值逻辑门 1 路由 1 能量获取与管理 1 电路设计 1 时序电路 1 无线传感网 1 心电监护 1 开关-信号理论 1 太阳能光伏电池 1 多值逻辑 1 冗余抑制 1 zigbee无线传感器网络节点 1 qca电路 1 qca designer软件 1

2011年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

2011年 科研热词 电路设计 低功耗 开关信号理论 多值逻辑 负电容电路 负压吸附机构 计数器 综述 绝热电路 绝热 电路与系统 现代温室 爬壁机器人 无线通信技术 开关一信号理论 带宽 加法器 加减法计数器 功耗 低能耗设计 三值逻辑 t运算 tctgal电路 d触发器 8值逻辑 2.4 ghz频段 2-4混值 推荐指数 3 3 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

数字集成电路物理设计

数字集成电路物理设计作者:陈春章艾霞王国雄出版社:科学出版社出版日期:2008年1月页数:285 装帧:开本:16 版次:商品编号:2022071 ISBN:703022031 定价:36元丛书序前言第1章集成电路物理设计方法1.1数字集成电路设计挑战1.2数字集成电路设计流程l.2.1展平式物理设计1.2.2硅虚拟原型设计1.2.3层次化物理设计1.3数字集成电路设计收敛1.3.1时序收敛1.3.2功耗分析1.3.3可制造性分析1.4数字集成电路设计数据库1.4.1数据库的作用与结构1.4.2数据库的应用程序接口1.4.3数据库与参数化设计1.5总结习题参考文献第2章物理设计建库与验证2.1集成电路工艺与版图2.1.1 CMOS集成电路制造工艺简介2.1.2 CMOS器件的寄生闩锁效应2.1.3版图设计基础2.2设计规则检查2.2.1版图设计规则2.2.2 DRC的图形运算函数2.2.3 DRC在数字IC中的检查2.3电路规则检查2.3.1电路提取与比较2.3.2电气连接检查2.3.3器件类型和数目及尺寸检查数字集成电路物理设计2.3.4 LVS在数字IC中的检查2.4版图寄生参数提取与设计仿真2.4.1版图寄生参数提取2.4.2版图设计仿真2.5逻辑单元库的建立2.5.1逻辑单元类别2.5.2逻辑单元电路2.5.3物理单元建库与数据文件2.5.4时序单元建库与数据文件2.5.5工艺过程中的天线效应2.6总结习题参考文献第3章布图规划和布局3.1布图规划3.1.1布图规划的内容和目标3.1.2 I/0接口单元的放置与供电3.1.3布图规划方案与延迟预估3.1.4模块布放与布线通道3.2电源规划3.2.1电源网络设计3.2.2数字与模拟混合供电3.2.3时钟网络3.2.4多电源供电3.3布局3.3.1展平式布局3.3.2层次化布局3.3.3布局目标预估3.3.4标准单元布局优化算法3.4扫描链重组3.4.1扫描链定义3.4.2扫描链重组3.5物理设计网表文件3.5.1设计交换格式文件3.5.2其他物理设计文件3.6总结习题参考文献第4章时钟树综合4.1时钟信号4.1.1系统时钟与时钟信号的生成4.1.2时钟信号的定义4.1.3时钟信号延滞4.1.4时钟信号抖动4.1.5时钟信号偏差4.2时钟树综合方法4.2.1时钟树综合与标准设计约束文件4.2.2时钟树结构4.2.3时钟树约束文件与综合4.3时钟树设计策略4.3.1时钟树综合策略4.3.2时钟树案例4.3.3异步时钟树设计4.3.4锁存器时钟树4.3.5门控时钟4.4时钟树分析4.4.1时钟树与时序分析4.4.2时钟树与功耗分析4.4.3时钟树与噪声分析4.5总结习题参考文献第5章布线5.1全局布线5.1.1全局布线目标5.1.2全局布线规划5.2详细布线5.2.1详细布线目标5.2.2详细布线与设计规则5.2.3布线修正5.3其他特殊布线5.3.1电源网络布线5.3.2时钟树布线5.3.3总线布线数字集成电路物理设计5.3.4实验布线5.4布线算法5.4.1通道布线和面积布线5.4.2连续布线和多层次布线5.4.3模块设计和模块布线5.5总结习题参考文献第6章静态时序分析6.1延迟计算与布线参数提取6.1.1延迟计算模型6.1.2电阻参数提取6.1.3电容参数提取6.1.4电感参数提取6.2寄生参数与延迟格式文件6.2.1寄生参数格式sPF文件6.2.2标准延迟格式SDF文件6.2.3 sDF文件的应用6.3静态时序分析6.3.1时序约束文件6.3.2时序路径与时序分析6.3.3时序分析特例6.3.4统计静态时序分析6.4时序优化6.4.1造成时序违例的因素6.4.2时序违例的解决方案6.4.3原地优化6.5总结习题参考文献第7章功耗分析7.1静态功耗分析7.1.1反偏二极管泄漏电流7.1.2门栅感应漏极泄漏电流7.1.3亚阈值泄漏电流7.1.4栅泄漏电流7.15静态功耗分析第8章信号完整性分析第9章低功耗设计技术与物理实施第10章芯片设计的终验证与签核附录索引数字专用集成电路的设计与验证本书作者:杨宗凯,黄建,杜旭编著第1章概述1.1 引言1.2 ASIC的概念1.3 ASIC开发流程1.4 中国集成电路发展现状第2章Verilog HDL硬件描述语言简介2.1 电子系统设计方法的演变过程2.2 硬件描述语言综述2.3 Verilog HDL的基础知识2.4 Verilog HDL的设计模拟与仿真第3章ASIC前端设计3.1 引言3.2 ASIC前端设计概念3.3 ASIC前端设计的工程规范3.4 设计思想3.5 结构设计3.6 同步电路3.7 ASIC前端设计基于时钟的划分3.8 同步时钟设计3.9 ASIC异步时钟设计4.10 小结第4章ASIC前端验证4.1 ASIC前端证综述4.2 前端验证的一般方法4.3 testbench4.4 参考模型4.5 验证组件的整合与仿真4.6 小结第5章逻辑综合5.1 综合的原理和思路5.2 可综合的代码的编写规范5.3 综合步骤5.4 综合的若干问题及解决……第6章可测性技术第7章后端验证附录A 常用术语表附录B Verilog语法和词汇惯用法附录C Verilog HDL关键字附录D Verilog 不支持的语言结构参考文献yoyobao编号:book194094作者:杨宗凯,黄建,杜旭编著(点击查看该作者所编图书)出版社:电子工业出版社(点击查看该出版社图书)出版日期:2004-10-1ISBN:7121003783装帧开本:胶版纸/0开/ 0页/480000字版次:1原价:¥28VLSI设计方法与项目实施点击看大图市场价:¥43.00 会员价:¥36.55【作者】邹雪城;雷鑑铭;邹志革;刘政林[同作者作品]【丛书名】普通高等教育“十一五”规划教材【出版社】科学出版社【书号】9787030194510【开本】16开【页码】487【出版日期】2007年8月【版次】1-1【内容简介】本书以系统级芯片LCD控制器为例,以数模混合VLSI电路设计流程为线索,系统地分析了VLSI系统设计方法,介绍了其设计平台及流行EDA软件。

【计算机系统应用】_低功耗设计_期刊发文热词逐年推荐_20140726

推荐指数 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2010年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25

科研热词 低功耗 餐饮管理模式 锂亚电池 链路通信 网络节点 组网 纹波 监测终端 现场可编程门阵列 流水线 毛刺 智能家居 无线传感器网络 开关电源 嵌入式usb主机 功率放大器 乘累加单元 主动电磁轴承 zigbee技术 zigbee pwm msp430 gprs fpga设计 ch375

2014年 序号 1 2 3 4 5

2014年 科研热词 载波侦听退避算法 低功耗设计 stm32f103cb simpliciti协议 adf7021 推荐指数 1 1 1 1 1

Hale Waihona Puke 2008年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

科研热词 车载gps导航 确定测试 电子地图 生物拖网 深海 折叠集 折叠矢量 嵌入式操作系统 低功耗设计 伪单输入跳变 人体感应 rs485 pxa310 modbus c8051f020

推荐指数 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

推荐指数 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

2011年 序号 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19

2011年 科研热词 超宽带 监控系统 多视点视频编码 全景视频 体域网 静态工作电流 阅读器 轮胎压力监测系统 超低功耗 管网 有源标签 智能终端产品 数据采集模块 微安 动态功耗 zigbee z-stack协议栈 rfid ata5749芯片 推荐指数 2 2 2 2 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1

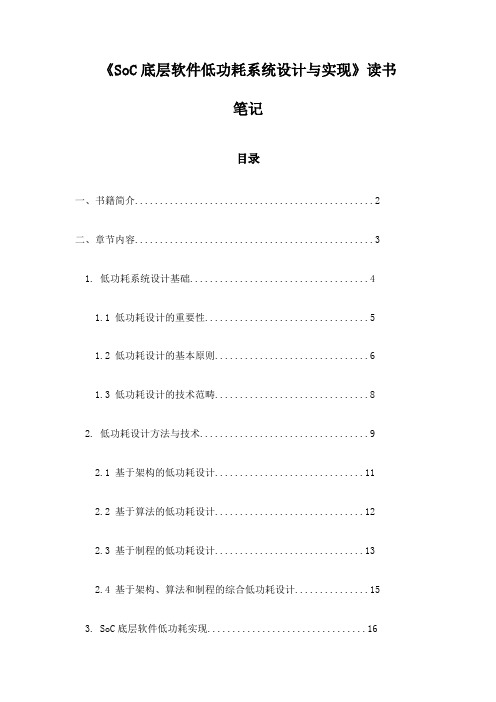

《SoC底层软件低功耗系统设计与实现》记录

《SoC底层软件低功耗系统设计与实现》读书笔记目录一、书籍简介 (2)二、章节内容 (3)1. 低功耗系统设计基础 (4)1.1 低功耗设计的重要性 (5)1.2 低功耗设计的基本原则 (6)1.3 低功耗设计的技术范畴 (8)2. 低功耗设计方法与技术 (9)2.1 基于架构的低功耗设计 (11)2.2 基于算法的低功耗设计 (12)2.3 基于制程的低功耗设计 (13)2.4 基于架构、算法和制程的综合低功耗设计 (15)3. SoC底层软件低功耗实现 (16)3.1 SoC底层软件的低功耗设计策略 (17)3.2 基于处理器架构的底层软件低功耗实现 (18)3.3 基于芯片架构的底层软件低功耗实现 (20)3.4 基于操作系统级别的底层软件低功耗实现 (21)4. 具体案例分析 (23)4.1 案例一 (24)4.2 案例二 (25)4.3 案例三 (27)5. 总结与展望 (28)5.1 本书总结 (29)5.2 未来低功耗设计的发展趋势 (31)三、个人学习体会 (32)一、书籍简介本书详细探讨了在现代电子设备中,如何有效地管理和优化SoC 的功耗,以延长设备的电池寿命和提高整体性能。

本书不仅涵盖了理论知识,还结合了大量实际案例和工程实践,为读者提供了一个全面、系统的学习体验。

本书首先从SoC的基本概念开始介绍,帮助读者了解SoC在嵌入式系统中的重要地位和作用。

深入探讨了低功耗设计的重要性和必要性,阐述了在现代电子设备中,功耗管理已成为一个不可忽视的关键因素。

本书详细介绍了低功耗系统设计的原理、方法和技巧,包括电源管理、时钟管理、休眠模式设计、软硬件协同优化等方面的内容。

本书还介绍了与低功耗设计紧密相关的技术,如嵌入式操作系统、微控制器编程、硬件抽象层(HAL)和驱动开发等。

这些内容的介绍为读者提供了更为广泛的知识背景和视角,帮助读者更加深入地理解和应用所学知识。

《SoC底层软件低功耗系统设计与实现》是一本实用性强、内容丰富的书籍。

数字电路低功耗设计(二)

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析。

由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具;更精确的功耗分析可以采用PT,关于PT的功耗分析可以查阅其他资料,这里不涉及使用PT的进行功耗分析。

<1>功耗分析与流程概述上一个小节中讲解了功耗的构成,并且结合工艺库进行简要地介绍了功耗的计算。

但是实际上,我们根本不可能人工地计算实际的大规模集成电路的功耗,我们往往借助EDA工具帮我们分析电路的功耗。

这里我们就介绍一下EDA工具分析功耗的<普遍>流程,然后下一小节我们将介绍低功耗电路的设计和优化。

①功耗分析流程的输入输出功耗分析的流程<从输入输出关系看>如下所示:上面的图中,需要四种东西:·tech library:这个就是包含功耗信息的工艺库了,比较精确的库里面还应该包含状态路径<SDPD>信息,代工厂提供。

·netlist:设计的门级网表电路,可以通过DC综合得到。

·parasitic:设计中连线等寄生参数,比如寄生电容、寄生电阻,这个一般是后端RC寄生参数工具提供,简单的功耗分析可以不需要这个文件。

·switch activity:包含设计中每个节点的开关行为情况,比如说节点的翻转率或者可以计算出节点翻转率的文件。

这个开关行为输入文件是很重要的。

这个开关行为可以有不同的形式提供,因此就有后面不同的分析功耗的方法。

〔注意,不管使用什么方法进行功耗分析,功耗分析的时候,输入设计文件的都是门级网表文件②开关行为的一些概念说到开关行为,我们前面的翻转率也是一种开关行为。

此外我们还有其他关于开关行为描述的概念,这里我们通过举例说明,如下图所示:·翻转<次>数:逻辑变化的次数,上图中信号的翻转数为3.·翻转率:前面也有相关介绍,这里重提一下,翻转率是单位时间内信号<包括时钟、数据等等信号>的翻转次数。

超大规模集成电路中低功耗设计与分析

随着IC设计的规模更大,速度更快,以及便携式设备的广泛需求,设计中功耗的问题越来越凸现出来,所以在整个设计流程中就需要对功耗进行分析和低功耗设计,这些技术可以保证芯片的每一部分都能高效、可靠、正确地工作。

选择合适的低功耗手段,必须以细致的功耗预估为前提,并且也要掌握工具的适用范围和能达到的低功耗底限。

在流程中尽可能早的分析出功耗需求,可以避免和功耗相关的设计失败。

通过早期的分析,可以使用高层次的技巧来降低大量的功耗,更容易达到功耗的要求。

本论文围绕数字CMOS电路的功耗问题进行展开,主要分成两大部分。

首先针对超大规模集成电路中的功耗分析进行探讨,介绍了在RTL级、门级不同层次上对功耗进行分析的方法和对实际设计的指导意义,并对一个450万门的超大规模芯片在各层次上进行功耗分析,并和流片后测试得到的结果有着很好的吻合。

然后是对低功耗进行了一些结构上的设计。

动态电压缩放(DVS)技术是一种通过将不同电路模块的工作电压调低到恰好满足系统最低要求来实时降低系统中不同电路模块功耗的方法,有着良好的应用前景。

本论文实现了一款动态电压缩放(DVS)电路,可应用于突发吞吐量工作模式的处理器,通过和一个电路实例的整体仿真,验证了该DVS电路的低功耗效果。

关键字:低功耗;功耗分析;动态电压缩放Liu Hainan (Microelectronics and Solid-State Electronics)Directed by Professor Zhou YumeiAs the design of IC go into larger and faster, the issue about power consumption is more critical. It is necessary to analysis the power accurately and manage low power techniques in every step of the design flow, so as to assure the efficient, reliable and correct function.Choosing the appropriate low power solutions depends on careful power analysis as well as understanding the capabilities of available tools. Analyzing power requirements as early as possible in the design flow helps avoid power related disasters. Early analysis also makes power goals easier to attain because higher-level techniques save the greatest amount of power.The thesis is made up of two main parts based on the discussion of the digital CMOS power consumption.First of all, this thesis introduces and demonstrates a top-down VLSI design methodology for power analysis, discuss the method to estimate the power on RTL and gate level, which could serve as a guide to the floorplan and place & route. And estimate the power consumption about a 4.5 million VLSI on several level, draw some conclusion from comparing the test result of the fabricated chip.In the second, completed a low power technique on the structure level. Dynamic V oltage Scaling is a technique using the lowest level voltage in real time on different block dramatically reducing energy consumption, while maintaining the desired level of performance, which has a nice prospect to realize low power. The thesis has developed a DVS circuit, which could get the corresponding lowest voltage according to the system frequency. Take a 16X16 multiplier as a test circuit to simulate together, proving the low power action of DVS.Keyword:low power, power analysis, Dynamic V oltage Scaling摘 要 (Ⅰ)目 录 (Ⅲ)第一章 绪论 (1)1.1 前言 (1)1.2 低功耗设计研究的现状 (2)1.3 论文的内容与安排 (3)第二章 低功耗设计方法 (5)2.1 功耗模型 (5)2.2 低功耗设计方法 (6)2.3 各个层次上的功耗预估 (13)2.4 450万门超大规模芯片的功耗预估 (20)第三章 动态电压缩放电路 (24)3.1 DVS概述 (24)3.2 DVS的适用范围 (28)3.3 DVS的应用 (31)3.4 DVS的性能指标 (32)3.5 动态DC-DC转换器的设计考虑 (34)第四章 动态电压缩放控制电路的实现 (41)4.1 DVS原理框图 (41)4.2 电路的实现 (43)4.3 电路的仿真与低功耗验证 (53)第五章 总结 (57)参考文献 (58)发表文章目录 (60)致 谢 (61)第一章绪论第一章绪论一、前言随着微电子技术的迅猛发展,最突出的表现是特征尺寸的不断缩小,集成度遵从摩尔定律不断提高。

浅谈CMOS集成电路低功耗设计

浅谈CMOS集成电路低功耗设计李名扬 20102466摘要:本文在对CMOS电路功耗来源分析的基础上,提出了降低电源电压、降低负载电容、降低开关活动性跳变率、调整晶体管的尺寸、降低MOS管的阈值电压等降低功耗的方法,然后介绍了CMOS集成电路低功耗设计中应注意的问题,最后对未来CMOS集成电路的发展进行了展望。

关键词:CMOS集成电路,低功耗,阈值电压,门控时钟1引言随着CMOS集成电路的规模越来越大,工作频率不断提高,芯片的功耗也越来越大,这就给电路的使用带来了两个负面的影响。

首先,为延长工作时间需要提高电源性能;其次,由于电路只能在一定的温度范围内工作,需要更精确的封装和良好的散热性能,这无疑会增加成本。

功耗特别是功耗密度问题变得越来越突出,将成为影响电路性能的关键问题。

功耗密度的增加将引起芯片温度升高,影响电路的可靠性,芯片温度每升高10℃,器件寿命将减少一半。

为了避免芯片发热,则要花费更多的成本解决芯片封装和冷却问题。

另外,VLSI的发展使整机体积缩小,促进了各种微小型的便携机和便携式设备的发展。

靠电池供电的便携式设备及航空航天设备都需要低功耗电路以维持更长的电池寿命。

因此,降低功耗是CMOS集成发展的需求,低功耗设计已成为一个关键的设计考虑。

以下从低功耗技术研究的意义开始,逐步介绍一下有关CMOS集成电路低功耗设计的方法及注意问题。

2低功耗技术的研究意义低功耗技术是上世纪九十年代开始由于实际应用需要受到广泛关注而迅速发展起来的,并且在集成电路设计中的重要性也随着工艺的发展越来越凸显。

促进低功耗技术研究的因素有很多,概括起来主要有以下几点:1.电路的可靠性电路的功耗将转化为热量而释放出来,过多的热量将导致期间工作温度升高,继而降低系统的可靠性,导致许多问题产生。

工作温度过高将使各种制造是的轻微物理缺陷所造成的故障显现出来,如桥接故障。

温度的提高意味着电迁移率的增加,当芯片温度上升到一定程度时,电路将无法正常工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第十章低功耗设计

功耗是成功应用的关键:

(1)功耗是便携式应用的关键:

¾便携式计算量日益增加,

便携设备功耗日益增加

¾功耗决定了电池寿命

(2)功耗是高性能应用的关键:

¾最高性能始终是追求目标

¾高性能设计受限于功耗

¾功耗决定了冷却和能耗成本

据2000年统计:全世界4 亿台个人

12

计算机每年消耗0.16 * 10 kWh 能量

相当于26 个核电站。

V dd

V dd

V dd

C L

功耗与数据的翻转概率相关

功耗与节点的翻转活动性有关

一个CMOS门在N 个时钟周期中的翻转能量为:

N个时钟周期中的翻转能量

N个时钟周期中0 1 的翻转次数

翻转活动性(概率):

等效电容:

静态CMOS 电路中的尖峰寄生信号(Glitching )

又称为“dynamic hazards ”NOR 门逻辑链

Glitch 的产生

存在尖峰寄生信号时,虽然输出结果最终正确,但尖峰寄生信号将产生额外的功耗。

¾I DS与V DS的关系

对于当前工艺,漏

极漏电的变化范围

相差

影响因数:

漏极漏电流为扩散电流(类似于双极晶体管),与阈值电压V T

漏极漏电流(亚阈值漏电)

¾I DS与V GS的关系

漏极漏电流随V GS按指数规律增长(DIBL)

亚阈值斜率约为:70mV/dec

薄栅氧中的隧穿

I /E ( MV /cm)

-1

( A ·cm /MV )

22 I ox /E

FN 隧穿

直接隧穿

栅电流与栅电压及栅氧厚度的关系

隧穿

Gate Voltage (V )

栅电流密度( A /cm )

2 t ox

I on I ds I off

I off 栅氧隧穿电流

2. 栅极漏电流

¾栅电流构成了总漏电电流的一部分

¾与亚阈值电流无关¾I GD ~e e ¾

I GS ~e e

¾NMOS 的栅漏电流通常比PMOS 严重

¾BSIM3v3 和BSIM4中均考虑栅漏电流,V gs

-T ox V gd -T ox

漏电情况日趋严重:

漏电能耗的增长将超过动态能耗

0.0

(3)短路电流功耗

短路电流~0短路电流达最大负载较大负载较小

第二节低能耗/功耗设计问题

分层的优化步骤

能耗和面积

能耗

能耗

不同的优化目标:

能耗、工作功耗、漏电功耗

第三节通过调整电路参数降低能耗/功耗优化能耗/功耗必须满足延时约束条件

每操作的能耗

拓扑A

拓扑B

全局优化

边界曲线

延时

(1)根据电路特点优化能耗

(1)反相器链(2)存储器译码器:

(3)树结构加法器:

¾分支多

¾大多数门不翻转

¾布线长¾路径重聚

¾多个输出同时翻转

每操作的能耗拓扑A

拓扑B

延时

(4)通过参数对能耗和延时灵敏度的分析优化能耗

能耗-延时的灵敏度

路径数目延时目标延时原始的延时分布优化后的延时分布

对于

同时调整(优化结果:

延时增加(%)

能量减少(%)D /D ref 灵敏度

第四节提高数据处理并行度以降低电源电压

¾关键路径延时=T adder + T comparator (=25ns )

f ref = 40MHz ¾被充放电(switched )的总电容=C ref

¾V dd = Vr ef = 5v

¾参照数据通路的功耗=P ref =C ref ·Vref ·f ref 2

比较器

加法器

参照数据通路

(一)采用并行结构的数据通路

加法器比较器

¾采用两路并行处理,当达到同样的数据处理量(throughput )时:时钟频率可降低至½: f par = f ref /2 ,电源电压可降低至V par =Vref /1.7 ¾C par = 2.15C ref ¾并行结构功耗:P par =(2.15C ref )·(Vref /1.7)·(f ref /2)= 0.36 P ref 2并行结构的数据通路

(二)采用流水线结构的数据通路

加法器

比较器

¾关键路径延时减小,由max [ T adder , T comparator ]确定;

¾在保持时钟频率不变(即f pipe

= f ref )的情况下,电源电压可以降低为:

V dd = Vr ef/1.7

¾被充放电(switched )的总电容略有增加:C pipe =1,15C ref

¾流水线结构的功耗:P pipe = (1.15C ref )·(Vref /1.7)·f ref = 0.39 P ref

2

流水线结构的数据通路

数据处理量相同、采用不同结构时

数据通路的面积和功耗

结构类型电源电压面积功耗

简单结构

(无流水线或并行结构)

流水线结构

并行结构

流水线+并行结构

不同结构(Architecture)

对设计灵活性及能耗的影响

设

计

灵

活

性

能耗

电平转换器关键路径关键路径

与两种电压(V L /V H )的比值之间的关系:

功耗降低比例与(V L /V H )比值的关系(理论计算值)

((因此,当采用两种电源电压(V L /V H )供电时,为使功耗最小,应

V L /V H

功耗降低的比例(R )

采用不同数目的电源电压时优化前后的功耗比

优

化

的

各

个

电

源

电

压

比

优

化

前

后

的

功

耗

比

(1)采用的电压种类越多,功耗越低,但功耗降低的效果趋于饱和,因此一般采用两种电源电压。

最优的V2/V1在0.7附近。

(2)电源电压降低时,或V TH /V DD较大时,采用多种电源电压降低功耗的效果减小

(1)尽快计算(ASAP )原则:总是实现高数据处理量

对可变处理速率的传统设计方法:电源电压(VDD )保持不变

(2)降低时钟频率:能量/每操作保持不变,但数据处理量随频率降低而减少过高的处理量

降低

实现的

数据处理量

实现的

数据处理量第六节动态电压调整

动态电压调整

改变动态调整

实现的

数据处理量

¾根据实际实现的数据处理量,动态地降低能量/每操作

¾总是尽可能降低速度,以使能量/每操作降到最低程度

¾对于完全相同的硬件,采用动态调整电压可以使电池寿命延长多至10倍

(一)利用计算量与数据输入量(速率)相关的特点调整电源电压

(二)利用计算量随时间变化的特点调整电源电压

景色改变时要求的计算量很大

所要求的计算量与(帧与帧之间)图像变化的情况(改变的程度)有关 虽然输入数据量相同(输入图像帧数不变),但计算量随时间而变 利用计算量随时间变化的特点来调整电源电压

计算负荷

比较当前图像

与前一帧图像接收器已更新了图像

(三)利用计算量的统计特性来确定电源电压的调整范围MPEG 离散余弦反变换(IDCT)的典型统计特性

尽快计算(ASAP)

优化算法

启发式算法(ZERO)归一化的能耗

(五)通过软硬件协同设计动态降低功耗

Clock V DD

要求的

速度

要求的速度

归

一

化

的

功

耗超线性增长如没有必要特别快的速度,尽可能减速以节省功耗。

因此,操作系统(软件)应综合考虑确定硬件工作的速度(频率)

设定V DD和f CLK的控制环路

¾反馈环设置V DD,使F ERR0

¾环振的延时与CPU 的关键路径相匹配

¾全定制的环路设计:可以优化C DD

由操作系统决定

所希望的频率。