cadence后仿教程

CADENCE仿真流程

CADENCE仿真流程1.设计准备在进行仿真之前,需要准备好设计的原理图和布局图。

原理图是电路的逻辑结构图,布局图是电路的物理结构图。

此外,还需要准备好电路的模型、方程和参数等。

2.确定仿真类型根据设计需求,确定仿真类型,包括DC仿真、AC仿真、时域仿真和优化仿真等。

DC仿真用于分析直流电路参数,AC仿真用于分析交流电路参数,而时域仿真则用于分析电路的时间响应。

3.设置仿真参数根据仿真类型,设置仿真参数。

例如,在DC仿真中,需要设置电压和电流源的数值;在AC仿真中,需要设置信号源的频率和幅度;在时域仿真中,需要设置仿真的时间步长和仿真时间等。

4.模型库选择根据设计需求,选择合适的元件模型进行仿真。

CADENCE提供了大量的元件模型,如晶体管、二极管、电感、电容等。

5.确定分析类型根据仿真目标,确定分析类型,例如传输功能分析、噪声分析、频率响应分析等。

6.仿真运行在仿真运行之前,需要对电路进行布局和连线。

使用CADENCE提供的工具对电路进行布局和连线,并生成物理设计。

7.仿真结果分析仿真运行后,CADENCE会生成仿真结果。

利用CADENCE提供的分析工具对仿真结果进行分析,观察电路的性能指标。

8.优化和修改根据仿真结果,对电路进行优化和修改。

根据需要,可以调整电路的拓扑结构、参数和模型等,以改进电路的性能。

9.再次仿真和验证根据修改后的电路,再次进行仿真和验证,以确认电路的性能指标是否得到改善。

最后需要注意的是,CADENCE仿真流程并不是一成不变的,根据具体的设计需求和仿真目标,流程可能会有所调整和修改。

此外,CADENCE还提供了许多其他的工具和功能,如电路板设计、封装设计、时序分析等,可以根据需要进行使用。

CADENCE仿真步骤

CADENCE仿真步骤

Cadence是一款电路仿真软件,它可以帮助设计师创建、分析和仿真

电子电路。

本文将介绍Cadence仿真的步骤。

1.准备仿真结构:第一步是准备仿真结构。

我们需要编写表示电路的Verilog或VHDL代码,然后将它们编译到Cadence Integrated Circuit (IC) Design软件中。

这会生成许多文件,包括netlist和verilog等文件,这些文件将用于仿真。

2.定义仿真输入输出信号:接下来,我们需要定义仿真的输入信号和

输出信号。

输入信号可以是电压、电流、时间和其他可测量的变量。

我们

需要定义输入信号的模拟和数字值,以及输出信号的模拟和数字值。

3.定义参数:参数是仿真中用于定义仿真设计的变量,这些变量可以

是仿真中电路的物理参数,如电阻、电容、时延、输入电压等,也可以是

算法参数,如积分步长等。

4.运行仿真:在所有参数和信号都设置完成后,我们可以运行仿真。

在运行仿真之前,可以使用自动参数检查来检查参数是否正确。

然后,使

用“开始仿真”命令即可启动仿真进程。

5.结果分析:在仿真结束后,我们可以使用结果分析器来查看输出信

号的模拟和数字值,以及仿真中电路的其他特性,如暂态分析、稳态分析、功率分析等。

以上就是Cadence仿真步骤。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (5)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (8)一、schematic电路图绘制 (8)二、版图设计 (25)画版图一些技巧: (35)三、后端验证和提取 (37)第三节后端仿真 (44)其它知识 (48)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压VDD=1.8V,MOS管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W 不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同) MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在windowXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看 .MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre的license只在linux重启或者刚开启的时候运行一次就可以了。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (4)2、然后桌面右键重新打开Terminal (6)双反相器的后端设计流程 (7)一、schematic电路图绘制 (7)二、版图设计 (21)画版图一些技巧: (30)三、后端验证和提取 (31)第三节后端仿真 (37)其它知识 (40)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top 处单击这些节点即可查看波形请单击此处的Top 查看如果要查看测量语句的输出结果请查看 .MTO 文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence 软件)一、开启linux 系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

cadence 教程

cadence 教程Cadence 是一种电子设计自动化工具,常用于模拟、验证和布局设计。

它可以帮助工程师在各种电子系统中设计和验证电路,从而提高电路设计的效率和可靠性。

下面将介绍一些 Cadence 的基本使用方法和技巧。

1. 创建新项目要使用 Cadence,首先需要创建一个新项目。

可以通过菜单栏上的"File" -> "New"来创建新项目。

然后输入项目名称、路径等信息,并选择适当的项目类型。

2. 添加电路在 Cadence 中,可以通过绘制电路原理图来添加电路。

可以使用"Create Schematic"工具来创建新的电路原理图。

在绘制电路原理图时,注意使用正确的元件符号和连线方式。

3. 设置仿真参数在进行电路仿真之前,需要设置仿真参数。

可以通过菜单栏上的"Simulator" -> "Edit Simulation"来打开仿真设置窗口。

在仿真设置窗口中,可以设置仿真类型(如DC、AC、Transient 等)、仿真时间范围、仿真步长等参数。

4. 运行仿真设置好仿真参数后,可以通过菜单栏上的"Simulator" -> "Run Simulation"来运行仿真。

运行仿真后,可以查看仿真结果,如电压波形、电流波形等。

5. 进行验证在验证电路设计时,可以使用 Cadence 提供的调试工具和验证功能。

可以通过菜单栏上的"Debug" -> "Start Debugging"来启动调试。

在调试过程中,可以查看电路元件的属性、信号的波形等信息,以发现和解决问题。

6. 进行布局设计在电路设计完成后,可以进行布局设计。

可以使用 Cadence 提供的布局工具来布局电路版图。

布局时,要注意合理安排电路元件的位置和走线方式,以满足电路设计的要求。

cadence原理图仿真

cadence原理图仿真

在进行Cadence原理图仿真时,我们需要注意以下几点,以确保仿真结果的准确性和可靠性:

1. 确认所使用的元件符合仿真要求,并正确地添加到原理图中。

这包括在仿真库中选择合适的元件模型,并将其与其他元件正确地连接起来。

2. 确认仿真的电源和接地连接正确无误。

确保电源和地线的连接不会导致任何不良影响,如电压下降或噪声干扰。

3. 设置仿真参数,如仿真时间、仿真步长等。

根据所需的仿真精度和仿真效率,选择适当的仿真参数。

4. 进行信号源的设置。

这包括选择合适的信号源类型(如AC

信号、脉冲信号等)、设置信号源的频率和振幅等参数。

5. 添加测量器件,以便在仿真过程中监测所需的电压或电流。

这些测量器件可以是电压表、电流表或示波器等。

6. 设置仿真分析类型。

根据需要进行直流分析、交流分析或者是时域分析等。

选择适当的仿真分析类型以获得所需的结果。

7. 运行仿真并分析结果。

运行仿真过程,等待仿真完成后,通过分析仿真结果来获取我们所需的电压、电流或其他信号参数。

通过遵循以上步骤,我们可以在Cadence中进行原理图仿真,并获取准确可靠的仿真结果,以验证电路设计的正确性和性能。

cadence后仿教程netlist

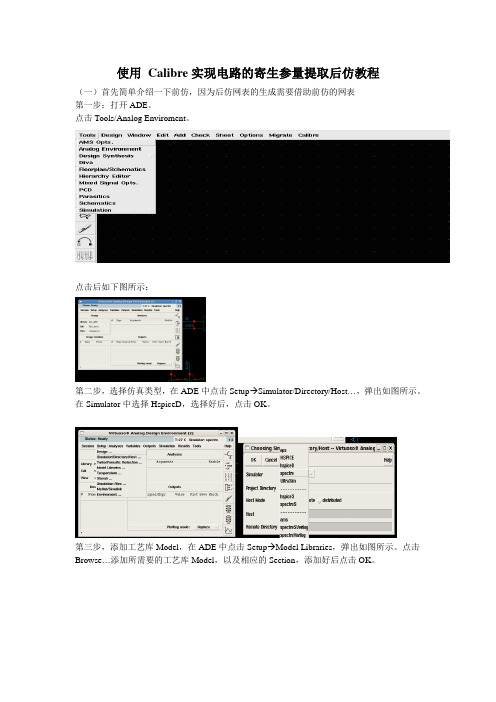

使用Calibre实现电路的寄生参量提取后仿教程(一)首先简单介绍一下前仿,因为后仿网表的生成需要借助前仿的网表第一步:打开ADE。

点击Tools/Analog Enviroment。

点击后如下图所示:第二步,选择仿真类型,在ADE中点击Setup→Simulator/Directory/Host…,弹出如图所示。

在Simulator中选择HspiceD,选择好后,点击OK。

第三步,添加工艺库Model,在ADE中点击Setup→Model Libraries,弹出如图所示。

点击Browse…添加所需要的工艺库Model,以及相应的Section,添加好后点击OK。

第三步,添加仿真变量。

点击Analyses→Choose,在弹出的窗口中选择仿真的类型,本次为tran,下面填写仿真start为0 ,stop为15un(根据实际情况设置),步长step为10n ,MAX step为10n。

填好后点击OK。

第四步,产生网表。

点击Simulation→Netlist→Create。

弹出所产生的网表,点击File→Save As,在弹出的窗口中,在File Name中填入保存的名字。

点击OK,网表保存至打开icfb的地方。

(二)后仿的操作第一步,点击cliabre后选择Run PEX选项,如下图所示1、Rules菜单中PEX Rules File和PEX Rules Directory保持一致,指向运行PEX的规则(否则无法运行PEX),设置好之后,点击File/Save Runset ,即可保存设置2、Inputs菜单中Netlist选项中选中Export from schemastic viewer3、Outputs 菜单中的Extraction Type 里,第一项通常选择Transistor Level 或Gate Level,分别代表晶体管级提取和门级提取。

第二项可以选择R+C+CC,R+C,R,C+CC,其中R代表寄生电阻,C 代表本征寄生电容,CC 代表耦合电容。

cadence仿真工具介绍

6.改名(rename):>mv A B (文件或目录改名) 7.删除: >rm fileA (删除文件,可以有多个文件名) >rm –r dirA (删除目录,可以有多个目录名) 8.编辑文件:>vi fileA (文件不存在时,自动创建新文件) 编辑命令:I(插入), o(下插入行), O(上插入行), Esc键(退出), x(删除字符), dd(删除行), h l k j或方向键(左右上下移动) 非编辑状态时,按Shift+:,文件尾出现“:”,此时可以 保存文件(w )和退出vi状态(q)。

打开工作窗口(terminal): 按mouse右键,点击open terminal

COPYRIGHT FOR ZHOUQN

关机:

在terminal中敲命令halt, 回车

重开机:

在terminal中敲命令reboot, 回车

COPYRIGHT FOR ZHOUQN

• LINUX操作系统常用命令简介

• 仿真环境设置

COPYRIGHT FOR ZHOUQN

• 仿真环境设置

COБайду номын сангаасYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

COPYRIGHT FOR ZHOUQN

• Linux操作系统:在pc机上,安装 (1) 虚拟机 (2) linux 操作系统 (3) 在linux操作系统中安装IC设计软件

COPYRIGHT FOR ZHOUQN

启动与登陆: (1) 虚拟机登陆

COPYRIGHT FOR ZHOUQN

• (2) 启动linux----点击start this virtual machine

cadence后仿教程

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

设置好库文件和仿真类型,点击Run 即可开始后仿!

方法二:

请参见LAB2 里的

Mixed-level simulation (简单说就是建一个config 文件,可以自己配制仿真 所调用的view的类型)

得修改引用路径,直接写成绝对路径就行

引用了LVS文件, 所以说PEX之 前其实又做了 一遍LVS

点一下就可 以对文本 进行修改

4.设置Inputs选项

5.设置Outputs选项

<1>提取类型选择:R表示提取寄生电阻 C表示提取到地寄生电容 CC表示提取线间寄生电容 在电路规模较大情况下,一般不提电阻寄生电阻, 因为这会导致电路节点极剧增多,无法进行后仿, 所以电阻的提取只限示小模块电路.一般选C+CC.

PMOS管 NMOS管

寄生电容的映射模型 选择理想电容,即 analogLib中的cap. 如果你选择了提取寄 生电阻,那么相应 的应该选择 analogLib中的res. 最终弹出Calibre Info(如左图所示), “0 warnings and 0 errors”说明 CalibreView成功生 成.

CADENCE仿真步骤

CADENCE仿真步骤1.电路设计:首先,需要使用电路设计软件(例如OrCAD)绘制电路原理图。

在设计电路时,应该合理选择电路元件,确保其参数和规格满足设计要求。

2.创建电路网络:在CADENCE中创建电路网络是第一步。

通过将电路原理图导入到CADENCE中,可以建立电路的模型。

在建立电路网络时,应定义元件的参数值,并将其连接起来。

3.定义仿真设置:在进行仿真之前,需要设置仿真参数。

这些参数包括仿真类型(例如直流、交流、蒙特卡罗等)、仿真步长、仿真时间等。

此外,还可以设置其他参数,如故障分析、参数扫描等。

4. 运行仿真:设置好仿真参数后,可以开始运行仿真了。

CADENCE 提供了多种仿真工具,如PSpice、Spectre等,可以根据不同的需求选择适合的工具。

在仿真过程中,CADENCE会使用电路元件的模型计算电路参数,根据仿真设置提供的信息生成相应的结果。

5.分析仿真结果:一旦仿真完成,CADENCE会生成仿真结果文件。

通过分析仿真结果,可以评估电路设计的性能。

常见的仿真结果包括电流、电压、功耗、频率响应等。

可以将仿真结果与预期结果进行比较,找出设计中的问题并进行优化。

6.优化电路设计:根据仿真结果,可以对电路设计进行调整和优化。

优化可以包括选择不同的元件、调整元件参数、改变电路拓扑等。

通过不断迭代仿真和优化,可以逐步改进电路设计,使其达到预期的性能指标。

7.验证仿真结果:当设计经过一系列的优化后,需要验证仿真结果是否可靠。

一种常用的验证方法是进行物理验证,即将最终的电路设计制作出来并测量其实际性能。

通过比较实际测量结果与仿真结果,可以验证仿真的准确性,并进行必要的修正。

8. 导出设计文件:一旦电路设计完成并验证通过,就可以将设计文件导出,准备进一步的生产制造。

将设计文件导出为标准的格式(如Gerber文件),可以将其发送给制造商进行生产。

总结:CADENCE仿真步骤包括电路设计、创建电路网络、定义仿真设置、运行仿真、分析仿真结果、优化电路设计、验证仿真结果和导出设计文件。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

CADENCE仿真步骤

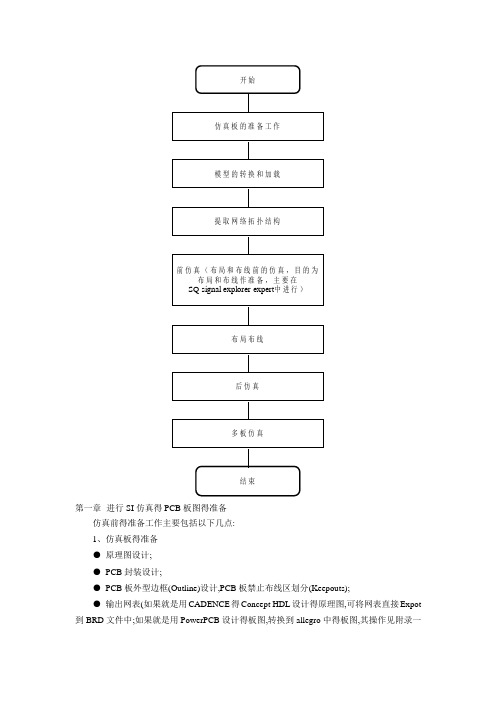

Cadence SPECCTRAQuest 仿真步骤[摘要]本文介绍了Cadence SPECCTRAQuest在高速数字电路的PCB设计中采用的基于信号完整性分析的设计方法的全过程。

从信号完整性仿真前的环境参数的设置,到对所有的高速数字信号赋予PCB板级的信号传输模型,再到通过对信号完整性的计算分析找到设计的解空间,这就是高速数字电路PCB板级设计的基础。

[关键词]板级电路仿真 I/O Buffer Information Specification(IBIS)1 引言电路板级仿真对于今天大多数的PCB板级设计而言已不再是一种选择而是必然之路。

在相当长的一段时间,由于PCB仿真软件使用复杂、缺乏必需的仿真模型、PCB仿真软件成本偏高等原因导致仿真在电路板级设计中没有得到普及。

随着集成电路的工作速度不断提高,电路的复杂性不断增加之后,多层板和高密度电路板的出现等等都对PCB板级设计提出了更新更高的要求。

尤其是半导体技术的飞速发展,数字器件复杂度越来越高,门电路的规模达到成千上万甚至上百万,现在一个芯片可以完成过去整个电路板的功能,从而使相同的PCB 上可以容纳更多的功能。

PCB已不仅仅是支撑电子元器件的平台,而变成了一个高性能的系统结构。

这样,信号完整性在PCB板级设计中成为了一个必须考虑的一个问题。

传统的PCB板的设计依次经过电路设计、版图设计、PCB制作等工序,而PCB的性能只有通过一系列仪器测试电路板原型来评定。

如果不能满足性能的要求,上述的过程就需要经过多次的重复,尤其是有些问题往往很难将其量化,反复多次就不可避免。

这些在当前激烈的市场竞争面前,无论是设计时间、设计的成本还是设计的复杂程度上都无法满足要求。

在现在的PCB板级设计中采用电路板级仿真已经成为必然。

基于信号完整性的PCB仿真设计就是根据完整的仿真模型通过对信号完整性的计算分析得出设计的解空间,然后在此基础上完成PCB设计,最后对设计进行验证是否满足预计的信号完整性要求。

CADENCE 仿真流程

第一章进行SI仿真得PCB板图得准备仿真前得准备工作主要包括以下几点:1、仿真板得准备●原理图设计;●PCB封装设计;●PCB板外型边框(Outline)设计,PCB板禁止布线区划分(Keepouts);●输出网表(如果就是用CADENCE得Concept HDL设计得原理图,可将网表直接Expot 到BRD文件中;如果就是用PowerPCB设计得板图,转换到allegro中得板图,其操作见附录一得说明);●器件预布局(Placement):将其中得关键器件进行合理得预布局,主要涉及相对距离、抗干扰、散热、高频电路与低频电路、数字电路与模拟电路等方面;●PCB板布线分区(Rooms):主要用来区分高频电路与低频电路、数字电路与模拟电路以及相对独立得电路。

元器件得布局以及电源与地线得处理将直接影响到电路性能与电磁兼容性能;2、器件模型得准备●收集器件得IBIS模型(网上下载、向代理申请、修改同类型器件得IBIS模型等)●收集器件得关键参数,如Tco、Tsetup、Tholdup等及系统有关得时间参数Tclock、Tskew、Tjitter●对IBIS模型进行整理、检查、纠错与验证。

3、确定需要仿真得电路部分,一般包括频率较高,负载较多,拓扑结构比较复杂(点到多点、多点到多点),时钟电路等关键信号线第二章IBIS模型得转化与加载CADENCE中得信号完整性仿真就是建立在IBIS模型得基础上得,但又不就是直接应用IBIS模型,CADECE得软件自带一个将IBIS模型转换为自己可用得DML(Device Model Library)模型得功能模块,本章主要就IBIS模型得转换及加载进行讲解。

1、IBIS模型到DML模型得转换在Allegro窗口中选择Analyse\SI/EMI SIM\Library,打开“signal analyze library browser”窗口,在该窗口得右下方点击“Translate →”按钮,在出现得下拉菜单中选择“ibis2signois”项,出现“Select IBIS Source File”窗口(图1),选择想要进行转换得源IBIS文件,按下“打开”按钮,出现转换后文件名及路径设置窗口(缺省设置为与源IBIS文件同名并同路径放置,但此处文件名后缀为dml),设置后按下“保存”按钮,出现保存确定窗口(图2),点击OK按钮即可,随后会出现一个“messages”窗口,该窗口中得报告文件说明在模型转换过程中出现得问题,对其中得“warning”可不用在意,但如果出现“error”则必须进行修改后重新进行模型格式转化直到没有“error”出现为止,此时转换得到得dml文件才就是有效得。

反相器设计前仿与后仿流程

目录前端电路设计与仿真 (2)第一节双反相器的前端设计流程 (2)1、画双反相器的visio原理图 (2)2、编写.sp文件 (2)第二节后端电路设计 (4)一、开启linux系统 (5)2、然后桌面右键重新打开Terminal (8)双反相器的后端设计流程 (9)一、schematic电路图绘制 (9)二、版图设计 (32)画版图一些技巧: (48)三、后端验证和提取 (49)第三节后端仿真 (58)其它知识 (61)前端电路设计与仿真第一节双反相器的前端设计流程1、画双反相器的visio原理图inV DDM2M3out图1.1其中双反相器的输入为in 输出为out,fa为内部节点。

电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。

2、编写.sp文件新建dualinv.txt文件然后将后缀名改为dualinv.sp文件具体实例.sp文件内容如下:.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角***********划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。

划紫色线条处的端口名称和顺序一定要一致MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同)MMX D G S B MNAME <L=val> <W= val > <AD= val > <AS= val > <PD= val > <PS= val > <NRD= val > <NRS= val >2.1、在wind owXP开始--程序这里打开Hspice程序2.2、弹出以下画面然后进行仿真1、打开.sp文件2、按下仿真按钮3形存放.sp文件的地址查看波形按钮按下后弹出以下对话框单击此处如果要查看内部节点的波形,双击Top处单击这些节点即可查看波形如果有多个子电路请单击此处的Top查看如果要查看测量语句的输出结果请查看.MTO文件(用记事本打开)至此前端仿真教程结束第二节后端电路设计前序(打开Cadence软件)一、开启linux系统双击桌面虚拟机的图标选择Power on this virtual machine 开启linux之后在桌面右键选择 Open Terminal 输入 xhost local:命令按回车之后输入 su xue命令按回车,这样就进入了xue用户1、输入命令加载calibre软件的license,按回车,等到出现以下画面再关闭Terminal窗口2、然后桌面右键重新打开Terminal 进入学用户,开启Cadence软件,如下图然后出现cadence软件的界面关闭这个help窗口,剩下下面这个窗口,这样cadence软件就开启了[如果在操作过程中关闭了cadence,只需要执行步骤2即可,步骤1加载calibre 的license只在linux重启或者刚开启的时候运行一次就可以了。

cadence后仿教程

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

<3>指定提取哪些节点的寄生参数: 默认是ALL Nets(提取所有节点) 也可以自定义(Specified Nets):可以提取除了指

定节点以外的所有节点(Exclude),也可以只提取指定的 节点(Include),在相应的文本框里写入节点的net名即 可,或者点击右侧的小箭头,然后在弹出的原理图里选择你 想输入的节点,按ESC键,你所选择的节点名就自动填在左 侧文本框中.

至此,我们仍未进行后仿,我们只是提取出 了寄生参数,并生成了带这些寄生参数的 calibre view,这都是为后仿做准备. 接下来介绍如何后仿.

方法一

1.打开测试平台,此 例是 INV_example_test. 2.打开ADE (仿真环 境)窗口 3.与仿真原理图不 同的是多出这一步: 点击Setup— >Environment 弹出一个配置窗口 (见下页)

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

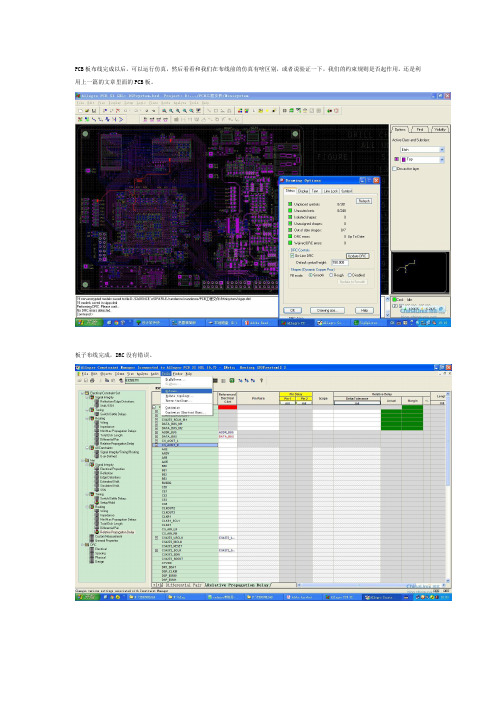

cadence布线后-反射仿真

PCB板布线完成以后,可以运行仿真,然后看看和我们在布线前的仿真有啥区别,或者说验证一下,我们的约束规则是否起作用。

还是利用上一篇的文章里面的PCB板。

板子布线完成,DRC没有错误。

必须勾选上面的2个选项。

启动sigxplorer,从下图我们可以看见,没有上一篇文章的那个圆柱形的导线,那是因为那是布线前仿真,所以软件就是用微带线代替导线,作为连接线来仿真,现在是布线后仿真,连接线是铜皮和过孔了,所以软件就使用铜皮和过孔的一些参数来仿真了,而不是理想的微带线了。

具体的铜皮导线和过孔模型参数,这是一门很理论,还要有实践经验的学问,比较多,你可以找信号完整性方面的书籍来阅读,有好几本很经典的书籍,都是外国人写的,可以google一下的。

设置过程和布线前仿真一样,没有啥需要说的。

这里的频率是100Mhz,可以看看下图,波形有失真的,可以参考一下。

这里的频率是50Mhz,波形规则一下。

不管布线前仿真,还是布线后仿真,都是理论上的,有些人创建了一些理论和数学公式来描述导线的电感,电容,阻抗,还有频率,距离,比较复杂,软件利用这些理论和公式,给我们制作PCB板提供一些方便,但是这毕竟是理论,需要实际检验的,所以呢,我的仿真都是给PCB的一个参考,不是绝对的,也包括我们的各种约束设置,具体效果就需要实际的PCB来检测。

但是我们需要理论的指导,这样就在以后的实践中少走弯路。

这些理论可都是很厉害的人发明的,也经受了实践的检验,我们这里就是坐享其成了,给自己的工作添

加一些便利。

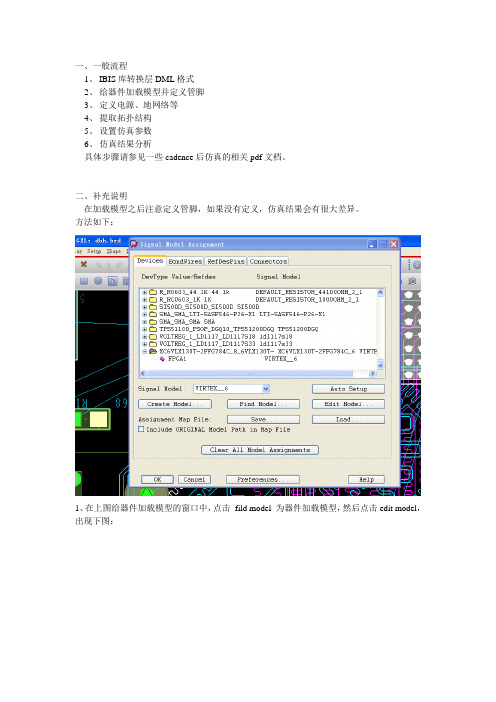

cadence对pcb进行后仿真

一、一般流程1、IBIS库转换层DML格式2、给器件加载模型并定义管脚3、定义电源、地网络等4、提取拓扑结构5、设置仿真参数6、仿真结果分析具体步骤请参见一些cadence后仿真的相关pdf文档。

二、补充说明在加载模型之后注意定义管脚,如果没有定义,仿真结果会有很大差异。

方法如下:1、在上图给器件加载模型的窗口中,点击fild model 为器件加载模型,然后点击edit model,出现下图:2、选择assign signal pins 然后在all pin中选择需要定义的管脚。

被选择的管脚会出现在selected pin方框中。

点击右侧的browse 出现下图:3、在dml model browser中选择需要的Iocell 关闭窗口、确定、完成。

4、如需对差分信号进行仿真的话,需要对差分pin进行设置。

三、pcb中FPGA与DDR2之间一根数据线的仿真。

1、提取的信号线为下图中白色高亮。

1、提取的拓扑结构包括走线和过孔的一些具体信息。

U17是DDR2,FPGA1是xilinx—c6v130tff784 2、层叠结构所仿真的信号线走的是S1层,为达到50 ohm 匹配,s1上下介质厚度为6mil。

3、仿真参数4、仿真结果Ddr2发送fpga接收时候的波形:浅绿色和浅蓝色分别是ddr2的pin和pad处的波形。

黑色和蓝色分别是fpga的pin和pad处的波形。

Fpga发送,ddr2接收时候的波形:5、以下是将走线拉直以后的仿真结果:Ddr2 发送,fpga接收:Fpga发送。

Ddr2接收:新手第一次做的仿真,希望与大家一起交流讨论。

可以加Q: 5.1.9.7.3.1.9.8.。

Cadence仿真流程

Cadence仿真流程Cadence 仿真流程第⼀章在Allegro 中准备好进⾏SI 仿真的PCB 板图1)在Cadence 中进⾏SI 分析可以通过⼏种⽅式得到结果:Allegro 的PCB 画板界⾯,通过处理可以直接得到结果,或者直接以*.brd 存盘。

使⽤SpecctreQuest 打开*.brd,进⾏必要设置,通过处理直接得到结果。

这实际与上述⽅式类似,只不过是两个独⽴的模块,真正的仿真软件是下⾯的SigXplore 程序。

直接打开SigXplore 建⽴拓扑进⾏仿真。

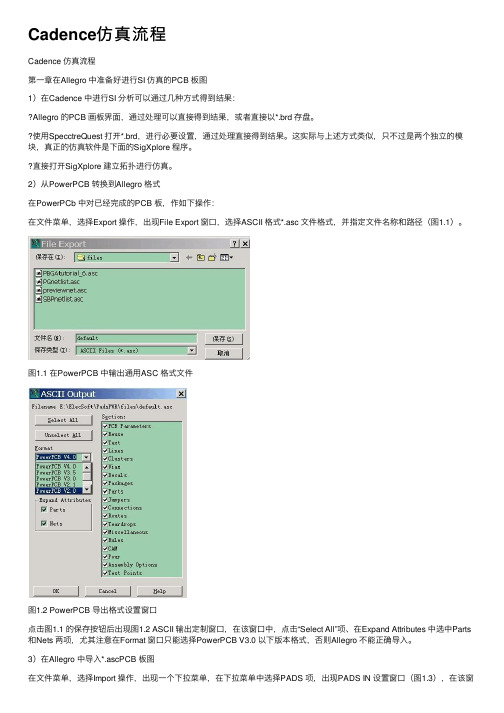

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在⽂件菜单,选择Export 操作,出现File Export 窗⼝,选择ASCII 格式*.asc ⽂件格式,并指定⽂件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通⽤ASC 格式⽂件图1.2 PowerPCB 导出格式设置窗⼝点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗⼝,在该窗⼝中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗⼝只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导⼊。

3)在Allegro 中导⼊*.ascPCB 板图在⽂件菜单,选择Import 操作,出现⼀个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗⼝(图1.3),在该窗⼝中需要设置3 个必要参数:图1.3 转换阿三次⽂件参数设置窗⼝i. 在的⼀栏那填⼊源asc ⽂件的⽬录ii. 在第⼆栏指定转换必须的pads_in.ini ⽂件所在⽬录(也可将此⽂件拷⼊⼯作⽬录中,此例)iii. 指定转换后的⽂件存放⽬录然后运⾏“Run”,将在指定的⽬录中⽣成转换成功的.brd ⽂件。

cadence版图仿真教程

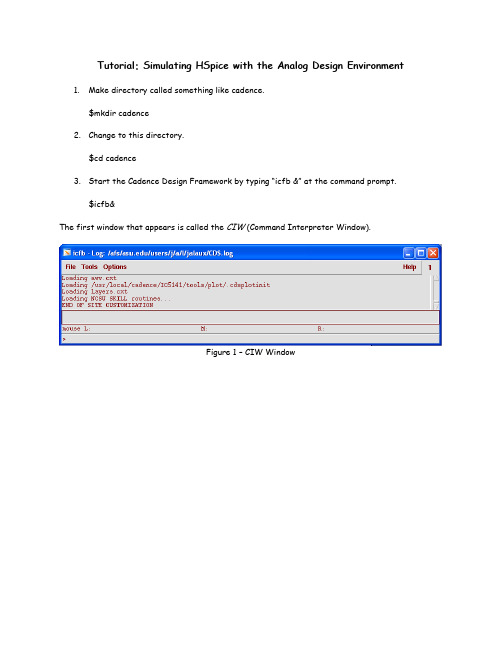

Tutorial: Simulating HSpice with the Analog Design Environment1.Make directory called something like cadence.$mkdir cadence2.Change to this directory.$cd cadence3.Start the Cadence Design Framework by typing “icfb &” at the command prompt.$icfb&The first window that appears is called the CIW (Command Interpreter Window).Figure 1 – CIW WindowAnother window that appears is the Library Manager. This window allows you to browse the available libraries and create your own.Figure 2 – Library Manager WindowIn the Library Manager, create a new library called EEE534. Select File->New->Library. This will open a new dialog window, in which you need to enter the name of your library, library path, and "Attach to existing tech library." Fill out the form as shown below, then select OK.Figure 3 – Create Library FormYou should see the library "EEE534" appear in the Library Manager.Figure 4 – Library Manager display newly created libraryNext, select the library you just created in the Library Manager and select File->New->Cell View.... We will create a schematic view of an inverter cell. Simply type in "INV" under cell-name and "schematic" under view. Click OK or hit the Enter key. Note: that the "Tool" is automatically set to "Composer-Schematic", the schematic editor.Figure 5 – Create New File FormAlternatively, you could select the "Composer-Schematic" tool, instead of typing out the view name. This will automatically set the view name to "schematic".After you hit "OK", the blank Composer screen will appear.Figure 6 – Virtuoso Schematic EditorTo generate a schematic, you will need to go through the following steps:•From the Schematic Window, choose Add->instance. The Component Browser, will then pop up.•In the Library field, select NCSU_Analog_Parts. We will place the pmos, nmos, vdd, gnd, vdc, vpulse andcap instances in the Schematic Window from the NCSU_Analog_Parts library asinstructed below.Note: pay special attention to the parameters specified in vdc, vpulse, and cap. These parameters are very important in simulation.Place pmos instance•In Component Browser, select P_Transistors and then pmos.•Place it in the Schematic WindowFigure 7 – Add pmos InstancePlace nmos instance•In Component Browser, select N_Transistors and then nmos.•Place it in the Schematic Window.Figure 8 – Add nmos InstancePlace gnd instance•In Component Browser, select Supply_Nets and then gnd.•Place it in the Schematic Window.Figure 9 – Add gnd Instance Place vdd instance•In Component Browser, select Supply_Nets and then vdd •Place it in the Schematic Window.Figure 10 – Add vdd InstancePlace IN pin•From the Schematic Window menu, select Add -> Pin...•In the Pin Name field , enter IN•In the Direction field, select input•Place it in the Schematic WindowFigure 11 – Add Input PinPlace OUT pin•From the Schematic Window menu, select Add -> Pin...•In the Pin Name field , enter OUT•In the Direction field, select output•Place it in the Schematic WindowFigure 12 – Add Output PinPlace vdc instance•In the Component Browser, select Voltage Sources and then vdc •In the DC voltage field, enter 5 V•Place it in the Schematic WindowFigure 13 – Add vdc SourcePlace vpulse instance•In the Component Browser, select Voltage_Sources and then vpulse •Enter the following values in the form:Figure 14 Edit Object vpulse SourcePlace cap instance•In Component Browser, select R_L_C and then cap•In the Capacitance field, enter OutCap F. (This Design Variable will be used in Artist.) •Place it in the Schematic WindowFigure 15 – Add cap InstancePlace wires•In the Schematic Window menu, select Add -> Wire (narrow)•Place wires to connect all the instances•Select Design -> Check and Save.Look at the CIW. You should see a message that says:Extracting “INV schematic”Schematic check completed with no errors.“EEE534 INV schematic” saved.If you do have some errors or warnings, the CIW will give a short explanation of what those errors are. Errors will also be marked on the schematic with a yellow or white box. Errors must be fixed for your circuit to simulate properly. When you find a warning it is up to you to decide if you shouldfix it or not. The most common warnings occur when there is a floating node or when there are wires that cross but are not connected. Just be sure that you know what effect each of these warning will have on your circuit when you simulate.Your schematic should look like the one shown below.Figure 16 – Completed SchematicIf you would like to learn more about the schematic editor, you can work through chapters 1-5 of the Composer Tutorial that comes with the Cadence documentation. Start the documentation browser by typingcdnshelp &at the command prompt. If you find that you cannot view the figures correctly in the web browser, you can click the View/Print PDF link at the top of the page to launch a PDF viewer for the tutorial. This documentation browser offers many more links for you to learn about the Cadence Design Framework.Simulate the Schematic with HSPICE within Virtuoso Analog Design EnvironmentSet up the Simulation EnvironmentYou are now prepared to simulate your circuit.From the Schematic Window menu, select Tools -> Analog Environment. A window will pop-up. This window is the Analog Design Environment Window.Figure 17 - Analog Design Environment WindowChoose a SimulatorFrom the Analog Design Environment menu, select Setup -> Simulator/Directory/Host. Enter the fields as shown below. Choose hspiceS as your simulator. Your simulation will run in the specified Project Directory. You may choose any valid pathname and filename that you like.Figure 18 Choosing Simulator/Directory/Host FormChoose AnalysisWe will setup to do a Transient Analysis on the circuit that we just produced.From the Analog Design Environment menu, select Analyses -> Choose... Fill out the form with the following values:Figure 19 – Choosing AnalysesAdd a VariableFrom the Analog Design Environment menu, select Variables -> Edit. The Editing Design Variables form will appear. Fill out the form as shown below, and then click Add to send this Variable to the Table of Design Variables.(Recall that we entered the OutCap Design Variable in the Capacitor component while editing the schematic in the previous section.)Figure 20 – Editing Design Variables FormSetup OutputWhen using Transient Analysis, the transient voltage will be saved automatically. We can save the current through capacitor C0 in the schematic by doing the following:From the Analog Design Environment menu, select Outputs -> To be Saved -> Select On Schematic In the Schematic Window, click on the lower terminal (not the wire) of capacitor C0.After you click on the terminal, the Analog Design Environment Window should look like this:Figure 21 Analog Design Environment WindownRun SimulationFrom the Analog Design Environment menu, select Simulation -> Run, Look at the echoing information in the CIW window. If the simulation succeeds, the window will display “...successful.”Figure 22 – CIW after simulationIf the simulation is unsuccessful, then one of the error messages should provide a clue as to what went wrong. Remember that you can move elements around in your schematic by clicking and dragging them. You can delete them by selecting them and pressing the “delete” key. You modify the properties of the elements by selecting them and pressing the “q” key.If you would like to learn more about the Analog Design Environment, select Analog Design Environment->Cadence Analog Design Environment User Guide in the cdnshelp browser window.View WaveformsFrom the Analog Design Environment menu, select Results -> Direct Plot -> Transient Signal. The Waveform Window will then pop up. In the Schematic Window, click on the IN wire and then Click on the OUT wire, then press ESC on your keyboard.The two curves (IN and OUT) will then be displayed in this window:Figure 23 – Waveform ViewerPress the Strip Chart Mode icon (4th icon from right) on the Waveform WindowThe waveforms will then be displayed separately as shown below:Figure 24 – Waveform Viewer, Strip Chart ModeIf you would like to learn more about the Waveform Viewer, select Analog Design Environment->Waveform User Guide in the cdnshelp browser window.Use CalculatorIn Analog Design Environment Window, go to Tools -> Calculator. The Calculator Window will then pop up, as shown below:Figure 25 – CalculatorIn Calculator Window, go to Options -> uncheck RPN. We are going to use the calculator to plot both the current through the capacitor and the absolute value of the capacitor current.In the Calculator Window, click on the tran tab then click the it radio button. In the Schematic Window, click on the lower terminal of the capacitor. Returning to the Calculator Window, the text area at the top should like this:Figure 26 – Calculator after selecting lower capacitor terminalIn the Calculator Window, press the plot icon to plot this waveform in the Waveform Window. In the Calculator Window, select the New Subwindow. In the Calculator Window, press the clear button to erase the text area, select abs, press the “(“ symbol and press the it radio button. In the Schematic Window, click on the lower terminal of the capacitor. Returning to the Calculator Window, press the “)” symbol, the text area at the top should like this:Figure 27 - Calculator after selecting lower capacitor terminalIn the Calculator Window, press the plot button to plot this waveform in the Waveform Window. Your Waveform Window should now look like this:Figure 28 – Waveform Display with current through the capacitor and the absolute value of thecapacitor current。

cadence仿真设置简介

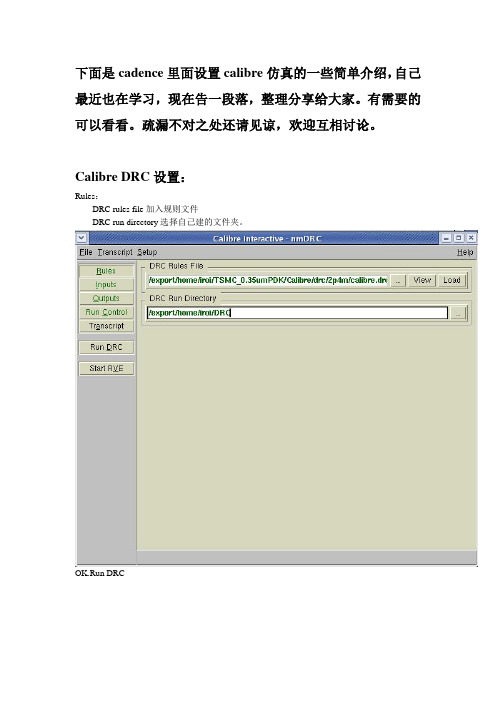

下面是cadence里面设置calibre仿真的一些简单介绍,自己最近也在学习,现在告一段落,整理分享给大家。

有需要的可以看看。

疏漏不对之处还请见谅,欢迎互相讨论。

Calibre DRC设置:Rules:DRC rules file加入规则文件DRC run directory选择自己建的文件夹。

OK.Run DRCLVS设置:Rules:LVS rules file加入规则文件LVS run directory选择自己建的文件夹。

最好再新建一个存放Inputs:勾选hierarchical和layout vs netlistlayout和netlists下面的export from viewer全都勾选OK.Run LVS上面两个验证如果出现错误,就对照着列出来的错误仔细修改至通过。

PEX(提参)设置:Rules:PEX rules file加入规则文件PEX run directory选择自己建的文件夹。

最好再新建一个存放Inputs:layout和netlists下面的export from viewer全都勾选。

类似LVS那样Outputs:Netlists里面的format选择Calibreview。

其他默认。

OK.run PEX这里如果出现这个错误:解决办法:到calibre.rcx的1219行,加入同一个文件夹下的rules文件路径即可如下图。

Run PEX结束后会自动跳出下面的设置界面:除了calview.cellmap文件选用自己的对应的之外。

其他设置仿照这个设置。

然后点击OK。

这是提参的最后一步,时间可能有点长,耐心等待。

结束后会出现下图,点击close即可。

Warning不用管。

后仿:到这里版图提参就结束了。

需要进行后仿。

打开ADE环境,在setup->Environment,switch view list一栏的最前面加上calibre 这个单词,如下图,点击OK。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

点击Start RVE导出如上图窗口,再点击“寄生虫” 按扭,弹出寄生参数窗口(见下页)

这里列出了所有节点的 名称,到地电容(C) 和线间电容(CC)的大小. 如果想要具体察看某个 节点到其他节点的寄生 电容的大小,那么选选 中这个节点,如左图所 示,再点击按扭”P”,弹出 窗口(如左下图),在 Capacitance选项卡中 列出了节点IN与 OUT,GND,VDD之间的 寄生电容的大小.

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

设置好库文件和仿真类型,点击Run 即可开始后仿!

方法二:

请参见LAB2 里的

Mixed-level simulation (简单说就是建一个config 文件,可以自己配制仿真 所调用的view的类型)

<3>指定提取哪些节点的寄生参数: 默认是ALL Nets(提取所有节点) 也可以自定义(Specified Nets):可以提取除了指

定节点以外的所有节点(Exclude),也可以只提取指定的 节点(Include),在相应的文本框里写入节点的net名即 可,或者点击右侧的小箭头,然后在弹出的原理图里选择你 想输入的节点,按ESC键,你所选择的节点名就自动填在左 侧文本框中.

至此,我们仍未进行后仿,我们只是提取出 了寄生参数,并生成了带这些寄生参数的 calibre view,这都是为后仿做准备. 接下来介绍如何后仿.

方法一

1.打开测试平台,此 例是 INV_example_test. 2.打开ADE (仿真环 境)窗口 3.与仿真原理图不 同的是多出这一步: 点击Setup— >Environment 弹出一个配置窗口 (见下页)

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

得修改引用路径,直接写成绝对路径就行

引用了LVS文件, 所以说PEX之 前其实又做了 一遍LVS

点一下就可 以对文本 进行修改

4.设置Inputs选项

5.设置Outputs选项

<1>提取类型选择:R表示提取寄生电阻 C表示提取到地寄生电容 CC表示提取线间寄生电容 在电路规模较大情况下,一般不提电阻寄生电阻, 因为这会导致电路节点极剧增多,无法进行后仿, 所以电阻的提取只限示小模块电路.一般选C+CC.

此时察看相应的Cell多出一个View:calibre

(这就是通过PEX得到的带有寄生参数的原理图)

点击查看calibre,由四部分组成

与映射文件配置窗口一同弹出的还有PEX网单 在这个文件 里,大家可 以察看各个 节点到衬底 (“0”)的 寄生电容和 各个节点之 间的线间电 容cc

察看寄生参数大小的另一种方法

PMOS管 NMOS管

寄生电容的映射模型 选择理想电容,即 analogLib中的中的res. 最终弹出Calibre Info(如左图所示), “0 warnings and 0 errors”说明 CalibreView成功生 成.

5.设置Outputs选项

Netlist选项卡

<2>输出格式选择:选择CALIBREVIEW CALIBREVIEW中节点的名称:建议选SCHEMATIC,

这样的话生成的CALIBREVIEW电路中的节点的名称用的是 原来原理图中的节点名称,查看起来比较方便.

5.设置Outputs选项 Nets选项卡

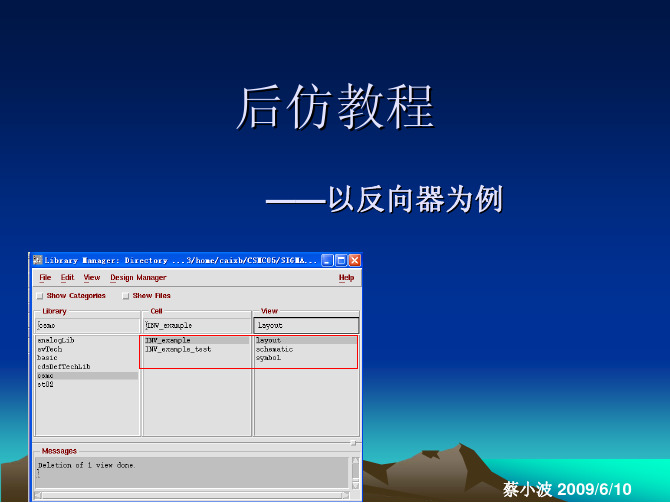

后仿教程

——以反向器为例

蔡小波 2009/6/10

1.打开Calibre的PEX(寄生参数提取)

2.选择PEX规则文件

PEX规则文件为:csmccalibre.xrc.a3

3.选择PEX运行的目录

如果目录选择CALIBRE(即csmccalibre.xrc.a3所在目 录),那就OK了. 如果你嫌在CALIBRE产生一堆文件,想自己建个 PEX运行目录,那就得注意了,此时要修改 csmccalibre.xrc.a3文件,点击View,转下页