105-1042-001;中文规格书,Datasheet资料

B0540WS-7;中文规格书,Datasheet资料

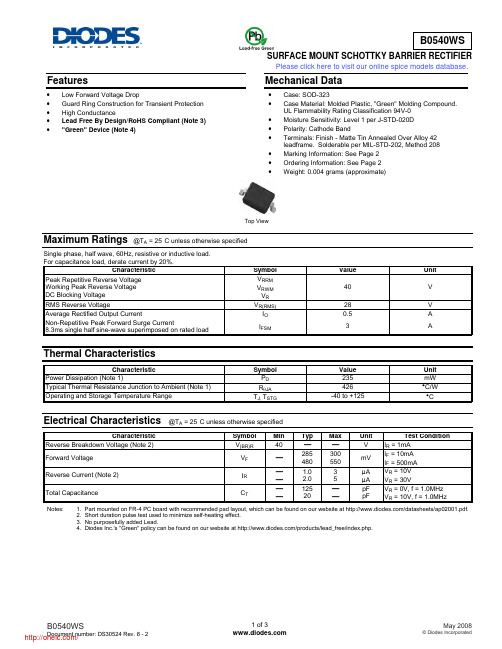

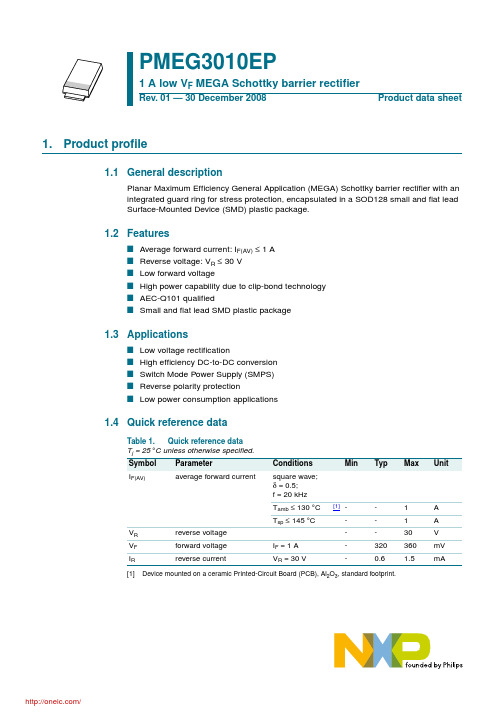

SURFACE MOUNT SCHOTTKY BARRIER RECTIFIERFeatures• Low Forward Voltage Drop• Guard Ring Construction for Transient Protection • High Conductance• Lead Free By Design/RoHS Compliant (Note 3) • "Green" Device (Note 4)Mechanical Data• Case: SOD-323• Case Material: Molded Plastic, "Green" Molding Compound.UL Flammability Rating Classification 94V-0• Moisture Sensitivity: Level 1 per J-STD-020D• Polarity: Cathode Band• Terminals: Finish - Matte Tin Annealed Over Alloy 42leadframe. Solderable per MIL-STD-202, Method 208 • Marking Information: See Page 2• Ordering Information: See Page 2• Weight: 0.004 grams (approximate)Top ViewMaximum Ratings@T A = 25°C unless otherwise specifiedSingle phase, half wave, 60Hz, resistive or inductive load.For capacitance load, derate current by 20%.Characteristic Symbol Value UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV R40 VRMS Reverse Voltage V R(RMS)28 V Average Rectified Output Current I O0.5 ANon-Repetitive Peak Forward Surge Current8.3ms single half sine-wave superimposed on rated load I FSM3 A Thermal CharacteristicsCharacteristic Symbol Value Unit Power Dissipation (Note 1) P D235 mW Typical Thermal Resistance Junction to Ambient (Note 1) RθJA426 °C/W Operating and Storage Temperature Range T J, T STG-40 to +125 °CElectrical Characteristics@T A = 25°C unless otherwise specifiedCharacteristic Symbol Min Typ Max Unit Test Condition Reverse Breakdown Voltage (Note 2) V(BR)R40 ⎯⎯V I R = 1mAForward Voltage V F⎯285480300550mVI F = 10mAI F = 500mAReverse Current (Note 2) I R ⎯⎯1.02.035μAμAV R = 10VV R = 30VTotal Capacitance C T ⎯⎯12520⎯⎯pFpFV R = 0V, f = 1.0MHzV R = 10V, f = 1.0MHzNotes: 1. Part mounted on FR-4 PC board with recommended pad layout, which can be found on our website at /datasheets/ap02001.pdf.2. Short duration pulse test used to minimize self-heating effect.3. No purposefully added Lead.4. Diodes Inc.'s "Green" policy can be found on our website at /products/lead_free/index.php.Please click here to visit our online spice models database.10100V, INSTANTANEOUS REVERSE VOLTAGE (V)Fig. 2 Typical Reverse CharacteristicsRI,INSTANTANEOUSFORWARDCURRENT(mA)FV, INSTANTANEOUS FORWARD VOLTAGE (V)Fig. 1 Typical Forward CharacteristicsF100C,TOTALCAPACITANCE(pF)TV, DC REVERSE VOLTAGE (V)Fig. 3 Total Capacitance vs. Reverse VoltageR0.250.50050100I,AVE150RAGEFORWARDCURRENT(A)F(AV)T, TERMINAL TEMPERATURE (C)Fig. 4 Forward Current Derating CurveT°0.751.02575125Ordering Information(Note 5)Part Number Case PackagingB0540WS-7 SOD-323 3000/Tape & ReelNotes: 5. For packaging details, go to our website at /datasheets/ap02007.pdf.Marking InformationSF SF = Product Type Marking CodePackage Outline DimensionsSuggested Pad LayoutIMPORTANT NOTICEDiodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to any product herein. Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights, nor the rights of others. The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website, harmless against all damages.LIFE SUPPORTDiodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.SOD-323 Dim Min Max A 0.25 0.35 B 1.20 1.40 C 2.30 2.70 H 1.60 1.80 J 0.00 0.10 K 1.0 1.1 L0.20 0.40 M 0.10 0.15α0° 8°All Dimensions in mmDimensions Value (in mm)Z 3.75 G 1.05 X 0.65 Y 1.35 C 2.40分销商库存信息: DIODESB0540WS-7。

104R功率电感规格书

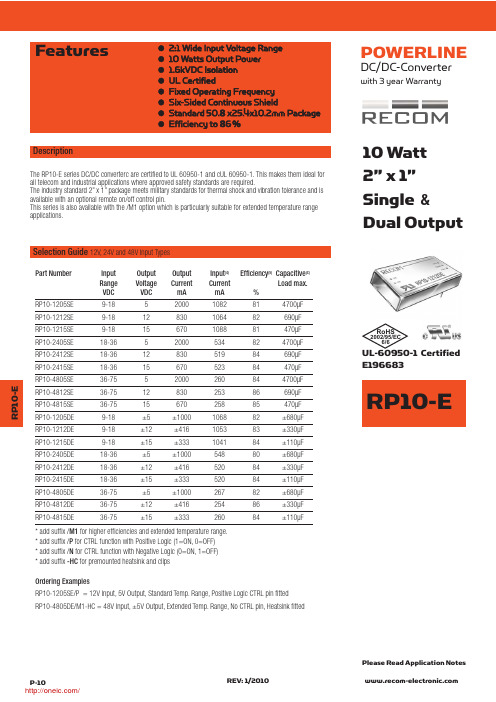

AMENDMENT RECORD TYPESDRH104 SYMBOL DATE PAGE CONTENTS DWN. BY CHK. BY APP. BY00 2010/09/09 NEW ISSUE L.WANG Y.L.LI Y.B.ZENGSPEC. No. 2/6U666-6063SPECIFICATION 1. DIMENSION(UNIT:mm)※ THE DIMENSIONS WITHOUT TOLERANCE ARE APPROX.2. RECOMMENDED DIMENSIONS (mm)3. CONNECTION (TOP VIEW)4.STAMPING (e.g.)TYPESDRH1044.7µH~39µHUNFIXED POSITION2.047µH~470µH5.ELECTRICAL CHARACTERISTIC* TESTING INSTRUMENTINDUCTANCE : HP 4284A OR EQUIV ALENT. D.C.R : TH2512B OR EQUIV ALENT. (Ta= 20℃)SATURA TION CURRENT: WK 3260B+3265B OR EQUIV ALENT.* TESTING CONDITIONS OF INDUCTANCE :(4.7-6.8µH )at 100 kHz /1V (10-470µH )at 1 kHz /1V . * SATURA TION CURRENT: INDICATES THE CURRENT WHEN THE INDUCTANCE DECREASES TO 75% OF INITIAL V ALUE. (Ta=20℃)No.UTOP P /N.CUS TOMERP /N.STAMPINDUCTANCE (µH)WI THI ND.C.R.(m Ω)Max.S ATURATION CURRENT(A)01 SDRH104-4R7NC 4R7 4.7±30% 35 3.2 02 SDRH104-6R8NC 6R8 6.8±30% 44 2.8 03 SDRH104-100MC 100 10±20% 50 2.4 04 SDRH104-120MC 120 12±20% 54 2.25 05 SDRH104-150MC 150 15±20% 61 2.0 06 SDRH104-180MC 180 18±20% 84 1.8 07 SDRH104-220MC 220 22±20% 94 1.65 08 SDRH104-270MC 270 27±20% 110 1.45 09 SDRH104-330MC 330 33±20% 150 1.35 10 SDRH104-390MC 390 39±20% 170 1.2 11 SDRH104-470MC 470 47±20% 210 1.1 12 SDRH104-560MC 560 56±20% 230 1.0 13 SDRH104-680MC 680 68±20% 260 0.93 14 SDRH104-820MC 820 82±20% 360 0.84 15 SDRH104-101MC 101 100±20% 410 0.76 16 SDRH104-121MC 121 120±20% 450 0.70 17 SDRH104-151MC 151 150±20% 640 0.63 18 SDRH104-181MC 181 180±20% 840 0.57 19 SDRH104-221MC 221 220±20% 960 0.52 20 SDRH104-271MC 271 270±20% 1070 0.47 21 SDRH104-331MC 331 330±20% 1370 0.43 22 SDRH104-391MC 391 390±20% 1550 0.39 23SDRH104-471MC471470±20%17400.36TYPESDRH104REMARKSPEC. No. 4/6U666-60636. GENERAL CHARACTERISTICS* STANDARD TESTING CONDITIONS:UNLESS OTHERWISE SPECIFIED, THE STANDARD RANGE OF ATMOSPHERIC CONDITIONS FOR MEASUREMENTS AND TESTS ARE AS FOLLOWS: AMBIENT TEMPERATURE: 15℃~35℃.RELATIVE HUMIDITY : 25% ~85%. AIR PRESSURE : 86kPa ~106kPa.IF THERE IS ANY DOUBT ABOUT THE RESULTS, MEASUREMENT SHALL BE MADE WITHIN THE FOLLOWING LIMITS: AMBIENT TEMPERATURE: 20℃±1℃. RELATIVE HUMIDITY: 63% ~67%.AIR PRESSURE : 86kPa ~106kPa.No. ITEMS CONDITIONS SPECIFICATION1 OPERA TION TEMPERA TURESTORAGE TEMPERA TURE -25 ~+ 85℃(INCLUDING COIL TEMPERA TURE RISE) -30 ~+ 85℃2 TEMPERA TURE COEFFICIENT -30 ~+85℃0 ~2000 ppm/℃3 FIXING STRENGTH SAMPLE IS PUSHED IN THREE DIRECTIONS OFX, Y AND Z WITH FORCE OF 5. 0N FOR 10±5SECONDS. AFTER SOLDERING BETWEENCOPPER PLA TE AND ELECTRODES.NO ELECTRODE DETACHMENT.4 RESISTANCE TO SOLDERINGHEA T TEST REFER TO THE SPEC “STD-001NP”. NO MECHANICAL BREAKAGE.DEVIA TION RELATIVE TO INITIALV ALUE:L: WITHIN ±5.0%5 SOLDERABILITY TEST IMMERSE THE ELECTRODE IN FLUX FOR 5SECONDS. THEN DIP THE ELECTRODE INTO ASOLDERING BA TH OF 245±5℃ FOR 2±0.5SECONDS. OVER 95% OF THE SURFACE BEING IMMERSED SHALL BE COVERED WITH NEW SOLDER UNIFORMLY.6 VIBRA TION TEST AMPLITUDE: 1.5mm P-PFREQUENCY:10~55~10Hz (1 MINUTE PER CYCLE)DURATION: 1 HOUR IN EACH OF X, Y, Z AXIS. DEVIA TION RELATIVE TO INITIAL V ALUE:L: WITHIN ±5.0%7 HUMIDITY TEST TEMPERA TURE: 40℃±2℃HUMIDITY: 90%~95%RHDURATION: 96±4 HOURS. DEVIA TION RELATIVE TO INITIAL V ALUE:L: WITHIN ±5.0%8 THERMAL SHOCK TEST 20 CYCLES OF +85℃FOR 30 MINUTES, -40℃FOR 30 MINUTES. CHARACTERISTICS AREMEASURED AFTER THE AMBIENT AIREXPOSURE OF 1 HOUR9 HIGH TEMPERA TURESTORAGE TEST TEMPERA TURE: 85℃±2℃DURATION: 96±4 HOURS10 LOW TEMPERA TURESTORAGE TEST TEMPERA TURE: -30℃±3℃DURATION: 96±4 HOURS.DEVIA TION RELATIVE TO INITIALV ALUE:L: WITHIN ±5.0%REMARK SPEC. No.5/6U666-60637. PACKINGPACKAGE TO BE ACCORDING TO PACKAGE SPECIFICATIONS (TICK THE RELEV ANT “ ” ) □KB-CTR049;* ENCLOSING CONDITION OF COILS.8. REMARK1.RoHS COMPLIANCE REMARKS* LEAD WILL BE PRESENT IN THE FERRITE CORE OF THE FRIT MATRIX IN THE COMPONENT.THIS USE, IS EXEMPT FROM RoHS LEGISLATION PER THE ANNEX (ITEM 7), WHICHREFERS TO “LEAD IN ELECTRONIC CERAMIC PART”.REMARK SPEC. No.6/6U666-6063。

BLF888A,112;中文规格书,Datasheet资料

RF performance in a common source 860 MHz narrowband test circuit f1 = 860; f2 = 860.1 860 858 858 DVB-T (8k OFDM) 858 858

[1] [2] [3] Measured at = 10 %; tp = 100 s. Measured [dBc] with delta marker at 4.3 MHz from center frequency. PAR (of output signal) at 0.01 % probability on CCDF; PAR of input signal = 9.5 dB at 0.01 % probability on CCDF.

Graphic symbol

BLF888A (SOT539A)

1 2 5 3 3 4 4 5 1

2

sym117

BLF888AS (SOT539B) 1 2 3 4 5 drain1 drain2 gate1 gate2 source

[1]

1

2 5

1

3

4

3 5 4

2

sym117

[1]

Connected to flange.

[1] [2]

Conditions VGS = 0 V; ID = 2.4 mA VDS = 10 V; ID = 240 mA VGS = 0 V; VDS = 50 V VGS = VGS(th) + 3.75 V; VDS = 10 V VGS = 10 V; VDS = 0 V VGS = VGS(th) + 3.75 V; ID = 8.5 A VGS = 0 V; VDS = 50 V; f = 1 MHz VGS = 0 V; VDS = 50 V; f = 1 MHz VGS = 0 V; VDS = 50 V; f = 1 MHz

NOIH2SM1000S-HHC;中文规格书,Datasheet资料

NOIH2SM1000AHAS2 Image SensorINTRODUCTIONScopeThis ICD version is generated after qualification campaign closure. This specification details the ratings, physical, geometrical, electrical and electro-opticalcharacteristics, and test- and inspection-data for the High Accuracy Star Tracker (HAS2) CMOS active pixel image sensor (CMOS APS).The device described in this document is protected by US patent 6,225,670 and others.Component Type ValuesTable 10 on page 8 provides a summary of the type variants of the basic CMOS image sensor. The complete list of specifications for each type variant is given in Detailed Specifications on page 9.All specifications in Detailed Specifications on page 9 are given at 25 ±3°C, under nominal clocking and bias conditions. Exceptions are noted in the ‘Remarks’ field. Maximum RatingTable 11 on page 9 specifies the maximum ratings. Do not exceed these ratings at any times, during use or storage. Physical Dimension and Geometrical Information Figure 2 on page 24 shows the physical dimensions of the assembled component. The geometrical information in Figure 4 on page 25 describes the position of the die in the package.Pin AssignmentFigure 5 on page 26 contains the pin assignment. The figure contains a schematic drawing and a pin list. A detailed functional description of each pin is available in Pin List on page 36.Soldering InstructionsSoldering is restricted to manual soldering only. No wave or reflow soldering is allowed. For manual soldering, the following restrictions are applicable:•Solder 1 pin on each of the four sides of the sensor.•Cool down for a minimum period of 1 minute before soldering another pin on each of the four sides.•Repeat soldering of 1 pin on each side, including a 1 minute cool down period.Handling PrecautionsThe component is susceptible to damage by electro-static discharge. Therefore, use suitable precautions for protection during all phases of manufacture, testing, packaging, shipment, and any handling. Follow these guidelines:•Always manipulate devices in an ESD controlled environment.•Always store the devices in a shielded environment that protects against ESD damage (at least a non-ESD generating tray and a metal bag).•Always wear a wrist strap when handling the devices and use ESD safe gloves.•The HAS2 is classified as class 1A (JEDEC classification - [AD03]) device for ESD sensitivity. For proper handling and storage conditions, refer to the ON Semiconductor application note AN52561.Limited WarrantyON Semiconductor’s Image Sensor Business Unit warrants that the image sensor products to be delivered hereunder, if properly used and serviced, will conform to Seller’s published specifications and will be free from defects in material and workmanship for two (2) years following the date of shipment. If a defect were to manifest itself within two (2) years period from the sale date, ON Semiconductor will either replace the product or give credit for the product.Return Material Authorization (RMA)ON Semiconductor packages its image sensor products in a clean room environment under strict handling procedures and ships all image sensor products in ESD-safe, clean-room-approved shipping containers. Products returned to ON Semiconductor for failure analysis should be handled under these same conditions and packed in its original packing materials, or the customer may be liable for the product.Storage InformationThe components must be stored in a dust-free and temperature-, humidity-and ESD-controlled environment.•Store devices in special ESD-safe trays such that the glass window is never touched.•Close the trays with EDS-safe rubber bands.•Seal the trays in an ESD-safe conductive foil in clean room conditions.•For transport and storage outside a clean room, pack the trays in a second ESD-save bag that is sealed in cleanroom.Additional InformationThe HAS sensor is subject to the standard European export regulations for dual use products. A Certificate of Conformance will be issued upon request at no additional charge. The CoC refers to this document. Additional screening tests is done on request at additional cost.The following data is delivered by default with FM sensors:•Sensor calibration data •Temperature calibration data •Certificate of Conformance to this detailed specification•Visual inspection report•Bad pixel mapITAR InformationThe NOIH2SM1000A is an ITAR-free component.Table 1. ORDERING INFORMATIONMarketing Part Number Description Package NOIH2SM1000T-HHC HAS2 Mono, Flight Model, Level 284-pin JLCC NOIH2SM1000A-HHC HAS2 Mono, Engineering ModelNOIH2SM1000S-HHC HAS2 Mono, Flight Model, Level 1NOIH2SM1000A-HWC HAS2 Mono Windowless, Engineering ModelNOIH2SM1000S-HWC HAS2 Mono Windowless, Flight Model, Level 1ORDERING CODE DEFINITIONO = OptoN = ON SemiconductorHAS2M=MonoH= JLCCCommercial Temperature Range 1000M HS = Standard Process1.0 MP Resolution A= Engineering Model H= BK7G18 GlassI I = Image Sensors H CN O H2S A −S= Flight Model, Level 1T= Flight Model, Level 2W= WindowlessAPPLICABLE DOCUMENTSThe following documents form part of this specification:Table 2. APPLICABLE DOCUMENTSNo.Reference Title Issue DateAD01ESCC Generic Specification 9020Charge Coupled Devices, Silicon, Photosensitive2March 2010AD02001-06225(Note 1)Electro-optical test methods for CMOS image sensors E October, 2008AD03JESD22-A114-B Electrostatic Discharge (ESD) Sensitivity Testing HumanBody Model (HBM)B June, 2000AD04APS2-FVD-06-003Process Identification Document for HAS22February, 2008 AD05001-49283Visual Inspection for FM devices1January, 2008 AD06001-49280HAS2 FM Screening2June, 20091.This specification will be superseded by the ESCC basic specification 25000, which is currently under development. The current referenceis an internal ON Semiconductor procedure and is a confidential document.2.Lot acceptance and screening are based on ESCC 9020 issue 2. Please note that Lot Acceptance and Screening on page 6 − is valid forthe Flight Model Level 1 devices. For more information on Flight Model 1 Windowless devices, please contact imagesensors@DETAILED INFORMATIONDeviations from Generic SpecificationLot acceptance and screening are based on ESCC 9020 issue 2. See Lot Acceptance and Screening on page 6 for more information.Mechanical RequirementsDimension CheckThe dimensions of the components specified here is checked and must comply with the specifications and the tolerances indicated in Figure 2 on page 24 Geometrical CharacteristicsThe geometrical characteristics of the components specified here is checked and must comply with the specifications and tolerances given in Figure 2 on page 24 and Figure 3 on page 25WeightThe maximum weight of the components specified here is specified in Table 14 on page 9Materials and FinishesThe materials and finishes is as specified in this document. Where a definite material is not specified, a material which enables the components to meet the performance requirements of this specification must be used. See Note 2. CaseThe case is hermetically sealed and must have a ceramic body and a glass window.Table 3. CASEType JLCC−84Material Black Alumina BA−914 Thermal expansion coefficient7.6 x 10−6/KHermeticity< 5 x 10−7 atms. cm3/s Thermal resistance(Junction to case)3.633°C/WLead Material and FinishTable 4. LEAD MATERIAL AND FINISHLead Material KOVAR1e Finish Nickel, min 2 m m2nd Finish Gold, min 1.5 m mWindowThe window material is a BK7G18 glass lid with anti-reflective coating applied on both sides.The optical quality of the glass must have the specifications in Table 15 on page 9.The anti reflective coating has a reflection coefficient less than 1.3% absolute and less than 0.8% on average, over a bandwidth from 440 nm to 1100 nm.Level 2 versus Level 1 differencesHAS2 Level 2 devices are differing from Level 1 devices in Lot Acceptance and Screening on page 6•100% screening is applied with burn-in limited to 168 hinstead of 240 h as for Level 1.•Assembly process is based on ESA qualified process (same procedures and materials)•Devices will be fully tested at room temperature, electrical testing at 85 degrees is limited to power consumption measurements only.•X/Y dye placement is relaxed to +/- 200 m m.•Mismatching between odd and even columns in Direct Readout is allowed but shall stay in the limit of127LSB.•The defect and particles specification will be the same as for the Engineering Model - NOIH2SM1000A-HHC – with the exception of the defective columns which are not allowed in the Level 2 devices. Refer to Table 10“Type Variant Summary” on page 8.•Endurance testing during wafer LAT is limited to a 1000 h burn in instead of 2000 h and will be performed on 3 un-screened parts instead of 6.•Prior to endurance testing and total dose testing, a stabilization bake of 48 hrs, followed by a 168 hrs burn-in, shall be performed.•During wafer LAT, the Electro-optical measurements is limited on 2 parts (1 from endurance testing and 1 from radiation testing) instead of 6.•For each assembly batch (manufacturing-lot), 2 screened devices will be made available for a DPA test. An assembly batch is defined as a group of parts which have been assembled within a time window of less than one week. The DPA devices can be rejected devices (glass lid cosmetic defects, electrical defects,…) but has to be screened through the same thermal steps as the HAS2 “level2”. The DPA test will be carried out by ON Semiconductor as a customer courtesy.Prior to DPA testing, the following tests are performed: Solderability and Resistance to Solvents (marking permeability).NOTE:As the glass lid removal is a best effort activity, the DPA test cannot be 100% guaranteed.•Pictures and defect maps are not included in the data pack, but will be made available upon request.•Assembly lot acceptance testing is not performed.Data PackEach set of devices will have a data pack which will be made available to the customer. The data pack consists of:•CoC form referring to the applicable specification •Calibration data •Screening Report•Life Test Report and Radiation (Total Dose) Test Report for each wafer lot •Electrical Test Report •Spectral response data •Visual Inspection Report •DPA Test ReportMarkingGeneralThe marking must consist of lead identification and traceability information.Lead IdentificationAn index to pin 1 must be located on the top of the package in the position defined in Figure 2 on page 24. The pin numbering is counter clock-wise, when looking at the top-side of the component.Traceability InformationEach component must be marked such that complete traceability is maintained.The component must have a number as follows:Figure 1. Product MarkingXXXXX = Specific Device Code A = Assembly Location WL = Wafer Lot YY = YearWW = Work WeekNNNN = Serial NumberTable 5. PACKAGE MARK DECODEROrderable Part Number Package Mark: Line 1Package Mark: Line 2Package Mark: Line 3NOIH2SM1000T-HHC NOIH2SM1000T -HHC_NNNN AWLYYWW NOIH2SM1000A-HHC NOIH2SM1000A -HHC_NNNN AWLYYWW NOIH2SM1000S-HHC NOIH2SM1000S -HHC_NNNN AWLYYWW NOIH2SM1000A-HWC NOIH2SM1000A -HWC_NNNN AWLYYWW NOIH2SM1000S-HWCNOIH2SM1000S-HWC_NNNNAWLYYWWwhere NNNN- serialized number controlled manually by ON Semiconductor, BELGIUM where DD-MM-YYYY represents the lot assembly date NOIH2SM1000T-HHC has a Minimum Order Quantity of 10Electrical and Electro −optical MeasurementsElectrical and Electro −optical Measurements at Reference TemperatureThe parameters to be measured to verify the electrical and electro-optical specifications are given in Table 18 on page 13 and Table 27 on page 23. Unless otherwise specified, the measurements must be performed at a environmental temperature of 22 ±3°C.For all measurements, the nominal power supply, bias,and clocking conditions apply. The nominal power supply and bias conditions are given in Table 28 on page 23; thetiming diagrams in Figure 35 on page 47 and Figure 37 on page 49.NOTE:The given bias and power supply settings implythat the devices are measured in ‘soft-reset’condition.Electrical and Electro −optical Measurements at High and Low TemperatureTable 19 on page 14 and Table 20 on page 15 list the parameters to be measured to verify electrical and electro-optical specifications. Unless otherwise specified,the measurements must be performed at –40 (–5 +0) °C and at +85 (+5 –0) °C.Circuits for Electrical and Electro−optical Measurements Circuits for performing the electro−optical tests in Table18 on page13 and Table 27 on page 23 are shown in Figure 49 on page 59 to Figure 52 on page 59.Burn−in TestParameter Drift ValuesThe parameter drift values for power burn-in are specified in Table 21 on page 17. Unless otherwise specified, the measurements must be conducted at an environmental temperature of 22 ±3°C and under nominal power supply, bias, and timing conditions.Do not exceed the parameter drift values. In addition to these drift value requirements, do not exceed the limit values of any parameter, as indicated in Table 18 on page13 Conditions for High Temperature Reverse Bias Burn-in Not ApplicableConditions for Power Burn-inThe conditions for power burn-in is specified in Table 24 on page 19 of this specification.Electrical Circuits for High Temperature Reverse Bias Burn-inNot ApplicableElectrical Circuits for Power Burn-inCircuits to perform the power burn-in test are shown in Figure 48 on page 58 and Figure 49 on page 59 of this specification.Environmental and Endurance TestsElectrical and Electro-optical Measurements on Completion of Environmental TestThe parameters to be measured on completion of environmental tests are listed in Table 25 on page 20. Unless otherwise stated, the measurements must be performed at a environmental temperature of 22 ±3°C. Measurements of dark current must be performed at 22 ±1°C and the actual environmental temperature must be reported with the test results.Electrical and Electro-optical Measurements At Intermediate Point During Endurance TestThe parameters to be measured at intermediate points during endurance test of environmental tests are listed in Table 25 on page 20. Unless otherwise stated, the measurements must be performed at an environmental temperature of 22 ±3°C.Electrical and electro-optical Measurements on Completion of Endurance TestThe parameters to be measured on completion of endurance tests are listed in Table 25 on page 20. Unless otherwise stated, the measurements must be performed at a environmental temperature of 22 ±3°C.Conditions for Operating Life TestThe conditions for operating life tests must be as specified in Table 24 on page 19 of this specification.Electrical Circuits for Operating Life TestCircuits for performing the operating life test are shown in Figure 49 on page 59 and next ones of this specification. Conditions for High Temperature Storage TestThe temperature to be applied must be the maximum storage temperature specified in Table 11 on page 9 of this specification.Total Dose Radiation TestApplicationThe total dose radiation test must be performed in accordance with the requirements of ESCC Basic Specification 22900.Parameter Drift ValuesThe allowable parameter drift values after total dose irradiation are listed in Table 22 on page 18 . The parameters shown are valid after a total dose of 42 KRad and 168h/100°C annealing.Bias ConditionsContinuous bias must be applied during irradiation testing as shown in Figure 49 on page 59 and next ones of this specification.Electrical and Electro-optical MeasurementsThe parameters to be measured, prior to, during and on completion of the irradiation are listed in Table 27 on page23 of this specification. Only devices that meet the specification in Table 18 on page 13 of this specification must be included in the test samples.Lot Acceptance and ScreeningThis section describes the Lot Acceptance Testing (LAT) and screening on the HAS2 FM devices. All tests on device level must be performed on screened devices (see Table 9 on page 7)Wafer Lot AcceptanceThis is the acceptance of the silicon wafer lot. This must be done on every wafer lot that is used for the assembly of flight models.Table 6.Test Test Method Number of Devices Test Condition Test Location Wafer processingdata reviewPID NA NA ON Semiconductor SEM ESCC 21400 4 naked dies NA Test houseTotal dose test ESCC 22900 3 devices42 krad, not to exceed3.6 krad/hr Test house by ON SemiconductorEndurance test MIL-STD-883 Method 1005 6 devices2000h at +125°C Test houseBefore and after total dose test and endurance test:•Electrical measurements before and after at high, low, and room temperature. See Table 18 on page13, Table 19 on page 14 and Table 20 on page 15 of this specification.•Visual inspection before and after•Detailed electro-optical measurements before and after Glass Lot AcceptanceTransmission and reflectance curves that are delivered with each lot must be compared with the specifications in Table 15. Three glass lids are chosen randomly from the lot and measured in detail. The results are compared with Figure 5 on page 26.Package Lot Acceptance•Five packages are chosen randomly from the lot and measured in detail. The results are compared with Figure 2 on page 24.•A solderability test is covered in the assembly lot acceptance tests (Table 7)Table 7. ASSEMBLY LOT ACCEPTANCETest Test Method Number ofDevices Test Condition Test LocationSpecial assembly house inprocess controlAssembly House Bond strength test MIL-STD-883 method 20112D Assembly HouseAssembly house geometrical datareviewReview All CYSolder ability MIL-STD883, method 20033D Test House Terminal strength MIL-STD 883, method 2004Marking permanence ESCC 24800Geometrical measurements PID All CY Temperature cycling MIL-STD 883, method 10105Condition B50 cycles–55°C / +125°CTest House Moisture resistance JEDEC Std. Method A101-B240 h at 85°C / 85%Test HouseTable 7. ASSEMBLY LOT ACCEPTANCETestTest LocationTest ConditionNumber of DevicesTest MethodDPADie shear test MIL-STD-883 method 20194N/A Test House Bond pull testMIL-STD-883 method 2011All wiresTest HouseNOTE:As the glass lid is removed from the packageprior to DPA, the results of the DPA cannot be guaranteed.Before and after the following tests are done:•Electrical measurements conform to Table 18 on page 13 of this specification •Detailed visual inspection •Fine leak test + gross leak testFine- and gross-leak tests must be performed using the following methods:Fine Leak test : MIL-STD-883, Test Method 1014,Condition AGross Leak test : MIL-STD-883, Test Method 1014,Condition CThe required leak rate for fine leak testing is 5x 10−7atms.cm 3/sTable 8. PERIODIC TESTINGTestTest MethodNumber of DevicesTest ConditionTest Location Mechanical shock MIL-STD 883, method 20022 B - 5 shocks, 1500 g – 0.5 ms – ½ sine, 6 axesTest House Mechanical vibration MIL-STD 883, method 20072A - 4 cycles, 20 g 80 to 2000 Hz, 0.06 inch 20 to 80 Hz, 3 axesTest HouseDPADie shear test MIL-STD-883 method 20192N/A Test House Bond pull testMIL-STD-883 method 2011All wiresTest HouseNOTE:As the glass lid is removed from the packageprior to DPA, the results of the DPA cannot be guaranteed.Periodic testing is required every two years. Before and after the following tests are done:•Electrical measurements conform to Table 18 on page 13•Detailed visual inspection •Fine leak test + gross leak testFine- and gross-leak tests must be performed using the following methods:Fine Leak Test : MIL-STD-883, Test Method 1014,Condition AGross Leak Test : MIL-STD-883, Test Method 1014,Condition CThe required leak rate for fine leak testing is 5x 107atms.cm 3/sTable 9. SCREENINGNo.TestTest MethodNumber of DevicesTest Condition Test Location 1HCRT Electrical measurements001-53958AllHT +85°C LT –40°C RT +25°CON Semiconductor2Visual inspection001-49283 + ICD All ON Semiconductor 3Die placement measurements Internal proc.All ON Semiconductor 4XRAYESCC 20900All Test House 5Stabilization bake MIL-STD-883 method 1008All 48h at 125°C Test House 6Fine leak testMIL-STD-883 method 1014AllATest HouseTable 9. SCREENING7Gross leak test MIL-STD-883 method 1014All C Test HouseTest House 8Temperature cycling MIL-STD-883 method 1010All B - 10 cycles–55°C +125°C 9Biased Burn-in ICD All240 h at +125°C ON Semiconductor 10Mobile Particle Detection MIL-STD-883 method 2020All A Test House 11Fine leak test MIL-STD-883 method 1014All A Test House 12Gross leak test MIL-STD-883 method 1014All C Test HouseON Semiconductor 13HCRT Electrical measurements001-53958All HT +85°CLT –40°CRT +25°C 14Final Visual Inspection001-49283 + ICD All ON SemiconductorTABLES AND FIGURESSpecification TablesTable 10. TYPE VARIANT SUMMARYHAS2 Type Variants Engineering Model Flight Model Optical quality (see Optical Quality − Definitions on page 67)Dead pixels10020Bright pixels in FPN image5020Bad pixels in PRNU image15050Bad columns50Bad rows50Bright pixel clusters2 adjacent bright pixels2524 or more adjacent bright pixels100DSNU defects at 22 dec BOL12001000DSNU defects at 22 dec EOL15001250 Particle contaminationFixed particles outside focal plane N/A N/AMobile particles > 20 m m00Fixed particles on focal plane > 20 m m00Mobile particles > 10 m m and < 20 m m2010Fixed particles on focal plane > 10 m m and < 20 m mParticles < 10 m m N/A N/AWafer lot acceptance (see section Wafer Lot Acceptance on page 6)NO YesGlass lot acceptance (see section Glass Lot Acceptance on page 6)NO Yes Assembly lot acceptance (Table 7 on page 6)NO Yes Periodic testing (Table 8 on page 7)NO Yes Screening (Table 9 on page 7)NO Yes Calibration data NO YesVisual Inspection + particle mapping NO YesTable 11. MAXIMUM RATINGSNo.Characteristic Min Typ Max Unit Remarks1Any supply voltage except VDD_RES–0.5 3.3+7.0V2Supply voltage at VDD_RES–0.5 3.3+5.0V 3.3 V for normal operation; up to5V for increased full well capacity.3Voltage on any input terminal–0.5 3.3Vdd + 0.5V4Soldering temperature NA NA260°C Hand soldering only; See Solder-ing Instructions on page 1 5Operating temperature–40NA+85°C6Storage temperature–55NA+125°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.Detailed Specifications − All Type VariantsTable 12. GENERAL SPECIFICATIONSNo.Characteristic Min Typ Max Unit Remarks1Image sensor format N/A1024 x 1024N/A pixels2Pixel size N/A18N/A m m3ADC resolution N/A12N/A bit10-bit accuracy at 5 Msamples/secTable 13. SILICON PARTICLE CONTAMINATION SPECIFICATIONSNo.Characteristic Min Typ Max Unit Remarks1Optical quality: Particle max size N/A N/A20m m See Type Variant Summary onpage 8Table 14. MECHANICAL SPECIFICATIONSNo.Characteristic Min Typ Max Unit Remarks1a Flatness of image area NA7.4NA m m Peak-to-peak at 25 ±3°CSpecified by the foundry over anentire 8-inch wafer 1b Flatness of glass lid NA90150m m Towards ceramic package2Mass7.77.858.0g3Total thickness 3.2 3.3 3.4mm Package + epoxy + glass lid4a Die position, X offset NA NA0.1mm Die in center of cavity4b Die position, Y offset NA NA0.1mm Die in center of cavity5Die position, parallelism vs window Die position, parallelism vs backside –0.10.10.10.1mm6Die position, Y tilt–0.100.1°7Die position, X tilt–0.100.1°8Die – window distance0.250.30.35mmTable 15. GLASS LID SPECIFICATIONSNo.Characteristic Min Typ Max Unit Remarks 1a XY size26.7 x 26.726.8 x 26.826.9 x 26.9mm1b Thickness 1.4 1.5 1.6mmTable 15. GLASS LID SPECIFICATIONSNo.RemarksUnitMaxTypMinCharacteristic2a Spectral range for optical coating ofwindow440NA1100nm2b Reflection coefficient for window NA<0.8<1.3%Over bandwidth indicated in 2a3Optical quality:Scratch max widthScratch max numberDig max sizeDig max number N/A N/A1056025m mTable 16. ENVIRONMENTAL SPECIFICATIONSNo.Characteristic Min Typ Max Unit Remarks1Operating temperature–40NA+85°C2Storage temperature–55NA+125°C Lower storage temperatures (up to–80°C) have been tested and thedevice survives, but this is not afully qualified temperature.3Sensor total dose radiation tolerance N/A42N/A krad (Si)Tested for functionality up to300krad, 42 krad is guaranteed4Sensor SEL threshold with ADC enabled NA NA>110MeV cm3mg-1Equivalent LET valueTable 17. ELECTRICAL SPECIFICATIONSNo Characteristic Min Typ Max Unit Remarks1Total power supply current stand-by1618.521mA2Total power supply current, operational353740mA ADC at 5 MHz sampling ratemeasured3Power supply current to ADC, operational: analog + digital 171921mA ADC at 5 MHz sampling ratemeasured4Power supply current to image core,operational1415.517mA5Input impedance digital input3NA NA M W6Input impedance ADC input3NA NA M W7Output amplifier voltage range 2.2 2.45 2.6V8Output amplifier gain setting 0NA1NA–Nominal 1measured reference9Output amplifier gain setting 1 1.9 2.1 2.3–Nominal 2relative to setting 010Output amplifier gain setting 2 3.8 4.1 4.4–Nominal 4relative to setting 011Output amplifier gain setting 37.27.78.2–Nominal 8relative to setting 012Output amplifier offset setting 00.860.93 1.0V0 decodes to middle value 13Output amplifier offset setting 31 1.30 1.35 1.40V14Output amplifier offset setting 320.430.510.6V15Output amplifier offset setting 630.800.90 1.0V16ADC ladder network resistance NA 1.8NA k W Typical value17ADC differential nonlinearity NA711lsb18ADC integral nonlinearity NA818lsb分销商库存信息: ONSEMINOIH2SM1000S-HHC。

GFC0412DS-DF00;中文规格书,Datasheet资料

SPECIFICATION FOR APPROVALCustomerDescription D C F A NPart No. R E V.Delta Model No.GFC0412DS-DF00 REV. 01 Sample Issue No.Sample Issue Date FEB.03.2009PLEASE SEND ONE COPY OF THIS SPECIFICAITONBACK AFTER YOU SIGNED APPROVAL FOR PRODUCTION PRE-ARRANGMENT.APPROVED BY:DATE :DELTA ELECTRONICS, INC.TAOYUAN PLANT252, SHANG YING ROAD, KUEI SAN INDUSTRIAL ZONE TAOYUAN SHIEN, TAIWAN, R.O.C.TEL:886-(0)3-3591968FAX:886-(0)3-3591991Application Notice1.Delta will not guarantee the performance of the products if the application conditionfalls outside the parameters set forth in the specification.2. A written request should be submitted to Delta prior to approval if deviation fromthis specification is required.3.Please exercise caution when handling fans. Damage may be caused when pressure isapplied to the impeller, if the fans are handled by the lead wires, or if the fan washard-dropped to the production floor.4.Except as pertains to some special designs, there is no guarantee that the products willbe free from any such safety problems or failures as caused by the introduction ofpowder, droplets of water or encroachment of insect into the hub.5.The above-mentioned conditions are representative of some unique examples and viewedas the first point of reference prior to all other information.6.I t is very important to establish the correct polarity before connecting the fan to thepower source. Positive (+) and Negative (-). Damage may be caused to the fans ifconnection is with reverse polarity, if there is no foolproof method to protect againstsuch error specifically mentioned in this spec.7.Delta fans without special protection are not suitable where any corrosive fluids areintroduced to their environment.8.Please ensure all fans are stored according to the storage temperature limits specified.Do not store fans in a high humidity environment. We highly recommend performance testing is conducted before shipping, if the fans have been stored over 6 months.9.Not all fans are provided with the Lock Rotor Protection feature. If you impair therotation of the impeller for the fans that do not have this function, the performanceof those fans will lead to failure.10. Please be cautious when mounting the fan. Incorrect mounting of fans may causeexcess resonance, vibration and subsequent noise.11.It is important to consider safety when testing the fans. A suitable fan guard should befitted to the fan to guard against any potential for personal injury.12.Except where specifically stated, all tests are carried out at room (ambient) temperature and relative humidity conditions of 25o C, 65% RH. The test value is only for fan performance itself.13.Be certain to connect an “ 4.7µF or greater” capacitor to the fan externally whenthe application calls for using multiple fans in parallel, to avoid any unstable power.Doc. No: FMBG-ES Form 001 Rev. 0001Date: June 24, 2009分销商库存信息: DELTA-PRODUCT-GROUPS GFC0412DS-DF00。

EV2011;中文规格书,Datasheet资料

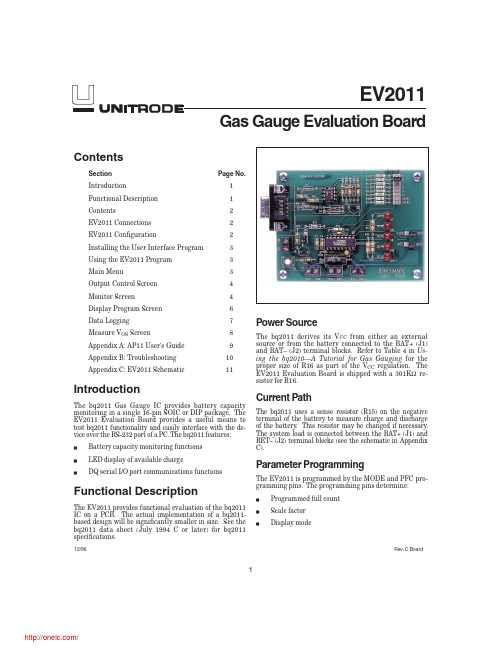

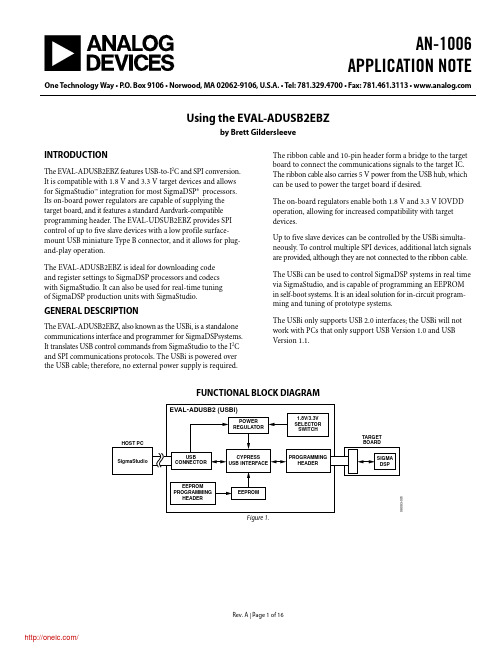

ContentsSection Page No.Introduction1Functional Description1Contents2EV2011 Connections2EV2011 Configuration2Installing the User Interface Program3Using the EV2011 Program3Main Menu3Output Control Screen4Monitor Screen4Display Program Screen6Data Logging7Measure V OS Screen8Appendix A:AP11 User's Guide9Appendix B:Troubleshooting10Appendix C:EV2011 Schematic11 IntroductionThe bq2011Gas Gauge IC provides battery capacity monitoring in a single16-pin SOIC or DIP package.The EV2011Evaluation Board provides a useful means to test bq2011functionality and easily interface with the de-vice over the RS-232port of a PC.The bq2011features:n Battery capacity monitoring functionsn LED display of available chargen DQ serial I/O port communications functions Functional DescriptionThe EV2011provides functional evaluation of the bq2011 IC on a PCB.The actual implementation of a bq2011-based design will be significantly smaller in size.See the bq2011data sheet(July1994C or later)for bq2011 specifications.Power SourceThe bq2011derives its V CC from either an external source or from the battery connected to the BAT+(J1) and BAT–(J2)terminal blocks.Refer to Table4in Us-ing the bq2010—A Tutorial for Gas Gauging for the proper size of R16as part of the V CC regulation.The EV2011Evaluation Board is shipped with a301KΩre-sistor for R16.Current PathThe bq2011uses a sense resistor(R15)on the negative terminal of the battery to measure charge and discharge of the battery.This resistor may be changed if necessary.The system load is connected between the BAT+(J1)and RET–(J2)terminal blocks(see the schematic in AppendixC).Parameter ProgrammingThe EV2011is programmed by the MODE and PFC pro-gramming pins.The programming pins determine:n Programmed full countn Scale factorn Display mode1EV2011Gas Gauge EvaluationBoard 12/96Rev.C BoardEV2011 ContentsEach package contains the following items:1EV2011 PC BoardThis includes the bq2011sample,current regulator, programming jumpers,battery divider resistors, and the PC serial port interface.1EV2011 DQ/RS-232 Cable1EV2011 (v2.0) User Interface Program Diskette This program runs on any AT-compatible computer equipped with a standard RS-232(COM1,COM2, COM3,or COM4)serial port,and provides the user with a complete menu-driven system to control, monitor,and log data from the EV2011Evaluation Board.The User Interface Program communicates with the bq2011over the DQ serial I/O port using the RS-232interface.Please check to make sure that all items are present and in good condition.If you have any problems,please con-tact your Benchmarq representative or call Benchmarq at214-407-0011.EV2011 ConnectionsThe connections for the EV2011are described below. Please refer to the attached schematic in conjunction with these descriptions.JP1–JP8Battery cell divider.JP1-JP6are usedto divide the battery voltage by5to10.JP7and JP8are user-definable,but areconfigured for11and12cells on thisboard.JP9V CC supply.This jumper is used to se-lect the V CC supply for the bq2011.WhenJP9is on B(near Q1),the supply is takenfrom the BAT+input and is regulated bythe bq2011and Q1.When JP9is on L(near D12),the V CC supply is provided byLBAT+.If V CC is supplied by LBAT+,itmust not exceed the specified V CC voltagerange in the bq2011data sheet.JP11PFC programming pins.This jumpercan be set low,high impedance,or high.Ifthe jumper is between the middle pin andlow,PFC is set low.If the jumper is re-moved,the PFC is high impedance,or Z.If the jumper is between the middle pinand high,PFC is set high.JP10MODE selection jumper.If the jumperis between the middle pin and V CC,thedisplay mode is relative.If the jumper isbetween the middle pin and MODE,thedisplay mode is absolute.If the jumper isremoved,no display is available.DSP Display input(DISP pin).DSP is con-nected in parallel with the push-buttonswitch S1provided on the EV2011board.An external switch configuration can bemade using DSP.When the EV2011isfloating and detects charging or dis-charging,the LED outputs are active toreflect the charge state.When the DISPinput is pulled low,the LEDs reflects thecharge state.EV2011 ConfigurationThe EV2011Evaluation Board may be used with or without the DQ/RS-232Interface Program.The Evalua-tion Board should first be configured before connecting the battery or the RS-232cable.Step1Connecting the power supplyThe EV2011can operate from power pro-vided by the battery being monitored orfrom LBAT+.Set the battery divider(JP1–JP8)to the correct number of bat-tery cells prior to connecting the battery.If the bq2011will be powered from thebattery,connect JP9to B.If the bq2011will be powered from an external supply,connect JP9to L.Important:Connectthe battery ONLY after setting JP1-JP8and JP9.Step3Connecting the RS-232cableConnect the cable provided to the serialport of any PC.Please ensure no mem-ory-resident programs use this serialport.Step4Connecting the loadThe external load is connected betweenBAT+and RET-(J2)on the EV2011.Asense resistor(R15)is in series with thenegative terminal of the battery.TheEV2011board is supplied with a0.005,1%3W resistor.Please ensure that thedischarge load does not exceed the V SRspecification for the bq2011.R15may bechanged to a different-value resistor.2Rev.C Board EV2011Installing the User Interface ProgramThe User Interface Program(named“EV2011”)runs on any PC-compatible computer.The program may be run from the disk provided,or it may be installed on any di-rectory on the computer's hard disk.To run the program from the hard disk,simply copy all the files from the disk supplied to the hard disk.All the files should re-side in the same directory.The User Interface Program installs a driver to control the DQ/RS-232interface.This driver asks which COM port is connected to the EV2011Evaluation board.If communication is not established with the EV2011 board,the Main Menu does not appear.Please refer to Appendix B(Troubleshooting)if the program does not establish communication with the EV2011.The EV2011uses the PC-AT real-time clock to provide the proper bit timing for serial communication with the bq2011.The modem control lines are used as the single-wire serial interface to the bq2011.Any TSR that uses the PC real-time clock affects the operation of the EV2011.For proper operation,the EV2011should not be operated from a DOS shell program.If the PC is a notebook or portable type,it may be config-ured to save battery power by adjusting the clocks ac-cording to the activity under way.Configure the notebook to run in“High Performance”mode for reliable communication between the EV2011and the PC.The EV2011UIP terminates if communication with the EV2011board is lost.Start the User Interface Program as follows:C>EV2011Using the EV2011 ProgramEV2011is a menu-driven program.Almost all of the functions and entries are made by positioning the high-lighted cursor on the function desired and pressing the ENTER key,or by typing a value and then pressing the ENTER key.Key functions are as follows:ARROWkeysUse the arrow keys to move the high-lighted cursor around the screen.ENTERkeyPress the ENTER key to select the valuecurrently being displayed for a parameter,or to perform a function selected by thehighlighted cursor.ESCAPEkeyPress the ESCAPE key to escape from anyfunction back to the main menu,or to es-cape from any parameter value screen backto the menu displaying that parameter.F3key Press the F3key to display a help file forthe selected function or parameter. Main MenuThe Main Menu appears after the EV2011program has started.If this menu does not appear,communication with the EV2011has not been established;please refer to Appendix B(Troubleshooting)if the EV2011does not display the Main Menu.The Main Menu shows six functions that may be activated;see e the cursor keys(arrow keys)to position the highlighted cursor over the function to be activated and press the ENTER key.For help,press the F3key,and a help note about the function appears.Press the ESCAPE key to exit from the EV2011program.3EV2011Rev.C BoardBenchmarq BQ2011Evaluation Board Main Menu(v2.0)<Initialize><Monitor><Output Control><Data Log><Display Program><Measure Vos>Please enter SR value B in Display Program for Proper OperationESC to exit program F3for HelpFigure 1. Main MenuThe Main Menu functions are as follows:<Initialize>Sends a reset command to the bq2011.<Output Control>Activates a screen from which the LEDs can be controlled.<Monitor>Activates a screen from which the bq2011activity is monitored on a real-time basis. <Data Log>Allows entering a file name to whichbq2011data will be logged,and the log-ging period in seconds.When the log isactivated,the display changes to theMonitor screen with a top display of:Logging Record:xx<Display Program>Activates a screen showing the current program settings for the bq2011.<Measure V OS>This allows the user to determine the ap-parent offset voltage of the bq2011under test.A minimum of2minutes is required to complete the V OS measurement,which has a resolution of±0.15mV per2minutes.Output Control ScreenThis screen controls the bq2011LEDs;see Figure2. Press the space bar to toggle the LED OFF and ON. Pressing the push-button switch activates the display. The bq2011LED output returns to normal on exiting this screen.Monitor ScreenThis screen monitors real-time changes of the bq2011; see Figure 3.The program continually updates the monitor screen.As conditions change,the new values are displayed.Time Time of day in HH:MM:DD,24-hour nota-tion.Empty/Full This indicates the current value for GG inthe TMPGG register of the bq2011.Thecapacity value is giventh steps.Date Current date in MM/DD/YY notation.NAC NAC register values multiplied by thescale value and divided by the sense re-sistor value to give mAH.LMD Last Measured Discharge expressed interms of mAH.This is the8-bit LMD reg-ister value multiplied by the scale valuetimes256and divided by the sense resis-tor to give mAH.Sense Resis-tor ValueThis is the sense resistor value from theProgramming menu.Average V SRCurrentThis is the average battery current.TimeRemainingDuring discharge only,this is the time re-maining at the average current(NAC/Avg.V SR current)DigitalFilter SettingThis is the value of the digital magnitudefilter.Temp Step This is a display of the active tempera-ture step,which ranges from0(for tem-peratures<-30°C)to12for temperatures>80°C).Activity This indicates the charging/dischargingactivity occurring with the battery.CHARGE is displayed if the battery ischarging,while DISCHARGING is dis-played if the battery is being discharged,or if it is idle(no charging taking place).OVERLOAD is displayed if the voltagedrop across the sense resistor exceeds the 4Rev.C BoardBenchmarq BQ2011Evaluation Board Output Control ScreenOutput PinsLED Display LED1:OFF/ON LED2:OFF/ONLED Display LED3:OFF/ON LED4:OFF/ONLED Display LED5:OFF/ONESC to main menuFigure 2. Output Control ScreenEV2011V SR1threshold.Please note that the ap-dependent,and may take some time after the application of a charging current or a discharge load depending on the PFC and scale selected,and the rate of charge or discharge being applied.VSR Step This is the value of the V SR current step as defined in the bq2011data sheet.GG StepThis is the lower four bits of the TMPGG register that correspond to the current NAC value relative to either the LMD or the original programmed full count (as determined by PROG 1-4).The GG step is reported as a step number from 0to 15,with step 0available capac-ity from 0to offull,and 15represent-ing available from full to full.Charge RateIndicates whether the present charge is TRICKLE or FAST depending on thestate of the charge rate (CR)bit in FLGS2.EDVThis is the state of the EDV flag.The EDV flag latches ON if V SB drops below the EDV threshold value.It remains latched until charging is detected,at which time it is cleared.Battery RemovedThis is the state of the battery removed flag.It is set (BRM =yes)if one of the conditions indicating battery removed oc-curs.This flag is reset when the battery is replaced.ValidDischargeThis is the state of the VDQ bit in FLGS1.VDQ =yes if the bq2011is charged until NAC =LMD.VDQ =no indi-cates the present discharge is not valid for LMD update.Full CountThis value is the contents of the Full Count register.This value times 16is the5EV2011Benchmarq BQ2011Evaluation Board Real-Time Monitor ScreenTime:99:99:99EMPTY ****_____FULL Date:99/99/99NAC:99999mAHLMD:99999mAHSense Resistor Value:XXX ΩAvg Vsr Current:±9999mATime remaining:9999min.Digital Filter Setting:+0.50mV=Vsrd -0.40mV=Vsrq Temp Step:XX Activity:XXXXX Vsr Current Step:XX GG Step:XX Charge Rate:XXXX First EDV:XXX Batt.Rem'vd:XXX Valid Discharge:XXXFull Count:XXXBatt.Repl'd:XXXCapacity Inaccurate:XXX Capacity Inaccurate Count:XXXFLGS1:XX X X X _X _FLGS2:X X X X___X C B B C V N E N C D D D N N N O H R R I D /D /R R R R ///V G PM Q U VU210U U U L S1DESC to main menu F1to modify NAC F2to modify LMDFigure 3. Real-Time Monitor ScreenRev.C Boardnumber of times that NAC has counted up to LMD after a valid discharge.Battery Replaced This is the state of the battery replaced flag.It is set(BRP=yes)if the battery valid condition returns after setting the battery removed flag.The battery re-placed flag is cleared if the battery is dis-charged to the EDV1level or if it is charged to NAC=LMD.This flag is set after a EV2011initialization.Capacity Inaccurate This is the state of the capacity inaccu-rate bit in FLGS1.It is set(CI=yes)to indicate that the battery capacity has not been updated during the last64charge cycles.Capacity Inaccurate Count This is the number of charge cycles be-tween an LMD update.This counter is reset to zero when NAC=LMD after a valid LMD update.FLGS1This indicates the present state of theFLGS1resistor.FLGS2This indicates the present state of theFLGS2resistor.Modifying NAC and LMDIt is possible to change the values of the NAC and LMD parameters from the screen using the F1and F2func-tion keys as follows.Changing NAC(F1)1)Press the F1 key.The NAC field is highlighted.2)Enter the value in mAH and press the ENTERkey to store the value.Note:Changing NAC disqualifies a subsequent LMD update.Changing LMD(F2)1)Press the F2 key.The LMD field is highlighted.2)Enter the value in mAH and press the ENTERkey to store the value.Display Program ScreenThis menu is accessed by selecting the<Display Pro-gram>function on the Main Menu.The Display Pro-gram Screen represents the state of the bq2011 programming pins;see Figure4.To change the bq2011 programming,reconfigure jumpers MODE and PFC and 6Rev.C BoardBenchmarq BQ2011Programming ScreenSense Resistor:0.005ΩScale Factor:1/80Display Full:RELATIVE PFC Count:XXXXPFC(mVH):XXXX mVHSelf-Discharge Battery Capacity:9999mAHRate:1/64NAC/dayProgramming Pin ConfigurationLED Drive***PFC***ESC to main menu F3for HelpFigure 4. Programming MenuEV2011initialize the bq2011.The reset allows the bq2011to read the program pins.Sense Resistor Enter the value of sense resistor in ohms. Typical values range from0.001to 0.005Ω.The sense resistor value is used by the EV2011UIP to develop meaningful infor-mation in terms of A,mA,and mAH in re-lation to battery capacity and current. The default value is0.005.Values from 0.001to0.256are saved in the battery ID RAM byte of the bq2011.Values greater than0.256must be re-entered each time EV2011is started.Scale Factor Select the scale factor from the available scales using JP11.Like the sense resistor,the scale factor is used to develop meaningful information for the programmed full count tables,battery full,and available capacity indications.Display Full Use JP10to choose between RELATIVE and ABSOLUTE full reference for the LED display.PFC Select the programmed full count usingJP11.Note that the selected PFC and thesense resistor value are used to determinethe initial battery full capacity(mAh)rep-resented by the PFC.Battery Capacity This display indicates the battery capac-ity represented by dividing the PFC by the sense resistor.In practice,picking a PFC and sense resistor that provide a battery full value slightly lower than (within5%)the rated battery capacity is recommended.Program-ming Pin Configura-tion This indicates the display mode as either LED DRIVE by MODE or V CC.The PFC pin state is shown as L,Z,H.Please refer to the bq2011data sheet for more infor-mation.Data LoggingThe data log is activated from the Main Menu by select-ing the Data Log function.A filename to be used and the log sample period must be entered.For example: Log Data to Filename:<filename.ext>Enter Sample Period(10sec or greater):<xx>Opening Data Log FileWhen the data log is started,the Monitor Screen dis-plays the number of the current log record between thetime and date fields at the top of the screen.To termi-nate the data log,press the ESCAPE key.The file is closed and data logging is terminated.The data log record contains fields of ASCII data sepa-rated by tab characters.The field names and descrip-tions in record order follow.TIME Time record written in secondsLMD LMD value in mAHNAC NAC value in mAHAvg.DischargeCurrentAverage V SR battery currentFLAGS1Binary setting of FLAGS1flags:Bit Meaning0Not used1EDV flag state2Not used3VDQ (valid discharge)4Capacity inaccurate5Battery removed flag state6Battery replaced flag state7Charge active flag stateFLAGS2Binary setting of FLAGS2flags:Bit Meaning0Overload flag state1–3Not used4–6Discharge rate7Charge rateThe log records should be readable by most spreadsheet programs.7EV2011Rev.C BoardMeasure V OS ScreenThis screen is used to measure the V OS of the bq2011; see Figure5.A minimum of120seconds are required to perform this test.Pressing the ESC key terminates thetest in progress.Operating the test for a longer period increases the resolution of the test.A“beep”signals test completion.8Benchmarq EV2011Evaluation Board VO SMeasurementPresent DMF Setting+0.50mV=Vsrd-0.40mV=VsrqCurrent Threshold(DMF(mv)/Rsns):XXXXmADo you want to test Vos?:Y/NCalculated Vos:Vos XXXmV,over last xxxx secondsElapsed time:XXXX seconds**Note:There must be no charge/discharge activity on the bq2011for this testto be valid.Running the test for a longer period of time increasesthe Vos measurement resolution.This test requires a minimumof2minutes before any value is displayed.ESC to main menuFigure 5. VOS Measurement ScreenEV2011Rev.C BoardAppendix A:AP11 User's GuideThe AP11utility(AP11.EXE)is used to communicate with the bq2011on a register basis.AP11uses a driver to communicate with the EV2011over serial port on a PC-AT personal computer.AP11The AP11utility is started by executing AP11.EXE.After AP11is started,the following prompt is displayed: Select COM Port<1234>CommandsThe user can respond with various commands at the prompt.Pressing“Q”causes the program to terminate.–>?Pressing the?key displays following menu:These commands may be used to send or receive data from the EV2011.–>AIf A is entered in response to–>,then a break bit is sent to the EV2011.This may be used to restart the commu-nication if a problem appears.If the prompt does not re-turn immediately,then proper communication has not been established;please refer to Appendix B for trouble-shooting procedures.–>R#If R#is entered in response to–>,where#is an applica-ble address in HEX format,AP11returns the value at that location from the EV2011.The addresses are de-fined in the bq2011data sheet.For example:–>R03causes the display to show:R03=##where##is the current NAC value in HEX format.Address00is used to read and display all readable reg-isters.–>S#If S#is entered in response to–>,where#is a valid bq2011address in HEX format,AP11continuously reads and displays the value at that location.The ad-dressed are defined in the bq2011data sheet.For exam-ple:–>S03causes the display to show:Address3=##after XXX.XX sec.where##is the value at location03and XXX.XX isthe number of seconds between changes in thisvalue.–>W#=**If W#=**is entered in response to–>,where#is an ap-plicable address in HEX format and**is the value to be written,AP11writes the value to that location.The ad-dresses are defined in the bq2011data sheet.For exam-ple:–>W05=A0causes the program to write A0in location05hex(LMD register).9EV2011Rev.C BoardThe following commands are available:?This display is shown.A Send break.Q Quit and return to DOS.R#Read at address#.S#Scan at address#.W#=**Write at address#value**.Appendix B:Troubleshooting If the EV2011Main Menu does not appear after starting EV2011,then communication to the bq2011has not been established.Please check the following:1.Confirm the proper serial port is being used.2.Confirm the battery divider is properly set for thenumber of cells in the battery pack.3.Confirm JP9is properly set for either an externalsupply through LBAT+(J1)or the microregulator.JP9on B enables the microregulator,while JP9on L enables LBAT+.If the battery divider on JP1–JP8is not set properly,the bq2011will not op-erate,and the EV2011UIP or AP11will not work.4.Confirm the battery is attached between BAT+andBAT–(J1and J2).5.Push S1.SEG1LED should be on indicating thatthe bq2011is properly powered.6.If the LED is not on,check the battery voltage onpin16of the bq2011to determine if it is above3Vbut below6.5V.7.If the LED is on,and the EV2011Main Menu stilldoes not appear,try using AP11to establish com-munication.Appendix A describes AP11.8.If communication cannot be established usingAP11,the problem is either the RS-232port in thePC or the EV2011interface section.Please contactBenchmarq if the interface section is not workingproperly on the EV2011board.10Rev.C Board EV2011分销商库存信息: TIEV2011。

MAC4DLMT4G;MAC4DLM-1G;MAC4DLM-001;中文规格书,Datasheet资料

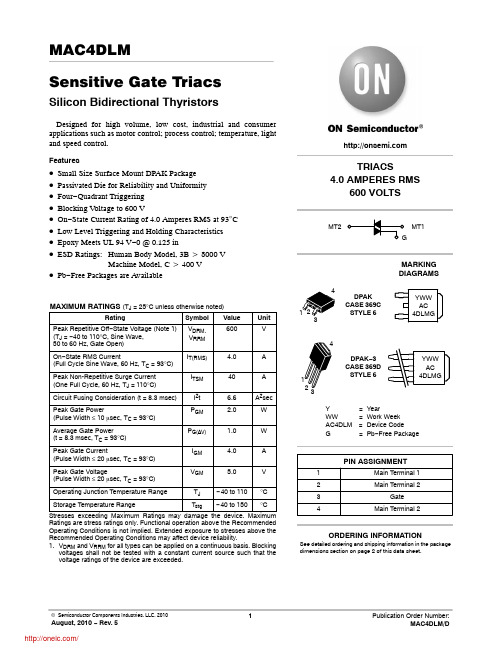

MAC4DLMSensitive Gate TriacsSilicon Bidirectional ThyristorsDesigned for high volume, low cost, industrial and consumer applications such as motor control; process control; temperature, light and speed control.Features•Small Size Surface Mount DPAK Package •Passivated Die for Reliability and Uniformity•Four−Quadrant Triggering•Blocking V oltage to 600 V•On−State Current Rating of 4.0 Amperes RMS at 93°C •Low Level Triggering and Holding Characteristics •Epoxy Meets UL 94 V−0 @ 0.125 in•ESD Ratings:Human Body Model, 3B u 8000 VMachine Model, C u 400 V•Pb−Free Packages are AvailableMAXIMUM RATINGS (T J = 25°C unless otherwise noted)Rating Symbol Value UnitPeak Repetitive Off−State Voltage (Note 1) (T J = −40 to 110°C, Sine Wave,50 to 60 Hz, Gate Open)V DRM,V RRM600VOn−State RMS Current(Full Cycle Sine Wave, 60 Hz, TC = 93°C)I T(RMS) 4.0APeak Non-Repetitive Surge Current(One Full Cycle, 60 Hz, T J = 110°C)I TSM40A Circuit Fusing Consideration (t = 8.3 msec)I2t 6.6A2secPeak Gate Power(Pulse Width ≤ 10 m sec, T C= 93°C)P GM 2.0WAverage Gate Power(t = 8.3 msec, T C = 93°C)P G(AV) 1.0W Peak Gate Current(Pulse Width ≤ 20m sec, T C = 93°C)I GM 4.0APeak Gate Voltage(Pulse Width ≤ 20m sec, T C = 93°C)V GM 5.0V Operating Junction Temperature Range TJ−40 to 110°C Storage Temperature Range T stg−40 to 150°C Stresses exceeding Maximum Ratings may damage the device. MaximumRatings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.V DRM and V RRM for all types can be applied on a continuous basis. Blockingvoltages shall not be tested with a constant current source such that the voltage ratings of the device are exceeded.TRIACS4.0 AMPERES RMS600 VOLTSPIN ASSIGNMENT123GateMain Terminal 1Main Terminal 24Main Terminal 2MT1MT2See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATIONDPAK−3CASE 369DSTYLE 6DPAKCASE 369CSTYLE 6MARKINGDIAGRAMSY= YearWW= Work WeekAC4DLM= Device CodeG=Pb−Free PackageYWWAC4DLMGTHERMAL CHARACTERISTICSCharacteristic Symbol Max UnitThermal Resistance− Junction−to−Case− Junction−to−Ambient− Junction−to−Ambient (Note 2)R q JCR q JAR q JA3.58880°C/WMaximum Lead Temperature for Soldering Purposes (Note 3)T L260°C ELECTRICAL CHARACTERISTICS (T J = 25°C unless otherwise noted; Electricals apply in both directions)Characteristic Symbol Min Typ Max Unit OFF CHARACTERISTICSPeak Repetitive Blocking Current(V D = Rated V DRM, V RRM; Gate Open)T J = 25°CT J = 110°C I DRM,I RRM−−−−0.012.0mAON CHARACTERISTICSPeak On−State Voltage (Note 4) − (I TM = ± 6.0 A)V TM− 1.3 1.6VGate Trigger Current (Continuous dc) (V D = 12 V, R L = 100 W) MT2(+), G(+)MT2(+), G(−)MT2(−), G(−)MT2(−), G(+)I GT−−−−1.82.12.44.23.03.03.05.0mAGate Trigger Voltage (Continuous dc) (V D = 12 V, R L = 100 W) MT2(+), G(+)MT2(+), G(−)MT2(−), G(−)MT2(−), G(+)V GT0.50.50.50.50.620.570.650.741.31.31.31.3VGate Non−Trigger Voltage(V D = 12 V, R L = 100 W, T J = 110°C)MT2(+), G(+); MT2(+), G(−); MT2(−), G(−); MT2(−), G(+)V GD0.10.4−VHolding Current(V D = 12 V, Gate Open, Initiating Current = ± 200 mA)I H− 1.515mALatching CurrentMT2(+), G(+)(V D = 12 V, I G = 5.0 mA) MT2(+), G(−)(V D = 12 V, I G = 5.0 mA) MT2(−), G(−)(V D = 12 V, I G = 5.0 mA) MT2(−), G(+)(V D = 12 V, I G = 10 mA)I L−−−−1.755.22.12.210101010mADYNAMIC CHARACTERISTICSRate of Change of Commutating Current(V D = 200 V, I TM = 1.8 A, Commutating dv/dt = 1.0 V/m sec,T J = 110°C, f = 250 Hz, CL = 5.0 m fd, LL = 80 mH, RS = 56 W, CS = 0.03 m fd) With snubber see Figure 11di/dt(c)− 3.0−A/msCritical Rate of Rise of Off−State Voltage(V D = 0.67 X Rated V DRM, Exponential Waveform, Gate Open, T J = 110°C)dv/dt10−−V/m s2.These ratings are applicable when surface mounted on the minimum pad sizes recommended.3.1/8″ from case for 10 seconds.4.Pulse Test: Pulse Width ≤ 2.0 msec, Duty Cycle ≤ 2%.ORDERING INFORMATIONDevice Package Type Package Shipping†MAC4DLM−001DPAK−3369D75 Units / RailMAC4DLM−001G DPAK−3(Pb−Free)369D75 Units / RailMAC4DLMT4DPAK369C2500 / Tape & ReelMAC4DLMT4G DPAK(Pb−Free)369C2500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.+ CurrentSymbolParameterV DRM Peak Repetitive Forward Off −State Voltage I DRM Peak Forward Blocking CurrentV RRM Peak Repetitive Reverse Off −State Voltage I RRM Peak Reverse Blocking Current Voltage Current Characteristic of Triacs(Bidirectional Device)V TM Maximum On −State Voltage I HHolding CurrentQuadrant Definitions for a TriacAll polarities are referenced to MT1.With in −phase signals (using standard AC lines) quadrants I and III are used.Figure 1. RMS Current Derating Figure 2. On −State Power DissipationFigure 3. On −State Characteristics Figure 4. Transient Thermal ResponseFigure 5. Typical Gate Trigger Current versusJunction Temperature Figure 6. Typical Gate Trigger Voltage versusJunction Temperature2.54.0I T(RMS), RMS ON-STATE CURRENT (AMPS)110105100I T(RMS), RMS ON-STATE CURRENT (AMPS)4.02.01.004.0V T , INSTANTANEOUS ON-STATE VOLTAGE (VOLTS)100101.00.1t, TIME (ms)1.00.11.00.10.013.5-2520-40T J , JUNCTION TEMPERATURE (°C)8.03.02.00T J , JUNCTION TEMPERATURE (°C)-2565-400.80.60.2205.0T C , M A X I M U M A L L O W A B L E C A S E T E M P E R A T U R E ( C )P I r (t ), T R A N S I E N T R E S I S T A N C E (N O R M A L I Z E D )95900.51.01.52.03.03.53.05.06.01.00.53.010100100010 K, G A T E T R I G G E R C U R R E N T (m A )I G T 50110654.05.011035500.4V G T , G A T E T R I G G E R V O L T A G E (V O L T S )°, A V E R A G E P O W E R D I S S I P A T I O N (W A T T S )(A V ), I N S T A N T A N E O U S O N -S T A T E C U R R E N T (A M P S )T 805.0Q3Q2Q11.0 1.02.52.01.5-1035956.07.0Q4-109580Figure 7. Typical Holding Current versusJunction TemperatureFigure 8. Typical Latching Current versusJunction TemperatureFigure 9. Minimum Exponential Static dv/dtversus Gate −MT1 Resistance 65110-40T J , JUNCTION TEMPERATURE (°C)2.0T J , JUNCTION TEMPERATURE (°C)4.02.00100010 K100R GK , GATE-MT1 RESISTANCE (OHMS)4015105.0I H , H O L D I N G C U R R E N T (m A )I S T A T I C d v /d t (V / s )1.00-255.02050958.01012, L A T C H I N G C U R R E N T (m A )L 4.03.05.0m 6.0-103580Figure 10. Critical Rate of Rise ofCommutating Voltage1.0di/dt(c), RATE OF CHANGE OF COMMUTATING CURRENT (A/ms)101.00.1C O M MU T A T I N G V O L T A G E (V / s )m 2.03.0d v /d t (c ), C R I T I C A L R A T E O F R I S E O F 4.05.06.020253035Figure 11. Simplified Test Circuit to Measure the Critical Rate of Rise of Commutating Current (di/dt)c200 VI TM Note: Component values are for verification of rated (di/dt)c . See AN1048 for additional information.DPAK CASE 369C ISSUE OVSUDIM MIN MAX MIN MAXMILLIMETERSINCHESA0.2350.245 5.97 6.22B0.2500.265 6.35 6.73C0.0860.094 2.19 2.38D0.0270.0350.690.88E0.0180.0230.460.58F0.0370.0450.94 1.14G0.180 BSC 4.58 BSCH0.0340.0400.87 1.01J0.0180.0230.460.58K0.1020.114 2.60 2.89L0.090 BSC 2.29 BSCR0.1800.215 4.57 5.45S0.0250.0400.63 1.01U0.020−−−0.51−−−V0.0350.0500.89 1.27Z0.155−−− 3.93−−−NOTES:1.DIMENSIONING AND TOLERANCINGPER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.ǒmminchesǓSCALE 3:1STYLE 6:PIN 1.MT12.MT23.GATE4.MT2*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DPAK −3CASE 369D −01ISSUE BEDIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.2350.245 5.97 6.35B 0.2500.265 6.35 6.73C 0.0860.094 2.19 2.38D 0.0270.0350.690.88E 0.0180.0230.460.58F 0.0370.0450.94 1.14G 0.090 BSC 2.29 BSC H 0.0340.0400.87 1.01J 0.0180.0230.460.58K 0.3500.3808.899.65R 0.1800.215 4.45 5.45S 0.0250.0400.63 1.01V 0.0350.0500.89 1.27NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.Z0.155−−−3.93−−−STYLE 6:PIN 1.MT12.MT23.GATE 4.MT2ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION分销商库存信息:ONSEMIMAC4DLMT4G MAC4DLM-1G MAC4DLM-001。

PUMH20,115;中文规格书,Datasheet资料