74AUP1G11GW中文资料

74系列芯片数据手册大全

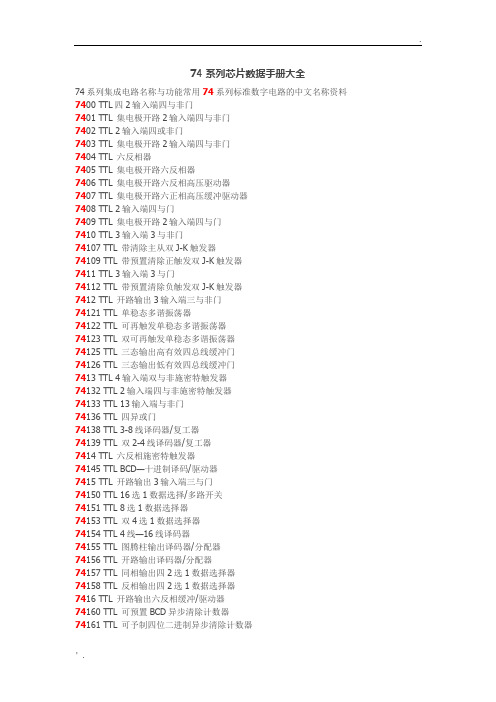

74系列芯片数据手册大全【强烈推荐】74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D 触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D 锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K 触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器113 双下降沿J-K触发器114 双下降沿J-K触发器116 双4位锁存器120 双脉冲同步驱动器121 单稳态触发器122 可重触发单稳态触发器123 可重触发双稳态触发器125 四总线缓冲器126 四总线缓冲器128 四2输入端或非线驱动器132 四2输入端与非门。

SN74AUP1G98DRLR,SN74AUP1G98DRLR,SN74AUP1G98DRLR,SN74AUP1G98DCKR, 规格书,Datasheet 资料

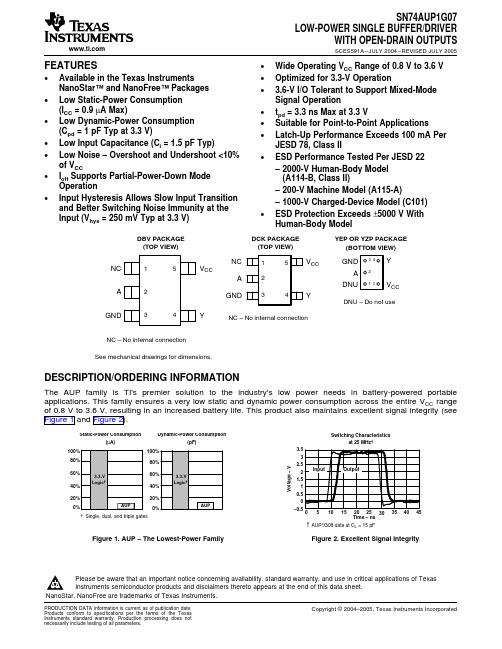

DBV PACKAGE(TOPVIEW)DCK PACKAGE(TOPVIEW)DRL PACKAGE(TOP VIEW)DRY PACKAGE(TOP VIEW)GND VCCB65423A YC1A Y34GND25B61VCCCDSF PACKAGE(TOP VIEW)YFP PACKAGE(VIEW)TOPABYCGND VCCYZP PACKAGE(TOP VIEW)ABYVCCGNDCSN74AUP1G98 SCES506H–NOVEMBER2003–REVISED MAY2010 LOW-POWER CONFIGURABLE MULTIPLE-FUNCTION GATECheck for Samples:SN74AUP1G98FEATURES•Available in the Texas Instruments NanoStar™•Wide Operating V CC Range of0.8V to3.6V Package•Optimized for3.3-V Operation•Low Static-Power Consumption• 3.6-V I/O Tolerant to Support Mixed-Mode(I CC=0.9m A Max)Signal Operation•Low Dynamic-Power Consumption•tpd=5.3ns Max at3.3V(C pd=4.6pF Typ at3.3V)•Suitable for Point-to-Point Applications•Low Input Capacitance(C i=1.5pF Typ)•Latch-Up Performance Exceeds100mA Per •Low Noise–Overshoot and Undershoot JESD78,Class II<10%of V CC•ESD Performance Tested Per JESD22•I off Supports Partial-Power-Down Mode–2000-V Human-Body Model Operation(A114-B,Class II)•Includes Schmitt-Trigger Inputs–1000-V Charged-Device Model(C101)See mechanical drawings for dimensions.DESCRIPTION/ORDERING INFORMATIONThe AUP family is TI's premier solution to the industry's low-power needs in battery-powered portable applications.This family ensures a very low static-and dynamic-power consumption across the entire V CC range of0.8V to3.6V,resulting in increased battery life(see Figure1).This product also maintains excellent signal integrity(see the very low undershoot and overshoot characteristics shown in Figure2).The SN74AUP1G98features configurable multiple functions.The output state is determined by eight patterns of 3-bit input.The user can choose the logic functions MUX,AND,OR,NAND,NOR,inverter,and noninverter.All inputs can be connected to V CC or GND.The device functions as an independent gate with Schmitt-trigger inputs,which allow for slow input transition and better switching-noise immunity at the input.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2003–2010,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.Static-Power Consumption(µA)Dynamic-Power Consumption(pF)†Single, dual, and triple gatesTime − nsV o l t a g e − V†AUP1G08 data at C L= 15 pF Switching CharacteristicsSN74AUP1G98SCES506H –NOVEMBER 2003–REVISED MAY 2010Figure 1.AUP –The Lowest-Power Family Figure 2.Excellent Signal IntegrityNanoStar™package technology is a major breakthrough in IC packaging concepts,using the die as thepackage.This device is fully specified for partial-power-down applications using I off .The I off circuitry disables the outputs,preventing damaging current backflow through the device when it is powered down.ORDERING INFORMATION (1)ORDERABLE TOP-SIDE T APACKAGE (2)PART NUMBER MARKING (3)NanoStar –WCSP (DSBGA)Reel of 3000SN74AUP1G98YFPR ___H R _0.23-mm Large Bump –YFP (Pb-free)NanoStar –WCSP (DSBGA)Reel of 3000SN74AUP1G98YZPR ___H R _0.23-mm Large Bump –YZP (Pb-free)QFN –DRY Reel of 5000SN74AUP1G98DRYR HR –40°C to 85°CuQFN –DSF Reel of 5000SN74AUP1G98DSFR HR SOT (SOT-23)–DBV Reel of 3000SN74AUP1G98DBVR H98_SOT (SC-70)–DCK Reel of 3000SN74AUP1G98DCKR HR_SOT (SOT-553)–DRLReel of 4000SN74AUP1G98DRLR(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI web site at .(2)Package drawings,thermal data,and symbolization are available at /packaging .(3)DBV/DCK/DRL:The actual top-side marking has one additional character that designates the wafer fab/assembly site.YFP/YZP:The actual top-side marking has three preceding characters to denote year,month,and sequence code,and one following character to designate the wafer fab/assembly site.Pin 1identifier indicates solder-bump composition (1=SnPb,●=Pb-free).FUNCTION TABLEINPUTSOUTPUTYC B A L L L H L L H H L H L L L H H L H L L H H L H L H H L H HHHL2Submit Documentation FeedbackCopyright ©2003–2010,Texas Instruments IncorporatedProduct Folder Link(s):SN74AUP1G98CBAY123654BY CV CCYAGND C YASN74AUP1G98SCES506H –NOVEMBER 2003–REVISED MAY 2010LOGIC DIAGRAM (POSITIVE LOGIC)Table 1.FUNCTION SELECTION TABLELOGIC FUNCTIONFIGURE NO.2-to-1data selector with inverted output Figure 32-input NAND gateFigure 42-input NOR gate with one inverted input Figure 52-input AND gate with one inverted input Figure 52-input NAND gate with one inverted input Figure 62-input OR gate with one inverted input Figure 62-input NOR gate Figure 7Noninverted buffer Figure 8InverterFigure 9LOGIC CONFIGURATIONSFigure 3.2-to-1Data Selector With Inverted OutputWhen C is L,Y =B When C is H,Y =Figure 4.2-Input NAND GateCopyright ©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):SN74AUP1G98CYAC YAYC YBGNDC YBYC GNDSN74AUP1G98SCES506H –NOVEMBER 2003–REVISED MAY 2010Figure 5.2-Input NOR Gate With One Inverted Input2-Input AND Gate With One Inverted InputFigure 6.2-Input NAND Gate With One Inverted Input2-Input OR Gate With One Inverted InputFigure 7.2-Input NOR GateFigure 8.Noninverted Buffer4Submit Documentation FeedbackCopyright ©2003–2010,Texas Instruments IncorporatedProduct Folder Link(s):SN74AUP1G98YBGNDSN74AUP1G98 SCES506H–NOVEMBER2003–REVISED MAY2010Figure9.InverterCopyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):SN74AUP1G98SN74AUP1G98SCES506H–NOVEMBER2003–REVISED ABSOLUTE MAXIMUM RATINGS(1)over operating free-air temperature range(unless otherwise noted)MIN MAX UNITV CC Supply voltage range–0.5 4.6VV I Input voltage range(2)–0.5 4.6VV O Voltage range applied to any output in the high-impedance or power-off state(2)–0.5 4.6VV O Output voltage range in the high or low state(2)–0.5V CC+0.5VI IK Input clamp current V I<0–50mAI OK Output clamp current V O<0–50mAI O Continuous output current±20mAContinuous current through V CC or GND±50mADBV package165DCK package259DRL package142q JA Package thermal impedance(3)°C/WDSF package300DRY package234YFP/YZP package123T stg Storage temperature range–65.°C(1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.(3)The package thermal impedance is calculated in accordance with JESD51-7.RECOMMENDED OPERATING CONDITIONS(1)MIN MAX UNIT V CC Supply voltage0.8 3.6VV I Input voltage0 3.6VV O Output voltage0V CC VV CC=0.8V–20AV CC=1.1V–1.1V CC=1.4V–1.7I OH High-level output currentV CC=1.65–1.9mAV CC=2.3V–3.1V CC=3V–4V CC=0.8V20m AV CC=1.1V 1.1V CC=1.4V 1.7I OL Low-level output currentV CC=1.65V 1.9mAV CC=2.3V 3.1V CC=3V4T A Operating free-air temperature–4085°C(1)All unused inputs of the device must be held at V CC or GND to ensure proper device operation.Refer to the TI application report,Implications of Slow or Floating CMOS Inputs,literature number SCBA004.6Submit Documentation Feedback Copyright©2003–2010,Texas Instruments IncorporatedProduct Folder Link(s):SN74AUP1G98SN74AUP1G98 SCES506H–NOVEMBER2003–REVISED MAY2010ELECTRICAL CHARACTERISTICSover recommended operating free-air temperature range(unless otherwise noted)T A=25°C T A=–40°C to85°C PARAMETER TEST CONDITIONS V CC UNITMIN TYP MAX MIN MAXV T+0.8V0.30.60.30.61.1V0.530.90.530.91.4V0.74 1.110.74 1.11Positive-going V input threshold 1.65V0.91 1.290.91 1.29voltage 2.3V 1.37 1.77 1.37 1.773V 1.88 2.29 1.88 2.29V T–0.8V0.10.60.10.61.1V0.260.650.260.651.4V0.390.750.390.75Negative-going V input threshold 1.65V0.470.840.470.84voltage 2.3V0.69 1.040.69 1.043V0.88 1.240.88 1.24ΔV T0.8V0.070.50.070.51.1V0.080.460.080.461.4V0.180.560.180.56V Hysteresis1.65V0.270.660.270.66(V T+–V T–)2.3V0.530.920.530.923V0.79 1.310.79 1.31I OH=–20m A0.8V to3.6V V CC–0.1V CC–0.1I OH=–1.1mA 1.1V0.75×V CC0.7×V CCI OH=–1.7mA 1.4V 1.11 1.03I OH=–1.9mA 1.65V 1.32 1.3V OH VI OH=–2.3mA 2.05 1.972.3VI OH=–3.1mA 1.9 1.85I OH=–2.7mA 2.72 2.673VI OH=–4mA 2.6 2.55I OL=20m A0.8V to3.6V0.10.1I OL=1.1mA 1.1V0.3×V CC0.3×V CCI OL=1.7mA 1.4V0.310.37I OL=1.9mA 1.65V0.310.35V OL VI OL=2.3mA0.310.332.3VI OL=3.1mA0.440.45I OL=2.7mA0.310.333VI OL=4mA0.440.45I I All inputs V I=GND to3.6V0V to3.6V0.10.5m AI off V I or V O=0V to3.6V0V0.20.6m AΔI off V I or V O=0V to3.6V0V to0.2V0.20.6m AV I=GND or(V CC to3.6V),I CC0.8V to3.6V0.50.9m AI O=0ΔI CC V I=V CC–0.6V(1),I O=0 3.3V4050m A0V 1.5C i V I=V CC or GND pF3.6V 1.5C o V O=GND0V3pF(1)One input at V CC–0.6V,other inputs at V CC or GND.Copyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):SN74AUP1G98SN74AUP1G98SCES506H–NOVEMBER2003–REVISED SWITCHING CHARACTERISTICSover recommended operating free-air temperature range,C L=5pF(unless otherwise noted)(see Figure10and Figure11)T A=–40°CT A=25°CFROM TO to85°C PARAMETER V CC UNIT (INPUT)(OUTPUT)MIN TYP MAX MIN MAX0.8V22.21.2V±0.1V2.79.113.6 2.2171.5V±0.1V2 6.49.2 1.511.1t pd A,B,or C Y ns1.8V±0.15V 1.4 5.27.20.98.92.5V±0.2V 1.23.8 5.30.7 6.33.3V±0.3V1 3.14.50.55.3 SWITCHING CHARACTERISTICSover recommended operating free-air temperature range,C L=10pF(unless otherwise noted)(see Figure10and Figure11)T A=–40°CT A=25°CFROM TO to85°C PARAMETER V CC UNIT (INPUT)(OUTPUT)MIN TYP MAX MIN MAX0.8V25.41.2V±0.1V 5.210.415.4 4.7191.5V±0.1V47.410.5 3.512.6t pd A,B,or C Y ns1.8V±0.15V 3.168.32.610.22.5V±0.2V 2.7 4.5 6.1 2.27.33.3V±0.3V 2.5 3.7526 SWITCHING CHARACTERISTICSover recommended operating free-air temperature range,C L=15pF(unless otherwise noted)(see Figure10and Figure11)T A=–40°CT A=25°CFROM TO to85°C PARAMETER V CC UNIT (INPUT)(OUTPUT)MIN TYP MAX MIN MAX0.8V28.71.2V±0.1V 3.711.517 3.221.11.5V±0.1V2.88.311.6 2.314t pd A,B,or C Y ns1.8V±0.15V2.1 6.79.2 1.611.32.5V±0.2V 1.85 6.7 1.38.13.3V±0.3V 1.64.15.5 1.16.6 SWITCHING CHARACTERISTICSover recommended operating free-air temperature range,C L=30pF(unless otherwise noted)(see Figure10and Figure11)T A=–40°CT A=25°CFROM TO to85°C PARAMETER V CC UNIT (INPUT)(OUTPUT)MIN TYP MAX MIN MAX0.8V39.71.2V±0.1V 5.115.321.6 4.626.81.5V±0.1V 3.910.914.6 3.417.6t pd A,B,or C Y ns1.8V±0.15V 3.18.911.52.614.12.5V±0.2V 2.6 6.78.4 2.110.13.3V±0.3V 2.3 5.5 6.9 1.88.38Submit Documentation Feedback Copyright©2003–2010,Texas Instruments IncorporatedProduct Folder Link(s):SN74AUP1G98SN74AUP1G98 SCES506H–NOVEMBER2003–REVISED MAY2010OPERATING CHARACTERISTICST A=25°CPARAMETER TEST CONDITIONS V CC TYP UNIT0.8V41.2V±0.1V41.5V±0.1V4C pd Power dissipation capacitance f=10MHz pF1.8V±0.15V42.5V±0.2V 4.33.3V±0.3V4.6Copyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):SN74AUP1G98From Output Under TestLOAD CIRCUIT1 M ΩVOLTAGE WAVEFORMS PROPAGATION DELAY TIMESINVERTING AND NONINVERTING OUTPUTSV OHV OHV OLV OLV I0 VInputOutputOutputNOTES: A.C L includes probe and jig capacitance.B.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z O = 50 Ω, slew rate ≥ 1 V/ns.C.The outputs are measured one at a time, with one transition per measurement.D.t PLH and t PHL are the same as t pd .E.All parameters and waveforms are not applicable to all devices.5, 10, 15, 30 pFV CC /2V CCV CC = 1.2 V ± 0.1 V V CC= 0.8 VVCC = 1.5 V ± 0.1 V V CC = 1.8 V ± 0.15 V V CC = 2.5 V ± 0.2 V V CC = 3.3 V ± 0.3 V 5, 10, 15, 30 pFV CC /2V CC5, 10, 15, 30 pFV CC /2V CC5, 10, 15, 30 pFV CC /2V CCC L V M V I5, 10, 15, 30 pFV CC /2V CC5, 10, 15, 30 pFV CC /2V CCData InputTiming InputV CC0 VV CC0 V0 VInputVOLTAGE WAVEFORMS SETUP AND HOLD TIMESVOLTAGE WAVEFORMS PULSE DURATIONV CCSN74AUP1G98SCES506H –NOVEMBER 2003–REVISED MAY 2010PARAMETER MEASUREMENT INFORMATION(Propagation Delays,Setup and Hold Times,and Pulse Duration)Figure 10.Load Circuit and Voltage Waveforms10Submit Documentation FeedbackCopyright ©2003–2010,Texas Instruments IncorporatedProduct Folder Link(s):SN74AUP1G98NOTES: A.C L includes probe and jig capacitance.B.Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control.Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.C.All input pulses are supplied by generators having the following characteristics: PRR ≤ 10 MHz, Z O = 50 Ω, slew rate ≥ 1 V/ns.D.The outputs are measured one at a time, with one transition per measurement.E.t PLZ and t PHZ are the same as t dis .F.t PZL and t PZH are the same as t en .G.All parameters and waveforms are not applicable to all devices.5, 10, 15, 30 pFV CC /2V CC 0.15 VV CC = 1.2 V ± 0.1 V V CC = 0.8 VV CC = 1.5 V ± 0.1 V V CC = 1.8 V ± 0.15 V V CC = 2.5 V ± 0.2 V V CC = 3.3 V ± 0.3 V 5, 10, 15, 30 pFV CC /2V CC 0.1 V5, 10, 15, 30 pFV CC /2V CC 0.1 V5, 10, 15, 30 pFV CC /2V CC 0.1 VC L V M V I V ∆5, 10, 15, 30 pFV CC /2V CC 0.15 V5, 10, 15, 30 pFV CC /2V CC 0.3 VOutput Waveform 1S1 at 2 × V CC (see Note B)Output Waveform 2S1 at GND (see Note B)V OLV OHV CC0 V≈0 VV CCVOLTAGE WAVEFORMS ENABLE AND DISABLE TIMES LOW- AND HIGH-LEVEL ENABLINGOutput Controlt PLZ /t PZL t PHZ /t PZH2 × V CC GNDTEST S1From Output LOAD CIRCUITGND× V CCSN74AUP1G98SCES506H –NOVEMBER 2003–REVISED MAY 2010PARAMETER MEASUREMENT INFORMATION(Enable and Disable Times)Figure 11.Load Circuit and Voltage WaveformsAddendum-Page 1PACKAGING INFORMATIONOrderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball FinishMSL Peak Temp(3)Samples (Requires Login)SN74AUP1G98DBVR ACTIVE SOT-23DBV 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DBVRE4ACTIVE SOT-23DBV 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DBVRG4ACTIVE SOT-23DBV 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DBVT ACTIVE SOT-23DBV 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DBVTE4ACTIVE SOT-23DBV 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DBVTG4ACTIVE SOT-23DBV 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKR ACTIVE SC70DCK 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKRE4ACTIVE SC70DCK 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKRG4ACTIVE SC70DCK 63000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKT ACTIVE SC70DCK 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKTE4ACTIVE SC70DCK 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DCKTG4ACTIVE SC70DCK 6250Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DRLR ACTIVE SOT DRL 64000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DRLRG4ACTIVE SOT DRL 64000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DRYR ACTIVE SON DRY 65000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98DSFR ACTIVE SON DSF 65000Green (RoHS & no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AUP1G98YFPRACTIVEDSBGAYFP63000Green (RoHS & no Sb/Br)SNAGCULevel-1-260C-UNLIM芯天下--/Addendum-Page 2Orderable Device Status(1)Package Type PackageDrawingPins Package QtyEco Plan(2)Lead/Ball Finish MSL Peak Temp (3)Samples (Requires Login)SN74AUP1G98YZPRACTIVEDSBGAYZP63000Green (RoHS & no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2)Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3)MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.芯天下--/TAPE AND REEL INFORMATION*All dimensions are nominalDevicePackage Type Package Drawing Pins SPQReel Diameter (mm)Reel Width W1(mm)A0(mm)B0(mm)K0(mm)P1(mm)W (mm)Pin1Quadrant SN74AUP1G98DBVR SOT-23DBV 63000180.08.4 3.23 3.17 1.37 4.08.0Q3SN74AUP1G98DBVT SOT-23DBV 6250180.08.4 3.23 3.17 1.37 4.08.0Q3SN74AUP1G98DCKR SC70DCK 63000180.08.4 2.25 2.4 1.22 4.08.0Q3SN74AUP1G98DCKT SC70DCK 6250180.08.4 2.25 2.4 1.22 4.08.0Q3SN74AUP1G98DRLR SOT DRL 64000180.09.5 1.78 1.780.69 4.08.0Q3SN74AUP1G98DRLR SOT DRL 64000180.08.4 1.98 1.780.69 4.08.0Q3SN74AUP1G98DRYR SON DRY 65000180.09.5 1.15 1.60.75 4.08.0Q1SN74AUP1G98DSFR SON DSF 65000180.09.5 1.16 1.160.5 4.08.0Q2SN74AUP1G98YFPR DSBGA YFP 63000178.09.20.89 1.290.62 4.08.0Q1SN74AUP1G98YZPRDSBGAYZP63000180.08.41.021.520.634.08.0Q1*All dimensions are nominalDevice Package Type Package Drawing Pins SPQ Length(mm)Width(mm)Height(mm) SN74AUP1G98DBVR SOT-23DBV63000202.0201.028.0 SN74AUP1G98DBVT SOT-23DBV6250202.0201.028.0 SN74AUP1G98DCKR SC70DCK63000202.0201.028.0 SN74AUP1G98DCKT SC70DCK6250202.0201.028.0 SN74AUP1G98DRLR SOT DRL64000180.0180.030.0 SN74AUP1G98DRLR SOT DRL64000202.0201.028.0 SN74AUP1G98DRYR SON DRY65000180.0180.030.0 SN74AUP1G98DSFR SON DSF65000180.0180.030.0 SN74AUP1G98YFPR DSBGA YFP63000220.0220.035.0SN74AUP1G98YZPR DSBGA YZP63000220.0220.034.0IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

74AUP1T00低功耗2输入NAND门电压级别翻译器产品数据手册说明书

74AUP1T00Low-power 2-input NAND gate with voltage-level translatorRev. 1 — 23 November 2017Product data sheet1General descriptionThe 74AUP1T00 provides the single 2-input NAND function. This device ensures avery low static and dynamic power consumption across the entire V CC range from2.3 V to3.6 V.The 74AUP1T00 is designed for logic-level translation applications with input switchinglevels that accept 1.8 V low-voltage CMOS signals, while operating from either a single2.5 V or3.3 V supply voltage.The wide supply voltage range ensures normal operation as battery voltage drops from3.6 V to 2.3 V.This device is fully specified for partial power-down applications using I OFF. The I OFFcircuitry disables the output, preventing the damaging backflow current through thedevice when it is powered down.Schmitt trigger inputs make the circuit tolerant to slower input rise and fall times acrossthe entire V CC range.2Features and benefits•Wide supply voltage range from 2.3 V to 3.6 V•High noise immunity•ESD protection:–HBM JESD22-A114F Class 3A exceeds 5000 V–CDM JESD22-C101E exceeds 1000 V•Low static power consumption; I CC = 1.5 μA (maximum)•Latch-up performance exceeds 100 mA per JESD 78 Class II•Inputs accept voltages up to 3.6 V•Low noise overshoot and undershoot < 10 % of V CC•I OFF circuitry provides partial power-down mode operation•Multiple package options•Specified from -40 °C to +85 °C and -40 °C to +125 °CLow-power 2-input NAND gate with voltage-level translator3Ordering information4Marking[1]The pin 1 indicator is located on the lower left corner of the device, below the marking code.5Functional diagramaaa-027680Y4BA12Figure 1. Logic symbol aaa-027681412&Figure 2. IEC logic symbol aaa-027682YBAFigure 3. Logic diagram6Pinning information6.1Pinning74AUP1T00B V CCA GNDYaaa-02768412354Figure 4. Pin configuration SOT353-1BV CCGND13254AYaaa-027685Transparent top view74AUP1T00Figure 5. Pin configuration SOT1226 (X2SON5)Low-power 2-input NAND gate with voltage-level translator6.2Pin description7Functional description[1][1]H = HIGH voltage level;L = LOW voltage level.8Limiting valuesTable 5. Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).[1]The minimum input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For TSSOP5 packages: above 87.5 °C the value of P tot derates linearly with 4.0 mW/K.For X2SON5 packages: above 118 °C the value of P tot derates linearly with 7.8 mW/K.Low-power 2-input NAND gate with voltage-level translator 9Recommended operating conditions10Static characteristicsTable 7. Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Low-power 2-input NAND gate with voltage-level translatorLow-power 2-input NAND gate with voltage-level translator[1]One input at 0.3 V or 1.1 V, other input at V CC or GND.[2]One input at 0.45 V or 1.2 V, other input at V CC or GND.Low-power 2-input NAND gate with voltage-level translator 11Dynamic characteristicsTable 8. Dynamic characteristicsVoltages are referenced to GND (ground = 0 V); for test circuit see Figure 7.Low-power 2-input NAND gate with voltage-level translator[1]All typical values are measured at nominal V CC.[2]t pd is the same as t PLH and t PHL[3]C PD is used to determine the dynamic power dissipation (P D in μW).P D = C PD x V CC2 x f i x N + Σ(C L x V CC2 x f o) where:f i = input frequency in MHz;f o = output frequency in MHz;C L = output load capacitance in pF;V CC = supply voltage in V;N = number of inputs switching;Σ(C L x V CC2 x f o) = sum of the outputs.Low-power 2-input NAND gate with voltage-level translator11.1Waveforms and test circuit[1]For measuring enable and disable times R L = 5 kΩ.For measuring propagation delays, setup and hold times and pulse width R L = 1 MΩ.Low-power 2-input NAND gate with voltage-level translator 12Package outlineLow-power 2-input NAND gate with voltage-level translatorLow-power 2-input NAND gate with voltage-level translator 13Abbreviations14Revision historyLow-power 2-input NAND gate with voltage-level translator 15Legal information15.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term 'short data sheet' is explained in section "Definitions".[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multipledevices. The latest product status information is available on the Internet at URL .15.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product is deemed to offer functions and qualities beyond those described in the Product data sheet.15.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracyor completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia. In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation -lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to make changesto information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunctionof an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitable and fit for the customer’s applications and products planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer’s third party customer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above thosegiven in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperia products aresold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects to applying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance orthe grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.Low-power 2-input NAND gate with voltage-level translatorNon-automotive qualified products — Unless this data sheet expressly states that this specific Nexperia product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. Nexperia accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications. In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without Nexperia's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond Nexperia's specifications such use shall be solely at customer’s own risk, and (c) customer fully indemnifies Nexperia for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond Nexperia's standard warranty and Nexperia's product specifications.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.15.4 TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.Low-power 2-input NAND gate with voltage-level translatorPlease be aware that important notices concerning this document and the product(s)described herein, have been included in section 'Legal information'.Contents1General description ............................................12Features and benefits .........................................13Ordering information ..........................................24Marking .................................................................25Functional diagram .............................................26Pinning information ............................................26.1Pinning ...............................................................26.2Pin description ...................................................37Functional description ........................................38Limiting values ....................................................39Recommended operating conditions ................410Static characteristics ..........................................411Dynamic characteristics .....................................711.1Waveforms and test circuit ................................912Package outline .................................................1013Abbreviations ....................................................1214Revision history (1215)Legal information (13)。

74HCT1G04GW中文资料

MNA109

Fig.3 IEC logic symbol. 2002 May 17

handbook, halfpage A

Y

MNA110

Fig.4 Logic diagram. 3

Philips Semiconductors

Inverter

Product specification

74HC1G04; 74HCT1G04

−40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C

PINS

5 5 5 5

PACKAGES

PACKAGE MATERIAL

SC-88A SC-88A SC-74A SC-74A

plastic plastic plastic plastic

2

Philips Semiconductors

Inverter

Product specification

74HC1G04; 74HCT1G04

ORDERING INFORMATION

TYPE NUMBER

74HC1G04GW 74HCT1G04GW 74HC1G04GV 74HCT1G04GV

TEMPERATURE RANGE

DESCRIPTION

handbook, halfpage

n.c. 1 A2

GND 3

5 VCC

04

4Y

MNA107

Fig.1 Pin configuration.

handbook, halfpage

2A

Y4

MNA108

Fig.2 Logic symbol.

handbook, halfpage

74HCT1G00GW中文资料

74HC1G00; 74HCT1G00

The 74HC1G/HCT1G00 is a high speed Si-gate CMOS device. The 74HC1G/HCT1G00 provides the 2-input NAND function. The standard output currents are 1⁄2 compared to the 74HC/HCT00.

Product specification

2-input NAND gate

FEATURES • Wide supply voltage range from 2.0 to 6.0 V • Symmetrical output impedance • High noise immunity • Low power dissipation • Balanced propagation delays • Very small 5 pins package • Output capability: standard. QUICK REFERENCE DATA GND = 0 V; Tamb = 25 °C; tr = tf ≤ 6.0 ns. DESCRIPTION

INTEGRATED CIRCUITS

DATA SHEET

74HC1G00; 74HCT1G00 2-input NAND gate

Product specification Supersedes data of 2001 Mar 02 2002 May 15

Philips Semiconductors

74HC1G00; 74HCT1G00

74HCT1G UNIT MAX. 6.0 VCC VCC +125 MIN. 4.5 0 0 −40 TYP. 5.0 − − +25 MAX. 5.5 VCC VCC +125 V V V °C

74LVC1G11GM中文资料

元器件交易网

NXP Semiconductors

74LVC1G11

Single 3-input AND gate

8. Limiting values

Table 5. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).

© NXP B.V. 2007. All rights reserved.

2 of 14

元器件交易网

NXP Semiconductors

74LVC1G11

Single 3-input AND gate

6. Pinning information

6.1 Pinning

74LVC1G11

A1

6C

GND 2

5 VCC

B3

4Y

001aac032

Fig 4. Pin configuration SOT363 and SOT457

74LVC1G11

A1

6C

GND 2

5 VCC

B3

4Y

001aac849 Transparent top view

Fig 5. Pin configuration SOT886

Symbol Parameter

Conditions

Min

Max

Unit

VCC

supply voltage

IIK

input clamping current

VI

input voltage

SN74AUP1G07DBVT中文资料

FUNCTION TABLE

INPUT A

H

L

OUTPUT Y

H

L

LOGIC DIAGRAM (POSITIVE LOGIC)

A2

4Y

2

元器件交易网

Absolute Maximum Ratings(1)

over operating free-air temperature range (unless otherwise noted)

SOT (SOT-23) – DBV

Reel of 3000

ORDERABLE PART NUMBER SN74AUP1G07YEPR

SN74AUP1G07YZPR

Reel of 3000 Reel of 250

SN74AUP1G07DBVR SN74AUP1G07DBVT

SOT (SC-70) – DCK

元器件交易网

74AUP1G74GT,115,74AUP1G74GT,115,74AUP1G74GD,125,74AUP1G74GN,115, 规格书,Datasheet 资料

Low-power D-type flip-flop with set and reset; positive-edge trigger

Rev. 7 — 22 May 2012 Product data sheet

1. General description

The 74AUP1G74 provides a low-power, low-voltage single positive-edge triggered D-type flip-flop with individual data (D), clock (CP), set (SD) and reset (RD) inputs and complementary Q and Q outputs. The SD and RD are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The D input must be stable one set-up time prior to the LOW-to-HIGH clock transition for predictable operation. Schmitt trigger action at all inputs makes the circuit tolerant to slower input rise and fall times across the entire VCC range from 0.8 V to 3.6 V. This device ensures a very low static and dynamic power consumption across the entire VCC range from 0.8 V to 3.6 V. This device is fully specified for partial power-down applications using IOFF. The IOFF circuitry disables the output, preventing the damaging backflow current through the device when it is powered down.

74LS11中文资料

静态特性(TA 为工作环境温度范围)

参数

测试 条件

V 输入嵌位电压

IK

Vcc =最小

【1】

II=-12mA 5 4

Vcc=最小 V =2V, =-18mA

VO 输出高电平电压

H

VO 输出低电平电压

L

II 最 大 输 入 电 压 时 输 入

IH

IOH=最大

7

4

5 4 Vcc=最小,V IL=最 74

大, OL=最大

I

VI=5.5V

0.8 -1000

.c 20 20

o

0.8 -400

µA

4

mA

8

‘H11

‘LS11

单位

最小

最大 -1.5

最小 最大 最小

m /‘S11

最大 -1.5

V

2.4

2.5

2.5

V

b-1.2 2.7

2.4

2.7

0.3

0.5

0.4

V

0.4

0.5

0.5

1

1

mA

电流

Vcc=最大

VI=7V

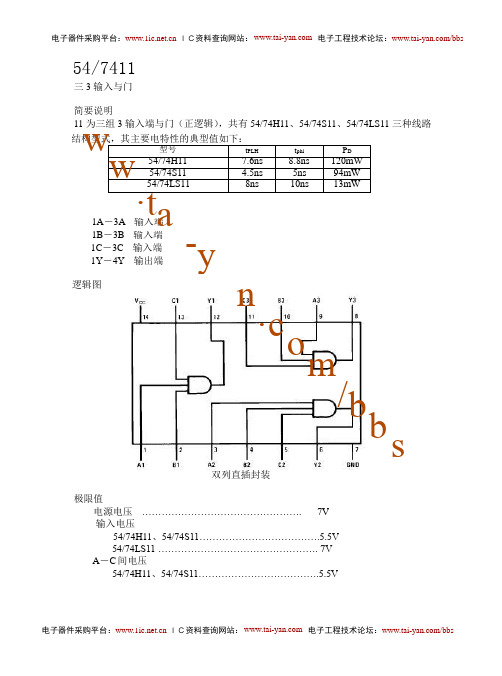

结构型式,其主要电特性的典型值如下:

型号

tPLH

tphl

PD

w 54/74H11 54/74S11

7.6ns 4.5ns

8.8ns 5ns

120mW 94mW

. ta54/74LS11

1A-3A 输入端

8ns

10ns 13mW

1B-3B 输入端 1C-3C 输入端 1Y-4Y 输出端

-y

逻辑图

54h1174h11最小额定45475254s1174s11额定5554ls1174ls11最小额定45547552最大5552508085002020最小454752最大55525080810002020最大55525070840048单位547455电源电压vccv输入高电平电压vih输入低电平电压vilvv5474输出高电平电流ioh输出低电平电流iol?ama5474静态特性ta为工作环境温度范围h11s11ls11参数测试条件1最小最大15最小最大最小252720最大1504050120041003666单位iik12maiik18mavik输入嵌位电压vcc最小12050515021002442v54745474242440252740voh输出高电平电压vcc最小vih2vioh最大vcc最小vil最大iol最大v030415021003048vol输出低电平电压vvi55vvi7vvih24vvih27vvil04vvil05vii最大输入电压时输入电流vcc最大maiih输入高电平电流vcc最大?aiil输入低电平电流vcc最大maios输出短路电流icch输出高电平时电源电流iccl输出低电平时电源电流1

SN74AUP1G79DBVR中文资料

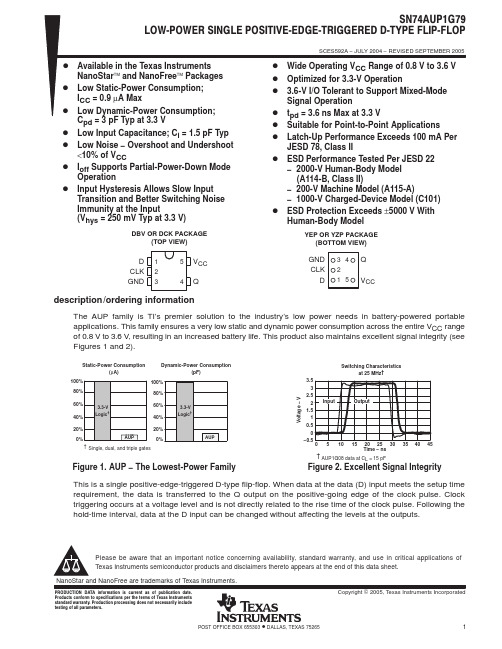

SCES592A − JULY 2004 − REVISED SEPTEMBER 2005

† Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at /sc/package. ‡ DBV/DCK: The actual top-side marking has one additional character that designates the assembly/test site. YEP/YZP: The actual top-side marking has three preceding characters to denote year, month, and sequence code, and one following character to designate the assembly/test site. Pin 1 identifier indicates solder-bump composition (1 = SnPb, • = Pb-free). FUNCTION TABLE INPUTS CLK ↑ ↑ L or H D H L X OUTPUT Q H L Q0

SN74AUP1G14YZPR中文资料

Switching Characteristics at 25 MHz† 3.5 3 2.5 2 1.5 1 0.5 0 −0.5 0 5 10 15 20 25 30 Time − ns 35 40 45 Input Output

LVC †

† Single, dual, and triple gates.

SCES578 – JUNE 2004

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

Supply voltage range, VCC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V Input voltage range, VI (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V Voltage range applied to any output in the high-impedance or power-off state, VO (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −0.5 V to 4.6 V Output voltage range in the high or low state, VO (see Note 1) . . . . . . . . . . . . . . . . . . . −0.5 V to VCC + 0.5 V Input clamp current, IIK (VI < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −50 mA Output clamp current, IOK (VO < 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −50 mA Continuous output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±20 mA Continuous current through VCC or GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±50 mA Package thermal impedance, θJA (see Note 2): DBV package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206°C/W DCK package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252°C/W YEP/YZP package . . . . . . . . . . . . . . . . . . . . . . . . . . . 132°C/W Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . −65°C to 150°C

74系列芯片数据手册大全

74系列芯片数据手册大全74系列集成电路名称与功能常用74系列标准数字电路的中文名称资料7400 TTL四2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压缓冲驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相高压缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器7425 双4输入端或非门(有选通端74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门缓冲器74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器7443 4线-10线译码器(余3码输入)7444 4线-10线译码器(余3葛莱码输入) 74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动7449 4线-7段译码器74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门7452 4路2-3-2-2输入与或门7453 4路2-2-2-2输入与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器7460 双4输入与扩展器7461 三3输入与扩展器7462 4路2-3-3-2输入与或扩展器7464 4路4-2-3-2输入与或非门74645 TTL 三态输出八同相总线传送接收器7465 4路4-2-3-2输入与或非门(OC)74670 TTL 三态输出4×4寄存器堆7470 与门输入J-K触发器√7471 与或门输入J-K触发器√7472 与门输入J-K触发器7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双上升沿D触发器7476 TTL 带预置清除双J-K触发器7478 双D型触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7487 4位二进制原码/反码7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器74101 与或门输入J-K触发器74102 与门输入J-K触发器74107 双主-从J-K触发器74108 双主-从J-K触发器74109 双主-从J-K触发器74110 与门输入J-K触发器74111 双主-从J-K触发器74112 双下降沿J-K触发器74113 双下降沿J-K触发器74114 双下降沿J-K触发器74116 双4位锁存器74120 双脉冲同步驱动器74121 单稳态触发器74122 可重触发单稳态触发器74123 可重触发双稳态触发器74125 四总线缓冲器74126 四总线缓冲器74128 四2输入端或非线驱动器74132 四2输入端与非门。

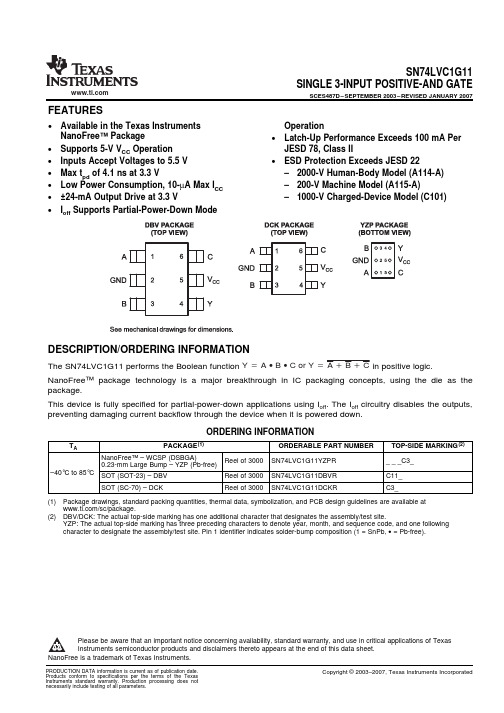

SN74LVC1G11DBVRE4中文资料

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

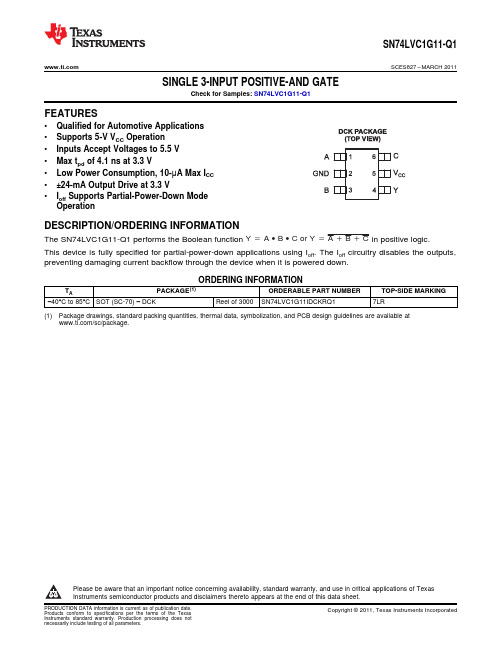

SN74LVC1G11 SINGLE 3-INPUT POSITIVE-AND GATE

SCES487D – SEPTEMBER 2003 – REVISED JANUARY 2007

Operation • Latch-Up Performance Exceeds 100 mA Per

JESD 78, Class II • ESD Protection Exceeds JESD 22

元器件交易网

FEATURES

• Available in the Texas Instruments NanoFree™ Package

• Supports 5-V VCC Operation • Inputs Accept Voltages to 5.5 V • Max tpd of 4.1 ns at 3.3 V • Low Power Consumption, 10-µA Max ICC • ±24-mA Output Drive at 3.3 V • Ioff Supports Partial-Power-Down Mode

74AUP1G08GW-G中文资料

0

200 ns/V

74AUP1G08_2

Product data sheet

Rev. 02 — 29 June 2006

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

4 of 17

Philips Semiconductors

4. Marking

Table 2. Marking Type number 74AUP1G08GW 74AUP1G08GM 74AUP1G08GF

5. Functional diagram

Marking code pE pE pE

1B 2A

Y4

mna113

Fig 1. Logic symbol

1

&

x JESD8-12 (0.8 V to 1.3 V) x JESD8-11 (0.9 V to 1.65 V) x JESD8-7 (1.2 V to 1.95 V) x JESD8-5 (1.8 V to 2.7 V) x JESD8-B (2.7 V to 3.6 V) s ESD protection: x HBM JESD22-A114-C Class 3A. Exceeds 5000 V x MM JESD22-A115-A exceeds 200 V x CDM JESD22-C101-C exceeds 1000 V s Low static power consumption; ICC = 0.9 µA (maximum) s Latch-up performance exceeds 100 mA per JESD 78 Class II s Inputs accept voltages up to 3.6 V s Low noise overshoot and undershoot < 10 % of VCC s IOFF circuitry provides partial Power-down mode operation s Multiple package options s Specified from −40 °C to +85 °C and −40 °C to +125 °C

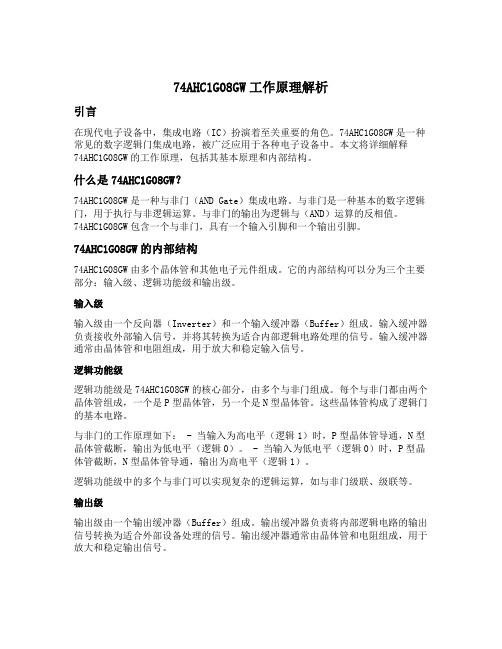

74ahc1g08gw工作原理

74AHC1G08GW工作原理解析引言在现代电子设备中,集成电路(IC)扮演着至关重要的角色。

74AHC1G08GW是一种常见的数字逻辑门集成电路,被广泛应用于各种电子设备中。

本文将详细解释74AHC1G08GW的工作原理,包括其基本原理和内部结构。

什么是74AHC1G08GW?74AHC1G08GW是一种与非门(AND Gate)集成电路。

与非门是一种基本的数字逻辑门,用于执行与非逻辑运算。

与非门的输出为逻辑与(AND)运算的反相值。

74AHC1G08GW包含一个与非门,具有一个输入引脚和一个输出引脚。

74AHC1G08GW的内部结构74AHC1G08GW由多个晶体管和其他电子元件组成。

它的内部结构可以分为三个主要部分:输入级、逻辑功能级和输出级。

输入级输入级由一个反向器(Inverter)和一个输入缓冲器(Buffer)组成。

输入缓冲器负责接收外部输入信号,并将其转换为适合内部逻辑电路处理的信号。

输入缓冲器通常由晶体管和电阻组成,用于放大和稳定输入信号。

逻辑功能级逻辑功能级是74AHC1G08GW的核心部分,由多个与非门组成。

每个与非门都由两个晶体管组成,一个是P型晶体管,另一个是N型晶体管。

这些晶体管构成了逻辑门的基本电路。

与非门的工作原理如下: - 当输入为高电平(逻辑1)时,P型晶体管导通,N型晶体管截断,输出为低电平(逻辑0)。

- 当输入为低电平(逻辑0)时,P型晶体管截断,N型晶体管导通,输出为高电平(逻辑1)。

逻辑功能级中的多个与非门可以实现复杂的逻辑运算,如与非门级联、级联等。

输出级输出级由一个输出缓冲器(Buffer)组成。

输出缓冲器负责将内部逻辑电路的输出信号转换为适合外部设备处理的信号。

输出缓冲器通常由晶体管和电阻组成,用于放大和稳定输出信号。

74AHC1G08GW的工作原理当外部输入信号被传递到74AHC1G08GW的输入引脚时,输入缓冲器将其转换为适合内部逻辑电路处理的信号。

SN74LVC1G11-Q1 数据手册说明书

–50

±50

±100

259

–65

150

UNIT V V V V mA mA mA mA

°C/W °C

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

10 ns/V

VCC = 5 V ± 0.5 V

10

–40

85 °C

(1) All unused inputs of the device must be held at VCC or GND to ensure proper device operation. Refer to the TI application report, Implications of Slow or Floating CMOS Inputs, literature number SCBA004.

2

Submit Documentation Feedback

74AUP1G11GM资料

74AUP1G11Low-power 3-input AND gateRev. 01 — 4 September 2007Product data sheet1.General descriptionThe 74AUP1G11 provides a low-power, low-voltage single 3-input AND gate.Schmitt trigger action at all inputs makes the circuit tolerant to slower input rise and falltimes across the entire V CC range from 0.8 V to 3.6 V.This device ensures a very low static and dynamic power consumption across the entireV CC range from 0.8 V to 3.6 V.This device is fully specified for partial power-down applications using I OFF.The I OFF circuitry disables the output, preventing the damaging backflow current throughthe device when it is powered down.2.Featuress Wide supply voltage range from 0.8 V to3.6Vs High noise immunitys Complies with JEDEC standards:x JESD8-12 (0.8 V to1.3 V)x JESD8-11 (0.9 V to1.65V)x JESD8-7 (1.2 V to1.95V)x JESD8-5 (1.8 V to2.7V)x JESD8-B (2.7 V to3.6V)s ESD protection:x HBM JESD22-A114E Class 3A exceeds 5000Vx MM JESD22-A115-A exceeds 200Vx CDM JESD22-C101C exceeds 1000Vs Low static power consumption; I CC = 0.9µA (maximum)s Latch-up performance exceeds 100mA per JESD 78 Class IIs Inputs accept voltages up to 3.6Vs Low noise overshoot and undershoot < 10 % of V CCs I OFF circuitry provides partial Power-down mode operations Multiple package optionss Specified from−40°C to+85°C and−40°C to+125°C3.Ordering information4.Marking5.Functional diagramTable 1.Ordering informationType numberPackageTemperature range NameDescriptionVersion 74AUP1G11GW −40°C to +125°C SC-88plastic surface-mounted package; 6 leadsSOT36374AUP1G11GM −40°C to +125°C XSON6plastic extremely thin small outline package;no leads;6 terminals; body 1×1.45×0.5mmSOT88674AUP1G11GF−40°C to +125°CXSON6plastic extremely thin small outline package;no leads;6 terminals; body 1×1×0.5mmSOT891Table 2.MarkingType number Marking code 74AUP1G11GW pU 74AUP1G11GM pU 74AUP1G11GFpUFig 1.Logic symbol Fig 2.IEC logic symbol Fig 3.Logic diagram001aac033A B C134Y6001aac029&4136001aac030AB CY6.Pinning information6.1Pinning6.2Pin description7.Functional description[1]H =HIGH voltage level;L =LOW voltage level;X =don’t care.Fig 4.Pin configuration SOT363(SC-88)Fig 5.Pin configuration SOT886(XSON6)Fig 6.Pin configuration SOT891(XSON6)74AUP1G11A C GNDBY001aag9171236V CC5474AUP1G11GND 001aag918ABV CCCYTransparent top view 23154674AUP1G11GND001aag919A BV CC C YTransparent top view231546Table 3.Pin descriptionSymbol Pin Description A 1data input GND 2ground (0V)B 3data input Y 4data output V CC 5supply voltage C6data inputTable 4.Function table [1]Input OutputA B C Y H H H H L X X L X L X L XXLL8.Limiting valuesTable 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol Parameter Conditions Min Max Unit V CC supply voltage−0.5+4.6VI IK input clamping current V I<0V−50-mAV I input voltage[1]−0.5+4.6VI OK output clamping current V O>V CC or V O<0V-±50mAV O output voltage Active mode and Power-down mode[1]−0.5+4.6VI O output current V O=0 V to V CC-±20mAI CC supply current-50mAI GND ground current−50-mAT stg storage temperature−65+150°CP tot total power dissipation T amb=−40°C to +125°C[2]-250mW[1]The minimum input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For SC-88 packages: above 87.5°C the value of P tot derates linearly with 4.0mW/K.For XSON6 packages: above 45°C the value of P tot derates linearly with 2.4mW/K.9.Recommended operating conditionsTable 6.Recommended operating conditionsSymbol Parameter Conditions Min Max Unit V CC supply voltage0.8 3.6VV I input voltage0 3.6VV O output voltage Active mode0V CC VPower-down mode; V CC=0V0 3.6VT amb ambient temperature−40+125°C ∆t/∆V input transition rise and fall rate V CC=0.8 V to3.6V-200ns/V10.Static characteristicsTable 7.Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions Min Typ Max Unit T amb = 25°CV IH HIGH-level input voltage V CC = 0.8 V0.70× V CC--VV CC = 0.9 V to 1.95 V0.65× V CC--VV CC = 2.3 V to 2.7 V 1.6--VV CC = 3.0 V to 3.6 V 2.0--VV IL LOW-level input voltage V CC = 0.8 V--0.30× V CC VV CC = 0.9 V to 1.95 V--0.35× V CC VV CC = 2.3 V to 2.7 V--0.7VV CC = 3.0 V to 3.6 V--0.9VV OH HIGH-level output voltage V I = V IH or V ILI O =−20µA; V CC = 0.8 V to 3.6 V V CC− 0.1--VI O =−1.1 mA; V CC = 1.1 V0.75× V CC--VI O =−1.7 mA; V CC = 1.4 V 1.11--VI O =−1.9 mA; V CC = 1.65 V 1.32--VI O =−2.3 mA; V CC = 2.3 V 2.05--VI O =−3.1 mA; V CC = 2.3 V 1.9--VI O =−2.7 mA; V CC = 3.0 V 2.72--VI O =−4.0 mA; V CC = 3.0 V 2.6--VV OL LOW-level output voltage V I = V IH or V ILI O = 20µA; V CC = 0.8 V to 3.6 V--0.1VI O = 1.1 mA; V CC = 1.1 V--0.3× V CC VI O = 1.7 mA; V CC = 1.4 V--0.31VI O = 1.9 mA; V CC = 1.65 V--0.31VI O = 2.3 mA; V CC = 2.3 V--0.31VI O = 3.1 mA; V CC = 2.3 V--0.44VI O = 2.7 mA; V CC = 3.0 V--0.31VI O = 4.0 mA; V CC = 3.0 V--0.44VI I input leakage current V I=GND to3.6V;V CC=0V to3.6V--±0.1µA I OFF power-off leakage current V I or V O = 0 V to 3.6 V; V CC = 0 V--±0.2µA∆I OFF additional power-offleakage current V I or V O = 0 V to 3.6 V;V CC=0V to0.2V--±0.2µAI CC supply current V I = GND or V CC; I O = 0A;V CC=0.8V to3.6V--0.5µA∆I CC additional supply current V I = V CC− 0.6 V; I O = 0A;V CC=3.3V[1]--40µAC I input capacitance V CC= 0 V to 3.6 V; V I = GND or V CC-0.8-pF C O output capacitance V O = GND; V CC= 0 V- 1.7-pFT amb =−40°C to +85°CV IH HIGH-level input voltage V CC = 0.8 V0.70× V CC--VV CC = 0.9 V to 1.95 V0.65× V CC--VV CC = 2.3 V to 2.7 V 1.6--VV CC = 3.0 V to 3.6 V 2.0--V V IL LOW-level input voltage V CC = 0.8 V--0.30× V CC VV CC = 0.9 V to 1.95 V--0.35× V CC VV CC = 2.3 V to 2.7 V--0.7VV CC = 3.0 V to 3.6 V--0.9V V OH HIGH-level output voltage V I = V IH or V ILI O =−20µA; V CC = 0.8 V to 3.6 V V CC− 0.1--VI O =−1.1 mA; V CC = 1.1 V0.7× V CC--VI O =−1.7 mA; V CC = 1.4 V 1.03--VI O =−1.9 mA; V CC = 1.65 V 1.30--VI O =−2.3 mA; V CC = 2.3 V 1.97--VI O =−3.1 mA; V CC = 2.3 V 1.85--VI O =−2.7 mA; V CC = 3.0 V 2.67--VI O =−4.0 mA; V CC = 3.0 V 2.55--V V OL LOW-level output voltage V I = V IH or V ILI O = 20µA; V CC = 0.8 V to 3.6 V--0.1VI O = 1.1 mA; V CC = 1.1 V--0.3× V CC VI O = 1.7 mA; V CC = 1.4 V--0.37VI O = 1.9 mA; V CC = 1.65 V--0.35VI O = 2.3 mA; V CC = 2.3 V--0.33VI O = 3.1 mA; V CC = 2.3 V--0.45VI O = 2.7 mA; V CC = 3.0 V--0.33VI O = 4.0 mA; V CC = 3.0 V--0.45V I I input leakage current V I=GND to3.6V;V CC=0V to3.6V--±0.5µA I OFF power-off leakage current V I or V O = 0 V to 3.6 V; V CC = 0 V--±0.5µA∆I OFF additional power-offleakage current V I or V O = 0 V to 3.6 V;V CC=0V to0.2V--±0.6µAI CC supply current V I = GND or V CC; I O = 0A;V CC=0.8V to3.6V--0.9µA∆I CC additional supply current V I = V CC− 0.6 V; I O = 0A;V CC=3.3V [1]--50µATable 7.Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions Min Typ Max UnitT amb =−40°C to +125°CV IH HIGH-level input voltage V CC = 0.8 V0.75× V CC--VV CC = 0.9 V to 1.95 V0.70× V CC--VV CC = 2.3 V to 2.7 V 1.6--VV CC = 3.0 V to 3.6 V 2.0--V V IL LOW-level input voltage V CC = 0.8 V--0.25× V CC VV CC = 0.9 V to 1.95 V--0.30× V CC VV CC = 2.3 V to 2.7 V--0.7VV CC = 3.0 V to 3.6 V--0.9V V OH HIGH-level output voltage V I = V IH or V ILI O =−20µA; V CC = 0.8 V to 3.6 V V CC− 0.11--VI O =−1.1 mA; V CC = 1.1 V0.6× V CC--VI O =−1.7 mA; V CC = 1.4 V0.93--VI O =−1.9 mA; V CC = 1.65 V 1.17--VI O =−2.3 mA; V CC = 2.3 V 1.77--VI O =−3.1 mA; V CC = 2.3 V 1.67--VI O =−2.7 mA; V CC = 3.0 V 2.40--VI O =−4.0 mA; V CC = 3.0 V 2.30--V V OL LOW-level output voltage V I = V IH or V ILI O = 20µA; V CC = 0.8 V to 3.6 V--0.11VI O = 1.1 mA; V CC = 1.1 V--0.33× V CC VI O = 1.7 mA; V CC = 1.4 V--0.41VI O = 1.9 mA; V CC = 1.65 V--0.39VI O = 2.3 mA; V CC = 2.3 V--0.36VI O = 3.1 mA; V CC = 2.3 V--0.50VI O = 2.7 mA; V CC = 3.0 V--0.36VI O = 4.0 mA; V CC = 3.0 V--0.50V I I input leakage current V I=GND to3.6V;V CC=0V to3.6V--±0.75µA I OFF power-off leakage current V I or V O = 0 V to 3.6 V; V CC = 0 V--±0.75µA∆I OFF additional power-offleakage current V I or V O = 0 V to 3.6 V;V CC=0V to0.2V--±0.75µAI CC supply current V I = GND or V CC; I O = 0A;V CC=0.8V to3.6V-- 1.4µA∆I CC additional supply current V I = V CC− 0.6 V; I O = 0A;V CC=3.3V [1]--75µATable 7.Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground=0V).Symbol Parameter Conditions Min Typ Max Unit[1]One input at V CC− 0.6 V, other input at V CC or GND.11.Dynamic characteristicsTable 8.Dynamic characteristicsVoltages are referenced to GND (ground=0V); for test circuit see Figure8.Symbol Parameter Conditions25°C−40°C to +125°C UnitMin Typ[1]Max Min Max(85°C)Max (125°C)C L = 5 pFt pd propagation delay A, B and C to Y;see Figure7[2]V CC = 0.8 V-18.9----nsV CC = 1.1 V to 1.3 V 3.0 5.69.5 2.89.910.0nsV CC = 1.4 V to 1.6 V 2.3 3.9 5.9 2.2 6.5 6.8nsV CC = 1.65 V to 1.95 V 1.9 3.1 4.8 1.8 5.3 5.5nsV CC = 2.3 V to 2.7 V 1.6 2.5 3.6 1.4 4.0 4.2nsV CC = 3.0 V to 3.6 V 1.3 2.2 3.2 1.2 3.5 3.7ns C L = 10 pFt pd propagation delay A, B and C to Y;see Figure7[2]V CC = 0.8 V-22.5----nsV CC = 1.1 V to 1.3 V 3.5 6.511.1 3.311.611.8nsV CC = 1.4 V to 1.6 V 2.8 4.5 6.8 2.67.57.8nsV CC = 1.65 V to 1.95 V 2.4 3.7 5.6 2.1 6.2 6.4nsV CC = 2.3 V to 2.7 V 1.9 3.0 4.4 1.7 4.8 5.1nsV CC = 3.0 V to 3.6 V 1.7 2.8 4.0 1.5 4.3 4.5ns C L = 15 pFt pd propagation delay A, B and C to Y;see Figure7[2]V CC = 0.8 V-23.6----nsV CC = 1.1 V to 1.3 V 3.97.312.5 3.613.313.4nsV CC = 1.4 V to 1.6 V 3.2 5.17.6 2.98.58.8nsV CC = 1.65 V to 1.95 V 2.7 4.2 6.3 2.4 6.97.3nsV CC = 2.3 V to 2.7 V 2.3 3.5 5.0 2.0 5.5 5.8nsV CC = 3.0 V to 3.6 V 2.0 3.2 4.6 1.8 5.0 5.2ns C L = 30 pFt pd propagation delay A, B and C to Y;see Figure7[2]V CC = 0.8 V-36.3----nsV CC = 1.1 V to 1.3 V 5.19.516.8 4.817.918.3nsV CC = 1.4 V to 1.6 V 4.2 6.710.0 3.811.311.8nsV CC = 1.65 V to 1.95 V 3.6 5.58.1 3.29.19.7nsV CC = 2.3 V to 2.7 V 3.0 4.6 6.6 2.87.27.5nsV CC = 3.0 V to 3.6 V 2.7 4.3 6.1 2.5 6.6 6.9ns[1]All typical values are measured at nominal V CC .[2]t pd is the same as t PLH and t PHL .[3]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ×V CC 2×f i ×N +Σ(C L ×V CC 2×f o ) where:f i =input frequency in MHz;f o =output frequency in MHz;C L =load capacitance in pF;V CC =supply voltage in V;N =number of inputs switching;Σ(C L ×V CC 2×f o )=sum of the outputs.12.WaveformsC L = 5 pF, 10 pF, 15 pF and 30 pF C PDpower dissipation capacitancef i = 1 MHz;V I =GND to V CC [3]V CC = 0.8 V - 2.7----pF V CC = 1.1 V to 1.3 V - 2.8----pF V CC = 1.4 V to 1.6 V - 2.9----pF V CC = 1.65 V to 1.95 V - 3.1----pF V CC = 2.3 V to 2.7 V - 3.5----pF V CC = 3.0 V to 3.6 V-4.1----pFTable 8.Dynamic characteristics …continuedVoltages are referenced to GND (ground =0V); for test circuit see Figure 8.Symbol ParameterConditions25°C −40°C to +125°C UnitMinTyp [1]MaxMinMax (85°C)Max (125°C)Measurement points are given in Table 9.Logic levels: V OL and V OH are typical output voltage drop that occur with the output load.Fig 7.Input A, B and C to output Y propagation delay times 001aad936A, B, C inputY outputt PLHt PHLGNDV IV MV MV OHV OLTable 9.Measurement pointsSupply voltageOutput Input V CCV M V M V I t r = t f 0.8 V to 3.6 V0.5× V CC0.5× V CCV CC≤ 3.0 ns[1]For measuring enable and disable times R L =5k Ω,for measuring propagation delays,setup and hold times and pulse width R L =1M Ω.Test data is given in T able 10.Definitions for test circuit:R L = Load resistance.C L = Load capacitance including jig and probe capacitance.R T = Termination resistance should be equal to the output impedance Z o of the pulse generator.V EXT = External voltage for measuring switching times.Fig 8.Load circuitry for switching times 001aac521DUTR TV I V OV EXTV CC R L5 k ΩC LGTable 10.Test dataSupply voltageLoad V EXT V CCC LR L [1]t PLH , t PHL t PZH , t PHZ t PZL , t PLZ 0.8 V to 3.6 V5 pF , 10 pF , 15pF and 30 pF 5 k Ω or 1 M ΩopenGND2× V CC13.Package outlineFig 9.Package outline SOT363 (SC-88)REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITA SOT363SC-88w BM b pD e 1epin 1indexAA 1L pQdetail XH EE v M AA B y01 2 mmscalecX132456Plastic surface-mounted package; 6 leadsSOT363UNIT A 1max b p c D E e 1H E L p Q y w v mm0.10.300.202.21.80.250.101.351.150.65e 1.32.22.00.20.10.2DIMENSIONS (mm are the original dimensions)0.450.150.250.15A 1.10.804-11-0806-03-16Fig 10.Package outline SOT886 (XSON6)terminal 1index areaREFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITASOT886MO-252SOT88604-07-1504-07-22DIMENSIONS (mm are the original dimensions)XSON6: plastic extremely thin small outline package; no leads; 6 terminals; body 1 x 1.45 x 0.5 mm DEe 1eA 1bLL 1e 11 2 mmscaleNotes1. Including plating thickness.2. Can be visible in some manufacturing processes.UNIT mm0.250.171.51.40.350.27A 1max b E 1.050.95D e e 1L 0.400.32L 10.50.6A (1)max 0.50.041625346×(2)4×(2)AFig 11.Package outline SOT891 (XSON6)terminal 1index areaREFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITASOT891SOT89105-04-0607-05-15XSON6: plastic extremely thin small outline package; no leads; 6 terminals; body 1 x 1 x 0.5 mm DEe 1eA 1b LL 1e 11 2 mmscaleDIMENSIONS (mm are the original dimensions)UNIT mm0.200.121.050.950.350.27A 1max b E 1.050.95D e e 1L 0.400.32L 10.350.55A max 0.50.04162534A6×(1)4×(1)Note1. Can be visible in some manufacturing processes.14.AbbreviationsTable 11.AbbreviationsAcronym DescriptionCDM Charged Device ModelCMOS Complementary Metal Oxide SemiconductorDUT Device Under TestESD ElectroStatic DischargeHBM Human Body ModelMM Machine Model15.Revision historyTable 12.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74AUP1G11_120070904Product data sheet--16.Legal information16.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s)described in this document may have changed since this document was published and may differ in case of multiple devices.The latest product status information is available on the Internet at URL .16.2DefinitionsDraft —The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet —A short data sheet is an extract from a full data sheet with the same product type number(s)and title.A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.16.3DisclaimersGeneral —Information in this document is believed to be accurate andreliable.However,NXP Semiconductors does not give any representations or warranties,expressed or implied,as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes —NXP Semiconductors reserves the right to make changes to information published in this document, including withoutlimitation specifications and product descriptions, at any time and without notice.This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use —NXP Semiconductors products are not designed,authorized or warranted to be suitable for use in medical, military, aircraft,space or life support equipment, nor in applications where failure ormalfunction of a NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage.NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer’s own risk.Applications —Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values —Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134)may cause permanent damage to the device.Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in theCharacteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale —NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale,as published at /profile/terms , including those pertaining to warranty,intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license —Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant,conveyance or implication of any license under any copyrights,patents or other industrial or intellectual property rights.16.4TrademarksNotice:All referenced brands,product names,service names and trademarks are the property of their respective owners.17.Contact informationFor additional information, please visit:For sales office addresses, send an email to:salesaddresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development.Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheetProductionThis document contains the product specification.18.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Ordering information. . . . . . . . . . . . . . . . . . . . . 24Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Functional diagram . . . . . . . . . . . . . . . . . . . . . . 26Pinning information. . . . . . . . . . . . . . . . . . . . . . 36.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 37Functional description . . . . . . . . . . . . . . . . . . . 38Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 49Recommended operating conditions. . . . . . . . 410Static characteristics. . . . . . . . . . . . . . . . . . . . . 511Dynamic characteristics . . . . . . . . . . . . . . . . . . 812Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 913Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1114Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 1415Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1416Legal information. . . . . . . . . . . . . . . . . . . . . . . 1516.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . 1516.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1516.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 1516.4T rademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 1517Contact information. . . . . . . . . . . . . . . . . . . . . 1518Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© NXP B.V.2007.All rights reserved.For more information, please visit: For sales office addresses, please send an email to: salesaddresses@Date of release: 4 September 2007。

74AUP1T34GW-G资料