22-16-2030;中文规格书,Datasheet资料

PSD4235G2-70U;PSD4235G2-90U;PSD4235G2-90UI;中文规格书,Datasheet资料

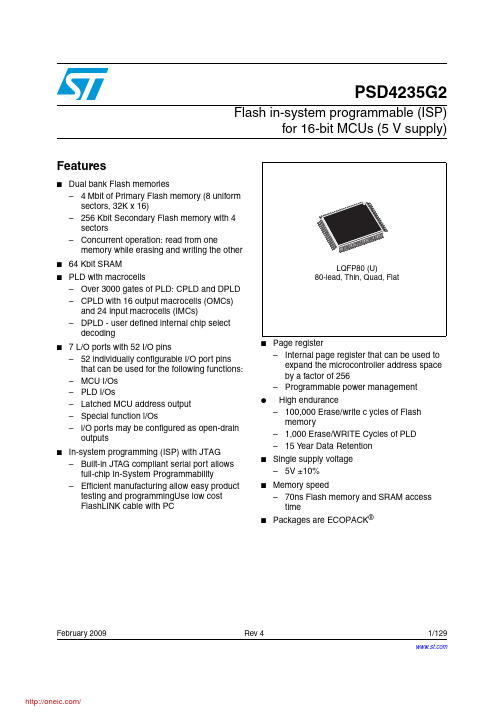

February 2009 Rev 41/129PSD4235G2Flash in-system programmable (ISP)for 16-bit MCUs (5 V supply)Features■Dual bank Flash memories– 4 Mbit of Primary Flash memory (8 uniform sectors, 32K x 16)–256 Kbit Secondary Flash memory with 4 sectors–Concurrent operation: read from onememory while erasing and writing the other ■64 Kbit SRAM■PLD with macrocells–Over 3000 gates of PLD: CPLD and DPLD –CPLD with 16 output macrocells (OMCs) and 24 input macrocells (IMCs)–DPLD - user defined internal chip select decoding ■7 L/O ports with 52 I/O pins–52 individually configurable I/O port pins that can be used for the following functions:–MCU I/Os –PLD I/Os–Latched MCU address output –Special function l/Os–l/O ports may be configured as open-drain outputs ■In-system programming (ISP) with JTAG –Built-in JTAG compliant serial port allows full-chip In-System Programmability–Efficient manufacturing allow easy product testing and programmingUse low cost FlashLINK cable with PC■Page register–Internal page register that can be used to expand the microcontroller address space by a factor of 256–Programmable power management ●High endurance–100,000 Erase/write c ycles of Flash memory–1,000 Erase/WRITE Cycles of PLD –15 Y ear Data Retention ■Single supply voltage –5V ±10%■Memory speed–70ns Flash memory and SRAM access time ■Packages are ECOPACK ®Contents PSD4235G2Contents1Summary description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1In-system programming (ISP) via JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1.1First time programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.1.2Inventory build-up of pre-programmed devices . . . . . . . . . . . . . . . . . . . 121.1.3Expensive sockets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.2In-application programming (IAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121.2.1Simultaneous READ and WRITE to Flash memory . . . . . . . . . . . . . . . . 131.2.2Complex memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.2.3Separate Program and Data space . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131.3PSDsoft™ Express . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163PSD architectural overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.1Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.2PLDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.3I/O ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.4MCU bus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.5ISP via JTAG port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.6In-System Programming (ISP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.7In-application programming (IAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.8Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.9Power management unit (PMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 4Development system . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 5PSD register description and address offsets . . . . . . . . . . . . . . . . . . . 266Register bit definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286.1Data-In registers - port A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . . 286.2Data-out registers - port A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . 286.3Direction registers - ports A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . 286.4Control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 2/129PSD4235G2Contents6.5Drive registers - Ports A, B, D, E, G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296.6Drive registers - Ports C and F . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296.7Enable-Out registers - Ports A, B, C, F . . . . . . . . . . . . . . . . . . . . . . . . . . 296.8Input macrocells registers- ports A, B, C . . . . . . . . . . . . . . . . . . . . . . . . . 296.9Output macrocells A/B registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.10Mask macrocells A/B registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.11Flash Memory Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306.12Flash Boot Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.13JTAG Enable register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.14Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.15PMMR0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 316.16PMMR2 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326.17VM register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336.18Memory_ID0 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 346.19Memory_ID1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 347Detailed operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357.1Memory blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357.2Primary Flash memory and Secondary Flash memory description . . . . . 367.2.1Memory block Select signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.2.2Ready/Busy (PE4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367.3Memory operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.1Power-up condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 398.2Reading Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.3Read memory contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.4Read Primary Flash identifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408.5Read Memory Sector Protection status . . . . . . . . . . . . . . . . . . . . . . . . . . 408.6Reading the Erase/Program status bits . . . . . . . . . . . . . . . . . . . . . . . . . . 408.7Data Polling (DQ7) - DQ15 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . 418.8Toggle flag (DQ6) - DQ14 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . 418.9Error flag (DQ5) - DQ13 for Motorola . . . . . . . . . . . . . . . . . . . . . . . . . . . . 428.10Erase timeout flag (DQ3) - DQ11 for Motorola . . . . . . . . . . . . . . . . . . . . . 423/129Contents PSD4235G29Programming Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439.1Data polling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439.2Data toggle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449.3Unlock Bypass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4510Erasing Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4710.1Flash Bulk Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4710.2Suspend Sector Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4810.3Resume Sector Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4811Specific features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.1Flash Memory Sector Protect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.2Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4911.3Reset (RESET) pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 12SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5013Memory Select signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.1Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.2Memory Select configuration for MCUs with separateProgram and Data spaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5113.3Separate space modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5213.4Combined space modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5213.580C51XA memory map example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 14Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 15Memory ID registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 16PLDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 17Decode PLD (DPLD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5918Complex PLD (CPLD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6118.1Output macrocell (OMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6218.2Product Term Allocator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 4/129PSD4235G2Contents18.3Loading and Reading the output macrocells (OMC) . . . . . . . . . . . . . . . . 6418.4The OMC Mask register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6418.5The output Enable of the OMC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6418.6Input macrocells (IMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6518.7External Chip Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6719MCU bus interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6919.1PSD interface to a multiplexed bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7019.2PSD interface to a non-multiplexed 8-bit bus . . . . . . . . . . . . . . . . . . . . . . 7119.3Data Byte Enable reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7119.4MCU bus interface examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7219.580C196 and 80C186 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7319.6MC683xx and MC68HC16 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7419.780C51XA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7519.8H8/300 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7619.9MMC2001 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7719.10C16x family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7720I/O ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8020.1General port architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8020.2Port operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8120.3MCU I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.4PLD I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.5Address Out mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8220.6Address In mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.7Data Port mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.8Peripheral I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8420.9JTAG in-system programming (ISP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8520.10MCU Reset mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8520.11Port Configuration registers (PCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.12Control register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.13Direction register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8620.14Port Data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8820.15Data In . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 885/129Contents PSD4235G26/12920.16Data Out register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.17Output macrocells (OMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.18Mask macrocell register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.19Input macrocells (IMC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 20.20Enable Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89 20.21Ports A, B and C - functionality and structure . . . . . . . . . . . . . . . . . . . . . 89 20.22Port D - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90 20.23Port E - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91 20.24Port F - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92 20.25Port G - functionality and structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9221Power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9421.1Automatic Power-down (APD) Unit and Power-down mode . . . . . . . . . . . 9521.2Power-down mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9521.3Other power saving options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9621.4PLD power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9621.5PSD Chip Select input (CSI, PD2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9721.6Input clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9721.7Input control signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9822Power-on Reset, Warm Reset and Power-down . . . . . . . . . . . . . . . . . . 9922.1Power-on Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9922.2Warm Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9922.3I/O pin, register and PLD status at Reset . . . . . . . . . . . . . . . . . . . . . . . . . 9922.4Reset of Flash Memory Erase and Program cycles . . . . . . . . . . . . . . . . . 9923Programming in-circuit using the JTAG serial interface . . . . . . . . . . 10123.1Standard JTAG signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10123.2JTAG extensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10223.3Security and Flash memory protection . . . . . . . . . . . . . . . . . . . . . . . . . . 102 24Initial delivery state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104 25Maximum rating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105PSD4235G2Contents 26DC and AC parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106 27Package mechanical . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124 28Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126 Appendix A Pin assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127 29Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1287/129List of tables PSD4235G2 List of tablesTable 1.Pin names. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Table 2.Pin description (for the LQFP package) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Table 3.PLD I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 4.JTAG signals on port E. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 5.Methods of programming different functional blocks of the PSD . . . . . . . . . . . . . . . . . . . . 23 Table 6.Register address offset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 7.Data-In registers - Ports A, B, C, D, E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 8.Data-Out registers - Ports A, B, C, D, E, F, G . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 9.Direction registers - Ports A, B, C, D, E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 10.Control registers - Ports E, F, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Table 11.Drive registers - Ports A, B, D, E, G. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 12.Drive registers - Ports C, F. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 13.Enable-Out registers - Ports A, B, C, F. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 14.Input macrocell registers - Port A, B, C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Table 15.Output macrocells A register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 16.Output macrocells B register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 17.Mask macrocells A register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 18.Mask macrocells B register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 19.Flash Memory Protection register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Table 20.Flash Boot Protection register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 21.JTAG Enable register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 22.Page register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 23.PMMR0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31 Table 24.PMMR2 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 Table 25.VM register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Table 26.Memory_ID0 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 27.Memory_ID1 register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 28.Memory block size and organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 Table 29.Instructions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Table 30.Status bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 31.Status bits for Motorola. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 32.DPLD and CPLD inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Table 33.Output macrocell Port and Data bit Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Table 34.MCUs and their control signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 Table 35.16-bit data bus with BHE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Table 36.16-bit data bus with WRH and WRL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 37.16-bit data bus with SIZ0, A0 (Motorola MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 38.16-bit data bus with LDS, UDS (Motorola MCU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Table 39.Port operating modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 Table 40.Port operating mode settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Table 41.I/O port latched address output assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84 Table 42.Port Configuration registers (PCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 Table 43.Port Pin Direction Control, output Enable P.T. not defined. . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 44.Port Pin Direction Control, output Enable P.T. defined. . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 45.Port direction assignment example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 46.Drive register pin assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 Table 47.Port Data registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88 Table 48.Effect of Power-down mode on ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95 8/129PSD4235G2List of tables Table 49.PSD timing and standby current during Power-down mode. . . . . . . . . . . . . . . . . . . . . . . . 96 Table 50.APD counter operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98 Table 51.Status During Power-On Reset, Warm Reset and Power-down mode. . . . . . . . . . . . . . . . 99 Table 52.JTAG port signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102 Table 53.Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105 Table 54.Example of PSD typical power calculation at V CC = 5.0V (with Turbo mode on). . . . . . . 107 Table 55.Example of PSD typical power calculation at V CC = 5.0V (with Turbo mode off). . . . . . . 108 Table 56.Operating conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 57.AC signal letters for PLD timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 58.AC signal behavior symbols for PLD timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109 Table 59.AC measurement conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110 Table 60.Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110 Table 61.DC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111 Table 62.CPLD Combinatorial timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112 Table 63.CPLD macrocell Synchronous clock mode timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113 Table 64.CPLD macrocell Asynchronous clock mode timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114 Table 65.Input macrocell timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115 Table 66.Program, WRITE and Erase times. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116 Table 67.READ timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117 Table 68.WRITE timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119 Table 69.Port F Peripheral Data Mode Read timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 70.Port F Peripheral Data Mode Write timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 71.Reset (RESET) timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121 Table 72.Power-down timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122 Table 73.ISC timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123 Table 74.LQFP80 - 80-lead plastic thin, quad, flat package mechanical data. . . . . . . . . . . . . . . . . 124 Table 75.Ordering information scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126 Table 76.PSD4235G2 LQFP80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127 Table 77.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1289/129。

TCST2103;中文规格书,Datasheet资料

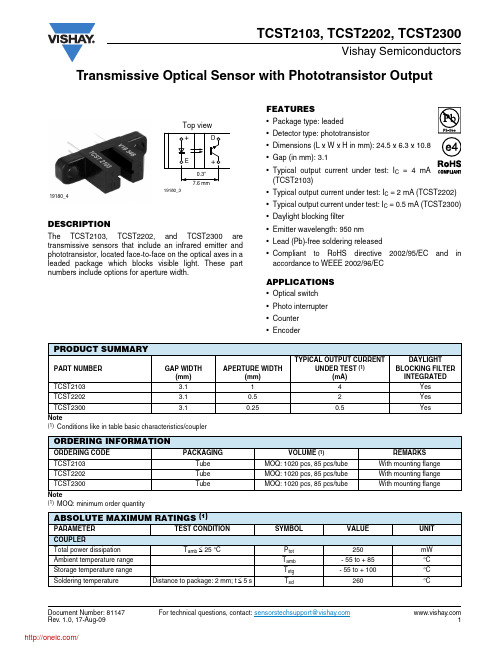

Transmissive Optical Sensor with Phototransistor OutputTCST2103, TCST2202, TCST2300Vishay SemiconductorsDESCRIPTIONThe TCST2103, TCST2202, and TCST2300 are transmissive sensors that include an infrared emitter and phototransistor, located face-to-face on the optical axes in a leaded package which blocks visible light. These part numbers include options for aperture width.FEATURES•Package type: leaded •Detector type: phototransistor•Dimensions (L x W x H in mm): 24.5 x 6.3 x 10.8•Gap (in mm): 3.1•Typical output current under test: C = 4 mA (TCST2103)•Typical output current under test: I C = 2 mA (TCST2202)•Typical output current under test: I C = 0.5 mA (TCST2300)•Daylight blocking filter •Emitter wavelength: 950 nm •Lead (Pb)-free soldering released•Compliant to RoHS directive 2002/95/EC and in accordance to WEEE 2002/96/ECAPPLICATIONS•Optical switch •Photo interrupter •Counter •EncoderNote(1)Conditions like in table basic characteristics/couplerNote(1)MOQ: minimum order quantity19180_4PRODUCT SUMMARYPART NUMBER GAP WIDTH(mm)APERTURE WIDTH(mm)TYPICAL OUTPUT CURRENTUNDER TEST (1)(mA)DAYLIGHTBLOCKING FILTER INTEGRATEDTCST2103 3.114Yes TCST2202 3.10.52Yes TCST23003.10.250.5YesORDERING INFORMATIONORDERING CODE PACKAGINGVOLUME (1)REMARKS TCST2103Tube MOQ: 1020 pcs, 85 pcs/tube With mounting flange TCST2202Tube MOQ: 1020 pcs, 85 pcs/tube With mounting flange TCST2300TubeMOQ: 1020 pcs, 85 pcs/tubeWith mounting flangeABSOLUTE MAXIMUM RATINGS (1)PARAMETER TEST CONDITIONSYMBOLVALUEUNITCOUPLERTotal power dissipation T amb ≤ 25 °CP tot 250mW Ambient temperature range T amb - 55 to + 85°C Storage temperature range T stg - 55 to + 100°C Soldering temperatureDistance to package: 2 mm; t ≤ 5 sT sd260°CTCST2103, TCST2202, TCST2300Vishay SemiconductorsTransmissive Optical Sensor withPhototransistor OutputNote (1)T amb = 25 °C, unless otherwise specifiedABSOLUTE MAXIMUM RATINGSFig. 1 - Power Dissipation Limit vs. Ambient TemperatureINPUT (EMITTER)Reverse voltage V R 6V Forward current I F 60mA Forward surge current t p ≤ 10 µs I FSM 3A Power dissipation T amb ≤ 25 °CP V 100mW Junction temperature T j100°COUTPUT (DETECTOR)Collector emitter voltage V CEO 70V Emitter collector voltage V ECO 7V Collector peak current t p /T = 0.5, t p≤ 10 msI CM 200mA Power dissipation T amb ≤ 25 °CP V 150mW Junction temperatureT j100°CABSOLUTE MAXIMUM RATINGS (1)PARAMETER TEST CONDITIONSYMBOLVALUEUNITBASIC CHARACTERISTICS (1)PARAMETER TEST CONDITIONPARTSYMBOLMIN.TYP.MAX.UNITCOUPLERCurrent transfer ratioV CE = 5 V, I F = 20 mATCST2103CTR 1020%TCST2202CTR 510%TCST2300CTR 1.25 2.5%Collector currentV CE = 5 V, I F = 20 mA TCST2103I C 24mA TCST2202I C 12mA TCST2300I C 0.250.5mA Collector emitter saturationvoltageI F = 20 mA, I C = 1 mA TCST2103V CEsat 0.4V I F = 20 mA, I C = 0.5 mA TCST2202V CEsat 0.4V I F = 20 mA, I C = 0.1 mA TCST2300V CEsat 0.4V Resolution, path of the shutter crossing the radiant sensitive zoneI Crel = 10 % to 90 %TCST2103s 0.6mm TCST2202s 0.4mm TCST2300s0.2mmTCST2103, TCST2202, TCST2300T ransmissive Optical Sensor withPhototransistor OutputVishay SemiconductorsNote (1)T amb = 25 °C, unless otherwise specifiedFig. 2 - Test Circuit for t on and t offFig. 3 - Switching TimesBASIC CHARACTERISTICST amb = 25°C, unless otherwise specifiedFig. 4 - Forward Current vs. Forward Voltage Fig. 5 - Relative Current Transfer Ratio vs. Ambient TemperatureINPUT (EMITTER)Forward voltage I F = 60 mA V F 1.25 1.6V Junction capacitance V R = 0 V, f = 1 MHzC j50pFOUTPUT (DETECTOR)Collector emitter voltage I C = 1 mA V CEO 70V Emitter collector voltage I E = 10 µAV ECO 7V Collector dark currentV CE = 25 V, I F = 0 A, E = 0 lxI CEO100nASWITCHING CHARACTERISTICS Turn-on time I C = 2 mA, V S = 5 V,R L = 100 Ω (see figure 2)t on 10µs Turn-off timeI C = 2 mA, V S = 5 V,R L = 100 Ω (see figure 2)t off8µsBASIC CHARACTERISTICS (1)PARAMETER TEST CONDITIONPARTSYMBOLMIN.TYP.MAX.UNIT10 %90 %100 %I FI C t p P u lse d u ration t d Delay time t rRise time t on (= t d + t r ) T u rn-on timet s Storage time t fFall time t off (= t s + t f )T u rn-off time96 11698TCST2103, TCST2202, TCST2300Vishay Semiconductors Transmissive Optical Sensor withPhototransistor OutputFig. 6 - Collector Dark Current vs. Ambient Temperature Fig. 7 - Collector Current vs. Forward Current Fig. 8 - Collector Current vs. Collector Emitter VoltageFig. 9 - Current Transfer Ratio vs. Forward Current Fig. 10 - Turn-off/Turn-on Time vs. Collector Current Fig. 11 - Relative Collector Current vs. DisplacementTCST2103, TCST2202, TCST2300T ransmissive Optical Sensor withPhototransistor OutputVishay SemiconductorsFig. 12 - Relative Collector Current vs. Displacement Fig. 13 - Relative Collector Current vs. DisplacementPACKAGE DIMENSIONS in millimetersTCST2103, TCST2202, TCST2300Vishay Semiconductors Transmissive Optical Sensor withPhototransistor Output TUBE DIMENSIONS in millimetersPackaging and Ordering InformationPackaging and Ordering InformationVishay SemiconductorsNotes(1)MOQ: minimum order quantity (2)Please refer to datasheetsTUBE SPECIFICATION FIGURESFig. 1PART NUMBER MOQ (1)PCS PER TUBETUBE SPEC.(FIGURE)CONSTITUENTS(FORMS)CNY70400080128TCPT1300X012000Reel (2)29TCRT10001000Bulk -26TCRT10101000Bulk -26TCRT5000450050227TCRT5000L 240048327TCST1030520065524TCST1030L 260065624TCST1103102085424TCST1202102085424TCST1230480060724TCST1300102085424TCST2103102085424TCST2202102085424TCST2300102085424TCST5250486030824TCUT1300X012000Reel (2)29TCZT8020-PAER2500Bulk-22Packaging and Ordering InformationVishay Semiconductors Packaging and Ordering InformationFig. 2Fig. 3Packaging and Ordering Information Packaging and Ordering Information Vishay SemiconductorsFig. 4Fig. 5Packaging and Ordering InformationVishay Semiconductors Packaging and Ordering InformationFig. 6Fig. 7分销商库存信息: VISHAYTCST2103。

BSS64;中文规格书,Datasheet资料

50

100

1

10 100 I C - COLLECTOR CURRE NT (mA)

200

/

BSS64

NPN General Purpose Amplifier

(continued)

Typical Characteristics

1 0.8

β = 10

V BEON - BASE EMITTER ON VOLTAGE (V)

SMALL SIGNAL CHARACTERISTICS

fT Cob Current Gain - Bandwidth Product Output Capacitance IC = 4.0 mA, VCE = 10, f = 35 MHz VCB = 10 V, f = 1.0 MHz 60 5.0 MHz pF

Absolute Maximum Ratings*

Symbol

VCEO VCBO VEBO IC TJ, Tstg Collector-Emitter Voltage Collector-Base Voltage Emitter-Base Voltage Collector Current - Continuous

TA = 25°C unless otherwise noted

Parameter

Value

80 120 5.0 200 -55 to +150

Units

V V V mA °C

Operating and Storage Junction Temperature Range

*These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

ORD9216-2030;中文规格书,Datasheet资料

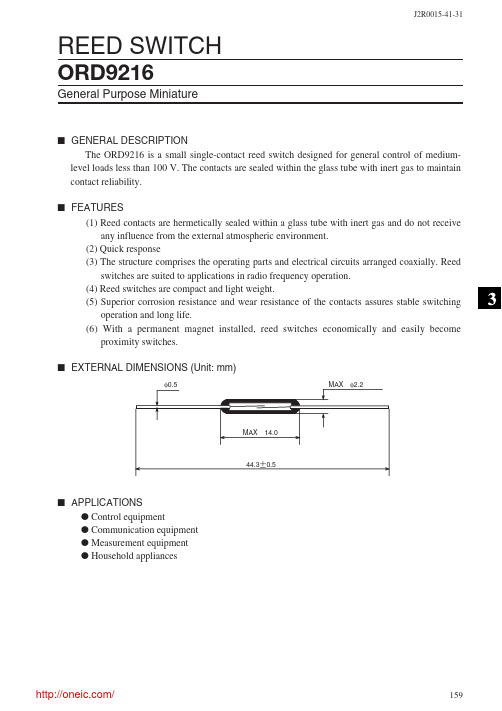

ORD9216 l

n MECHANICAL CHARACTERISTICS

(1) Lead tensile test (static load)

2.27kg-10sec

(2) Lead tensile strength

99.9

AT 60

Cumulative frequency percent (%)

99 95 90 80 70 60 50 40 30 20 10 5 1 0.1 0 2 4 6 8 10kg Breaking load

Pull-in Value • Drop-out Value

50

40

PI

30

20

DO

10

0 Contact resistance

80

CR

60

40

Before test After test

0.4 Operate time

0.3

0.2

0.1

0

10

20

30 Pull-in Value

40

50

0.1

AT

0

0.1

0.2

0.3

0.4

ms

Bounce time

(3) Release time

(4) Resonant frequency

99.9

Cumulative frequency percent (%)

n ENVIRONMENTAL CHARACTERISTICS

(1) Temperature characteristics

40 CR 30

Rate of change percent

20 DO 10 PI 0

10

QSD2030;中文规格书,Datasheet资料

QSD2030 — Plastic Silicon PhotodiodePlastic Silicon PhotodiodeFeatures■ PIN photodiode■ Package type: T-1 3/4 (5mm lens diameter) ■ Wide reception angle, 40°■ Package material and color: clear epoxy■ High sensitivity■ Peak sensitivity λ = 880nm■ Radiant sensitive area: 1.245mm x 1.245mmPackage Dimensions0.195 (4.95)0.040 (1.02)NOM0.100 (2.54) NOM0.050 (1.25)0.800 (20.3)MIN0.305 (7.75)0.240 (6.10)0.215 (5.45)0.020 (0.51)SQ. (2X)REFERENCE SURFACECATHODECATHODEANODENotes:SchematicQSD2030 — Plastic Silicon PhotodiodeNotes:1. Derate power dissipation linearly 1.33mW/°C above 25°C.2. RMA flux is recommended.3. Methanol or isopropyl alcohols are recommended as cleaning agents.4. Soldering iron 1/16” (1.6mm) minimum from housing.Electrical/Optical Characteristics (T A =25°C)T OPR Operating Temperature -40 to +100°C T STG Storage Temperature-40 to +100°C T SOL-I Soldering Temperature (Iron)(2,3,4) 240 for 5 sec °C T SOL-F Soldering Temperature (Flow)(2,3) 260 for 10 sec°C V BR Reverse Breakdown Voltage 50V P DPower Dissipation (1)100mWSymbolParameterTest Conditions Min.Typ.Max.UnitsλPS Peak Sensitivity Wavelength 880nm λSR Wavelength Sensitivity Range 4001100nm Θ Reception Angle ±20°V F Forward Voltage I F = 80mA 1.3VI D Reverse Dark Current V R = 10V , Ee = 010nA I L Reverse Light Current Ee = 0.5mW/cm 2 , V R = 5V , λ = 950nm1525µA V O Open Circuit VoltageEe = 0.5mW/cm 2 , λ = 880nm 420mV TC V Temperature Coefficient of V O +0.6mV / K I SC Short Circuit CurrentEe = 0.5mW/cm 2 , λ = 880nm 50µA TC I Temperature Coefficient of I SC +0.3% / K C Capacitance V R = 0, f = 1MHz, Ee = 060pF t r Rise Time V R = 5V , R L = 50 Ω , λ = 950nm5nst fFall Time5QSD2030 — Plastic Silicon PhotodiodeFigure 4. Dark Current vs. Reverse VoltageFigure 3. Capacitance vs. Reverse VoltageVR–Break Down Voltage (V)I D –D a r k C u r r e n t (n A )Vr–Reverse Voltage (V)C j –C a p a c i t a n c e (p F )51015202530350.30.40.50.60.70.80.91.01.11.21.3T A = 25°C246810121416182014121086420Ee–Emitter output power (mw/cm 2)0.00.10.20.30.40.50.60.70.80.940°50°60°70°80°90°1.00.90.80.7I L –R e v e r s e L i g h t C u r r e n t V o l t 0510152025303540subsidiaries,and is notAccuPower™Auto-SPM™Build it Now™CorePLUS™CorePOWER™CROSSVOLT™CTL™Current Transfer Logic™DEUXPEED®Dual Cool™EcoSPARK®EfficientMax™ESBC™®Fairchild®Fairchild Semiconductor®FACT Quiet Series™FACT®FAST®FastvCore™FETBench™FlashWriter®*FPS™F-PFS™FRFET®Global Power Resource SMGreen FPS™Green FPS™e-Series™G max™GTO™IntelliMAX™ISOPLANAR™MegaBuck™MICROCOUPLER™MicroFET™MicroPak™MicroPak2™MillerDrive™MotionMax™Motion-SPM™OptoHiT™OPTOLOGIC®OPTOPLANAR®®PDP SPM™Power-SPM™PowerTrench®PowerXS™Programmable Active Droop™QFET®QS™Quiet Series™RapidConfigure™™Saving our world,1mW/W/kW at a time™SignalWise™SmartMax™SMART START™SPM®STEALTH™SuperFET™SuperSOT™-3SuperSOT™-6SuperSOT™-8SupreMOS®SyncFET™Sync-Lock™®*The Power Franchise®TinyBoost™TinyBuck™TinyCalc™TinyLogic®TINYOPTO™TinyPower™TinyPWM™TinyWire™TriFault Detect™TRUECURRENT™*"SerDes™UHC®Ultra FRFET™UniFET™VCX™VisualMax™XS™*Trademarks of System General Corporation,used under license by Fairchild Semiconductor.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY,FUNCTION,OR DESIGN.FAIRCHILD DOES NOT ASSUME ANYLIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS,NOR THE RIGHTS OF OTHERS.THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD’S WORLDWID E TERMS AND CONDITIONS,SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body or(b)support or sustain life,and(c)whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury of the user.2.A critical component in any component of a life support,device,orsystem whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.ANTI-COUNTERFEITING POLICYFairchild Semiconductor Corporation's Anti-Counterfeiting Policy.Fairchild's Anti-Counterfeiting Policy is also stated on ourexternal website,, under Sales Support.Counterfeiting of semiconductor parts is a growing problem in the industry.All manufacturers of semiconductor products are experiencing counterfeiting of their parts.Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation,substa ndard performance,failed applications,and increased cost of production and manufacturing delays.Fairchild is taking strong measures to protect ourselv es and our customers from the proliferation of counterfeit parts.Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fa irchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above.Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts,have full traceability,meet Fairchild's quality standards for handling and storage and provide access to Fa irchild's full range of up-to-date technical and product information.Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately addr ess any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources.Fairchild is c ommitted to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.PRODUCT STATUS DEFINITIONSDefinition of TermsDatasheet Identification Product Status Definitionn QSD2030 — Plastic Silicon Photodiode分销商库存信息: FAIRCHILDQSD2030。

IRMCK203;中文规格书,Datasheet资料

Data Sheet No. PD60225 Rev BIRMCK203High Performance Sensorless Motion Control ICFeaturesComplete Sensorless control IC for PermanentMagnet AC motorsNo phase voltage feedback sensing required Sinusoidal current waveform with SynchronouslyRotating Frame closed loop current control High starting torque and smooth speed ramping Direct interface to IR2175 current sensing highvoltage IC Auto Retry at startup with configurable startingtorque Versatile loss minimization Space Vector PWM Serial communication interface (RS232C, RS422,SPI) I 2C serial interface to 1k bit serial EEPROM forparameter storage for stand alone operation Phase loss/Overcurrent/Overvoltage protection 7-bit discrete I/O for sequencing and statusmonitorIntegrated brake IGBT control for dc bus voltage limitation ServoDesigner TM tool for easy operationParallel interface for microcontroller expansionProduct SummaryMax Clock input33.3 MHz Sensorless control computation time 10 µsec max Speed operating range (typical) 5% to 100% Speed control resolution15 bit full range Adjustable current limit at start-up 15 bit full range Programmable retry on start-upmax 16 trialsOver current, speed, phase loss, dc bus fault protection PWM carrier frequency16 bit/33MHzIR2175 Current feedback data resolution 10bit Inverter leg current sensing (optional) 12bitRS232C speedup to 57.6 Kbps Optional RS422 communication up to 1 MbpsMax SPI Clock 8 MHzPackage: QFP80DescriptionIRMCK203 is a high performance digital motion control IC for Sensorless AC permanent magnet motor application. Control is based on closed loop vector control for sinusoidal Back EMF motors. With IRMCK203, the users can readily build a high performance Sensorless drive system without any programming effort and minimum start-up time. Built-in unique start-up and ramping algorithm enables wide application. This IC is versatile enough that the users can configure and optimize system performance according to the needs of each application. With International Rectifier iMOTION products including high voltage ICs such as IR2175 current sensing IC and IRAM series of Intelligent IGBT module in combination with IRMCK203, the end result is a fully optimized system with reduced electronics component counts. This simplifies the design for low cost Sensorless drive modules. IRMCK203 can be easily adapted to various permanent magnet motors through ServoDesigner TM tool, which is the fully configurable graphic user interface tool.OverviewIRMCK203 is a new International Rectifier integrated circuit device designed for one-chip solution for complete closed loop current and velocity control of a high performance Sensorless drive for PM motors. Unlike a traditional microcontroller or DSP, IRMCK203 does not require any programming to complete complex Sensorless algorithm development. Combined with International Rectifier's high voltage gate drive and current sensing IC, the user can implement complete speed control of PM motors with minimum component count and virtually no design effort. In addition to Sensorless closed loop speed control operation, features such as Start-up retry, Phase Loss detection, Low Loss PWM, Regeneration Braking control and various drive protections are all implemented inside IRMCK203. Analog and digital I/Os can also be configured. Host communication logic contains Asynchronous Communication Interface for RS232C or RS422 communication interface, a fast slave SPI interface and an 8 bit wide Host Parallel Interface. All communication ports have the same access capability to the host register set. The users can write to, and read from the predefined registers to configure and monitor the drive through these communication ports.IRMCK203 Main functions• Complete closed loop current control based on Synchronously Rotating Frame Field Orientation (using Rotor Angle Observer)• Closed loop velocity control based on estimated speed• Configurable parameters (PI controller gains, PI output limit range, current feedbackscaling, PWM carrier frequency) provide adaptation to various PM motors• Built-in Sensorless control logic for start-up, ramping, and running conditions• Auto Retry (programmable) on start-up with configurable torque current limit• Analog reference input (can be used for speed reference)• RS232C/RS422 reference input• Full dynamic braking control for DC bus voltage limitation• Cycle-by-cycle on/off Control for Brake IGBT• Loss minimization Space Vector PWM with deadtime insertion• Build-in two IR2175 current sensing IC interfaces• Phase Loss, Overcurrent (GATEKILL input), Overvoltage, Undervoltage, Overspeed protection• Low cost serial 12bit A/D interface with multiplexer and sample/hold circuit• Optional Inverter Leg (low side) current sensing in lieu of IR2175 IC• 4 channel analog output (PWM)• Local EEPROM for startup initialization of internal data/parameters through host register interface AT24C01A, 128X8• Versatile host communication interfaceRS232C or RS422 host interfaceFast SPI slave host interface with multi-drop capabilityParallel Host interface (total 12 pins)• Multiplexed data/address busAddress EnableRD/WR• Discrete I/Os for Standalone mode operationSTARTSTOP (Input)ESTOP (Input)DIR (Input) FLTCLR (Input) FAULT (Output) SYNC (Output) REDLED (Output)GREENLED (Output)Table of Contents Overview (2)IRMCK203 Main functions (2)IRMCK203 Block Diagrams (7)Basic Block Diagram (7)Input/Output of IRMCK203 (8)Application Connections (12)IC Crystal Clock Circuitry (13)PLL Clock Circuitry (14)Low Pass Filter (14)Implementing the Low Pass Filter Shield (15)Cp Rp and Cs Component Values (15)PLL Reset (15)DC Electrical Characteristics and Operating Conditions (16)Absolute Maximum Ratings (16)Recommended Operating Conditions (16)DC Characteristics (17)Common Quiescent and Leakage Current (17)Input Characteristics – Non Schmitt Inputs (17)Input Characteristics – Schmitt Inputs (17)Output Characteristics (17)Output Characteristics OSC2CLK (18)Pin and I/O Characteristic Table (19)Power Consumption (21)AC Electrical Characteristics and Operating Conditions (22)System Level AC Characteristics (22)Sync Pulse to Sync Pulse Timing (22)FAULT and REDLED Response to GATEKILL (23)Host Interface AC Characteristics (24)SPI Timing (24)Host Parallel Timing (25)Host Parallel Read Cycle (25)Host Parallel Write Cycle (26)Discrete I/O Electrical Characteristics (27)Motion Peripheral Electrical Characteristics (28)PWM Electrical Characteristics (28)IR2175 Interface (28)Analog Interface Electrical Characteristics (29)ADC Timing (29)PLL Interface Electrical Characteristics (30)Appendix A Host Register Map (31)Register Access (31)Host Parallel Access (31)SPI Register Access (31)RS-232 Register Access (31)Write Register Definitions (36)PwmConfig Register Group (Write Registers) (36)CurrentFeedbackConfig Register Group (Write Registers) (37)SystemControl Register Group (Write Registers) (38)TorqueLoopConfig Register Group (Write Registers) (38)VelocityControl Register Group (Write Registers) (39)IRMCK203 FaultControl Register Group (Write Registers) (40)SystemConfig Register Group (Write Registers) (41)EepromControl Registers (Write Registers) (42)ClosedLoopAngleEstimator Registers (Write Registers) (43)OpenLoopAngleEstimator Registers (Write Registers) (44)StartupAngleEstimator Registers (Write Registers) (44)StartupRetrial Registers (Write Registers) (45)PhaseLossDetect Registers (Write Registers) (47)D/AConverter Registers (Write Registers) (47)Factory Test Register (Write Register) (48)Read Register Definitions (49)SystemStatus Register Group (Read Registers) (49)DcBusVoltage Register Group (Read Registers) (49)FocDiagnosticData Register Group (Read Registers) (50)FaultStatus Register Group (Read Registers) (51)VelocityStatus Register Group (Read Registers) (52)CurrentFeedbackOffset Register Group (Read Registers) (53)EepromStatus Registers (Read Registers) (53)FOCDiagnosticDataSupplement Register Group (Read Registers) (54)ProductIdentification Registers (Read Registers) (55)Factory Register (Read Register) (55)Appendix B Package (56)Table of FiguresFigure 1: IRMCS2031 Simplified Blocks (7)Figure 2: Input/Output of IRMCK203 (8)Figure 3: Application Connection of IRMCK203 (12)Figure 4: Oscillator Circuit (13)Figure 5: PLL Low Pass Filter Shielding (14)Figure 6: System Level SYNC To SYNC Timing (22)Figure 7: FAULT and REDLED Response to GATEKILL (23)Figure 8: SPI Timing (24)Figure 9: Host Parallel Read Cycle (25)Figure 10: Host Parallel Write Cycle (26)Figure 11: Discrete I/O Timing (27)Figure 12: PWM Timing (28)Figure 13: IR2175 Interface (28)Figure 14: Top Level ADC Timing (29)Table of TablesTable 1: Typical Values for the Clock Circuit (13)Table 2: PLL Test Pin Assignments (14)Table 3: PLL Low Pass Filter Values (15)Table 4: Absolute Maximum Ratings (16)Table 5: Recommended Operating Conditions (16)Table 6: DC Characteristics (17)Table 7: Non Schmitt Input Characteristics (17)Table 8: Schmitt Input Characteristics (17)Table 9: Output Characteristics (17)Table 10: Output Characteristics OSC2CLK (18)Table 11: Pin and I/O Characteristics (21)Table 12: IRMCK203 Power Consumption (21)Table 13: System Level SYNC to SYNC Timing (22)Table 14: FAULT and REDLED Response to GATEKILL (23)Table 15: SPI Timing (24)Table 16: Host Parallel Read Cycle Timing (25)Table 17: Host Parallel Write Cycle Timing (26)IRMCK203 Block DiagramsBasic Block DiagramFigure 1 shows the basic block diagram of the IRMCK203 surrounded by International Rectifiers’ ICs. Host communications are provided over SPI, RS-232C or Host parallel ports. Two current sensing ICs (IR2175) and a three phase high voltage gate drive typically implement the high voltage / current interface between the IRMCK203 IC and motor.The IRMCK203 can operate in a “stand-alone” mode without the host controller. A serial EEPROM would be utilized to load motor-specific parameters into the IC.AC PowerConfigurable parameters are provided to tailor design to various applications (motor and load). These configurable parameters can be modified via the host register interface through the communication interface. In the IRMCK203 product, a design spread sheet is provided to aid the user for ease of drive start-up, the spread sheet will input high level application data such as motor name plate information, max speed, current limit, speed and current regulator bandwidth, base on this information the program will generate the required configurable parameters. Detail on Drive commissioning is described in the IRMCK203 Application Developer’s Guide.All logic and algorithms are pre-programmed, and the user does not need to make any effort to develop code, alleviating the tedious design process. If needed, the user can configure the drive to tailor the control per specificneeds to meet the required specification. This configuration can be easily done by accessing the host register interface through the communication interface.Input/Output of IRMCK203The I/O signals are shown in Figure 2. The interface signals are divided into sub-groups. For detailed pin assignment, please refer to appendix (Pin definition).PWMUH PWMUL PWMVL BRAKEGATEKILLIFB[0-1]ADCLK ADOUT ADCONVST ADMUX[0-2]RESSAMPLEPWM gate signalInterfaceIR2175 Interface A/D InterfaceSPI Interface Parallel InterfaceLED/StatusPLL Clock ControlCrystalDAC[0-3]D/A Interface (PWM output)RESETNSystem ResetFLTCLROUT Figure 2: Input/Output of IRMCK203Host Interface GroupSignal Input (I) /Output (O)Low (L) /High (H) TrueAsserted FunctionSPICLK IPositive edgesensitiveSPI clockSPIMISO O - Master input and slave output SPIMOSI I - Master output and slave input SPICSN I L SPI chip selectHP_nOE I LParallel data output enable HP_nWE I LParallel data write cycleidentificationHP_D [7:0] I/O - Parallel dataHP_A I HParallel data address cycleidentificationHP_nCS I L Chip select TX O - RS-232 data out RX I - RS-232 data inBAUDSEL[1:0] I H RS-232 baud rate: 00 = 19.3K bps;01 = 38.4K bps10 = 57.6K bps;11 = 1.031250M bpsSYNC O L Start of PWM cycleCLK1XOUT O -33.333 MHz output of PLL. This signal has no phase relationshipwith the OSC1CLK or OSC2CLK inputs.Discrete I/O GroupSignalInput (I) / Output (O)Low (L) / High (H) True AssertedFunctionSTARTSTOP I HStart / Stop command edgesensitiveDIR I HForward/Reverse Directioncommand, level sensitiveFAULTCLR I H Fault ClearESTOP I HEmergency Stop, statesensitivePWEN O H PWM enable/disable state SYNC O H SYNC pulse FAULT O H Fault stateMotion Peripheral GroupSignalInput (I) / Output (O)Low (L) / High (H) True AssertedFunctionPWMUH O PWM phase U high side PWMUL O PWM phase U low side PWMVH O PWM phase V high sidePWHVL O PWM phase V low side PWMWH O PWM phase W high side PWMWL O -PWM phase W low side BRAKE O L IGBT gateGATEKILL I Varies, Based onWrite Register0x0C Bit 7When asserted, negates all sixPWM signals, host writeableIFB0 I - Channel 0 (phase V) IFB1 I - Channel 1 (phase W)Analog Interface GroupSignal Input (I) /Output (O)Low (L) /High (H) TrueAsserted FunctionADCLK ONegative EdgeSensitiveClock to ADS7818ADOUT I - Serial data from ADS7818 DAC [3:0] O - Diagnostic DACADCONVST O LConversion start to ADS7818 RESSAMPLE OSample/hold control signalchannel 0 A/D converterADMUX0 O H Analog input MUX select ADMUX1 O H Analog input MUX selectPLL Interface GroupSignal Input (I) /Output (O)Low (L) /High (H) True AssertedFunctionXPD I L PLL reset RESETN I L Digital logic resetBYPASSCLK I HInternal test pin – force to logiclowBYPASSMODE I HInternal test pin – force to logiclowOSC1CLK I - 33.33 MHz crystal input OSC2CLK I - 33.33 MHz crystal inputPLLTEST I HInternal test pin – force to logiclowCHGO I/O - Low pass filter LPVSS I/O - Low pass filter ground分销商库存信息: IRIRMCK203。

20263;中文规格书,Datasheet资料

BDCCA 4.52.461.800 3.600R.0212 PLCS.2056PLCS2.122.00±.02.066 PLCSFULL RAD 6 PLCSR.134 PLCSAASEE NOTE 4.188.188.007SEE DETAILSECTION A-ANOTES:1. MATERIAL: MAKE FROM HENKEL AL-2-45H-212.2. THICKNESS: .007±.001.3. SEE DETAIL FOR ASSY ORDER.4. FOR ARTWORK SHOWN HERE SEE DWG# 20200.5. DENOTE CRITICAL CHARACTERISTIC FOR LOT INSPECTION.6. RoHS COMPLIANT PER CST-0001 LATEST REVISION.7. PRIOR TO ASSEMBLY, PRODUCTS SHALL BE STORED IN A COOL, DRY LOCATION IN ORIGINAL PACKAGING AT TEMPERATURES BELOW 40°C (104°F). UNDER THESE CONDITIONS THE SHELF LIFE IS INDEFINITE. THERMMATE PADS CAN BE PRE-APPLIED TO BASEPLATES OR HEAT SINKS WHICH ARE THEN SHIPPED TO A FINAL ASSEMBLY LOCATION, AS LONG AS THE TEMPERATURE DOES NOT EXCEED THE LEVEL INDICATED ABOVE.FEDETAIL :A. SPLIT RELEASE LINER.B. ADHESIVE STRIP; .0025 THICK .188 WIDE.C. ALUMINUM ALLOY 1145-0; .002 THICK.D. ROLL CARRIER WITH ADHESIVE STRIP BONDING.E. PHASE CHANGE THERMAL COMPOUND.F. ADHESIVE STRIPS ON ROLL CARRIER.(VERTICAL THICKNESS IS NOT SHOWN TO SCALE).188.007PEI AABBCCDDEEFF1122334455667788SWDTHERMAL INTERFACE PADTHERMATE (MAXI)P/N 202632/13/97J. RENAUDDATE DRAWN REV5DWG NO16188CAGE CODE67131SIZEBSHEET 1 OF 1SCALE 1: 1RELEASED PER E0430434VICORUNLESS OTHERWISE SPECIFIED DIMENSIONS ARE INCH [MM]TOLERANCES ARE:DECIMALS ANGLES X.XX [X.X] = ±0.01 [0.25] ±1°X.XXX [X.XX] = ±0.005 [0.127]FN 2REVISED PER E101310b KUK 09/16/04REVISED PER E090673C REVISED PER E091595a AR JS 3404/22/0909/10/09REJH REJH DO NOT SCALE DRAWINGTHIRD ANGLE PROJECTIONVICOR CONFIDENTIALTHIS DOCUMENT AND THE DATA DISCLOSED HEREIN OR HEREWITH IS NOT TO BE REPRODUCED, USED ORDISCLOSED IN WHOLE OR IN PART TO ANYONE WITHOUT THE PERMISSION OF VICOR CORP.DATE 1DESCRIPTIONFINISHREVISIONSREV MATERIALAPPROVED10/22/10AR 11/07/11KUKREVISED PER E1110905REJH/分销商库存信息: VICOR20263。

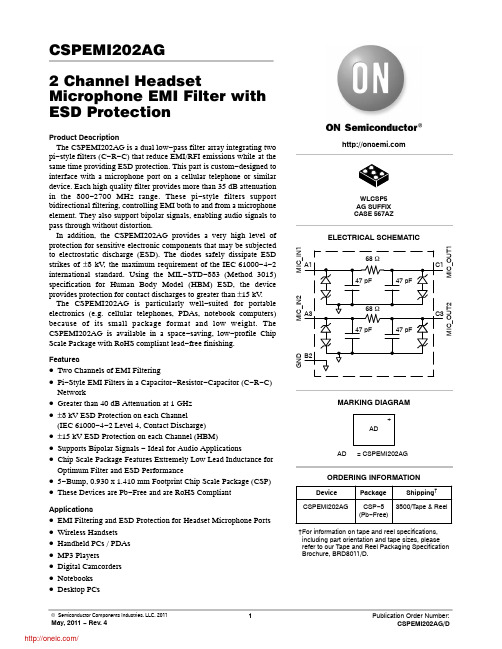

CSPEMI202AG;中文规格书,Datasheet资料

Publication Order Number: CSPEMI202AG/D

MIC_OUT2

MIC_OUT1

CSPEMI202AG

Table 1. PIN DESCRIPTIONS

5−bump CSP Package

Pin

Name

Description

A1 MIC_IN1 Microphone Input 1 (from microphone)

பைடு நூலகம்

Table 3. STANDARD OPERATING CONDITIONS Parameter

Operating Temperature Range

Rating −40 to +85

Units °C

Table 4. ELECTRICAL OPERATING CHARACTERISTICS (Note 1)

(IEC 61000−4−2 Level 4, Contact Discharge)

• ±15 kV ESD Protection on each Channel (HBM) • Supports Bipolar Signals − Ideal for Audio Applications • Chip Scale Package Features Extremely Low Lead Inductance for

68 W

A1

C1

47 pF

47 pF

68 W

A3

C3

47 pF

47 pF

B2

MARKING DIAGRAM

+ AD

AD = CSPEMI202AG

ORDERING INFORMATION

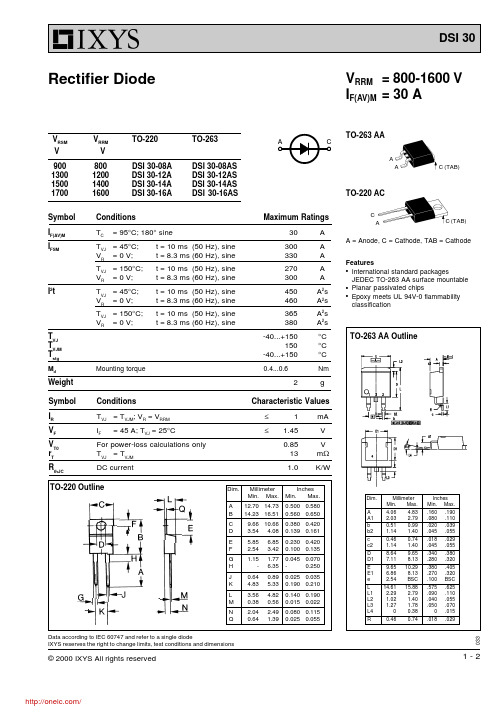

DSI30-12AS;DSI30-08AS;DSI30-16AS;DSI30-08A;DSI30-12A;中文规格书,Datasheet资料

0 0 20 40 60 80 100 120 140 °C TC

Fig. 4 Power dissipation versus direct output current and ambient temperature, sine 180°

1.2 K/W 1.0

ZthJC

Fig. 5 Max. forward current versus case temperature

Nm

A

C (TAB)

TO-220 AC

C A C (TAB)

Conditions TC = 95°C; 180° sine t = 10 ms (50 Hz), sine t = 8.3 ms (60 Hz), sine t = 10 ms (50 Hz), sine t = 8.3 ms (60 Hz), sine t = 10 ms (50 Hz), sine t = 8.3 ms (60 Hz), sine t = 10 ms (50 Hz), sine t = 8.3 ms (60 Hz), sine

50

TVJ = 150°C

10

0 0.0

0.4

0.8 VF

1.2 V

1.6

0 0.001

102 0.01 0.1 t s 1 1 2 3 4 5 6 7 ms 8 910 t

Fig. 1 Forward current versus voltage drop per diode

60 W

Fig. 2 Surge overload current

Inches Min. Max. .160 .080 .020 .045 .018 .045 .340 .280 .380 .270 .100 .575 .090 .040 .050 0 .018 .190 .110 .039 .055 .029 .055 .380 .320 .405 .320 BSC .625 .110 .055 .070 .015 .029

CS5532-BSZR;CS5534-BSZR;CDB5532U;中文规格书,Datasheet资料

Copyright © Cirrus Logic, Inc. 2008CS5532/34-BS24-bit ∆Σ ADCs with Ultra-low-noise PGIAFeaturesChopper-stabilized PGIA (ProgrammableGain Instrumentation Amplifier, 1x to 64x)– 6 nV/√Hz @ 0.1 Hz (No 1/f noise) at 64x –1200pA Input Current with Gains >1 Delta-sigma Analog-to-digital Converter –Linearity Error: 0.0007% FS–Noise-free Resolution: Up to 23 bits Two- or Four-channel Differential MUX Scalable Input Span via Calibration –±5 mV to differential ±2.5VScalable V REF Input: Up to Analog Supply Simple Three-wire Serial Interface –SPI™ and Microwire™ Compatible –Schmitt Trigger on Serial Clock (SCLK) R/W Calibration Registers Per Channel Selectable Word Rates: 6.25 to 3,840 Sps Selectable 50 or 60 Hz RejectionPower Supply Configurations–VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V–VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V –VA+ = +3 V; VA- = -3 V; VD+ = +3 VGeneral DescriptionThe CS5532/34 are highly integrated ∆Σ Analog-to-Digi-tal Converters (ADCs) which use charge-balance techniques to achieve 24-bit performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale, process control, scientific, and medical applications.To accommodate these applications, the ADCs come as either two-channel (CS5532) or four-channel (CS5534)devices and include a very low-noise, chopper-stabilized instrumentation amplifier (6 nV/√Hz @ 0.1 Hz) with se-lectable gains of 1×, 2×, 4×, 8×, 16×, 32×, and 64×.These ADCs also include a fourth-order ∆Σ modulator followed by a digital filter which provides twenty selectable output word rates of 6.25, 7.5, 12.5, 15, 25, 30, 50, 60, 100,120, 200, 240, 400, 480, 800, 960, 1600, 1920, 3200, and 3840 Sps (MCLK =4.9152MHz).To ease communication between the ADCs and a micro-controller, the converters include a simple three-wire se-rial interface which is SPI™ and Microwire™ compatible with a Schmitt-trigger input on the serial clock (SCLK).High dynamic range, programmable output rates, and flexible power supply options makes these ADCs ideal solutions for weigh scale and process control applications.ORDERING INFORMATIONSee page 47VA+C1C2VREF+VREF-VD+DIFFERENTIAL 4TH ORDER ∆ΣMODULATORPGIA 1,2,4,8,16PROGRAMMABLE SINC FIR FILTERMUX(CS5534SHOWN)AIN1+AIN1-AIN2+AIN2-AIN3+AIN3-AIN4+AIN4-SERIAL INTERFACELATCHCLOCK GENERATORCALIBRATION SRAM/CONTROLLOGICDGNDCSSDI SDO SCLKOSC2OSC1A1A0/GUARD VA-32,64OCT ‘08TABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (4)ANALOG CHARACTERISTICS (4)TYPICAL RMS NOISE (NV) (7)TYPICAL NOISE-FREE RESOLUTION(BITS) (7)5 V DIGITAL CHARACTERISTICS (8)3 V DIGITAL CHARACTERISTICS (8)DYNAMIC CHARACTERISTICS (9)ABSOLUTE MAXIMUM RATINGS (9)SWITCHING CHARACTERISTICS (10)2.GENERAL DESCRIPTION (12)2.1.Analog Input (12)2.1.1. Analog Input Span (13)2.1.2. Multiplexed Settling Limitations (13)2.1.3. Voltage Noise Density Performance (13)2.1.4. No Offset DAC (14)2.2.Overview of ADC Register Structure and Operating Modes (14)2.2.1. System Initialization (15)2.2.2. Serial Port Interface (22)2.2.3. Reading/Writing On-Chip Registers (23)2.3.Configuration Register (23)2.3.1. Power Consumption (23)2.3.2. System Reset Sequence (23)2.3.3. Input Short (24)2.3.4. Guard Signal (24)2.3.5. Voltage Reference Select (24)2.3.6. Output Latch Pins (24)2.3.7. Offset and Gain Select (25)2.3.8. Filter Rate Select (25)2.4.Setting up the CSRs for a Measurement (27)2.5.Calibration (30)2.5.1. Calibration Registers (30)2.5.2. Performing Calibrations (31)2.5.3. Self Calibration (31)2.5.4. System Calibration (32)2.5.5. Calibration Tips (32)2.5.6. Limitations in Calibration Range (33)2.6.Performing Conversions (33)2.6.1. Single Conversion Mode (33)2.6.2. Continuous Conversion Mode (34)2.6.3. Examples of Using CSRs to Perform Conversions and Calibrations (35)ing Multiple ADCs Synchronously (36)2.8.Conversion Output Coding (36)2.9.Digital Filter (38)2.10.Clock Generator (39)2.11.Power Supply Arrangements (39)2.12.Getting Started (43)2.13.PCB Layout (43)3.PIN DESCRIPTIONS (44)4.SPECIFICATION DEFINITIONS (46)5.ORDERING INFORMATION (47)6.ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION (47)7.PACKAGE DRAWINGS (48)LIST OF FIGURESFigure 1. SDI Write Timing (Not to Scale) (11)Figure 2. SDO Read Timing (Not to Scale) (11)Figure 3. Multiplexer Configuration (12)Figure 4. Input models for AIN+ and AIN- pins (13)Figure 5. Measured Voltage Noise Density (13)Figure 6. CS5532/34 Register Diagram (14)Figure 7. Command and Data Word Timing (22)Figure 8. Guard Signal Shielding Scheme (24)Figure 9. Input Reference Model when VRS = 1 (25)Figure 10. Input Reference Model when VRS = 0 (25)Figure 11. Self Calibration of Offset (32)Figure 12. Self Calibration of Gain (32)Figure 13. System Calibration of Offset (32)Figure 14. System Calibration of Gain (32)Figure 15. Synchronizing Multiple ADCs (36)Figure 16. Digital Filter Response (WR = 60 Sps) (38)Figure 18. 120 Sps Filter Phase Plot to 120 Hz (38)Figure 17. 120 Sps Filter Magnitude Plot to 120 Hz (38)Figure 19. Z-Transforms of Digital Filters (38)Figure 20. On-chip Oscillator Model (39)Figure 21. CS5532 Configured with a Single +5 V Supply (40)Figure 22. CS5532 Configured with ±2.5 V Analog Supplies (41)Figure 23. CS5532 Configured with ±3 V Analog Supplies (41)Figure 24. CS5532 Configured for Thermocouple Measurement (42)Figure 25. Bridge with Series Resistors (42)LIST OF TABLESTable 1. Conversion Timing – Single Mode (34)Table 2. Conversion Timing – Continuous Mode (35)Table 3. Command Byte Pointer (35)Table 4. Output Coding for 24-bit CS5532 and CS5534 (37)1. CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VREF+ = 5 V; VA-, VREF-, DGND = 0 V; MCLK = 4.9152 MHz; OWR (Output Word Rate) = 60 Sps; Bipolar Mode; Gain = 32)(See Notes 1 and 2.)Notes: 1.Applies after system calibration at any temperature within -40 °C ~ +85 °C.2.Specifications guaranteed by design, characterization, and/or test. LSB is 24 bits.3. This specification applies to the device only and does not include any effects by external parasiticthermocouples. The PGIA contributes 5 nV of offset drift, and the modulator contributes 640/G nV of offset drift, where G is the amplifier gain setting.4.Drift over specified temperature range after calibration at power-up at 25 °C.ParameterMin Typ Max Unit Accuracy Linearity Error -±0.0007±0.0015%FS No Missing Codes 24--Bits Bipolar Offset -±16±32LSB 24Unipolar Offset-±32±64LSB 24Offset Drift(Notes 3 and 4)-640/G +5-nV/°C Bipolar Full-scale Error -±8±31ppm Unipolar Full-scale Error -±16±62ppm Full-scale Drift(Note 4)-2-ppm/°CANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)Notes: 5.The voltage on the analog inputs is amplified by the PGIA, and becomes V CM ± Gain*(AIN+ - AIN-)/2 atthe differential outputs of the amplifier. In addition to the input common mode + signal requirements for the analog input pins, the differential outputs of the amplifier must remain between (VA- + 0.1 V) and (VA+ - 0.1 V) to avoid saturation of the output stage.6.See the section of the data sheet which discusses input models.7.Input current on AIN+ or AIN- (with Gain =1), or VREF+ or VREF- may increase to 250nA if operatedwithin 50mV of VA+ or VA-. This is due to the rough charge buffer being saturated under these conditions.ParameterMin TypMaxUnitAnalog InputCommon Mode + Signal on AIN+ or AIN-Bipolar/Unipolar ModeGain = 1 Gain = 2, 4, 8, 16, 32, 64(Note 5)VA-VA- + 0.7--VA+VA+ - 1.7V V CVF Current on AIN+ or AIN-Gain = 1 (Note 6, 7)Gain = 2, 4, 8, 16, 32, 64--501200--nA pA Input Current Noise Gain = 1 Gain = 2, 4, 8, 16, 32, 64--2001--pA/√Hz pA/√Hz Input Leakage for Mux when Off (at 25 °C)-10-pA Off-channel Mux Isolation -120-dB Open Circuit Detect Current 100300-nA Common Mode Rejection dc, Gain = 1dc, Gain = 6450, 60 Hz ---90130120---dB dB dB Input Capacitance -60-pF Guard Drive Output -20-µA Voltage Reference Input Range (VREF+) - (VREF-)1 2.5(VA+)-(VA-)V CVF Current (Note 6, 7)-50-nA Common Mode Rejection dc 50, 60 Hz --120120--dB dB Input Capacitance 11-22pF System Calibration Specifications Full-scale Calibration Range Bipolar/Unipolar Mode 3-110%FS Offset Calibration Range Bipolar Mode -100-100%FS Offset Calibration Range Unipolar Mode -90-90%FSANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)8.All outputs unloaded. All input CMOS levels.9.Power is specified when the instrumentation amplifier (Gain ≥ 2) is on. Analog supply current is reducedby approximately 1/2 when the instrumentation amplifier is off (Gain = 1).10.Tested with 100 mV change on VA+ or VA-.ParameterMinTypMaxUnitPower SuppliesDC Power Supply Currents (Normal Mode)I A+, I A-I D+- - 130.5151mA mA Power ConsumptionNormal Mode (Notes 8 and 9)Standby Sleep---70450080--mW mW µW Power Supply Rejection (Note 10)dc Positive Supplies dc Negative Supply--115115--dB dBTYPICAL RMS NOISE (nV)(See notes 11, 12, 13 and 14)Notes:11.The -B devices provide the best noise specifications.12.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25 °C.13.For Peak-to-Peak Noise multiply by 6.6 for all ranges and output rates.14.Word rates and -3dB points with FRS = 0. When FRS = 1, word rates and -3dB points scale by 5/6.TYPICAL NOISE-FREE RESOLUTION(BITS)(See Notes 15 and 16)15.Noise-free resolution listed is for bipolar operation, and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar operation, the input span is 1/2 as large, so one bit is lost. The input span is calculated in the analog input span section of the data sheet. The noise-free resolution table is computed with a value of 1.0 in the gain register. Values other than 1.0 will scale the noise, and change the noise-free resolution accordingly.16.“Noise-free resolution” is not the same as “effective resolution”. Effective resolution is based on theRMS noise value, while noise-free resolution is based on a peak-to-peak noise value specified as 6.6 times the RMS noise value. Effective resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.948.59101526509915 3.88121315213770139307.751718213052991966015.524252942731402771203134364259103198392240628013626051410202050409048012211319436973014502900581096023015927452310302060411082301,920390260470912181036207230145003,84078013602690538010800215004300086000Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gainx64x32x16x8x4x2x17.5 1.942021222323232315 3.8820212222222222307.75192021222222226015.5192021212121211203118192021212121240621717181818181848012217171717171717960230161617171717171,920390161616161616163,840780131313131313135 V DIGITAL CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VA-, DGND = 0 V; See Notes 2 and 17.)3 V DIGITAL CHARACTERISTICS(T A = 25 °C; VA+ = 5V ±5%; VD+ = 3.0V±10%; VA-, DGND = 0V; See Notes 2 and 17.)17.All measurements performed under static conditions.ParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45--VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45-VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICS18.The ADCs use a Sinc 5 filter for the 3200 Sps and 3840 Sps output word rate (OWR) and a Sinc 5 filterfollowed by a Sinc 3 filter for the other OWRs. OWR sinc5 refers to the 3200 Sps (FRS = 1) or 3840 Sps (FRS = 0) word rate associated with the Sinc 5 filter.19.The single conversion mode only outputs fully settled conversions. See Table 1 for more details aboutsingle conversion mode timing. OWR SC is used here to designate the different conversion time associated with single conversions.20.The continuous conversion mode outputs every conversion. This means that the filter’s settling timewith a full scale step input in the continuous conversion mode is dictated by the OWR.ABSOLUTE MAXIMUM RATINGS(DGND = 0 V; See Note 21.)Notes:21.All voltages with respect to ground.22.VA+ and VA- must satisfy {(VA+) - (VA-)} ≤ +6.6 V.23.VD+ and VA- must satisfy {(VD+) - (VA-)} ≤ +7.5 V.24.Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.25.Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power supply pin is ±50 mA.26.Total power dissipation, including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Ratef s MCLK/16Sps Filter Settling Time to 1/2 LSB (Full Scale Step Input)Single Conversion mode (Notes 18, 19, and 20)Continuous Conversion mode, OWR < 3200 Sps Continuous Conversion mode, OWR ≥ 3200 Spst s t s t s1/OWR SC5/OWR sinc5 + 3/OWR5/OWRs s sParameterSymbol Min Typ Max Unit DC Power Supplies(Notes 22 and 23)Positive Digital Positive Analog Negative Analog VD+VA+VA--0.3-0.3+0.3---+6.0+6.0-3.75V V V Input Current, Any Pin Except Supplies (Notes 24 and 25)I IN --±10mA Output Current I OUT--±25mA Power Dissipation (Note 26)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA (VA-) -0.3(VA-) -0.3--(VA+) + 0.3(VA+) + 0.3V V Digital Input VoltageV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage Temperature T stg-65-150°CSWITCHING CHARACTERISTICS(VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V ±10% or 5 V ±5%;DGND = 0 V; Levels: Logic 0 = 0 V, Logic 1 = VD+; C L = 50 pF; See Figures 1 and 2.)Notes:27.Device parameters are specified with a 4.9152 MHz clock.28.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.29.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.ParameterSymbol Min Typ MaxUnitMaster Clock Frequency (Note 27)External Clock or Crystal OscillatorMCLK1 4.91525MHz Master Clock Duty Cycle 40-60%Rise Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL = 4.9152 MHz(Note 29)t ost-20-ms Serial Port Timing Serial Clock Frequency SCLK 0-2MHz Serial Clock Pulse Width High Pulse Width Lowt 1t 2250250----ns nsSDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disable t 6100--nsSDO Read Timing CS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150ns分销商库存信息:CIRRUS-LOGICCS5532-BSZR CS5534-BSZR CDB5532U。

W9412G6JH-5I;中文规格书,Datasheet资料

Read Operation............................................................................................................. 12 Write Operation ............................................................................................................. 13 Precharge ..................................................................................................................... 13 Burst Termination ......................................................................................................... 13 Refresh Operation ........................................................................................................ 13 Power Down Mode ....................................................................................................... 14 Input Clock Frequency Change during Precharge Power Down Mode ........................ 14 Mode Register Operation .............................................................................................. 14 Publication Release Date: Nov. 29, 2011 Revision A03

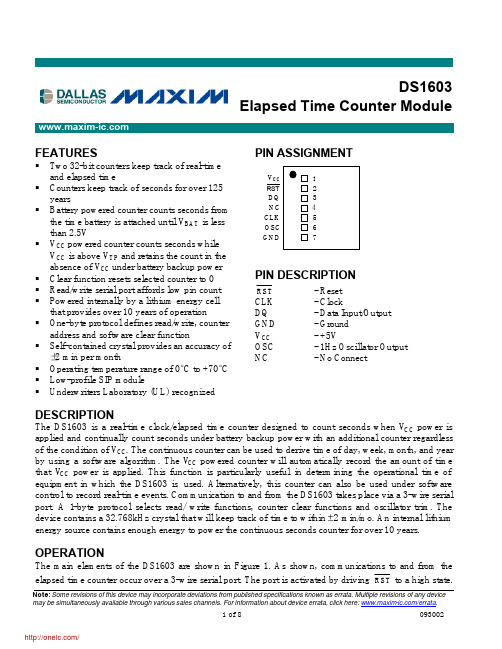

DS1603;中文规格书,Datasheet资料