6Cxxxx-xxx-3HG中文资料

TCC89xx 91xx 92xx WinCE BSP Development Guide

TCC8900/9100/9200 WinCE BSP Driver Modification GuideSeptember, 2009TelechipsWinCE BSP TeamCONTENTS1.How to set CPU and BUS clocks on TCC8900 WinCE BSP1)Overview2)F_CPU: Available CPU Clock3)F_MBUS: Available Memory BUS(DDR2) Clock, clock change4)F_VBUS, F_VCOD2.Touch Driver3.Backlight Control Example Guide-Out Guide5.Serial Driver6.DRAM Control1)ODT(On Die Termination)2)DRAM Type Selection7.How to configure VFP (Vector Floating Point) on BSP8.Hive-based Registry Setup•Overview–TCC8900 have 4 PLL sources, each PLL is asserted to each BUS and peripheral –Below figure shows overview of clock settingsName DescriptionF_CPU CPU Clock FrequencyF_MBUS CPU Interface and Memory Bus ClockF_DBUS Bus Clock for Display Device (Video In/Out + Display Related Hardwares)F_GBUS Bus Clock for Graphic DeviceF_VBUS Bus Clock for Video Processing (Video Codec)F_VCOD Core Clock for Video Codec (Moving Video Only)F_IOBUS Bus Clock for I/O Interface DevicesF_SMUBus Clock for System Management UnitPLL0Nominal: 540MHz High: 800MHz PLL1Nominal: 560MHz High: 660MHzPLL2468MHz PLL3528MHzF_CPU F_MBUS F_DBUSF_GBUS F_VBUS F_VCOD F_SMU ADC LCD LVDSSDMMC USB Host1.1Nominal voltage High voltage 600MHz 280MHz 264MHz 264MHz330MHz F_IOBUS common176MHz 156MHz 176MHz156MHz 117MHz 264MHz 234MHz234MHz 39MHz UART 52MHz 156MHz 132MHz 48MHz132MHzCore Voltage 506MHz•F_CPU: Available CPU Clock–Below table shows available clock values of CPU.–You can change F_CPU in application layer by IOCTL. Refer below example60000005062500486000047250004556250438750042525004050000394875037800003712500364500035100003375000324000030375002970000283500027000002632500243000023625002227500216000020250001890000182250017500001687500162000014850001417500135000012150001015000945000810000675000607500540000405000Core Freq.(100Hz)-Application Example CodepCKCIOCTL.ioctlcode = IOCTL_CKC_SET_CHANGECPU ;pCKCIOCTL.cpuvalue = 5062500;KernelIoControl(IOCTL_HAL_TCCCKC , &, &pCKCIOCTL pCKCIOCTL pCKCIOCTL, , , sizeof(stckcioctl sizeof(stckcioctl sizeof(stckcioctl), &), &), &pCKCINFO pCKCINFO pCKCINFO, , sizeof(stckcinfo sizeof(stckcinfo), &), &), &returnedbyte returnedbyte returnedbyte););•F_MBUS: Available Memory BUS(DDR2) Clock–Below table shows available clock values of BUS.–You can change F_MBUS in application layer by IOCTL. Refer below exampleCaution:MEM_BUS = Source/(divisor+1)The divisor should not be “Even Number”or “ZERO”.If divisor is even number, system would be unstable.330000032000003120000300000029000002800000270600026060002500000240000023000002200000210000020000001900000180000017000001600000150000014500001410000Fmbus Unit (100hz)-Application Example CodepCKCIOCTL.ioctlcode = IOCTL_CKC_SET_CHANGEMEM ; // ; // IOCtrl IOCtrl Name Name --Update Update ioctl_code.h ioctl_code.h pCKCIOCTL.busvalue pCKCIOCTL.busvalue= 3200000; // 2640000;= 3200000; // 2640000;KernelIoControl(IOCTL_HAL_TCCCKC , &, &pCKCIOCTL pCKCIOCTL pCKCIOCTL, , , sizeof(stckcioctl sizeof(stckcioctl sizeof(stckcioctl), ), &pCKCINFO,sizeof(stckcinfo pCKCINFO,sizeof(stckcinfo), &), &), &returnedbyte returnedbyte returnedbyte););•F_xBUS: Available Clock–Below table shows available clock values of F_xBUS.–You can change F_xBUS in application layer by IOCTL. Refer below example2340000264000015600001760000117000013200009360001056000780000880000668600754300585000660000520000586700468000528000425500480000390000440000360000406200334300377100312000352000292500330000Fxbus Unit(100Hz)-Application Example CodepCKCIOCTL.ioctlcode = IOCTL_CKC_SET_CHANGEFBUS ; // ; // IOCtrl IOCtrl Name Name --Update Update ioctl_code.h ioctl_code.h pCKCIOCTL.pckcname = CLKCTRL5; // = CLKCTRL5; // Fvbus Fvbus pCKCIOCTL.pckcfreq = 2640000; // 2640000;KernelIoControl(IOCTL_HAL_TCCCKC , &, &pCKCIOCTL pCKCIOCTL pCKCIOCTL, , , sizeof(stckcioctl sizeof(stckcioctl sizeof(stckcioctl), &), &), &pCKCINFO pCKCINFO pCKCINFO, , sizeof(stckcinfo sizeof(stckcinfo), &), &), &returnedbyte returnedbyte returnedbyte););•F_MBUS–Before changing clock of DDR2, DDR2 should be paused.–Refer below flow chart.–Currently, changing clock of DDR2 is only supported on bootloader.1. Location of source code-Src\LIB\SOC\DDR\TCC89x\init_MEM.c 2. Function to be referred-volatile void init_bootddr(void)-void init_copybootddr(voidCopy init_bootddr() from DDR2 to SRAMPause DDR2Change Clock of DDR2Turn on DLL volatile void init_bootddr(void){…//PLL1 is assigned for clock of DDR2*(volatile unsigned long *)0xF0400024= 0x0000fa03; // pll pwr offif(lpll1 == 660) // to use 660, clock voltage should be increased{*(volatile unsigned long *)0xF0400024= 0x00006E02; // pms-pllout_660M *(volatile unsigned long *)0xF0400024= 0x80006E02; // pll pwr on }else if(lpll1 == 560){*(volatile unsigned long *)0xF0400024= 0x00008c03; // pms-pllout_560M *(volatile unsigned long *)0xF0400024= 0x80008c03; // pll pwr on }else{*(volatile unsigned long *)0xF0400024= 0x00008c03; // pms-pllout_560M *(volatile unsigned long *)0xF0400024= 0x80008c03; // pll pwr on }…// Set clock of DDR2*(volatile unsigned long *)0xF0400008 = (0x00200000 | ((lmem_div-1) << 4)|lmem_source); // CKC-CLKCTRL2 -Mem…}Turn off DLLGo DDR2Caution:MEM_BUS = Source/(divisor+1) // The divisor should not be “Even Number”or “ZERO”In case of above code, value of lmem_div should be “Even number”•F_MBUS–Compile procedureTouch Driver•You should modify MIN_X, MAX_X, MIN_Y, MAX_Y according to version of EVB.1.#ifdef _USING_GPIO_MODE_2.#define MAX_X 38043.#define MIN_X 2254.#define MAX_Y 36905.#define MIN_Y 4006.#else7.#if _OLD_BOARD_8.#define MAX_X 31009.#define MIN_X 105010.#define MAX_Y 268011.#define MIN_Y 136012.#else13.#define MAX_X 315014.#define MIN_X 97015.#define MAX_Y 269016.#define MIN_Y 134017.#endif 18.#endifFile Location: \Magellan \Src \DRIVERS \Touch2H/W Ver.: TCC89/91/9200_MAIN V0.1H/W Ver.: TCC89/91/9200_MAIN V1.0/1.1Backlight Control Example Guide•To control brightness of LCD backlight, modify value of “vTimerAddr->TMREF3”–Maximum value of that variable is BKL_LEVEL_MAXexamplevoid tca_bkl_init(unsigned int tmr_vaddr, unsigned int gpio_vaddr){PTIMER vTimerAddr= (PTIMER) tmr_vaddr;PGPIO vGpioAddr= (PGPIO) gpio_vaddr;vTimerAddr->TCFG3 = 0x124;vTimerAddr->TREF3 = BKL_LEVEL_MAX;vTimerAddr->TCFG3 = 0x125;BITCSET(vGpioAddr->GPAFN0, Hw32-Hw28, Hw29);BITSET(vGpioAddr->GPAEN,Hw7);BITSET(vGpioAddr->GPADAT,Hw7);}•IOCTLs–IOCTL_BLK_SETPOWER : set backlight 0 ~ 100–IOCTL_BLK_GETPOWER : get backlight valueWinCE BSP TV-Out Guide •Check Catalog Item –TvOut DriverSet TV Output FormatEnable TV-OutDisable TV-OutLCD OutputTV OutputSwitching: LCD-OutChanging: TV-Out FormatSwitching: TV-Out •Overview: Switching LCD/TV Output & Change TV-Out Format•Set TV Output Format–Synopsis•DeviceIoControl(handle, IOCTL_TVOUT_TYPE,&mode, sizeof(mode), NULL, NULL, NULL, NULL);–Parameters:•IOCTL_TVOUT_TYPE–IOCTL code for setting TV output format.–Refer to: ‘IOCTL Code Definition for TV-Out’•handle: TVOUT device handle.•mode : TV output format code–Data-type: unsigned int (4 bytes)–Value: Refer to‘Supported TV Output Format’•Enable TV-Out–Synopsis•DeviceIoControl(handle, IOCTL_TVOUT_OPEN,NULL, NULL, NULL, NULL, NULL, NULL);–Parameters:•IOCTL_TVOUT_OPEN–IOCTL code for enable TV-out.–Refer to: ‘IOCTL Code Definition for TV-Out’•handle: TVOUT device handle.•Disable TV-Out (Enabled LCD-Out)–Synopsis•DeviceIoControl(handle, IOCTL_TVOUT_CLOSE,NULL, NULL, NULL, NULL, NULL, NULL);–Parameters:•IOCTL_TVOUT_CLOSE–IOCTL code for disable TV-Out.–Refer to: ‘IOCTL Code Definition for TV-Out’•handle: TVOUT device handle.•Connect LCDC–Synopsis•DeviceIoControl(handle, IOCTL_TVOUT_CONNECT_LCDC, &id, sizeof(id), NULL, NULL, NULL, NULL);–Parameters:•IOCTL_TVOUT_CONNECT_LCDC–IOCTL code for connect LCDC0 or LCDC1–Default: Connected with LCDC1.•handle: TVOUT device handle.•id : LCDC Index–Data-type: unsigned int(4 bytes)–0: LCDC0, 1: LCDC1•API: Supported TV Output Format Definition/* Supported TV Output Format Code Definition*/#define NTSC_M0x0000#define NTSC_M_J0x0001#define NTSC_N0x0010#define NTSC_N_J0x0011#define NTSC_4430x0020#define PAL_M0x0100#define PAL_N0x0110#define PAL_B0x0120#define PAL_G0x0130#define PAL_H0x0140#define PAL_I0x0150#define PSEUDO_NTSC 0x1000#define PSEUDO_PAL0x1010•API: IOCTL Code Definition for TV-Out/* IOCTL Code for TV-Out */#define IOCTL_TVOUT_TYPE TCC_IOCTLCode(1200, METHOD_BUFFERED) #define IOCTL_TVOUT_OPEN TCC_IOCTLCode(1201, METHOD_BUFFERED) #define IOCTL_TVOUT_CLOSE TCC_IOCTLCode(1202, METHOD_BUFFERED) #define IOCTL_TVOUT_CONNECT_LCDC TCC_IOCTLCode(1203, METHOD_BUFFERED)int lcd_tvout(int mode_idx){int handle;unsigned int mode;switch(mode_idx){case 1 : mode = NTSC_M; break;case 2 : mode = NTSC_M_J; break;case 3 : mode = NTSC_N; break;case 4 : mode = NTSC_N_J; break;case 5 : mode = NTSC_443; break;case 6 : mode = PAL_M; break;case 7 : mode = PAL_N; break;case 8 : mode = PAL_B; break;case 9 : mode = PAL_G; break;case 10 : mode = PAL_H; break;case 11 : mode = PAL_I; break;case 12 : mode = PSEUDO_NTSC; break;case 13 : mode = PSEUDO_PAL; break;case 0 :default :mode = 0xFFFF;break;}handle = CreateFile(L"TVO1:", GENERIC_WRITE, NULL, NULL, OPEN_ALWAYS, FILE_ATTRIBUTE_NORMAL, NULL);if ( handle == INVALID_HANDLE_VALUE)return -1;if(mode== 0xFFFF){DeviceIoControl(handle, IOCTL_TVOUT_CLOSE,NULL, NULL, NULL, NULL, NULL, NULL);}else{DeviceIoControl(handle, IOCTL_TVOUT_TYPE,&mode, sizeof(mode), NULL, NULL, NULL, NULL);ioctl(fd, TCC_LCD_FB_IOCTL_TVOUT_TYPE, &mode);DeviceIoControl(handle, IOCTL_TVOUT_CLOSE,NULL, NULL, NULL, NULL, NULL, NULL);}CloseHandle(handle);return 0;}•Example•TV-OUT Demo: Using TCDiagnostics application1.Run TCDiagnostics application2.Select [TV-Out]tab.3.Select TVOUT format•Using [Tv Type]combo box•NTSC_M, PAL_M, …4.Display to TV.•Using [TV Output]button5.Display to LCD.•Using [LCD Output]button•Channel and Port–Channel: TCC8900 provides 6 number of channels, UART 0~5•refer datasheet of TCC8900–Port: Port 0~5–In TCC8900 BSP, basically channel number and port number same•Channel and port of UART driver on TCC8900 Evaluation Board–Bluetooth: Port1 –GPS: Port5•GDMA–UART channel 0~3 only can use GDMA, other channel can not use GDMA1-1 (TX)1-0 (RX) 11COM23-1 (Reserved)3-0 (TX) 53COM1GDMAPort Channel•BOOL CPddUart::Init(DWORD nComNumber)(pddserial.cpp)//DMA TX UsagebUsingDMA=TRUE;// Set GDMA Number to be usedPTV_DMA(3,&pVirtualDmaAddr); // using DMA ch3// Set GDMAx Channel to be usedm_DmaNumber= 0;// Configure Buffer for GDMA ChannelTXBUFFADDR=(DWORD*)ptVtSysparam->DMA3.CH0_BUFFER; TXBUFFADDR_PHY=(DWORD*)ptPhySysparam->DMA3.CH0_BUFFER;// register DMA ISRSetupDmaISR(m_ComNumber, true);// Initialize interruptKernelIoControl(IOCTL_HAL_REQUEST_SYSINTR…..);m_DMATxEvent= CreateEvent(0,FALSE,FALSE,NULL); InterruptInitialize(m_dwSysIntrDMATx,m_DMATxEvent,0,0);//DMA RX UsageRXIntrusing=TRUE;//Set GDMA Number to be usedPTV_DMA(1,&pVirtualDmaAddr); // using DMA ch1// Set GDMAx Channel to be usedm_RXDmaNumber= 1;// Configure Buffer for GDMA ChannelRXBUFFADDR=(DWORD*)ptVtSysparam->DMA1.CH1_BUFFER; RXBUFFADDR_PHY=(DWORD*)ptPhySysparam->DMA1.CH1_BUFFER;// register DMA ISRSetupDmaISR(m_ComNumber, false);// Initialize interruptKernelIoControl(IOCTL_HAL_REQUEST_SYSINTR…..);m_DMATxEvent= CreateEvent(0,FALSE,FALSE,NULL); InterruptInitialize(m_dwSysIntrDMARx,m_DMARxEvent,0,0);TX Configuration of UART RX Configuration of UART•Change Port and change (COM1 COM2)Original Setting; Physical COM1;(GPS ch: 3, GPIO port: 5)[HKEY_LOCAL_MACHINE\Drivers\BuiltIn\Serial1] "COM_ChNum"=dword:3"COM_PortNum"=dword:5; Physical COM2; (BT ch: 1, GPIO port: 1)[HKEY_LOCAL_MACHINE\Drivers\BuiltIn\Serial2] "COM_ChNum"=dword:1"COM_PortNum"=dword:1Modified Setting; Physical COM1;(GPS ch: 3, GPIO port: 5)[HKEY_LOCAL_MACHINE\Drivers\BuiltIn\Serial1] "COM_ChNum"=dword:1"COM_PortNum"=dword:1; Physical COM2; (BT ch: 1, GPIO port: 1)[HKEY_LOCAL_MACHINE\Drivers\BuiltIn\Serial2] "COM_ChNum"=dword:3"COM_PortNum"=dword:5DRAM Control•ODT(On-Die-Termination) Enable/Disable–ODT is enabled normally.–Location of source:•Src\LIB\SOC\DDR\TCC89x\init_MEM.c–Function to refer•InitRoutine_Start(void) / init_bootdr(void), tag: //ZQCTRLHow to configure VFP (Vector Floating Point) on BSP•To use VFP on BSP, just check VFP option on catalog.-VFP option on OS design Wizard-VFP option on Catalog Items ViewHive-based Registry Setup •To use the hive-based registry–Add the “Hive-based Registry”catalog item.–Verify the following registry settingsin the “platform.reg”file; @CESYSGEN IF FILESYS_FSREGHIVE; HIVE BOOT SECTION[HKEY_LOCAL_MACHINE\init\BootVars]"SYSTEMHIVE"="Documents and Settings\\system.hv""PROFILEDIR"="Documents and Settings""Flags"=dword:3 ;"RegistryFlags"=dword:1 ;; END HIVE BOOT SECTION; @CESYSGEN ENDIF FILESYS_FSREGHIVE –Set the profile for the file sytem driver registry, “Nand.reg”; HIVE BOOT SECTION[HKEY_LOCAL_MACHINE\Drivers\BuiltIn\nand]"Dll"="nand.dll""Prefix"="DSK""Index"=dword:1"Profile"="Nand""IClass"=multi_sz:"{A4E7EDDA-E575-4252-9D6B-4195D48BB865}""Order"=dword:1"Flags"=dword:1000…[HKEY_LOCAL_MACHINE\System\StorageManager\Profiles\Nand] "MountFlags"=dword:0"MountAsBootable"=dword:1"MountAsRoot"=dword:1[HKEY_LOCAL_MACHINE\System\StorageManager\FATFS]"MountFlags"=dword:0; END HIVE BOOT SECTIONThank You。

XC6103D635资料

1/26XC6101_07_XC6111_17 ETR0207_009Preliminary◆CMOS Voltage Detector◆Manual Reset Input ◆Watchdog Functions ◆Built-in Delay Circuit ◆Detect Voltage Range: 1.6~5.0V, ± 2% ◆Reset Function is Selectable V DFL (Low When Detected) V DFH (High When Detected)■GENERAL DESCRIPTION The XC6101~XC6107, XC6111~XC6117 series aregroups of high-precision, low current consumption voltage detectors with manual reset input function and watchdog functions incorporating CMOS process technology. The series consist of a reference voltage source, delay circuit, comparator, and output driver.With the built-in delay circuit, the XC6101 ~ XC6107, XC6111 ~ XC6117 series’ ICs do not require any external components to output signals with release delay time. Moreover, with the manual reset function, reset can be asserted at any time. The ICs produce two types of output; V DFL (low when detected) and V DFH (high when detected).With the XC6101 ~ XC6105, XC6111 ~ XC6115 series’ ICs, the WD pin can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V IN pin voltage level, the ICs can be used with the manual reset pin left unconnected if the pin is unused.The detect voltages are internally fixed 1.6V ~ 5.0V in increments of 100mV, using laser trimming technology. Six watchdog timeout period settings are available in a range from 6.25msec to 1.6sec. Seven release delay time 1 are available in a range from 3.13msec to 1.6sec.■APPLICATIONS●Microprocessor reset circuits●Memory battery backup circuits ●System power-on reset circuits ●Power failure detection■TYPICAL APPLICATION CIRCUIT* Not necessary with CMOS output products.■FEATURESDetect Voltage Range: 1.6V ~ 5.0V, +2% (100mV increments)Hysteresis Range : V DF x 5%, TYP .(XC6101~XC6107)V DF x 0.1%, TYP .(XC6111~XC6117)Operating Voltage Range : 1.0V ~ 6.0V Detect Voltage Temperature Characteristics : +100ppm/O C (TYP .) Output Configuration : N-channel open drain,CMOSWatchdog Pin : Watchdog inputIf watchdog input maintains ‘H’ or ‘L’ within the watchdog timeout period, a reset signal is output to the RESET output pinManual Reset Pin : When driven ‘H’ to ‘L’levelsignal, the MRB pin voltage asserts forced reset on theoutput pin.Release Delay Time : 1.6sec, 400msec, 200msec,100msec, 50msec, 25msec, 3.13msec (TYP .) can be selectable.Watchdog Timeout Period : 1.6sec, 400msec, 200msec,100msec, 50msec,6.25msec (TYP .) can be selectable.■TYPICAL PERFORMANCE CHARACTERISTICS ●Supply Current vs. Input Voltage* ‘x’ represents both ‘0’ and ‘1’. (ex. XC61x1⇒XC6101 and XC6111)2/26XC6101~XC6107, XC6111~XC6117 SeriesPIN NUMBERXC6101, XC6102 XC6103 XC6104, XC6105XC6106, XC6107XC6111, XC6112 XC6113 XC6114, XC6115XC6116, XC6117SOT-25 USP-6C SOT-25 USP-6C SOT-25 USP-6C SOT-25USP-6CPIN NAMEFUNCTION1 4 - - 1 4 1 4 R ESETB Reset Output(V DFL : Low Level When Detected)2 5 2 5 2 5 2 5 V SSGround3 2 3 2 - -4 1 M RB ManualReset 4 1 4 1 4 1 - - WDWatchdog5 6 5 6 5 6 5 6 V IN Power Input - - 1 4 3 2 3 2 RESETReset Output (V DFH: High Level When Detected)■PIN CONFIGURATION SOT-25 (TOP VIEW)MRBV IN WD RESETBV SSMRBWD RESETV SSV IN RESETWD RESETBV SS V IN SOT-25 (TOP VIEW)RESETMRB RESETBV SS V IN SOT-25 (TOP VIEW) ■PIN ASSIGNMENT●SOT-25XC6101, XC6102 SeriesXC6111, XC6112 SeriesSOT-25 (TOP VIEW)XC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 Series●USP-6CXC6101, XC6102 Series XC6111, XC6112 SeriesXC6103 & XC6113 SeriesXC6104, XC6105 Series XC6114, XC6115 SeriesXC6106, XC6107 Series XC6116, XC6117 SeriesUSP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)USP-6C (BOTTOM VIEW)* The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the V SS pin.3/26XC6101 ~ XC6107, XC6111~ XC6117SeriesRESET OUTPUTSERIES WATCHDOGMANUAL RESET V DFL (RESETB)V DFH (RESET)XC6101 XC6111 Available Available CMOS - XC6102XC6112AvailableAvailableN-channel open drain-XC6103 XC6113 Available Available - CMOS XC6104 XC6114 Available Not AvailableCMOS CMOS XC6105 XC6115 Available Not Available N-channel open drain CMOS XC6106 XC6116 Not Available AvailableCMOSCMOS XC6107XC6117Not AvailableAvailableN-channel open drainCMOSDESIGNATORDESCRIPTIONSYMBOLDESCRIPTION0 : V DF x 5% (TYP .) with hysteresis ① Hysteresis Range1 : V DF x 0.1% (TYP .) without hysteresis② Functions and Type of Reset Output1 ~ 7: Watchdog and manual functions, and reset output type as per Selection Guide in the above chartA : 3.13msec (TYP .)B : 25msec (TYP .) C: 50msec (TYP .) D : 100msec (TYP .) E : 200msec (TYP .) F : 400msec (TYP .) ③ Release Delay Time * H : 1.6sec (TYP .)0 : No WD timeout period forXC6106, XC6107, XC6116, XC6117 Series 1: 6.25msec (TYP .) 2 : 50msec (TYP .) 3 : 100msec (TYP .) 4 : 200msec (TYP .) 5 : 400msec (TYP .) ④ Watchdog Timeout Period6: 1.6sec (TYP .) ⑤⑥ Detect Voltage 16 ~ 50: Detect voltageex.) 4.5V: ⑤⇒4, ⑥⇒5M : SOT-25 ⑦ Package E : USP-6C R : Embossed tape, standard feed ⑧ Device OrientationL: Embossed tape, reverse feed* Please set the release delay time shorter than or equal to the watchdog timeout period. ex.) XC6101D427MR or XC6101D327MR■PRODUCT CLASSIFICATION ●Selection Guide ●Ordering Information XC61①②③④⑤⑥⑦⑧4/26XC6101~XC6107, XC6111~XC6117 Series■PACKAGING INFORMATION●SOT-25●USP-6C5/26XC6101 ~ XC6107, XC6111~ XC6117Series④ Represents production lot number0 to 9 and A to Z and inverted 0 to 9 and A to Z repeated. (G, I, J, O, Q, W expected.) * ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)■MARKING RULE●SOT-25①②③④SOT-25 (TOP VIEW)6/26XC6101~XC6107, XC6111~XC6117 Series① Represents product series② Represents release delay time MARK RELEASE DELAY TIME PRODUCT SERIES A 3.13msec XC61XxAxxxxx B 25msec XC61XxBxxxxx C 50msec XC61XxCxxxxx D 100msec XC61XxDxxxxx E 200msec XC61XxExxxxx F 400msec XC61XxFxxxxx H 1.6sec XC61XxHxxxxx③ Represents watchdog timeout period MARK WATCHDOG TIMEOUT PERIOD PRODUCT SERIES 0 XC61X6, XC61X7 series XC61Xxx0xxxx 1 6.25msec XC61Xxx1xxxx 2 50msec XC61Xxx2xxxx 3 100msec XC61Xxx3xxxx 4 200msec XC61Xxx4xxxx 5 400msec XC61Xxx5xxxx 6 1.6sec XC61Xxx6xxxx④⑤ Represents detect voltage MARK④ ⑤DETECT VOLTAGE (V)PRODUCT SERIES3 3 3.3 XC61Xxxx33xx 5 0 5.0XC61Xxxx50xx⑥ Represents production lot number0 to 9 and A to Z repeated. (G, I, J, O, Q, W excepted.)* No character inversion used. ** ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)MARK PRODUCT SERIES MARK PRODUCT SERIES 3 XC6101xxxxxx 8 XC6111xxxxxx 4 XC6102xxxxxx 9 XC6112xxxxxx 5 XC6103xxxxxx A XC6113xxxxxx 6 XC6104xxxxxx B XC6114xxxxxx 7 XC6105xxxxxx C XC6115xxxxxx 3 XC6106xxxxxx 8 XC6116xxxxxx 4 XC6107xxxxxx 9 XC6117xxxxxx■MARKING RULE (Continued)●USP-6CUSP-6C (TOP VIEW)7/26XC6101 ~ XC6107, XC6111~ XC6117Series■BLOCK DIAGRAMS●XC6101, XC6111 Series●XC6102, XC6112 Series●XC6103, XC6113 Series8/26XC6101~XC6107, XC6111~XC6117 Series■BLOCK DIAGRAMS (Continued)●XC6107, XC6117 Series●XC6106, XC6116 Series●XC6105, XC6115 Series●XC6104, XC6114 Series9/26XC6101 ~ XC6107, XC6111~ XC6117SeriesPARAMETERSYMBOL RATINGSUNITSV INV SS -0.3 ~ 7.0 VM RBV SS -0.3 ~ V IN +0.3 VInput Voltage WD V SS -0.3 ~ 7.0V Output Current I OUT 20 mACMOS Output RESETB/RESET V SS -0.3 ~ V IN +0.3Output Voltage N-ch Open Drain Output RESETB V SS -0.3 ~ 7.0VSOT-25 250Power Dissipation USP-6C Pd 100mWOperational Temperature Range Topr -40 ~ +85 OCStorage Temperature Range Tstg -40 ~ +125 OC■ABSOLUTE MAXIMUM RATINGSTa = 25O C10/26XC6101~XC6107, XC6111~XC6117 SeriesNOTE:*1: XC6101~XC6107 (with hysteresis) *2: XC6111~XC6117 (without hysteresis)*3: ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111) *4: V DF(T): Setting detect voltage*5: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).PARAMETERSYMBOLCONDITIONSMIN.TYP .MAX. UNITS CIRCUITDetect Voltage V DFL V DFHV DF(T)× 0.98V DF(T) V DF(T)× 1.02 V 1 Hysteresis Range XC6101~XC6107 (*1) V HYS V DF × 0.02V DF × 0.05 V DF× 0.08 V 1Hysteresis Range XC6111~XC6117 (*2) V HYS 0 V DF × 0.001 V DFx 0.01V 1V IN =V DF(T)×0.9V - 5 11 V IN =V DF(T)×1.1V- 10 16 XC61X1/XC61X2/XC61X3XC61X4/XC61X5 (*3)(The MRB & the WD Pin: No connection) V IN =6.0V - 1218 V IN =V DF(T)×0.9V - 4 10 V IN =V DF(T)×1.1V - 8 14 Supply Current I SS XC61X6/XC61X7 (*3)(The MRB Pin: No connection)V IN = 6.0V - 1016 µA 2Operating Voltage V IN 1.0 - 6.0 V 1VIN = 1.0V 0.15 0.5 -V IN =2.0V (V DFL(T)> 2.0V) 2.0 2.5 - V IN =3.0V (V DFL(T) >3.0V) 3.0 3.5 -N-ch.V DS = 0.5V V IN =4.0V (V DFL(T) >4.0V) 3.5 4.0 - 3 V DFL Output Current (RESETB) I RBOUTCMOS,P-chV DS = 0.5V V IN = 6.0V - - 1.1 -0.8 mA 4 N-chV DS = 0.5VV IN =6.0V 4.4 4.9 - 3V IN =1.0V - - 0.08 - 0.02 V IN =2.0V (V DFH(T)> 2.0V)- - 0.50 - 0.30 V IN =3.0V (V DFH(T)>3.0V)- - 0.75 - 0.55V DFHOutput Current (RESET) I ROUT P-ch. V DS = 0.5V V IN =4.0V (V DFH(T)>4.0V)- - 0.95 - 0.75 mA 4Temperature Characteristics △V DF / △Topr ・V DF -40OC < Topr < 85 O C - +100 - ppm / O C12 3.13 5 13 25 3825 50 75 60 100 140 120 200 280 240 400 560Release Delay Time(V DF <1.8V)T DR Time until V IN is increased from1.0V to2.0Vand attains to the release time level,and the Reset output pin inverts.960 1600 2240 ms 5 2 3.13 5 13 25 38 25 50 7560 100 140 120 200 280 240 400 560 Release Delay Time(V DF >1.9V)T DRTime until V IN is increased from1.0V to (V DF x1.1V) and attains to the releasetime level,and the Reset output pin inverts. 960 1600 2240ms 5 Detect Delay Time T DFTime until V IN is decreased from 6.0V to 1.0V and attains to the detect voltage level, and the Reset output pin detectswhile the WD pin left opened.- 3 30 µs 5V DFL /V DFH CMOS Output Leak CurrentI LEAK V IN =6.0V, RESETB=6.0V (V DFL ) V IN =6.0V, RESET=0V (V DFH )- 0.01 - µA 3V DFL N-ch Open DrainOutput Leak CurrentI LEAKV IN =6.0V, RESETB=6.0V-0.010.10µA 3■ELECTRICAL CHARACTERISTICS●XC6101~XC6107, XC6111~XC6117 SeriesTa = 25O CSeriesPARAMETERSYMBOL CONDITIONS MIN.TYP . MAX. UNITS CIRCUIT3.13 6.25 9.38 25 50 7560 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF <1.8V)T WDTime until V IN increases form1.0V to2.0V andthe Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 3.13 6.25 9.38 25 50 75 60 100 140 120 200 280240 400 560 Watchdog Timeout Period (V DF >1.9V)T WDTime until V IN increases form1.0V to (V DF x1.1V)and the Reset output pin is released to go into the detection state. (WD=V SS )960 1600 2240 ms 6 WatchdogMinimum Pulse Width T WDIN V IN =6.0V,Apply pulse from 6.0V to 0Vto the WD pin. 300 - - ns 7 Watchdog High Level VoltageV WDH V IN =V DF x 1.1V ~ 6.0V V IN x 0.7- 6 V 7 Watchdog Low Level Voltage V WDL V IN =V DF x 1.1V ~ 6.0V0 - V IN x 0.3 V 7 V IN =6.0V, V WD =6.0V (Avg. when peak )- 12 19Watchdog Input Current I WD V IN =6.0V, V WD =0V (Avg. when peak) - 19 -12 -µA 8 Watchdog Input ResistanceR WDV IN =6.0V, V WD =0V, R WD =V IN / |I WD |315500880k Ω8PARAMETERSYMBOL CONDITIONS MIN.TYP . MAX.UNITS CIRCUITMRBHigh Level VoltageV MRH V IN =V DF x1.1V ~ 6.0V 1.4 - V IN 9MRBLow Level VoltageV MRL V IN =V DF x1.1V ~ 6.0V-0.35 V9MRBPull-up Resistance R MR V IN =6.0V, MRB=0V, R MR =V IN / |I MRB | 1.6 2.4 3.0 M Ω 10 MRB Minimum Pulse Width (*3) XC6101~XC6105 XC6111~XC6115 T MRINV IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin 2.8 - -MRB Minimum Pulse Width (*4) XC6106, XC6107 XC6116, XC6117T MRIN V IN =6.0V,Apply pulse from 6.0V to 0V tothe MRB pin1.2 - -µs11●XC6101 ~ XC6103, XC6106 ~ XC6107, XC6111 ~ XC6113, XC6116 ~ XC6117 Series NOTE:*1: V DF(T): Setting detect voltage *2: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected). *3: Watchdog function is available. *4: Watchdog function is not available.Ta = 25O CTa = 25O C ■ELECTRICAL CHARACTERISTICS (Continued)●XC6101~XC6105, XC6111~XC6115 Series■OPERATIONAL EXPLANATIONThe XC6101~XC6107, XC6111~XC6117 series compare, using the error amplifier, the voltage of the internal voltage reference source with the voltage divided by R1, R2 and R3 connected to the V IN pin. The resulting output signal from the error amplifier activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the V IN pin voltage gradually falls and finally reaches the detect voltage, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type ICs.<RESETB / RESET Pin Output Signal>* V DFL (RESETB) type - output signal: Low when detected.The RESETB pin output goes from high to low whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESETB pin remains low for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the RESETB pin output remains low for the release delay time (T DR), and thereafter the RESET pin outputs high level signal. * V DFH (RESET) type – output signal: High when detected.The RESET pin output goes from low to high whenever the V IN pin voltage falls below the detect voltage, or whenever the MRB pin is driven from high to low. The RESET pin remains high for the release delay time (T DR) after the V IN pin voltage reaches the release voltage. If neither rising nor falling signals are applied to the WD pin within the watchdog timeout period, the V OUT pin output remains high for the release delay time (T DR), and thereafter the RESET pin outputs low level signal.<Hysteresis>When the internal comparator output is high, the NMOS transistor connected in parallel to R3 is turned ON, activating the hysteresis circuit. The difference between the release and detect voltages represents the hysteresis range, as shown by the following calculations:V DF (detect voltage) = (R1+R2+R3) x Vref(R2+R3)V DR (release voltage) = (R1+R2) x Vref(R2)V HYS (hysteresis range)=V DR-V DF (V)V DR > V DF* Detect voltage (V DF) includes conditions of both V DFL (low when detected) and V DFH (high when detected).* Please refer to the block diagrams for R1, R2, R3 and Vref.Hysteresis range is selectable from V DF x 0.05V (XC6101~XC6107) or V DF x 0.001V (XC6111~XC6117).<Watchdog (WD) Pin>The XC6101~XC6107, XC6111~XC6117 series use a watchdog timer to detect malfunction or “runaway” of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB/RESET pin output maintains the detection state for the release delay time (T DR), and thereafter the RESET/RESETB pin output returns to the release state (Please refer to the FUNCTION CHART). The timer in the watchdog is then restarted. Six watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 6.25msec.<MRB Pin>Using the MRB pin input, the RESET/RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low in the case of the V DFL type ICs, and the RESET pin output goes from low to high in the case of the V DFH type. Even after the MRB pin is driven back high, the RESET/RESETB pin output maintains the detection state for the release delay time (T DR). Since the MRB pin is internally pulled up to the V IN pin voltage level, leave the MRB pin open if unused (Please refer to the FUNCTION CHART). A diode, which is an input protection element, is connected between the MRB pin and V IN pin. Therefore, if the MRB pin is applied voltage that exceeds V IN, the current will flow to V IN through the diode. Please use this IC within the stated maximum ratings (V SS -0.3 ~ V IN+0.3) on the MRB pin.<Release Delay Time>Release delay time (T DR) is the time that elapses from when the V IN pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WD pin, until the RESET/RESETB pin output is released from the detection state. Seven release delay time (T DR) watchdog timeout period settings are available in 1.6sec, 400msec, 200msec, 100msec, 50msec, 25msec, 3.13msec.<Detect Delay Time>Detect Delay Time (T DF) is the time that elapses from when the V IN pin voltage falls to the detect voltage until the RESET/ RESETB pin output goes into the detection state.Series■TIMING CHARTS●CMOS Output●T DF (CMOS Output)VINVDFL LevelGNDVIN Level VDFL Level GNDVIN x 0.1V■NOTES ON USE1. Please use this IC within the stated maximum ratings. Operation beyond these limits may cause degrading or permanent damage to the device.2. When a resistor is connected between the V IN pin and the input, the V IN voltage drops while the IC is operating and a malfunction may occur as a result of the IC’s through current. For the CMOS output products, the V IN voltage drops while the IC is operating and malfunction may occur as a result of the IC’s output current. Please be careful with using the XC6111~XC6117 series (without hysteresis).3. In order to stabilize the IC’s operations, please ensure that the V IN pin’s input frequency’s rise and fall times are more than 1 µ sec/V.4. Noise at the power supply may cause a malfunction of the watchdog operation or the circuit. In such case, please strength the line between V IN and the GND pin and connect about 0.22µF of a capacitor between the V IN pin and the GND pin.5. Protecting against a malfunction while the watchdog time out period, an ignoring time (no reaction time) occurs to the rise and fall times. Referring to the figure below, the ignoring time (no reaction time) lasts for 900µsec at maximum.GNDGNDGNDVIN Pin Wave FormWD Pin Wave FormRESETB Pin Wave Form (VDFL)SeriesPIN NAMELOGIC CONDITIONSH V IN >V DF +V HYS V IN L V IN <V DF H MRB>1.40V MRBL MRB<0.35V H When keeping W D >V WDH more than T WD L When keeping W D <V WDL more than T WD L → H V WDL → V WDH , T WDIN >300nsec WDH → L V WDH →V WDH , T WDIN >300nsecV IN MRB WD RESETB (*2) H HH LRepeat detect and release (H →L →H)H OpenH L → HH H or Open H → L H HLL *1 LV IN MRB WD RESETB (*3) H HH LRepeat detect and release (L →H →L)H OpenH L → HH H or Open H → L L HLL *1 HV IN WD RESETB (*2) RESET (*3) H HH L Repeat detect and release (H →L →H)Repeat detect and release (L →H →L)H OpenH L → HH H → L H L HL*1 L HV IN MRB RESETB (*2)RESET (*3)H H or Open H LH LL L H■PIN LOGIC CONDITIONSNOTE:*1: If only “V DF ” is indicated, it represents both V DFL (low when detected) and V DFH (high when detected).*2: For the details of each parameter, please see the electrical characteristics. V DF : Detect VoltageV HYS : Hysteresis RangeV WDH : WD High Level Voltage V WDL: WD Low Level Voltage T WDIN : WD Pulse Width T WD : WD Timeout Period■FUNCTION CHART●XC6103/XC61113 Series●XC6104/XC61114, XC6105/XC6115 Series●XC6106/XC61116, XC6107/XC6117 Series●XC6101/XC61111, XC6102/6112 Series*1: Including all logic of WD (WD=H, L, L →H, H →L, OPEN). *2: When the RESETB is High, the circuit is in the release state. When the RESETB is Low, the circuit is in the detection state. *3: When the RESET is High, the circuit is in the release state. When the RESET is Low, the circuit is in the detection state.■TEST CIRCUITSCircuit 1Circuit 2Circuit 3Circuit 4Series ■TEST CIRCUITS (Continued)Circuit 5Circuit 6Circuit 7■TEST CIRCUITS (Continued)Circuit 8Circuit 9Circuit 10Circuit 11Series■TYPICAL PERFORMANCE CHARACTERISTICS(1.1) Supply Current vs. Input Voltage(1.2) Supply Current vs. Input Voltage■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(2) Detect, Release Voltage vs. Ambient Temperature(1.2) Supply Current vs. Input Voltage (Continued)Series■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (3-1) Output Voltage vs. Input Voltage (V DFL ) (3.1) Detect, Release Voltage vs. Input Voltage (V DFL )(3.2) Detect, Release Voltage vs. Input Voltage (V DFH )■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(4) N-ch Driver Output Current vs. V DSSeries(6) P-ch Driver Output Current vs. Input Voltage 1■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(8) Release Delay Time vs. Ambient Temperature(7) P-ch Driver Output Current vs. Input Voltage 2■TYPICAL PERFORMANCE CHARACTERISTICS (Continued) (10) Release Delay Time vs. Input Voltage(11) Watchdog Timeout Period vs. Input VoltageSeries■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)(14) MRB Low Level Voltage vs. Ambient Temperature(15) MRB High Level Voltage vs. Ambient Temperature* ‘X’ represents both ‘0’ and ‘1’. (ex. XC61X1⇒XC6101 and XC6111)。

标准草案-电力一次设备用电子标签技术规范

.T/XXX X X X X X X X X X X X标准T/XXX XXXX-YYYY电力一次设备用电子标签技术规范(草案)Technical specification for electrical tagof primary power equipmentXXXX - XX - XX发布XXXX - XX - XX实施目次前言 (II)1范围 (3)2规范性引用文件 (3)3术语定义 (4)4符号、代号及缩略语 (6)4.1符号 (6)4.2代号 (6)4.3缩略语 (6)5种类及规格要求 (7)5.1封装形式 (7)5.2材质及外观要求 (7)5.3尺寸要求 (8)5.4安装要求 (8)5.5功能要求 (8)6技术要求 (8)6.1电子标签物理性能 (8)6.2电子标签电气性能 (10)6.3 通信规约 (11)7试验要求 (11)7.1测试的一般要求 (11)7.2直观检测 (11)7.3条码印制质量测试 (11)7.4物理性能试验 (12)7.5电性能试验 (13)7.6通信试验 (14)7.7 通信规约试验 (15)8检验规则 (15)8.1全性能检验 (15)8.2抽样验收检验 (15)附录 A (17)索引 (19)编制说明 (20)前言为规范电力一次设备用电子标签要求,提高电力一次设备在运维检修、资产管理过程中的质量与效率,有效支撑电力设备智能运检业务管理,特编制标准。

本标准规定了电力一次设备用电子标签技术适用范围、术语和定义、标签种类及规格要求、技术要求、试验要求、检验规则等内容,提出了电力一次设备用电子标签在检验、安装和使用过程中的具体要求,为电子标签在电力一次设备上进行标准化应用提供技术依据。

本标准由xxxxxx提出并解释。

本标准由xxxxxx归口。

本标准起草单位:国网江苏省电力公司电力科学研究院、国网江苏省电力公司检修分公司、中科院-南京宽带无线移动通信研发中心、北京智芯微电子科技有限公司、南京华乘电气科技有限公司本标准主要起草人:xxxxx。

ccccccccccccccccccxxxxxxxxxxxxx

国际IP地址和国际化域名是使用Internet网及其相联的网络系统,运行Internet网必然涉及的十分重要的概念,不掌握它用户无法进行通信。

在In-ternet网的发展基础上,人们于1982年提出了一种IP协议,此协议要求参加Internet网的网节点要有一个统一规定格式的地址,这个地址称为符合IP协议的地址,缩称为IP地址。

什么是IP地址的物理含义?1.它是人们在环球网上的通信地址IP地址是人们在全世界环球网和中国教育与科研计算机网上使用的唯一、明确、供全世界识别的通邮地址。

2.它是Internet网运行的通用地址在Internet网上,每个网络和每一台计算机都被唯一分配一个IP地址,这个IP地址在整个网络(Internet网)中是唯一的。

3.它是全球认可有的通用地址格式在Internet上通信必须有一个32位的二进制地址,采用这种32位(bit)的通用地址格式,才能保证Internet网成为向全世界开放的、可互操作的通信系统。

它是全球认可的计算机网络标识方法,通过这种方法,才能正确标识信息的收与发。

4.它是微机、服务器和路由器的端口地址a在Internet网上,任何一台服务器和路由器的每一个端口必须有一个IP地址。

5.它是运行TCP/IP协议的唯一标识符TCP/IP协议与Novell的网络协议的区别就在于它是上层协议,这是在Internet发展中形成的。

不管下层是什么拓扑结构,以太网、TokenRing、passing令牌传递网、FDDI网上的地址,全要统一在这上层IP地址上。

任何网要与Internet网挂联上,只要用IP地址就可以了。

一句话,您的微机上网后,IP地址是唯一的。

IP地址的格式和分类1.IP地址的格式IP地址有二进制格式和十进制格式;十进制格式是由二进制翻译过去的。

用十进制表示,是为了使用户和网管人员便于使用和掌握。

二进制的IP地址共有32位,例如:10000011,01101011,00000011,00011000。

HQxxxx-xxx-3AA中文资料

HQ SeriesSPECIFICATIONS STANDARD*SPECIAL ELECTRICALCenter Frequency (Fc)100 to 1000 Mhz80 to 1400 MHz 3dB Relative Bandwidth (% of FC) 4 to 40 4 to 50 Number of Sections Available 3 to 8 2 to 10 Nominal Impedance50 Ohms50 to 75 Ohms Maximum Insertion Loss See Curve See Curve Maximum VSWR 1.5/1 1.3/1 Attenuation in the Stopband See Graph See GraphMaximum Input Power (Average)(Watts to10,000 ft.)500 x 3dB BW (MHz)(Loss Factor)(Fc MHz)See StandardMaximum Input Power (Peak)(Watts to10,000 ft.)300 x 3dB BW (MHz)Fc (MHz)2,000ENVIRONMENTALShock15 G's25 G's Vibration 5 G's10 G's Humidity90% relative100% relativeINSERTION LOSS:The Maximum Insertion Loss at center frequency is equal to :LF x (N + 0.5) / % 3 dB BW + 0.2 Where:LF= Loss Factor, N= Number of Sections% 3dB BW:3dB BW (MHz) x 100divided byCenter Frequency (MHz) Example:A 3 section HQ with a center frequency of 400 MHz and a 3dB BW of 40 MHz would have,1.5 x 3.5 / 10 = 5.25 / 10 = 0.525 0.525 + 0.2 = 0.8 dBConnectors Available on HQ Series:Lark Code Type C DIM.Inches & MMLarkCodeType C DIM.Inches & MMA SMA JACK.800 & 20.3G N JACK 1.625 & 41.3B SMA PLUG.855 & 22.5H N PLUG 1.585 & 40.3C TNC JACK 1.350 & 34.3L SOLDER MPINAXIAL.625 & 15.9D TNC PLUG 1.280 & 32.5*M SOLDER PINRADIAL.625 & 15.9E BNC JACK 1.350 & 34.3S SPECIALF BNC PLUG 1.280 & 32.5*Not recommended for use with this series.LENGTH:The approximate length of a Lark HQ series filter can be determined by the formula:( 0.5 N + 2 / %BW ) x LC = LWhere N is the number of sections used, % BW is:3dB BW (MHz) x 100divided byCENTER FREQUENCY (MHz)LC is the length constant at the specified center frequency, L is the dimension between theconnectors; C1 and C2 are the connector lengths as shown above. All of the length information given here is approximate. Exact length specifications must be quoted by the factory. If a special length is needed,please submit all of your requirements - both electrical and mechanical. This will enable Lark Engineering to quote the optimum design for your application.Example:A 3 section HQ with a center frequency of 400 MHz a 3dB BW of 40 MHz and SMA jack input and output connectors would be:(1.5 + 0.2) x 1.38 = 2.35 + C1 + C2In most cases, the L dimension is rounded to the nearest 1/4 inch which in this instance would be 2.25inches and the O.A.L. is:2.25 + .800 + .800 =3.85 inches.To convert inches to millimeters multiply x 25.40.Lark Engineering HQ SERIES元器件交易网STOPBAND ATTENUATIONThe graph on the following pages defines the normal specification limits on attenuation Lark bandpass filter series HP, HQ, SF, and SM. The minimum level of attenuation in dB is shown as a "number of 3dB bandwidths from center frequency".Since the frequency characteristics vary for differing bandwidths, it is necessary to establishspecifications for each bandwidth of filter. The different graphs represent various 3dB percentage bandwidths. Intermediate values should be interpolated. The 3dB percentage bandwidth is defined asfollows:STOPATT5.HTM元器件交易网As the 3dB bandwidth is exactly 10% of the center frequency, the answer can be read directly from the 10% graph. Using the 5 section curve at the point -1.5 (255 MHz) we find the minimum level of attenuation is 36dB. At +1.6 (348 MHz) the minimum level of attenuation is 48dB.For special requirements, please contact our Application Engineering Department.STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPATT5.HTM元器件交易网STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPBAND ATTENUATION。

JCTXXX-XXXX 夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜

JCTXXX-XXXX 夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜Q 34JC中华人民共和国建材行业标准JC/T XXX-XXXX夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜Polyvinyl butyral interlayer (PVB) for laminated glass(送审稿)xxxx xxxx 公布xxxx xxxx实施xxxx xxxx 公布JC/TXXX-XXXX前言本标准由中国建筑材料检验认证中心提出。

本标准由全国建筑标准化技术委员会归口。

本标准由中国建筑材料检验认证中心负责起草本标准的参加起草单位:XXXXXXXXXXXXXXXXXXX 本标准的要紧起草人:XXXXXXXXXXXXXXXXXXXXXXJC/ TXXX-XXXX夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜1 范畴本标准规定了夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜的产品分类、技术要求、试验方法、检验规则、包装、运输和贮存等要求。

本标准适用于建筑夹层玻璃、汽车夹层玻璃、机车夹层玻璃、船舶夹层玻璃、防弹夹层玻璃等夹层玻璃用聚乙烯醇缩丁醛(PVB)中间膜。

PE T膜、PU胶片等可参照执行。

2 规范性引用文件下列文件中的条款通过本标准的引用而成为本标准的条款。

凡是注日期的引用文件,其随后所有的修改单(不包括勘误的内容)或修订版均不适用于本部分,然而,鼓舞本部分达成协议的各方研究是否可使用这些文件的最新版本。

凡是不注日期的引用文件,其最新版本适用于本部分。

GB/T 1039 塑料力学性能试验方法总则GB/T 1040 塑料拉伸试验方法GB/T 2680-1994, 建筑玻璃可见光透射比、太阳光直截了当透射比、太阳能总透射比、紫外线透射比及有关窗玻璃参数的试验GB/T2828 计数抽样检验程序GB/T 5137.2-2002汽车安全玻璃试验方法GJB 1258A-2005 聚乙烯醇缩定醛中间膜HG/T3862-2006塑料黄色指数试验方法3 术语和定义下列术语和定义适用于本标准。

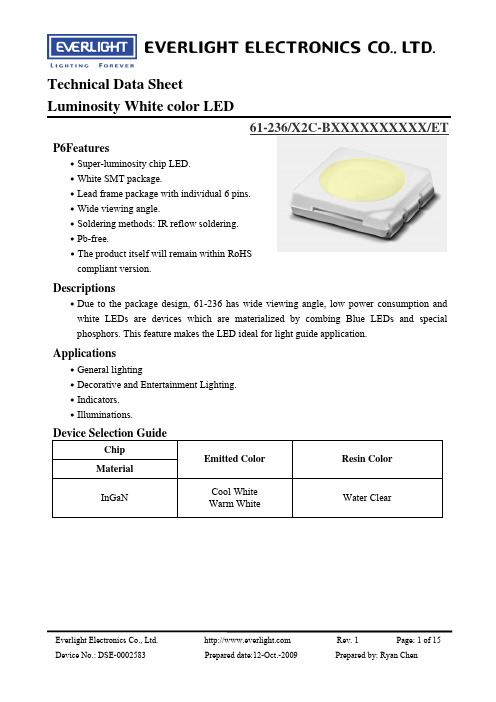

61-236-X2C-BXXXXXXXXX-2T

Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETP6Features․Super-luminosity chip LED. ․White SMT package.․Lead frame package with individual 6 pins. ․Wide viewing angle.․Soldering methods: IR reflow soldering. ․Pb-free.․The product itself will remain within RoHS compliant version.Descriptions․Due to the package design, 61-236 has wide viewing angle, low power consumption and white LEDs are devices which are materialized by combing Blue LEDs and special phosphors. This feature makes the LED ideal for light guide application.Applications․General lighting․Decorative and Entertainment Lighting. ․Indicators.․Illuminations.Device Selection GuideChip Material Emitted Color Resin ColorInGaNCool White Warm WhiteWater ClearTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETProduct Number Explanation61–236 / X 2 C - B XX XX XX XX XX / 2TNotesTable of Color Rendering IndexSymbolDescriptionM CRI (min) : 60 L CRI (min) : 70 K CRI (min) : 80 H CRI (min) : 90Example:61-236/L2C-B45564F2GB2/2TCRI Min=70 CCT 4500K~5650K IV 5200mcd~6200mcdVF2.9V~3.6VBin Group of Forward VoltageBin Group of Max. Luminous Intensity Bin Group of Min. Luminous Intensity Max. Color temperature Min. Color temperatureBin Code of Color Rendering IndexTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET Mass Production listProduct CRIminCCT(K)I V(mcd)MinI V(mcd)MaxΦ(lm)Typ.61-236/L2C-B50632FAGB2/2T 70 5000K~6300K 5000 6000 15.4061-236/L2C-B50634E2FB2/2T70 5000K~6300K 4200 5200 12.94 61-236/L2C-B50638D6EB2/2T70 5000K~6300K 3600 4600 10.47 61-236/L2C-B45564F2GB2/2T70 4500K~5650K 5200 6200 15.96 61-236/L2C-B45566E4FB2/2T70 4500K~5650K 4400 5400 13.41 61-236/L2C-B4556AE8EB2/2T 70 4500K~5650K 3800 4800 10.8561-236/L2C-B28324E2FB2/2T70 2850K~3250K 4200 5200 13.16 61-236/L2C-B28328D6EB2/2T70 2850K~3250K 3600 4600 11.05 61-236/L2C-B2832AD8DB2/2T 70 2850K~3250K 2800 3800 8.95Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETPackage Outline Dimensions1234Polarity56Recommend solding pad design+++ Note: The tolerances unless mentioned is ±0.1mm, Unit = mmTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET Absolute Maximum Ratings (Ta=25℃)*1Parameter Symbol RatingUnit Reverse Voltage*1R 5 VForward Current*1I F 30 mA Peak Forward Current(Duty 1/10 @ 1KHZ)*1I FP 100 mA Power Dissipation*1Pd 110 mW Electrostatic Discharge(HBM)*1ESD 1000 V Operating Temperature Topr -40 ~ +85 ℃Storage Temperature Tstg -40~ +90 ℃Soldering Temperature Tsol Reflow Soldering : 260 ℃for 10 sec. Hand Soldering : 350 ℃for 3 sec.* 1. The value are based on 1 die performanceElectro-Optical Characteristics (Ta=25)℃Parameter SymbolMin.Typ.Max.UnitsCondition Viewing Angle*12θ1/2 ----- 120 ----- deg I F=20mA*2Reverse Current I R ----- ----- 50 μA V R*2=5V*1 When three LED dies are operated simultaneously.*2 For each die.Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET Bin Range of Luminous Intensity*1Bin Code Min. Max. Unit Condition8C26002800AD280030002D300032004D320034006D340036008D36003800AE380040002E400042004E42004400mcd I F=20*2mA 6E440046008E46004800AF480050002F500052004F520054006F540056008F560058002G600062004G620064006G64006600Notes:1. *1 When three LED dies are operated simultaneously.2. *2 For each die.3. Tolerance of Luminous Intensity ±11%Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETBin Range of Forward Voltage*1UnitConditionMax.CodeGroup BinMin.34 2.7 2.835 2.8 2.936 2.9 337 3 3.138 3.1 3.2V I F=20*2mA GB239 3.2 3.340 3.3 3.441 3.4 3.542 3.5 3.643 3.6 3.7Notes:1. *1 When three LED dies are operated simultaneously.2. *2 For each die.3. Tolerance of Forward Voltage ±0.05V4. Forward Voltage rank is the average forward voltage of three diesTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET*1*21. Tolerance of Chromaticity Coordinates: ±0.012. *1 When three LED dies are operated simultaneously.3. *2 For each die.Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET The C.I.E. 1931 Chromaticity DiagramTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETTypical Electro-Optical Characteristics Curves10Forward Voltage V -(Volts)F10R e l a t i v e l u m i n o u s i n t e n s i t y (%)Ambient Temperature T (°C -60110-20-400206040)a 100801001000Ambient TemperatureAmbient Temperature T (°C a)Forward Current Derating Curve10F o r w a r d C u r r e n t02030I (m A )5040F 0.70.80.91.01Ta=25°Wavelength λ(nm)100F o r w a r d C u r r e n t 1020I (m A )305040FSpectrum Distribution0.10.30.50.20.40.6Radiation DiagramTa=25°Forward Current 1010I (mA)FRelative Luminous Intensity vs.Ta=25°Forward Current Forward Current vs.Forward VoltageRelative Luminous Intensity vs.R e l a t i v e l u m i n o u s i n t e n s i t y (%)R e l a t i v e l u m i n o u s i n t e n s i t y (%)Technical Data SheetNote:Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET Carrier Tape Dimensions: Loaded Quantity 800 pcs Per ReelTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ETReliability Test Items and ConditionsThe reliability of products shall be satisfied with items listed below. Confidence level :90% LTPD :10%No. ItemsTest Condition TestHours/CyclesSample Size Ac/Re1 Reflow SolderingTemp. : 260±5℃℃Max. 10sec. 6 Min. 22 PCS. 0/1 2 Temperature Cycle H : +100 15min ℃∫ 5 minL : -40 15min ℃ 300 Cycles 22 PCS. 0/1 3 Thermal Shock H : +100 5min ℃∫ 10 secL : -10 5min ℃ 300 Cycles22 PCS.0/1 4 High Temperature Storage Temp. : 100℃ 1000 Hrs. 22 PCS. 0/1 5 Low Temperature Storage Temp. : -40℃ 1000 Hrs. 22 PCS. 0/1 6 DC Operating Life I F *2 = 20 mA1000 Hrs.22 PCS.0/1 7High Temperature / HighHumidity85/ 85%RH ℃ 1000 Hrs. 22 PCS.0/1*2 For each dieTechnical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET Precautions for Use1. Over-current-proofCustomer must apply resistors for protection, otherwise slight voltage shift will cause big current change ( Burn out will happen ).2. Storage2.1 Do not open moisture proof bag before the products are ready to use.℃2.2 Before opening the package: The LEDs should be kept at 30 or less and 90%RH or less.2.3 After opening the package: The LED's floor life are 168 hours under 30℃or less and 60% RHor less. If unused LEDs remain, it should be stored in moisture proof packages.2.4 If the moisture absorbent material (silica gel) has faded away or the LEDs have exceeded thestorage time, baking treatment should be performed using the following conditions.℃Baking treatment : 60±5 for 24 hours.3. Soldering Condition3.1 Pb-free solder temperature profile1~5 °C / Sec.3.2 Reflow soldering should not be done more than two times.3.3 When soldering, do not put stress on the LEDs during heating.3.4 After soldering, do not warp the circuit board.Technical Data SheetLuminosity White color LED61-236/X2C-BXXXXXXXXXX/ET 4. Soldering Iron℃Each terminal is to go to the tip of soldering iron temperature less than 350 for 3 seconds within once in less than the soldering iron capacity 25W. Leave two seconds and more intervals, and do soldering of each terminal. Be careful because the damage of the product is often started at the time of the hand solder.5. RepairingRepair should not be done after the LEDs have been soldered. When repairing is unavoidable, a double-head soldering iron should be used (as below figure). It should be confirmed beforehand。

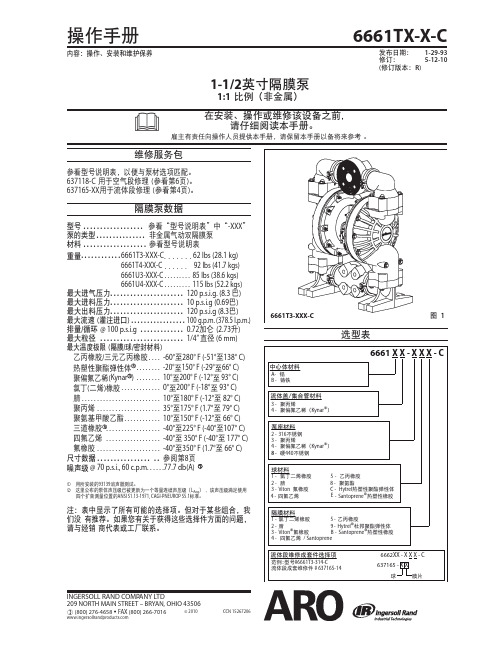

6661TX-XXX-C-ZH

内容:操作、安装和维护保养

1-1/2英寸隔膜泵

1:1 比例(非金属)

6661TX-X-C

发布日期: 1-29-93

修订:

5-12-10

(修订版本:R)

在安装、操作或维修该设备之前, 请仔细阅读本手册。

雇主有责任向操作人员提供本手册,请保留本手册以备将来参考 。

维修服务包

参看型号说明表,以便与泵材选项匹配。 637118-C 用于空气段修理 (参看第6页)。 637165-XX用于流体段修理 (参看第4页)。

(800) 276-4658 y FAX (800) 266-7016

© 2010

CCN 15267206

操作和安全预防措施

阅读、理解并遵照此处信息操作,以避免出现伤害或财产损失。

过高的空气压力 静电火花

危险物料 危险压力

警告 过高的空气压力。可能造成泵的损坏、人身伤 害 或财产损失。 y 切勿超过泵体铭牌上说明的最大进气口压力。 y 确保物料软管和其他零部件能够承受由该泵产生的压 力。 检查所有软管进行,是否有损坏或磨损。确保分配

警告 切记 注意

= 危险或不安全的作业,可能会造成严重的 人身伤害、死亡或重大财产损失。

= 危险或不安全的作业,可能会造成较轻的 人身伤害、产品或财产损失。

= 重要的安装、操作和维护保养信息。

第 2 页,共 8 页

6661TX-X-C (zh) Nhomakorabea一般说明

在空气压力很低时,ARO隔膜泵甚至也能泵送大量物料, 而且物料相容性的选择范围很广。请参看型号和选项表。 ARO隔膜泵具有抗失速设计和空气马达/流体段模块化的特 点。 气动双隔膜泵利用气室中的压差,交替造成流体室内的吸 入压力和流体正压力,同时球形单向阀确保流体正流量。 当施加空气压力时,泵的循环开始,它会连续泵送物料不 断满足需求。循环将建立并维持管路压力,一旦达到最高 管路压力(分配装置关闭),循环停止,并根据需要,重 新进行泵送。。

世界业余无线电呼号前缀图

世界业余无线电呼号前缀图文字版:在业余无线电中,呼号的前两位字母或数字代表一个国家的某一地区,通常一个国家会将本国的业余无线电呼号划分为多个分区,我国的呼号前两位为BA到BZ这里收录了世界各国的呼号前缀。

供查询参考。

2A—2Z Uni ted Kin gdom (英国)3A-3A Monaco(xx)3B—3B Mauritius (毛里求斯)3C—3C Equatorial Gui nea (赤道几内亚)3DA—3DM Swaziland (斯威士兰)3DN—3DZ Fij(i xx)3E—3F Panama( xx)3G—3G Chile( xx)3H—3U China( xx)3V—3V Tunisia( xx)3W—3W Vietnam( xx)3X—3X Guinea( xx)3Y—3Y Norway( xx)3Z—3Z Poland( xx)4A—4C Mexico( xx)4D—41 Philippines (菲律宾)4J—4K Azerbaijan (阿塞拜疆)4L-4L Georgia(xx)4M —4M Venezuela (委内瑞拉)4N —4O Serbia and Montenegro (塞尔维亚和黑山)4P—4S Sri Lank(a 斯里兰卡)4T—4T Peru(xx)4U —4U United Nations (联合国)4V—4V Haiti (海地)4W —4W Timor Leste (东帝汶)4X—4X Israel(xx)4Y—4Y In ter natio nal Civil Aviatio n Orga ni zation (国际民用航空组织)4Z—4Z Israel(xx)5A—5A Libya(xx)5B—5B Cyprus(xx)5C—5G Morocco(xx)5H—51 Tanzania (坦桑尼亚)5J—5K Colombia (哥伦比亚)5L—5M Liberia(xx)5N—5O Nigeria(xx)5P—5Q Denmark(xx)5R—5S Madagasca(r 马达加斯加)5T—5T Mauritania (毛里塔尼亚)5U-5U Niger(xx)5V—5V Togo( xx)5W—5W Samoa( xx)5X—5X Uganda( xx)5Y—5Z Kenya( xx)6A—6B Egypt( xx)6C—6C Syria( xx)6D—6J Mexico( xx)6K—6N Korea( xx)6O—6O Somalia( xx)6P—6S Pakista n (巴基斯坦)6T—6U Sudan( xx)6V—6W Senega(l xx)6X—6X Madagasca(r 马达加斯加) 6Y—6Y Jamaica( xx)6Z—6Z Liberia( xx)7A—71 In do nesia (印度尼西亚)7J—7N Japan( xx)7O—70 Yemen (也门)7P—7P Lesotho (莱索托)7Q-7Q Malawi(xx)7R—7R Algeria (阿尔及利亚)7S-7S Sweden(xx)7T—7Y Algeria (阿尔及利亚)7Z—7Z Saudi Arabia (沙特阿拉伯)8A—81 In do nesia (印度尼西亚)8J—8N Japan(xx)8O—80 Botswana (博茨瓦纳)8P—8P Barbados (巴巴多斯)8Q—8Q Maldives (马尔代夫)8R—8R Guyana(xx)8S—8S Sweden(xx)8T—8Y India(xx)8Z—8Z Saudi Arabia (沙特阿拉伯)9A—9A Croatia(xx)9B—9D Iran(xx)9E—9F Ethiopia (埃塞俄比亚)9G—9G Ghana (加纳)9H—9H Malta(xx)9I—9J Zambia(xx)9K—9K Kuwait(xx)9L—9L Sierra Leo ne(塞拉里昂)9M —9M Malaysia (马来西亚)9N—9N Nepal( xx)9O—9T Democratic Republic of Cong(o 刚果民主共和国) 9U—9U Burundi( xx)9V—9V Singapore (新加坡)9W —9W Malaysia (马来西亚)9X—9X Rwanda( xx)9Y—9Z Trin idad and Tobago (特立尼达和多巴哥)A2 —A2 Botswana (博茨瓦纳)A3—A3 Tonga( xx)A4—A4 Oman( xx)A5—A5 Bhutan( xx)A6—A6 United Arab Emirates (阿拉伯联合酋长国)A7—A7 Qatar( xx)A8—A8 Liberia( xx)A9—A9 Bahrain( xx)AA—AL Un ited States of America (美国)AM —AO Spain( xx)AP—AS Pakista n (巴基斯坦)AT—AW India( xx)AX—AX Australia (澳大利亚)AY—AZ Argentine (阿根廷)BA—BZ China( xx)C2—C2 Nauru (瑙鲁)C3—C3 Andorra( xx)C4—C4 Cyprus( xx)C5—C5 Gambia( xx)C6—C6 Bahamas( xx)C7—C7 World Meteorological Organization (世界气象组织) C8— C9 Mozambique (莫桑比克)CA—CE Chile( xx)CF—CK Canada( xx)CL—CM Cuba( xx)CN—CN Morocco( xx)CO—CO Cuba( xx)CP—CP Bolivia( xx)CQ—CU Portuga(l xx)CV—CX Uruguay( xx)CY—CZ Canad(a xx)D2—D3 Angola( xx)D4 —D4 Cape Verde (佛得角)D5-D5 Liberia(xx)D6-D6 Comoros(xx)D7-D9 Korea(xx)DA-DR Germany(xx)DS-DT Korea(xx)DU—DZ Philippines (菲律宾)E2-E2 Thailand(xx)E3- E3 Eritrea (厄立特里亚)E4—E4 Palestine (巴勒斯坦)E5—E5 Cook Island(s 库克群岛)EA—EH Spain(xx)EI—EJ Ireland(xx)EK—EK Armenia(xx)EL—EL Liberia(xx)EM—EO Ukraine(xx)EP—EQ Iran(xx)ER— ER Moldova (摩尔多瓦)ES—ES Estonia(xx)ET—ET Ethiopia (埃塞俄比亚)EU—EW Belarus(xx)EX—EX Kyrgyzsta(n 吉嗉?顾固梗EY— EY Tajikista n (塔吉克斯坦)EZ— EZ Turkmenistan (土库曼斯坦)FA—FZ France(xx)GA—GZ Uni ted Kin gdom (英国)H2—H2 Cyprus(xx)H3—H3 Panama(xx)H4 —H4 Solo mon Isla nds (所罗门群岛)H6—H7 Nicaragua (尼加拉瓜)H8—H9 Panama(xx)HA—HA Hungary(xx)HB—HB Switzerland (瑞士)HC—HD Ecuado(r 厄瓜多尔)HE—HE Switzerland (瑞士)HF—HF Poland(xx)HG—HG Hungary(xx)HH—HH Haiti (海地)HI —HI Domi nican Republic (多米尼加共和国)HJ— HK Colombia (哥伦比亚)HL—HL Korea(xx)HM —HM Democratic People ' s Republic of Ko朝鲜)HN—HN Iraq (伊拉克)HO-HP Panama(xx)HQ—HR Ho nduras (洪都拉斯)HS-HS Thailand(xx)HT—HT Nicaragua (尼加拉瓜)HU—HU El Salvado(r 厄瓜多尔)HV—HV Vatican(xx)HW—HY France(xx)HZ—HZ Saudi Arabia(沙特阿拉伯)IA—IZ Italy(xx)J2—J2 Djibouti(xx)J3—J3 Gre nada (格林纳达)J4—J4 Greece(xx)J5—J5 Guinea-Bissa(u 几内亚-比绍)J6—J6 Sai nt Lucia(圣卢西亚)J7—J7 Dominica (多米尼加)J8—J8 Saint Vincent and the Grenadine(s 圣文森特和格林纳丁斯)JA—JS Japa(n xx)JT—JV Mongolia(xx)JW—JX Norway(xx)JY—JY Jorda n (约旦)JZ— JZ Indon esia(印度尼西亚)KA—KZ Un ited States of America (美国)L2 —L9 Argentine (阿根廷)LA—LN Norway(xx)LO— LW Argentine (阿根廷)LX— LX Luxembourg (卢森堡)LY—LY Lithuania (立陶宛)LZ— LZ Bulgaria (保加利亚)MA —MZ United Kingdom (英国)NA—NZ Uni ted States of America (美国)OA—OC Peru(xx)OD—OD Lebanon(xx)OE—OE Austria(xx)OF—OJ Finland(xx)OK—OL Czech Republi(c 捷克共和国)OM —OM Slovakia (斯洛伐克)ON—OT Belgium(xx)OU—OZ Denmark(xx)P2—P2 Papua New Guine(a 巴布亚新几内亚)P3—P3 Cyprus(xx)P4—P4 Aruba(xx)P5—P9 Democratic Peoples Republic ofK朝鲜aPA—PI Netherlands (荷兰)PJ— PJ Netherla nds An tilles (荷属安的列斯群岛)PK— PO I ndonesia (印度尼西亚)PP—PY Brazi(l xx)PZ—PZ Surinam(xx)RA—RZ Russi(a xx)S2—S3 Ban gladesh(孟加拉国)55— S5 Slove nia (斯洛文尼亚)56— S6 Si ngapore(新加坡)57— S7 Seychelle(s 塞舌尔)58— S8 South Africa (南非)59— S9 Sao Tome and Princip(e 圣多美和普林西比)SA—SM Sweden(xx)SN—SR Poland(xx)SSA-SSM Egyp(txx)SSN-STZ Suda (n xx)SU—SU Egyp(t xx)SV—SZ Greece(xx)T2 —T2 Tuvalu (图瓦卢)T3—T3 Kiribati (基里巴斯)T4—T4 Cuba(xx)T5-T5 Somalia( xx)T6—T6 Afghanistan (阿富汗)T7—T7 San Mari no (圣马力诺)T8—T8 Palau( xx)T9—T9 Bosnia and Herzegovin(a 波斯尼亚和黑塞哥维那) TA—TC Turkey( xx)TD—TD Guatemala (危地马拉)TE—TE Costa Ric(a 哥斯达黎加)TF—TF Iceland( xx)TG— TG Guatemala (危地马拉)TH—TH France( xx)TI —TI Costa Rica(哥斯达黎加)TJ—TJ Cameroon( xx)TK—TK France( xx)TL—TL Central African Republi(c 中非共和国)TM—TM France( xx)TN—TN Congo (刚果)TO—TQ France( xx)TR—TR Gabon( xx)TS—TS Tunisia( xx)TT—TT Chad( xx)TU—TU Cote d ' lv(科特迪瓦)TV-TX France(xx)TY—TY Benin(xx)TZ—TZ Mali (马里)UA—Ul Russia(xx)UJ— UM Uzbekistan (乌兹别克斯坦)UN—UQ Kazakhsta n (哈萨克斯坦)UR—UZ Ukraine(xx)V2 —V2 Antigua and Barbuda (安提瓜和巴布达)V3—V3 Belize(xx)V4 —V4 Sai nt Kitts and Nevis(圣基茨和尼维斯)V5—V5 Namibia(xx)V6 —V6 Micronesia (密克罗尼西亚)V7 —V7 Marshall Islands (马绍尔群岛)V8—V8 Brunei(xx)VA—VG Canada(xx)VH— VN Australia (澳大利亚)VO—VO Canada(xx)VP— VQ United Kingdom (英国)VR— VR Hong Ko ng(中国香港)VS— VS United Kingdom (英国)VT-VW India(xx)VX-VY Canada( xx)VZ— VZ Australia (澳大利亚)WA —WZ United States (美国) XA—XI Mexico( xx)XJ—XO Canada( xx)XP—XP Denmark( xx)XQ—XR Chile( xx)XS—XS China( xx)XT—XT Burkina Fas(o 布基纳法索) XU—XU Cambodia( xx)XV—XV Vietnam( xx)XW—XW Laos( xx)XX—XX Macau( xxxx)XY—XZ Myanmar( xx)Y2—Y9 Germany( xx)YA—YA Afghanistan (阿富汗) YB—YH In do nesia(印度尼西亚) Yl—YI Iraq (伊拉克)YJ-YJ Van uatu (瓦努阿图) YK—YK Syria( xx)YL-YL Latvia(xx)YM-YM Turkey(xx)YN—YN Nicaragua (尼加拉瓜)YO-YR Romania(xx)YS—YS El Salvado(r 厄瓜多尔)YT—YU Serbia and Montenegro (塞尔维亚和黑山)YV—YY Venezuel(a 委内瑞拉)YZ— YZ Serbia and Mon te negro (塞尔维亚和黑山)Z2 —Z2 Zimbabwe (津巴布韦)Z3—Z3 Maced onia (马其顿)ZA—ZA Albania (阿尔巴尼亚)ZB— ZJ Un ited Kin gdom (英国)ZK— ZM New Zealand (新西兰)ZN—ZO United Kingdom (英国)ZP—ZP Paraguay(xx)ZQ—ZQ Uni ted Kin gdom (英国)ZR— ZU South Africa (南非)ZV—ZZ Brazi(l xx)2A—2Z Uni ted Kin gdom (英国)3A—3A Monaco(xx)3B—3B Mauritius (毛里求斯)3C—3C Equatorial Gui nea (赤道几内亚)3DA—3DM Swaziland (斯威士兰)3DN—3DZ Fij(i xx)3E—3F Panama( xx)3G—3G Chile( xx)3H—3U China( xx)3V—3V Tunisia( xx)3W—3W Vietnam( xx)3X—3X Guinea( xx)3Y—3Y Norway( xx)3Z—3Z Poland( xx)4A—4C Mexico( xx)4D—41 Philippines (菲律宾)4J—4K Azerbaijan (阿塞拜疆)4L—4L Georgia( xx)4M —4M Venezuela (委内瑞拉)4N —4O Serbia and Montenegro (塞尔维亚和黑山) 4P—4S Sri Lank(a 斯里兰卡)4T—4T Peru( xx)4U —4U United Nations (联合国)4V—4V Haiti (海地)4W —4W Timor Leste (东帝汶)4X-4X Israel(xx)4Y—4Y In ter natio nal Civil Aviatio n Orga ni zation (国际民用航空组织) 4Z—4Z Israel( xx)5A—5A Libya( xx)5B—5B Cyprus( xx)5C—5G Morocco( xx)5H—51 Tanzania (坦桑尼亚)5J—5K Colombia (哥伦比亚)5L—5M Liberia( xx)5N—5O Nigeria( xx)5P—5Q Denmark( xx)5R—5S Madagasca(r 马达加斯加)5T—5T Mauritania (毛里塔尼亚)5U—5U Niger( xx)5V—5V Togo( xx)5W—5W Samoa( xx)5X—5X Uganda( xx)5Y—5Z Kenya( xx)6A—6B Egypt( xx)6C—6C Syria( xx)6D-6J Mexico(xx)6K-6N Korea(xx)6O-6O Somalia(xx)6P—6S Pakista n (巴基斯坦)6T-6U Sudan(xx)6V—6W Senega(l xx)6X—6X Madagasca(r 马达加斯加)6Y—6Y Jamaica(xx)6Z—6Z Liberia(xx)7A—71 In do nesia (印度尼西亚)7J—7N Japan(xx)7O—70 Yemen (也门)7P—7P Lesotho (莱索托)7Q—7Q Malawi (xx)7R—7R Algeria (阿尔及利亚)7S—7S Sweden(xx)7T—7Y Algeria (阿尔及利亚)7Z—7Z Saudi Arabia (沙特阿拉伯)8A—8I In do nesia (印度尼西亚)8J—8N Japan(xx)80—80 Botswana (博茨瓦纳)8P—8P Barbados (巴巴多斯)8Q—8Q Maldives (马尔代夫)8R—8R Guyana( xx)8S—8S Sweden( xx)8T—8Y India( xx)8Z—8Z Saudi Arabia (沙特阿拉伯)9A—9A Croatia( xx)9B—9D Iran( xx)9E—9F Ethiopia (埃塞俄比亚)9G—9G Ghana (加纳)9H—9H Malta( xx)9I—9J Zambia( xx)9K—9K Kuwait( xx)9L—9L Sierra Leo ne(塞拉里昂)9M —9M Malaysia (马来西亚)9N—9N Nepal( xx)9O—9T Democratic Republic of Cong(o 刚果民主共和国) 9U—9U Burundi( xx)9V—9V Singapore (新加坡)9W —9W Malaysia (马来西亚)9X—9X Rwanda( xx)9Y—9Z Trin idad and Tobago (特立尼达和多巴哥) A2 —A2 Botswana (博茨瓦纳)A3—A3 Tonga( xx)A4—A4 Oman( xx)A5—A5 Bhutan( xx)A6—A6 United Arab Emirates (阿拉伯联合酋长国) A7—A7 Qatar( xx)A8—A8 Liberia( xx)A9—A9 Bahrain( xx)AA—AL Un ited States of America (美国) AM—AO Spain( xx)AP—AS Pakista n (巴基斯坦)AT—AW India( xx)AX—AX Australia (澳大利亚)AY—AZ Argentine (阿根廷)BA—BZ China( xx)C2—C2 Nauru (瑙鲁)C3—C3 Andorra( xx)C4—C4 Cyprus( xx)C5—C5 Gambia( xx)C6—C6 Bahamas( xx)C7—C7 World Meteorological Organization (世界气象组织) C8— C9 Mozambique (莫桑比克)CA—CE Chile( xx)CF—CK Canada( xx)CL—CM Cuba( xx)CN—CN Morocco( xx)CO—CO Cuba( xx)CP—CP Bolivia( xx)CQ—CU Portuga(l xx)CV—CX Uruguay( xx)CY—CZ Canad(a xx)D2—D3 Angola( xx)D4 —D4 Cape Verde (佛得角)D5—D5 Liberia( xx)D6—D6 Comoros( xx)D7—D9 Korea( xx)DA—DR Germany( xx)DS—DT Korea( xx)DU—DZ Philippines (菲律宾)E2—E2 Thailand( xx)E3- E3 Eritrea (厄立特里亚)E4- E4 Palestine (巴勒斯坦)E5-E5 Cook Island(s 库克群岛)EA- EH Spain( xx)EI- EJ Ireland( xx)EK- EK Armenia( xx)EL- EL Liberia( xx)EM- EO Ukraine( xx)EP- EQ Iran( xx)ER— ER Moldova (摩尔多瓦)ES- ES Estonia( xx)ET—ET Ethiopia (埃塞俄比亚) EU—EW Belarus (xx)EX—EX Kyrgyzsta(n 吉嗉?顾固梗? EY— EY Tajikista n (塔吉克斯坦)EZ— EZ Turkmenistan (土库曼斯坦) FA—FZ France( xx)GA—GZ Uni ted Kin gdom (英国)H2—H2 Cyprus( xx)H3—H3 Panama( xx)H4 —H4 Solo mon Isla nds (所罗门群岛) H6—H7 Nicaragua (尼加拉瓜)H8-H9 Panama(xx)HA-HA Hungary(xx)HB—HB Switzerland (瑞士)HC-HD Ecuado(r 厄瓜多尔)HE—HE Switzerland (瑞士)HF—HF Poland(xx)HG—HG Hungary(xx)HH—HH Haiti (海地)HI —HI Domi nican Republic (多米尼加共和国)HJ— HK Colombia (哥伦比亚)HL—HL Korea(xx)HM —HM Democratic People ' s Republic of !(朝鲜)HN—HN Iraq (伊拉克)HO—HP Panama(xx)HQ—HR Ho nduras (洪都拉斯)HS—HS Thailand(xx)HT—HT Nicaragua (尼加拉瓜)HU—HU El Salvador 厄瓜多尔)HV—HV Vatican(xx)HW—HY France(xx)HZ—HZ Saudi Arabia(沙特阿拉伯)IA-IZ Italy(xx)J2-J2 Djibouti(xx)J3—J3 Gre nada (格林纳达)J4-J4 Greece(xx)J5—J5 Guinea-Bissa(u 几内亚-比绍)J6—J6 Sai nt Lucia(圣卢西亚)J7—J7 Dominica (多米尼加)J8—J8 Saint Vincent and the Grenadine(s 圣文森特和格林纳丁斯)JA—JS Japa(n xx)JT—JV Mongolia(xx)JW—JX Norway(xx)JY—JY Jorda n (约旦)JZ— JZ Indon esia(印度尼西亚)KA—KZ Un ited States of America (美国)L2 —L9 Argentine (阿根廷)LA—LN Norway(xx)LO— LW Argentine (阿根廷)LX— LX Luxembourg (卢森堡)LY—LY Lithuania (立陶宛)LZ- LZ Bulgaria (保加利亚)MA —MZ United Kingdom (英国)NA—NZ Un ited States of America (美国)OA-OC Peru(xx)OD—OD Lebanon( xx)OE—OE Austria( xx)OF—OJ Finland( xx)OK—OL Czech Republi(c 捷克共和国)OM —OM Slovakia (斯洛伐克)ON—OT Belgium( xx)OU—OZ Denmark( xx)P2—P2 Papua New Guine(a 巴布亚新几内亚)P3—P3 Cyprus( xx)P4—P4 Aruba( xx)P5—P9 Democratic People ' s Republic ofK朝鲜a PA—PI Netherlands (荷兰)PJ— PJ Netherla nds An tilles (荷属安的列斯群岛) PK— PO I ndonesia (印度尼西亚)PP—PY Brazi(l xx)PZ—PZ Surinam( xx)RA—RZ Russi(a xx)S2—S3 Ban gladesh(孟加拉国)S5— S5 Slove nia (斯洛文尼亚)S6— S6 Si ngapore(新加坡)S7-S7 Seychelle(s 塞舌尔)58— S8 South Africa (南非)59— S9 Sao Tome and Princip(e 圣多美和普林西比)SA—SM Sweden(xx)SN—SR Poland(xx)SSA-SSM Egyp(txx)SSN-STZ Suda (n xx)SU—SU Egyp(t xx)SV—SZ Greece(xx)T2 —T2 Tuvalu (图瓦卢)T3—T3 Kiribati (基里巴斯)T4—T4 Cuba(xx)T5—T5 Somalia(xx)T6—T6 Afghanistan (阿富汗)T7—T7 San Mari no (圣马力诺)T8—T8 Palau(xx)T9—T9 Bosnia and Herzegovin(a 波斯尼亚和黑塞哥维那)TA—TC Turkey(xx)TD—TD Guatemala (危地马拉)TE—TE Costa Ric(a 哥斯达黎加)TF-TF Iceland(xx)TG— TG Guatemala (危地马拉)TH-TH France(xx)TI —TI Costa Rica(哥斯达黎加)TJ—TJ Cameroon( xx)TK—TK France( xx)TL—TL Central African Republi(c 中非共和国) TM—TM France( xx)TN—TN Congo (刚果)TO—TQ France( xx)TR—TR Gabon( xx)TS—TS Tunisia( xx)TT—TT Chad( xx)TU—TU Cote d ' lvo(科特迪瓦)TV—TX France( xx)TY—TY Benin( xx)TZ—TZ Mali (马里)UA—UI Russia( xx)UJ— UM Uzbekistan (乌兹别克斯坦)UN—UQ Kazakhsta n (哈萨克斯坦)UR—UZ Ukraine( xx)V2 —V2 Antigua and Barbuda (安提瓜和巴布达)V3-V3 Belize(xx)V4 —V4 Sai nt Kitts and Nevis(圣基茨和尼维斯)V5—V5 Namibia(xx)V6 —V6 Micronesia (密克罗尼西亚)V7 —V7 Marshall Islands (马绍尔群岛)V8—V8 Brunei(xx)VA—VG Canada(xx)VH— VN Australia (澳大利亚)VO—VO Canada(xx)VP— VQ United Kingdom (英国)VR— VR Hong Ko ng(中国香港)VS— VS United Kingdom (英国)VT—VW India(xx)VX—VY Canada(xx)VZ— VZ Australia (澳大利亚)WA —WZ United States (美国)XA—XI Mexico(xx)XJ—XO Canada(xx)XP—XP Denmark(xx)XQ—XR Chile(xx)XS-XS China(xx)XT-XT Burkina Fas(o 布基纳法索)XU-XU Cambodia(xx)XV-XV Vietnam(xx)XW-XW Laos(xx)XX-XX Macau(xxxx)XY-XZ Myanmar(xx)Y2-Y9 Germany(xx)YA—YA Afghanistan (阿富汗)YB—YH In do nesia(印度尼西亚)YI—YI Iraq (伊拉克)YJ-YJ Van uatu (瓦努阿图)YK—YK Syria(xx)YL—YL Latvia(xx)YM—YM Turkey(xx)YN—YN Nicaragua (尼加拉瓜)YO—YR Romania(xx)YS—YS El Salvado(r 厄瓜多尔)YT—YU Serbia and Montenegro (塞尔维亚和黑山)YV—YY Venezuel(a 委内瑞拉)YZ— YZ Serbia and Mon te negro (塞尔维亚和黑山)Z2 —Z2 Zimbabwe (津巴布韦)Z3—Z3 Maced onia (马其顿)ZA—ZA Albania (阿尔巴尼亚)ZB— ZJ Un ited Kin gdom (英国)ZK— ZM New Zealand (新西兰)ZN—ZO United Kingdom (英国)ZP—ZP Paraguay(xx)ZQ—ZQ Uni ted Kin gdom (英国)ZR— ZU South Africa (南非)ZV—ZZ Brazi(l xx)。

T8XX-XXXH中文资料

®1/11Table 1: Main FeaturesDESCRIPTIONAvailable either in through-hole or surface-mount packages, the BTA08, BTB08 and T8 triac series is suitable for general purpose AC switching. They can be used as an ON/OFF function in applica-tions such as static relays, heating regulation, in-duction motor starting circuits... or for phase control operation in light dimmers, motor speed controllers,...The snubberless versions (BTA/BTB...W and T8series) are specially recommended for use on inductive loads, thanks to their high commutation performances.Logic level versions are designed to interface directly with low power drivers such as microcontrollers.By using an internal ceramic pad, the BTA series provides voltage insulated tab (rated at 2500V RMS ) complying with UL standards (file ref.:E81734).Symbol Value Unit I T(RMS)8A V DRM /V RRM 600 and 800V I GT (Q 1)5 to 50mABTA08, BTB08 and T8 Series8A TRIAC SREV. 6February 2006SNUBBERLESS™, LOGIC LEVEL & STANDARDTable 2: Order CodesPart Number Marking BTA08-xxxxxRG See page table 8 onpage 10BTB08-xxxxxRG T8xx-xxxG T8xx-xxxH T8xx-xxxBBTA08, BTB08 and T8 Series2/11Table 3: Absolute Maximum Ratings Tables 4: Electrical Characteristics (T j = 25°C, unless otherwise specified)■SNUBBERLESS and Logic Level (3 quadrants)Symbol ParameterValue Unit I T(RMS)RMS on-state current (full sine wave)IPAK/D 2PAK/DPAK/TO-220AB T c = 110°C 8ATO-220AB Ins.T c = 100°C I TSM Non repetitive surge peak on-state current (full cycle, T j initial = 25°C) F = 50 Hz t = 20 ms 80A F = 60 Hz t = 16.7 ms84I ²t I ²t Value for fusingt p = 10 ms 36A ²s dI/dt Critical rate of rise of on-state cur-rent I G = 2 x I GT , t r ≤ 100 ns F = 120 Hz T j = 125°C 50A/µs I GM Peak gate currentt p = 20 µsT j = 125°C 4A P G(AV)Average gate power dissipation T j = 125°C1W T stg T jStorage junction temperature rangeOperating junction temperature range- 40 to + 150- 40 to + 125°CSymbol Test ConditionsQuad-rantT8BTA08 / BTB08Unit T810T835TW SW CW BW I GT (1)V D = 12 V R L = 30 ΩI - II -III MAX.10355103550mA V GT I - II - III MAX.1.3V V GD V D = V DRM R L = 3.3 k ΩT j = 125°C I - II - IIIMIN.0.2V I H (2)I T = 100 mA MAX.153510153550mA I L I G = 1.2 I GTI - III MAX.255010255070mAII306015306080dV/dt (2)V D = 67 %V DRM gate open T j = 125°CMIN.4040020404001000V/µs (dI/dt)c (2)(dV/dt)c = 0.1 V/µs T j = 125°CMIN.5.4- 3.5 5.4--A/ms(dV/dt)c = 10 V/µs T j = 125°C2.8- 1.5 2.98--Without snubber T j = 125°C- 4.5-- 4.57BTA08, BTB08 and T8 Series3/11■Standard (4 quadrants)Table 5: Static Characteristics Table 6: Thermal resistance Symbol Test ConditionsQuadrant BTA08 / BTB08Unit C B I GT (1)V D = 12 V R L = 30 ΩI - II - III IV MAX.255050100mA V GT ALL MAX. 1.3V V GD V D = V DRM R L = 3.3 k Ω T j = 125°C ALLMIN.0.2V I H (2)I T = 500 mA MAX.2550mA I L I G = 1.2 I GTI - III - IVMAX.4050mA II80100dV/dt (2)V D = 67 %V DRM gate open T j = 125°CMIN.200400V/µs (dV/dt)c (2)(dI/dt)c = 5.3 A/ms T j = 125°C MIN.510V/µsSymbol Test ConditionsValueUnit V T (2)I TM = 11 A t p = 380 µs T j = 25°C MAX. 1.55V V to (2)Threshold voltage T j = 125°C MAX.0.85V R d (2)Dynamic resistance T j = 125°C MAX.50m ΩI DRM I RRMV DRM = V RRMT j = 25°C MAX.5µA T j = 125°C1mANote 1: minimum I GT is guaranted at 5% of I GT max.Note 2: for both polarities of A2 referenced to A1.Symbol ParameterValue Unit R th(j-c)Junction to case (AC)IPAK / D 2PAK / DPAK / TO-220AB 1.6°C/WTO-220AB Insulated 2.5R th(j-a)Junction to ambientS = 1 cm ²D 2PAK 45°C/WS = 0.5 cm ²DPAK70TO-220AB / TO-220AB Insulated 60IPAK100S = Copper surface under tab.BTA08, BTB08 and T8 Series4/11Figure 1: Maximum power dissipation versus RMS on-state current (full cycle)Figure 2: RMS on-state current versus case temperature (full cycle)Figure 3: RMS on-state current versus ambient temperature (printed circuit board FR4, copper thickness: 35µm) (full cycle)Figure 4: Relative variation of thermal impedance versus pulse durationFigure 5: On-state characteristics (maximum values)Figure 6: Surge peak on-state current versus number of cyclesBTA08, BTB08 and T8 Series5/11Figure 7: Non-repetitive surge peak on-state current for a sinusoidal pulse with width t p < 10 ms and corresponding value of I 2tFigure 8: Relative variation of gate trigger current, holding current and latching current versus junction temperature (typical values)Figure 9: Relative variation of critical rate of decrease of main current versus (dV/dt)c (typical values) (Snubberless & L ogic level types)Figure 10: Relative variation of critical rate of decrease of main current versus (dV/dt)c (typical values) (Standard types)Figure 11: Relative variation of critical rate of decrease of main current versus junction temperatureFigure 12: DPAK and D 2P AK Thermal resistance junction to ambient versus copper surface under tab (printed circuit board FR4, copper thickness:35µm)BTA08, BTB08 and T8 Series6/11Figure 13: Ordering Information Scheme (BTA08 and BTB08 series)Figure 14: Ordering Information Scheme (T8 series)Table 7: Product SelectorPart NumberVoltage (xxx)Sensitivity Type Package 600 V 800 V BTA/BTB08-xxxB X X 50 mA Standard TO-220AB BTA/BTB08-xxxBW X X 50 mA Snubberless TO-220AB BTA/BTB08-xxxC X X 25 mAStandard TO-220AB BTA/BTB08-xxxCW X X 35 mA Snubberless TO-220AB BTA/BTB08-xxxSW X X 10 mA Logic level TO-220AB BTA/BTB08-xxxTW X X 5 mA Logic Level TO-220AB T810-xxxG X X 10 mA Logic Level D2PAK T810-xxxH X X 10 mA Logic Level IPAK T835-xxxB X X 35 mA Snubberless DPAK T835-xxxG X X 35 mA Snubberless D 2PAK T835-xxxHXX35 mASnubberlessIPAKBTB: non insulated TO-220AB packageBTA08, BTB08 and T8 Series Figure 15: D2PAK Package Mechanical DataFigure 16: D2PAK Foot Print Dimensions(in millimeters)7/11BTA08, BTB08 and T8 SeriesFigure 17: DPAK Package Mechanical DataFigure 18: DPAK Foot Print Dimensions (in millimeters)8/11BTA08, BTB08 and T8 Series9/11BTA08, BTB08 and T8 Series10/11In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: .Table 8: Ordering InformationOrdering type Marking Package Weight Base qtyDelivery modeBTA/BTB08-xxxyzRGBTA/BTB08-xxxyzTO-220AB 2.3 g 50Tube T8yy-xxxG T8yyxx D 2PAK 1.5 g 50Tube T8yy-xxxG-TR T8yyxx 1000Tape & reel T8yy-xxxB T8yyxx DPAK 0.3 g 75Tube T8yy-xxxB-TR T8yyxx 2500Tape & reel T8yy-xxxHT8yyxxIPAK0.4 g75TubeNote: xxx = voltage, yy = sensitivity, z = typeTable 9: Revision HistoryDate Revision Description of ChangesApr-20025A Last update.13-Feb-20066TO-220AB delivery mode changed from bulk to tube.ECOPACK statement added.元器件交易网BTA08, BTB08 and T8 Series Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequencesof use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is grantedby implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subjectto change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are notauthorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics.All other names are the property of their respective owners© 2006 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America11/11。

gxxx

)% )% )% ) × 10−3 ) × 10−3 )% )% )% )% × 10−3 CL=95%

searched for

searched for

Page 3

Created: 9/15/2006 13:44

Citation: W.-M. Yao et al. (Particle Data Group), J. Phys. G 33, 1 (2006) (URL: )

Page 4

Created: 9/15/2006 13:44

Citation: W.-M. Yao et al. (Particle Data G (URL: )

Additional Z Bosons Z SM with standard couplings Mass m > 825 GeV, CL = 95% (p p direct search) Mass m > 1500 GeV, CL = 95% (electroweak fit) ZLR of SU(2)L ×SU(2)R ×U(1) (with gL = gR ) Mass m > 630 GeV, CL = 95% (p p direct search) Mass m > 860 GeV, CL = 95% (electroweak fit) Zχ of SO(10) → SU(5)×U(1)χ (with gχ =e /cosθW ) Mass m > 690 GeV, CL = 95% (p p direct search) Mass m > 781 GeV, CL = 95% (electroweak fit) Zψ of E6 → SO(10)×U(1)ψ (with gψ =e /cosθW ) Mass m > 675 GeV, CL = 95% (p p direct search) Mass m > 366 GeV, CL = 95% (electroweak fit) Zη of E6 → SU(3)×SU(2)×U(1)×U(1)η (with gη =e /cosθW ) Mass m > 720 GeV, CL = 95% (p p direct search) Mass m > 619 GeV, CL = 95% (electroweak fit) Scalar Leptoquarks Mass m > 256 GeV, CL = 95% (1st generation, pair prod.) Mass m > 298 GeV, CL = 95% (1st gener., single prod.) Mass m > 202 GeV, CL = 95% (2nd gener., pair prod.) Mass m > 73 GeV, CL = 95% (2nd gener., single prod.) Mass m > 148 GeV, CL = 95% (3rd gener., pair prod.) (See the Particle Listings for assumptions on leptoquark quantum numbers and branching fractions.)

XXXX年第10期节能-中国质量认证中心

节能、环保、节水产品认证企业获证信息公告二〇一〇年第十期(总第143期)节能产品认证获证企业信息:计算机制造商:Dell Inc.获证规格型号:P06S: 19.5VDC 3.34A[电源适配器: LA65NS0-00、HA65NE0-00、HA65NE1-00、HA65NS1-00、HA65NS2-00、DA65NS3-00、HA65NS5-00、FA65NE0-00、FA65NE1-00、LA65NE0-01、LA65NE1-01、FA065LS1-01、LA65NS2-01, 输出: 19.5VDC, 3.34A]证书编号:CQC生效日期:2010-03-10有效期至:2012-08-18品牌:戴尔/Dell制造商:Hewlett-Packard pany获证规格型号:HSTNN-Q78C-4 18.5VDC,3.5A or19VDC,4.74A (电源适配器:Series PPP009H,PPP009D,Series HSTNN-LA15 输出:18.5VDC,3.5A;Series PPP012L-E,SeriesPPP012H-S,Series HSTNN-LA13,PPP012D-S 输出:19VDC,4.74A;Series PPP009L-E,输出:19.5VDC,3.33A 或18.5VDC,3.5A)证书编号:CQC生效日期:2010-03-11有效期至:2013-03-11品牌:hp制造商:Hewlett-Packard pany获证规格型号:HSTNN-Q78C-3 18.5VDC,3.5A or19VDC,4.74A (电源适配器:Series PPP009H,PPP009D,Series HSTNN-LA15 输出:18.5VDC,3.5A;Series PPP012L-E,SeriesPPP012H-S,Series HSTNN-LA13,PPP012D-S 输出:19VDC,4.74A;Series PPP009L-E,输出:19.5VDC,3.33A 或18.5VDC,3.5A)证书编号:CQC生效日期:2010-03-11有效期至:2013-03-11品牌:hp制造商:万利达集团XX获证规格型号:PC-1801V、PC-1801T、PC-1801、PC-91801、PC-91802、PC-91803、PC-91804、PC-91805、PC-1802、PC-1803、PC-1804、PC-1805、PC-1802T、PC-1803T、PC-1804T、PC-1805T、PC-1802V、PC-1803V、PC-1804V、PC-1805V:12VDC 4A 48W(电源适配器:XKD-Z4000IC12.0-48W 输入:100-240VAC 50/60Hz 1.2A MAX, 输出:12VDC 4.0A)证书编号:CQC生效日期:2010-03-11有效期至:2013-03-11品牌:万利达制造商:XX星网锐捷通讯股份XX获证规格型号:升腾MI945XX系列("M"代表15寸一体机机壳;"I945"代表硬件平台为Intel 945方案;"XX"为数字"0~9",大写字母"A~Z"及""(空格)的组合,代表系统软件和客户编号。

XC6106C620资料