PHP79NQ08LT中文资料

LM79M05CH资料

LM79Microprocessor System Hardware MonitorGeneral DescriptionThe LM79is a highly integrated Data Acquisition system for hardware monitoring of servers,Personal Computers,or virtually any microprocessor based system.In a PC,the LM79can be used to monitor power supply voltages,tem-peratures,and fan speeds.Actual values for these inputs can be read at any time,and programmable WATCHDOG limits in the LM79activate a fully programmable and maskable interrupt system with two outputs.The LM79has an on-chip temperature sensor,5positive analog inputs,two inverting inputs (for monitoring negative voltages),and an 8-bit ADC.An input is provided for the overtemperature outputs of additional temperature sensors and this is linked to the interrupt system.The LM79provides inputs for three fan tachometer outputs.Additional inputs are provided for Chassis Intrusion detection circuits,5VID moni-tor inputs,and chainable interrupt.The LM79provides both ISA and Serial Bus interfaces.A 32-byte auto-increment RAM is provided for POST (Power On Self Test)code stor-age.Compared to the LM78,the LM79has the following differ-ences:•an additional VID input pin•an additional register for device identification •open drain Power Switch Bypass OutputFeaturesn Temperature sensing n 5positive voltage inputsn 2op amps for negative voltage monitoring n 3fan speed monitoring inputsn Input for additional temperature sensors n Chassis Intrusion Detector inputn WATCHDOG comparison of all monitored values n POST code storage RAMnISA and I 2C ™Serial Bus interfacesKey Specificationsj Voltage monitoringaccuracy±1%(max)j Temperature Accuracy−10˚C to +100˚C±3˚C (max)j Supply Voltage 5Vj Supply Current Operating:1mA typ Shutdown:10µA typj ADC Resolution8BitsApplicationsn System Hardware Monitoring for Servers and PCs n Office Electronicsn Electronic Test Equipment and InstrumentationOrdering InformationTemperature Range Package−10˚C ≤T A ≤+100˚COrder Number Device Marking LM79CCVFLM79CCVFVGZ44A #Indicates Active Low (“Not”)Connection DiagramI 2C ®is a registered trademark of the Phillips Corporation.DS100036-2February 2000LM79Microprocessor System Hardware Monitor©2001National Semiconductor Corporation Typical ApplicationDS100036-1L M 79 2Block Diagram Pin DescriptionPin Name(s)PinNumberNumberof PinsType DescriptionIORD11Digital Input An active low standard ISA bus I/O Read Control.IOWR21Digital Input An active low standard ISA bus I/O Write Control.SYSCLK31Digital Input The reference clock for the ISA bus.Typically ranges from4.167MHz to8.33MHz.The minimum clock frequency this input can handle is1Hz. D7–D04–118Digital I/O Bi-directional ISA bus Data lines.D0corresponds to the low order bit,with D7the high order bit.V CC(+5V)121POWER+5V V CC power.Bypass with the parallel combination of10µF(electolytic or tantalum)and0.1µF(ceramic)bypass capacitors.GNDD131GROUND Internally connected to all digital circuitry.SMI__IN141Digital Input Chainable SMI(System Management Interrupt)Input.This is an activelow input that propagates the SMI signal to the SMI output of the LM79via SMI Mask Register Bit6and SMI enable Bit1of the ConfigurationRegister.Chassis Intrusion 151Digital I/O An active high input from an external circuit which latches a ChassisIntrusion event.This line can go high without any clamping actionregardless of the powered state of the LM79.The LM79provides aninternal open drain on this line,controlled by Bit7of NMI Mask Register2,to provide a minimum20ms reset of this line.DS100036-3LM793Pin Description(Continued)Pin Name(s)Pin Number Number of PinsType DescriptionPower Switch Bypass 161Digital OutputAn active low open drain output intended to drive an external P-channel power MOSFET for software power control.FAN3–FAN117–193Digital Input 0V to +5V amplitude fan tachometer input.SCL 201Digital Input Serial Bus Clock.SDA 211Digital I/O Serial Bus bidirectional Data.RESET221Digital OutputMaster Reset,5mA driver (open drain),active low output with a 20ms minimum pulse width.Available when enabeld via Bit 7in SMI Mask Register 2.VID4/NTEST 231Digital Input/Test Output By default an input for the VID4power supply readout for the system processor (Pentium/PRO).Can be programmed as a NAND Treetotem-pole output that provides board-level connectivity testing.Refer to Section 11.0on NAND Tree testing.GNDA 241GROUND Internally connected to all analog circuitry.The ground reference for all analog inputs.−IN6251Analog Input Ground-referred inverting op amp input.Refer to Section 4.0,“ANALOG INPUTS”.FB6261Analog Output Output of inverting op amp for Input 6.Refer to Section 4.0,“ANALOG INPUTS”.FB5271Analog Output Output of inverting op amp for Input 5.Refer to Section 4.0,“ANALOG INPUTS”.−IN5281Analog Input Ground-referred inverting op amp input.Refer to Section 4.0,“ANALOG INPUTS”.IN4–IN029–335Analog Input 0V to 4.096V FSR Analog Inputs.VID3–VID034–374Digital Input Inputs for the power supply readouts for system microprocessor (Pentium/PRO).This value is read in the VID/Fan Divisor Register.BTI 381Digital Input Board Temperature Interrupt driven by O.S.outputs of additionaltemperature sensors such as LM75.Provides internal pull-up of 10k Ω.NMI/IRQ391Digital OutputNon-Maskable Interrupt (open source)/Interrupt Request (open drain).The mode is selected with Bit 5of the Configuration Register and the output is enabled when Bit 2of the Configuration Register is set to 1.The default state is disabled and IRQ mode.SMI 401Digital OutputSystem Management Interrupt (open drain).This output is enabled when Bit 1in the Configuration Register is set to 1.The default state is disabled.A2–A041–433Digital Input The three lowest order bits of the 16-bit ISA Address Bus.A0corresponds to the lowest order bit.CS441Digital InputChip Select input from an external decoder which decodes high order address bits on the ISA Address Bus.This is an active low input.TOTAL PINS44L M 79 4Absolute Maximum Ratings(Notes1,2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Positive Supply Voltage(V CC) 6.5V Voltage on Any Input or Output Pin−0.3V to(V CC+0.3V) Ground Difference(GNDD–GNDA)±300mV Input Current at any Pin(Note3)±5mA Package Input Current(Note3)±20mA Maximum Junction Temperature(T J max)150˚C ESD Susceptibility(Note5)Human Body Model2000V Machine Model175V Soldering InformationPQFP Package(Note6):Vapor Phase(60seconds)215˚C Infrared(15seconds)220˚C Storage Temperature−65˚C to+150˚COperating Ratings(Notes1,2)Operating Temperature Range T MIN≤T A≤T MAX LM79−55˚C≤T A≤+125˚C Specified Temperature Range T MIN≤T A≤T MAX LM79−10˚C≤T A≤+100˚C Junction to Ambient Thermal Resistance(θJA(Note4))NS Package ID:VGZ44A62˚C/W Supply Voltage(V CC)+4.25V to+5.75V Ground Difference(IGNDD–GNDAI)≤100mV V IN Voltage Range−0.05V to V CC+0.05VDC Electrical CharacteristicsThe following specifications apply for+4.25V DC≤V CC≤+5.75V DC,f SYSCLK=8.33MHz,R S=25Ω,unless otherwise speci-fied.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.(Note7)Symbol Parameter Conditions Typical Limits Units(Note8)(Note9)(Limits) POWER SUPPLY CHARACTERISTICSI CC Supply Current Interface Inactive 1.02mA(max)Shutdown Mode10µA TEMPERATURE-TO-DIGITAL CONVERTER CHARACTERISTICSAccuracy−10˚C≤T A≤+100˚C±3˚C(max)Resolution1˚C(min) ANALOG-TO-DIGITAL CONVERTER CHARACTERISTICSResolution(8bits with full-scale at4.096V)16mVTUE Total Unadjusted Error(Note10)±1%(max)DNL Differential Non-Linearity±1LSB(max)PSS Power Supply Sensitivity±1%/Vt C Total Monitoring Cycle Time(Note11) 1.0 1.5sec(max)OP AMP CHARACTERISTICSOutput Current(Sourcing)50µAInput Offset Voltage I OUT=50µA±1mVInput Bias Current±0.1nAPSRR60dBDC Open Loop Gain70dBGain Bandwidth Product500kHz MULTIPLEXER/ADC INPUT CHARACTERISTICSOn Resistance4002000Ω(max)Off Channel Leakage Current±0.1nAInput Current(On Channel Leakage Current)±0.1nAFAN RPM-TO-DIGITAL CONVERTERAccuracy+25˚C≤T A≤+75˚C±10%(max)−10˚C≤T A≤+100˚C±15%(max) Full-scale Count255(max)LM795DC Electrical Characteristics(Continued)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DC ,f SYSCLK =8.33MHz,R S =25Ω,unless otherwise speci-fied.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.(Note 7)SymbolParameterConditionsTypical Limits Units (Note 8)(Note 9)(Limits)FAN RPM-TO-DIGITAL CONVERTERFAN1and FAN2Nominal Input RPM (See Section 6.0)Divisor =1,Fan Count =153(Note 12)8800RPM Divisor =2,Fan Count =153(Note 12)4400RPM Divisor =3,Fan Count =153(Note 12)2200RPM Divisor =4,Fan Count =153(Note 12)1100RPM FAN3Design Nominal Input RPM Fan Count =153(Note 12)4400RPM Internal Clock Frequency+25˚C ≤T A ≤+75˚C 22.520.2kHz (min)24.8kHz (max)−10˚C ≤T A ≤+100˚C22.519.1kHz (min)25.9kHz (max)DIGITAL OUTPUTS (VID4/NTEST,NMI/IRQ)V OUT(1)Logical “1”Output Voltage I OUT =±5.0mA 2.4V (min)V OUT(0)Logical “0”Output Voltage I OUT =±5.0mA 0.4V (max)ISA D0–D7DIGITAL OUTPUTSV OUT(1)Logical “1”Output Voltage I OUT =±12.0mA 2.4V (min)V OUT(0)Logical “0”Output Voltage I OUT =±12.0mA 0.4V (max)I OUTTRI-STATE ®Output CurrentV OUT =0V DC 0.0051µA (max)V OUT =V CC−0.005−1µA (min)OPEN DRAIN DIGITAL OUTPUTS (Power Switch Bypass,SDA,RESET,SMI,Chassis Intrusion)V OUT(0)Logical “0”Output Voltage I OUT =−5.0mA 0.4V (min)I OHHigh Level Output Current V OUT =V CC0.1100µA (max)RESET and Chassis Intrusion 4520ms (min)Pulse WidthDIGITAL INPUTS:SMI__IN,VID0–VID3,VID4/NTEST,BTI,CS,A0,A1,A2,Mode Control and Interface Inputs (IORD,IOWR,SYSCLK),Data Lines (D0–D7),Chassis Intrusion,and Tach Pulse Logic Inputs (FAN1,FAN2,FAN3)V IN(1)Logical “1”Input Voltage 2.0V (min)V IN(0)Logical “0”Input Voltage 0.8V (max)SERIAL BUS DIGITAL INPUTS (SCL,SDA)V IN(1)Logical “1”Input Voltage 0.7x V CC V (min)V IN(0)Logical “0”Input Voltage 0.3x V CCV (max)ALL DIGITAL INPUTS EXCEPT FOR BTII IN(1)Logical “1”Input Current V IN =V CC −0.005−1µA (min)I IN(0)Logical “0”Input Current V IN =0V DC0.0051µA (max)C IN Digital Input Capacitance 20pF BIT DIGITAL INPUTI IN(1)Logical “1”Input Current V IN =V CC 110µA (max)I IN(0)Logical “0”Input Current V IN =0V DC −500−2000µA (max)C INDigital Input Capacitance20pFL M 79 6LM79AC Electrical Characteristics(Note13)The following specifications apply for+4.25V≤V CC≤DC +5.75V DC unless otherwise specified.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.Symbol Parameter Conditions Typical Limits Units(Note8)(Note9)(Limits)ISA TIMING CHARACTERISTICSf SYSCLK System Clock(SYSCLK)Input Frequency8.33MHzt CS(setup)CS Active to IORD/IOWR Active10ns(min)t CS(hold)IORD/IOWR Inactive to CS Inactive10ns(min)t SA(setup)Address Valid to IORD/IOWR Active30ns(min)t SA(hold)IORD/IOWR Inactive to Address Invalid10ns(min)ISA WRITE TIMINGt SDWR(setup)Data Valid to IOWR Active5ns(min)t SDWR(hold)IOWR Inactive to Data Invalid5ns(min)t WR(setup)IOWR Active to Rising Edge of SYSCLK20ns(min) ArrayDS100036-4The delay between consecutive IORD and IOWR pulses should be greater than50ns to ensure that a Power-on reset does notoccur unintentionally.(See Section3.2‘Resets’)FIGURE1.ISA Bus Write Timing Diagram7AC Electrical Characteristics (Note 13)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DC unless otherwise specified.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.(Continued)SymbolParameterConditionsTypical Limits Units (Note 8)(Note 9)(Limits)ISA READ TIMING t SDRD (setup)Data Valid to IORD Inactive 120ns (min)t SDRD (hold)IORD Inactive to Data Invalid5ns (min)t RD (setup)IORD Active to Rising Edge of SYSCLK 20ns (min)t RS (delay)Rising Edge of SYSCLK number 1to Data ValidWith 8.33MHz SYSCLK360ns (max)DS100036-5The delay between consecutive IORD and IOWR pulses should be greater than 50ns to ensure that a Power-on reset does not occur unintentionally.(See Section 3.2‘Resets’)FIGURE 2.ISA Bus Read Timing DiagramL M 79 8AC Electrical Characteristics (Note 13)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DC unless otherwise specified.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.(Continued)SymbolParameterConditionsTypical Limits Units (Note 8)(Note 9)(Limits)SERIAL BUS TIMING CHARACTERISTICS t 1SCL (Clock)Period2.5µs (min)t 2Data In Setup Time to SCL High 100ns (min)t 3Data Out Stable After SCL Low0ns (min)t 4SDA Low Setup Time to SCL Low (start)100ns (min)t 5SDA High Hold Time After SCL High (stop)100ns (min)Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.For guaranteed specifications and test conditions,see the Electrical Characteristics.The guaranteed specifications apply only for the test conditions listed.Some performance characteristics may degrade when the device is not operated under the listed test conditions.Note 2:All voltages are measured with respect to GND,unless otherwise specifiedNote 3:When the input voltage (V IN )at any pin exceeds the power supplies (V IN <(GNDD or GNDA)or V IN >V CC ),the current at that pin should be limited to 5mA.The 20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5mA to four.Note 4:The maximum power dissipation must be derated at elevated temperatures and is dictated by T J max,θJA and the ambient temperature,T A .The maximum allowable power dissipation at any temperature is P D =(T J max−T A )/θJA .Note 5:The human body model is a 100pF capacitor discharged through a 1.5k Ωresistor into each pin.The machine model is a 200pF capacitor discharged directly into each pin.Note 6:See the section titled “Surface Mount”found in any post 1986National Semiconductor Linear Data Book for other methods of soldering surface mount devices.Note 7:Each input and output is protected by a nominal 6.5V breakdown voltage zener diode to GND;as shown below,input voltage magnitude up to 0.3V above V CC or 0.3V below GND will not damage the LM79.There are parasitic diodes that exist between the inputs and the power supply rails.Errors in the ADC conversion can occur if these diodes are forward biased by more than 50mV.As an example,if V CC is 4.50V DC ,input voltage must be ≤4.55V DC ,to ensure accurate conversions.DS100036-6FIGURE 3.Serial Bus Timing DiagramLM799AC Electrical Characteristics (Note 13)The following specifications apply for +4.25V DC ≤V CC ≤+5.75V DC unless otherwise specified.Boldface limits apply for T A =T J =T MIN to T MAX ;all other limits T A =T J =25˚C.(Continued)Note 8:Typicals are at T J =T A =25˚C and represent most likely parametric norm.Note 9:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 10:TUE (Total Unadjusted Error)includes Offset,Gain and Linearity errors of the ADC and any error introduced by the amplifiers as shown in the circuit of Figure 13.Note 11:Total Monitoring Cycle Time includes temperature conversion,7analog input voltage conversions and 3tachometer readings.Each temperature and input voltage conversion takes 100ms typical and 112ms maximum.Fan tachometer readings take 20ms typical,at 4400rpm,and 200ms max.Note 12:The total fan count is based on 2pulses per revolution of the fan tachometer output.Note 13:Timing specifications are tested at the TTL logic levels,V IL =0.4V for a falling edge and V IH =2.4V for a rising edge.TRI-STATE output voltage is forced to 1.4V.DS100036-7An x indicates that the diode exists.Pin Name D1D2D3IORD x IOWR x SYSCLK xD0–D7x x x SMI__IN x Chassis Intrusion x x Power Switch BypassxxPin Name D1D2D3FAN1–FAN3x SCLxSDA x x RESET x x VID4/NTESTxxxPin Name D1D2D3−IN6x x FB6x x x FB5x x x −IN5x x IN4–IN0x x x VID3–VID0xxxPin Name D1D2D3BTI x x NMI/IRQ xx x SMI xx A0–A2x CSxFIGURE 4.ESD Protection Input StructureL M 79 10Test CircuitFunctional Description1.0GENERAL DESCRIPTIONThe LM79provides7analog inputs,a temperature sensor,a Delta-Sigma ADC(Analog-to-Digital Converter),3fan speed counters,WATCHDOG registers,and a variety of inputs and outputs on a single chip.Interfaces are provided for both the ISA parallel bus or Serial Bus.The LM79performs power supply,temperature,and fan monitoring for personal com-puters.The LM79continuously converts analog inputs to8-bit digital words with a16mV LSB(Least Significant Bit)weighting, yielding input ranges of0V to4.096V.The two negative analog inputs provide inverting op amps,with their non-inverting input referred to ground.With additional exter-nal feedback components,these inputs provide measure-ments of negative voltages(such as-5V and-12V power supplies).The analog inputs are useful for monitoring sev-eral power supplies present in a typical computer.Tempera-ture is converted to an8-bit two’s-complement digital word with a1˚C LSB.Fan inputs measure the period of tachometer pulses from the fans,providing a higher count for lower fan speeds.The fan inputs are digital inputs with an acceptable range of0V to 5V and a transition level of approximately1.4V.Full scale fan counts are255(8-bit counter)and this represents a stopped or very slow fan.Nominal speeds,based on a count of153, are programmable from1100to8800RPM on FAN1and FAN2,with FAN3fixed at4400RPM.Signal conditioning circuitry is included to accommodate slow rise and fall times. The LM79provides a number of internal registers,as de-tailed in Figure6.These include:•Configuration Register:Provides control and con-figuration.•Interrupt Status Registers:Two registers to provide status of each WATCHDOG limit or Interrupt event.•Interrupt Mask Registers:Allows masking of indi-vidual Interrupt sources,as well as separate masking for each of both hardware Interrupt outputs.•VID/Fan Divisor Registers:A register to read the status of the VID0-VID3input lines.The high bits of this register contain the divisor bits for FAN1and FAN2in-puts.•Serial Bus Address Register:Contains the Serial Bus address.At power on it assumes the default value of 0101101binary,and can be altered via the ISA or Serial Bus interface.•Chip Reset/VID4/Device ID Register:Allows resetting of all the registers to the default power-on reset value.The state of VID4is reflected in this register.The identity of the divice being used can be determined by reading the state of the D7of this register.An LM79would be identified when D7is set high.•POST RAM:FIFO RAM to store up to32bytes of8-bit POST codes.Overflow of the POST RAM will set an Interrupt.The POST RAM,located at base address x0h and x4h,allows for easy decoding to address80h and 84h,the normal addresses for outputting of POST codes.Interrupt will only be set when writing to port x0h or x4h.The POST RAM can be read via ports85h and86h.•Value RAM:The monitoring results:temperature,volt-ages,fan counts,and WATCHDOG limits are all con-tained in the Value RAM.The Value RAM consists of a total of64bytes.The first11bytes are all of the results, the next19bytes are the WATCHDOG limits,and are located at20h-3Fh,including two unused bytes in the upper locations.The next32bytes,located at60h-7Fh, mirror the first32bytes with identical contents.The only difference in the upper bytes are that they auto-increment the LM79Internal Address Register when read from or written to via the ISA bus(auto-increment is not available for Serial Bus communications).When the LM79is started,it cycles through each measure-ment in sequence,and it continuously loops through the sequence approximately once every second.Each mea-sured value is compared to values stored in WATCHDOG,or Limit registers.When the measured value violates the pro-grammed limit the LM79will set a corresponding Interrupt in the Interrupt Status Registers.Two hardware Interrupt lines, SMI and NMI/IRQ,are fully programmable with separate masking of each Interrupt source,and masking of each output.In addition,the Configuration Register has control bits to enable or disable the hardware Interrupts. Additional digital inputs are provided for chaining of SMI (System Management Interrupt),outputs of multiple external LM75temperature sensors via the BTI(Board Temperature Interrupt)input,and a Chassis Intrusion input.The Chassis DS100036-8FIGURE5.Digital Output Load Circuitry LM79Functional Description(Continued)Intrusion input is designed to accept an active high signal from an external circuit that latches when the case is re-moved from the computer.2.0INTERFACEThe LM79only decodes the three lowest address bits on the ISA bus.Referring to the ISA bus timing diagrams in and ,the Chip Select Input,CS,should be taken low by external address decoder circuitry to access the LM79.The LM79decodes the following base addresses:-Port x0h:Power On Self Test codes from ISA bus.-Port x4h:Power On Self Test codes from ISA bus.-Port x5h:The LM79s Internal Address Register -Port x6h:Data RegisterIORD is the standard ISA bus signal that indicates to the LM79that it may drive data on to the ISA data bus.IOWR is the standard ISA command to the LM79that it may latch data from the ISA bus.SYSCLK is the standard ISA SYSCLK,typically 8.33MHz.This clock is used only for timing of the ISA interface of theLM79.All other clock functions within LM79such as the ADC and fan counters are done with a separate asynchronous internal clock.A typical application designed to utilize the POST RAM would decode the LM79to the address space starting at 80h,which is where POST codes are output to.Otherwise,the LM79can be decoded into a different desired address space.To communicate with an LM79Register,first write the ad-dress of that Register to Port x5h.Read or write data from or to that register via Port x6h.A write will take IOWR low,while a read will take IORD low.If the Serial Bus Interface and ISA bus interface are used simultaneously there is the possibility of collision.To prevent this from occurring in applications where both interfaces are used,read port x5h and if the Most Significant Bit,D7,is high,ISA communication is limited to reading port x5h only until this bit is low.A Serial Bus communication occurring while ISA is active will not be a problem,since even a single bit of Serial Bus communication requires 10microseconds,in comparison to less than a microsecond for an entire ISA communication.L M 79Functional Description(Continued)DS100036-9FIGURE6.LM79Register Structure LM79Functional Description(Continued)2.1Internal Registers of the LM79TABLE 1.The internal registers and their corresponding internal LM79address is as follows:RegisterLM79Internal HexAddress Power on ValueNotes(This is the data to be written to Port x5h)Configuration Register 40h 00001000Interrupt Status Register 141h 00000000Auto-increment to the address of Interrupt Status Register 2after a read or write to Port x6h.Interrupt Status Register 242h 00000000SMI Mask Register 143h 00000000Auto-increment to the address of SMI Mask Register 2after a read or write to Port x6h.SMI Mask Register 244h 00000000NMI Mask Register 145h 00000000Auto-increment to the address of NMI Mask Register 2after a read or write to Port x6h.NMI Mask Register 246h 01000000VID/Fan Divisor Register47h0101XXXXThe first four bits set the divisor for FanCounters 1and 2.The lower four bits reflect the state of the VID0-VID3inputs.Serial Bus Address Register 48h 00101101Chip Reset/VID4/Device ID Register 49h 1100000XD7identifies this device as the LM79.D0reflects the state of VID4.POST RAM00h-1FhAuto-increment when written to from Port x0h or x4h.Auto-increment after a read or write to Port x6h,with a separate pointer.Auto-incrementing stops when address 1Fh is reached.Value RAM 20h-3Fh Value RAM60h-7FhAuto-increment after a read or write to Port x6h.Auto-incrementing stops when address 7Fh is reached.A typical communication with the LM79would consist of:1.Write to Port x5h the LM79Internal Address (from col-umn 2above)of the desired register.Alternatively,when both ISA and Serial Bus interfaces are used,the first step in a communication may be to read Port x5h to ascertain the state of the Busy bit to avoid contention with an Serial Bus communication.2.Read or write the corresponding registers data withreads/writes from Port x6h.The LM79Internal Address latches,and does not have to be written if it is already pointing at the desired register.The LM79Internal Address Register is read/write (Bit 7is read only).L M 79Functional Description(Continued) 2.2Serial Bus InterfaceWhen using the Serial Bus Interface a write will always consist of the LM79Serial Bus Interface Address byte,fol-lowed by the Internal Address Register byte,then the data byte.There are two cases for a read:1.If the Internal Address Register is known to be at thedesired Address,simply read the LM79with the Serial Bus Interface Address byte,followed by the data byte read from the LM79.2.If the Internal Address Register value is unknown,writeto the LM79with the Serial Bus Interface Address byte, followed by the Internal Address Register byte.Then restart the Serial Communication with a Read consisting of the Serial Bus Interface Address byte,followed by the data byte read from the LM79.In all other respects the LM79functions identically for Serial Bus communications as it does for ISA communications.Auto-Increment does not operate.When writing to or reading from a Register which Auto-Increments with ISA communi-cations,the Register must be manually incremented for Serial Bus communications.The default power on Serial Bus address for the LM79is: 0101101binary.This address can be changed by writing any desired value to the Serial Bus address register,which can be done either via the ISA or Serial Bus.During and Serial Bus communication on the BUSY bit(bit7)in the address register at x5h will be high,and any ISA activity in that situation should be limited to reading port x5h only.All of these communications are depicted in the Serial Bus Interface Timing Diagrams as shown in Figure7.DS100036-10(a)Serial Bus Write to the Internal Address Register followed by the Data ByteDS100036-11(b)Serial Bus Write to the Internal Address Register OnlyDS100036-12 (c)Serial Bus Read from a Register with the Internal Address Register Preset to Desired LocationFIGURE7.Serial Bus Timing LM79Functional Description(Continued)3.0USING THE LM793.1Power OnWhen power is first applied,the LM79performs a “power on reset”on several of its registers.The power on condition of registers in shown in Table I.Registers whose power on values are not shown have power on conditions that are indeterminate (this includes the value RAM and WATCH-DOG limits).The ADC is inactive.In most applications,usu-ally the first action after power on would be to write WATCH-DOG limits into the Value RAM.3.2ResetsConfiguration Register INITIALIZATION accomplishes the same function as power on reset on most registers.The POST RAM,Value RAM conversion results,and Value RAM WATCHDOG limits are not Reset and will be indeterminate immediately after power on.If the Value RAM contains valid conversion results and/or Value RAM WATCHDOG limits have been previously set,they will not be affected by a Configuration Register INITIALIZATION.Power on reset,or Configuration Register INITIALIZATION,clear or initialize the following registers (the initialized values are shown on Table 1):•Configuration Register •Interrupt Status Register 1•Interrupt Status Register 2•SMI Mask Register 1•SMI Mask Register 2•NMI Mask Register 1•NMI Mask Register 2•VID/Fan Divisor Register•Serial Bus Address Register (Power on reset only,not reset by Configuration Register INITIALIZATION)Configuration Register INITIALIZATION is accomplished by setting Bit 7of the Configuration Register high.This bit automatically clears after being set.The LM79allows the user to perform an unconditional com-plete Power-on reset by writing a one to Bit 5of the Chip Reset/VID4/Device ID Register.The LM79allows an uncon-ditional complete Power-on reset to be initiated by taking the IOWR and IORD signal lines low simultaneously,for at least 50ns,while CS is high.The delay between consecutive IORD and IOWR pulses should be greater than 50ns to ensure that an Power-on reset does not occur unintention-ally.In systems where the serial bus is only being used it may be advantageous to take both IOWR and IORD to the system reset pulse.In this way whenever the system is reset the LM79will also be reset to its initial Power-on state.3.3Using the Configuration RegisterThe Configuration Register provides all control over the LM79.At power on,the ADC is stopped and INT__Clear is asserted,clearing the SMI and NMI/IRQ hardwire outputs.The Configuration Register starts and stops the LM79,en-ables and disables interrupt outputs and modes,and pro-vides the Reset function described in Section 3.2.Bit 0of the Configuration Register controls the monitoring loop of the LM79.Setting Bit 0low stops the LM79monitor-ing loop and puts the LM79in shutdown mode,reducing power consumption.ISA and Serial Bus communication ispossible with any register in the LM79although activity on these lines will increase shutdown current,up to as much as maximum rated supply current,while the activity takes place.Taking Bit 0high starts the monitoring loop,described in more detail subsequently.Bit 1of the Configuration Register enables the SMI Interrupt hardwire output when this bit is taken high.Similarly,Bit 2of the Configuration Register enables the NMI/IRQ Interrupt hardwire output when taken high.The NMI/IRQ mode is determined by Bit 5in the Configuration Register.When Bit 5is low the output is an active low IRQ output.Taking Bit 5high inverts this output to provide an active high NMI output.The Power Switch Bypass provides an active low at the open drain Power Switch Bypass output when set high.This is intended for use in software power control by activating an external power control MOSFET.3.4Starting ConversionThe monitoring function (Analog inputs,temperature,and fan speeds)in the LM79is started by writing to the Configu-ration Register and setting INT__Clear (Bit 3),low,and Start (bit 0),high.The LM79then performs a “round-robin”moni-toring of all analog inputs,temperature,and fan speed inputs approximately once a second.The sequence of items being monitored corresponds to locations in the Value RAM and is:1.Temperature 2.IN03.IN14.IN25.IN36.IN47.-IN58.-IN69.Fan 110.Fan 211.Fan 33.5Reading Conversion ResultsThe conversion results are available in the Value RAM.Conversions can be read at any time and will provide the result of the last conversion.Because the ADC stops,and starts a new conversion whenever it is read,reads of any single value should not be done more often then once every 120ms.When reading all values,allow at least 1.5seconds between reading groups of values.Reading more frequently than once every 1.5seconds can also prevent complete updates of Interrupt Status Registers and Interrupt Output’s.A typical sequence of events upon power on of the LM79would consist of:1.Set WATCHDOG Limits2.Set Interrupt Masks3.Start the LM79monitoring process4.0ANALOG INPUTSThe 8-bit ADC has a 16mV LSB,yielding a 0V to 4.08V (4.096–1LSB)input range.This is true for all analog inputs.In PC monitoring applications these inputs would most often be connected to power supplies.The 2.5V and 3.3V supplies can be directly connected to the inputs.The 5V and 12V inputs should be attenuated with external resistors to any desired value within the input range.L M 79。

LM7805中文资料

目次1.lm7805 介绍2.现实运用3.引脚序号.引脚功效4.lm7805 运用电路5.7805 电参数三端稳压集成电路 lm7805.电子产品中,罕有的三端稳压集成电路有正电压输出的lm78 ×× 系列和负电压输出的lm79××系列.顾名思义,三端 IC 是指这种稳压用的集成电路,惟独三条引脚输出,分离是输入端.接地端和输出端.它的样子象是通俗的三极管,TO- 220 的尺度封装,也有 lm9013 样子的 TO-92 封装.用 lm78/lm79 系列三端稳压 IC 来构成稳压电源所需的外围元件少少 ,电路内部还有过流 .过热及调剂管的呵护电路 ,运用起来靠得住 .便利,并且价钱便宜.该系列集成稳压 IC 型号中的 lm78 或者 lm79 后面的数字代表该三端集成稳压电路的输出电压 ,如 lm7806 暗示输出电压为正 6V,lm7909 暗示输出电压为负 9V.因为三端固定集成稳压电路的运用便利 ,电子创造中时常采取 .最大输出电流,LM78XX系列输出电压分离为5V;6V;8V;9V;10V;12V;15V;18V;24V.在现实运用中 ,应在三端集成稳压电路上装配足够大的散热器(固然小功率7805IC 内部电路图.的前提下不必) .当稳压管温渡过高时 ,稳压机能将变差 ,甚至破坏 .当创造中须要一个能输出 1.5A 以上电流的稳压电源 ,平日采取几块三端稳压电路并联起来 ,使其最大输出电流为 N 个 1.5A,但运用时需留意:并联运用的集成稳压电路应采取统一厂家 .统一批号的产品 ,以包管参数的一致 .别的在输出电流上留有必然的余量 ,以防止个体集成稳压电路掉效时导致其他电路的连锁销毁 .在 lm78 ** .lm79 ** 系列三端稳压器中最常运用的是 TO-220 和 TO- 202 两种封装.这两种封装的图形以及引脚序号 .引脚功效如附图所示 .图中的引脚号标注办法是按照引脚电位从高到底的次序标注的 .如许标注便于记忆 .引脚①为最高电位,③脚为最低电位,②脚居中 .从图中可以看出 , 不管正压照样负压,②脚均为输出端 .对于 lm78** 正压系列,输入是最高电位 , 天然是①脚 ,地端为最低电位 ,即③脚,如附图所示 .对与 lm79** 负压系列,输入为最低电位 ,天然是③脚 ,而地端为最高电位 ,即①脚,如附图所示 .此外,还应留意,散热片老是和最低电位的第③脚相连 .如许在 lm78** 系列中,散热片和地相衔接 ,而在 lm79** 系列中,散热片却和输入端相衔接 .lm7805 典范运用电路图 :lm78XX 系列集成稳压器的典范运用电路图 ,是一个输出正 5V 直流电lm7805 稳压电路压的稳压电源电路 .IC 采集成稳压器 lm7805,C1.C2 分离为输入端和输出端滤波电容,RL 为负载电阻 .当输出电流较大时 ,lm7805 应配上散热板 .为进步输出电压的运用电路 .稳压二极管 VD1 串接在 lm78XX 稳压器 2 脚与地之间,可使输出电压 Uo 得到必然的进步 ,输出电压 Uo 为 78XX 稳压器输出电压与稳压二极管 VC1 稳压值之和 .VD2 是输出呵护二极管 ,一旦输出电压低于 VD1 稳压值时,VD2 导通,将输出电流旁路 ,呵护 lm7800 稳压器输出级不被破坏.为输出电压可在必然规模内调节的运用电路 .因为 R1.RP 电阻采集的感化,使得输出电压被进步 ,进步的幅度取决于 RP 与 R1 的比值.调节电位器 RP, 即可必然规模内调节输出电压 .当 RP=0 时,输出电压 Uo 等于 lm78XX 稳压器输出电压 ;当 RP 慢慢增大时 ,Uo 也随之慢慢进步 .为扩展输出电流的运用电路 .VT2 为外接扩流率管 ,VT1 为推进管,二者为达林顿衔接 .R1 为偏置电阻 .该电路最大输出电流取决于 VT2 的参数.参数输出电压符号Vo测试前提Tj=25℃最小值典范值最大值单位V5.0mA<1o<1.0A,Po<15WV Vi=7.5v to 20v线性调△Vo剂率Tj=25℃,Vi=7.5V to 25V100 mV负载调△Vo 剂率静态电IQ 流Tj=25℃,Vi=8V to 12VTj=25℃,lo=250mA to 750mATj=25℃9450100508mVmVmVmA静态电流变更△IQ mA 率Vi=8V to 25V mA输出电压温漂输出噪音电压纹波克制比输入输出电压差输出阻抗短路电流峰值电流△Vo/△Tto 100KHz,Ta=25℃f=120Hz,Vi=8V to 18Vlo=1.0A,Tj=25℃f=1KHzVi=35V,Ta=25℃Tj=25℃mV/ ℃f=10Hzlo=5mAmΩ2301PK1SCμVmAVoVNRoRR4262dB7315AV2。

78系列和79系列 引脚图及稳压电路图资料

78系列和79系列引脚图及稳压电路图资料7805最大输出电流[1.5]A7805是我们最常用到的稳压芯片了,他的使用方便,用很简单的电路即可以输入一个直流稳压电源,他的输出电压恰好为5v,刚好是51系列单片机运行所需的电压,他有很多的系列如ka7805,ads7805,cw7805等,性能有微小的差别,用的最多的还是lm7805,下面我简单的介绍一下他的3个引脚以及用它来构成的稳压电路的资料。

左手665收藏时间:2017年4月23日17287805三端稳压集成电路,电子产品中,常见的三端稳压集成电路有正电压输出的78 ××系列和负电压输出的79××系列。

顾名思义,三端IC是指这种稳压用的集成电路,只有三条引脚输出,分别是输入端、接地端和输出端。

它的样子象是普通的三极管,TO- 220 的标准封装,也有9013样子的TO-92封装。

输出电压:4.8V~5.2V最大输出电流: 1.5A7805引脚图其中1接整流器输出的+电压,2为公共地(也就是负极),3就是我们需要的正5V输出电压了,下面介绍一个简单的7805电路lm7805稳压电路上图中R1用220Ω,R2用680Ω的这个是用来调节输出电压的。

输出电压公式Uo≈Uxx(1+R2/R1),此稳压电路可在5~12V稳压范围内实现输出电压连续可调节。

此三端集成稳压集成电路lm7805最大输入电压为35V,输入输出差需保持2V以上,这样该电路中因为稳压器的直流输入电压是正14V,故该稳压电路的最大输出电压为正12V。

此电路的精度一般可达到0.04以上,用lm7805就能满足一般需求了。

左手665欢迎你怎么判断l7805cv管脚是否已经烧坏左手665收藏时间:2017年4月24日09:107800系列的三端稳压IC,因厂家不同和产品的差异,用万用表测出的数值会有较大的出入,在一般情况下,输入-地之间电阻为15-45千欧,输出-地4-12千欧,地-输入4-6千欧,地-输出4-7千欧,输入-输出30-50千欧,输出-输入4.5-5.0千欧,电阻值是交换表笔测量,如果出入较大或出现0与“无穷大”均已损坏。

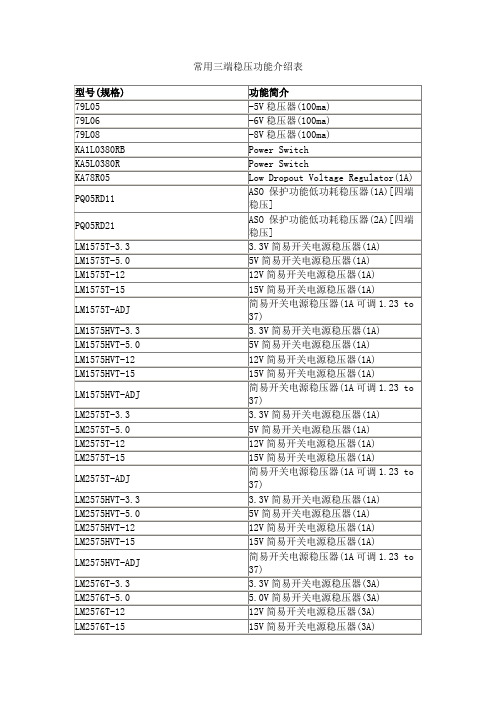

稳压管大全)

3.3V简易开关电源稳压器(1A)

LM1575T-5.0

5V简易开关电源稳压器(1A)

LM1575T-12

12V简易开关电源稳压器(1A)

LM1575T-15

15V简易开关电源稳压器(1A)

LM1575T-ADJ

简易开关电源稳压器(1A可调1.23 to 37)

LM1575HVT-3.3

LM2575HVT-ADJ

简易开关电源稳压器(1A可调1.23 to 37)

LM2576T-3.3

3.3V简易开关电源稳压器(3A)

LM2576T-5.0

5.0V简易开关电源稳压器(3A)

LM2576T-12

12V简易开关电源稳压器(3A)

LM2576T-15

15V简易开关电源稳压器(3A)

LM2576T-ADJ

79L08

-8V稳压器(100ma)

KA1L0380RB

Power Switch

KA5L0380R

Power Switch

KA78R05

Low Dropout Voltage Regulator(1A)

PQ05RD11

ASO保护功能低功耗稳压器(1A)[四端稳压]

PQ05RD21

ASO保护功能低功耗稳压器(2A)[四端稳压]

型号(规格)

功能简介

兼容型号

CA3130

高输入阻抗运算放大器

Intersil[DATA]

CA3140

高输入阻抗运算放大器

CD4573

四可编程运算放大器

MC14573

ICL7650

斩波稳零放大器

LF347(NS[DATA])

带宽四运算放大器

H79L05中文资料

输出电流超过 100mA 低噪声 纹波抑制比高 具有功放输出保护 过热保护 过流及短路保护

█ 极限值(Ta=25℃)

VIN——输入电压……………………………………………-30V

Tamb——工作环境温度……………………………… -20~85℃ Tstg——贮存温度…………………………………… -55~150℃ Tj——结温…………………………………………… -55~150℃

参数符号

符 号 说 明 最小值 典型值 最大值

单 位

测试条件

-4.8 -5.0 -5.2

Tj=25℃

VO

输出电压

-4.75

-5.25 V -20V≤VIN≤-7V,1mA≤IO≤40mA

-4.75

-5.25

VIN=-10V,1mA≤IO≤70mA

ΔVO 电压调整率

15

150

Tj=25℃, -20V≤VIN≤-7V

RR

纹波抑制比

30 μV Tj=25℃,10Hz≤f≤100kHz

41

60

dB Tj=25℃, -18V≤VIN≤-8V, f=120Hz

VD

下降电压

1.7VBiblioteka Tj=25℃█ 外形图及引脚排列

TO-92

1―地 GND 2―输入 IN 3―输出 OUT

█ 功能框图

█ 典型连接图

元器件交易网 汕头华汕电子器件有限公司

H 79L05

B

█ 电参数(除非另有说明,VIN=-10V,IO=40mA,0℃≤Tj≤125℃,CIN=0.33μF,COUT=0.1μF)

mV

100

Tj=25℃, -20V≤VIN≤-8V

ΔVO 负载调整率

电子元件基础教程共12页文档

第二章:半导体器件第四节集成电路? ? 集成电路是一种采用特殊工艺,将晶体管、电阻、电容等元件集成在硅基片上而形成的具有一定功能的器件,英文为缩写为IC,也俗称芯片。

集成电路是六十年代出现的,当时只集成了十几个元器件。

后来集成度越来越高,也有了今天的P-III。

? ? 集成电路根据不同的功能用途分为模拟和数字两大派别,而具体功能更是数不胜数,其应用遍及人类生活的方方面面。

集成电路根据内部的集成度分为大规模中规模小规模三类。

其封装又有许多形式。

“双列直插”和“单列直插”的最为常见。

消费类电子产品中用软封装的IC,精密产品中用贴片封装的IC等。

? ? 对于CMOS型IC,特别要注意防止静电击穿IC,最好也不要用未接地的电烙铁焊接。

使用IC也要注意其参数,如工作电压,散热等。

数字IC多用+5V的工作电压,模拟IC工作电压各异。

集成电路有各种型号,其命名也有一定规律。

一般是由前缀、数字编号、后缀组成。

前缀表示集成电路的生产厂家及类别,后缀一般用来表示集成电路的封装形式、版本代号等。

常用的集成电路如小功率音频放大器LM386就因为后缀不同而有许多种。

LM386N是美国国家半导体公司的产品,LM代表线性电路,N代表塑料双列直插。

这里有各大IC生产公司的商标及其器件型号前缀。

? ? 集成电路型号众多,随着技术的发展,又有更多的功能更强、集成度更高的集成电路涌现,为电子产品的生产制作带来了方便。

在设计制作时,若没有专用的集成电路可以应用,就应该尽量选用应用广泛的通用集成电路,同时考虑集成电路的价格和制作的复杂度。

在电子制作中,有许多常用的集成电路,如NE555(时基电路)、LM324(四个集成的运算放大器)、TDA2822(双声道小功率放大器)、KD9300(单曲音乐集成电路)、LM317(三端可调稳压器)等。

? ? 为了您的方便使用,Bitbaby以后将在网站上建立一个集成电路数据库,您可以通过WEB查询获得各种集成电路的参数及常用集成电路的典型应用。

K9F5608X0D资料

Revision History

Revision No. History

0.0

Initial issue

0.1

1. Leaded package devices are eliminated

0.2

1.0

1.1

1. LOCKPRE pin mode is eliminated

• Fast Write Cycle Time - Program time : 200µs(Typ.) - Block Erase Time : 2ms(Typ.)

• Command/Address/Data Multiplexed I/O Port • Hardware Data Protection

* Samsung Electronics reserves the right to change products or specification without notice.

1

元器件交易网

K9F5608R0D K9F5608U0D K9F5608D0D

Document Title

FLASH MEMORY

Draft Date

May 16th. 2005

Remark

Advance

Aug. 11th. 2005 Advance

Oct. 17th. 2005 Preliminary

Oct. 30th. 2005 Final

Dec. 30th 2005

Note : For more detailed features and specifications including FAQ, please refer to Samsung’s Flash web site. /Products/Semiconductor/Flash/TechnicalInfo/datasheets.htm

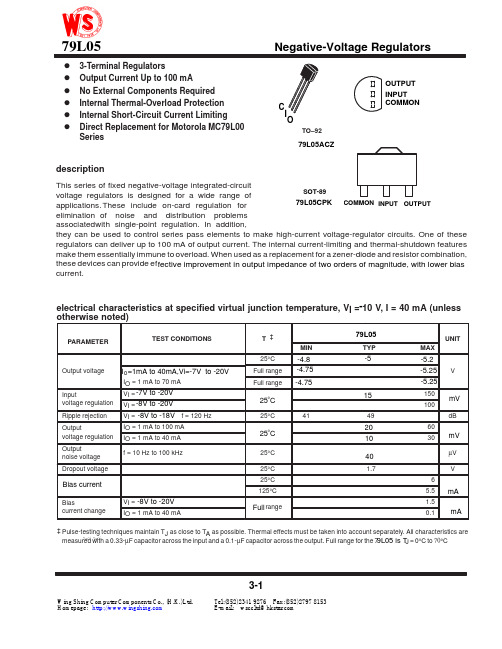

79L05中文资料

15

49

mV mV dB

20 10 40

1.7

60 30

mV µV V

mV

Biascurrent Bias ccurrent rrent

Bias current change

6 5.5 1.5 0.1

mA

mA

mA

Hale Waihona Puke mA‡ Pulse-testing techniques maintain TJ as close to TA as possible. Thermal effects must be taken into account separately. All characteristics are measured with a 0.33-µF capacitor across the input and a 0.1-µF capacitor across the output. Full range for the 7 9L05 is T J = 0°C to 70°C

3-1

Wing Shing Computer Components Co., (H.K.)Ltd. Homepage: Tel:(852)2341 9276 Fax:(852)2797 8153 E-mail: wsccltd@

元器件交易网

recommended operating conditions

79L05 Input voltage, VI Output current, IO Operating virtual junction temperature, TJ 0 MIN –7 MAX – 20 UNIT V mA °C

100

70

3-2

SH79F081规格书中文资料

4

SH79F081

5. 引脚描述

引脚编号 I/O端口 P0.2-P0.7 P1.2-P1.7 P2.0-P2.7 P3.0-P3.4 定时器 T0 T1 T2 T2EX PWM0 PWM1 PWM2 PWM01 PWM11 PWM21 FLT EUART RXD TXD SPI MOSI MISO SCK

SS ADC AN0 - AN7 中断&复位&时钟&电源 INT0 - INT1 INT40 - INT43 INT45 - INT46

————

RST XTAL1 XTAL2 Vss 蜂鸣器 BUZCON

5

SH79F081

续上表 引脚编号 电容 C 编程器 TDO (P1.2) TMS (P1.3) TDI (P1.4) TCK (P1.5) O I I I 调试接口:测试数据输出 调试接口:测试模式选择 调试接口:测试数据输入 调试接口:测试时钟输入 内建稳压源滤波电容引脚,推荐选用47µF电容 类型 说明

1

V2.2

SH79F081

3. 方框图

VDD Reset circuit Power Pipelined 8051 architecture Watch Dog 8K Bytes Flash ROM RST

Port 0 Configuration I/O P0.2 - P0.7

Internal 256 Bytes Data RAM

说明

I/O I/O I/O I/O I/O I/O I/O I O O O O O O I I/O O I/O I/O I/O I I I I I I I O P O

与PWM0有固定相位关系的12位PWM定时器输出引脚 与PWM1有固定相位关系的8位PWM定时器输出引脚 与PWM2有固定相位关系的8位PWM定时器输出引脚 PWM故障输入引脚 EUART数据输入 EUART数据输出 SPI主输出从输入引脚 SPI主输入从输出引脚 SPI串行时钟引脚 SPI从设备选择引脚 ADC输入通道 外部中断外部中断40-43 外部中断45-46 该引脚上保持10µs以上的低电平,CPU将复位。由于有内建100kΩ上拉电阻 连接到VDD,所以仅接一个外部电容即可实现上电复位。 谐振器输入 谐振器输出 接地 蜂鸣器

PHB110NQ08LT中文资料

PHP/PHB110NQ08LTN-channel TrenchMOS™ logic level FETRev. 01 — 29 March 2004Product data1.Product profile1.1DescriptionLogic level N-channel enhancement mode field-effect transistor in a plastic package using T renchMOS™ technology.1.2Features1.3Applications1.4Quick reference data2.Pinning information[1]It is not possible to make connection to pin 2 of the SOT404 package.s Logic level thresholds Very low on-state resistance.s Motors, lamps, solenoids s Uninterruptible power supplies s DC-to-DC converterss General industrial applications.s V DS ≤75V s I D ≤75As P tot ≤230Ws R DSon ≤8.5m Ω.Table 1:Pinning - SOT78 (TO-220AB) and SOT404 (D 2-PAK), simplified outline and symbolPin DescriptionSimplified outlineSymbol1gate (g)SOT78 (TO-220AB)SOT404 (D 2-PAK)2drain (d)[1]3source (s)mbmounting base;connected to drain (d)MBK10612mb3132MBK116mbsdgMBB0763.Ordering information4.Limiting valuesTable 2:Ordering informationType numberPackage NameDescriptionVersionPHP110NQ08LT TO-220AB Plastic single-ended package;heatsink mounted;1mounting hole;3leads SOT78PHB110NQ08LTD 2-P AKPlastic single-ended surface mounted package;3leads (one lead cropped)SOT404Table 3:Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol Parameter Conditions Min Max Unit V DS drain-source voltage (DC)25°C ≤T j ≤175°C-75V V DGR drain-gate voltage (DC)25°C ≤T j ≤175°C; R GS =20k Ω-75V V GS gate-source voltage (DC)-±20V I D drain current (DC)T mb =25°C; V GS =10V;Figure 2and 3-75A T mb =100°C; V GS =10V;Figure 2-75A I DM peak drain current T mb =25°C; pulsed; t p ≤10µs;Figure 3-240A P tot total power dissipation T mb =25°C;Figure 1-230W T stg storage temperature −55175°C T j junction temperature−55175°C Source-drain diodeI S source (diode forward) current (DC)T mb =25°C-75A I SMpeak source (diode forward) current T mb =25°C; pulsed; t p ≤10µs-240A Avalanche ruggednessE DS(AL)S non-repetitive drain-sourceavalanche energyunclamped inductive load; I D =75A;t p =0.15ms; V DD ≤75V; R GS =50Ω;V GS =10V; starting T j =25°C-560mJFig 1.Normalized total power dissipation as afunction of mounting base temperature.Fig 2.Normalized continuous drain current as afunction of mounting base temperature.T mb =25°C; I DM is single pulse; V GS =10VFig 3.Safe operating area; continuous and peak drain currents as a function of drain-source voltage.03aa1604080120050100150200T mb (°C)P der (%)03ap5604080120050100150200T mb (°C)I der (%)P der P totP tot 25C °()-----------------------100%×=I der I DI D 25C °()-------------------100%×=03ap58110102103 110102103V DS (V)I D (A)DC100 ms 10 msLimit R DSon = V DS / I D1 mst p = 10 µs1 s5.Thermal characteristics5.1Transient thermal impedanceTable 4:Thermal characteristicsSymbol ParameterConditionsMin Typ Max Unit R th(j-mb)thermal resistance from junction to mounting base Figure 4--0.65K/W R th(j-a)thermal resistance from junction to ambient SOT78vertical in still air-60-K/W SOT404mounted on printed-circuit board; minimum footprint;vertical in still air.-50-K/WFig 4.Transient thermal impedance from junction to mounting base as a function of pulse duration.03ap5710-210-1110-410-310-210-11t p (s)Z th(j-mb) (K/W)single pulseδ = 0.50.20.10.050.02t pt p TPtTδ =6.CharacteristicsTable 5:CharacteristicsT j=25°C unless otherwise specified.Symbol Parameter Conditions Min Typ Max Unit Static characteristicsV(BR)DSS drain-source breakdown voltage I D=250µA; V GS=0VT j=25°C75--VT j=−55°C70--VV GS(th)gate-source threshold voltage I D=1mA; V DS=V GS;Figure9T j=25°C1 1.52VT j=175°C0.5--VT j=−55°C-- 2.2VI DSS drain-source leakage current V DS=75V; V GS=0VT j=25°C--10µAT j=175°C--500µA I GSS gate-source leakage current V GS=±10V; V DS=0V-2100nA R DSon drain-source on-state resistance V GS=10V; I D=25A;Figure7and8T j=25°C-7.28.5mΩT j=175°C-15.117.9mΩV GS=5V; I D=25A;Figure7and8-7.69mΩV GS=4.5V; I D=25A;Figure8--9.95mΩDynamic characteristicsQ g(tot)total gate charge I D=25A; V DD=60V; V GS=10V;Figure13-127.3-nCQ gs gate-source charge-12.5-nC Q gd gate-drain (Miller) charge-54.5-nCC iss input capacitance V GS=0V; V DS=25V; f=1MHz;Figure11-6631-pFC oss output capacitance-905-pF C rss reverse transfer capacitance-610-pFt d(on)turn-on delay time V DD=30V; R L=1.2Ω;V GS=5V;R G=10Ω-47-nst r rise time-185-ns t d(off)turn-off delay time-424-ns t f fall time-226-ns Source-drain diodeV SD source-drain (diode forward) voltage I S=25A; V GS=0V;Figure12-0.77 1.2V t rr reverse recovery time I S=20A; dI S/dt=−100A/µs; V GS=0V-70-ns Q r recovered charge-213-nCT j =25°C T j =25°C and 175°C; V DS >I D x R DSonFig 5.Output characteristics: drain current as afunction of drain-source voltage;typical values.Fig 6.Transfer characteristics: drain current as afunction of gate-source voltage; typical values.T j =25°CFig 7.Drain-source on-state resistance as a functionof drain current; typical values.Fig 8.Normalized drain-source on-state resistance factor as a function of junction temperature.03ap5908016024001234V DS (V)I D (A)T j = 25 °CV GS = 2.2 V2.6 V5 V10 V 3.4 V3 V03ap6102550750123V GS (V)I D (A)V DS > I D x R DSonT j = 175 °C25 °C03ap6005101520080160240I D (A)R DSon (m Ω)V GS = 3 VT j = 25 °C3.4 V10 V5 V 2.6 V03nb2500.81.62.4-6060120180T j(°C)aa RDSon R DSon 25C °()----------------------------=I D =1mA; V DS =V GS T j =25°C; V DS =5VFig 9.Gate-source threshold voltage as a function ofjunction temperature.Fig 10.Sub-threshold drain current as a function ofgate-source voltage.V GS =0V; f =1MHzFig 11.Input, output and reverse transfer capacitances as a function of drain-source voltage; typical values.03aa3300.511.522.5-6060120180T j (°C)V GS(th)(V)maxtypmin03aa3610-610-510-410-310-210-10123V GS (V)I D (A)maxtypmin03ap6310210310410510-11 10102V DS (V)C (pF)C issC oss C rssT j =25°C and 175°C; V GS =0V I D =25A; V DD =14V and 60VFig 12.Source (diode forward) current as a function ofsource-drain (diode forward) voltage; typical values.Fig 13.Gate-source voltage as a function of gatecharge; typical values.03ap62025507500.30.60.91.2V SD (V)I S (A)T j = 25 °C175 °CV GS = 0 V03ap640246810050100150Q G (nC)V GS (V)I D = 25 A T j = 25 °CV DD = 60 V14 V7.Package outlineFig 14.SOT78 (TO-220AB).REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC EIAJ SOT78SC-463-lead TO-220ABDD 1qpL123L 1(1)b 1e eb0510 mmscalePlastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220ABSOT78DIMENSIONS (mm are the original dimensions)A E A 1cNote1. Terminals in this zone are not tinned.QL 2UNIT A 1b 1D 1e p mm2.54q Q A b D c L 2max.3.03.83.615.013.53.302.793.02.72.62.20.70.415.815.20.90.71.31.04.54.11.391.276.45.910.39.7L 1(1)E L 00-09-0701-02-16mounting baseFig 15.SOT404 (D 2-PAK).UNIT A REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECEIAJmmA 1D 1D max.E e L p H D Q c 2.542.602.2015.8014.802.902.10111.601.2010.309.704.504.101.401.270.850.600.640.46b DIMENSIONS (mm are the original dimensions) SOT4040 2.5 5 mmscalePlastic single-ended surface mounted package (Philips version of D 2-PAK); 3 leads (one lead cropped)SOT404e eEbD 1H DDQL pc A 1A132mounting base99-06-2501-02-128.Revision historyTable 6:Revision historyRev Date CPCN Description0120040329-Product data (9397 750 12924)Contact informationFor additional information, please visit .For sales office addresses, send e-mail to:sales.addresses@ .Fax: +31 40 27 248259.Data sheet status[1]Please consult the most recently issued data sheet before initiating or completing a design.[2]The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL .[3]For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.10.DefinitionsShort-form specification —The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device.These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.11.DisclaimersLife support —These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductorscustomers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes —Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’),relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes noresponsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to theseproducts,and makes no representations or warranties that these products are free from patent,copyright,or mask work right infringement,unless otherwise specified.12.TrademarksTrenchMOS —is a trademark of Koninklijke Philips Electronics N.V .Level Data sheet status [1]Product status [2][3]DefinitionI Objective data Development This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.IIPreliminary dataQualificationThis data sheet contains data from the preliminary specification.Supplementary data will be published at a later date.Philips Semiconductors reserves the right to change the specification without notice,in order to improve the design and supply the best possible product.III Product data ProductionThis data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design,manufacturing and supply.Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN).© Koninklijke Philips Electronics N.V .2004.Printed in The NetherlandsAll rights are reserved.Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract,is believed to be accurate and reliable and may be changed without notice.No Contents1Product profile . . . . . . . . . . . . . . . . . . . . . . . . . . 11.1Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.2Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.3Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.4Quick reference data. . . . . . . . . . . . . . . . . . . . . 12Pinning information. . . . . . . . . . . . . . . . . . . . . . 13Ordering information. . . . . . . . . . . . . . . . . . . . . 24Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 25Thermal characteristics. . . . . . . . . . . . . . . . . . . 45.1T ransient thermal impedance . . . . . . . . . . . . . . 46Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 57Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 98Revision history. . . . . . . . . . . . . . . . . . . . . . . . 119Data sheet status. . . . . . . . . . . . . . . . . . . . . . . 1210Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1211Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1212Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 12。

TS79L08CT中文资料

TS79L00 series3-Terminal Low Current Negative Voltage RegulatorVoltage Range - 5V to - 24V Output Current up to 100mAGeneral DescriptionThe TS79L00 Series of negative voltage regulators are inexpensive, easy-to-use devices suitable for a multitude of applications that require a regulated supply of up to 100mA. Like their higher power TS7900 and TS79M00 Series cousins, these regulators feature internal current limiting and thermal shutdown making them remarkably rugged. No external components are required with the TS79L00 devices in many applications.These devices offer a substantial performance advantage over the traditional zener diode-resistor combination, as output impedance and quiescent current are substantially reduced.This series is offered in 3-pin TO-92, SOT-89 and 8-pin SOP-8 package.FeaturesOutput current up to 100mA No external components required Internal thermal overload protection Internal short-circuit current limitingOutput transistor safe-area compensationOutput voltage offered in 4% toleranceOrdering InformationNote: Where xx denotes voltage option.Part No.Operating Temp.(Ambient)PackageTS79LxxCT TO-92TS79LxxCY SOT-89TS79LxxCS -20 ~ +85 o C SOP-8 Standard ApplicationA common ground is required between the input and theoutput voltages. The input voltage must remain typically 2.0V above the output voltage even during the low point on the Input ripple voltage. XX = these two digits of the type number indicate voltage.* = Cin is required if regulator is located an appreciabledistance from power supply filter.** = Co is not needed for stability; however, it doesimprove transient response.Pin AssignmentPin No.TS79L00CT TS79L00CY TS79L00CSPin Description3 3 1 Output 222, 3, 6, 7Input1 1 5 Ground 4, 8 Non connectedAbsolute Maximum RatingInput Voltage Vin * - 35 V Input Voltage Vin ** - 40 V Power Dissipation TO-92TO-89 SOP-8 Pd0.6250.50.5WOperating Junction Temperature Range T J0 ~ +125 o C Storage Temperature Range T STG-65 ~ +150 o C Note : * TS79L05 to TS79L18** TS79L24TS79L05 Electrical Characteristics(Vin= -10V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 4.80 - 5 - 5.20Output voltage Vout -7.5V≤Vin≤ -20V,5mA≤Iout≤100mA - 4.75 - 5 - 5.25VLine Regulation REGline Tj=25 o C -7.5V≤Vin≤ -20V,Io=40mA-- 50 150 5mA≤Iout≤100mA -- 20 60Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA --1030mVQuiescent Current Iq Iout=0, Tj=25 o C --36-8V≤Vin≤ -20V -- -- 1.5Quiescent Current Change ∆Iq1mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 40 -- uVRipple Rejection Ratio RR f=120Hz, -8V≤Vin≤ -18V 41 49 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A z Pulse testing techniques are used to maintain the junction temperature as close to the ambient temperature aspossible, and thermal effects must be taken into account separately.z This specification applies only for DC power dissipation permitted by absolute maximum ratings.TS79L06 Electrical Characteristics(Vin= -11V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)ParameterTestConditionsMinTypMaxUnitTj=25 o C - 5.76 - 6 - 6.24Output voltage Vout -8.5V≤Vin≤ -21V,5mA≤Iout≤100mA - 5.70 - 6 - 6.30VLine Regulation REGline Tj=25 o C -8.5V≤Vin≤ -21V,Io=40mA-- 50 150 5mA≤Iout≤100mA -- 20 60Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 1030mVQuiescent Current Iq Iout=0, Tj=25 o C --36-9V≤Vin≤ -21V -- -- 1.5Quiescent Current Change ∆Iq1mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 40 -- uVRipple Rejection Ratio RR f=120Hz, -9V≤Vin≤ -19V 41 49 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A TS79L08 Electrical Characteristics(Vin= -14V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 7.69 - 8 - 8.32Output Voltage Vout -10.5V≤Vin≤ -23V,5mA≤Iout≤100mA - 7.61 - 8 - 8.40VLine Regulation REGline Tj=25 o C -10.5V≤Vin≤ -23V,Io=40mA-- 80 160 5mA≤Iout≤100mA -- 25 80Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 10 40mVQuiescent Current Iq Iout=0, Tj=25 o C --36-11V≤Vin≤ -23V -- -- 1.5Quiescent Current Change ∆lq1mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 60 -- uVRipple Rejection Ratio RR f=120Hz, -13V≤Vin≤ -23V 37 57 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A z Pulse testing techniques are used to maintain the junction temperature as close to the ambient temperature aspossible, and thermal effects must be taken into account separately.z This specification applies only for DC power dissipation permitted by absolute maximum ratings.TS79L09 Electrical Characteristics(Vin= -15V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 8.65 - 9 - 9.36Output Voltage Vout -11.5V≤Vin≤ -24V,5mA≤Iout≤100mA - 8.57 - 9 - 9.45VLine Regulation REGline Tj=25 o C -11.5V≤Vin≤ -24V,Io=40mA-- 90 180 5mA≤Iout≤100mA -- 30 90Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 15 45mVQuiescent Current Iq Iout=0, Tj=25 o C --36-12V≤Vin≤ -24V -- -- 1.5Quiescent Current Change ∆lq5mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 60 -- uVRipple Rejection Ratio RR f=120Hz, -14V≤Vin≤ -24V 37 57 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A TS79L12 Electrical Characteristics(Vin= -19V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 11.53- 12 - 12.48Output Voltage Vout -14.5V≤Vin≤ -27V,5mA≤Iout≤100mA - 11.42- 12 - 12.60VLine Regulation REGline Tj=25 o C -14.5V≤Vin≤ -27V,Io=40mA-- 120 240 mV 5mA≤Iout≤100mA -- 40 120Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 20 60Quiescent Current Iq Tj=25 o C, Iout=0 -- 3 6.5-16V≤Vin≤ -27V -- -- 1.5Quiescent Current Change ∆lq5mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 80 -- uVRipple Rejection Ratio RR f=120Hz, -15V≤Vin≤ -25V 37 42 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A z Pulse testing techniques are used to maintain the junction temperature as close to the ambient temperature aspossible, and thermal effects must be taken into account separately.z This specification applies only for DC power dissipation permitted by absolute maximum ratings.TS79L15 Electrical Characteristics(Vin= -23V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 14.42- 15 - 15.60Output Voltage Vout -17.5V≤Vin≤ -30V,5mA≤Iout≤100mA - 14.28- 15 - 15.75VLine Regulation REGline Tj=25 o C -17.5V≤Vin≤ -30V,Io=40mA-- 150 300 mV 5mA≤Iout≤100mA -- 50 150Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 25 75Quiescent Current Iq Tj=25 o C, Iout=0 -- 3 6.5-20V≤Vin≤ -30V -- -- 1.5Quiescent Current Change ∆lq5mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C -- 90 -- uVRipple Rejection Ratio RR f=120Hz, -18V≤Vin≤ -28V 34 39 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A TS79L18 Electrical Characteristics(Vin= -27V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 17.30- 18 - 18.72Output Voltage Vout -21V≤Vin≤- 33V,5mA≤Iout≤100mA - 17.14- 18 - 18.90VLine Regulation REGline Tj=25 o C -21V≤Vin≤ -33V,Io=40mA-- 180 360 mV 5mA≤Iout≤100mA -- 60 180Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 30 90Quiescent Current Iq Tj=25 o C, Iout=0 -- 3 6.5-21V≤Vin≤ -33V -- -- 1.5Quiescent Current Change ∆lq5mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C --150--uVRipple Rejection Ratio RR f=120Hz, -23V≤Vin≤ -33V 33 48 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A z Pulse testing techniques are used to maintain the junction temperature as close to the ambient temperature aspossible, and thermal effects must be taken into account separately.z This specification applies only for DC power dissipation permitted by absolute maximum ratings.TS79L24 Electrical Characteristics(Vin= -33V, Iout=40mA, 0 o C≤Tj≤125 o C, Cin=0.33uF, Cout=0.1uF; unless otherwise specified.)Parameter Symbol TestConditions MinTypMaxUnitTj=25 o C - 23.07- 24 - 24.96Output Voltage Vout -27V≤Vin≤ -38V,5mA≤Iout≤100mA - 22.85- 24 - 25.20VLine Regulation REGline Tj=25 o C -27V≤Vin≤ -38V,Io=40mA-- 200 400 mV 5mA≤Iout≤100mA -- 80 240Load Regulation REGload Tj=25 o C5mA≤Iout≤40mA -- 40 120Quiescent Current Iq Iout=0, Tj=25 o C --47-28V≤Vin≤ -38V -- -- 1.5Quiescent Current Change ∆lq5mA≤Iout≤40mA ----0.1mAOutput Noise Voltage Vn 10Hz≤f≤100KHz, Tj=25 o C --200--uVRipple Rejection Ratio RR f=120Hz, -29V≤Vin≤ -35V 31 45 -- dBVoltage Drop Vdrop Tj=25 o C -- 1.7 -- VPeak Output Current Io peak Tj=25 o C --0.15--A z Pulse testing techniques are used to maintain the junction temperature as close to the ambient temperature aspossible, and thermal effects must be taken into account separately.z This specification applies only for DC power dissipation permitted by absolute maximum ratings.。

UA79M06CKTPR中文资料

PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)7704001HA OBSOLETE CFP U 10None Call TI Call TIUA79M05CKC ACTIVE TO-220KC 350None Call TI Level-1-220C-UNLIM UA79M05CKCS ACTIVE TO-220KCS 350None Call TI Level-NC-NC-NC UA79M05CKTPR ACTIVE PFM KTP 23000None Call TI Level-1-220C-UNLIM UA79M05MUB OBSOLETE CFP U 10None Call TI Call TI UA79M06CKTPR OBSOLETE PFM KTP 2None Call TI Call TI UA79M08CKC OBSOLETE TO-220KC 3None Call TI Call TIUA79M08CKTPR ACTIVE PFM KTP 23000None Call TI Level-1-220C-UNLIM UA79M12CKC OBSOLETE TO-220KC 3None Call TI Call TI UA79M12CKTPR OBSOLETE PFM KTP 2None Call TI Call TI UA79M15CKC OBSOLETE TO-220KC 3None Call TI Call TI UA79M15CKTPR OBSOLETE PFM KTP 2None Call TI Call TI UA79M20CKTPR OBSOLETE PFM KTP 2None Call TI Call TI UA79M24CKTPROBSOLETEPFMKTP2NoneCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -May not be currently available -please check /productcontent for the latest availability information and additional product content details.None:Not yet available Lead (Pb-Free).Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean "Pb-Free"and in addition,uses package materials that do not contain halogens,including bromine (Br)or antimony (Sb)above 0.1%of total product weight.(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDECindustry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM11-Feb-2005元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

PHP108NQ03LT中文资料

Fig 1. Normalized total power dissipation as a function of mounting base temperature.

103

ID (A)

Limit RDSon = VDS / ID

102

DC 10

120

Ider (%)

Tmb = 25 °C Tmb = 25 °C; pulsed; tp ≤ 10 µs

EDS(AL)S non-repetitive drain-source avalanche energy

unclamped inductive load; ID = 43 A; tp = 0.25 ms; VDD ≤ 15 V; RGS = 50 Ω; VGS = 10 V; starting Tj = 25 °C

VSD

source-drain (diode forward) voltage IS = 25 A; VGS = 0 V; Figure 12

trr

reverse recovery time

Qr

recovered charge

IS = 20 A; dIS/dt = −100 A/µs; VGS = 0 V; VDS = 25 V

Product availability:

PHP108NQ03LT in SOT78 (TO-220AB) PHB108NQ03LT in SOT404 (D2-PAK) PHD108NQ03LT in SOT428 (D-PAK).

1.2 Features

s Logic level compatible

TrenchMOS™ logic level FET

LM79LXXAC中文资料

LM320L/LM79LXXAC/LM13121Series 3-Terminal Negative RegulatorsGeneral DescriptionThe LM320L/LM79LXXAC/LM13121dual marked series of 3-terminal negative voltage regulators features fixed output voltages of −5V,−12V,and −15V with output current capa-bilities in excess of 100mA.These devices were designed using the latest computer techniques for optimizing the pack-aged IC thermal/electrical performance.The LM79LXXAC series,even when combined with a minimum output com-pensation capacitor of 0.1µF,exhibits an excellent transient response,a maximum line regulation of 0.07%V O /V,and a maximum load regulation of 0.01%V O /mA.The LM320L/LM79LXXAC/LM13121series also includes,as self-protection circuitry:safe operating area circuitry for out-put transistor power dissipation limiting,a temperature inde-pendent short circuit current limit for peak output current limiting,and a thermal shutdown circuit to prevent excessive junction temperature.Although designed primarily as fixed voltage regulators,these devices may be combined with simple external circuitry for boosted and/or adjustable volt-ages and currents.The LM79LXXAC series is available inthe 3-lead TO-92package,8-lead SOIC package,and the 6-Bump micro SMD package.The LM320L series is avail-able in the 3-lead TO-92package.For output voltage other than −5V,−12V and −15V,the LM137L series provides an output voltage range from 1.2V to 47V.Featuresn Preset output voltage error is less than ±5%overload,line and temperaturen Specified at an output current of 100mAn Easily compensated with a small 0.1µF output capacitorn Internal short-circuit,thermal and safe operating area protectionn Easily adjustable to higher output voltagesn Maximum line regulation less than 0.07%V OUT /V n Maximum load regulation less than 0.01%V OUT /mA n See AN-1112for micro SMD considerationsTypical ApplicationsFixed Output Regulator00774801*Required if the regulator is located far from the power supply filter.A 1µF aluminum electrolytic may be substituted.**Required for stability.A 1µF aluminum electrolytic may be substituted.Adjustable Output Regulator00774803−V 0=−5V −(5V/R1+I Q )•R2,5V/R1>3I QConnection Diagrams6-Bump micro SMD00774820Bump Side DownTO-92Plastic Package (Z)00774802Bottom ViewJanuary 2003LM320L/LM79LXXAC/LM13121Series 3-Terminal Negative Regulators©2003National Semiconductor Corporation Connection Diagrams(Continued)SO-8Plastic (Narrow Body)00774804Top ViewOrdering InformationPackage Part Number Package Marking Transport Media NSC Drawing8-Lead SOICLM79L05ACM LM79L05ACM95Units/Rail M08ALM79L05ACMX 2.5k Units Tape and ReelLM79L13ACM LM79L12ACM 95Units/Rail LM79L13ACMX 2.5k Units Tape and ReelLM79L15ACM LM79L15ACM 95Units/Rail LM79L15ACMX2.5k Units Tape and Reel 3-Pin TO-92LM13121Z-5.0320L79L051800Units Per Box Z03A LM13121Z-12320L79L121800Units Per Box LM13121Z-15320L79L151800Units Per Box 6-Bump micro SMDLM79L05ACTL XTPB 250Units Tape and Reel TLA06AMA LM79L05ACTLX3k Units Tape and ReelL M 320L /L M 79L X X A C /L M 13121 2Absolute Maximum Ratings(Note1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Input VoltageV O=−5V,−12V,−15V−35V Internal Power Dissipation(Note2)Internally Limited Operating Temperature Range0˚C to+70˚C Maximum Junction Temperature+125˚C Storage Temperature Range−55˚C to+150˚C Lead Temperature(Soldering,10sec.)260˚CElectrical Characteristics(Note3)T A=0˚C to+70˚C unless otherwise noted.Output Voltage−5V−12V−15V Input Voltage(unless otherwise noted)−10V−17V−20V Units Symbol Parameter Conditions Min Typ Max Min Typ Max Min Typ MaxV O OutputVoltageT J=25˚C,I O=100mA−5.2−5−4.8−12.5−12−11.5−15.6−15−14.41mA≤I O≤100mA−5.25−4.75−12.6−11.4−15.75−14.25V MIN≤V IN≤V MAX(−20≤V IN≤−7.5)(−27≤V IN≤−14.8)(−30≤V IN≤−18)V1mA≤I O≤40mA−5.25−4.75−12.6−11.4−15.75−14.25V MIN≤V IN≤V MAX(−20≤V IN≤−7)(−27≤V IN≤−14.5)(−30≤V IN≤−17.5)∆V O LineRegulationT J=25˚C,I O=100mA604545mVV MIN≤V IN≤V MAX(−20≤V IN≤−7.3)(−27≤V IN≤−14.6)(−30≤V IN≤−17.7)VT J=25˚C,I O=40mA604545mVV MIN≤V IN≤V MAX(−20≤V IN≤−7)(−27≤V IN≤−14.5)(−30≤V IN≤−17.5)V∆V O LoadRegulation T J=25˚C50100125mV 1mA≤I O≤100mA∆V O Long TermStabilityI O=100mA204860mV/khrsI Q QuiescentCurrentI O=100mA262626mA ∆I Q QuiescentCurrent1mA≤I O≤100mA0.30.30.3 Change1mA≤I O≤40mA0.10.10.1mAI O=100mA0.250.250.25mAV MIN≤V IN≤V MAX(−20≤V IN≤−7.5)(−27≤V IN≤−14.8)(−30≤V IN≤−18)VV n Output NoiseVoltage T J=25˚C,I O=100mA4096120µV f=10Hz−10kHzRipple Rejection T J=25˚C,I O=100mA505250dB f=120HzInput Voltage T J=25˚C,I O=100mA−7.3−14.6−17.7VRequired to I O=40mA−7.0−14.5−17.5VMaintain LineRegulationNote1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note2:Thermal resistance of Z package is60˚C/WθJC,232˚C/WθJA at still air,and88˚C/W at400ft/min of air.The M packageθJA is180˚C/W in still air.The maximum junction temperature shall not exceed125˚C on electrical parameters.Note3:To ensure constant junction temperature,low duty cycle pulse testing is used.LM320L/LM79LXXAC/LM131213Typical Performance CharacteristicsMaximum Average Power Dissipation (TO-92)Peak Output Current0077481100774812Short Circuit Output Current Dropout Voltage0077481300774814Ripple RejectionOutput Voltage vs.Temperature (Normalized to 1V @25˚C)0077481500774816L M 320L /L M 79L X X A C /L M 13121 4Typical Performance Characteristics(Continued)Quiescent CurrentOutput Impedance0077481700774818Typical Applications±15V,100mA Dual Power Supply00774806LM320L/LM79LXXAC/LM131215Schematic Diagrams−5V00774809−12V and −15V00774810L M 320L /L M 79L X X A C /L M 13121 6Physical Dimensionsinches (millimeters)unless otherwise notedSOIC Package (M)NS Package Number M08AMolded Offset TO-92(Z)NS Package Number Z03ALM320L/LM79LXXAC/LM131217Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)NOTES:UNLESS OTHERWISE SPECIFIED 1.EPOXY COATING.2.63Sn/67Pb EUTECTIC BUMP.3.RECOMMEND NON-SOLDER MASK DEFINED LANDING PAD.4.PIN A1ESTABLISHED BY LOWER LEFT CORNER WITH RESPECT TO TEXT ORIENTATION.5.XXX IN DRAWING NUMBER REPRESENTS PACKAGE SIZE VARIATION WHERE X1IS PACKAGE WIDTH,X2IS PACKAGE LENGTH AND X3IS PACKAGE HEIGHT.6.REFERENCE JEEC REGISTRATION MO-211,VARIATION BC.6-Bump micro SMDNS Package Number TLA06AMAX 1=1006µm X 2=1793µm X 3=600µmLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support Center Fax:65-62504466Email:ap.support@ Tel:65-62544466National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:nsj.crc@ Tel:81-3-5639-7560L M 320L /L M 79L X X A C /L M 13121S e r i e s 3-T e r m i n a l N e g a t i v e R e g u l a t o r sNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

MC79M08BTG中文资料

Characteristic

Symbol

Min

Typ

Max Unit

Output Voltage (TJ = 25°C) Line Regulation, TJ = 25°C (Note 1)

−7.0 Vdc ≥ VI ≥ −25 Vdc −8.0 Vdc ≥ VI ≥ −18 Vdc

VO

−4.8

−5.0

元器件交易网

MC79M00 Series

500 mA Negative Voltage Regulators

The MC79M00 series of fixed output negative voltage regulators are intended as complements to the popular MC78M00 series devices.

TO−220−3 T SUFFIX CASE 221AB

MC 79MxxyT AWLYWWG

4

12 3

DPAK−3 DT SUFFIX CASE 369C

9MxxBG ALYWW

79MxxG ALYWW

xx y A WL, L Y WW G

= 05, 08, 12, or 15 = B or C = Assembly Location = Wafer Lot = Year = Work Week = Pb−Free Device

VI−VO

Vdc

−

1.1

−

Average Temperature Coefficient of Output Voltage IO = 5.0 mA, 0°C ≤ TJ ≤ 125°C

DVO/DT

mV/°C

−

W78C51_DataSheet