UFM201中文资料

201品牌说明书资料

使用手册请您在使用之前认真阅读安装使用指南,以便得到正确的安装方式及快速网上激活使用。

产品外观、颜色如有改动,请以实物为准!城市漫步守护星201通过短信和GPRS形式,快速地将其位置信息传送给手机和电脑,可通过访问“城市漫步 在线服务平台或手机,查询定位器所在车辆的运行状况.定位查询网址:手机查询网址:PC客户端,安卓智能手机客户端软件下载:备注:包装盒内有一张城市漫步VIP会员卡,守护星201登入平台帐号就是会员卡用户名平台密码默认是:123456一、产品描述此追踪器通过短信和GPRS,将追踪器的位置信息发送到您的手机或者个人电脑的网络服务端追踪器具有如下功能特性超大容量电池超长待机通过短信或者GPRS进行追踪当前位置反馈定时反馈SOS报警越界报警控制低电报警超速报警实时语音监听振动报警无漂移汽车防盗二、主机介绍三、追踪器参数首次使用时请准备一张可正常使用的SIM卡,并装入追踪器请确认SIM卡没有欠费,请确认SIM卡锁已经取消,并开通了GPRS数据业务。

四、指示灯说明注: 机器开机,如检测到未插入SIM 卡或者机器SIM 卡异常,三个LED 灯挨个亮灭(走马灯)五、操作说明守护星201追踪器出厂时预设每隔5分钟自动连接到上报当前位置信息,并从服务中心获取最新的设置.事先请确保追踪器已经在服务中心 注册。

1. 在服务中心注册您的追踪器,并获得用户名和密码。

此操作需要追踪器的IMEI号码。

IMEI号码粘贴在追踪器的背面。

2. 检查预设的APN列表如果您使用的SIM卡运营商没有在APN列表中,请通过短信手工设置APN3.当APN设置完毕,追踪器将会自动连接到,并每隔5秒向服务中心反馈位置信息. 您可登陆服务中心查看追踪器的轨迹。

六、“城市漫步”PC-WEB服务平台登陆 进入“城市漫步”WEB版服务平台,填写用户名、密码及验证码,点击“登陆”,进入平台界面。

七、“城市漫步”手机WEB服务平台手机浏览器访问,输入用户名/密码(同PC WEB版用户名/密码一致),八、“城市漫步”PC客户端城市漫步PC-Mini客户端支持WinXP、Win7等多种Windows 操作系统,方便用户一键登录或开机自动登录平台,可登陆城市漫步官网下载PC客户端。

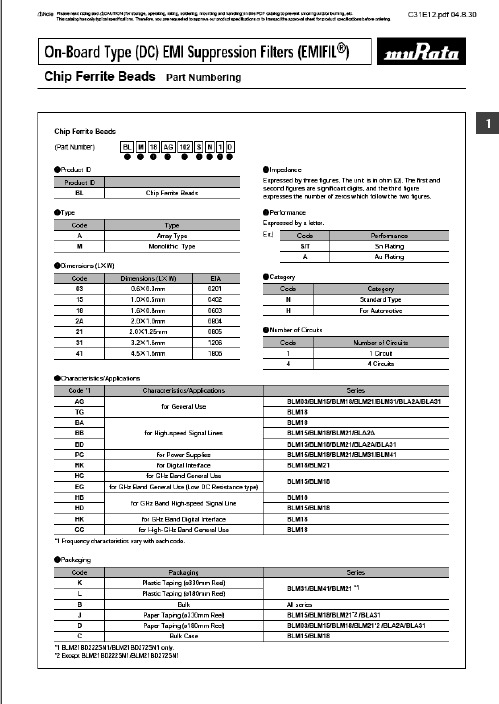

NFM21CC471R1H3资料

420 420

400

Impedance (Ω) at 100MHz

330 330

330 330

240

220 220 220 220 220 220 220 220

200

150 150

150 150

140

120 120 120 120 120 120 120 120 120

100

70 70

75 75 75 60 60

C31E12.pdf 04.8.30

•TThhisisccaatatalologghhaassoonnlylytytyppicicaal lssppeeccificfiacatiotionns.sTbheecraeufosree,thyeorueaisrenroeqsupeascteedfotrodaeptapirleodvesopuercipfircoadtuiocntss.pTehceifriceafotiroen,spoleratosetrapnpsarocvtethoeuarppprorodvuacltsshpeeectifiocraptiroondsuoctr strpaencsifaiccat ttihoensapbepfrorvealosrdheereint gfo. r product specifications before ordering.

-

1800±25%

-

100

10 (Typ.)

-

1000

600±25%

1000±40%

300

1000±25%

1400±40%

250

600±25%

1400±40%

300

1000±25%

2000±40%

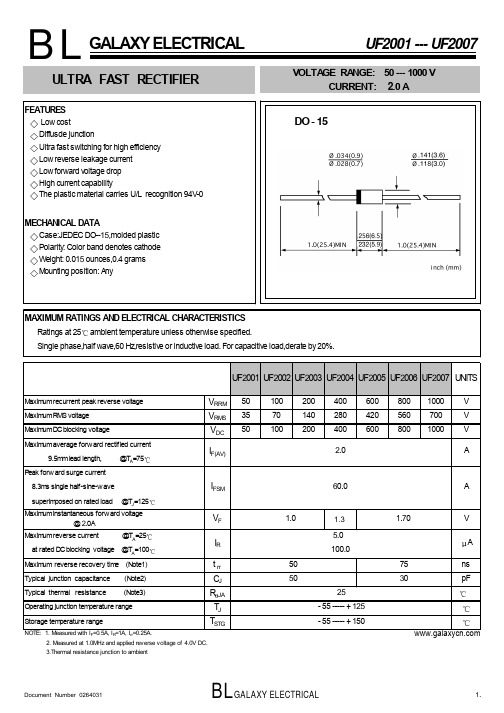

UF2001中文资料

UF2001-UF2007

FIG.2 -- MAXIMUM FORWARD SURGE CURRENT

PEAK FORWARD SURGE CURRENT, AMPERSE

ห้องสมุดไป่ตู้

75

8.3ms SINGLE HALF SINE-WAVE (JEDEC METHOD)

3.0

60

45

1.5 60Hz RESISTIVE OR INDUCTIVE LOAD

TJ =25 f=1MHz

TJ=25 Pulse width=300

s

0.01 0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8

1

1

10

100

PERCENT OF RATED PEAK REVERSE VOLTAGE INSTANTANEOUS FORWARD VOLTAGE, VOLTS

INSTANTANEOUS FORWARD CURRENT, AMPERSE

100

UF2001toUF2004

INSTANTANEOUS REVERSE CURRENT, MICRO AMPERSE

10

UF2004 UF2001-UF2004

1

10

UF2005toUF2007

0.1

UF2005-UF2007

Document Number 0264031

BLGALAXY ELECTRICAL

1.

RATINGS AND CHARACTERISTIC CURVES

FIG.1 -- TYPICAL FORWARD CURRENT DERATING CURVE AVERAGE FORWARD OUTPUT CURRENT, AMPERSE

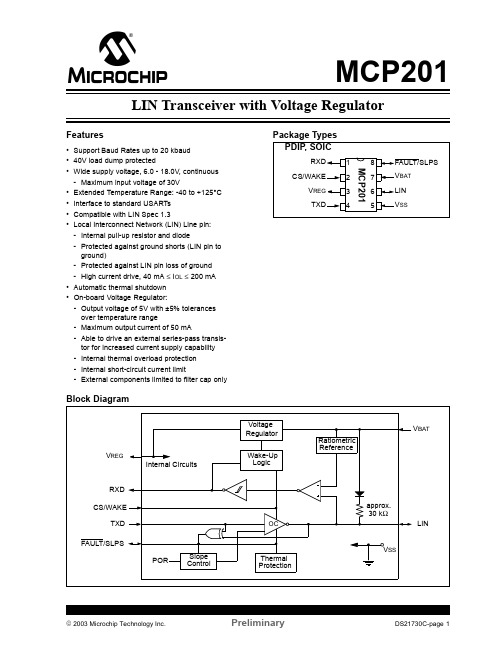

MCP201中文资料

power transients (see Figure 1-2).This protection is optional, but should be considered as good engineering practice.

1.1.2

REVERSE BATTERY PROTECTION

An external reverse battery blocking diode can be used to provide polarity protection (see Figure 1-2). This protection is optional, but should be considered as good engineering practice.

2003 Microchip Technology Inc.

1.0

DEVICE OVERVIEW

The MCP201 provides a physical interface between a microcontroller and a LIN half-duplex bus. It is intended for automotive and industrial applications with serial bus speeds up to 20 kbaud. The MCP201 provides a half-duplex, bidirectional communications interface between a microcontroller and the serial network bus. This device will translate the CMOS/TTL logics levels to LIN level logic, and vice versa. The LIN specification 1.3 requires that the transceiver of all nodes in the system be connected via the LIN pin, referenced to ground and with a maximum external termination resistance of 510Ω from LIN bus to battery (510Ω is the maximum load of the LIN bus, which corresponds to one Master and 16 Slave nodes). The MCP201 provides a +5V 50 mA regulated power supply. This function is short-circuit-protected and it can generate a thermal shutdown. The regulator has been specifically designed to operate in the automotive environment and will survive reverse battery connections, +40V load dump transients, and double-battery jumps (see Section 1.6, “Internal Voltage Regulator”).

住友压力式膜组件资料(中文版)

3

生化处理出水

OPM 系列膜组件 (0.1 m) (三级处理)

浊度 : < 0.2 NTU

( 数据仅供参考, 不提供任何保证. )

PTFE是什么 ?

4

PTFE = Polytetrafluoroethylene

FF

CC

FF n

PVDF : -CF2-CH2-n PE : -CH2-CH2-n

耐化学药剂性能 耐热性能

TMP (kPa)

5. 结果

3 2.5

2 1.5

1 0.5

0

Flux (m3/n2/day)

12/8 12/13 12/18 12/23 12/28

1/2 1/7 1/12 1/17 1/22 1/27 2/1 2/6 2/11 2/16 2/21 2/26 3/3 3/8 3/13 3/18 3/23 3/28 4/2 4/7 4/12 4/17 4/22 4/27 5/2 5/7 5/12 5/17 5/22 5/27 6/1 6/6 6/11 6/16 6/21

相当于MBR池中使用

4个月

结果 无破损

破裂

产品特点2 –良好的耐久性(4)

15

耐碱性

含油、硅和硅酸盐的废水过滤

碱液清洗

★化学清洗测试

用 4 wt% NaOH 浸泡 - 50℃ × 10 days

★浸泡以后・・・・・

住友 POREFLON

PVDF A

PVDF B

无变化!

膜丝出现断裂

产品特点2 – 良好的耐久性(4)

产品特点1 – 高通量(2)

10

不对称的微观结构

支撑层孔径 2μm

过滤层孔径 0.1μm

产品特点2 – 良好的耐久性(1)

维萨拉MAWS201中文版说明书

维萨拉HydroMet TM自动气象站MAWS201MAWS201是一款便携式自动气象站,设计可用于各种环境和任何天气情况。

产品特点●经济,部署快捷,便于携带的自动气象站●适用于多种用途:气象研究、环境影响研究、应急响应、废弃物管理●设计紧凑、结实耐用且重量轻●功耗低●经过现场验证的可靠性和精度●多种传感器和设置选项可供选择●丰富的计算与数据记录能力便于安装与配置MAWS201的安装非常方面。

每个传感器均配有易于安装的电缆和连接器。

所有组件均可轻松装配,不需要任何特殊工具。

维萨拉安装软件Lizard可简化传感器测量、计算、数据记录传输的配置工作。

安装模板可引导您完成初始设置,如果你想进一步完成自定义设置,多个设置选项可供选择。

高精度传感器基本的传感器组件可测量风速/风向、大气压力、空气温度、相对湿度和降水。

选配传感器可实现诸如土壤/水温度、太阳总辐射和净辐射、土壤湿度和水位的测量。

传感器性能在各种环境条件下已通过现场试验。

全天候可靠性MAWS201在任何天气条件下均能够可靠的工作:其耐腐蚀阳极铝材质的结构即坚固又防水。

电缆采用高品质聚氨酯制造,并配有完全符合IP68标准的模压防水连接器。

所有输入均可有防浪涌保护。

质量控制软件可根据用户设定的气候限值以及连续测量值之间的阶跃变化检验传感器数据。

每项统计计算均具备其自身的验证流程,而且所有这些均可由用户进行配置。

统计计算统计计算包括最小值、最大值、平均值、标准差和累积值。

所有这些值均基于用户自定义的时间间隔进行计算。

所有极限值均具有时间标记。

此外,还可提供包括单位换算、露点、霜点、QNH、QFF、QFE、蒸发蒸腾量、日照时数、森林火灾指数、风寒程度、热应力等在内的数据。

多功能数据输出用户可自由配置数据输出格式,多个现成模板让这一过程变得更加容易。

报警模块可在测量值或计算值超出用户设定的阈值时向用户发出通知。

报警模块可配置用于发生报警信息、修改时间间隔、记录数据或设定控制外部设备的激励电压等。

ESMQ161VSN102MQ30S中文资料(United Chemi-Con)中文数据手册「EasyDatasheet - 矽搜」

25℃价值和

20℃价值不得超过

Rated Voltage ( V ) Z ( 25 C ) / Z ( 20 C )

160 - 250 4

315 - 400 8

420, 450 8

频率(Hz)

DC Rated Voltage 160 - 250V 315 - 450V

50Hz

120Hz

300Hz

1kHz

ESMQ181VSN471MP25S ESMQ181VSN561MP30S ESMQ181VSN681MP30S ESMQ181VSN821MP35S ESMQ181VSN102MP45S ESMQ181VSN122MP50S ESMQ181VSN681MQ25S ESMQ181VSN821MQ30S ESMQ181VSN102MQ35S ESMQ181VSN122MQ40S ESMQ181VSN152MQ45S ESMQ181VSN182MQ50S ESMQ181VSN102MR25S ESMQ181VSN122MR30S ESMQ181VSN152MR35S ESMQ181VSN182MR40S ESMQ181VSN222MR45S ESMQ181VSN122MA25S ESMQ181VSN152MA30S ESMQ181VSN182MA30S ESMQ181VSN222MA40S ESMQ181VSN272MA45S ESMQ181VSN332MA50S

ESMQ161VSN561MP25S ESMQ161VSN681MP30S ESMQ161VSN821MP35S ESMQ161VSN102MP40S ESMQ161VSN122MP45S ESMQ161VSN152MP50S ESMQ161VSN102MQ30S ESMQ161VSN122MQ35S ESMQ161VSN152MQ40S ESMQ161VSN182MQ45S ESMQ161VSN122MR25S ESMQ161VSN152MR30S ESMQ161VSN182MR35S ESMQ161VSN222MR40S ESMQ161VSN152MA25S ESMQ161VSN182MA30S ESMQ161VSN222MA35S ESMQ161VSN272MA40S ESMQ161VSN332MA45S ESMQ161VSN392MA50S

UFM 型超声波流量计 使用说明书

UFMULTRASONIC FLOW METER UFM型超声波流量计使用说明书UFM-DT-JS-1035-2019(A)感谢您选择丹东通博电器(集团)有限公司的产品。

本使用说明书给您提供有关安装、连接和调试以及针对维护、故障排除和贮存方面的重要信息。

请在安装调试前仔细阅读并将它作为产品的组成部分保存在仪表的近旁,供随时翻阅。

并可通过下载本说明书。

如未遵照本说明书进行操作,则本仪表所提供的防护可能会被破坏。

商标、版权和限制说明通博、通博电器、通博泵业、DDTOP、均为公司的注册商标。

本仪表的性能规格自发布之日起生效,如有更改,恕不另行通知。

丹东通博电器(集团)有限公司有权在任何时候对本说明书所述的产品进行修改,恕不另行通知。

质保丹东通博电器(集团)有限公司保证所有刮板流量计自出厂之日起,一年之内无材料和制造工艺方面的缺陷。

在质保期内,如产品出现质量问题而返回,提出的索赔要求经制造厂检验后确定属于质保范围内,则丹东通博电器(集团)有限公司负责免费为买方(或业主)维修或更换。

丹东通博电器(集团)有限公司对因设备使用不当,劳动力索赔、直接或后续损伤以及安装和使用设备所引起的费用概不负责。

除了关于丹东通博电器(集团)有限公司某些产品的特殊书面保修证明,丹东通博电器(集团)有限公司不提供任何明示或暗示的质量保证。

质量丹东通博电器(集团)有限公司通过了ISO9001质量体系认证,产品生产的全过程均严格依照质量体系的规定范围执行,对产品和服务质量提供最强有力的保证。

1安全提示 (4)1.1爆炸可能会导致死亡或严重伤害。

(4)1.2过程泄漏可能导致严重伤害或死亡。

(4)1.3不遵守安全安装准则可能导致死亡或严重受伤。

(4)2产品说明 (4)2.1 产品主要结构 (4)2.2工作原理 (4)2.5仓储 (4)3主要参数 (5)4开箱及检查 (5)4.1开箱验货注意事项 (5)4.2检查内容 (5)5界面与操作 (5)5.1主界面 (5)5.2菜单界面 (6)5.3键盘与操作 (6)6参数设置 (6)6.1参数设置 (6)6.2显示设置 (9)7调试 (9)7.1单点校准 (9)7.2两点校准和多点校准 (9)7.3校准方法 (9)8系统设置 (10)8.1语言 (10)8.2日期时间 (10)8.3恢复出厂设置 (10)8.4工厂设置 (10)9常见问题解答 (10)9.1怎样辨别管道中的流体流向 (10)9.2怎样设置零点切除避免无效累积 (10)9.3怎样设置4~20mA输出 (11)附录常用参数 (11)1安全提示出于安全的原因,明确禁止擅自改装或改变产品,维修或替换只允许使用由制造商指定的配件。

ESMH201VNN821MQ45T中文资料(United Chemi-Con)中文数据手册「EasyDatasheet - 矽搜」

22 25 22 30 22 30 22 35 22 40 22 50 25.4 25 25.4 25 25.4 30 25.4 35 25.4 40 25.4 45 25.4 50 30 25 30 25 30 30 30 35 30 40 30 45 30 50 35 25 35 30 35 30 35 35 35 40 35 45 35 63 35 80 40 25 40 30 40 35 40 40 40 50 40 63 40 80

Tan ( DF ) Max.† 0.60 0.50 0.40 0.30 0.25 0.20 0.15

*0.10*

0.15

*0.15 maximum for 35mm and 40mm diameter.

†For rated voltages ≤ 63V, values are not valid for case sizes >35mmin diameter or >63V, values are not valid for case sizes 35mmin diameter or 50mmin length.

P

W

W1

W2

VSN Ø22 - Ø 30 4.0 0.5

VSN Ø35 VNN Ø22 - Ø 35

3.5 0.5 5.8 1.0 1.5 0.2

1.0

1.0

VND Ø35 - Ø 40 5.8 1.0

注意:

* 使用仅用于机械支撑空白的终端.空白终端不能连接到PC板上的焊 料迹,但可从负极或正极端子电隔离.

18场

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

(E S)MH 2 0 1 V S N 4 7 1M的p 3 5吨

UF201资料

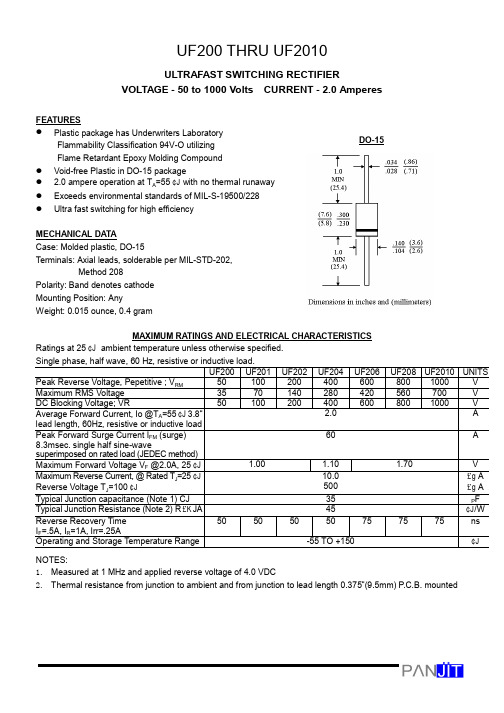

UF200 THRU UF2010ULTRAFAST SWITCHING RECTIFIERVOLTAGE - 50 to 1000 Volts CURRENT - 2.0 AmperesFEATURESl Plastic package has Underwriters Laboratory Flammability Classification 94V-O utilizingFlame Retardant Epoxy Molding Compound l Void-free Plastic in DO-15 packagel 2.0 ampere operation at T A =55¢J with no thermal runaway l Exceeds environmental standards of MIL-S-19500/228l Ultra fast switching for high efficiencyMECHANICAL DATACase: Molded plastic, DO-15Terminals: Axial leads, solderable per MIL-STD-202, Method 208Polarity: Band denotes cathode Mounting Position: AnyWeight: 0.015 ounce, 0.4 gramMAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICSRatings at 25¢J ambient temperature unless otherwise specified.Single phase, half wave, 60 Hz, resistive or inductive load.UF200UF201UF202UF204UF206UF208UF2010UNITS Peak Reverse Voltage, Pepetitive ; V RM 501002004006008001000V Maximum RMS Voltage 3570140280420560700V DC Blocking Voltage; VR 501002004006008001000VAverage Forward Current, Io @T A =55¢J 3.8”lead length, 60Hz, resistive or inductive load 2.0APeak Forward Surge Current I FM (surge)8.3msec. single half sine-wavesuperimposed on rated load (JEDEC method)60A Maximum Forward Voltage V F @2.0A, 25¢J1.00 1.10 1.70V Maximum Reverse Current, @ Rated T J =25¢J Reverse Voltage T J =100¢J10.0500£g A £g A Typical Junction capacitance (Note 1) CJ 35P F Typical Junction Resistance (Note 2) R £K JA 45¢J /W Reverse Recovery Time I F =.5A, I R =1A, Irr=.25A50505050757575ns Operating and Storage Temperature Range -55 TO +150¢JNOTES:1. Measured at 1 MHz and applied reverse voltage of 4.0 VDC2. Thermal resistance from junction to ambient and from junction to lead length 0.375”(9.5mm) P.C.B. mountedDO-15RATING AND CHARACTERISTIC CURVES UF200 THRU UF2010NOTE:1.Rise Time = 7ns max.Input Impedance = 1 megohm. 22pF 2.Rise Time = 10ns max. Source Impedance = 50 Ohms50 ns/cmFig. 1-REVERSE RECOVERY TIME CHARACTERISTIC AND TEST CIRCUIT DIAGRAMFORWARD VOLTAGE-VFM(Vpk)AMBIENT TEMPERATURE, ¢JFig. 2-FORWARD CHARACTERISTICS Fig. 3-FORWARD CURRENT DERATING CURVEREVERSE VOLTAGE, VOLTS2040 NUMBER OF CYCLES AT 60HzFig. 4-TYPICAL JUNCTION CAPACITANCE Fig. 5-PEAK FORWARD SURGE CURRENT。

最新201不锈钢板简介

●201不锈钢板简介:中国标准(GB)-牌号:1Cr17Mn6Ni5N ,201不锈钢板联众牌号LH低镍L1高镍L4(202不锈钢板,宝钢BN1(201不锈钢板,BN4(202不锈钢板),通过Mn,N元素替代Ni元素开发的200系列奥氏体不锈钢。

该钢种具有较好的耐蚀性和冷热加工性能,替代室内、内陆城市室外等腐蚀性不高的环境使用的304制品。

,主要有以下几种200系钢种:J1,J3,J4,201,202。

后来又出现了对镍含量控制更低的200等钢种,至于201C,就是在这后期中国个别钢厂研发的201的引申钢种,201的国家标准牌号是:1Cr17Mn6Ni5N,201C在201的基础上继续减少镍的含量,增加锰的含量。

201不锈钢板的定义:200 系列Cr—Mn 不锈钢镍价的波动促使许多的生产商寻求另一种与AISI304 性能相同的奥氏体不锈钢替代产品。

在20 世纪30 年代初,生产出了最初的铬锰(Cr—Mn)奥氏体不锈钢,钢中锰元素取代了部分镍。

此后,对具体的成分比例进行了更多的研究,使用了氮(N)和铜(Cu),控制强烈影响材料性能的元素碳(C)和硫(S)。

200 系列不锈钢的应用在印度所以成功,是由于在一些特定的用途中有可能替代304 不锈钢,而且没有危险。

与此相反,在其他地方,在市场上售处的200 系列不锈钢几乎没有控制硫、碳含量、存在着损害终端用户和不锈钢形象的风险。

●201不锈钢板用途:201不锈钢材、具有耐酸、耐碱,密度高、抛光无气泡、无针孔等特点,是生产各种表壳、表带底盖优质材料等。

主要用于做装饰管,工业管,一些浅拉伸的制品.●201不锈钢板性能:抗拉强度:100,000 to 180,000 psi 屈服强度:50,000 to 150,000 psi 伸长率:55 to 60% 弹性模量:29,000,000 psi 密度:.280lbs/cubic inch(密度7.93g/cm3)●201不锈钢板化学成分:201不锈钢板的元素锰(和氮)取代部分或全部镍有可能生产更低镍含量达不到平衡而形成了铁素体,为此,200 系列不锈钢中的铬铁含量降到15%-16%,某些情况下降到了13%-14%,其耐腐蚀性是不能与304和其他类似的钢比的。

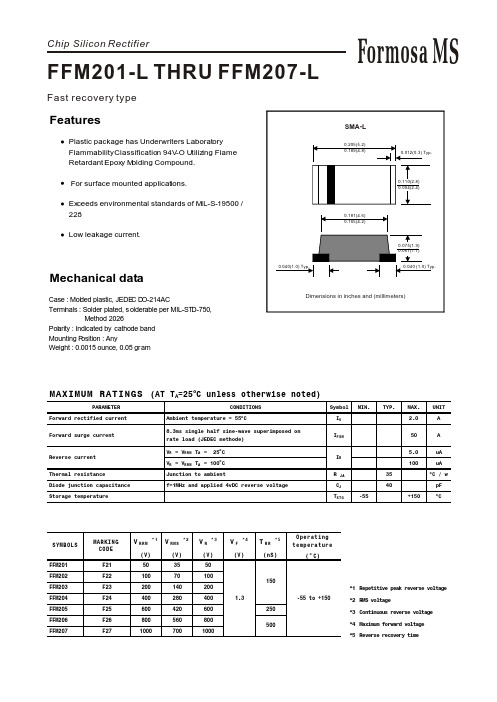

FFM201-L资料

*2 RMS voltage *3 Continuous reverse voltage *4 Maximum forward voltage *5 Reverse recovery time

元器件交易网

RATING AND CHARACTERISTIC CURVES (FFM201-L THRU FFM207-L)

元器件交易网

Chip Silicon Rectifier

FFM201-L THRU FFM207-L

Fast recovery type

Formosa MS

SMA-L

0.205(5.2) 0.189(4.8) 0.012(0.3) Typ.

Features

Plastic package has Underwriters Laboratory Flammability Classification 94V-O Utilizing Flame Retardant Epoxy M olding Compound. For surface mounted applications. Exceeds environmental standards of MIL-S-19500 / 228 Low leakage current.

PEAK FORWAARD SURGE CURRENT,(A)

50

0.2

.02

.6

.8

1.0

1.2

1.4

1.6

1.8

2.0

FORWARD VOLT AGE,(V)

40

FIG.3- TEST CIRCUIT DIAGRAM AND REVERSE RECOVERY TIME CHARACTERISTICS

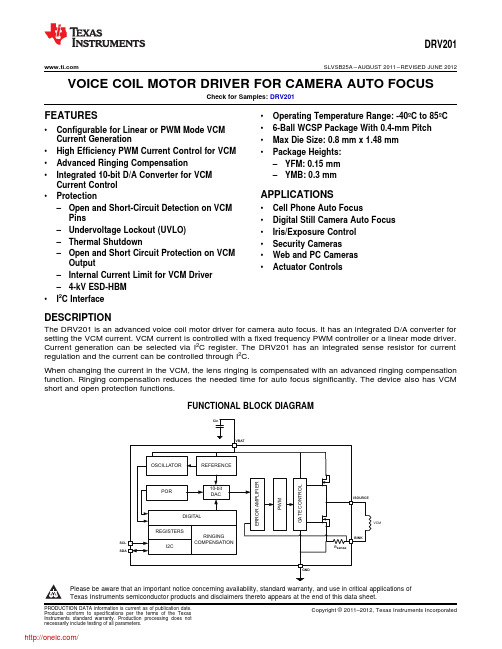

DRV201YFMT;DRV201YFMR;DRV201EVM;中文规格书,Datasheet资料

VCMDRV201 SLVSB25A–AUGUST2011–REVISED JUNE2012 VOICE COIL MOTOR DRIVER FOR CAMERA AUTO FOCUSCheck for Samples:DRV201FEATURES•Operating Temperature Range:-40ºC to85ºC•6-Ball WCSP Package With0.4-mm Pitch •Configurable for Linear or PWM Mode VCMCurrent Generation•Max Die Size:0.8mm x1.48mm•High Efficiency PWM Current Control for VCM•Package Heights:•Advanced Ringing Compensation–YFM:0.15mm•Integrated10-bit D/A Converter for VCM–YMB:0.3mmCurrent ControlAPPLICATIONS•Protection–Open and Short-Circuit Detection on VCM•Cell Phone Auto FocusPins•Digital Still Camera Auto Focus –Undervoltage Lockout(UVLO)•Iris/Exposure Control–Thermal Shutdown•Security Cameras–Open and Short Circuit Protection on VCM•Web and PC CamerasOutput•Actuator Controls–Internal Current Limit for VCM Driver–4-kV ESD-HBM•I2C InterfaceDESCRIPTIONThe DRV201is an advanced voice coil motor driver for camera auto focus.It has an integrated D/A converter for setting the VCM current.VCM current is controlled with a fixed frequency PWM controller or a linear mode driver. Current generation can be selected via I2C register.The DRV201has an integrated sense resistor for current regulation and the current can be controlled through I2C.When changing the current in the VCM,the lens ringing is compensated with an advanced ringing compensation function.Ringing compensation reduces the needed time for auto focus significantly.The device also has VCM short and open protection functions.FUNCTIONAL BLOCK DIAGRAMPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2011–2012,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.CB A21NanoFree YFM PACKAGE(BOTTOM VIEW)YMB package package markings:YM =YEAR /MONTH DATE CODE D =DAY OF LASER MARK S =ASSEMBLY SITE CODE 0=Pin A1(Filled Solid)NanoFree YMB PACKAGE(TOP VIEW)NanoFree YFM PACKAGE(TOP VIEW)C B A21NanoFree YMB PACKAGE(BOTTOM VIEW)YFM package has no top side markingsDRV201SLVSB25A –AUGUST 2011–REVISED JUNE 2012This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.ORDERING INFORMATION (1)T APACKAGE (2)ORDERABLE PART NUMBERYFM DRV201YFMR -40°C to 85°CYMBDRV201YMBR(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TI web site at .(2)Package drawings,thermal data,and symbolization are available at /packaging .DEVICE INFORMATIONTERMINAL FUNCTIONSTERMINAL I/ODESCRIPTIONNAME NO.VBAT 2A Power GND 1A GroundI_SOURCE 2B Voice coil positive terminal I_SINK 1B Voice coil negative terminal SCL 2C I I 2C serial interface clock inputSDA1CI/O I 2C serial interface data input/output (open drain)2Submit Documentation FeedbackCopyright ©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):DRV201DRV201 SLVSB25A–AUGUST2011–REVISED JUNE2012ABSOLUTE MAXIMUM RATINGSover operating free-air temperature range(unless otherwise noted)(1)VALUE UNIT VBAT,ISOURCE,ISOURCE pin voltage range(2)–0.3to5.5VVoltage range at SDA,SCL–0.3to3.6VContinuous total power dissipation Internally limitedθJA Junction-to-ambient thermal resistance(3)130°C/WT J Operating junction temperature-40to125°CT A Operating ambient temperature-40to85°CT stg Storage temperature-55to150°C(HBM)Human body model±4000ESD rating V(CDM)Charged device model±500(1)Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied.Exposure to absolute maximum rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to network ground terminal.(3)This thermal data is measured with high-K board(4-layer board).ELECTRICAL CHARACTERISTICSOver recommended free-air temperature range and over recommended input voltage range(typical at an ambient temperature range of25°C)(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT INPUT VOLTAGEV BAT Input supply voltage 2.5 3.7 4.8VV BAT rising 2.2V UVLO Undervoltage lockout threshold VV BAT falling2V HYS Undervoltage lockout hysteresis50100250mV INPUT CURRENTInput supply current shutdown,I SHUTDOWN MAX:V BAT=4.4V0.151µAincludes switch leakage currentsInput supply current standby,includesI STANDBY MAX:V BAT=4.4V120200µAswitch leakage currentsSTARTUP,MODE TRANSITIONS,AND SHUTDOWNt1Shutdown to standby100µst2Standby to active100µst3Active to standby100µst4Shutdown time Active or standby to shutdown0.51ms VCM DRIVER STAGEResolution10bitsI RES Relative accuracy-1010LSB Differential nonlinearity-11Zero code error0mAOffset error At code323mA%of Gain error±3FSR Gain error drift0.30.4%/°COffset error drift0.30.5%/°C I MAX Maximum output current102.3mAI LIMIT Average VCM current limit See(1)110160240mA(1)During short circuit condition driver current limit comparator will trip and short is detected and driver goes into STANDBY and short flagis set high in the status register.Copyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback3Product Folder Link(s):DRV201DRV201SLVSB25A–AUGUST2011–REVISED ELECTRICAL CHARACTERISTICS(continued)Over recommended free-air temperature range and over recommended input voltage range(typical at an ambient temperature range of25°C)(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Minimum VCM code for OPEN andI DETCODE See(2)256mASHORT detectionf SW Switching frequency Selectable through CONTROL register0.54MHz V DRP Internal dropout See(3)0.4VL VCM VCM inductance30150µHR VCM VCM resistance1122ΩLENS MOVEMENT CONTROLt set1Lens settling time±10%error band2/f VCM mst set2Lens settling time±10%error band1/f VCM ms VCM resonance frequency50150Hzf VCM When1/f VCM compensation is used-1010VCM resonance frequency tolerance%When2/f VCM compensation is used-3030LOGIC I/Os(SDA AND SCL)V=1.8V,SCL-4.25 4.25I IN Input leakage currentµAV=1.8V,SDA-11R PullUp I2C pull-up resistors SDA and SCL pins 4.7kΩV IH Input high level See(4) 1.17 3.6VV IL Input low level See(5)00.63Vt TIMEOUT SCL timeout for shutdown detection0.51msR PD Pull down resistor at SCL line500kΩf SCL I2C clock frequency400kHz INTERNAL OSCILLATORf OSC Internal oscillator20°C≤T A≤70°C-33%Frequency accuracy-40°C≤T A≤85°C-55% THERMAL SHUTDOWNT TRIP Thermal shutdown trip point140°C(2)When testing VCM open or short this is the recommended minimum VCM code(in dec)to be used.(3)This is the voltage that is needed for the feedback resistor and high side driver.It should be noted that the maximum VCM resistance islimited by this voltage and supply voltage.E.g.3-V supply maximum VCM resistance is:R VCM=(V BAT–V DRP)/I VCM=(3V-0.4V)/102.3mA=25.4Ω.(4)During shutdown to standby transition V IH low limit is1.28V.(5)During shutdown to standby transition V IL high limit is0.51V.4Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):DRV201VCMDRV201V inDRV201SLVSB25A –AUGUST 2011–REVISED JUNE 2012PARAMETER MEASUREMENT INFORMATIONList of components:•C in -Panasonic ECJ0EB1A105M •VCM -Mitsumi VCM KAF-V85S60•Actuator size:8.5x 8.5x 3.4(mm)•Lens in the VCM:M6(Pitch:0.35)•Weight:75mg •TTL:4.2mm •FB:1.1mmCopyright ©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback5Product Folder Link(s):DRV201DRV201SLVSB25A–AUGUST2011–REVISED TYPICAL CHARACTERISTICSFigure1.Lens Positions With and Without Ringing Figure2.Lens Positions With and Without RingingCompensation With100-µm Step on the Lens Position Compensation With100-µm Step on the Lens Position,Zoomed InFigure3.Lens Positions With and Without Ringing Figure4.Lens Positions With and Without RingingCompensation With30-µm Step on the Lens Position Compensation With30-µm Step on the Lens Position,Zoomed In6Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):DRV201Vbat ISC/SCLmodeDAC DRV201 SLVSB25A–AUGUST2011–REVISED JUNE2012FUNCTIONAL DESCRIPTIONThe DRV201is intended for high performance autofocus in camera modules.It is used to control the current in the voice coil motor(VCM).The current in the VCM generates a magnetic field which forces the lens stack connected to a spring to move.The VCM current and thus the lens position can be controlled via the I2C interface and an auto focus function can be implemented.The device connects to a video processor or image sensor through a standard I2C interface which supports up to 400-kbit/s data rate.The digital interface supports IO levels from1.8V to3.3V.All pins have4-kV HBM ESD rating.When SCL is low for at least0.5ms,the device enters SHUTDOWN mode.If SCL goes from low to high the driver enters STANDBY mode in less than100μs and default register values are set as shown in Figure5. ACTIVE mode is entered whenever the VCM_CURRENT register is set to something else than zero.Figure5.Power Up and Down SequenceVCM current can be controlled via an I2C interface and VCM_CURRENT registers.Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed.This mechanical ringing is compensated internally by generating an optimized ramp whenever the current value in the VCM_CURRENT register is changed.This enables a fast autofocus algorithm and pleasant user experience.Current in the VCM can be generated with a linear or PWM control.In linear mode the high side PMOS is configured as a current source and current is set by the VCM_CURRENT control register.In PWM control the VCM is driven with a half bridge driver.With PWM control the VCM current is increased by connecting the VCM between V BAT and GND through the high side PMOS and then released to a‘freewheeling’mode through the sense resistor and low side NMOS.PWM mode switching frequency can be selected from0.5MHz up to4MHz through a CONTROL register.PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.Copyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback7Product Folder Link(s):DRV201DRV201SLVSB25A–AUGUST2011–REVISED MODES OF OPERATIONSHUTDOWN If the driver detects SCL has a DC level below0.63V for duration of at least0.5ms,the driver will enter shutdown mode.This is the lowest power mode of operation.The driver will remain in shutdown for as long as SCL pin remain low.STANDBY If SCL goes from low to high the driver enters STANDBY mode and sets the default register values.In this mode registers can be written to through the I2C interface.Device will be in STANDBY mode when VCM_CURRENT register is set to zero.From ACTIVE mode the device will enter STANDBY if theSW_RST bit of the CONTROL register is set.In this case all registers will be reset to default values.STANDBY mode is entered from ACTIVE mode if any of the following faults occur:Overtemperature protection fault(OTPF),VCM short(VCMS),or VCM open(VCMO).WhenSTANDBY mode is entered due to a fault condition current register is cleared.ACTIVE The device is in ACTIVE mode whenever the VCM_CURRENT control is set to something else than zero through the I2C interface.In ACTIVE mode VCM driver output stage is enabled all the time resulting in higher power consumption.The device remains in active mode until the SW_RST bit in the CONTROL register is set,SCL is pulled low for duration of0.5ms,VCM_CURRENT control is set to zero,or any of the following faults occur:Over temperature protection fault(OTPF),VCM short(VCMS),or VCM open (VCMO).If active mode is entered after fault the status register is automatically cleared.8Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):DRV201DRV201 SLVSB25A–AUGUST2011–REVISED JUNE2012VCM DRIVER OUTPUT STAGE OPERATIONCurrent in the VCM can be controlled with a linear or PWM mode output stage.Output stage is enabled in ACTIVE mode which can be controlled through VCM_CURRENT control register and the output stage mode is selected from MODE register bit PWM/LIN.In linear mode the output PMOS is configured to a high side current source and current can be controlled from a VCM_CURRENT registers.In PWM control the VCM is driven with a half bridge driver.With PWM control the VCM current is increased by connecting the VCM between V BAT and GND through the high side PMOS and then released to a‘freewheeling’mode through the sense resistor and low side NMOS.Current in the VCM is sensed with a1-Ωsense resistor which is connected into an error amplifier input where the other input is controlled by the10-bit DAC output. PWM mode switching frequency can be selected from0.5MHz up to4MHz through a CONTROL register.PWM or linear mode can be selected with the PWM/LIN bit in the MODE register.RINGING COMPENSATIONVCM current can be controlled via an I2C interface and VCM_CURRENT registers.Lens stack is connected to a spring which causes a dampened ringing in the lens position when current is changed.This mechanical ringing is compensated internally by generating an optimized ramp whenever the current value in the VCM_CURRENT register is changed.This enables a fast auto focus algorithm and pleasant user experience.Ringing compensation is dependent on the VCM resonance frequency and this can be controlled via VCM_FREQ register(07h)from50Hz up150Hz.Table1shows the VCM_FREQ register setting for each resonance frequency in1-Hz steps.If more accurate resonance frequency is available,the control value can be calculated with Equation1.Ringing compensation is designed in a way that it can tolerate±30%frequency variation in the VCM resonance frequency when2/f VCM compensation is used and±10%variation with1/f VCM so only statistical data from the VCM is needed in production.Copyright©2011–2012,Texas Instruments Incorporated Submit Documentation Feedback9Product Folder Link(s):DRV201DRV201SLVSB25A–AUGUST2011–REVISED Table1.VCM Resonance Frequency Control Register(07h)Table VCM VCM_FREQ[7:0](07h)VCM VCM_FREQ[7:0](07h)VCM VCM_FREQ[7:0](07h) Resonance Resonance ResonanceFrequency Frequency FrequencyDEC BIN DEC BIN DEC BIN [Hz][Hz][Hz]50008415410011010118220110111005171118515710011101119222110111105214111086160101000001202231101111153211010187162101000101212241110000054271101188165101001011222261110001055341000108916710100111123227111000115640101000901701010101012422811100100574610111091172101011001252291110010158521101009217410101110126231111001115958111010931771011000112723211101000606311111194179101100111282331110100161681000100951811011010112923411101010627310010019618310110111130235111010116378100111097185101110011312361110110064831010011981871011101113223811101110658810110009918910111101133239111011116692101110010019110111111134240111100006796110000010119311000001135241111100016810111001011021951100001113624211110010691051101001103197110001011372431111001170109110110110419811000110138244111101007111311100011052001100100013924511110101721161110100106202110010101402461111011073120111100010720411001100141247111101117412411111001082051100110114224811111000751271111111109207110011111432491111100176130100000101102081101000014425011111010771341000011011121011010010145251111110117813710001001112212110101001462511111101179140100011001132131101010114725211111100801431000111111421511010111148253111111018114610010010115216110110001492541111111082149100101011162171101100115025511111111831521001100011721911011011---10Submit Documentation Feedback Copyright©2011–2012,Texas Instruments IncorporatedProduct Folder Link(s):DRV201分销商库存信息:TIDRV201YFMT DRV201YFMR DRV201EVM。

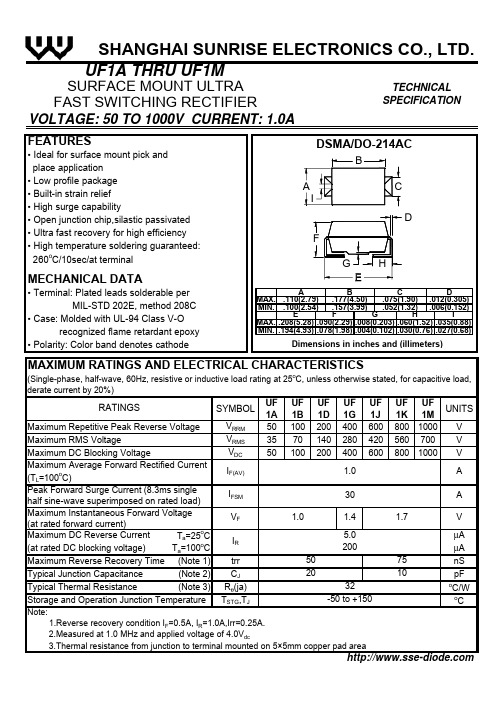

UF1M资料

UF 1A

UF 1D 200 140 200

UF 1G 400 280 400

UF 1J 600 420 600

UF UF UNITS 1K 1M 800 1000 V 560 700 V 800 1000 V

A A 1.7 V µA µA 75 10

FEATURES

• Ideal for surface mount pick and place application • Low profile package • Built-in strain relief • High surge capability • Open junction chip,silastic passivated • Ultra fast recovery for high efficiency • High temperature soldering guaranteed: 260oC/10sec/at terminal

o

nS pF C/W o C

元器件交易网

SHANGHAI SUNRISE ELECTRONICS CO., LTD. UF1A THRU UF1M

SURFACE MOUNT ULTRA FAST SWITCHING RECTIFIER

VOLTAGE: 50 TO 1000V CURRENT: 1.0A

C A B D .075(1.90) .012(0.305) .177(4.50) MAX. .110(2.79) .157(3.99) .052(1.32) .006(0.152) MIN. .100(2.54) E F G H I MAX. .208(5.28) .090(2.29) .008(0.203) .060(1.52) .035(0.88) MIN. .194(4.93) .078(1.98) .004(0.102) .030(0.76) .027(0.68)

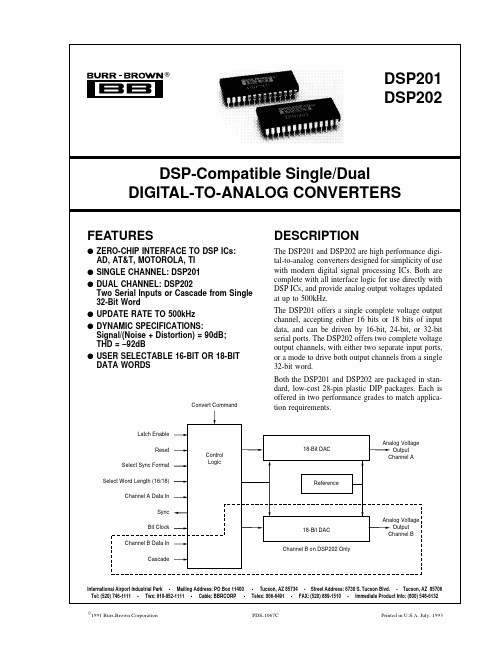

DSP201资料

ZERO-CHIP INTERFACE TO DSP ICs:DESCRIPTIONThe DSP201 and DSP202 are high performance digi-tal-to-analog converters designed for simplicity of use with modern digital signal processing ICs. Both are complete with all interface logic for use directly withDSP-Compatible Single/Dual DIGITAL-TO-ANALOG CONVERTERSSPECIFICATIONSELECTRICALT A = 0°C to 70°C, Output Update Frequency, f S, = 400kHz, V A+ = V D+ = +5V, V A– = V D– = –5V, unless otherwise specified.NOTES: (1) The data transfer clock must be at least 24 times the update rate for the standard mode, and 40 times the update rate in the DSP202 Cascade Mode.(2) All dynamic specifications are based on 2048-point FFTs. (3) Data for the 1kHz test is bandlimited to 0 to 20kHz. Data for the 10kHz test is bandlimited to 0 to 40kHz. (4) All specifications in dB are referred to a full-scale output, ±3Vp-p. (5) Adjustable to zero with external potentiometer.®DSP201/2022®DSP201/2023BIPOLAR ZERO ERROR AND GAIN ERRORvs TEMPERATUREAmbient Temperature (°C)B i p o l a r Z e r o E r r o r (m V )10 5–5 –10–50–25255075100G a i n E r r o r (% o f 6V F u l l S c a l e R a n g e )0.30.20.1–0.1INTEGRAL AND DIFFERENTIAL LINEARITY ERRORvs TEMPERATURE (For Worst-Case Codes.)Ambient Temperature (°C)A b s o l u t e V a l u e o f E r r o r (%)0.020 0.0150.0100.0050.0–50–25255075100SIGNAL-TO-(NOISE + DISTORTION)vs OUTPUT UPDATE RATEOutput Update Rate (kHz)0.4440400S i g n a l -t o -(N o i s e + D i s t o r t i o n ) R a t i o (d B )TOTAL HARMONIC DISTORTIONvs OUTPUT FREQUENCYOutput Frequency (kHz)0.2220200–50 –60–70–80–90–100T o t a l H a r m o n i c D i s t o r t i o n (d B )SIGNAL-TO-(NOISE + DISTORTION) RATIO vs TEMPERATURE AND AMPLITUDEAmbient Temperature (°C)S i g n a l -t o -(N o i se +D i s t o r t i o n ) R a t i o (d B )100 90 80 70 60 50 40 30 20 10 0–50–25255075100DYNAMIC PERFORMANCE vs TEMPERATUREAmbient Temperature (°C)S I N A D , S N R a n d S F D R (d B )80 859095100–50–25255075100T H D (d B )–80 –85–90–95–100TYPICAL PERFORMANCE CURVEST A = +25°C; Update Frequency, f S = 400kHz; V A + = V D + = +5V; V A – = V D – = 5V; SWL = HIGH;CASC = LOW; Output Bandwidth Limited to 20kHz; unless otherwise noted.The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.®DSP201/2024INTERMODULATION DISTORTION vs TEMPERATUREAmbient Temperature (°C)I n t e r m o d u l a t i o n D i s t o r t i o n (d B )–85–90–95–100–105–50–25255075100POWER SUPPLY REJECTION vs SUPPLY RIPPLE FREQUENCYSupply Ripple Frequency (kHz)0.1110100–35–45–55–65–75S u p p l y R i p p l e R e j e c t i o n (d B )OUTPUT VOLTAGE SETTLING TIMESettling Time (µs)123456789100.1 0.010.001A c c u r a c y (% o f 6V F u l l S c a l e R a n g e )TYPICAL PERFORMANCE CURVES (CONT)T A = +25°C; Update Frequency, f S = 400kHz; V A + = V D + = +5V; V A – = V D – = 5V; SWL = HIGH; CASC = LOW;Output Bandwidth Limited to 20kHz; unless otherwise noted.The DSP201 and DSP202 are ESD (electrostatic discharge)sensitive devices, and normal standard precautions should be taken. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. When not in use,devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.PACKAGE INFORMATIONPACKAGE DRAWINGMODEL PACKAGE NUMBER (1)DSP201JP 28-Pin Plastic DIP 215DSP201KP 28-Pin Plastic DIP 215DSP202JP 28-Pin Plastic DIP 215DSP202KP28-Pin Plastic DIP215NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.ORDERING INFORMATIONABSOLUTE MAXIMUM RATINGSV A + to Analog Common ......................................................................+7V V A – to Analog Common...................................................................... –7V V D + to Digital Common ..................................................................... +7V V D – to Digital Common....................................................................... –7V Analog Common to Digital Common...................................................±1V Control Inputs to Digital Common ............................... –0.5 to V D + 0.5V Maximum Junction Temperature .....................................................150o C Internal Power Dissipation.............................................................825mW Lead Temperature (soldering, 10s)...............................................+300o C Thermal Resistance, θJA : Plastic DIP............................................50o C/W®DSP201/2025DSP201 PIN ASSIGNMENTSPIN #NAME DESCRIPTION 1V A ––5V Analog Power.2No Internal Connection.3No Internal Connection.4AGND Analog Ground.5No Internal Connection.6V D ++5V Digital Power.7V D ++5V Digital Power.8RESETReset. If LOW, DAC output will be 0V after two convert commands, and will remain there as long as the Reset input is LOW. If HIGH, normaloperation proceeds. Two convert commands are required after Reset goes from LOW to HIGH before the output will relate to the input word.9SSFSelect Sync Format In. Tie HIGH for use with Motorola and TI DSP ICs. Tie LOW for use with AT&T DSP ICs.10SWLSelect Word Length In. If HIGH, DSP201 accepts first 16 bits of data. If LOW, DSP201 accepts first 18 bits of data.11SYNC Data Synchronization Output. Active HIGH when SSF is HIGH, active LOW when SSF is LOW.12XCLK Data Transfer Clock Input.13SINSerial Data In. MSB first, Binary Two’s Comple-ment format.14No Internal Connection.15CONV Convert Command In. DAC is updated on falling edge, and initiates clocking new data in.16DGND Digital Ground.17ENABLELatch Enable In. If LOW, DAC output will be latched with new data word on falling edge of Convert Command. If HIGH, Convert Commands will be ignored.18DGND Digital Ground.19DGND Digital Ground.20V D ––5V Digital Power.21VOUT Voltage Out.22AGND Analog Ground.23VOS VOS Adjust In.24MSB MSB Adjust In.25VPOT Trim Reference Out for MSB adjustment.26V A ++5V Analog Power.27DGND Digital Ground.28AGNDAnalog Ground.DSP201 PIN CONFIGURATION®DSP201/2026DSP202 PIN CONFIGURATIONDSP202 PIN ASSIGNMENTSPIN #NAME DESCRIPTION1V A ––5V Analog Power.2MSBB Channel B MSB Adjust In.3VOSB Channel B VOS Adjust In.4AGNDB Channel B Analog Ground.5VOUTB Channel B Voltage Out.6V D ++5V Digital Power.7V D ++5V Digital Power.8RESETReset. If LOW, DAC output will be 0V after two Convert Commands, and will remain there as long as the Reset input is LOW. If HIGH, normaloperation proceeds. Two Convert Commands are required after Reset goes from LOW to HIGH before the output will relate to the input word.9SSFSelect Sync Format In. Tie HIGH for use with Motorola and TI DSP ICs. Tie LOW for use with AT&T DSP ICs.10SWLSelect Word Length In. If HIGH, DSP202 accepts first 16 bits of data. If LOW, DSP202 accepts first 18 bits of data. Must be HIGH if CASC is HIGH.11SYNC Data Synchronization Output. Active HIGH when SSF is HIGH, active LOW when SSF is LOW.12XCLK Data Transfer Clock Input.13SINAChannel A Serial Data In. MSB first, Binary Two’s Complement format. In Cascade Mode, connect to SINB and to DSP IC output.14SINBChannel B Serial Data In. MSB first, Binary Two’s Complement format. In Cascade Mode, connect to SINA and to DSP IC output.15CONV Convert Command In. DAC is updated on falling edge, and initiates clocking new data in.16CASCSelect Cascade Mode In. If HIGH, DSP202accepts a 32-bit word, and uses the first 16 bits to update channel A, and the second 16 bits to update channel B. In Cascade Mode, SINA and SINB are connected together. If CASC is LOW,data is strobed into both channels on each clock cycle.17ENABLELatch Enable In. If LOW, DAC output will be latched with new data word on falling edge of Convert Command. If HIGH, Convert Commands will be ignored.18DGND Digital Ground.19DGND Digital Ground.20V D ––5V Digital Power.21VOUTA Channel A Voltage Out.22AGNDA Channel A Analog Ground.23VOSA Channel A VOS Adjust In.24MSBA Channel A MSB Adjust In.25VPOT Trim Reference Out for MSB adjustments.26V A ++5V Analog Power.27DGND Digital Ground.28AGNDAnalog Ground.®DSP201/2027THEORY OF OPERATIONThe DSP201 and DSP202 are basic voltage output digital-to-analog converters with complete logic interface circuitry for ease of use with standard digital signal processing ICs.Data words are transmitted from the DSP IC on its serial port, leaving the DSP IC parallel ports free for digital communication.The DSP201 and DSP202 are pipelined internally. When the user gives a convert command at time t, two actions are initiated. First, the data stored in the internal shift registers following the previous convert command (at t – 1) is used to update the output D/A converters immediately. Second, the DSP201 or DSP202 transmits a synchronization pulse to the DSP IC and starts clocking new data into the shift register using the system Bit Clock. This data is then used to update the D/As when the t + 1 convert command is received.Both the DSP201 and DSP202 are 18-bit D/As internally.On-chip logic can be programmed to use 18-bits of data to update the D/A outputs, or can be programmed to update the D/A based on 16-bit data words. Additionally, the logic in the DSP202 can accept a 32-bit data word (the Cascade Mode), and update both D/A channels simultaneously with 16 bits each. All of these modes can be hard-wired or logic-controlled externally, so that no extra overhead on the part of the DSP IC is required.In the 16-bit modes, the DSP201 and DSP202 will append zeros to the 16-bits transferred to each of the internal D/As,which are full 18-bit converters. The 18-bit word-length mode can be used with DSP ICs programmed for either 24-bit or 32-bit output words, in which case the DSP201 or DSP202 will clock in the first 18-bits of data after the synchronization pulse, and ignore additional information on the serial line. When programmed to accept 16-bit words,the DSP201 and DSP202 can be used with DSP ICs pro-grammed to output 16-, 24-, or 32-bit words, and will ignore additional information after the first 16 bits on the serial line.The DSP201 and DSP202 are complete voltage output D/A converters, with on-chip references and output amplifiers to drive ±3V into 375Ω loads. State-of-the-art bipolar tech-nologies are used in the D/A section to maximize the output update rate, to maximize dynamic performance, and to eliminate glitch problems. Advanced plastic packaging meth-ods makes this performance attainable economically.BASIC OPERATIONDATA FORMAT AND OUTPUT LEVELSThe DSP201 and DSP202 accept serial data, MSB first, in standard Binary Two’s Complement format. The length of the data words can be selected as shown below, and the D/A output level generated by a specific input code is shown in Table I.As with all standard D/As, the output ranges from negative full scale (–3V) to 1 LSB below positive full scale (+3V –1LSB). The bipolar output amplifiers are designed to drive 375Ω loads at full speed and accuracy.UPDATING THE OUTPUTWith ENABLE (pin 17) LOW, the falling edge of a Convert Command arriving on CONV (pin 15) will immediately update the D/A outputs with the data stored in the internal shift registers following the previous Convert Command.The Convert Command can be asynchronous to any other signals or clocks without reducing accuracy, although sys-tem accuracy is often enhanced by synchronizing digital signals.For a full-scale change in the input code, the output will typically settle to within ±0.006% of its final level within 2.5µs. The slew rate of the output amplifier is typically 15V/µs, for a full power bandwidth close to 800kHz. All of the specifications and typical performance curves are achieved with a full 400kHz update rate, unless otherwise specified.The DSP201 and DSP202 are guaranteed operational to a full 500kHz update rate, which exceeds the maximum Bit Clock rate for most standard DSP ICs.DATA TRANSFERData is transmitted serially to the DSP201 or DSP202, and is clocked into the internal shift registers on the rising edge of the external Data Transfer Clock or Bit Clock (XCLK input on pin 12.) This clock can be as fast as 12MHz. The Data Transfer Clock can tolerate duty cycles from 40% to 60%.As indicated in the timing diagrams in Figure 1, either 16-or 18-bits of data will be clocked into the DSP201 or DSP202, or 32-bits will be clocked into the DSP202 in theINPUT CODEOUTPUT VOLTAGE16-BIT MODE AND HEX16-BIT MODE AND BINARY DSP202 CASCADE MODE18-BIT MODEDSP202 CASCADE MODE18-BIT MODE 0111...11117FFF 1FFFF +2.999908V2.999977V0000...00000000000000V 0V 1111...1111FFFF 3FFFF –92µV –23µV 1000 (00008000)20000–3.000000V –3.000000V Theoretical LSB Size91.6µV22.9µVTABLE I. Output Voltage vs Input Code.FIGURE 1. DSP201 and DSP202 Timing.®DSP201/2028®DSP201/2029Cascade Mode, but internal digital overhead requires addi-tional Data Transfer Clock cycles before a new Convert Command can be sent. The minimum time between Convert Commands is 24 times the Data Transfer Clock period for either the DSP201 or the DSP202 in standard modes, and 40times the Data Transfer clock period for the DSP202 in the Cascade Mode. There is no maximum time between Convert Commands.These additional clock cycles are used to set up the internal shift registers and logic, and are included in the specifica-tions for maximum update rate. This means a 12MHz Bit Clock can achieve the maximum specified update rate of 500kHz.DATA SYNCHRONIZATIONThe DSP201 and DSP202 have internal logic to generate a synchronization pulse (SYNC on pin 11) to signal the host processor to transmit data. The synchronization pulse is sent when a Convert Command is received, and the SYNC output changes on the rising edge of XCLK. Timing is shown in Figure 1.The synchronization pulse can be programmed to be either active High or active Low, depending on the logic level input on SSF (Select Sync Format on pin 9.) If SSF is LOW,SYNC will be normally HIGH, and will transmit a LOW pulse after a Convert Command is received. If SSF is HIGH,SYNC will be normally LOW, and will transmit a HIGH pulse after a Convert Command is received. The SYNC pulse will be as wide as one clock cycle on the Data Transfer Clock input on XCLK (pin 12.)SELECTING WORD LENGTHIf the Select Word Length input (SWL, pin 10) is HIGH, the DSP201 or DSP202 will accept 16 bits of data after a Convert Command, with the timing shown in Figure 1. After these 16bits, additional data on SIN (DSP201 pin 13) or SINA and SINB (DSP202 pins 13 and 14) will be ignored. Transparent to the user, the internal shift register will append two zeroes to the 16-bit data words before updating the D/As on the next Convert Command.If SWL is LOW, the DSP201 or DSP202 will clock 18 bits of data into the internal shift register after a Convert Com-mand, with the timing shown in Figure 1. Subsequent data on SIN (DSP201 pin 13) or SINA and SINB (DSP202 pins 13 and 14) will be ignored.In the 16-bit mode, an increment of 1 LSB will change the D/A output by approximately 91.6µV (the 6V full scale range divided by 216), while an LSB in the 18-bit mode will change the output approximately 22.9µV (6V/218).The DSP201 and DSP202 analog performance is tested in production using the 16-bit mode (with SWL HIGH), and the typical performance curves were generated using the 16-bit mode. Verification is made during final test that the 18-bit mode functions, but the extra resolution of these last two bits is not used when testing the analog performance.DSP202 CASCADE MODEIf CASC on the DSP202 (pin 16) is HIGH, the Cascade Mode is implemented. In this mode, SINA (pin 13) and SINB (pin 14) are strapped together and connected to the serial output port of an appropriate DSP IC or other data word source. A Convert Command initiates the transfer of a 32-bit word to the DSP202.In the Cascade Mode, care must be taken to make sure SWL (pin 10) is HIGH.LATCH ENABLEIf ENABLE (pin 17) is LOW, the D/A outputs will be latched with new data on the falling edge of the Convert Command. Taking ENABLE HIGH causes the DSP201 or DSP202 to ignore Convert Commands. With ENABLE HIGH when a Convert Command arrives at time t, data latched in the internal shift register after the Convert Com-mand at t – 1 is not latched to the D/As, but a new synchronization pulse is still generated and the data in the shift register is overwritten. This feature allows multiple DSP201s or DSP202s to share a single DSP IC and still be independently updated.RESETTaking RESET (pin 8) LOW will cause the D/As to output 0V after two Convert Commands are received. The two Convert Commands clear out the internal shift registers, and data input on the serial input lines will be ignored while RESET is low. This facilitates designing an analog output system that goes into a known, benign state either at power-up, after fault conditions or during a calibration cycle.ENABLE (pin 17) must be LOW when resetting the DSP201or DSP202 outputs to 0V.After RESET is taken HIGH, two Convert Commands are required before the output will relate to the input data. Also,ENABLE must be LOW for the data to be latched to the D/As.The first Convert Command again latches the outputs at 0V,and the second Convert Command drives the output to the level determined by the data clocked in after the first Convert Command.A RESET command after power up is not required for proper operation of the DSP201 or YOUT CONSIDERATIONSBecause of the high resolution, linearity and speed of the DSP201 and DSP202, system design problems such as ground path resistance, contact resistance and power supply quality become very important.GROUNDSTo achieve the maximum performance from the DSP201 or DSP202, care should be taken to minimize the effect of current flows in the system grounds that may corrupt the output voltages generated by the D/As. Pin 22 on the DSP201 and pins 4 and 22 on the DSP202 are the most®DSP201/20210critical internal grounds, and care should be taken especially at these points to make them as close as possible to the same potential as the system analog ground. The design of the DSP201 and DSP202 insures that these pins will have minimal current flowing through them.Internally, power currents are directed to the digital grounds (pins 18, 19, and 27) for internal digital currents, which are primarily switching currents, and to the analog grounds (pin 28, plus pin 4 on the DSP201) for analog currents, which are primarily from the internal current switches and the output amplifier. Pin 16 on the DSP201 is used internally as a logic level, and injects essentially no current into the ground.Wherever possible, it is strongly recommended that separate analog and digital ground planes be used. With an LSB level of 92µV in 16-bit modes, and one quarter of that in 18-bit modes, the currents switched in a typical DSP system (processor, memory, etc.) can easily corrupt the output accuracy of the D/A’s unless great care is taken to analyze and design for current flows.POWER SUPPLY DECOUPLINGAll of the supplies should be decoupled to the appropriate grounds using tantalum capacitors in parallel with ceramic capacitors, as shown in Figures 2 and 3. For optimum performance of any high resolution D/A, all of the supplies need to be as clean as possible. If separate digital and analog supplies are available in a system, care should be taken to insure that the difference between the analog and the digital supplies is not more than 0.5V for more than a few hundred milliseconds, as may occur at power-on.Separate –5V analog and digital supplies are not needed.These pins are kept separate internally to minimize cou-pling. Drive pin 20 from the –5V analog supply, and make sure that the decoupling shown in Figure 2 or 3 are placed as close as possible to the D/As.CALIBRATION AND ADJUSTMENTOPTIONAL EXTERNAL OFFSET AND MSB TRIMS All of the specifications for the DSP201 and DSP202, plus the typical performance curves, are based on the perfor-mance of these D/As without external trims. In most appli-cations, external trims are not required.If external trims are not used, pins 23, 24, and 25 on the DSP201 should be left open, as should pins 2, 3, 23, 24 and 25 on the DSP202. These pins should not be decoupled with capacitors or tied to any specific potential, or the noise on the D/A outputs may increase.ADJUSTING OFFSETWhere required by specific applications, offsets can be trimmed using the circuits in Figure 2 (DSP201) or Figure 3(DSP202.) As with all standard D/As, offset on the DSP201and DSP202 means the difference of the output from the ideal negative full scale value. The DSP201 and DSP202 usea current switching D/A architecture, and the current from this is internally amplified to produce a ±3V output range.Negative full scale output thus results from having all of the internal current switches turned off. Offset on the DSP201and DSP202 should not be confused with the delta from 0V with an input code of 0000...0000 (0000 hex for 16-bit Modes, 00000 hex for 18-bit Modes). This is often described as bipolar zero error, and includes the effects of both offset and gain error.To trim the offsets, first latch the D/As with 1000...0000(8000 hex or 20000 hex). Then adjust the offset adjustment pots to produce an output of –3.000000V.ADJUSTING THE MSB WEIGHTThe MSB adjustment circuitry shown in Figure 2 for the DSP201 and in Figure 4 for the DSP202 basically change the weight of the MSB by adding to or subtracting from the current controlled by the internal MSB switch.Depending on the application, the MSB adjustments can be made in one of three different ways to optimize the system performance using the DSP201 or DSP202. For dynamic performance, the MSB can be adjusted to minimize distor-tion of either a full-scale or low level sine-wave output. For applications stressing differential linearity, the 0000...0000(0000 hex or 00000 hex) to 1000...0000 (FFFF hex or 3FFFF hex) transition can be trimmed to change the output of the D/As precisely 1 LSB (92µV in the 16-bit Mode or 23µV in the 18-bit Mode.)To adjust for minimum distortion of full-scale sinewaves,strobe the inputs to the DSP201 or DSP202 with codes representing ideal full scale sine waves, then trim the MSB adjustment circuit to minimize distortion, as measured by either a distortion analyzer or by digitizing the output with an appropriate A/D and running FFT analyses.In many audio applications, it is more appropriate to adjust for minimum distortion with low level sinewave outputs.This minimizes zero-crossover error, which can be a con-cern in high-end audio systems. To do this, strobe the inputs to the DSP201 or DSP202 with codes representing ideal low-level sine waves (–60dB from full scale works well),and then trim the MSB adjustment circuit to minimize distortion, again using a distortion analyzer or FFT analyses to check the results of the trims.The MSB adjustment circuits can also be used to trim the D/A outputs directly for the transition from 0000...0000 (0000hex or 00000 hex) to 1111...1111 (FFFF hex or 3FFFF hex),eliminating differential linearity error at the major carry.Ideally, this transition of the digital input code should cause the D/A outputs to change 92µV in the 16-bit Mode or 23µV in the 18-bit Mode. A simple way to make this adjustment is to continually load alternately the codes 1111...1111 (FFFF hex or 3FFFF hex) and 0000...0000 (0000 hex or 00000 hex)into the DSP201 or DSP202. An amplifier with sufficient gain can then drive an oscilloscope input, and the transition output step can be adjusted.GAIN ERRORGain error on the DSP201 or DSP202 cannot be directly adjusted. If required in a specific application, gain can be trimmed out at the system level by adjusting the gain used in an output amplifier stage, such as would be used in any active output filter. In this case, the bipolar zero error should be adjusted first as discussed above. Then, the gain on the output amplifier should be adjusted to minimize the devia-tion from ideal for –Full Scale (1000...000; 8000 hex or 20000 hex) and +Full Scale (0111...1111; 7FFF hex or 1FFFF hex.)An alternative for calibrating on a bench is to tie SIN (DSP201pin 13) or SINA and SINB (DSP202 pins 13 and 14) HIGH,and provide a Bit Clock and periodic Convert Commands.This loads 1111...1111 (FFFF HEX or 3FFFF HEX ), driving the output to 1LSB below 0V. Then periodically bring RESET (pin 8) LOW for at least two Convert Commands, which is the equivalent of loading all 0s, so the output is 0V. Now the output can be adjusted for an ideal transition step.ADJUSTING BIPOLAR ZERO ERRORIf it is important in a specific application to adjust bipolar zero error, the user should first adjust the MSB trim circuits,and then use the offset adjust circuits to adjust the outputs to 0V with input codes of all 0s (0000...0000; 0000 hex or 00000 hex.) In this case, it is not possible to also trim offset at –Full Scale, as described above.FIGURE 2. DSP201 Power Supply Connections and Optional Adjust Circuits.FIGURE 3. DSP202 Power Supply Connections and Optional Offset Voltage Adjustment.FIGURE 4. DSP202 Optional MSB Adjust Circuit.APPLICATIONSUSING PARALLEL PORTSWITH THE DSP201 OR DSP202Figure 5 shows a circuit for converting parallel outputs into the serial data stream required by the DSP201, and meets the requirements for timing signals. Doubling this circuit allows the DSP202 to be driven from a 32-bit parallel port. In most applications, this circuit can be easily incorporated into gate arrays or other programmed logic circuits already used in the system, since the extra gate count is not high. DEGLITCHINGParticularly in high resolution D/A converters, changing input codes may cause glitching on the output that exces-sively corrupts the dynamic purity of an output signal. The DSP201 and DSP202 are designed to minimize output glitching, and all of the performance specifications and typical performance curves are based on tests with no extra deglitching circuitry. In particular, the guaranteed Signal-to-(Noise + Distortion) performance would be impossible to attain with any significant PLETE ANALOG INPUT/OUTPUT SYSTEM The DSP201 or DSP202 can be paired with the Burr-Brown DSP101 or DSP102 analog-to-digital converter to provide both analog input and analog output for a complete digital signal processing system. The DSP101 and DSP102 are respectively single and dual channel 200kHz sampling A/Ds with easy to use interfacing logic that complement the DSP201 and DSP202. Figure 6 shows a single channel analog input and output system based on a DSP201 and a DSP101, and the minimal connections required to interface to a DSP IC. A pair of channels can be implemented using a single DSP202 and a single DSP102, either with two separate DSP ICs, with a single DSP IC with dual serial input and output channels, or a single DSP IC capable of 32-bit words in the Cascade Mode.For maximum flexibility in system design, the DSP201 or DSP202 D/As can be updated at a different rate than the conversion rate used on the DSP101 or DSP102 A/Ds, and either or both of these rates can be asynchronous to the clocks used with the DSP IC.FIGURE 5. Driving the DSP201 from a 16-Bit Parallel Port.。

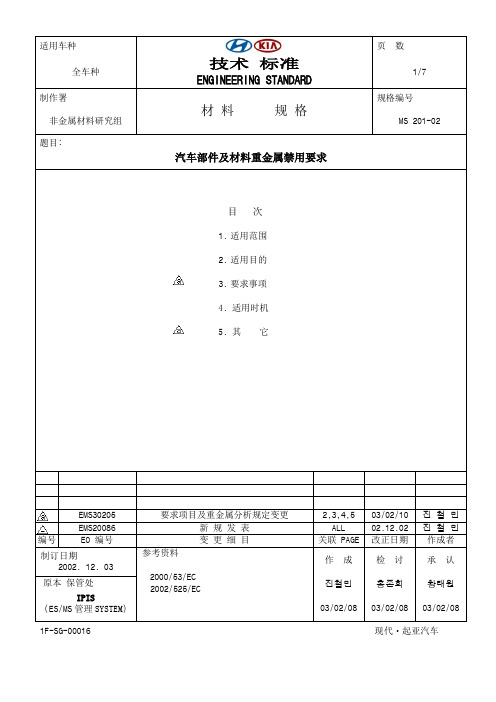

MS201-02(中文)

适用车种技术标准ENGINEERING STANDARD 页数全车种1/7制作署材料规格规格编号非金属材料研究组MS 201-02题目:汽车部件及材料重金属禁用要求目次1.适用范围2.适用目的3.要求事项4. 适用时机5.其它EMS30205 要求项目及重金属分析规定变更2,3,4,5 03/02/10 진철민EMS20086 新规发表ALL 02.12.02 진철민编号EO 编号变更细目关联 PAGE 改正日期作成者制订日期2002. 12. 03参考资料2000/53/EC2002/525/EC作成진철민03/02/08检讨홍존희03/02/08承认황태원03/02/08原本保管处IPIS(ES/MS管理SYSTEM)1F-SG-00016 现代ㆍ起亚汽车1.适用范围本规定对EU报废车再循环规定中限定的汽车M1(9人以下乘用车,小面包车,RV等),N1(车辆总重量3.5吨以下的卡车)及이들车种After Service用部件的材质及不能混合的特定重金属的物质名, 分析方法,管理方法适用.(对只在工程中使用不会在最终产品中残留的切削油,洗洁剂,MaskingTape等及在最终制品中不会残留的材料不适用.)2. 适用目的1) 本规定目的在于防止车辆运营及报废阶段的部件及材料所包含重金属造成的污染并针对国际环境法规积极应对.2) 本规定目的在于依据2000年 10月 21日起发布的EU 报废车再循环规定(Directive 2000/53/ECof the European Parliament and of the Council)中所涉及的车辆制造时重金属禁止条件(等同于法规Article 4 的 2项及 Annex Ⅱ)并实现HMC 及 KMC 车辆的环境性提高.3) 本规定在EU报废车再循环规定(Directive 2000/53/EC of the European Parliament and of theCouncil)中重金属使用规定被改正时也应做出相应改正.3. 要求事项3.1 在汽车使用的部件及材料中不能使用铅(lead, Pb), 汞(mercury, Hg), 铬(Cadmium, Cd), 6价铬(hexavalent chromium, Cr6+) 4种重金属.3.2 例外的EU报废车再循环法规(2000/53/EC)的ANNEX Ⅱ (2002/525/EC)中被确定事项,重金属可以局部使用. (参照附录Ⅱ)3.3 不纯物许用值:对各个材料中不是故意掺入重金属而是重金属作为不纯物被混入的情况,被检出重金属在以下许用范围以内的允许使用. 但,对该类并非有意加入的重金属应在公式文件(得到代表理事, 研究所长的签署的文件)中提出.区分最大不纯物容许量 (ppm)截止2004.12.31. 2005.1.1.以后铅900 100汞900 100铬90 706价铬900 1003.4 报告方法:相关部件构成中不包含铅, 铬, 6价铬, 汞的各个材料应在文件(参考分析成绩书中包含的附录)中标出(例外情况下得到重金属使用许可的材料及部件在同一文件中提出, 这时部件或材料中没有禁止使用重金属的例外部件应明确标出).4. 适用时机本规定自登陆日起适用,EU规定中정한시점보다必须6个月以前量产适用.5.其它对本规定的全部内容如有疑问请向现代·起亚研究开发本部高分子材料研究组询问.< 附录Ⅰ > 分析关联规定/分析成绩书要件1. 重金属分析关联规定材质分类分析规定大分类中分类小分类Pb Cd Hg Cr6+金属铁铁钢Steel, Iron ASTM E 350 ASTM E 350 - -合金ASTM E 352 ASTM E 352 - -Zn-Al 镀金钢板ASTM E 1277 ASTM E 1277 - - 铸铁铸铁ASTM E 351 ASTM E 351 - -锰铁, 低锰铁ASTM E 361 ASTM E 361 - - 非铁铜及合金ISO 4749 ISO 5960 JIS H 1066 -铝及合金ISO 4192 ASTM E 34 - -镍及合金ISO 11437-1ISO 11437-2ISO 6351 - - 鋅及合金ASTM E 536 ASTM E 536 - -镁及合金ASTM E 35 ASTM E 35 - -非金属塑料ASTM D 6018 BS EN 1122- -皮肤ASTM D 6018 ASTM D 6018 - -橡胶ISO 6101-2 ISO 6101-2 - -油漆ISO 6503 ASTM D 3335 ISO 7252-玻璃ASTM C 169-92 ASTM C 169-92 - -纸ISO 10775ISO 10775 --燃料ISO 3830 ISO 3830 - -润滑油ASTM D 5185 ASTM D 5185 ASTM D 5185 -铬酸盐(Chromate)表面处理- - - ISO 3613✓对在以上材质分类中未包含的材料应与专门分析机构协议,借用类似材料的分析方法实施分析.✓汞(Hg)与6价铬分析方法处于未开发状态,在原材料制造时应向我公司报告未含有以上重金属.✓对分析方法不能决定的情况向本社非金属材料研究部署分析担当者询问.✓原材料供给企业单独使用既定分析方法的情况应在接收分析成绩书时详细的附注说明分析方法.2. 接收分析成绩书时必须包含的事项✓分析日✓分析机构及分析者✓正确的试料名称:材料名, 原料生产商, 材料Grade名(在必要的情况下应包含 Color名)等必需尽可能正确的表示. 以便无论谁看到试料的名称都能正确的理解, 不会发生与其它材料产生误解的情况.✓按原料别分析, 所使用分析方法的规定编号;✓检出限界值✓分析结果及单位✓分析机构的签印3. 分析成绩书的有效要件✓分析成绩书只认证原本.(但,对分析机构发行的副本、抄本均进行认证.对一本分析成绩书对应多个部件的情况,应对原件进行认证并对副本进行认证)✓可在原材料企业对正式发行的分析成绩书进行认证. ( 但, 必须具备代表理事盖章,研究所长盖章等正式文件要件.)✓对外协企业自身具有分析能力的情况,须与我公司的品质部门或研究所负责人协议后才能进行认证.< 附录Ⅱ > 根据法规内容1. 法规内容1.1 2000/53/EC Article 4中第2项内容2. (a) 对EU会员国2003年 7月 1日以后出售车辆的材料与部件必须保证铅, 汞, 铬或 6价铬等重金属含有量在Annex Ⅱ规定条件中罗列的分量以下.(b) 依照Article 11规定的顺序对Commission技术性的,科学性的进步并依据以下事项修正Annex Ⅱ的内容.(ⅰ) 依据必要的特征物质及部件耐subparagraph(a)所涉及物质的유예限定值设定最大浓度.(ⅱ) 特定材料及部件不可避免得使用相关物质的情况,对(a)项的规定可以例外.(ⅲ) 万一出现该物质没有被使用的情况, 从Annex Ⅱ的材料及部件目录上删除.(ⅳ) 上记(ⅰ)和 (ⅱ)的情况, 可以事前处理的应铭记下来. 使用labeling,或其它适当的方法便于识别.(c) Commission 2001年 10月 21日以前 Annex Ⅱ的内容必须修正 1次. 어떠한경우에도2003년 1月 1日以前 Annex上被罗列的例外事项不能被删除.1.2 Annex Ⅱ内容 (2002/525/EC) - Article 4(2) (a)中例外物质及部件.-材料及部件范围及延缓期间必要Labeling 合金中铅含量1.用于机械加工的steel及(电镀钢材)galvanised steel : 0.35wt% 以下2. a) 用于机械加工的Al : 2wt% 以下2005.7.1.1b) 用于机械加工的Al : 1wt% 以下2008.7.1.23. 铜合金 : 4wt% 以下4. Lead-bronze bearing shells andbushes铅及含铅部件5. Batteries Labeling6. Vibration dampers Labeling7. Wheel balance weights 2003.7.1.以前行驶车辆及 A/S用部件:2005.7.1.3Labeling8. 流体用及powertrain用elastomer上2005.7.1.41截止2005.1.1.对EU Commission例外条件的删除日期需要讨论或审议.2与上记第1项同一内容(有效期间:2008.7.1.).3截止2005.1.1.对EU Commission例外条件的删除日期需要讨论或审议.4与上记第1项同一内容(有效期间:2008.7.1.).强化材料及安全材料9. 电着涂料的稳定剂2005.7.1.10. 电机马达用 Carbon brushes 2003.7.1.以前行驶车辆及A/S用部件:2005.1.1.11. 电子回路及其它电器部件用Solder Labeling512. 刹车线(break lining)中所包含铜:0.5wt% 2003.7.1.以前行驶车辆及 A/S用部件:2004.7.1.Labeling13. Valve seats 2003.7.1.以前开发的 Engine types : 2006.7.1.14. 玻璃灯泡与陶瓷器matrix混合物中包含납을的电气部件.(灯泡玻璃及点火塞釉药除外) Labeling6 (引擎压电部件以外的部件用)15. 灯泡玻璃及点火塞釉药2005.1.116. 燃烧引发剂2007.7.1.6价铬17. 为防止腐蚀进行表面处理2007.7.1.18. 移动住宅车辆(motorcaravans)的absorption refrigeratorsLabeling 水银19. 水银灯及I/P 显示器Labeling 镉20. 厚薄膜粘接剂2006.7.1.21. 电力车用 battery 2005.12.31.2005.12.31.以后,之前上市的车辆的替代用品可使用 Ni-C dbatteryLabeling<Notes>- 对不是有意图添加重金属的情况7, 均一物质(homogeneous)的铅, 水银, 6价铬的许用量为:0.1wt%(1000ppm), 均一物质的铬许用量为:0.01wt%(100ppm)- 对不是有意图添加重金属铝(Al)的情况8, 铝(Al)的许用量为:0.4wt%- 对不是有意图添加重金属的情况9, 截止2007.7.1.在刹车线用摩擦剂中加入许用量:0.4wt%.- 例外期间期满以前投放市场车辆的部件被Re-use的情况可以无限期使用.- 截止2007.7.1, 在article 4(2)(a)得到免除车辆的部件进行更换修理后10,新更换的部件同样适用免除条件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VOLTAGE RANGE 50 to 200 Volts CURRENT 2.0 Ampere

MAXIMUM RATINGS (@ T A =25 O C unless otherwise noted)

ELECTRICAL CHARACTERISTICS (@T A =25 O C unless otherwise noted)

RATINGS

Maximum Recurrent Peak Reverse Voltage Maximum RMS Voltage Maximum DC Blocking Voltage

Maximum Average Forward Rectified Current at T A = 55O C

Peak Forward Surge Current 8.3 ms single half sine-wave superimposed on rated load (JEDEC method)Typical Thermal Resistance (Note 1)Typical Junction Capacitance (Note 2)SYMBOL V RRM V DC I FSM C J T STG

V RMS UNITS Volts Volts Volts Amps 2.0507518Amps

0C/W 0

C/W 0C Storage Temperature Range

R q J A Typical Thermal Resistance (Note 1)20R q J L I O pF

Operating Temperature Range T J UFM201

50150-55 to + 150

C

UFM202

UFM203

100150357010550

100

150

UFM204

UFM201UFM202UFM203UFM204200200

1402006-11

CHARACTERISTICS

Maximum Average Reverse Current at Rated DC Blocking Voltage

V F SYMBOL I R m A Maximum Instantaneous Forward Voltage at 2.0A DC Volts 5350@T A = 25o C @T A = 100o

C

m A UNITS 0.9trr

Maximum Reverse Recovery Time (Note 4)

nSec 20

NOTES : 1. Thermal Resistance :Mounted on PCB.

2. Measured at 1 MHz and applied reverse voltage of 4.0 volts.

3. "Fully ROHS compliant","100% Sn plating (Pb-free)".

4. Test Conditions: I F = 0.5A, I R = -1.0A, I RR = -0.25A.

AMBIENT TEMPERATURE, (O C)I N S T A N T A N E O U S R E V E R S E C U R R E N T , (m A )

RATING AND CHARACTERISTICS CURVES ( UFM201 THRU UFM204 )

FIG.2 TYPICAL FORWARD CURRENT DERATING CURVE

FIG.1 TEST CIRCUIT DIAGRAM AND REVERSE RECOVERY TIME CHARACTERISTIC

PERCENT OF RATED PEAK REVERSE VOLTAGE, (%)

A V E R A G E F O R W A R D C U R R E N T , (A )

0.1

10

1.0

1000

100

FIG.3 TYPICAL REVERSE CHARACTERISTICS

50 W

10 W

SET TIME BASE FOR 50/100 ns/cm

1 megohm. 22pF.

2. Rise Time = 10ns max. Source Impedance = 50 ohms.

NUMBER OF CYCLES AT 60Hz

P E A K F O R W A R D S U R G E C U R R E N T , (A )

INSTANTANEOUS FORWARD VOLTAGE, (V)

10

3020

50100

200

I N S T A N T A N

E O U S

F O R W A R D C U R R E N T , (A )

1.00.30.10.030.01

3.01020RATING AND CHARACTERISTICS CURVES ( UFM201 THRU UFM204 )

FIG.4 TYPICAL INSTANTANEOUS FORWARD CHARACTERISTICS

FIG.5 MAXIMUM NON-REPETITIVE FORWARD SURGE CURRENT

REVERSE VOLTAGE, (V)

J U N C T I O N C A P A C I T A N C E , (p F )

464020106020010021FIG.6 TYPICAL JUNCTION CAPACITANCE

Mounting Pad Layout

Dimensions in inches and (millimeters)。