zedboard系统移植

ZedBoard试用测评+HDMI接口硬件平台

ZedBoard试用测评+HDMI接口硬件平台因为我拿的这套是全新的,先上张板子的全家福。

见下图:除了一个大信封里装的是板子上的各种IC 的厂家的资料的外,还有一张ISE14.1 的安装光盘。

但是建议大家采用ISE14.2 的开发环境,因为这个对zynq 的器件支持会多一些。

想到评测这块ARM SOC 的FPGA 的板子,这块板子和以往FPGA 开发板或者是ARM 的开发板的区别。

其实就是更好的体现ARM 与FPGA 直接的数据交互。

还有本人没做过linux 系统,所以先不做系统的移植方面的。

主要评测一下ARM 与FPGA 之间的数据交互。

先先搭好硬件系统。

首先使用PlanAhead 建立工程,然后采用添加文件的方式创建嵌入式系统的xmp 文件,这里需要注意的是:使用ZYNQ 中的ARM 硬需采用PlanAhead,ISE 只能创建嵌入式软核。

需要采用create sub-design 的方式创建。

以后和过程和使用软化差不多了。

具体的设置步骤可以参见相关的文档,或者导入现成的.xmp 文件在上面的架构中,PS 部分是主要部分,外面的接口部分的存储器采用的SD 卡,SPI Flash 以及512M 的DDR3。

我所使用的控制HDMI 接口芯片的控制时序作为自定义的IP 核通过AXI 总线挂到PS 中。

使用心得:1.搭好上述硬件平台后,以后的使用的操作就和使用Microblaze 的方法差不多了。

在没有跑操作系统的情况下,先把他当做一个硬化吧CPU 吧。

2.主要是使用这块板子做HDMI 接口显示方面的工作。

具体的功能的实现是通过PS 提供提供需要显示的数据,PL 部分完成HDMI 接口芯片时序的。

后面在继续进行C 的代码。

zedboard的大体架构介绍(PS、PL、硬件互联)

zedboard 可以将逻辑资源和软件分别映射到 PS 和 PL 中,这样可以实 现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻 辑。以及二者之间的互联特性。这篇笔记主要记录 zedboard 的大体架构。 1. 处理系统(PS) 应用处理单元(APU) 存储器接口 I/O外设,包括静态存储器和Flash存储器接口,可以通过共 享一个 54 引脚的多路复用 io(MIO) 互联,也可以扩展访问 PL 中的 IO 2. 可编程逻辑(PL)

GPIO, 3 模式的以太网控制器, USB 控制器,可以作为主设备或者 OTG SD/SDIO 控制器,两个,可以作为基本的启动设备,支持 sd 2.0 规 范, SPI 控制器:四线总线,MOSI,MISO,SCLK,SS,支持全双工操 作, CAN 控制器(两个) UART 控制器两个 i2c 控制器(两个)

1. 基于 AXI 高性能数据通路开关的 PS 互联 OCM 互联,提供来自中央互联和 PL 的,用于对 256KB 存储器的访 问, CPU 和 ACP 的接口, 中央互联, 中央互联是 64 位的,将 IOP 和。将以太网、usb、和 sd/sdio 控制器内的本地 DMA 单元连接到中央互联,将 PS 内的主设备连接到 IOP。 2. PS-PL 接口,包含所有 PL 设计者的可用信号,可以基于 PL 的功 能和 PS 集结在 一起。 功能接口,包含 AXI 互联,用于大多数的 IO 外设、中断,DMA 控 制流、时钟和调试接口的扩展 MIO 接口,

可编程逻辑 PL 特性 可配置逻辑块(CLB) 36KB 的 Bram,双端口,最多 72 位宽度,可编程 fifo 逻辑, 数字信号处理-DSP48E1 芯片 时钟管理 可配置的 io 模数转换特性(XADC) 互联特性

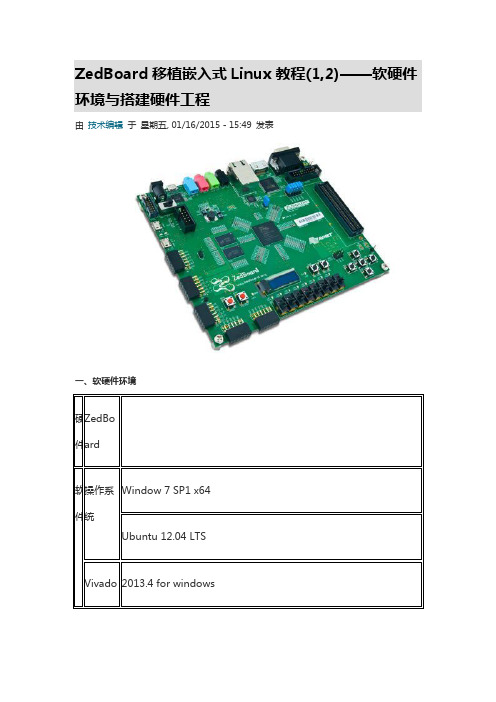

ZedBoard移植嵌入式Linux教程

说明:有地方使用的linux版本是https:///Xilinx/linux-xlnx,Uboot是https:///Xilinx/u-boot-xlnx,没有测试过。

二、搭建硬件工程创建一个最简单的Zynq项目,如下:选择Next点击Next,我们不需要添加Verilog/VHDL源文件或者约束文件,勾选Do not specify sources at this time点击Next,选择Boards,并选择ZedBoard Zynq Evaluation and Development Kit点击Next点击Finish完成创建向导,出现如下界面先创建一个Block Design,点击如下地方输入名称等待创建完成在Diagram视图中点击Add IP在弹出的窗口中输入Zynq进行搜索,在结果中选择第一个点击Run Block Automation,并选择/processing_system7_0完成自动连线完成之后双击ZYNQ进行自定义配置出现取消不需要的部分首先点击Clock Configuration,展开PL Fabric Clocks,取消FCLK_CLK0该时钟是PS提供给PL的时钟,在结构图中的如下部分取消之后Diagram中的FCLK_CLK0会消失另外,我们要取消掉如下引脚对于TTC,我们点击如下部分,取消掉TTC再点击取消掉AXI GP0 interface最后取消掉QSPI点击OK完成回到Block Design的sources视图在System上右键选择Create HDL Wrapper完成后点击左边Flow Navigator中的Generate BitStream等待Vivado完成综合、实现、生成bitstream之后,出现如下点击Cancel取消。

点击File->Export->Export Hardware for SDK勾选Launch SDK并点击OK。

《一步一步学ZedBoard

(这是本系列的第一篇,每个步骤均给出截图)硬件平台:Diligent ZedBoard开发环境:Windows XP 32 bit软件:PlanAhead 14.1 + XPS 14.1 + SDK 14.1Zed板上的Zynq是一个PS(processing system, 双核A9 + 存储管理+ 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 芯片开发一样。

不同的是PS单元是可配置,因而硬件信息是不固定的。

这也是zynq灵活性的一个表现。

一、配置硬件信息启动PlanAhead,进入新建工程向导选择工程名和路径工程类型,这里选择RTL 工程由于只需要PS部分信息,而这部分在后面由XPS完成,因而不需要添加任何文件一直点下一步,直道出现芯片和板载信息。

直接选择Boards,选择系列是Zynq-7000。

14.1目前只支持XC7Z020器件。

完成新建工程向导PlanAhead进入工作视图,在Project Manger中选择建立的工程,右键,Add Sources选择Add or Create Embeded Sources单击Create Subdesign输入需要建立嵌入系统名称,这里填duocore确定后,提示所建立的工程是一个Zynq工程,提示是否添加PS到系统。

点确认。

XPS会被启动,可以看到Zynq的配置界面。

Diligent公司做好了一套配置方案,从其网站上能下载到配置文件:import这个配置文件,点“+”找到文件位置后,点OK可以看到配置后的结果,同时MHS和UCF文件也被修改。

其中有颜色标记为使用,没有颜色标记表示没有使用。

可以对其修改,这是对应ZedBoard的硬件接口,保持默认就可。

至此,硬件配置结束。

关闭XPS,切换到PlanAHead。

可以看到duocore.xmp已经加入到工程中。

在硬件配置文件duocore.xmp上右键,选择Create Top HDL,生成顶层HDL文件可以看到生成的duocor_stub.v文件最后一步,将硬件信息导入到SDK。

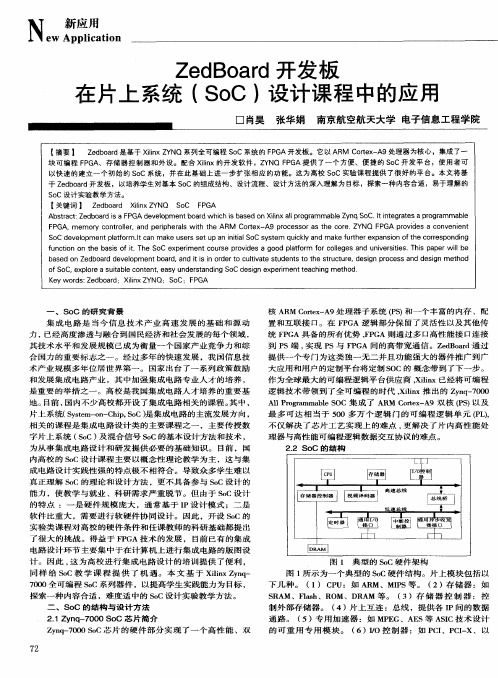

ZedBoard开发板在片上系统(SoC)设计课程中的应用

o f S oC, ex pl or e a s ui t a b l e c on t en t , e a s y u n der s t an di n g SoC de s i g n e x pe r i me n t t e a ch i n g me t h od . Ke y wor d s : 7e db oa r d:Xi l i n x ZYNQ ; S oC ;FPGA

块可 编程 F P G A、存储器控 制器 和外设。 配合 Xi l i n x的开发软 件 ,Z Y NQ F P G A提供 了一 个方便 、便捷 的 S o C开发 平台 ,使用 者可 以快速 的建立一 个初始 的 S o C系统 ,并在此基 础上进 一步扩张相 应 的功 能。这为高校 S o C实验 课程提供 了很好 的平 台。本 文将基 于Z e d b o a r d开发板 ,以培养 学生对 基本 S o C的组成结构 、设计流程 、设计 方法的深入理解为 目标 ,探索一种内容合适 ,易于理解 的

N 新 e w A p 应 p l i 用 c a t i o n

Z e d B o a r d开 发 板 在 片上 系统 ( S o C) 设计 课程 中的应 用

口 肖昊 张华娟 南京航空航天大 Z e d b o a r d是基于 X i l i n x Z Y N Q 系列 全可编程 S o C系统 的 F P G A开发板。它 以 A R M C o t r e x — A 9处理器 为核 心 ,集成 了一

一

、

S o C的研 究背景

集 成 电 路 是 当 今 信 息 技 术 产 业 高 速 发 展 的 基 础 和 源 动

核 A R M C o r t e x — A 9处 理 器 子 系 统 ( P S ) 和一 个 丰 富 的 内存 、配 置 和互联 接 口。在 F P G A 逻辑 部分保 留了灵 活性 以及其 他传 统 F P G A 具 备 的所 有 优 势 , F P G A 则 通 过 多 口高 性 能 接 口连 接 到 P S端 , 实现 P S与 F P G A 间的高带 宽通信 。Z e d B o a r d 通 过 提 供 一 个 专 门 为 这 类 独 一 无 二 并 且 功 能 强 大 的 器 件 推 广 到 广 大应 用和用 户的定制平 台将定 制 S O C的 概 念 带 到 了下 一 步 。 作 为全球 最大 的可编程逻 辑平 台供应商 , Xi l i n x已 经 将 可 编 程 逻 辑 技 术 带 领 到 了全 可 编 程 的 时 代 , X i l i n x推 出 的 Z y n q 一 7 0 0 0 A l l P r o g r a mma b l e S O C集 成 了 A R M C o r t e x — A 9双核 ( P S ) 以 及 最 多 可 达相 当于 5 0 0多 万个 逻 辑 门 的可 编 程逻 辑 单元 ( P L ) , 不 仅解 决 了芯 片工艺 实 现上 的难 点 , 更 解 决 了 片 内 高 性 能 处 理 器与高 性能可 编程逻辑 数据 交互协议 的难点 。

基于XVC协议的Zedboard平台远程更新与调试

基于X V C协议的Z e d b o a r d平台远程更新与调试朱琛1,沈小波1,周志刚2(1.中国电子科技集团公司第五十八研究所,无锡214000;2.中国船舶重工集团公司第702研究所)摘要:船舶雷达数据处理设备是许多科研院所面对庞大的雷达数据而研发的处理设备㊂此类处理设备属于船用设备,且设备中处理板卡众多㊂为了在不打开设备的情况下,脱离专用的U S B J T A G下载电缆对处理板中的F P G A进行远端升级,本文提出一种虚拟线缆协议,通过以太网,利用Z e d b o a r d平台的P S端控制P L端生成的J T A G接口对其进行远程更新与调试的方法㊂该方案成本较低,易于拓展,同时也提高了更新可靠性㊂关键词:X V C协议;Z e d b o a r d;J T A G接口;T C P/I P;远程更新与调试中图分类号:T N919文献标识码:AR e m o t e U p d a t i n g a n d D e b u g g i n g o f Z e d b o a r d P l a t f o r m B a s e d o n X V C P r o t o c o lZ h u C h e n1,S h e n X i a o b o1,Z h o u Z h i g a n g2(1.T h e58R e s e a r c h I n s t i t u t e o f C h i n a E l e c t r o n i c s T e c h n o l o g y G r o u p C o r p o r a t i o n,W u x i214000,C h i n a;2.T h e702R e s e a r c h I n s t i t u t e o f C h i n a S h i p b u i l d i n g I n d u s t r y C o r p o r a t i o n)A b s t r a c t:T h e s h i p r a d a r d a t a p r o c e s s i n g e q u i p m e n t i s d e v e l o p e d b y m a n y s c i e n t i f i c r e s e a r c h i n s t i t u t e s i n t h e f a c e o f h u g e r a d a r d a t a.T h i s k i n d o f p r o c e s s i n g e q u i p m e n t b e l o n g s t o m a r i n e e q u i o m e n t,a n d t h e r e a r e m a n y p r o c e s s i n g b o a r d s i n t h e e q u i p m e n t.T h i s s t u d y a i m s t o d e s i g n a n d i m p l e m e n t r e m o t e u p d a t i n g a n d d e b u g g i n g m u l t i-f i e l d p r o g r a mm a b l e g a t e a r r a y f o r t h e d e t e c t o r w i t h o u t o p e n i n g t h e e q u i p-m e n t,s e p a r a t e f r o m t h e s p e c i l a U S B-J T A G d o w n l o a d c a b l e.I n t h e p a p e r,a n e t w o r k b a s e d Z e d b o a r d̓s p r o c e s s i n g s y s t e m i s u s e d t o a c c e p t c o n f i g u r a t i o n f i l e s v i a n e t w o r k a n d g e n e r a t e J T A G b y Z e d b o a r d̓s p r o g r a mm a b l e l o g i c s e q u e n c e t o F P G A b y m e a n s o f X i l i n x v i s u a l c a b l e p r o t o c o l.T h e r e m o t e u p d a t i n g a n d d e b u g g i n g o f m u l t i-F P G A a r e r e a l i z e d.T h i s m e t h o d i m p r o v e s t h e r e l i a b i l i t y o f r e m o t e u p d a t i n g a n d d e b u g g i n g o f F P G A s a n d i s e a s y t o e x t e n d w i t h l o w c o s t.K e y w o r d s:X V C p r o t o c o l;Z e d b o a r d;J T A G i n t e r f a c e;T C P/I P;r e m o t e u p d a t i n g a n d d e b u g g i n g0引言早期的船舶雷达设备和其他电子设备一样经历过电子管和晶体管的元件阶段㊂随着大规模集成电路的出现,现在的船舶导航雷达处理单元,大多采用高性能的F P G A 进行数据采集及加速㊂当大量模块单元需要升级时,需要拆卸机箱,耗时耗力[1]㊂考虑到对设备进行程序更新及版本升级,拆卸设备工作量较大且更新时易出错,本文设计了一种基于X V C (X i l i n x V i r t u a l C a b l e)的协议,通过以太网,配合A R M+ F P G A混合架构的Z Y N Q7000系列板卡,利用G P I O口模拟J T A G接口进行远程更新调试的方案㊂该方案操作简单,无需额外开发T C P/I P软件,基于网络的通信能够保证足够远距离的灵活可靠的数据传输,还能对F P G A进行远程H a r d w a r e M a n a g e r调试㊂同时,通过简单的J T A G链路连接可以完成远端多片F P G A在线升级及调试㊂1系统架构本设计采用Z e d b o a r d平台嵌入式开发板,其基于X i l-i n x Z Y N Q7000系列芯片㊂Z Y N Q7000采用A R M+ F P G A架构,具有高度集成性,整个系统具有丰富的处理器和扩展资源,用户可以根据需求将不同的模块连接起来,实现自定义逻辑功能[2],因而非常利于多片F P G A远程更新与调试㊂Z e d b o a r d开发板实物图如图1所示㊂通过A R M处理器中网络口控制A X I(A d v a n c e d e X-t e n s i b l e I n t e r f a c e)总线,将更新程序发送到F P G A端,F P-G A端例化一个J T A G接口对光纤接口板进行更新与调试[3]㊂设计实现远程更新船舶雷达设备中光纤接口板(核心芯片为x c7k325t),整体架构图如图2所示㊂2基于Z e d b o a r d平台的P L端开发在Z e d b o a r d平台上进行P L(P r o g r a mm a b l e L o g i c)端开发,核心是通过G P I O口实现J T A G模块功能㊂J T A G图1 Z e d b o a r d开发板实物图图2 设计整体架构图模块功能主要是通过器件内部的T A P (T e s t A c c e s s P o r t,图3 F P G A 端设计架构测试访问端口)对芯片内部的寄存器进行访问㊂T A P 控制器包含一个具有16个状态的自动状态机,对数据寄存器D R (D a t a R e g i s t e r )和指令寄存器I R (I n s t r u c t i o n R e g-s i t e r)进行相关操作㊂本设计中需要4个I P 核:p r o c e s s i n g _s ys t e m 7_0㊁a x i _i n t e r c o n n e c t _0㊁p r o c _s y s _r e s e t _0和a x i _j t a g _0㊂p r o c e s s -i n g _s y s t e m 7_0为Z Y N Q 7000的系统I P 核㊂a x i _i n t e r -c o n n e c t _0为A X I 总线中转I P 核㊂p r o c _s ys _r e s e t _0为系统连接其他A X I 的复位I P 核㊂a x i _j t a g_0为G P I O 配置J T A G 时序I P 核㊂F P G A 端的设计架构图如图3所示㊂P S (P r o c e s s i n g S y s t e m )端通过A X I 总线对a x i _j t a g_0进行数据传输,主要是内核中寄存器的读写,本文中a x i_j t a g _0内核设计了5个寄存器,即[31ʒ0]s l v _r e g0㊁[31ʒ0]s l v _r e g 1㊁[31ʒ0]s l v _r e g 2㊁[31ʒ0]s l v _r e g3㊁[31ʒ0]s l v _r e g 4,分别对应数据传输长度L E N G T H ㊁J T A G 总线的TM S 信号数据㊁J T A G 总线的T D I 信号据㊁J T A G 总线的T D O 信号数据及P S 端传输有效E N A B L E信号㊂通过开发软件设置a x i _j t a g _0的IP 核寄存器起始地址为0x 43C 0_0000,长度为64K B ㊂最后R T L 分析综合㊁实现并生成二进制文件,给P S 端提供软件设计的硬件平台㊂3 基于Z e d b o a r d 的嵌入式L i n u x 平台开发本设计基于Z e d b o a r d 开发板,在P S 端移植嵌入式L i n u x 系统,并需要在开发应用程序中实现X V C 虚拟网络功能㊂3.1 引导程序的移植嵌入式操作系统都会采用引导程序来引导内核,本设计使用u b o o t 作为启动引导[5]㊂由于使用Z Y N Q 系列芯片,在引导操作系统与之前单纯的只含有A R M 架构的芯片有所不同,需要在u b o o t 之前增加F S B L .e l f 及s ys -t e m.b i t 文件,其L i n u x 系统启动过程如图4所示㊂并对u b o o t 进行相应配置,主要包含内核镜像㊁设备树㊁文件系统㊁网络地址㊁加载方式等信息,配置启动方式为Q S P I 启动,Q S P I 的存储文件及地址分配如图5所示㊂图4 Z Y N Q 7000系统启动过程图5 Q S P I 内部存储文件及地址分配3.2 移植L i n u x 内核及生成设备树及文件系统L i n u x 内核是嵌入式系统的关键部分[4]㊂由于嵌入式系统比较精简,通常需要对L i n u x 内核进行裁剪㊂官网下载L i n u x 内核进行相应的配置,编译生成z I m a ge 文件㊂Z Y N Q 7系列芯片的A R M 内核是通过设备树形式的数据结构来配置系统启动的设备参数[5]㊂本设计需要在官方提供的设备树d e v i c e t r e e .d t b 中增加J T A G 接口I P 核的信息,代码如下:&a m b ar a n g e s ; a x i _j t a g _0:a x i j t a g@43C 00000{ c o m p a t i a b l e ="ge n e r i c u i o "; r e g =<0x 43C 000000x 10000>; };};文件系统为嵌入式系统及设备提供文件输入输出等文件管理功能,本设计不展开叙述,编译生成文件系统r a m d i s k 8M.i m a g e .gz 压缩包[6]㊂在启动过程中,u b o o t 会将此文件加载到内存中,并将内存地址传递给内核,待内核启动时,即可同时运行文件系统[7]㊂3.3 X V C 应用程序设计X V C 协议是一种基于T C P /I P 的虚拟线缆协议[8],允许用户通过网络访问X i l i n x F P G A 的J T A G 接口并对其进行高效率的远程更新与调试㊂X V C 协议内容简单,使用方便,其基本内容可总结为如下三条指令[9],如表1所列㊂表1 函数指令功能函数名功 能ge f i n f o ()获取X V C 服务的版本信息㊁t m s 及t d i 字节向量一次能够移位的最大长度s h i f t (n u m b i t s ,t m s v e c t o r ,t d i v e c t o r )以字节向量T M S v e c t o r 和T D I v e c t o r 的形式发送n u m _b i t s 个二进制数给X V C服务器s e t t c k()设置通信协议周期成纳秒,返回值为实际周期值本设计实现的X V C 服务器功能主要通过T C P /I P 协议以及内存映射来进行数据交互㊂首先打开U I O 设备即在系统中生成a x i _j t a g _0的设备,并进行内存映射;然后进行T C P /I P 通信需要的一些初始化的工作,建立通信,通过h a n d l e _d a t a ()函数来交互数据㊂X V C 服务器程序设计如图6所示㊂图6 X V C 服务器程序设计流程图h a n d l e _d a t a ()函数内利用m e m c m p ()及m e m c p y()实现命令识别及应用层与设备的数据交互㊂h a n d l e _d a t a()函数内部设计如图7所示㊂图7 h a n d l e _d a t a()函数流程图X V C 协议具体实现内容如下:由于V i v a d o 软件每次发送s h i f t 指令的最大长度为2048字节,故设置接收缓存区b u f f e r 大小为2048,而发送缓存区r e s u l t 大小为1024㊂网络设置包括创建s o c k e t ()进行网络通信,并设置其通信协议为T C P ,非阻塞模式,端口号为2542,并为其分配I P 地址和MA C 地址㊂打开s o c k e t ()并监听网络连接请求㊂从s o c k e t()接收6个字节数据到缓存区,如果与字符串s h i f t 相同,则继续读取4字节的内容作为n u m _b i t s,并转换为n r _b yt e s ㊂接着按该字节数分别读取T M S v e c t o r 和T D I v e c t o r 到接收缓存区b u f f e r ,之后通过m e m c p y()将数据映射到a x i _j t a g _0设备的寄存器中,a x i _j t a g_0模块将读到的寄存器数据赋值给TM S 和T D I 引脚,同时产生周期性的T C K 信号㊂a x i _j t a g _0模块检测到TD O 引脚上的信号写入寄存器s l v _r e g 3,应用层通过m e m c p y ()读到寄存器,发送给P C ㊂P C 验证收到的T D O 数据无误,继续通过s h i f t 指令发送下一个数据包㊂由此便实现了一个完整的J T A G 数据链路,从而实现远程P C 由网络将配置数据通过模拟的J T A G 接口配置给F P G A 的过程㊂4 测试验证及总结利用V i v a d o 软件中的H a r d w a r e M a n a ge r 进行远程更新,首先通过S D K 软件将系统启动所需要的文件烧写进Z e d b o a r d 平台,启动L i n u x 系统㊂在Z e d b o a r d 运行X V C 服务程序,等待P C 通过网络配置F P G A ㊂在V i v a d o 的T C L c o n s o l e 输入以下命令:>>c o n n e c t _h w _s e r v e r>>o p e n _h w _t a r ge t -x v c _u r l 192.168.1.10:2542从图8中可以看出,已经成功连接到光纤接口板,网络I P 地址为192.168.1.10,端口号为2542㊂图8 实验结果该设计具有可扩展性,可以拓展为多F P G A 远程更新与调试,只需要在逻辑设计时加入多个J T A G 模块,并在X V C 应用层程序中更改相应的设备,即可实现多个F P G A 远程更新与调试㊂随着船用雷达的不断更新换代以及多功能化的实现,设备的更新在所难免,本设计给后续升级提供了可靠便捷的保障,已在某型号舰载设备上使用,对今后工业化设备在线升级算法㊁远程更新程序,具有重要引导意义㊂参考文献[1]陶吉怀.基于S O P C 的船用雷达处理单元研究与设计[D ].成都:电子科技大学,2013.[2]文华武.基于以太网的F P G A 远程程序升级系统的设计与研究[D ].重庆:重庆大学,2012.[3]王利军,张超.基于C P U 实现F P G A 远程更新[J ].信息通信,2013,20(6):4445.[4]薛乾,曾云,张杰.基于X V C 网络协议的多F P G A 远程更新与调试[J ].核技术,2015,38(12).[5]3G P P T S 36.322.R a d i o L i n k C o n t r o l (R T C )pr o t o c o l [S ],2015.[6]余婷婷.嵌入式文件系统的研究与设计[D ].武汉:武汉理工大学,2007.[7]华抒军.基于Z e d b o r a d 的软件无线电软件平台的设计与实现[J ].软件,2015,36(10):5760.[8]X i l i n x .X i l i n x v i r t u a l c a b l e o v e r v i e w ,2015.[9]X i l i n x .X i l i n x v i r t u a l c a b l e r u n n i n g o n Z y n q 7000u s i n g th e pe t a l L i n u x t o o l s ,2015.朱琛(工程师),主要研究方向为F P G A 逻辑设计及嵌入式硬件设计;沈小波(工程师),主要研究方向为雷达信号处理系统;周志刚(工程师),主要研究方向为嵌入式L i n u x 系统及应用㊂(责任编辑:薛士然 收稿日期:2020-06-18)。

zedboard启动流程新

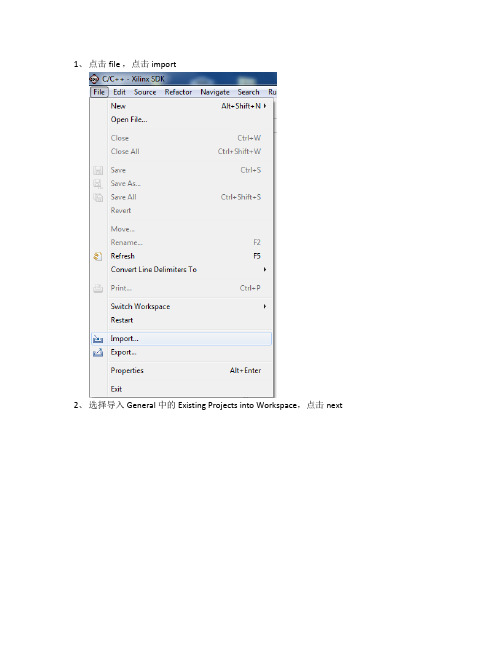

1、点击file ,点击import2、选择导入General 中的Existing Projects into Workspace,点击next3、点击Browse4、选中解压出的NJ-cpu1-src,点击OK5、弹出界面如下图,点击Finish6、在Project Explorer可看到如下界面:7:点击展开app_cpu1,继续点击展开src,双击app_cpu1.c8、此时界面如下:9、点击Xilinx Tools ,点击Creat Zynq Boot Image10、点击browse,选择BIF文件保存位置,取名为zrobot.bif11、一次添加amp_fsbl.elf、system.bit、u-boot.elf、app_cpu1.elf。

前3个文件直接使用提供的,第4个替换成自己编译的文件。

点击add后弹窗如下:12、点击Browse,选中NJ-cpu1-targets中的amp_fsbl.elf,点击Open13、点击OK14、继续点击add,点击Browse,选中NJ-cpu1-targets中的system.bit,点击Open15、点击OK16、继续点击add,点击Browse,选中NJ-cpu1-targets中的u-boot.elf,点击Open17、点击OK18、继续点击add,点击Browse,选中NJ-cpu1-targets中的app_cpu1.elf,点击Open19、点击OK20、create image界面最终如下,可以看到添加的四个文件。

必须按照此顺序修改输出文件名,讲output.bin修改成BOOT.bin21、点击Create Image,Console窗口输出结果如下:下图是SD卡中必要的文件,其中init2.sh是由init.sh文件重命名的。

如果你需要由SD自启动需将此文件修改成init.sh文件名,如果你需要Linux单步调试,则需要将其修改成init2.sh,或者其他名称。

ZedBoard移植嵌入式Linux教程

ZedBoard移植嵌入式Linux教程

1.准备硬件

首先,我们需要准备好ZedBoard开发板以及适配器和连接线,确保电源正常连接。

另外,我们需要一台配有SD卡读卡器的计算机。

3.设置与建立支持文件系统

在SDK中,我们需要创建一个新的应用程序工程,并选择Zynq FSBL 模板作为起点。

然后我们需要按照SDK的指导建立新的设备树文件和根文件系统。

4.配置并构建内核

5.设置并测试启动

完成内核构建后,我们将使用Xilinx SDK生成的文件将ZedBoard启动到U-Boot中。

首先,我们将使用Vivado生成的bit文件和FSBL文件来设置FPGA和启动载入代码。

然后,我们将使用U-Boot设置启动参数并通过TFTP加载内核映像和设备树文件。

最后,我们可以通过串行终端连接到ZedBoard并查看启动输出,确保系统正常启动。

需要注意的是,这仅仅是嵌入式Linux移植的基本步骤。

根据具体情况,可能需要进行更多的定制和调整。

此外,由于涉及到硬件和软件的复杂性,可能需要更深入的了解和经验才能成功完成移植过程。

教你ZedBoard开发板如何玩转linaro系统

开发板:ZedBoard ?REV_D 镜像文件:BOOT.BIN、 zImage 和 devicetree Linaro 文件系统:linaro-precise-ubuntu-desktop-20120923-436.tar.gz?或者 在 linaro 官网下载 PC 平台:Ubuntu 准备好一张 4G 或以上的 SD 卡,我用的是开发板自带的卡,步骤如下 1、SD 卡分区

使用磁盘工具把 SD 卡分成两个分区,第一分区分成 FAT32 格式,用于 保存内核等镜像文件,500M 大小就足够了;第二个分区分成 EXT4 格式,用 于保存 linaro 文件系统,把 SD 卡剩余的空间都分配给它; 2、把 BOOT.BIN、zImage 和 devicetree.dtb 拷贝到分区 1 3、解压缩 linaro 文件系统,在当前会生成 binary 目录,进入 binary/boot/filesystem.dir 后可以看到文件系统目录 4、先执行 mount 命令查看第二个分区的挂载点,然后执行如下命令把文 件系统写到 SD 卡的第二个分区 # sudo rsync -a --progress ./ /第/二/分/区/挂/载/点/目/录 文件系统比较大,需要等待一段时间 5、把 SD 卡插入到 zedboard,连接 USB HUB, 插上鼠标和键盘,再连上 显示器,我用的是 HDMI 转 VGA

Opencv移植和Zedboard测试

Opencv移植和Zedboard测试继上次生成了ARM架构的链接库之后,我们要把他们拷贝到装载有文件系统的SD卡中即可,在拷贝时,最好是/usr/lib下实践一:将那些lib拷贝到U盘里面,因为之前跑过demo,里面就是一个简易的linux系统,就暂且用他试试了,正常启动后,挂载U盘,这些在之前都有做过,mount /dev/sda1 /mnt拷贝文件夹cp -R /mnt/lib /usr/ 结果出现提示空间不足,仔细发现问题,发现这个ramdisk镜像最大只能有8M,而整个lib有10.3M,肯定会提示空间不足了,在看看/usr/lib下有哪些文件发现拷贝了一些lib文件进来。

这时就想到了实践二的方法、。

疑问:然后还有一个就是书上的一句话,如果你使用的是ramdisk文件系统,则需要在拷贝完Opencv链接库之后需要重新压缩出一个镜像文件。

(有待解决这个问题)问题解释:来自于rainysky,用的系统是SD自带的那个精简版的系统,容量比较小,没法直接将编译的文件复制到里面,只能做一个镜像啦。

实践二:想利用单板机(光盘中第九章有)中的文件来实验一下,单板机的系统时linaro 的系统,之前有一个sd卡已经做好了分区,在windows下只能读出第一个分区,第二个分区在windows下是读不出来的。

将BOOT.BIN,zImage,devicetree.dtb,zynq-zed-adv7511.dtb拷贝到第一个分区,也就是FAT分区。

将ubuntu-image.tar.gz在linux 下拷贝到EXT4分区,但是结果发现这个系统时不能正常启动的,是否是因为需要PC的外设才能正常启动??(有待验证),现在只能是制作镜像了。

原来是光盘提供的BOOT.BIN 文件有问题,有待实验。

实践三:制作镜像的方法:OpenCV库:。

制作ZedBoard上linux根文件系统(ramdisk)

制作ZedBoard上linux根文件系统(ramdisk)Digilent的OOB设计给出了一个ZedBoard上完整的运行的linux系统所需要的所有文件,包括配置FPGA的bit文件、配置ARM PS系统的First-Stage boot loader(FSBL)和引导linux需要的Second-Stage boot loader(SSBL)、Linux内核zImage、设备树文件devicetree_ramdisk.dtb 以及根文件系统ramdisk8M.image.gz。

linux在运行时,加载这个ramdisk8M.image.gz镜像文件到DDR3中来执行实现根文件系统的建立,很多并不像在ubuntu中对文件系统操作那样简单。

本小节介绍如何制作ZedBoard可运行的根文件系统ramdisk8M.image.gz镜像文件,参照xilinx wiki 。

通过本小节的学习,在以后的开发中,可以更加顺利的修改文件系统,给设计带来方便。

硬件平台:Digilent ZedBoard开发环境:Windows XP 32 bit + Wmare 8.0 + Ubuntu 10.04 + arm-linux-xilinx-gnueabi交叉编译环境Zedboard linux: Digilent OOB Design1、FHS(Filesystem Hierarchy Standard)标准介绍当我们在linux下输入ls / 的时候,见到的目录结构以及这些目录下的内容都大同小异,这是因为所有的linux发行版在对根文件系统布局上都遵循FHS标准的建议规定。

该标准规定了根目录下各个子目录的名称及其存放的内容:目录名存放的内容/bin必备的用户命令,例如ls、cp等/sbin必备的系统管理员命令,例如ifconfig、reboot等/dev设备文件,例如mtdblock0、tty1等/etc。

ZedBoard的启动流程(以运行linux操作系统为例)

ZedBoard的启动流程(以运行linux操作系统为例)ZedBoard启动需要的文件:1、BOOT.bin (由fsbl.elf、system.bit、u-boot.elf 组成)2、devicetree.dtb3、uImage4、uramdisk.image.gzZedBoard的启动流程通常可以分为三个步骤:阶段0:在器件上电运行后,处理器会自动执行片内BootROM中的代码,BootROM中的代码是固化的,不可修改。

BootROM中的代码将对zynq的NAND、NOR、SD等基本外设控制器进行初始化,使ARM核可以访问使用这些外设。

而DDR等其他外设将在阶段1之后进行初始化。

同时BootROM的代码还负责将阶段1的启动镜像(fsbl镜像)加载到OCM(zynq片上一个256K的RAM,但在fsbl运行前只能使用其中的192K,所以fsbl要小于192K),然后运行fsbl。

至于从哪个外部存储器中加载fsbl镜像,要看ZedBoard上MIO[5:3]引脚选择哪种启动方式。

一般是选择从SD卡启动(这就是为什么BootROM要先对SD卡等基本外设控制器进行初始化的原因)。

阶段1:该阶段运行的是fsbl代码。

完成的主要工作是根据XPS中的配置,完成PS端的初始化(这一部分应该包括对DDR外设控制器的初始化)使用比特流文件(Bitstream)对PL进行配置(如果不使用PL,就不需要这一步)加载阶段2的代码(ssbl)到内存空间(DDR上),并运行ssbl代码注:fsbl的代码可以直接使用xilinx的SDK软件自动生成(也可根据需要进行修改),步骤很简单。

阶段2:该阶段运行的是ssbl(u-boot.elf),ssbl会完成Linux内核启动之前所必需的硬件初始化,例如串口、USB设备等。

并设置好启动参数,然后将Linux内核、设备树镜像从SD卡加载到内存中。

之后将控制权交给内核。

当Linux内核拥有系统的控制权后,就会先进行初始化,建立内核的运行环境,如进行虚拟地址到物理地址的映射。

ZedBoard上的点灯签名实验(三)linux内核引导

ZedBoard上的点灯签名实验(三)linux内核引导

经过实验一和实验二我们完成了硬件部分的工作,并且将设计导出到SDK,现在我们希望Linux可以到我们的硬件上运行,为此我们需要给Linux一个提示并且告诉它入口在哪里,这些工作就有u-boot 和FSBL来完成,他们就相当于PC机的Bios. u-boot 可以用digilent提供的,在ZedBoard_linux_Design/boot_image/里边,当然也可以自己编译。

现在我们编辑一下FSBL,在SDK中,-->File-->New-->Project-->Xilinx-->ApplicaTIon Project-->next, 然后为我们的工程起个名字,叫FSBL,其他的默认即可。

然后next进入Templates选项卡,在这儿选择Zynq FSBL,然后点Finish。

然后在Project Explorer找到-->FSBL-->src-->main.c, 会发现这里边有很多的错误,原因是因为缺少一个库文件造成的,添加#include xdevcfg.h,所有错误消失。

然后找个位置加入下面的代码,

/* Reset the USB */

{

fsbl_printf(DEBUG_GENERAL, Reset USB...\r\n);

/* Set data dir */。

《基于Zedboard和云服务器的步态识别系统的实现》范文

《基于Zedboard和云服务器的步态识别系统的实现》篇一一、引言随着人工智能技术的不断发展,步态识别作为一种生物特征识别技术,在安全监控、智能门禁等领域得到了广泛应用。

本文旨在介绍一种基于Zedboard和云服务器的步态识别系统的实现方法,通过结合硬件加速和云计算的优势,提高步态识别的准确性和效率。

二、系统架构本系统采用Zedboard作为硬件平台,通过与云服务器进行数据交互,实现步态识别功能。

系统架构主要包括以下几个部分:1. Zedboard硬件平台:Zedboard是一款基于FPGA(现场可编程门阵列)的开发板,具有丰富的接口和强大的计算能力,为步态识别提供了硬件支持。

2. 图像采集模块:通过摄像头等设备采集步态图像,将图像数据传输至Zedboard进行处理。

3. 图像处理模块:在Zedboard上运行图像处理算法,对步态图像进行预处理、特征提取等操作。

4. 数据传输模块:将处理后的步态特征数据传输至云服务器,进行进一步的识别和分析。

5. 云服务器:云服务器负责接收Zedboard传输的步态特征数据,通过机器学习、深度学习等算法进行步态识别,并将识别结果反馈至Zedboard或客户端。

三、实现过程1. 硬件平台搭建:首先,搭建Zedboard硬件平台,连接摄像头等设备,确保硬件平台正常工作。

2. 图像采集与处理:通过摄像头等设备采集步态图像,利用Zedboard上的图像处理模块进行预处理、特征提取等操作。

这一过程需要编写相应的算法程序,并利用FPGA的并行计算能力进行优化。

3. 数据传输:将处理后的步态特征数据通过网络传输至云服务器。

这一过程需要确保数据传输的稳定性和安全性。

4. 云服务器端实现:在云服务器上运行步态识别算法,对接收到的步态特征数据进行识别和分析。

这一过程可以采用机器学习、深度学习等算法,通过大量数据训练模型,提高识别的准确性和效率。

5. 结果反馈与交互:云服务器将识别结果反馈至Zedboard或客户端,实现人机交互。

rainysky陪你一起在zedboard上移植qt+opencv(三):安装界面程序qt

rainysky 陪你一起在zedboard 上移植qt+opencv

(三):安装界面程序qt

到这基本的开发环境已经差不多了,正如标题说的那样,需要安装qt,第一步就是在ubuntu 上安装QT,这个其实比较简单,在终端里面输入命令

apt-get install qtcreator 就可以自动安装下载啦(前提是你的虚拟机可以联网),安装过程是一堆安装中的细节,有兴趣的也不要干等,可以看一下安装信息,说不定有用呢。

安装完成后在点击左上角的Dash,输入qt 可以看到安装的文件

其中qtcreator 就是经常用到的程序啦,点击它

这就是qt 的主界面啦。

点击创建项目,建立一个项目,建立QT Gui 应用程序,建立路径和项目名称如下(中间新建了一个helloworld 文件夹)。

zedboard之GPIO驱动(从FPGA一直到LINUX应用)

zedboard之GPIO驱动(从FPGA一直到LINUX应用)1 EDK 大家知道我们在EDK中建立GPIO然后倒出到SDK中,在SDK中可以用C语言操作外设GPIO,但是这还是裸机程序,没有用到LINUX。

本文将记录从FPGA EDK生成GPIO一直到导入SDK中,建立.fsbl 文件,creat BOOT.BIN,然后根据前面的文章(生成uboot.elf 以及生成zImage,.dtb文件)。

然后我们在linux中编写GPIO 驱动程序,操作我们在FPGA中建立的GPIO。

这个过程十分复杂任何一个方面都要搞几个月,但是站在巨人的肩膀上就是好。

首先我们要在EDK中建立GPIO 外设,这里我用的AXI_GPIO,详细的过程不讲述了,可以参考官网资料CTT:/detail/xiabodan/7235031图1 FPGA 硬件地址分配表图2 硬件设计 2 SDK 然后到出到SDK,生成BOOT.BIN,具体步骤见/xiabodan/article/details/23379645 3 驱动编写[cpp] view plain copy#include <linux/module.h>#include <linux/kernel.h> #include <linux/fs.h>#include <linux/device.h> #include <asm/io.h>#define DEVICE_NAME "AXI_GPIO_MOUDLE" #definePWM_MOUDLE_PHY_ADDR 0x41200000 //This Address is based XPS 见图1MODULE_AUTHOR("Xilinx ");MODULE_DESCRIPTION("AXI GPIO moudle dirver"); MODULE_VERSION("v1.0"); MODULE_LICENSE("GPL"); static int pwm_driver_major; static struct class*axi_gpio_driver_class = NULL; static struct device*axi_gpio_driver_device = NULL; unsigned longAXI_gpio_fre_addr = 0; //AXI_GPIO moulde'svisual address static struct file_operations axi_gpio_fops = { .owner = THIS_MODULE, }; static ssize_tsys_axi_gpio_set (struct device* dev, struct device_attribute* attr, const char* buf, size_t count) { // unsigned int direg; //unsigned int opreg; printk("I am come in");outl(0x00000000, pwm_fre_addr+12); //设置AXI GPIO的方向输出outl(0xffffffff, pwm_fre_addr+8); //设置AXI GPIO的方向输出全为高printk("sys_axi_gpio_setpwm_fre_adr is %ld \n",axi_gpio_fre_addr);return count; } static DEVICE_ATTR(axi_gpio,S_IWUSR, NULL, sys_axi_gpio_set); static int __initaxi_gpio_driver_module_init(void) { int ret;axi_gpio_driver_major=register_chrdev(0, DEVICE_NAME,&axi_gpio_fops );//内核注册设备驱动if(axi_gpio_driver_major < 0){ printk("failed to register device.\n"); return -1; }axi_gpio_driver_class = class_create(THIS_MODULE,"axi_gpio_driver");//创建设备类if(IS_ERR(axi_gpio_driver_class)){ printk("failed to create zxi_gpio moudle class.\n");unregister_chrdev(axi_gpio_driver_major, DEVICE_NAME); return -1; } axi_gpio_driver_device =device_create(axi_gpio_driver_class, NULL,MKDEV(axi_gpio_driver_major, 0), NULL, "axi_gpio_device"); if (IS_ERR(axi_gpio_driver_device)){ printk("failed to create device .\n");unregister_chrdev(axi_gpio_driver_major, DEVICE_NAME); return -1; } ret =device_create_file(axi_gpio_driver_device,&dev_attr_axi_gpio); // if (ret < 0)printk("failed to create axi_gpio endpoint\n");axi_gpio_fre_addr = (unsignedlong)ioremap(PWM_MOUDLE_PHY_ADDR,sizeof(u32));//To get Custom IP--gpio moudle's virtual address //将模块的物理地址映射到虚拟地址上printk(" axi_gpiodriver initial successfully!\n"); return 0;} static void __exit axi_gpio_driver_module_exit(void){ device_remove_file(axi_gpio_driver_device,&dev_attr_axi_gpio);device_destroy(axi_gpio_driver_class,MKDEV(axi_gpio_driver_major, 0));class_unregister(axi_gpio_driver_class);class_destroy(axi_gpio_driver_class);unregister_chrdev(axi_gpio_driver_major, DEVICE_NAME); printk("axi_gpio module exit.\n"); }module_init(axi_gpio_driver_module_init);module_exit(axi_gpio_driver_module_exit);4 编写makefile 然后编译驱动具体见博客/xiabodan/article/details/242367575 加载insmod insmod gpio.ko进入/sys/class/axi_gpio/在此目录下echo 0 > axi_gpio可以看到zedboard上所有的LED都亮了6 声明其实以上的做法是不对的因为理论上讲驱动只为我们提供策略,不应该在驱动里面实现功能函数,不然就和裸鸡程序一抹一样了,但是这里我只是本着测试目的,不必较真。

基于Zedboard平台AXI DMA数据传输与显示的设计

基于Zedboard平台AXI DMA数据传输与显示的设计谭景甲;何乐生;王俊;朱绪东【期刊名称】《电视技术》【年(卷),期】2018(42)6【摘要】由于AXI_DMA可以大数据量的批量处理,效率要远高于单地址的数据读存.本文基于Zynq AP SoC平台的双核ARMCortex-A9多核处理器的处理系统(Processing System,PS)以及可编程逻辑(Programmable Logic,PL)单元体系结构,使用zedboard开发板PL端的的AXI DMA IP核资源,实现PL和PS高吞吐率的数据交互操作.编写linux下驱动调用xil-inx提供的AXI DMA IP驱动程序,并移植qt镜像到zedboard开发板运行的嵌入式linux操作系统中,编写qt应用程序,实现AXI DMA接口对数据的传输并在qt应用程序中显示.通过测试发现使用AXI DMA IP核进行数据传输,减轻了CPU负担,有效的提高了数据的传输效率.【总页数】5页(P41-45)【作者】谭景甲;何乐生;王俊;朱绪东【作者单位】云南大学信息学院,云南昆明 650500;云南大学信息学院,云南昆明650500;云南大学信息学院,云南昆明 650500;云南大学信息学院,云南昆明650500【正文语种】中文【中图分类】TN47【相关文献】1.基于PCIE总线主模式DMA高速数据传输系统设计 [J], 李超;邱柯妮;张伟功;罗俊鹏;徐远超2.基于FPGA的PCIExpress总线的DMA数据传输设计 [J], 姚明超;3.基于FPGA的DMA数据传输系统设计 [J], 王炳辉; 何小海; 卿粼波; 熊淑华4.基于ZYNQ-7000 DMA控制器的UART数据传输的设计与实现 [J], 夏柯;门兰宁5.基于AXI-DMA总线控制器的HDMI视频多帧缓存架构处理系统设计 [J], 贾庆生;魏伟;张楷龙;沈佳洁因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(注意:mkimage 工具是在u-boot中编译生成的)

挂载SD卡: mount /dev/mmcblk0p1 /mnt/

网卡配置:

ifconfig lo up //启动本地回环 ifconfig eth0 down //关闭eth0网卡 ifconfig eth0 up //开启eth0网卡 ifconfig eth0 192.168.58.222 //配置板子的网卡的IP

md 地址 查看内存的值 nm 地址 向该地址写入某个值

(二)内核移植 1、配置编译内核

make ARCH=arm xilinx_zynq_defconfig make ARCH = arm

make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- uImage LOADADDR=8000

char buf_n[N] = "000800"; char buf_msg[N] = "0A67095C0F5077FF01FF01\x1a";

memset(buf_thief,0,sizeof(buf_thief)); strcat(buf_thief,buf_center); strcat(buf_thief,buf_num); strcat(buf_thief,buf_n); strcat(buf_thief,buf_msg); char buf_msg1[N] = "164F60662F62117684773CFF01621172314F60554AFF01\x1a"; //`char buf_msg1[N] = "0A6709706B60C5FF01FF01\x1a"; //char buf_msg1[N] = "044F60597D\x1a"; //char buf_msg1[N] = "024F60\x1a";

int i = 0; char tmp;

for(i = 0; i < 14; i++) { if((i%2) == 0) { tmp = buf_num[i]; buf_num[i] = buf_num[i+1]; buf_num[i+1] = tmp; }

} printf("%s\n",buf_num);

}

}

sleep(1); if(news == THIEF) { if(write(fd,buf_thief,strlen(buf_thief)) == -1) { perror("fail to write AT+CMGF"); exit(-1); } } if(news == FIRE) { printf("%s\n",buf_msg); if(write(fd,buf_fire,strlen(buf_fire)) == -1) { perror("fail to write AT+CMGF"); exit(-1); } } printf("Send message over\n");

sleep(1);

if(write(fd,at_cmgf,strlen(at_cmgf)) == -1) { perror("fail to write AT+CMGF"); exit(-1); }

sleep(1);

if(write(fd,at_cmgs,strlen(at_cmgs)) == -1) { perror("fail to write AT+CMGS"); exit(-1);

zedboard系统移植

Zedboard系统移植

(一)u-boot移植 下载u-boot源码u-boot-xlnx-master.tar.gz 切换目录到家目录下:cd 解压源码:tar -xzvf u-boot-xlnx-master.tar.gz

切换目录:cd u-boot-xlnx-master

SDK2014.1里边生成设备树出现如下错误:

错误原因:设备树描述的网卡和Linux驱动里边的驱动不匹配,导致找不到网卡驱动

三、根文件系统移植 拷贝交叉编译库: ~/CodeSourcery/Sourcery_CodeBench_Lite_for_Xilinx_GNU_Linux/arm-xilinx-linux-gnueabi/libc/lib

memset(buf_fire,0,sizeof(buf_fire)); strcat(buf_fire,buf_center); strcat(buf_fire,buf_num); strcat(buf_fire,buf_n); strcat(buf_fire,buf_msg1); printf("%s\n",buf_msg); if((fd = open("/dev/s3c2410_serial1",O_RDWR | O_NOCTTY | O_NDELAY)) < 0) { perror("fail to open serial port"); exit(-1); } serial_init(fd); if(write(fd,at,strlen(at)) == -1) { perror("fail to write AT");3, =__mmap_switched @ address to jump to after @ mmu has been enabled

b __enable_mmu b __turn_mmu_on mov pc, r13//跳到__mmap_switched处执行

b start_kernel

Linux内核启动流程分析: 1.设置成SVC模式,关闭所有的中断 safe_svcmode_maskall r9 @ safe_svcmode_maskal 2.检查proc和arch以及atag的有效性 bl __lookup_processor_type @ r5=procinfo r9=cpuid bl __vet_atags 3.如果使能了SMP,则修正和SMP相关的代码 bl __fixup_smp 4.创建页表项 bl __create_page_tables 5.使能MMU b __enable_mmu

修改顶层Makefile文件:vim Makefile

make ARCH=arm CROSS_COMPILE=arm-xilinx-linux-gnueabi- zynq_zed_config 1、修改Makefile文件

2、配置zedboard make zynq_zed_config 3、make编译

ZedBoard以NFS服务启动内核:

setenv bootargs noinitrd root=/dev/nfs rw nfsroot=192.168.1.50:/home/wtw/rootfs ip=192.168.1.123:192.168.1.50:192.168.1.123:255.255.255.0::eth0:off

设备树制作:

./scripts/dtc/dtc -I dts -O dtb -o devicetree.dtb ./arch/arm/boot/dts/digilent-zed.dts -I :指定输入源文件dts -O:指定输出文件格式为dtb -o:指定输出文件名

setenv bootargs 'console=ttyPS0,115200 root=nfs nfsroot=192.168.2.50:/home/linux/rootfs ip=192.168.2.123 init=linuxrc'

make uImage LOADADDR=8000 内核启动是出现如下错误:

解决办法(转换ramdisk映象文件): mkimage -n 'Ramdisk Image' -A arm -O linux -T ramdisk -C gzip -d uramdisk.image.gz uramdisk1.image.gz

IP设置:

setenv serverip 192.168.58.222 setenv ipaddr 192.168.58.111 setenv serverip 192.168.1.50 setenv ipaddr 192.168.1.123 TFTP下载: tftpboot 3000000 uImage && bootm 0x3000000 0x2000000 0x2A00000 bootm 0x3000000 0x2000000 0x2A00000 ifconfig lo up ifconfig eth0 up ifconfig eth0 192.168.58.222 NFS挂载: mount -t nfs 192.168.58.111:/home/wtw/rootfs /mnt -o nolock mknod /dev/led c 230 222

init=/linuxrc console=ttyPS0,115200

setenv bootargs noinitrd root=/dev/nfs rw nfsroot=192.168.58.222:/home/wtw/rootfs ip=192.168.58.111:192.168.58.222:192.168.58.112:255.255.255.0::eth0:off init=/linuxrc console=ttyPS0,115200

下载好交叉编译软件xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin 将dash改为bash,在终端中输入dpkg-reconfigure dash。 选择no 修改权限:chmod a+x xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin 在终端输入:./xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin 设置环境变量在ubuntu中,环境变量的文件是 /etc/bash.bashrc,修改这个文件就行了(命令vim /etc/bash.bashrc),在末尾增加内容: export ARCH=arm export CROSS_COMPILE=arm-xilinx-linux-gnueabiexport PATH=/root/CodeSourcery/Sourcery_CodeBench_Lite_for_Xilinx_GNU_Linux/bin/:$PATH arm-xilinx-linux-gnueabi-gcc -v,如果可以打印出交叉编译器的版本信息,说明设置成功 void gprs_sendMessage(int news,char num[N]) { printf("%s\n",num); int fd; char at[N] = "AT\r"; char at_cmgf[N] = "AT+CMGF=0\r"; printf("%s\n",at_cmgf); char at_cmgs[N] = "AT+CMGS=37\r"; printf("%s\n",at_cmgs); char buf_thief[N] ; char buf_fire[N] ; char buf_center[N] = "0891683108100005F011000D91"; char buf_num[N]; memset(buf_num,0,sizeof(buf_num)); strcpy(buf_num,"86"); strcat(buf_num,num); strcat(buf_num,"F"); printf("%s\n",buf_num);