基于FPGA的微波炉控制器系统的设计(1)

基于FPGA的小型化微波发射系统设计

第44卷第1期电子器件Vol.44No.1Feb.2021 2021年2月Chinese Journal of ElccLmn DevicesDesign of Miniaturization Microwave Transmission System Based on FPGA* YANG Kai',SHEN Xuejing2ZHANG Huixin1*LIANG Yonggang3('.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan Shanxi030051,China;2.Capital Aerospace Machinery Co.,Ltd.,Bei/ing100076,China;3.The Unit68216of the People's Liberation Army of China,Bei/ing100076,China)Abstract:According Lo the test requirements of working parameters of small aircrafL during flight,a miniaLurized broadband zero-IF wireless transmitting system based on FPGA is designed.The system takes the FPGA as the main control unit,receives the parameters of the sensor on the air vehicle,and completes the output of the RF signal of the required frequency band through QPSK modulation and a reasonable up-conversion module.After testing,the transmitter output modulation signal frequency up to4000MHz,power up to10dBm,the various parameters meet the design requirements,enabling high-speed data transmission.Key words:FPGA;miniaturization;QPSK;Zero-IF;microwave;transmitterEEACC:1350doi:10・3969/j・issn.1005-9490・2021・01・006基于FPGA的小型化微波发射系统设计杨凯打沈学静2,张会新",梁永刚3(1.中北大学电子测试技术重点实验室,山西太原030051;2.首都航天机械有限公司,北京100076;3.中国人民解放军68216部队,北京100076)摘要:针对小型飞行器在飞行过程中工作状态参数的测试需求,设计了一种基于FPGA的小型化宽带零中频微波发射系统。

基于FPGA的微波炉控制器的设计

1 微波 炉的 设计 与分析

现需设 计一 个微波 炉控 制器 WB K Q, L Z 其外部 结构 如

图1 所示 。通过该 控 制 器再 配 以 4 七 段 数 码 二极 管 完 个 成 微波 炉的定 时及信 息显示 。

trb 1 k 2 a t

^ T — o £墓 嚣 -

R 慧 霉 慧 t 臀 蕾 T — T 尊 _ T 一 糍

基 于 F G 的 微 波 炉 控 制 器 的 设 计 PA

陈 平, 王树 森

( 济源职业技 术学院 信息工程 系, 河南 济源 49 0 ) 5 00

摘

要: 于FG 基 P A的 微 波 炉 控 制 器 以现 场 可 编 程 门 阵 列 F G 为载 体 , 用硬 件描 述 语 言 V D PA 使 H L编 程 实现 各

需 时问 , 系统 自动 回到 复位 状 态 , 然后 同时 4个七 段 数 码

管 显示 时间 信 息 ( 设 系统 最 长 的 烹 调 时 间 为 5 假 9分 5 9

秒) 。再 按 S A T键后 系统 进 入 烹调状 态 ,O K信 号 开 TR CO 始 为高 电平 , 此时 , 个七 段 数 码管 每 隔 1 钟变 化一 次 , 4 秒 用 以刷新 还剩 多少 时间结 束 烹调 。烹 调结 束 后 , O K信 CO

中图分类号 :M9 15 T 2 .

文献标识码 : A

文章编号 :6 17 6 (0 2 0 - 1-3 17 -84 2 1 ) 20 30 0

孛 . . . . . . ・ ・ ,夺 . . . ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ ・ 夺 夺 夺 夺 争 争 夺 { ・ 幸 幸 幸 夺 夺 夺 夺 夺 争 夺 夺 孛 夺 夺 夺 夺 夺 夺 孛 孛 牵 夺 孛 夺 孛 夺 夺 幸 夺 争 夺 夺 夺 夺 ÷ 夺

基于Verilog的微波炉控制器的设计

基于FPGA 的微波炉控制器的设计一、设计任务及要求该实验主要完成微波炉控制器的设计。

主要功能有复位开关、模式选择、烹调时间设置、LED 指示烹调状态及数码管显示烹调剩余时间。

上电后,系统处于复位状态。

工作时首先进行烹调时间设置,并使用数码管显示时间信息,设要求最长的烹调时间为59分59秒,时间设置完毕后系统处于等待状态状态;选择开始烹调模式时系统进入烹调状态,时间显示数码管按每秒减1的倒计时方式显示剩余烹调时间;烹调结束后,系统回到复位状态。

二、设计方案及流程微波炉控制器系统主要有一下五个电路模块组成:分频模块、模式选择电路、时间设置电路、倒计时模块、显示模块。

分频模块完成系统50MHz 的时钟向1Hz 的分频,使计时器能够按照1S 的频率倒计时。

模式选择电路,其功能是控制微波炉工作过程中模式的切换,选择不同的模式系统计入不同的工作状态。

时间设置模块,该模块主要是可根据用户需求输入烹调时间;倒计时电路会根据用户所设置的时间进行倒计时,由数码管显示电路显示目前烹调状态,同时由LED 灯指示系统反正在烹调。

系统总体框图如下:系统的输入输出信号如下:输入clk ,key0,key1,key2,key3,key4五个信号,输出hex0,hex1,hex2,hex3,sec_flag ,cook 六个信号。

时间设置模块50MHz 分1Hz 的 分频模块数码管显示电路倒计时电路模式选择模块图1 系统总体框图clk作为50MHz分频模块的输入,时钟上升沿有效。

Key3作为模式选择信号,mode0表示系统进入分设置模块,mode1表示系统进入秒设置模块,mode2表示系统设置时间完成,进入烹调状态。

key2的作用是在mode0及mode1模式下对分、秒设置进行加操作,按一下分、秒加1。

key1的作用是在mode0及mode1模式下对分、秒设置进行减操作,按一下分、秒信号减1。

key0作为系统的复位信号,在不同模式下按下key0系统都会进入复位状态,数码管显示”0000”,cook标志的LED灯处于灭状态。

基于FPGA的微波炉控制器系统的设计

基于FPGA的微波炉控制器系统的设计

高绘玲;赵卫东;张秀娟;倪倩;张建立

【期刊名称】《福建电脑》

【年(卷),期】2005(000)012

【摘要】本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法,系统用VHDL编程实现各底层模块的功能,顶层设计用图形输入完成.文章着重讲述了模块化设计思想和状态图描述方法在硬件描述语言中的应用,并展示了其在MAX+plusⅡ下的部分仿真结果,体现了硬件描述语言在电子设计自动化(EDA)中的方便应用.

【总页数】2页(P96-97)

【作者】高绘玲;赵卫东;张秀娟;倪倩;张建立

【作者单位】山东科技大学,信息科学与工程学院,山东,青岛,266510;山东科技大学,信息科学与工程学院,山东,青岛,266510;山东科技大学,信息科学与工程学院,山东,青岛,266510;山东科技大学,信息科学与工程学院,山东,青岛,266510;山东科技大学,信息科学与工程学院,山东,青岛,266510

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于FPGA的微波炉控制器设计 [J], 李正宇

2.基于FPGA的微波炉定时系统设计 [J], 梁丽

3.基于FPGA的微波炉控制器的设计 [J], 陈平;王树森

4.基于FPGA的微波炉控制器实验教学案例分析 [J], 李涛;吴迪;周丽娜

5.基于FPGA微波炉控制器设计 [J], 韩团军

因版权原因,仅展示原文概要,查看原文内容请购买。

基于某FPGA技术地微波炉控制器

**大学**学院现代电子系统设计**系(院)**专业题目:基于FPGA技术的微波炉控制器学生姓名:班级:学号:指导教师:完成日期:年月摘要本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法。

系统使用VHDL编程实现各底层模块的功能,顶层的设计采用图形输入完成。

本文主要阐述模块化设计的思想和状态图的描述方法,以及它们在硬件描述语言中的应用,并展示了其在QuartusⅡ开发系统下的仿真结果和烧写到EPM570T100C5后的现象。

主要有以下几个模块:状态控制器KZQ、数据装载器ZZQ、烹调计时器JSQ、显示译码器YMQ47以及分频器和动态显示电路。

该控制器具有系统复位、状态控制、时间设定、烹饪计时、动态显示译码等功能。

关键字:FPGA;VHDL;微波炉;控制器;状态图;定时器目录1.绪论 (1)1.1任务的提出 (1)1.2设计的基本要求 (1)1.3设计的目的和意义 (1)2.系统总体设计 (2)2.1系统总体方案设计 (2)2.2系统功能模块描述(具体的电路图和VHDL设计文件将在附件中给出)23.系统详细设计 (2)3.1 状态控制器KZQ的设计 (2)3.2 数据装载器ZZQ的设计 (5)3.3 烹调计时器JSQ的设计 (5)3.4 显示译码器YMQ47的设计 (5)4系统仿真 (6)4.1状态转换控制器KZQ仿真图 (6)4.2数据装载器ZZQ仿真图 (6)4.3计时器JSQ仿真 (7)4.4显示译码器YMQ47仿真图 (8)5.设计总结 (8)6.参考文献 (8)7.附件 (9)7.1整体的原理图 (9)7.2各个基本模块的VHDL语言 (9)7.2.1分频器 (9)7.2.2控制器KZQ (10)7.2.3装载器ZZQ (11)7.2.4计时器JSQ,和其中需用到的DCNT6和DCNT10 (12)7.2.5译码器YMQ47 (15)7.2.6动态显示电路需要用到的DCNT4和decoder (15)1.绪论随着人民生活水平的提高,微波炉开始进入越来越多的家庭,它给人们的生活带来了极大的方便。

基于FPGA的微波炉定时系统设计

基于FPGA的微波炉定时系统设计作者:梁丽来源:《中国教育技术装备》2016年第20期摘要介绍基于FPGA的微波炉定时系统的设计思想、开发过程和仿真结果。

用EDA技术设计电子系统,具有设计效率高、修改快捷、易于升级和性能稳定等一系列优点。

关键字 FPGA;EDA技术;微波炉;定时系统中图分类号:G642 文献标识码:B文章编号:1671-489X(2016)20-0047-031 前言以EDA工具为开发环境,以硬件描述语言VHDL为编程语言,以可编程逻辑器件FPGA 为设计载体,采用EDA技术自顶向下的电子系统设计,改进传统的电子系统设计观念。

这种方法从系统级设计入手,在顶层、方框图级、功能级、门级等分别进行系统描述、功能设计、逻辑设计、电路设计等,由于设计的主要仿真和调试过程是在高层次上完成的,极大地提高了电子系统的设计效率、可靠性和灵活性。

下面以微波炉定时系统的设计为例,介绍在MAX+PLUSⅡ软件环境下进行设计、测试,基于FPGA芯片进行硬件实现的设计过程。

2 设计要求设计一种基于FPGA的微波炉定时系统。

要求:系统通电后处于复位状态。

首先,系统读入烹调时间,并显示在数码管上;然后按START键,系统进入烹调状态,剩余烹调时间在数码管上实时刷新;烹调结束后,数码管显示烹调结束信息,系统回到复位状态。

在烹调过程中,按PAUSE键或RESET键,可使系统暂停工作或使系统回到复位状态;在复位状态下,按TEST键可测试数码管工作是否正常[1]。

3 总体设计方案从系统设计要求出发,自顶向下地将设计细化,使功能具体化、模块化。

微波炉定时系统由状态控制器、数据装载器、烹调计时器和动态显示电路等模块构成。

将各模块连接起来,用图形输入法形成顶层模块,微波炉定时系统顶层模块连接如图1所示。

4 设计实现首先进行系统设计,划分各个功能模块,然后借助于EDA工具进行具体的模块设计。

采用VHDL语言对各模块进行编程,在MAX+PLUSⅡ环境下对各程序进行编译和仿真验证,创建各模块的器件符号,待建立整体系统顶层文件时调用。

基于FPGA技术的微波炉控制器

基于FPGA技术的微波炉控制器**大学**学院现代电子系统设计**系(院)**专业题目:基于FPGA技术的微波炉控制器学生姓名:班级:学号:指导教师:完成日期:年月摘要本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法。

系统使用VHDL编程实现各底层模块的功能,顶层的设计采用图形输入完成。

本文主要阐述模块化设计的思想和状态图的描述方法,以及它们在硬件描述语言中的应用,并展示了其在QuartusⅡ开发系统下的仿真结果和烧写到EPM570T100C5后的现象。

主要有以下几个模块:状态控制器KZQ、数据装载器ZZQ、烹调计时器JSQ、显示译码器YMQ47以及分频器和动态显示电路。

该控制器具有系统复位、状态控制、时间设定、烹饪计时、动态显示译码等功能。

关键字:FPGA;VHDL;微波炉;控制器;状态图;定时器1.绪论随着人民生活水平的提高,微波炉开始进入越来越多的家庭,它给人们的生活带来了极大的方便。

它省事、省电、方便和卫生。

作为现代的烹饪工具,微波炉控制器体现着它的重要性能指标。

目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本文采用先进的EDA技术,利用QuartusⅡ工作平台和VHDL设计语言,设计了一种新型的微波炉控制器系统。

该控制器具有系统复位、状态控制、时间设定、烹饪计时、动态显示译码等功能。

1.1任务的提出设计一个微波炉控制器1.2设计的基本要求(1)七段数码管及发光二极管完成微波炉的定时及状态显示;(2)控制器的输入信号包括定时控制信号、定时数据的输入、复位信号、开始煮饭的控制信号等;(3)其他(我们自己添加了测试数码管是否能够正常显示的TEST信号)。

1.3设计的目的和意义目前大部分微波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵活。

本文采用先进的EDA技术,利用QuartusⅡ工作平台和VHDL设计语言,设计了一种新型的微波炉控制器系统。

基于FPGA的微波炉定时系统设计

技术在线・- 47 -2016年10月下 第20期(总第398期)10.3969/j.issn.1671-489X.2016.20.047基于FPGA的微波炉定时系统设计◆梁丽摘 要 介绍基于FPGA 的微波炉定时系统的设计思想、开发过程和仿真结果。

用EDA 技术设计电子系统,具有设计效率高、修改快捷、易于升级和性能稳定等一系列优点。

关键字 FPGA;EDA 技术;微波炉;定时系统中图分类号:G642 文献标识码:B 文章编号:1671-489X(2016)20-0047-031 前言以EDA 工具为开发环境,以硬件描述语言VHDL 为编程语言,以可编程逻辑器件FPGA 为设计载体,采用EDA 技术自顶向下的电子系统设计,改进传统的电子系统设计观念。

这种方法从系统级设计入手,在顶层、方框图级、功能级、门级等分别进行系统描述、功能设计、逻辑设计、电路设计等,由于设计的主要仿真和调试过程是在高层次上完成的,极大地提高了电子系统的设计效率、可靠性和灵活性。

下面以微波炉定时系统的设计为例,介绍在MAX+PLUS Ⅱ软件环境下进行设计、测试,基于FPGA 芯片进行硬件实现的设计过程。

2 设计要求设计一种基于FPGA 的微波炉定时系统。

要求:系统通电后处于复位状态。

首先,系统读入烹调时间,并显示在数码管上;然后按START 键,系统进入烹调状态,剩余烹调时间在数码管上实时刷新;烹调结束后,数码管显示烹调结束信息,系统回到复位状态。

在烹调过程中,按PAUSE 键或RESET 键,可使系统暂停工作或使系统回到复位状态;在复位状态下,按TEST 键可测试数码管工作是否正常[1]。

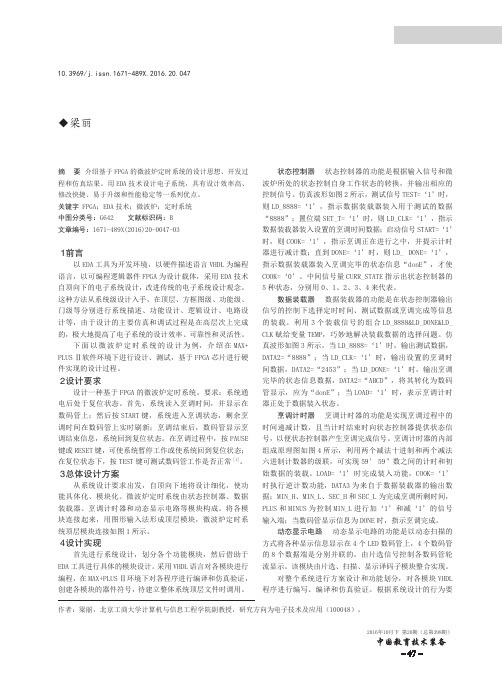

3 总体设计方案从系统设计要求出发,自顶向下地将设计细化,使功能具体化、模块化。

微波炉定时系统由状态控制器、数据装载器、烹调计时器和动态显示电路等模块构成。

将各模块连接起来,用图形输入法形成顶层模块,微波炉定时系统顶层模块连接如图1所示。

基于FPGA技术的微波炉控制器论文

南昌工程学院毕业设计(论文)信息工程学院系(院)电子信息工程专业毕业设计(论文)题目基于FPGA技术的微波炉控制器学生姓名荆玉峰班级06电子信息工程(1)班学号2006100173指导教师谢剑锋完成日期 2010 年 6 月 13 日南昌工程学院(本)毕业设计(论文)南昌工程学院毕业设计(论文)任务书I、毕业设计(论文)题目:基于FPGA技术的微波炉控制器设计II、毕业设计(论文)使用的原始资料(数据)及设计技术要求:1. 用FPGA设计微波炉控制器电路;2.可设置烹调时间;3. 具有显示功能。

4. 用MAXPLUSII软件仿真。

5. 硬件调试I I I、毕业设计(论文)工作内容及完成时间:3.29~4.15 完成开题报告;4.15~5.1 软件设计及仿真;5.2~6.10 硬件调试;6.11~7.1 撰写论文。

Ⅳ主要参考资料:1.UweMeyer-Baese.数字信号处理的FPGA实现[M],北京:清华大学出版社,20022. (英)渥伦斯基Digital System Design with VHDL,Second Edition [M]工业出版社2004.073.侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版,19994. Stephan W.Mondwurf.BENEFITSOF THE CORDIC-ALGORITHM IN A VERSATILECOFDM MODULATOR/DEMODULATOR DESIGN [M]. Fourth IEEE InternationalCaracas Conference on Devices, Circuits电子工程系电子信息工程专业类 1 班学生:荆玉峰日期:自2010年3月8日至2010年6月20日指导教师:谢剑锋助理指导教师(并指出所负责的部分):教研室主任:附注:任务书应该附在已完成的毕业设计说明书首页。

毕业设计论文_基于FPGA_的微波炉控制器设计

目 录

1. 绪论................................................................................................................................. 1 1.1. 任务的提出.......................................................................................................... 1 1.2. 课题的内容和要求.............................................................................................. 1 1.3. 设计的目的和意义.............................................................................................. 2 2. 关键技术简介................................................................................................................. 3 2.1. FPGA 简介........................................................................................................... 3 2.2. VHDL 语言概述.................................................................................................. 3 2.3. Quartus II 开发系统简介.................................................................................... 5 3. 系统总体设计................................................................................................................. 7 3.1. 系统总体设计方案.............................................................................................. 7 3.2. 系统功能模块描述.............................................................................................. 9 3.2.1. 输入模块..................................................................................................10 3.2.2. 控制模块..................................................................................................10 3.2.3. 显示模块.................................................................................................. 11 3.3. 系统的工作流程................................................................................................ 11 4. 系统详细设计............................................................................................................... 13 4.1. 输入模块设计.................................................................................................... 13 4.1.1. 键盘扫描..................................................................................................13 4.1.2. 键盘译码..................................................................................................16 4.1.3. 输入模块的实现......................................................................................17 4.2. 控制模块设计.................................................................................................... 18 4.2.1. 状态转换控制..........................................................................................19 4.2.2. 数据装载..................................................................................................22 4.2.3. 烹饪计时..................................................................................................23 4.2.4. 温度控制..................................................................................................26 4.2.5. 控制模块的实现......................................................................................29 4.3. 显示模块设计.................................................................................................... 31 5. 系统仿真....................................................................................................................... 35 5.1. 输入模块仿真.................................................................................................... 35

开题报告

-5-

主程序流程图

开

系统复 ,barbecue

Start键 ? 运

N

时间

? N

结

研究方法与技术路线

根据微波炉控制器的功能要求,可将系统分为5个部分

分频模块

功能控制 模块

计时模块

数据输入 模块

显示模块

-7-

研究方法与技术路线

分频模块

1.输入一个1KHz的信号,经分频后得到1Hz的信号,用来整个系统计数定时用。

out1[6..0] out2[6..0] out3[6..0] out4[6..0]

LED

-12-

研究方法与技术路线

顶层电路

6.各模块设计仿真实现后,可分别创建成元件符号。顶层就是将各分模块用Verilog HDL语言或者是图形方法连接起来。图所示是采用图形法新建的电路图,在图中 添加各模块元件符号,便可连接起来的实现系统电路。

基于FPGA的微波炉控制器设计

基于FPGA的微波炉控制器设计

选题背景与意义

3

研究基本内容与拟解决的问题

7

研究方法与技术路线

10

研究总体安排与进度

16

-2-

选题背景与意义

•随着系统化程度越来越高,微波炉控制正在迅速地从机 电解决方案向电控制转变。现在绝大多数的微波炉已由数 字控制。目前,应用最多的是在数字单片机上实现微波炉 控制器的设计, 利用单片机实现时间设定、 倒计时及各 种功能键都比较容易实现, 但是速度慢, 稳定性及实时 性较差,系统的硬件电路结构比较复杂。微波炉专用芯片 具有体积小,性能高,处理速度快等优点,但也存在价格 昂贵,灵活性差,设计周期长等缺点。

1 4 7 re

2 5 8 0

基于FPGA技术的微波炉控制器

**大学**学院现代电子系统设计**系(院)**专业题目:基于FPGA技术的微波炉控制器学生姓名:班级:学号:指导教师:完成日期:年月摘要本文介绍了应用FPGA芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法。

系统使用VHDL编程实现各底层模块的功能,顶层的设计采用图形输入完成。

本文主要阐述模块化设计的思想和状态图的描述方法,以及它们在硬件描述语言中的应用,并展示了其在QuartusⅡ开发系统下的仿真结果和烧写到EPM570T100C5后的现象。

主要有以下几个模块:状态控制器KZQ、数据装载器ZZQ、烹调计时器JSQ、显示译码器YMQ47以及分频器和动态显示电路。

该控制器具有系统复位、状态控制、时间设定、烹饪计时、动态显示译码等功能。

关键字:FPGA;VHDL;微波炉;控制器;状态图;定时器目录1.绪论 (1)任务的提出 (1)设计的基本要求 (1)设计的目的和意义 (1)2.系统总体设计 (2)系统总体方案设计 (2)系统功能模块描述(具体的电路图和VHDL设计文件将在附件中给出). 2 3.系统详细设计 (2)状态控制器KZQ的设计 (2)数据装载器ZZQ的设计 (5)烹调计时器JSQ的设计 (5)显示译码器YMQ47的设计 (5)4系统仿真 (6)状态转换控制器KZQ仿真图 (6)数据装载器ZZQ仿真图 (6)计时器JSQ仿真 (7)显示译码器YMQ47仿真图 (8)5.设计总结 (8)6.参考文献 (8)7.附件 (9)整体的原理图 (9)各个基本模块的VHDL语言 (9)7.分频器 (9)控制器KZQ (10)装载器ZZQ (11)计时器JSQ,和其中需用到的DCNT6和DCNT10 (12)译码器YMQ47 (15)动态显示电路需要用到的DCNT4和decoder (15)1.绪论随着人民生活水平的提高,微波炉开始进入越来越多的家庭,它给人们的生活带来了极大的方便。

它省事、省电、方便和卫生。

微波炉控制器的设计[1]

![微波炉控制器的设计[1]](https://img.taocdn.com/s3/m/da79b07c1eb91a37f1115c4e.png)

二、文献综述现有市售的微波炉其主要弊端为:不能按既有程序进行烹调,在节能方面也未做过多考虑。

烹调经验告诉我们,家常菜大多可按固定程序烹调、炖肉、煮饭、烘烤。

若采取分时、分档火力加热,则可节能。

微波炉控制系统功能比较齐全,在火力档位设了解冻、烹调、烘烤、保温、自定义加热、自定义烹调以及按给定程序烹调等七种主要功能,其中程序烹调共设置了八种不同的烹调流程,供用户选择。

在控制方面,实现了智能化,信息化管理,并且具有密码开锁功能,即只有知道相应模式键继续运行的号码的人,才能对该机进行操作等等功能。

STC12C5404AD单片机是具有全新流水线和精简指令集结构的高速率、低功耗新一代单片机。

它带有8路10位精度ADC、4路PWM/PCA(可编程计数器阵列)、SPI同步通信口以及内部集成的MAX810专用复位电路。

这些特点不但增加了开发者的使用灵活性,同时还可以帮助用户减小PCB尺寸和系统成本。

此外,STC12C5404AD型处理器还可以通过串口(P3.0/P3.1)直接下载用户程序,从而使其适合于在系统(ISP)及在应用(IAP)中编程,因而可为许多计算密集的嵌入式控制应用领域提供功能强大、使用灵活且性价比高的解决方案。

STC12C5404AD是STC系列单片机,采用RISC型CPU内核,兼容普通8051指令集,片内含有10KB Flash 程序存储器,2KB Flash 数据存储器,512B RAM 数据存储器,同时内部还有看门狗(WDT);片内集成MAX810专用复位电路、8通道10位ADC以及4通道PWM,具有在系统编程(ISP)和在应用编程(IAP),片内资源丰富、集成度高、使用方便。

STC12C5404AD对系统的工作进行实施调度,实现外部输入参数的设置、蓄电池及负载的管理、工作状态的指示等。

电磁式继电器一般由铁芯、线圈、衔铁、触点簧片等组成。

只要在线圈两端加上一定的电压,线圈中就会流过一定的电流,从而产生电磁效应,衔铁就会在电磁力吸引的作用下克服返回弹簧的拉力吸向铁芯,从而带动衔铁的动触点与静触点(常开触点)吸合。

B组:微波炉设计任务书()

湖南工程学院课程设计任务书课程名称:EDA技术题目:基于FPGA的微波炉控制器设计专业: 电子科学与技术班级:0981姓名:贺垚焱学号:08指导老师:郭照南审批:任务书下达日期2012年5月28日星期一设计完成日期2012年6月8日星期五目录总体设计。

1 课题的主要内容及基本要求。

1 设计思路。

1 设计方案。

2 模块分析。

4 状态控制电路模块。

4 数据控制电路模块。

5 计时器模块。

6 程序设计及仿真。

8 程序简要说明。

8 仿真时序图。

8 硬件调试。

11 总结。

14 参考文献。

14 附录一原理图。

15 附录二源程序。

16总体设计要求采用EDA技术设计一个微波炉控制器,可完成以下功能:(1)可控制烹调的开关;(2)可设置烹调时间,(假设系统最长的烹调时间为59分59秒);(3)可显示烹调的剩余时间。

设计思路现代数字系统设计一般采用自顶向下的方法,其过程大致可分为三个大的步骤:系统调研;模块的划分;模块的实现。

承接一个数字系统设计的课题后,一般不要急于动手设计,而应对课题作充分的分析和调研,然后确定初步的方案。

分析:课题的任务、要求、原理和使用条件等。

调研:课题现状并和相同或相近课题进行比较。

现代数字系统设计一般是将其划分为控制器和受控电路两大部分,控制器由ASM图或MDS图决定,而受控电路则使用各种通用模块实现。

下面分析微波炉定时器的工作过程及基本要求:上电后,系统处于复位状态。

工作时首先进行烹调时间设置,并使用数码管显示时间信息,设要求最长的烹调时间为59分59秒,时间设置完毕后系统自动回到初始状态;按开始烹调按键进入烹调状态,时间显示数码管按每秒减1的倒计时方式显示剩余烹调时间;烹调结束后,系统回到复位状态。

系统要求分析及初步方案的确定:根据系统的基本要求,着重应考虑如下问题:(1)计时电路的设计:芯片内部产生和外部提供。

本例中由外部时钟电路以BCD码的形式提供。

(2)时间设置出错及工作过程的取消等情况的处理:设置一个复位按键。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 2 主程序流程图 3 微波炉控制器芯片的设计

由图 1 的微波炉结构框图可以看出,控制器芯片是整个系 统的核心,该芯片的输入输出信号已有明确的定义:

计时控制模块是整个微波炉控制器芯片的核心模块,负责 完成烹饪过程中的时间递减计数,还提供烹饪完成时的状态信 号 finish 使控制状态机进入复位状态,完成信号 finish 还能控制 扬声器发出音乐提示烹调完毕。同时该模块也能产生控制信号 j1 来控制磁控管的间歇通电,以实现微波炉解冻、加热和烧烤的 不同功能。 4 芯片的编译与测试

单“MAX + plusII”—>“simulator”,启 动 仿 真 操 作 ,结 束 后 观 察 仿 真波形如图 4 所示。

图 4 仿真波形 从仿真波形中可以看出,该芯片较好地实现了微波炉控制 器 系 统 的 各 项 功 能 。为 了 进 一 步 验 证 所 设 计 电 路 的 正 确 性 ,最 后 将程序下载到 FPGA 芯片中进行硬件测试。连接硬件系统后,选 择“MAX + plusII”—>“programmer”菜 单 , 调 出 编 程 器 (program- mer) 窗口。一切就绪后,按下编程器窗口中的“configure”按钮,设 计的内 容 就 下 载 到 芯 片 EPF10K10LC84- 3 中 去 。 通 过 测 试, 该 微 波 炉 控 制 系 统 工 作 正 常 ,基 本 上 达 到 了 预 期 的 设 计 要 求 。 5 结论 应用 FPGA 芯片 和 VHDL 设 计 的 微 波 炉 控 制 器 系 统, 硬 件 电路简单,开发周期短,成本低,同时也能提高系统的可靠性和精 度 ,并 使 系 统 更 加 灵 活 ,便 于 修 改 。

为了便于描述,将整个微波炉控制器芯片的结构分成 6 大 子 模 块 :时 钟 产 生 模 块 、控 制 状 态 机 模 块 、控 制 逻 辑 模 块 、计 时 控 制 模 块 、数 据 译 码 模 块 和 显 示 控 制 模 块 。篇 幅 有 限 这 里 只 介 绍 几 个主要模块。 3.1 时钟产生模块

ASP.NET 技术实现,并在 window2003 及 SQL Server2000 环境下 测试通过的。达到了预期的目的。 结束语

随着 SQL Server 数据库管理系统功能的不断增强、性能不 断完善,将各类数据完全由数据库管理系统统一存储和管理已 成 为 可 能 。只 有 利 用 数 据 库 对 各 种 数 据 进 行 管 理 ,数 据 的 安 全 性 才 能 得 到 充 分 的 保 障 ,并 使 得 诸 如 数 据 检 索 、复 制 、备 份 等 工 作 变得非常简单容易。

图 3 最顶层的图形 编 译 成 功 后 由 于 本 设 计 中 时 钟 信 号 频 率 跨 度 较 大 ,从 10MHz 到 1Hz,为了进行整体波形仿真,将时钟信号作适当减小 后 进 行 仿 真 。首 先 建 立 波 形 文 件 ,波 形 文 件 建 好 并 存 盘 后 ,选 择 菜

参考文献: [1] 黄正瑾,徐 坚. CPLD 系统设计技术入门与应用[M] . 电子工业出

【关键词】 FPGA;VHDL;微波炉;状态图

1 引言 随着人民生活水平的提高,微波炉开始进入越来越多的家

庭,它给人们的生活带来了极大的方便。微波炉由 2450MHz的 超 高 频 来 加 热 食 物 。它 省 时 、省 电 、方 便 和 卫 生 ,作 为 现 代 的 烹 饪 工 具 ,微 波 炉 的 控 制 器 体 现 着 它 的 重 要 性 能 指 标 。目 前 大 部 分 微 波炉控制器采用单片机进行设计,电路比较复杂,性能不够灵 活。本文采用先进的 EDA 技术,利用 MAX+plusII 工作 平 台 和 VHDL 设计语言,设计了一种新型的微波炉控制器芯片,该 芯 片 具有系统复位、时间设定和烹饪计时的功能,用一片 FPGA 芯片 实现。 2 微波炉的总体结构及功能

End Sub

在 上 面 的 代 码 中 首 先 打 开 数 据 库 , 并 通 过 SQLDataReader 对象在数据库中获取 images;在输出时,必须设置 Response.con- tentType 的 类 型 跟 图 片 的 类 型 一 致 。 并 且 用 Response.Binary- Write 代 替 Response.Write 来 显 示 image 文 件 。 以 上 代 码 利 用

96

福建电脑

2005年第 12 期

基于 FP GA 的微波炉控制器系统的设计

高绘玲 赵卫东 张秀娟 倪 倩 张建立

(山东科技大学 信息科学与工程学院 山东 青岛 266510)

【摘 要】 本文介绍了应用 FPGA 芯片和硬件描述语言(VHDL)设计微波炉控制器系统的方法,系统用 VHDL 编 程 实 现 各 底 层 模 块 的 功 能 ,顶 层 设 计 用 图 形 输 入 完 成 。 文 章 着 重 讲 述 了 模 块 化 设 计 思 想 和 状 态 图 描 述 方 法 在 硬 件 描 述 语言中的应用,并展示了其在 MAX+ plusII 下的部分仿真结果,体现了硬件描述语言在电子设计自动化(EDA)中的方便 应用。

时 钟 输 入 信 号—clk;复 位 信 号 —reset;时 间 设 定 信 号—set; 加 信 号 —add;功 能 选 择 信 号 —解 冻 unfreeze、烹 调 cook 和 烧 烤 barbecue;LED 段 码 输 出 —q[7..0];LED 位 码 输 出 —dis4[3..0];扬 声器控制信号输出—finish 和继电器控制信号输出—j1。

时钟模块 的 输 入 信 号 是 10MHz的 时 钟 信 号 ;主 要 产 生 1Hz 用 于 定 时 计 数 、4Hz用 于 时 间 设 定 时 LED 闪 烁 和 1KHz用 于 LED扫 描 的 输 出 信 号 。 3.2 控制逻辑模块

2005年第 12 期

福建电脑

97

该 模 块 完 成 微 波 炉 的 系 统 逻 辑 控 制 ,包 括 时 间 的 设 定 、时 间 设定过程中 LED 位的闪烁、显示扫描的逻辑控制,还有 解 冻 、烹 调和烧烤状态信号的保持。因系统中所使用的按键为开关式按 键 ,按 键 按 下 时 产 生 有 效 信 号 ,抬 起 后 有 效 信 号 消 失 ,故 分 别 用 状态信号 unfreezeo、cooko 和 barbecueo 来标志解冻、烹调和烧烤 状态。 3.3 计时控制模块

当 各 小 模 块 分 别 编 译 成 功 后 ,则 创 建 一 个 个 元 件 符 号 。再 用 图形编辑器将各元件模块组装起来, 这就是本设计中的最顶层 的图形设计文件(如图 3 所示) 。然后选择用于编程的目标芯片, 这里用的是 altera 公司的 EPF10K10LC84- 3。 接 着,确 定 各 输 入 输出的引脚。设定完后就可以进行编译了。

微波炉的系统结构框图如图 1 所示:

27s 为 一 个 单 元 ,解 冻 是 每 27s 通 电 3s,断 电 24s;烹 调 是 第 27s 通电 15s,断电 12s;烧烤是每停 止 工 作 。

该微波炉控制系统的功能为:上电后系统首先处于复位状 态,此时数码管显示 00.00。在工作时首先按 set 键设置烹调时 间 ,第 一 次 按 set 键 时 设 置 秒 个 位 ,通 过 按 add 键 对 秒 个 位 循 环 加 1;第 二 次 按 set 键 时 设 置 秒 十 位 ;依 次 类 推 分 别 设 置 分 个 位 和 分 十 位 ,设 置 某 个 数 位 时 该 数 位 对 应 的 LED 闪 烁(假 设 系 统 最长的设置时间是 59 分 59 秒)。然后按下解冻 unfreeze 或烹调 cook 或烧烤 barbecue 键选择相应的烹调功率,在按 start 键 后 系 统进入烹饪状态,此时 4 个 7 段数码管每隔一秒变化一次,用于 刷新还剩多少时间结束烹饪。烹饪结束后,输出完成信号 finish, 扬 声 器 发 出 音 乐 提 示 烹 调 完 毕 ,然 后 系 统 回 到 复 位 状 态 。系 统 可 以通过 reset 键随时回到复位状态。其主程序流程图 2 如下:

航 空 航 天 大 学 出 版 社 ,2003.

!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!!

(上接第 132 页)

conn.Close() End Sub

4. 从数据库中输出图片 上面完成了将图片存储到数据库的操作。当需要显示图片 时 ,怎 样 从 数 据 库 中 取 出 呢 ? 下 面 是 有 关 代 码 :

开关 k1、k2 受控 于 微 波 炉 门 , 炉 门 打 开 时 ,k1、k2 断 开 ;炉 门闭合时,k1、k2 闭合。为了避免微 波 泄 漏 ,正 常 加 热 过 程 中 不 允许开门。若在加热过程中炉 门 被 打 开 ,k1、k2 立 即 断 开 ,磁 控 管停止发射微波即停止工作。

当 j1 为 1 时,继电器 jj 接通,高压发生器接通 220V 向磁控 管提供电源,磁控管产生微波烹饪(照射)食物。当 j1 为 0 时 ,jj 断 开 ,磁 控 管 停 止 工 作 。

从 图 中 可 以 看 到 ,该 系 统 由 按 键 输 入 电 路 、消 抖 同 步 电 路 、 时钟脉冲发生器、7 段 LED 显示器和控制器芯片组成。控制器芯 片是整个系统的控制核心, 它负责接收其它模块传来的输入信 号,再根据系统的功能产生相应的输出信号送到 LED 显示模块, 产生相应的控制信号给蜂鸣器和继电器。消抖同步电路用来消 去开关电平抖动现象并提供同步信号。时钟输入端是由外部时 钟发生器的输出提供的,本设计采用 10MHz 的脉冲输入。4 位显 示器要采用 4 个 7 段带点共阴极的 LED 数码管,分 别 表 示 分 和 秒 ,控 制 器 芯 片 的 8 条 segment: q[7..0]输 出 线 与 LED 的 对 应 段 相连。控制芯片的 4 条 common: dis[3..0]输出线分别接到各个 LED, 用 来 选 择 显 示 的 LED。Common 以 166Hz的 频 率 使 4 个 LED 按次序循环点亮,从而可以得到人眼观察无闪烁的稳定的 显示输出。