实验1存储器块清零

单片机实验报告

单片机实验报告实验一:存储器块清零或赋值一、实验目的1 熟悉存储器的读写方法,熟悉51汇编语言结构。

2 熟悉循环结构程序的编写。

3 熟悉编程环境和程序的调试。

二、实验内容指定存储器中某块的起始地址和长度,要求将其内容清零或赋值。

例如将4000H开始的10个字节内容清零或全部赋值为33H。

注意:1 文件不要用中文名称保存时不要用中文路径(目录),不要放在“桌面”上,源文件和工程要放在同一个文件夹下,文件名称和路径名称不要太长。

2 查看存储器菜单使用:窗口---数据窗口---XDATA 观察存储器内容3 查看SFR:窗口---CPU窗口查看CPU寄存器SFR4 单步执行:执行---单步执行(F8),每执行一步,查看每条语句涉及到的寄存器和存储器内容的变化结果,是否是指令所要得到的结果,如不是,检查错误原因,修改。

5利用多种执行方法和观察各种窗口调试程序,直至程序满意为止。

三、实验仪器微机、VW,WA VE6000编程环境软件,(单片机实验箱)Lab6000/Lab6000通用微控制器MCS51实验四、实验步骤1、新建工程文件。

(注意:文件不要用中文名称保存时不要用中文路径)2、编写程序。

3、运行和调试过程。

外部数据存储器(4000H为首地址的10个字节)中初始状态(随便赋值FFH):单步执行程序,观察SFR中外部地址指针的变化;全速执行程序,可以看到外部数据存储器已赋值33H:五、实验结果可以看到外部数据存储器已赋值33H:六、问题讨论本次实验能够清楚地了解存储器中数据的移动和赋值过程,通过单步执行,对于每一步的指令操作过程能够了解如何执行,查看每条语句涉及到的寄存器和存储器内容的变化结果。

同时,学习掌握汇编程序的编写和调试过程。

实验二:存储块移动一、实验目的1 熟悉51汇编语言程序结构。

2 熟悉循环结构程序的编写,进一步熟悉指令系统。

3 熟悉编程环境和程序的调试。

二、实验内容将指定源地址(3000H)和长度(10字节)的存储块移动到目的地址(3050H)。

实验一 清零程序 7000H

实验一清零程序7000H-70FFHMOV A,#00HMOV DPTR ,#7000HMOV R1,#00HLOOP: MOVX @DPTR ,AINC DPTRDJNZ R1,LOOPSJMP $END实验二拆字程序把7000H拆开高位放在7001H低放在7002HORG 0000HMOV DPTR, #7000HMOVX A, @DPTRMOV B,ASWAP AANL A,#0FHINC DPTRMOVX @DPTR ,AINC DPTRMOV A,BANL A,#0FHMOVX @DPTR ,ASJMP $END实验三数据传送子程序把(R2,R3)源RAM区首地址内的(R6,R7)个字节数据传送到(R4,R5)ORG 0000HMOV R2,#60HMOV R3,#00HMOV R4,#70HMOV R5,#00HMOV R6,#0FHMOV R7,#0FFHMAIN:MOV DPH,R2MOV DPL,R3MOVX A,@DPTRMOV DPH,R4MOV DPL,R5MOVX @DPTR,ACJNE R3,#0FFH,YINC R2Y:INC R3CJNE R5 ,#0FFH,MDINC R4MD :INC R5CJNE R7 ,#00H,SZ1CJNE R6 ,#00H ,SZ2SJMP $SZ1:DEC R7SJMP MAINSZ2:DEC R7DEC R6SJMP MIANEND实验五、查找相同数个数在7000H-700FH中查出几个字节是零…….. 外部:ORG 0000HMOV R0,#10HMOV R1,#00HMOV DPTR,#7000HLOOP:MOVX A,@DPTRCJNE A,#00H,LOOPINC R1LOOP1:INC DPTRDJNZ R0,LOOPMOV 30H,R1SJMP $END内部:ORG OOHMOV R2,.#10HMOV R0,#30HMOV R1,#00HLOOP:MOV A,@R0SJNE A,#00H,NEXTINC R1NEXT:INC R0DJNZ R2,LOOPMOV 40H,R1SJMP $END硬件实验一P3.3输入、P1口输出看L1-L8发光二极管的亮灯状况ORG 0000HMOV A,#00HMOV P1,ALOOP:JB P3.3,LOOPLACALL DELAYJB P3.3,LOOPLOOP1:JNB P3.3,LOOP1LACALL DELAYINC AMOV P1,AAJMP LOOPDELAY:MOV R6,#00HMOV R7,#FFHDJNZ R7,,$DJNZ R6,DELAYRETEND实验三并行I/O口8255扩展(红绿灯)MOV A,#80HMOV DPTR,#FF2BHMOVX @DPTR,ASTART:MOV DPTR,#0FF29HMOV A,#09HMOVX @DPTR,AINC DPTRMOV A,#24HMOVX @DPTR,AACALL DELAYSTART1:MOV DPTR,#0FF29HMOV A,#01HMOVX @DPTR,AINC DPTRMOV A,#86HMOVX @DPTR,AACALL DELAYMOV R1,#3START2: MOV DPTR,#0FF29HMOV A,#01HMOV @DPTR,AINC DPTRMOV A,#45HMOVX @DPTR,AACALL DEL YSDJNZ R1,S2MOV DPTR,#0FF29HMOV A,#0CHMOVX @DPTR,AINC DPTRMOV A,#30HMOVX @DPTR,AACALL DELAYMOV R1,#3S3: MOV DPTR,#0FF29HMOV A,#6AHMOV @DPTR,AINC DPTRMOV A,#28HMOVX @DPTR,AACALL DEL YSMOV DPTR,#0FF29HMOV A,#08HMOVX @DPTR,AINC DPTRMOV A,#20HMOVX @DPTR,AACALL DELYSDJNZ R1,S3JMP START1 DELYS:MOV R6,#00H DELY1:MOV R7,#00HDJNZ R7,$DJNZ R6,DEL Y1RETDELYA:MOV R5,#100D02:MOV R6,#100D03:MOV R7,#100DJNZ R7,$DJNZ R6,D03DJNZ R5,D02RETEND实验七串并转换实验ORG 0000HAJMP MAINORG OOOBHAJMP INT-T0MAIN :MOV SP ,#7FHMOV TMOD ,#01HMOV TH0,#4BHMOV TL0,#00HMOV SCON ,#00HMOV R0 ,#00HMOV R1 ,#20SETB TR0SETB ET0CLR TICLR RISETB EASJMP $INT-T0 :MOV TH0,#48HMOV TL0,#00HDJNZ R1 ,EXITMOV R1,#20MOV DPTR ,#TABMOV A ,R0MOVC A,@A+DPTRCLR TIMOV SBUF ,AINC R0CJNZ R0, #0AH ,EXITMOV R0 ,#00HEXIT :RETITAB :DB 0FCH 60H DAH F2H 66H B6H BEH E0H FEH F6H END。

单片机实验一片内外清零、数据块的传送

单片机实验报告专业:电子信息工程班级:姓名:学号:指导教师:单片机实验报告实验项目名称:片内外清零、置位和数据块传送程序实验日期: 2010-10-27 实验成绩:实验评定标准:1)实验内容否完整A()B()C()2)实验结果分析是否正确A()B()C()3)实验报告是否按照规定格式A()B()C()一、实验目的1、掌握汇编语言中对芯片内外存储器的清零,置位。

2、掌握8031 内部RAM 和外部RAM 之间的数据传送方法;掌握这两部分RAM 存贮器的特点与应用,掌握各种数据传送方法。

二、实验内容及要求1、将片内从50H开始的连续30个地址内容清零;将片外7000H_79FFH单元内容清零;将片内从20H开始的连续30个地址内容设置为0FEH。

2、试编写将外部的数据存贮区6030~607FH 的内容写入外部RAM 3030~307H 中。

三、实验步骤1、片内外清零、置位打开Keil程序,执行菜单命令“Project”→“New Project ”创建“片内外清零置位”项目,并选择单片机型号为AT89C51。

执行菜单命令“File”→“New ”创建文件,输入源程序,保存为“片内外清零置位.A51”。

在“Project”栏的File项目管理窗口中右击文件组,选择“Add Files to Group ‘Source Group1’”将源程序“片内外清零置位.A51”添加到项目中。

执行菜单命令“Project”→Options for Target ‘Target 1’”,在弹出的对话框中选择“Output”选项卡,选中“Greate HEX File”。

执行菜单命令“Project”→“Build Target 1”,编译源程序。

如果编译成功,则在“Outp ut Window”窗口中显示没有错误,并创建了,“片内外清零置位. HEX”文件。

执行菜单命令“Debug”→“Start/Stop Debug Seesion”,按键F11键,单步运行程序。

清零程序实验报告

清零程序实验报告清零程序实验报告一、引言在计算机科学领域中,清零程序是一种常见且重要的操作。

它的作用是将某个变量或内存空间的值归零,以便重新使用或准备下一次计算。

清零程序的设计和实现对于提高计算机性能和保证数据的准确性具有重要意义。

本实验旨在探索清零程序的设计思路和实现方法,并通过实际编写代码来验证其功能和效果。

二、实验目的1. 理解清零程序的概念和作用;2. 掌握清零程序的设计原则和实现技巧;3. 通过实验验证清零程序的正确性和效率。

三、实验方法本实验采用C语言作为编程语言,使用Visual Studio Code作为开发工具。

实验步骤如下:1. 定义一个变量或内存空间,并初始化其值;2. 设计清零程序的算法和逻辑;3. 编写代码实现清零程序;4. 运行程序并验证清零结果;5. 分析程序的效率和优化空间。

四、实验过程1. 定义变量并初始化在本实验中,我们选择一个整型变量x作为示例。

首先,我们给x赋一个初始值,例如x=100。

2. 设计清零程序的算法和逻辑清零程序的算法和逻辑可以有多种实现方式。

在本实验中,我们选择一种简单而高效的方法来实现清零功能。

具体算法如下:将变量x的值赋为0。

3. 编写代码实现清零程序根据上述算法,我们可以使用C语言编写清零程序的代码。

代码示例如下:```c#include <stdio.h>int main() {int x = 100; // 初始化变量x的值为100x = 0; // 清零操作printf("清零后的值为:%d\n", x);return 0;}```4. 运行程序并验证清零结果将上述代码保存为一个C文件,使用编译器进行编译和运行。

在运行程序后,我们可以看到输出结果为"清零后的值为:0",证明清零程序的功能正常。

五、实验结果与分析通过本实验,我们成功设计并实现了一个简单的清零程序。

在实验中,我们选择了一种简单而高效的清零算法,即直接将变量的值赋为0。

存储器块清零实验报告

竭诚为您提供优质文档/双击可除存储器块清零实验报告篇一:实验1存储器块清零实验一存储器块清零一、实验目的1.掌握存储器读写方法2.了解存储器的块操作方法二、实验设备1.伟福Lab6000增强型开放式通用实验/仿真系统;2.计算机。

三、实验要求指定存储器中某块的起始地址和长度,要求能将其内容清零。

将外部数据存储器中2000h开始的20个存储器单元内容清零。

四、实验说明通过本实验,学生可以了解单片机读写存储器的读写方法,同时也可以了解单片机编程,调试方法。

如何将存储器块的内容置成某固定值(例全填充为0FFh)?请学生修改程序,完成此操作。

五、程序框图六、实验结果七、实验分析篇二:实验1存储器块清零程序实验1存储器块清零程序一、实验要求指定存储器中某块的起始地址和长度,将其内容清零。

二、实验目的1、学习使用模拟软件,编辑简单程序;2、掌握存储器的读写方法;3、了解存储器块操作块操作方法三、实验内容1、实验步骤启动pc机,打开uVision2软件。

创建工程project文件,然后创建main.c源程序,。

实现对数据块Da[10]的清零函数clearDataZone:2、对代码进行编译,编译无误后,进入Debug运行程序,打开数据窗口(DATA),点击暂停按钮,观察要清零的数据区是否被清零。

同时打开反汇编代码窗口,找出这段c代码用到的汇编指令有哪些?并对反汇编代码截图。

指令:moVsJmpLJmpoRLcLRJnZJZLcALLDec3、针对2中你看到的每一句汇编代码写出相应的含义,并标出。

c:0x011b7808moVR0,#0x08含义:将0x08这个数据传送到R0寄存器中c:0x0138120XXDLcALLclearDataZone(c:013D)含义:长调用指令,调用clearDataZone函数c:0x013b80FesJmpc:013b含义:短转移指令c:0x01441DDecR5含义:减1指令。

清零

SJMP $ 在一个源程序中必须有END伪指 令,而且只能有一个END,且放 END 在整个程序的最后。

思考 假使把2000H~20FFH中的内容改成FFh, 如何修改程序。

查找零的个数(在2000H--200FH中查出有几个 字节是零,把个数放在2100H单元中)

L00: ORG 0000H MOV R0,#10H ;查找16个字节 MOV R1,#00H MOV DPTR,#2000H MOVX A,@DPTR CJNE A,#00H,L16 ;取出内容与00H相等吗? INC R1 ;取出个数加1 INC DPTR DJNZ R0,L11 ;未完继续 MOV DPTR,#2100H MOV A,R1 MOVX @DPTR,A ;相同数个数送2100H SJMP L1E

L11:

L16:

L1E:

SE01: MOV R0,#00H

MOV DPTR,#2000H ;(2000H)送DPTR ORG用于指定该伪指令后面的源程序存放的 LOO1: CLR A 起始地址,也就是汇编后的目标机器码存放的首 MOVX @DPTR,A ;0送(DPTR) 地址。若ORG后面不带地址参数,则默认为0。 INC DPTR ;DPTR+1 在一个源程序中,可以根据需要多次使用ORG伪 INC R0 ;字节数加1 指令来定位。 CJNE R0,#00H,LOO1 ;不到FF个字节再清

软件实验一 清零程序

软件实验一 清零程序

实验目的

掌握汇编语言设计和调试方法,熟悉键盘

操。

实验内容

把2000H~20FFH的内容清零。

首地址

实验步骤

以0640H为起始地址用连续或单步方式运 行程序,检查2000H~20FFH中执行程序前 后的内容变化。

实验一 存储器块清零

实验一存储器块清零一、实验目的:1、掌握存储器读写方法;2、了解存储器的块操作方法。

二、实验设备:电脑和THGZ-1单片机.CPLD/FPGA综合开发实验装置三、实验说明:实验给出存储器的起始地址和长度,要求能将其内容清零。

通过实验了解单片机读写存储器的方法,了解单片机编程、调试方法。

四、实验内容及步骤1、推上左侧空气开关;2、启动计算机,打开伟福仿真软件 Keil Uvsion2,进入仿真环境,⑴、建立工程项目:点击主菜单 PROJEKT→NEW PROJECT→工程名 XXX.UV2(保存在桌面上)a、CPU选择:ATMEL公司→ AT89C51Copy Standrrd 8051 Startup Code……? 否⑵、进行仿真器的设置:打开 View →PROJECT WINDOW 界面,右键点击TARGET1 选择 OPTIONS FOR TARGET TARGET1b、目标机晶振选择:TARGET → XTAL → (24.0 改为 11.0592 MHZ)c、调试选项:DEBUG →⊙USE SIMULATOR⑶、创建程序文件:FILE→NEW FILE→在 TEXT 文本界面(英文输入状态)输入源程序START EQU 8000HORG 0000HAJMP MAINORG 0030HMAIN: MOV DPTR, #START ;起始地址MOV R0,#00H ;设置256字节计数值CLR ALOOP: MOVX @DPTR,AINC DPTR ;指向下一个地址DJNZ R0,LOOP ;计数值减一LJMP $END输入完毕,另存文件 SAVE AS名 XXX.ASM(保存在桌面上)⑷、添加程序到工程组:点开TARGET1→SOURCE GROUP →ADD FILES TO GROUP “SOURCE GROUP1”在文件类型窗口选择: ALL FILES在文件名窗口输入要调试的程序文件名 : 桌面: ???.ASM点击“ADD”键,并关闭此窗口⑸、查看源程序:双击 SOURCE GROUP 下的文件名 ???.ASM (SOURCE GROUP下只允许一个文件,其他用 REMOVE FILE FROM SOURCE GROUP 删去)打开XXX.ASM 源程序,阅读、理解、分析该程序。

实验一 清零实验

用来编写汇编程序

第一次课实验内容

片内清零实验 将片内RAM30H-40H单元清零 片外实验 将片外8000H~80FFH单元写入数据 “AB” 片外实验

实验内容

拆字实验 将片内RAM20H单元中的数据在 数码管上显示出来

一、片内实验

内容:将片内RAM30H-40H单元清零。

7 FH

40H

0

30H

……

00H ~ 7FH即128字节用户RAM区。

00 H

RAM

每个字节只能存放一位8位数据

三种写入方式

一,立即数直接传送

MOV 30H, #0 MOV 31H, #0…………….MOV 4H, #0三种写入方式

二、间接传送指令循环送数

MOV R0, #30H 不是40H(因为30H 到40H为11个单元) LOOP: MOV @R0,#0 INC R0 CJNE R0,#41H, LOOP 判断 AJMP & 等待

实验内容第一次第二次第三次第四次清零实验?拆字实验定时器实验?系统设计方法串并转换第五次第六次第七次第八次da转换?习题课?直流电机速度检测?考试实验环境介绍一硬件at89c51系列单片机实验箱二软件keilc软件用来编写汇编程序第一次课实验内容将将片内ram30h40h单元清零片内清零实验片外实验将片内ram20h单元中的数据在数码管上显示出来将片内ram20h单元中的数据在数码管上显示出来将片外8000h80ffh单元写入数据将片外8000h80ffh单元写入数据ab拆字实验实验内容片外实验一片内实验内容

添加成功

4,编译、调试

5, 运行

查看结果(考试内容) 单步运行查看结果 查看片内30H单元中的值

连续运行查看结果

单片机存储器清零

ORG 0000H;定义下一条指令的地址

MOV A,R0;取转换值

ANL A,#0FH;屏蔽高4位

ADD A,#03H;计算偏移量

MOVC A,@A+PC;查表

MOV R0,A;存结果于R0中

SJMP $

ORG 2000H;定义以下数据表的首地址

ASCTAB:DB ‘0’,‘1’,‘2’,‘3’;十六进制数据表

材 料

设 备

单片机仿真实验系统

(单片机、PC机、LED 8只、74LS240、连接线若干等)

实 验

实 训

内 容

方 法

步 骤

复习提问:

1.单片机控制八个发光二极管的硬件电路如何搭接?

2.在上节课的实训中如何实现点亮一个或多个LED的控制?

(学生回顾回答)

引入:回顾汇编语言清零程序?如何在实训设备上完成、并观察到效果。

DB ‘4’,‘5’,‘6’,‘7’

DB ‘8’,‘9’,‘A’,‘B’

DB ‘C’,‘D’,‘E’,‘F’

END

老师给学生讲解:

1)各指令的含义及使用方法;

2)编程的格式;

3)注释的格式及作用。

试输入、保存、调试、单步运行程序。并查看程序存储器中的结果。

实 验

实 训

要 求

考 核

方 法

1、正确理解数据传送指令的功能及程序的功能。(40分)

实训内容:

用单片机实现7000H~70FFH的内容硬件电路图。正确连接PC机与单片机,开机(开单片机和PC机)。

(让学生搭建单片机控制的硬件电路)

2、在PC机上运行DVCC-52实验系统,按PCDBG键。

3、输入源程序并保存为XXX.ASM文件,再执行“编译连接传送”功能。

单片机软件实验1清零实验

单片机软件实验1-清零实验姓名:学号:班级:同组人:指导老师:报告日期:软件设计实验1:清零实验➢实验目的:掌握汇编语言设计和调试方法。

➢实验内容:使用AT89C52单片机对单片机内部RAM进行清零操作,实验内容如下:1.把 90H-AFH的内容置为#55H;2.把90H-9FH的内容清零。

➢实验问答:1.清零之后,90H-9FH的内容是什么?A0H-AFH的内容是什么?答:90H-9FH内容:00H;A0H-AFH:#55H2.累加器A、堆栈指针SP的初始状态是什么?答:累加器A:00H,堆栈指针SP:07H。

➢实验程序:================================================ $NOMOD51$INCLUDE (80C52.MCU);======================= ======================== ; DEFINITIONS;======================= ========================;======================= ======================== ; VARIABLES;======================= ========================;======================= ======================== ; RESET and INTERRUPT Loop:jmp Loop;======================= ======================== ENDVECTORS;======================= ========================; Reset Vectororg 0000hjmp Start;======================= ======================== ; CODE SEGMENT;======================= ========================org 0100hStart:MOV R0,#90HMOV R3,#20HLOOP1:MOV @R0,#55HINC R0DJNZ R3,LOOP1MOV R2,#10HMOV R1,#90HCLR0:MOV @R1,#00HINC R1DJNZ R2,CLR0; Write your codehere** 单个实验报告内容限制在两页之内,采用双面打印,所有报告统一装订;表头内容需要手工签写。

存储器块清零实验报告

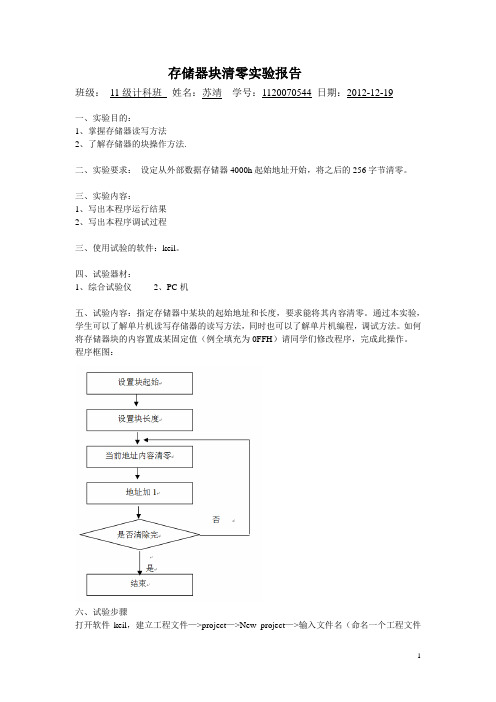

存储器块清零实验报告班级:11级计科班姓名:苏靖学号:1120070544 日期:2012-12-19一、实验目的:1、掌握存储器读写方法2、了解存储器的块操作方法.二、实验要求:设定从外部数据存储器4000h起始地址开始,将之后的256字节清零。

三、实验内容:1、写出本程序运行结果2、写出本程序调试过程三、使用试验的软件:keil。

四、试验器材:1、综合试验仪2、PC机五、试验内容:指定存储器中某块的起始地址和长度,要求能将其内容清零。

通过本实验,学生可以了解单片机读写存储器的读写方法,同时也可以了解单片机编程,调试方法。

如何将存储器块的内容置成某固定值(例全填充为0FFH)请同学们修改程序,完成此操作。

程序框图:六、试验步骤打开软件keil,建立工程文件—>project—>New project—>输入文件名(命名一个工程文件夹)—>选择单片机型号—>Atmel—>选择AT89c52型号,点确定。

然后新建文件,并命名—>输入程序保存(.asm或.c,对应汇编语言或C语言)添加目标文件,然后调试程序及理解:Org 0000hLjmp start1start1:Mov dptr,#3000h ;起始地址mov r2,#08h ;清零mov a, #00hloop:Movx @dptr, a ;指向下一个地址inc dptr ;记数减一djnz r2, loopSjmp $end然后启动仿真调试:最后把程序从PC机下载到综合试验仪里面,观察灯的闪烁情况。

七、试验中遇到的难题R0的地址以及程序代码的编写。

六、实验后的心得体会熟练掌握了存储器读写方法,了解了存储器的块操作方法,并对代码的编写有了更深的体会。

反馈清零法实验总结报告

反馈清零法实验总结报告

实验目的

1、掌握内存读写方法。

2、了解内存的块操作方法。

二、实验内容

对指定内存起址和长度的块,要求将其内容清零,设起址为4000H,长度为1000H。

三、实验程序框图

四、实验步骤

脱机模式:

(1)在P态下,按SCAL键,输入2DC0,按EXEC键。

(2)按复位键RST,查看内存4000H 4FFFH单元内容应为00联机模式:

(1)在PC机和实验系统联机状态下,运行该实验程序,可用鼠标左键单击菜单栏“文件”或工具栏“打开图标”,弹出“打开文件”的对话框,然后打开8kAsm文件夹,点击S5.ASM文件,单击“确定”即可装入源文件,再单击工具栏中编译,即可完成源文件自动编译、装载日标代码功能,再单击“调试”中“连续运行”或工具图标运行,即开始运行程序。

(2)按“系统复位”键,查看内存4000H~4FFFH单元内容应为00。

实验一-清零程序

实验一-清零程序实验一清零程序一、实验目的: 掌握汇编语言设计和调试方法,熟悉键盘操作。

二、实验内容:把2000H~20FFH 的内容清零。

三、实验程序框图四、实验步骤: 用连续或单步方式运行程序,检查2000~20FF 中执行程序前后的内容变化。

五、思考:假使把1000H~10FFH 中的内容改成FF,如何修改程序,请分别用连续和单步方式运行程序来完成校验证六、程序清单(1)基本程序(文件名SW01.ASM)ORG 0000HLJMP SE01ORG 0640HSE01: MOV R0,#00H ;(00H)送R0,R0 为计数器MOV DPTR,#2000H ;(2000H)送DPTRLOO1: CLR A ;累加器A 清零MOVX @DPTR,A ;存储空间内容清零INC DPTR ;DPTR 加1INC R0 ;R0 加1CJNE R0,#FFH,LOO1 ;若R0 不等于00,则跳转至LOO1 继续循环LOOP: SJMP LOOPEND七、思考:假使把1000H~10FFH 中的内容改成FF程序如下:ORG 0000HLJMP SE01ORG 0640HSE01: MOV R0,#00H ;(00H)送R0,R0 为计数器MOV DPTR,#1000H ;(2000H)送DPTRLOO1: MOV A,#FF;累加器A 置FFMOVX @DPTR,A ;存储空间内容置FFINC DPTR ;DPTR 加1INC R0 ;R0 加1CJNE R0,#FFH,LOO1 ;若R0 不等于00,则跳转至LOO1 继续循环LOOP: SJMP LOOPEND现象:运行第一条程序可以发现1000H~10FFH 中的内容变成FF,运行第二条程序1000H~10FFH 中的内容改成00.而其它单元的内容不变。

心得:该实验的内容比较简单。

实验二P3.3 口输入,P1 口输出一、实验目的:掌握P3 口、P1 口简单使用。

单片机实验指导书0807

单片机实验指导书张彦编机电职业技术学院机电系单片机实验室(2008年6月编)伟福仿真器系统概述本仿真器系统由仿真主机+仿真头、MULT1A用户板、实验板、开关电源等组成。

本系统的特点是:1.主机+仿真头的组合,通过更换不同型号的仿真头即可对各种不同类型的单片机进行仿真,是一种灵活的多CPU仿真系统。

采用主机+POD组合的方式,更换POD,可以对各种CPU进行仿真。

本仿真器主机型号为E2000/S,仿真头型号为POD8X5X(可仿真51系列8X5X单片机)。

2.双平台,具有DOS版本和WINDOWS版本,后者功能强大,中/英文界面任选,用户源程序的大小不再有任何限制,支持ASM,c,PLM语言混合编程,具有项目管理功能,为用户的资源共享、课题重组提供强有力的手段。

支持点屏显示,用鼠标左键点一下源程序中的某一变量,即可显示该变量的数值。

有丰富的窗口显示方式,多方位,动态地显示仿真的各种过程,使用极为便利。

本操作系统一经推出,立即被广大用户所喜爱。

3.双工作模式1.软件模拟仿真(不要仿真器也能模拟仿真)。

2.硬件仿真。

4.双CPU结构,100%不占用户资源。

全空间硬件断点,不受任何条件限制,支持地址、数据、外部信号、事件断点、支持实时断点计数、软件运行时间统计。

5.双集成环境编辑、编译、下载、调试全部集中在一个环境下。

多种仿真器,多类CPU仿真全部集成在一个环境下。

可仿真51系列,196系列,PIC系列,飞利蒲公司的552、LPC764、DALLAS320,华邦438等51增强型CPU。

为了跟上形势,现在很多工程师需要面对和掌握不同的项目管理器、编辑器、编译器。

他们由不同的厂家开发,相互不兼容,使用不同的界面,学习使用都很吃力。

伟福WINDOWS调试软件为您提供了一个全集成环境,统一的界面,包含一个项目管理器,一个功能强大的编辑器,汇编Make、Build 和调试工具并提供千个与第三方编译器的接口。

由于风格统一,大大节省了您的精力和时间。

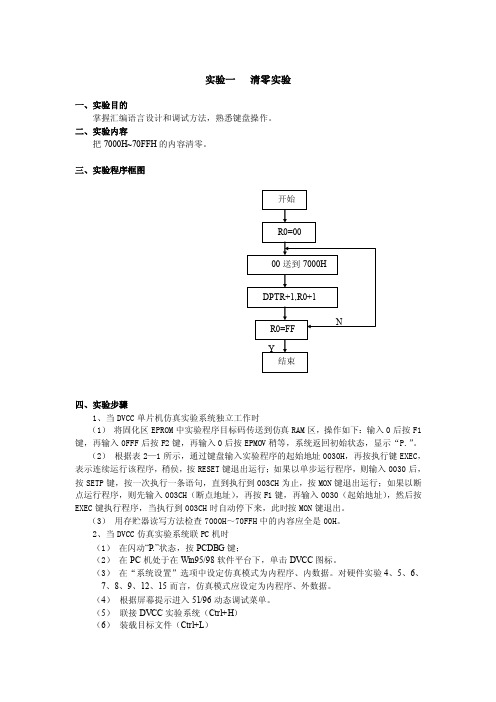

实验一清零实验

实验一清零实验一、实验目的掌握汇编语言设计和调试方法,熟悉键盘操作。

二、实验内容把7000H~70FFH的内容清零。

三、实验程序框图四、实验步骤1、当DVCC单片机仿真实验系统独立工作时(1)将固化区EPROM中实验程序目标码传送到仿真RAM区,操作如下:输入0后按F1键,再输入0FFF后按F2键,再输入0后按EPMOV稍等,系统返回初始状态,显示“P.”。

(2)根据表2—1所示,通过键盘输入实验程序的起始地址0030H,再按执行键EXEC,表示连续运行该程序,稍侯,按RESET键退出运行;如果以单步运行程序,则输入0030后,按SETP键,按一次执行一条语句,直到执行到003CH为止,按MON键退出运行;如果以断点运行程序,则先输入003CH(断点地址),再按F1键,再输入0030(起始地址),然后按EXEC键执行程序,当执行到003CH时自动停下来,此时按MON键退出。

(3)用存贮器读写方法检查7000H~70FFH中的内容应全是00H。

2、当DVCC仿真实验系统联PC机时(1)在闪动“P.”状态,按PCDBG键;(2)在PC机处于在Win95/98软件平台下,单击DVCC图标。

(3)在“系统设置”选项中设定仿真模式为内程序、内数据。

对硬件实验4、5、6、7、8、9、12、15而言,仿真模式应设定为内程序、外数据。

(4)根据屏幕提示进入51/96动态调试菜单。

(5)联接DVCC实验系统(Ctrl+H)(6)装载目标文件(Ctrl+L)(7)设置PC起始地址(8)从起始地址开始连续运行程序(F9)或单步(F8)或断点运行程序(9)单步、断点运行完后,在存贮器窗口内检查7000H~70FFH中的内容是否全为00H一、思考:假使要把7000~70FFH中的内容改成FF,如何编制程序。

实验二拆字实验一、实验目的掌握汇编语言设计和调试方法。

二、实验内容把7000H的内容拆开,高位送7001H低位,低位送7002H低位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一存储器块清零

软件操作过程:新建文件→保存文件(汇编语言后缀.ASM、C语言后缀.C)→新建项目(出现3个对话框)→对话框1:加入模块文件(选择要加的文件)→对话框2:加入包含文件(头文件之类的,没有可以点取消)→对话框3:保存项目(输入项目名称,注意项目和加入的文件必须在同一个文件夹中)→打开相应的模块文件,输入程序→点击绿色“开始”按钮,运行检查错误修改,直到没有错误为止。

窗口:CPU窗口——特殊功能寄存器窗口、工作寄存器窗口

数据窗口——DATA片内数据存储器

XDAT片外数据存储器

CODE程序存储器

BIT 位存储区

仿真器设置:点仿真器→仿真器设置→选择仿真(Lab2000p仿真)→选择仿真头(MCS51实验)→选择CPU(8031/8032)→选择是否使用软件模拟器→点击好

请编写程序,将片内RAM 30H-4FH单元中的内容清零。

MOV R0,#30H

MOV R1,#32

L0:MOV @R0,#00H

INC R0

DJNZ R1,L0

SJMP $

请编写程序,将片内RAM 60H-7FH单元中的内容置为FEH。

MOV R0,#60H

MOV R1,#32

L0:MOV @R0,#0FEH

INC R0

DJNZ R1,L0

SJMP $

1、片外ram50h—7fh内容置为:feh

MOV DPTR,#50H

MOV R1,#48

MOV A,#0feH

L0:MOVX @DPTR,A

INC DPTR

DJNZ R1,L0

SJMP $

2、片内RAM 20H-4FH中内容置为(20h)=00h,(21h)=01h,(22h)=02h, ,(4fh)=2fh MOV A,#00H

MOV R1,#20H

MOV R0,#48

MOV @R1,A

LOOP: INC A

INC R1

MOV @R1,A

DJNZ R0,LOOP

END。