新EDA 与数字系统设计 第2版 教学课件 李国丽 等编著 附录A

合集下载

数字电路EDA设计(第二版)第六章 典型数字系统设计

9

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY div_half IS

PORT(clkin:IN STD_LOGIC;

div_out:BUFFER STD_LOGIC);

END div_half;

第六章 典型数字系统设计

● 分频器; ● 交通灯控制器; ● 数字频率计; ● 数字钟电路; ● LCD接口控制电路; ● 串行口控制器; ● 2FSK/2PSK信号产生器

1

分频电路

分频电路是数字电路中应用十分广泛的一种单元电路。尤其在EDA系统中, 由于FPGA芯片外接晶振通常频率较高(如XILINX公司的BASYS电路板的晶 振最高可产生100MHz的时钟信号),而系统中不同模块所需的工作时钟频 率一般是不同的,当所需频率小于晶振提供的频率时,就需要分频电路对晶振 提供的高频时钟频率进行降频,以获得所需的工作时钟。

(3)电平定义: 按键s1按下时相当于输入信号为低电平。 (4)观察验证: 用示波器36脚的输出波形与12引脚的时钟信号的频率,可以观察到12 引脚的时钟信号为10MHz,而36脚的波形为0.67MHz方波信号,从而实现了 占空比50%的15分频分频器的逻辑功能。

11

交通灯控制器

介绍模仿十字路口的交通灯控制效果的VHDL编程控制方法, 实验过程采用实验平台上的红黄绿三种色彩的LED灯代表红灯、 黄灯与绿灯,在东西和南北方向各有一组红黄绿灯,通过编程 控制不同方向不同色彩的LED按照交通指挥的规律亮灭。

ELSE cnt2<=cnt2+1;

END IF;

END IF;

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY div_half IS

PORT(clkin:IN STD_LOGIC;

div_out:BUFFER STD_LOGIC);

END div_half;

第六章 典型数字系统设计

● 分频器; ● 交通灯控制器; ● 数字频率计; ● 数字钟电路; ● LCD接口控制电路; ● 串行口控制器; ● 2FSK/2PSK信号产生器

1

分频电路

分频电路是数字电路中应用十分广泛的一种单元电路。尤其在EDA系统中, 由于FPGA芯片外接晶振通常频率较高(如XILINX公司的BASYS电路板的晶 振最高可产生100MHz的时钟信号),而系统中不同模块所需的工作时钟频 率一般是不同的,当所需频率小于晶振提供的频率时,就需要分频电路对晶振 提供的高频时钟频率进行降频,以获得所需的工作时钟。

(3)电平定义: 按键s1按下时相当于输入信号为低电平。 (4)观察验证: 用示波器36脚的输出波形与12引脚的时钟信号的频率,可以观察到12 引脚的时钟信号为10MHz,而36脚的波形为0.67MHz方波信号,从而实现了 占空比50%的15分频分频器的逻辑功能。

11

交通灯控制器

介绍模仿十字路口的交通灯控制效果的VHDL编程控制方法, 实验过程采用实验平台上的红黄绿三种色彩的LED灯代表红灯、 黄灯与绿灯,在东西和南北方向各有一组红黄绿灯,通过编程 控制不同方向不同色彩的LED按照交通指挥的规律亮灭。

ELSE cnt2<=cnt2+1;

END IF;

END IF;

EDA及数字系统设计

电气工程与自动化学院

College of Electrical Engineering and Automation

Ⅰ QuartusⅡ上手

• 新建一个工程; • 创建文件; • 编译工程; • 分配引脚; • 时序仿真; • 下载调试;

电气工程与自动化学院

College of Electrical Engineering and Automation

十六进制/任意进制计数器;

(1、74160/74161/7490芯片方案; 2、D触发器方案;)

二十四进制、六十进制计数 器模块(VHDL方案);

Ⅳ 0820 PM

校时模块;

Ⅴ 0821 AM 数字钟设计;

闹钟模块;

Ⅵ 0821 PM

系统联调、精简;

Ⅶ 0822 AM

电气工程与自动化学院

College of Electrical Engineering and Automation

• File -> New Project Wizard

第一个空格里填工程 文件夹保存地址,地址 不支持包含中文;

第二个空格填上工程 的名称(注意:与“模 块名”区分),不支持 中文,且前三个字符不 允许数字;

第三个空格默认与第 二个空格一致;

电气工程与自动化学院

College of Electrical Engineering and Automation

电气工程与自动化学院

College of Electrical Engineering and Automation

Ⅰ QuartusⅡ上手

• 新建一个工程; • 创建文件; • 编译工程; • 分配引脚; • 时序仿真; • 下载调试;

数字系统设计与EDA技术(第2版)4

4.2.2 编辑文件

1.建立图形输入文件 单击File→New选项,弹出如图4-9所示的新文件选择 对话框。

选中Block Diagram/Schematic File(图形输 入方式)选项,单击【OK】按钮确认。进入

图形编辑器的编辑环境

2.输入元件及管脚 在图4-10所示图形编辑窗口中 图形编辑区的任意位置上双击,即可弹出元件输入

4.1.2 安装与授权

1.安装 双击下载软件90_quartus_free的图标,出 现安装向导。

2 .单击【Next】按钮开始安装 3 .授权 不同的授权文件具有不同的权限,学习版

或基本版授权的软件在使用时会受到某些限制, 例如有些功能或器件不可用,但对于学习软件的 使用方法及其开发过程并不影响。其他版本的软 件在安装完成之后,还需要完成授权工作,才能 保证软件的正常工作。

2.启动软件

单击桌面上的图标或单击“开始”→“所 有程序”→Altera→QuartusⅡ 9.0 Web Edition→QuartusⅡ 9.0 Web Edition,

3.打开项目建立向导

单击【Create a New Project】按钮,弹出 的新项目建立向导介绍界面。

单击【Next】按钮,打开如图4-4所示的新项目建 立向导对话框。

4.2 设计向导

为使介绍言简意明,以第2章实训中设计的楼梯 照明控制电路为例学习操作,楼梯照明控制电路 如图所示。

4.2.1 项目建立

1.项目准备

在E盘根目录下建立E:\Example文件夹作为 项目文件夹,项目名是Control,项目仅含 一个设计文件,顶层设计文件名也是 Control,采用图形输入方式。

4.建立项目

• 单击第1个对话框右侧的 按钮,在弹出的窗 口中选择E:\Example文件夹,单击【打开 】按钮;然后在第2个对话框中输入项目名 、在第3个对话框输入顶层设计文件名。项 目和文件名称可由字母、数字和下划线组 成。在本例中项目和顶层文件名均为 Control。

数字逻辑与数字集成电路第2版

CATALOGUE

06

平均无故障时间、平均修复时间、可用性等,这些指标用于衡量数字系统的可靠性水平。

采用冗余设计、容错技术、故障检测与恢复机制等手段,提高数字系统的可靠性,确保系统稳定运行。

设计方法

可靠性指标

故障诊断

通过监控系统的运行状态、分析异常数据等方式,快速定位故障原因,为故障排除提供依据。

详细描述

总结词

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。

详细描述

可编程逻辑器件是一种可以通过编程实现各种数字逻辑功能的集成电路。它由可编程的逻辑门电路组成,用户可以通过编程来配置这些门电路的连接和参数,从而实现所需的数字逻辑功能。常见的可编程逻辑器件包括可编程逻辑阵列(PLA)、可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)等。由于其灵活性高、可重复编程的特点,可编程逻辑器件被广泛应用于数字系统设计、数字信号处理和嵌入式系统等领域。

数字系统设计

CATALOGUE

03

将数字系统设计分为逻辑抽象、功能抽象和行为抽象三个层次,以便更好地理解和设计复杂的数字系统。

抽象化设计

从系统总体功能和行为出发,逐步细化设计,直至完成每个最小单元的设计。

自顶向下设计

将复杂的数字系统划分为若干个相对独立、功能明确的模块,便于设计、调试和维护。

模块化设计

数字逻辑与数字集成电路第2版

contents

目录

数字逻辑基础数字电路基础数字系统设计数字信号处理数字通信与网络数字系统安全与可靠性

数字逻辑基础

CATALOGUE

01

03

逻辑表达式的化简

通过逻辑代数的基本定理和运算规则,将复杂的逻辑表达式化简为简单的形式,便于分析和理解。

EDA技术与VHDL实用教程(第2版)电子课件 第1章EDA技术概述

2.计算机辅助工程设计CAE阶段

各种设计工具,如原理图输入、编译与 连接、逻辑模拟、测试码生成、版图自动布 局以及各种单元库均已齐全。由于采用了统 一数据管理技术,因而能够将各个工具集成 为一个CAE系统。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

3.电子系统设计自动化ESDA阶段

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

三、 面向FPGA/CPLD的常用EDA工具

可编程逻辑器件PLD(Programmable Logic Device)是一种可根据用户需要而自行构造逻辑功 能的逻辑器件。目前主要有两大类型:CPLD( Complex PLD)和FPGA(Field Programmable Gate Array)。借助于EDA工具软件,用原理图、硬件描 述语言等设计输入法,可设计生成相应的目标文件 ,最后用编程器下载到目标器件实现用户需要的逻 辑功能。生产PLD的厂家很多,但最有代表性的PLD 厂家为Altera、Xilinx和Lattice公司。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

1. ALTERA 其原先的开发工具MAX+PLUS II是较成功的PLD 开发平台,现在使用Quartus II开发软件。

2. XILINX 开发软件为Foundation和ISE。

3. Lattice-Vantis 开发工具ispLEVER比Altera和Xilinx略逊一筹。

EDA技术与VHDL实用教程

作者: 苏莉萍 陈东 廖超平

1. ALTERA 其原先的开发工具MAX+PLUS II是较成功的PLD 开发平台,现在使用Quartus II开发软件。

EDAPPT课件

1. EDA技术的起源 2. EDA技术的发展技术及特点

常用EDA软件介绍

1. EDA软件的分类 2. EDA软件的发展趋势

EDA工程的设计流程 EDA工程的设计方法

1.1 EDA技术简介

EDA(Electronic Design Automation 电子设计

自动化)的定义:

1. 狭义的定义: 以计算机为工作平台; 以相关的EDA开发软件为工具; 以大规模可编程逻辑器件(包括CPLD、FPGA、 EPLD等)为设计载体; 以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述的主要表达方式; 自动完成系统算法,电路设计,最终形成电子系统或 专用集成芯片的一门新技术。

20世纪70年代,由于设计师对图形符号使用数量有限, 因此传统的手工布图方法无法满足产品复杂性的要求, 更不能满足工作效率的要求,就产生了一些单独的软件 工具,主要有印制电路板(PCB)布线设计、电路模拟、 逻辑模拟及版图的绘制等。

这种应用计算机进行辅助设计的时期,就是计算机辅助 设计CAD阶段。

利用这些工具,设计师能在产品制作之前预知产品的

功能与性能,能生成产品制造文件,使设计阶段对产 品性能的分析前进了一大步,这就是真正的计算机辅 助工程设计CAE阶段。

飞速发展,其工艺水平已

达到了深亚米微米级,在一个芯片上可以集成上百万、 上千万乃至上亿个晶体管,芯片的工作频率可达到 GHz,发展到了甚超大规模集成电路阶段。

该阶段的硬件系统设计,仍然使用大量不同型号的标

准芯片,实现电子系统设计。

随着微电子工艺的发展,相继出现了集成上万只晶体

管的微处理器、集成几十万乃至上百万储存单元的随 机存储器和只读存储器的超大规模集成电路。

常用EDA软件介绍

1. EDA软件的分类 2. EDA软件的发展趋势

EDA工程的设计流程 EDA工程的设计方法

1.1 EDA技术简介

EDA(Electronic Design Automation 电子设计

自动化)的定义:

1. 狭义的定义: 以计算机为工作平台; 以相关的EDA开发软件为工具; 以大规模可编程逻辑器件(包括CPLD、FPGA、 EPLD等)为设计载体; 以硬件描述语言HDL(Hardware Description Language)为系统逻辑描述的主要表达方式; 自动完成系统算法,电路设计,最终形成电子系统或 专用集成芯片的一门新技术。

20世纪70年代,由于设计师对图形符号使用数量有限, 因此传统的手工布图方法无法满足产品复杂性的要求, 更不能满足工作效率的要求,就产生了一些单独的软件 工具,主要有印制电路板(PCB)布线设计、电路模拟、 逻辑模拟及版图的绘制等。

这种应用计算机进行辅助设计的时期,就是计算机辅助 设计CAD阶段。

利用这些工具,设计师能在产品制作之前预知产品的

功能与性能,能生成产品制造文件,使设计阶段对产 品性能的分析前进了一大步,这就是真正的计算机辅 助工程设计CAE阶段。

飞速发展,其工艺水平已

达到了深亚米微米级,在一个芯片上可以集成上百万、 上千万乃至上亿个晶体管,芯片的工作频率可达到 GHz,发展到了甚超大规模集成电路阶段。

该阶段的硬件系统设计,仍然使用大量不同型号的标

准芯片,实现电子系统设计。

随着微电子工艺的发展,相继出现了集成上万只晶体

管的微处理器、集成几十万乃至上百万储存单元的随 机存储器和只读存储器的超大规模集成电路。

EDA技术与数字系统设计第4章 VHDL语言基础幻灯片PPT

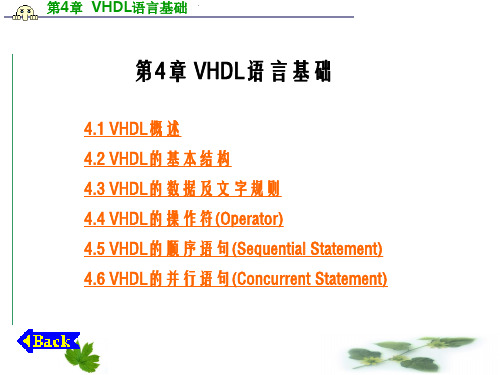

第4章 VHDL语言基础

ARCHITECTURE choice OF mux41 IS

--结构体说明

SIGNAL able:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

able<=sel;

PROCESS(able) --进程

BEGIN

CASE able IS

WHEN "00"=> p<=a;

第4章 VHDL语言基础

4.1 VHDL 概 述

4.1.1 VHDL语言的起源 VHDL语言起源于1983年,1986年IEEE标准化组织开始工

作,讨论VHDL语言标准。1987年12月IEEE接受VHDL为 标准HDL,这就是IEEE Std.l076-1987(LRM87)。1993年 IEEE对VHDL重新修订,增加了一些功能,公布了新的 标准版本IEEE Std.1076-1993 (LRM93)。

实 体 (E N T IT Y ) 结 构 体 (A R C H IT E C T U R E )

进 程 (P R O C E S S ) 或其他结构

配 置 (C O N F IG U R A T IO N )

图4.1 VHDL程序的基本结构示意图

第4章 VHDL语言基础

从例4.1的描述可以看出,一个最基本的VHDL程序由三部 分组成:库说明(LIBRARY)、实体说明(ENTITY)和结构 体说明(ARCHITECTURE),其它的结构层次可根据需要 选用。一个程序只能有一个实体,但可以有多个结构 体。

并且可以并入设计库。其功能是对设计实体与外部电路 进行接口描述,例如它可以对一个门电路、一个芯片、 一块电路板乃至整个系统进行接口描述。

最新课件-EDA技术与数字系统设计教学第1章EDA技术概述 精品

XC9500/4000、Coolrunner (XPLA3)、Spartan、Virtex 系列等,可用门数为1200~18 000;A1tera公司的主要 产品有MAX3000/7000、FLEX10K、APEX20K、 ACEX1K、Stratix、Cyclone系列等,提供门数为 5000~250 000;Lattice公司的主要产品有 ispLSI2000/5000/8000、MACH4/5、ispMACH4000等, 集成度可多达25 000个PLD等效门。

Foundation 项目管理器集成了 Xilinx 实现工具,并包含

了强大的Synopsys FPGA Express综合系统,是业界最 强大的EDA设计工具之一。

1.2.3 输入方式 常用的硬件描述语言有 VHDL 语言、 Verilog 语言和 ABEL语言。 VHDL 语言作为 IEEE 的工业标准硬件描述语言,在 电子工程领域已成为事实上的通用硬件描述语言。

第1章 EDA技术概述

1.1 EDA技术的发展史

1.2 EDA技术的主要内容

1.3 EDA技术的发展趋势

1.1 EDA技术的发展史

EDA技术伴随着计算机、集成电路、电子系统设计 的 发 展 , 经 历 了 计 算 机 辅 助 设 计 (Computer Assist Design ,简称 CAD) 、计算机辅助工程设计 (Computer Assist Engineering Design,简称CAED)和电子设计自动 化 (Electronic Design Automation ,简称 EDA) 三个发展 阶段。

Verilog 语言支持的 EDA 工具较多,适用于 RTL 级和

门电路级的描述,其综合过程较 VHDL 稍简单,但在 高级描述方面不如VHDL。

Foundation 项目管理器集成了 Xilinx 实现工具,并包含

了强大的Synopsys FPGA Express综合系统,是业界最 强大的EDA设计工具之一。

1.2.3 输入方式 常用的硬件描述语言有 VHDL 语言、 Verilog 语言和 ABEL语言。 VHDL 语言作为 IEEE 的工业标准硬件描述语言,在 电子工程领域已成为事实上的通用硬件描述语言。

第1章 EDA技术概述

1.1 EDA技术的发展史

1.2 EDA技术的主要内容

1.3 EDA技术的发展趋势

1.1 EDA技术的发展史

EDA技术伴随着计算机、集成电路、电子系统设计 的 发 展 , 经 历 了 计 算 机 辅 助 设 计 (Computer Assist Design ,简称 CAD) 、计算机辅助工程设计 (Computer Assist Engineering Design,简称CAED)和电子设计自动 化 (Electronic Design Automation ,简称 EDA) 三个发展 阶段。

Verilog 语言支持的 EDA 工具较多,适用于 RTL 级和

门电路级的描述,其综合过程较 VHDL 稍简单,但在 高级描述方面不如VHDL。

EDA课件第2章

PLD的集成度分类 的集成度分类

可编程逻辑器件(PLD)

简单 PLD

复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

一般将GAL22V10(500门~750门 )作为简单 ( 一般将 门 门 作为简单PLD 和高密度PLD的分水岭 和高密度 的分水岭

பைடு நூலகம்

四种SPLD器件的区别 器件的区别 四种

ispLSI器件的结构与特点 器件的结构与特点 (1)采用 工艺。 )采用UltraMOS工艺。 工艺 器件均支持ISP功能。 功能。 (2)系统可编程功能,所有的 )系统可编程功能,所有的ispLSI器件均支持 器件均支持 功能 (3)边界扫描测试功能。 )边界扫描测试功能。 (4)加密功能。 )加密功能。 (5)短路保护功能。 )短路保护功能。

JATG模 模 式

TCK

GND

-

-

GND

JTAG方式的在系统编程 方式的在系统编程

CPLD编程下载连接图 编程下载连接图

JTAG方式的在系统编程 方式的在系统编程

多个MAX器件的 器件的JTAG链配置方式 多个 器件的 链配置方式

FPGA器件的配置 器件的配置

Cyclone器件的 模式配置电路 器件的AS模式配置电路 器件的

2.9 FPGA/CPLD器件概述 器件概述

Xilinx公司的 公司的FPGA和CPLD器件系列 公司的 和 器件系列

1. Virtex-4系列 系列FPGA 系列 2. SpartanⅡ& Spartan-3 & Spartan 3E器件系列 Ⅱ 器件系列 3. XC9500 & XC9500XL系列 系列CPLD 系列 4. Xilinx FPGA配置器件 配置器件SPROM 配置器件 5. Xilinx的IP核 的 核

EDA课件—数字系统设计

延时 物理时间

可编程ASIC技术

22

可编程ASIC技术

• 可编程ASIC技术概论 • Altera可编程ASIC器件 • Xilinx可编程ASIC器件

23

电子设计自动化Electronic Desige Automation(EDA)

CAE(前端) Viewlogic Summit Synopsys Cadence OrCAD Data I/O COMPASS ASIC VHDL VHDL VHDL Verilog HDL Abel CAD(后端) Xilinx Altera Lattice AMD Foundation MAX+PlusII PDS+ Microsim

Pilkington FPAA FPMA

配置文件

24

集成电路的发展是从小规模—中规模—大规模—超大规模, 发展的方向是两方面:通用集成电路,专用集成电路 定制 半定制1.标准单元 2.门阵列 3.可编程逻辑器件 编程方式:1.一次编程 熔丝开关, 反熔丝开关 2.多次编程 浮栅编程 3.无限次编程 基于SRAM编程元件 1.静态存储器 2.反熔丝开关 3.浮栅编程技术:浮栅,叠栅,电可改写,闪速存储单元

31

练习一

• 上网查找EDA相关网站及相关设计、仿真工具 • 重点查找网站 /

32

Altera¿ ±³ Ã Õ Á É à Ì Å ó Ð ¨PLD£ Í (FLEX) £ © º

13

图:嵌入式Internet应用

14

最新进展之:可编程片上系统(SOPC)

• SOPC:可编程逻辑器件在嵌入式应用中的完美体现 • SOPC的技术基础 – 超大规模可编程逻辑器件及其开发工具的成熟

• FPGA密度提高 • FPGA成本足以与ASIC抗衡 • FPGA设计、综合、仿真、测试工具性能飞速提高

可编程ASIC技术

22

可编程ASIC技术

• 可编程ASIC技术概论 • Altera可编程ASIC器件 • Xilinx可编程ASIC器件

23

电子设计自动化Electronic Desige Automation(EDA)

CAE(前端) Viewlogic Summit Synopsys Cadence OrCAD Data I/O COMPASS ASIC VHDL VHDL VHDL Verilog HDL Abel CAD(后端) Xilinx Altera Lattice AMD Foundation MAX+PlusII PDS+ Microsim

Pilkington FPAA FPMA

配置文件

24

集成电路的发展是从小规模—中规模—大规模—超大规模, 发展的方向是两方面:通用集成电路,专用集成电路 定制 半定制1.标准单元 2.门阵列 3.可编程逻辑器件 编程方式:1.一次编程 熔丝开关, 反熔丝开关 2.多次编程 浮栅编程 3.无限次编程 基于SRAM编程元件 1.静态存储器 2.反熔丝开关 3.浮栅编程技术:浮栅,叠栅,电可改写,闪速存储单元

31

练习一

• 上网查找EDA相关网站及相关设计、仿真工具 • 重点查找网站 /

32

Altera¿ ±³ Ã Õ Á É à Ì Å ó Ð ¨PLD£ Í (FLEX) £ © º

13

图:嵌入式Internet应用

14

最新进展之:可编程片上系统(SOPC)

• SOPC:可编程逻辑器件在嵌入式应用中的完美体现 • SOPC的技术基础 – 超大规模可编程逻辑器件及其开发工具的成熟

• FPGA密度提高 • FPGA成本足以与ASIC抗衡 • FPGA设计、综合、仿真、测试工具性能飞速提高

C1.1(new)数设

电子CAE (Computer Aided Engineering)计算机辅助工程

EDA阶段 电子设计自动化

15

系统级设计

混合电路设计

综合与仿真

数字电路设计

EDA 工具

模拟电路设计

版图设计

PCB板设计

PLD开发

高速电路设计

EDA技术的功能和范畴

16

※系统设计层次的划分:

版图级 (物理级) 逻辑门级 寄存器传输级 系统级(行为 级、算法级)

一、数字系统的概念

二、数字系统的发展 三、数字系统的设计流程

四、用于开发PLD (FPGA和CPLD) 的EDA工具

10

一、数字系统的概念

是指对数字信息进行存储、传输、处理的电子系统。 它的输入和输出都是数字量。

通常把门电路、触发器等称为逻辑器件;将由逻辑 器件构成,能执行某单一功能的电路,如计数器、译码 器、加法器等,称为逻辑功能部件;把由逻辑功能部件 组成的能实现复杂功能的数字电路称数字系统。

17

※现代EDA技术的特点:

(1)逻辑综合与优化

(2)采用硬件描述语言进行设计 (3)开放性和标准化 (4)更完备的库

18

三. 数字系统的两种设计思路:

●自底向上法(Bottom-up设计)

设计过程从最底层设计开始。设计系统硬件时,首先选择具 体的元器件,用这些元器件通过逻辑电路设计,完成系统中各独 立功能模块的设计,再把这些功能模块连接起来,搭建成完整的 硬件系统。

第一部分数字系统设计概论第二部分可编程逻辑器件pld第四部分veriloghdl语言第一章4学时第二章4学时第四五六七章14学时第六部分上机实验quartusii软件16学时第五部分总复习2学时10四用于开发pldfpga和cpld的eda工具一数字系统的概念二数字系统的发展三数字系统的设计流程11一数字系统的概念是指对数字信息进行存储传输处理的电子系统