用VerilogHDL实现I_2C总线功能_图文.

iic协议--Verilog及仿真

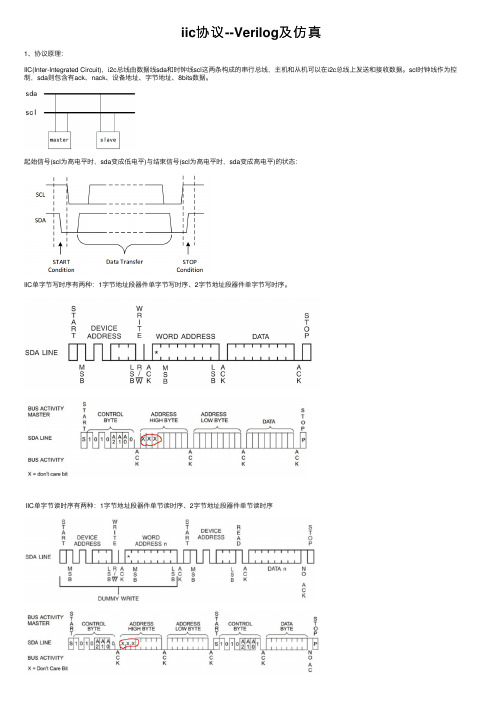

iic协议--Verilog及仿真1、协议原理:IIC(Inter-Integrated Circuit),i2c总线由数据线sda和时钟线scl这两条构成的串⾏总线,主机和从机可以在i2c总线上发送和接收数据。

scl时钟线作为控制,sda则包含有ack、nack、设备地址、字节地址、8bits数据。

起始信号(scl为⾼电平时,sda变成低电平)与结束信号(scl为⾼电平时,sda变成⾼电平)的状态:IIC单字节写时序有两种:1字节地址段器件单字节写时序、2字节地址段器件单字节写时序。

IIC单字节读时序有两种:1字节地址段器件单节读时序、2字节地址段器件单节读时序字节地址⾼三位xxx:这⾥使⽤的EEPROM的存储容量只有8192bits(1024bits*8)=210*23=213,所以16位的字节地址就多余了三位。

2、协议代码:1、这⾥实现的是2字节单次读写。

2、开始和结束时,虽然scl为⾼电平,sda仍要变化;接下来传输字节,scl为低电平,sda才能变化。

这⾥采取在scl⾼电平和低电平中线产⽣标志。

3、通过状态机来实现读写。

综合代码:module IIC_AT24C64(input sys_clk,input sys_rst_n,input iic_en,input [2:0]cs_bit,//可编程地址input [12:0]byte_address,//字节地址input write,input read,input [7:0]write_data,output reg[7:0]read_data,output reg scl,inout sda,output reg done);parameterSYS_CLK=50_000_000,//系统时钟50MHzSCL_CLK=200_000;//scl时钟200KHzreg [7:0]scl_cnt;//时钟计数parameter div_cnt=SYS_CLK/SCL_CLK;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)scl_cnt<=8'd0;else if(scl_cnt == div_cnt-1'b1)scl_cnt<=8'd0;elsescl_cnt<=scl_cnt+1'b1;end//⽣成scl时钟线always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)scl<=1'b1;else if(scl_cnt == (div_cnt>>1)-1'b1)scl<=1'b0;else if(scl_cnt == div_cnt-1'b1)scl<=1'b1;elsescl<=scl;end//scl电平中线reg scl_high_middle;//scl⾼电平中线reg scl_low_middle;//scl低电平中线always @(posedge sys_clk or negedge sys_rst_n)beginscl_high_middle<=1'b0;scl_low_middle<=1'b0;endelse if(scl_cnt == (div_cnt>>2))scl_high_middle<=1'b1;else if(scl_cnt == (div_cnt>>1)+(div_cnt>>2))scl_low_middle<=1'b1;else beginscl_high_middle<=1'b0;scl_low_middle<=1'b0;endendreg [15:0]state;parameteridle=16'd1,//空闲状态w_or_r_start=16'd2,//设备地址device_ADDR=16'd3,//发送ACK1=16'd4,byte_ADDR_high=16'd5,//字节地址⾼8位ACK2=16'd6,byte_ADDR_low=16'd7,//字节地址低8位ACK3=16'd8,w_data=16'd9,//写数据ACK4=16'd10,r_start=16'd11,//读开始device_ADDR_r=16'd12,//设备地址读ACK5=16'd13,r_data=16'd14,//读数据NACK=16'd15,//⾮应答位stop=16'd16;reg sda_en;//sda数据线使能reg sda_reg;//sda数据暂存位reg [7:0]sda_data_out;//sda数据发给从机暂存reg [7:0]sda_data_in;//sda数据取之从机暂存reg [3:0]bit_cnt;//每⼀bitassign sda=sda_en?sda_reg:1'bz;//读写标志位reg w_flag;reg r_flag;always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)beginstate<=idle;w_flag<=1'b0;r_flag<=1'b0;sda_reg<=1'b1;done<=1'b0;sda_en<=1'b0;endelse begincase(state)idle:beginsda_reg<=1'b1;w_flag<=1'b0;r_flag<=1'b0;sda_en<=1'b0;sda_reg<=1'b1;done<=1'b0;if(iic_en && write)beginw_flag<=1'b1;sda_en<=1'b1;sda_reg<=1'b1;state<=w_or_r_start;endelse if(iic_en && read)beginr_flag<=1'b1;sda_en<=1'b1;sda_reg<=1'b1;state<=w_or_r_start;endelsestate<=idle;endw_or_r_start:beginif(scl_high_middle)beginsda_reg<=1'b0;sda_data_out<={4'b1010,cs_bit,1'b0};//在这⾥装好设备地址bit_cnt<=4'd8;state<=device_ADDR;endelse beginsda_reg<=1'b1;state<=w_or_r_start;endenddevice_ADDR:beginif(scl_low_middle)beginsda_reg<=sda_data_out[7];sda_data_out<={sda_data_out[6:0],1'b0};//在这⾥发出设备地址。

VerilogHDL实验报告

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用

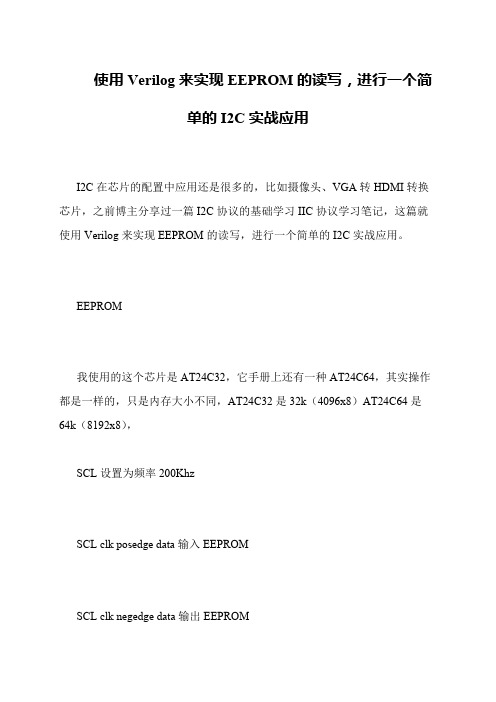

使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用 I2C在芯片的配置中应用还是很多的,比如摄像头、VGA转HDMI转换芯片,之前博主分享过一篇I2C协议的基础学习IIC协议学习笔记,这篇就使用Verilog来实现EEPROM的读写,进行一个简单的I2C实战应用。

EEPROM 我使用的这个芯片是AT24C32,它手册上还有一种AT24C64,其实操作都是一样的,只是内存大小不同,AT24C32是32k(4096x8)AT24C64是64k(8192x8), SCL设置为频率200Khz SCL clk posedge data输入EEPROM SCL clk negedge data输出EEPROM SDA 双向Pin A2,A1,A0 Device Addr default all 0,只操作一片可悬空引脚。

WP 接地正常读写,WP接Vcc写操作被禁止 字节寻址地址,是由12(AT24C32)或13bit(AT24C64)的地址组成,需要操作16位字地址高3或4位忽略即可。

Device Address 8’hA0写器件地址,8’hA1读器件地址 写字节操作 随机读字节操作 我这个芯片是双字节数据地址,所以在写数据地址时要写两次,先是高字节后是低字节。

开始结束标志 这个I2C总线的时序是一致的。

EEPROM应答 输出应答sclk的第九个周期给出,低电平应答。

如果主机没有收到应答,需要重新配置。

数据传输时序 sda数据线在scl时钟的下降沿中间变化,可以避免产生误触开始结束标志。

I2C Design i2c_start为高电平有效,传输完成后会产生一个i2c_done结束标志,表示操作完成。

I2C状态转移图 I2C写操作 (1)产生start位 (2)传送器件地址ID_Address,器件地址的最后一位为数据的传输方向位,R/W,低电平0表示主机往从机写数据(W),1表示主机从从机读数据(R)。

复杂数字逻辑的VerilogHDL设计方法HDLV

模块C

模 块A1

模 块A2

模 块A3

模 块B1

模 块B2

模 块C1

模 块C2

电路图 设计文件

电路功能 仿真

有问题

没问题

HDL 设计文件

HDL 功能仿真

没问题 HDL 综合

有问题

确定实现电路 的具体库名

与实现逻辑的物 理器件有关的工艺 技术文件

优 化 、布 局 布 线

布线后门级仿真 没问题

电路制造工艺文件 或 FPGA 码 流 文 件

- 软件只能提高系统的灵活性能 - 军用系统的实时、高可靠、低功耗要求 - 系统的功能专一,但对其各种性能要求极高 - 降低系统的设计和制造成本

怎样设计如此复杂的系统?

• 传统的设计方法: - 查用器件手册;

- 选用合适的微处理器和电路芯片; - 设计面包板和线路板; - 调试; - 定型; - 设计复杂的系统(几十万门以上)极其困难。

程就是。

• 常用的编程语言:C、Pascal、Fortran、Basic

或汇编语言。

计算机体系结构和硬线逻辑 的基本概念

• 计算机体统结构:是一门讨论和研究通

用的计算机中央处理器如何提高运算速度 性能的学问。

• 硬线逻辑: 由与门、或门、非门、触发

器、多路器等基本逻辑部件造成的逻辑系 统。

数字信号处理系统的分类

实时数字信号 处理系统实现中存在的技术难点

和解决办法

电路实现的两个方向: • FPGA • 专用集成电路

实时数字信号 处理系统实现中存在的技术难点

和解决办法

用于信号处理的 FPGA 和专用集成 电路(ASIC)设计的方法: Verilog HDL建模、仿真、综合和全

PCI总线目标接口状态机的Verilog HDL实现

关 键 词 : C 总 线 ; 独 热 编 码 方 式 ;V ro H ; 状 态 机 ; C L PI ei g DL l PD

中图法分 类号 :P 7 +5 T 23.

文 献标 识码 : A

为 计 算 机 的标 准 总 线 。C 总 线 具 有 总 线 主 控 能 力 , 3 MH PI 在 3 z

O 引 言

随 着 计 算 机 技 术 的 发 展 ,C 总线 已逐 渐 取 代 IA总线 成 PI S

设 备 都 对 此 地 址 译 码 , 选 中 的 从 设 备 要 置 DE E # 效 以 被 VS L 有

声 明 自己 被 选 中 ,同时 对 命 令 译 码 确 定 访 问 类 型 。 在 接 下 来

QI i—n XI nl , L i ANG J ny n i —o g a

(co l f eh i l h s s X da nvri , ’ 10 1 hn ) Sh o Tc nc y i , ii U ies y Xin7 0 7 i o aP c n d a C a

的 数 据 期 中,R # T D 分 别 表 示 主 、 P I 备 准 备好 。 IDY 和 R Y# 从 C设 两者 同时 有 效 , 在 时 钟 上 升 沿 传 输 数 据 : 从 双 方 可 以分 别 则 主 通 过 使 ID 或 T DY 无 效 , 数 据 期 中插 入 等 待 周 期 。数 R Y# R # 在 据 传 输 结 束 前 , 主 P I 过 撤 销 F AME 并 建 立 I D # 明 C通 R # R Y 标

文章编 号 :007 2 2 0 ) 226 .2 10 .0 4(06 1.2 80

verilog课件 lec02_hdl

Chapter 4 <18>

单击此B处it编M辑母a版n标ip题u样l式ations: Example 2

SystemVerilog:

module mux2_8(input logic [7:0] d0, d1,

Chapter 4 <7>

单击此H处D编L辑母S版im标题u样la式tion

SystemVerilog:

module example(input logic a, b, c, output logic y);

assign y = ~a & ~b & ~c | a & ~b & ~c | a & ~b & c; endmodule

/*…*/ multiline comment

Chapter 4 <12>

单击此R处e编d辑u母c版t标io题n样O式 perators

module and8(input logic [7:0] a,

output logic

y);

assign y = &a;

// &a is much easier to write than

Chapter 4 <5>

单击此S处y编s辑te母m版标V题e样r式ilog Modules

a b c

Verilog Module

y

Two types of Modules:

– Behavioral: describe what a module does – Structural: describe how it is built from simpler

i2cverilog代码

4'd5: sda_r <= db_r[2]; 4'd6: sda_r <= db_r[1]; 4'd7: sda_r <= db_r[0]; default:endcase//sda_r <= db_r[4'd7-num]; //送EEPROM地址(高bit开始)cstate <= ADD2;endend//else if(`SCL_POS) db_r <= {db_r[6:0],1'b0}; //器件地址左移1bitelsecstate <= ADD2;endACK2:beginif(/*!sda*/`SCL_NEG) begin//从机响应信号if(!sw1_r) begincstate <= DATA;//写操作db_r <= `WRITE_DATA; //写入的数据endelse if(!sw2_r) begindb_r <= `DEVICE_READ; //送器件地址(读操作)地址读需要执行该步骤以下操作cstate <= START2;//读操作endendelse cstate <= ACK2;//等待从机响应START2: begin //读操作起始位if(`SCL_LOW) beginsda_link <= 1'b1; //sda作为outputsda_r <= 1'b1;//拉高数据线sdacstate <= START2;endelse if(`SCL_HIG) begin //scl为高电平中间sda_r <= 1'b0;//拉低数据线sda,产生起始位信号cstate <= ADD3;endelse cstate <= START2; endADD3:begin//送读操作地址if(`SCL_LOW) beginif(num==4'd8) beginnum <= 4'd0;//num计数清零sda_r <= 1'b1;sda_link <= 1'b0;//sda置为高阻态(input)cstate <= ACK3; endelse beginnum <= num+1'b1; case (num)4'd0: sda_r <= db_r[7];4'd1: sda_r <= db_r[6]; 4'd2: sda_r <= db_r[5]; 4'd3: sda_r <= db_r[4]; 4'd4: sda_r <= db_r[3];4'd5: sda_r <= db_r[2]; 4'd6: sda_r <= db_r[1]; 4'd7: sda_r <= db_r[0]; default:endcase//sda_r <= db_r[4'd7-num]; //送EEPROM地址(高bit开始)cstate <= ADD3;endend//else if(`SCL_POS) db_r <= {db_r[6:0],1'b0}; //器件地址左移1bitelse cstate <= ADD3;endACK3:beginif(/*!sda*/`SCL_NEG) begincstate <= DATA;//从机响应信号sda_link <= 1'b0;endelse cstate <= ACK3;//等待从机响应endDATA:beginif(!sw2_r) begin//读操作if(num<=4'd7) begin cstate <= DATA;if(`SCL_HIG) beginnum <= num+1'b1; case (num)4'd0: read_data[7] <= sda;4'd1: read_data[6] <= sda; 4'd2: read_data[5] <= sda; 4'd3: read_data[4] <= sda; 4'd4: read_data[3] <= sda;4'd5: read_data[2] <= sda; 4'd6: read_data[1] <= sda; 4'd7: read_data[0] <= sda;default:endcase//read_data[4'd7-num] <= sda; // 读数据(高开始)end//elseif(`SCL_NEG)read_data<={read_data[6:0],read_data[7]}; //数据循环右移endelse if((`SCL_LOW) && (num==4'd8)) beginnum <= 4'd0;//num计数清零cstate <= ACK4;endelse cstate <= DATA;endelse if(!sw1_r) begin //写操作sda_link <= 1'b1;if(num<=4'd7) begin cstate <= DATA;if(`SCL_LOW) beginsda_link <= 1'b1;//数据线sda作为outputnum <= num+1'b1; case (num)4'd0: sda_r <= db_r[7]; 4'd1: sda_r <= db_r[6]; 4'd2: sda_r <= db_r[5]; 4'd3: sda_r <= db_r[4];4'd4: sda_r <= db_r[3]; 4'd5: sda_r <= db_r[2]; 4'd6: sda_r <= db_r[1]; 4'd7: sda_r <= db_r[0];default:endcase//sda_r <= db_r[4'd7-num]; //写入数据(高bit开始)end//else if(`SCL_POS) db_r <= {db_r[6:0],1'b0}; //写入数据左移1bitendelse if((`SCL_LOW) && (num==4'd8)) beginnum <= 4'd0;sda_r <= 1'b1;sda_link <= 1'b0;//sda置为高阻态cstate <= ACK4;endelse cstate <= DATA;endendACK4: beginif(/*!sda*/`SCL_NEG) begin //sda_r <= 1'b1; cstate <= STOP1; endelse cstate <= ACK4; endSTOP1:beginif(`SCL_LOW) beginsda_link <= 1'b1;sda_r <= 1'b0;cstate <= STOP1;endelse if(`SCL_HIG) begin sda_r <= 1'b1; //scl为高时,sda产生上升沿(结束信号)cstate <= STOP2;endelse cstate <= STOP1;endSTOP2:beginif(`SCL_LOW) sda_r <= 1'b1;else if(cnt_20ms==20'hffff0) cstate <= IDLE;else cstate <= STOP2;enddefault: cstate <= IDLE;endcaseendassign sda = sda_link ? sda_r:1'bz;assign dis_data = read_data;//---------------------------------------------endmodule写寄存器的标准流程为:1. Master发起START2. Master发送I2C addr(7bit)和w操作0(1bit),等待ACK3. Slave发送ACK4. Master发送reg addr(8bit),等待ACK5. Slave发送ACK6. Master发送data(8bit),即要写入寄存器中的数据,等待ACK7. Slave发送ACK8. 第6步和第7步可以重复多次,即顺序写多个寄存器9. Master发起STOP读寄存器的标准流程为:1. Master发送I2C addr(7bit)和w操作1(1bit),等待ACK2. Slave发送ACK3. Master发送reg addr(8bit),等待ACK4. Slave发送ACK5. Master发起START6. Master发送I2C addr(7bit)和r操作1(1bit),等待ACK7. Slave发送ACK8. Slave发送data(8bit),即寄存器里的值9. Master发送ACK10. 第8步和第9步可以重复多次,即顺序读多个寄存器原理整理清楚编程思路就有了,首先要有开始工作的信号,分读和写来驱动I2C,本设计用M2408这款芯片进行工作,主要是了解到datasheet中时序的要求来进行编写。

基于SystemVerilog的I 2C总线模块验证

Ke wo d s se e i g; I b s; g n rto y rs y tmv rl o z C u e eain; d v i re

随着 S C的快速发 展 , O 数字逻辑设 计复 杂度 随之提 高, 验证的难度也越来越大 。调查显示 , 1 有 / 2以上 的 S C O

b s p oo o si to u e u rtc li nr d c d. Afe h t te p p rfc s sO3t e d sg fte afi e e ao n rv n te v rf— trta , h a e o u e 1 h e i o farg n r tra d d ei h e i . n h i i

论述 了验证环境 中事务 产生器及 驱动 器的设计 。

关键词

Ss m ei g 2 yt vro ;1C总线 ;事务产生器 ;事务驱动 器 e l

T 47 N 0 文献标 识码 A 文章编号 10 7 2 (0 1 1 0 5—0 0 7— 80 2 1 )2— 3 3

中图分类号

Ve i c to fI Bu o lUsng S s e rf a i n o 2 i C s M de i y t mVe l g i ro

( 合肥 工业大学 电子科学与应用物理学 院 ,安徽 合 肥 2 00 ) 3 0 9

摘 要 针对 IC总线模块 ,介 绍了一种基 于 Ss m eig验证环境的验证 I 。 yt vro e l P设计。这种基 于面向对 象设计 的验

证架构可 以很容 易地被 重用。文 中分析 了基 于 Ss m ei g 证环境 的结 构,并在介 绍 Ic总线协议 的基础 上,重点 yt vro 验 e l

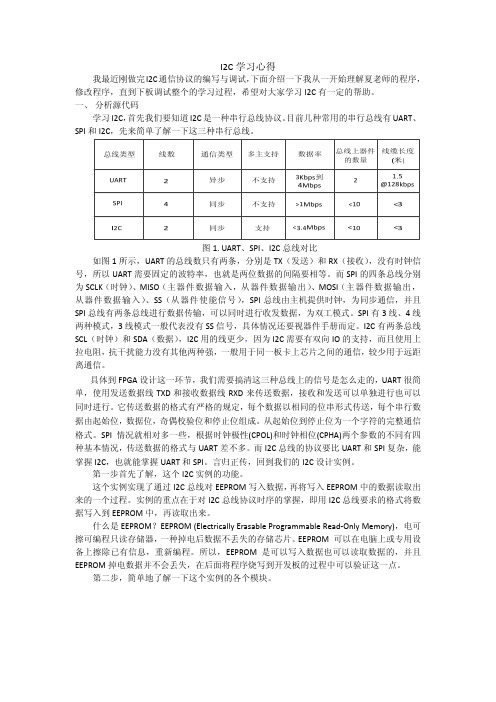

I2C verilog (非常详细的i2c学习心得)

图 4. AT24C02/4/8/16 字节写入帧格式

启 动 SDA线 S 1 0 1 0 X X X 应 答 应 S 1 0 答 1 0 X X X 应 答 非 P 应 答 控制字节 写 读 EEPROM存储单元 指定地址(n) 启 动 控制字节 数据(n) 停 止

( 1)总线非忙状态( A 段) :数据线 SDA 和 时钟线 SCL 都保持高电平。 ( 2)启动数据传输( B 段) :当时钟线( SCL)为高电平状态时,数据线( SDA)由 高电平变为低电平的下降沿被认为是 “ 启动 ”信号。只有出现 “ 启动 ”信号后,其它的命令 才有效。 ( 3)停止数据传输( C 段) :当时钟线( SCL)为高电平状态时,数据线( SDA)由 低电平变为高电平的上升沿被认为是 “ 停止 ”信号。随着 “停在 ” 信号出现,所有的外部操 作都结束。 ( 4)数据有效( D 段) :在出现 “启动 ”信号以后,在时钟线( SCL)为高电平状态时 数据线是稳定的,这时数据线的状态就要传送的数据。数据线( SDA )上的数据的改变 必须在时钟线为低电平期间完成, 每位数据占用一个时钟脉冲。 每个数传输都是由 “启动 ” 信号开始,结束于 “停止 ”信号。 ( 5)应答信号:每个正在接收数据的从机 EEPROM 在接到一个字节的数据后,通 常需要发出一个应答信号。而每个正在发送数据的 EEPROM 在发出一个字节的数据后, 通常需要接收一个应答信号。 EEPROM 读写控制器必须产生一个与这个应答位相联系的 额外的时钟脉冲。在 EEPROM 的读操作中, EEPROM 读写控制器对 EEPROM 完成的最 后一个字节产生一个高的应答位,这叫做非应答信号,随后给 EEPROM 一个结束信号。 第四步,理解各个模块的代码。 首先介绍核心模块——EEPROM_WR 模块,这个模块就干一件事,严格控制 SDA 与 SCL 总线上的信号, 使其满足 I2C 总线时序要求。 这里要用到状态机来控制 SDA 与 SCL 上的信号, 所以难点就在于对状态机的编写。因为 EP2C8‐2010 开发板采用的 EEPROM 是 AT24C02, 所以该状态机控制的 SCL 与 SDA 时序就要满足 AT24C02 的写入和读取格式。图 4、5 分别 是 AT24C02/4/8/16 字节写入帧格式和读指定地址存储单元的数据帧格式,简单分析一下字 节写入格式,如图 4 所示:第 1 位启动信号,接下来的第 2‐9 位是控制字节写入,其中 2‐5 位是固定的机器码 1010,6‐8 位是页地址,第 10 位是 EEPROM 给出的应答信号 0,第 11‐18 位是存储单元地址,19 位是 EEPROM 给出的应答信号 0,第 20‐27 位是写入的数据,28 位 应答信号,29 位停止信号。而 AT24C02/4/8/16 的字节读取格式也是大同小异,先写入控制 字和存储地址, 然后是启动信号与控制字节信号, 这时, 控制字节的第 8 位变为了 1 (读取) , 最后读取数据,并且在读取完毕后,主机将 SDA 拉高作为非应答信号。最后是停止位。 可能有人还是对这种字节写入与读取格式不明白, 其实这种格式是别人定好的, 我们所 需要的就是要让 SDA 与 SCL 的信号满足这种格式要求即可,下面我们来看夏老师的 EEPROM_WR 程序。

i2s的verilog代码

i2s的verilog代码i2s的Verilog代码是指用Verilog语言编写的用于实现i2s (Inter-IC Sound)接口功能的代码。

i2s接口是一种常用的音频数据传输接口,广泛应用于音频芯片、音频设备和数字信号处理器等领域。

i2s接口由三根线组成,分别是时钟线(SCLK)、数据线(SD)和帧同步线(WS)。

时钟线用于同步数据的传输,数据线用于传输音频数据,帧同步线用于标志数据的起始和结束。

在Verilog代码中,首先需要定义i2s接口的输入输出端口,并根据接口规范进行信号的定义和赋值。

接下来可以根据具体的应用需求,编写相应的模块和逻辑来实现i2s接口的功能。

一个简单的i2s接口的Verilog代码示例如下:```verilogmodule i2s_interface (input wire SCLK, // 时钟线input wire SD, // 数据线input wire WS, // 帧同步线output wire audio // 音频数据输出);reg [15:0] audio_data; // 音频数据寄存器always @(posedge SCLK) beginif (WS) beginaudio_data <= SD; // 读取音频数据endendassign audio = audio_data; // 输出音频数据endmodule```上述代码中,定义了一个名为i2s_interface的模块,该模块包含了一个i2s接口,输入端口为SCLK、SD和WS,输出端口为audio。

在always块中,通过检测时钟线的上升沿,判断帧同步线的状态,如果帧同步线为高电平,则将数据线的数据存入音频数据寄存器中。

最后,通过assign语句将音频数据输出到audio端口。

需要注意的是,上述代码仅为示例,实际的i2s接口实现可能需要根据具体的应用需求进行修改和优化。

此外,在实际应用中,还需要考虑时序约束、数据格式、时钟频率等因素,以确保i2s接口的正常工作。

eeprom_interface Verilog实现的简单程序(I2C总线接口)

eeprom_interface Verilog实现的简单程序(I2C总线接口)// i2c.vhd////这是是能从一个外部NUM(AT24C02A)读数据到一个256x8的外部SRAM块的I2C主接口程序,//当用于写NUM的外部逻辑寄存器存取时,SRAM就从外部源读数据并且把数据写到特定的I2C地址。

//----------------------------------------------------------------------////Copyright 2004 Actel corporation////----------------------------------------------------------------------//// Version 1.2 06/04/04 J.Vorgert - working file////---------------------------------------------------------------------- `timescale 1ns / 1psmodule i2c (Reset_n, CLK, INIT, IENB, IADDR, IDATA, ICLK, UPDT, UENB, UADDR, UDATA, SDI, SDO, SCK);input Reset_n; /* active low reset */input CLK ; /* processor clock */output INIT ; /* high during init */output IENB ; /* low to enable write */output [7:0] IADDR ; /* init address */output [7:0] IDATA ; /* init data */output ICLK ; /* init clock */input UPDT ; /* high to trigger mirror image update */output UENB ; /* low to enable fifo */input [7:0] UADDR; /* write address */input [7:0] UDATA; /* write data */input SDI ; /* serial input */output SDO ; /* active low open-drain drive enable - data */output SCK ; /* active low open-drain drive enable - clock */reg IENB;reg INIT;reg UENB;reg BTCK;wire STEN; reg [3:0] CSTATE; reg [3:0] BCNT ; reg [7:0] CCNT ; reg DLY ;reg D2 ;wire D2I;wire NKI ;reg NACK ;wire WRI ;wire RDI ;reg [8:0] BYTE ; reg [8:0] SDATA ; wire LD_BYTE ;reg STSP ;wire CTL_VAL ;always @ (posedge CLK or negedge Reset_n)begin if(Reset_n == 1'b0) BTCK else BTCK // reaches state 0101.always @ (negedge Reset_n or posedge CLK)begin if(Reset_n == 1'b0) INIT else if(CSTATE == 4'b0101) INIT end// This state machine is set-up to read/write data to an AT24C02A // serial Flash memory//这个状态机是建立AT24C02A串行闪存串行闪存的数据读写// At power-up, the INIT bit is set, and the state machine executes// a 'sequencial read' operation starting at address 0x000 and // procedding until all 256 bytes have been read and forwarded into // the internal memory block. The state machine then sends a// stop bit to the Flash and clears the INIT control bit.////在上电上电时,INIT被设置为高,状态机从地址0x000开始执行“连续读”操作,//一直进行下去直到所有的256字节都被读,然后向前到内部存储区,//状态机然后给FLASH发送一个停止位并且清除INIT控制位。

I_2C总线串行数据接口的Verilog实现

邮局订阅号:82-946360元/年技术创新嵌入式网络技术应用《PLC技术应用200例》您的论文得到两院院士关注I2C总线串行数据接口的Verilog实现TheVerilogachievementofI2CSerialBusadapter(华南理工大学)林健磊殷瑞祥LINJIANLEIYINRUIXIANG摘要:本文介绍了I2C总线规范,并根据该规范对I2C进行模块化设计,用VerilogHDL语言对每个模块进行具体描述,并通过模块之间的调用,基本实现了I2C的主机从机的发送和接收功能。

关键词:I2C总线;VerilogHDL;模块化设计中图分类号:TN87文献标识码:BAbstract:ThispaperintroducesthestandardofI2CBus,carrysouttheI2Cmodulardesignaccordingtothisstandard,givesthespe-cificdescriptionofeverymoduleinVerilogHDL,bycallingbetweenmodules,achievesthesendingandreceivingfunctionsofI2CMaster/SlaveMachinebasically.Keyword:I2Cbus,VerilogHDL,Modulardesign文章编号:1008-0570(2007)08-2-0043-021引言I2C(Inter-IntegratedCircuit)是由Philip开发的一种简单的双向两线总线。

I2C只要求两条总线路:串行数据线SDA和串行时钟线SCL,来实现有效的IC之间的控制,而且使硬件效益最大而电路最简单。

同时,通过一个CPU的接口来和片上的总线进行数据交换,可以实现对控制寄存器和数据寄存器的读写。

2I2C总线的工作原理2.1.基本结构总线的串行数据(SDA)和串行时钟(SCL)线,在连接到总线的器件间传递信息。

i平方c总线的工作原理

i平方c总线的工作原理I²C总线是一种常用的串行通信协议,广泛应用于各种电子设备中。

它的工作原理基于两根线路:SDA(串行数据线)和SCL(串行时钟线),通过这两根线路实现设备之间的通信。

I²C总线是由飞利浦公司(现在的恩智浦半导体)在上世纪80年代初推出的,用于连接微控制器和外围设备。

它的设计初衷是为了解决多个设备之间通信的问题,可以同时连接多个设备,每个设备都有一个唯一的地址,通过地址来区分不同的设备。

I²C总线采用了主从结构,主设备负责发起通信,从设备负责响应通信。

主设备通过发送起始信号来启动通信,然后按照一定的时序发送或接收数据。

从设备在接收到起始信号后,根据主设备发送的地址决定是否响应通信。

如果地址匹配,从设备会返回一个应答信号,然后主设备就可以发送或接收数据了。

在I²C总线中,数据的传输是基于时钟信号的。

SCL线由主设备控制,通过产生一系列的时钟脉冲来同步数据的传输。

数据线SDA上的数据在每个时钟脉冲的上升沿或下降沿进行传输,由主设备或从设备控制。

主设备在时钟脉冲上升沿将数据线上的数据采样,而从设备在时钟脉冲下降沿将数据线上的数据输出。

为了保证数据的可靠传输,I²C总线规定了一些时序参数。

时钟频率是其中一个重要参数,它决定了数据传输的速度。

常见的时钟频率有100kHz和400kHz,也有更高的频率。

时钟频率越高,数据传输速度越快,但也会增加传输的误差。

I²C总线还定义了起始信号和停止信号。

起始信号由主设备产生,表示通信开始。

停止信号也由主设备产生,表示通信结束。

起始信号和停止信号的产生都是通过控制SDA线上的电平变化来实现的。

总的来说,I²C总线的工作原理是通过主设备产生起始信号,然后按照一定的时序发送或接收数据,最后由主设备产生停止信号来完成通信。

通过SDA线和SCL线的协作,实现了设备之间的串行通信。

这种通信方式简单灵活,并且可以同时连接多个设备,因此在很多电子设备中得到了广泛应用。

i2c顶层inout 的处理verilog代码

i2c顶层inout 的处理verilog代码什么是I2C 协议?I2C(Inter-Integrated Circuit)是一种串行通信协议,用于在微控制器、传感器、显示屏、存储器和其他外设之间进行数字数据传输。

它于1982年由Philips(现在的NXP半导体)开发,并在全球范围内广泛应用。

I2C 协议中的顶层inout 接口在设计I2C 通信系统时,顶层inout 接口起着核心作用。

I2C 协议中有两条主要的线路,即数据线(SDA)和时钟线(SCL)。

顶层inout 接口是将这两条线路连接到外部设备的关键。

常见的I2C 顶层inout 接口处理方法有几种,下面将逐步介绍这些方法。

第一种方法:Tri-State Buffer(三态缓冲器)Tri-State Buffer 是一种常用的I2C 顶层inout 接口处理方法。

它通过控制一个使能信号来决定输入输出的状态。

当使能信号有效时,内部数据将根据输入信号确定输出;当使能信号无效时,输出则处于高阻态(Hi-Z)。

使用Tri-State Buffer 的I2C 顶层inout 接口处理方法如下:verilogmodule i2c_top (inout wire sda,inout wire scl,input wire enable);TriStateBuffer #(.WIDTH(1)) tri_sda (.i(sda), .o(sda_s), .oe(enable)); TriStateBuffer #(.WIDTH(1)) tri_scl (.i(scl), .o(scl_s), .oe(enable));endmodule在上述代码中,`sda` 和`scl` 是输入输出的I2C 数据线和时钟线,`enable` 是使能输入信号。

通过Tri-State Buffer 控制使能信号,即可实现对I2C 顶层inout 接口的处理。

第二种方法:Assign 语句除了使用Tri-State Buffer,还可以使用Assign 语句来处理I2C 顶层inout 接口。

verilog hdl数字集成电路设计与原理(一)

verilog hdl数字集成电路设计与原理(一)Verilog HDL数字集成电路设计与原理1. 引言•Verilog HDL是一种硬件描述语言,用于描述数字集成电路的行为和结构。

•本文将从基础开始,详细介绍Verilog HDL的设计与原理。

2. Verilog HDL基础知识•Verilog HDL是一种高级硬件描述语言,它允许我们使用模块化的方式来描述数字集成电路。

•通过Verilog HDL,我们可以描述电路的输入、输出以及内部逻辑。

•Verilog HDL使用模块化的形式,将电路划分为多个模块,每个模块负责完成特定的功能。

3. Verilog HDL模块•在Verilog HDL中,一个模块可以包含多个输入端口和输出端口。

•输入端口用于接收外部信号,输出端口用于输出内部计算结果。

•通过模块之间的互连,可以构建出复杂的电路结构。

4. Verilog HDL信号•在Verilog HDL中,信号是电路中的基本元素,可以是任何数据类型。

•信号可以通过赋值语句进行操作,例如逻辑运算、赋值操作等。

•信号的值可以在时钟的上升沿或下降沿进行更新。

5. Verilog HDL运算符•Verilog HDL提供了各种运算符,用于实现数字集成电路的运算功能。

•运算符包括逻辑运算符、位运算符、算术运算符等。

•运算符的选择和使用需要根据电路的需求进行灵活调整。

6. Verilog HDL过程•在Verilog HDL中,过程用于描述电路的行为和时序逻辑。

•过程包括组合逻辑过程和时序逻辑过程。

•组合逻辑过程是对输入进行组合运算得到输出,时序逻辑过程则需要考虑时钟和状态的变化。

7. Verilog HDL测试与调试•在实际设计中,测试与调试是非常重要的环节。

•可以通过自动生成测试向量、仿真、波形查看等方式进行测试与调试。

•通过不断优化和调试,可以确保电路设计的正确性和可靠性。

8. 总结•Verilog HDL是数字集成电路设计与原理中的重要工具和技术。

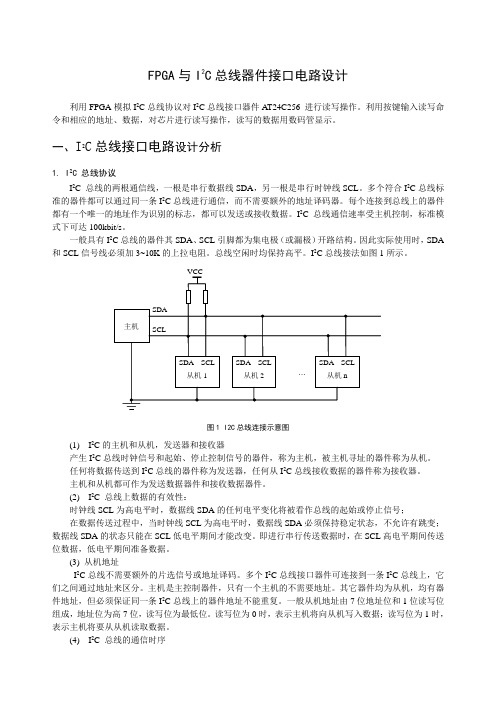

I2C总线接口电路设计

FPGA与I2C总线器件接口电路设计利用FPGA模拟I2C总线协议对I2C总线接口器件AT24C256 进行读写操作。

利用按键输入读写命令和相应的地址、数据,对芯片进行读写操作,读写的数据用数码管显示。

一、I2C总线接口电路设计分析1. I2C 总线协议I2C 总线的两根通信线,一根是串行数据线SDA,另一根是串行时钟线SCL。

多个符合I2C总线标准的器件都可以通过同一条I2C总线进行通信,而不需要额外的地址译码器。

每个连接到总线上的器件都有一个唯一的地址作为识别的标志,都可以发送或接收数据。

I2C 总线通信速率受主机控制,标准模式下可达100kbit/s。

一般具有I2C总线的器件其SDA、SCL引脚都为集电极(或漏极)开路结构。

因此实际使用时,SDA 和SCL信号线必须加3~10K的上拉电阻。

总线空闲时均保持高平。

I2C总线接法如图1所示。

图1 I2C总线连接示意图(1) I2C的主机和从机,发送器和接收器产生I2C总线时钟信号和起始、停止控制信号的器件,称为主机,被主机寻址的器件称为从机。

任何将数据传送到I2C总线的器件称为发送器,任何从I2C总线接收数据的器件称为接收器。

主机和从机都可作为发送数据器件和接收数据器件。

(2) I2C 总线上数据的有效性:时钟线SCL为高电平时,数据线SDA的任何电平变化将被看作总线的起始或停止信号;在数据传送过程中,当时钟线SCL为高电平时,数据线SDA必须保持稳定状态,不允许有跳变;数据线SDA的状态只能在SCL低电平期间才能改变。

即进行串行传送数据时,在SCL高电平期间传送位数据,低电平期间准备数据。

(3) 从机地址I2C总线不需要额外的片选信号或地址译码。

多个I2C总线接口器件可连接到一条I2C总线上,它们之间通过地址来区分。

主机是主控制器件,只有一个主机的不需要地址。

其它器件均为从机,均有器件地址,但必须保证同一条I2C总线上的器件地址不能重复。

一般从机地址由7位地址位和1位读写位组成,地址位为高7位,读写位为最低位。

verilog iic 读写

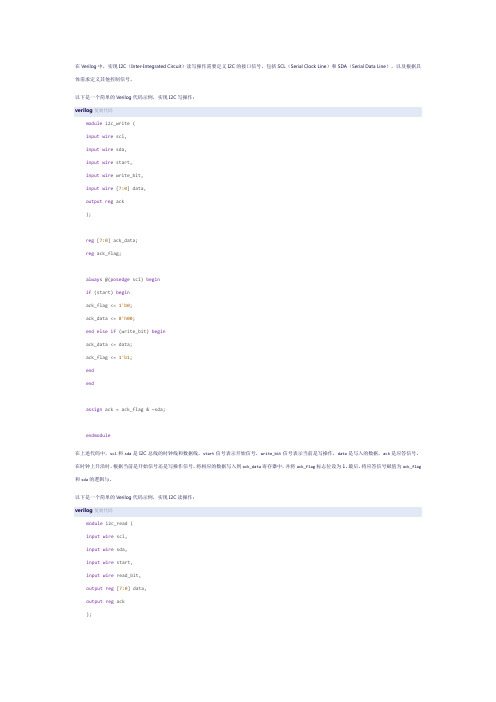

在Verilog中,实现I2C(Inter-Integrated Circuit)读写操作需要定义I2C的接口信号,包括SCL(Serial Clock Line)和SDA(Serial Data Line),以及根据具体需求定义其他控制信号。

以下是一个简单的Verilog代码示例,实现I2C写操作:verilog复制代码module i2c_write (input wire scl,input wire sda,input wire start,input wire write_bit,input wire [7:0] data,output reg ack);reg [7:0] ack_data;reg ack_flag;always @(posedge scl) beginif (start) beginack_flag <= 1'b0;ack_data <= 8'h00;end else if (write_bit) beginack_data <= data;ack_flag <= 1'b1;endendassign ack = ack_flag & ~sda;endmodule在上述代码中,scl和sda是I2C总线的时钟线和数据线,start信号表示开始信号,write_bit信号表示当前是写操作,data是写入的数据,ack是应答信号。

在时钟上升沿时,根据当前是开始信号还是写操作信号,将相应的数据写入到ack_data寄存器中,并将ack_flag标志位设为1。

最后,将应答信号赋值为ack_flag 和sda的逻辑与。

以下是一个简单的Verilog代码示例,实现I2C读操作:verilog复制代码module i2c_read (input wire scl,input wire sda,input wire start,input wire read_bit,output reg [7:0] data,output reg ack);reg [7:0] ack_data;reg ack_flag;reg read_data;always @(posedge scl) beginif (start) beginack_flag <= 1'b0;ack_data <= 8'h00;end else if (read_bit) beginack_data <= sda;ack_flag <= 1'b1;end else if (!sda) begin// 读取数据时,sda为低电平read_data <= ack_data; // 读取数据到read_data寄存器中endendassign ack = ack_flag & ~sda; // 应答信号为ack_flag和sda的逻辑与取反值assign data = read_data; // 将读取的数据输出到data信号上endmodule在上述代码中,读操作的过程与写操作类似,只是在读取数据时,需要将sda信号拉低,并在时钟上升沿时将读取的数据存储到read_data寄存器中。

第9章verilog_HDL_程序设计PPT课件

reg[12:0] temp2; reg[11:0] temp3; reg[10:0] temp4;

reg[9:0] temp5; reg[8:0] temp6;

reg[7:0] temp7;

function[7:0] mult8x1;

//该函数实现8×1乘法

input[7:0] operand; input sel;

temp5<=((mult8x1(a,b[2]))<<2);temp4<=((mult8x1(a,b[3]))<<3);

temp3<=((mult8x1(a,b[4]))<<4);temp2<=((mult8x1(a,b[5]))<<5);

temp1<=((mult8x1(a,b[6]))<<6);temp0<=((mult8x1(a,b[7]))<<7);

module count7(reset,clk,cout);

input clk,reset; output wire cout;

reg[2:0] m,n; reg cout1,cout2;

assign cout=cout1|cout2;

//两个计数器的输出相或

always @(posedge clk)

endmodule

(4)查找表乘法器

查找表乘法器将乘积直接存放在存储器中,将操作数 (乘数和被乘数)作为地址访问存储器,得到的输出 数据就是乘法运算的结果。

查找表方式的乘法器速度只局限于所使用存储器的存 取速度。但由于查找表规模随操作数位数增加而迅速 增大,因此如用于实现位数宽的乘法操作,需要 FPGA器件具有较大的片内存储器模块。比如,要实 现8×8乘法,要求存储器的地址位宽为16位,字长 为16位,即存储器大小为1M比特。