CC1808JKNPOEBN100中文资料

BJ100白酒输送计算机

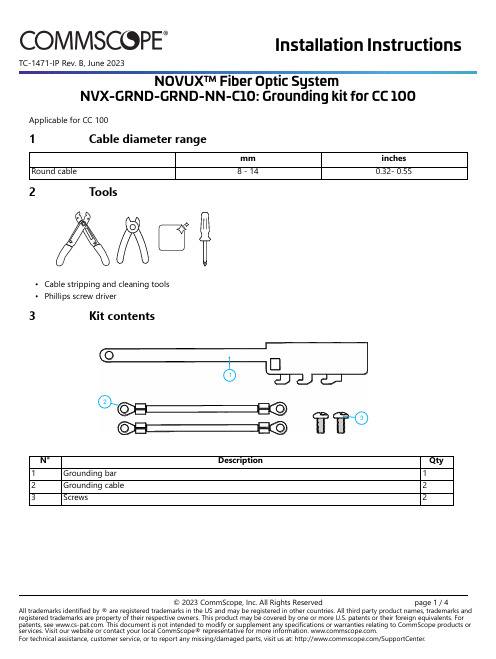

BJ100白酒输送计算机用户手册邯郸市金帆自动化控制技术有限公司目录1. 简介 (1)2. 结构及组成 (1)3. 各键功能简介 (2)4. 设备安装 (4)5. 注意事项 (5)6. GJ100白酒输送计算机计量控制实例 (5)7. 密码设置 (9)8. 精度校验 (9)9. 切换 (11)10.各工具键的用法实例 (11)11.常见计量误差产生的原因及排除方法 (16)一、简介:我公司在充分调研了白酒行业计量现状的基础上,研发了全新一代BJ100白酒输送计算机,该机主要由两部分组成。

第一是主计算机,它是整个系统的“大脑”,除了对白酒进行重量计量和控制输送泵运行外,在它的版面上还集成了白酒行业最新的数据资料及计算工具。

第二是信息采集计算机,它的作用是动态的实时的将采集到的信息传输给主计算机,最终由主计算机显示计量结果。

其特点如下:1、功能齐全:BJ100白酒输送计算机即是一台控制器又是一台计算器,在它上面集成有八个基本工具(文字表示)和四个高级工具(图形表示)它几乎能完成目前白酒行业的所有计算任务及数据查询。

2、高可靠性:强、弱电分离主电路版优化设计并由直流模块电源供电,有极强的抗干扰能力。

3、智能化:主计算机实时监测外部电源状况,当出现故障突然停电时,主计算机会及时将运行数据保存下来以便查询。

同时主计算机还会对当前任务的完成情况,做出判断并提示操作人员注意。

4、易操作:主计算机各键功能均由中文提示使您操作下来更加简单。

二、结构及组成:BJ100白酒输送计算机由主计算机,信息采集计算机、流量传感器、温度传感器、导线等组成。

三、各键功能简介:1、控制按键:1.1、:控制BJ100白酒输送计算机的上电与断电。

1.2、:设定输送白酒的酒度。

1.3、:主计算机上电后默认为自动感温模式,操作人员不必设定温度值,计算机自动检测物料的温度,并对计量结果实时温度补偿,当温度传感器出现故障时,您可将自动感温模式切换为温度设定模式,以支持您的工作,这时您就可手动输入温度值。

C100__操作说明中文版__说明书

Model C100SmartBob Console操作说明安装和操作之前请仔细阅读.Division of Garner Industries7201 North 98th StreetLincoln, NE 685079741(402) 4349102目录安全摘要 (3)1.0介绍 (4)2.0 说明 (4)3.0 安装 (6)ٛ 3.1 安装 (6)ٛ 3.2 连接与接线........................................................................................................... .. (7)3.3 RS485 网络要求................................................................................................. .. (11)ٛ 3.4 防雷法/过载保护............................................................. ................................... .. (12)ٛ 3.5 布线图...................................................................................................... ... ... ... (13)4.0 操作. ... ... .. (14)ٛ 4.1 按键 (14)ٛ 4.2 菜单系统 (14)5.0 固件更新 (21)ٛ 5.1 更新要求....... ....... ....... . (21)ٛ 5.2 Atmel’s FLIP的下载与安装和JAVA运行环境 (21)ٛ 5.3 更新过程 (22)6.0 质保和服务 (23)ٛ 6.1 有限保修 (23)ٛ 6.2 技术支持,客户服务和修理r (23)7.0处理 (23)安全摘要为避免受伤和损坏设备,请看以下安全防护措施.产品必须由有资格的权威的个人来安装维护、.根据安装说明书来安装,且要符合所有国家和当地的有关规定.应用中用的电线是有额定电压和电流来额定的.在正常运行中要确保外壳盖子是紧紧牢固的盖着的.在潮湿的环境中要确保所有电气入口密封良好.如果该产品在某种程度上不是用在生产商指定的,那安全保护可能被损害.安全术语和标志警告:警告是鉴别会导致受伤和危及生命的情况发生,电击危险.小心: 小心是指示会导致产品或其它财产的损坏的情况发生.FCC 承诺注意: 本产品经过测试符合FCC规定第15部分中A级数码产品要求.符合这些要求的产品在商业环境下进行操作时能够提供合理防护并防止有害干扰.本设备产生,使用并发射无线电波,如果不按照使用手册进行安装或使用,可能对无线通讯造成干扰.在居民区使用本设备可能会造成有害的干扰在此情况下,用户需要自费排除干。

JMT1808R 微控制器用户手册说明书

JMT1808R MCU用户手册江苏宏云技术有限公司*************Dec. 2016 V1.12微控制器JMT1808R 1产品概述 (20)1.1功能描述 (20)1.2主要特性 (20)1.3框图 (22)1.4应用范围 (22)1.5引脚配置 (23)1.5.1 LQFP48L引脚图 (23)1.5.2 LQFP32L引脚图 (24)1.5.3 QFN32L引脚图 (25)1.5.4 TSSOP28L引脚图 (26)1.5.5 引脚说明 (27)2电源管理(PMU) (30)2.1概述 (30)2.2低功耗控制 (30)2.2.1 降低系统时钟频率 (31)2.2.2 外设时钟门控 (32)2.2.3 关闭模拟模块 (32)2.2.4 四种低功耗模式 (32)2.2.5 OSC开关说明 (34)2.3寄存器 (34)2.3.1 低功耗控制寄存器(PMUCTR) [0xA1] (35)3时钟复位管理(CRM) (36)3.1时钟管理 (36)3.1.1 概述 (36)3.1.2 框图 (36)3.1.3 功能描述 (37)3.1.4 寄存器描述 (42)3.2复位管理 (52)3.2.1 概述 (52)3.2.2 框图 (53)3.2.3 功能描述 (53)3.2.4 寄存器 (56)1微控制器JMT1808R4JMT51 MCU核 (61)4.1概述 (61)4.2指令集 (61)5JMT018 DSP核 (67)5.1概述 (67)5.1.1 框图 (67)5.1.2 系统总线 (67)5.1.3 运算单元(ALU) (68)5.1.4 乘累加单元(MAC) (68)5.1.5 除法单元(DIV) (68)5.1.6 硬件循环(HW loop) (69)5.1.7 数据传输 (69)5.1.8 存储单元 (69)5.2指令集 (69)5.2.1 数据传输指令 (69)5.2.2 算术运算指令 (71)5.2.3 移位运算指令 (72)5.2.4 逻辑运算指令 (73)5.2.5 乘法运算指令 (73)5.2.6 并行运算指令 (74)5.2.7 程序控制指令 (77)5.3数据运算器 (78)5.3.1 通用寄存器 (78)5.3.2 累加器A (79)5.3.3 乘法 (83)5.3.4 乘加运算 (84)5.3.5 加减运算 (86)5.3.6 移位运算 (86)5.3.7 四舍五入方法 (87)5.4DSP存储空间 (87)5.4.1 数据存储空间 (87)5.4.2 程序存储空间 (88)5.5DSP工作配置 (89)2微控制器JMT1808R 5.6DSP代码生成与下载 (89)5.6.1 DSP代码生成 (89)5.6.2 DSP代码下载 (89)5.7DSP内部寄存器 (90)5.7.1 DSP通用寄存器R0 (90)5.7.2 DSP通用寄存器R1 (91)5.7.3 DSP通用寄存器R2 (91)5.7.4 DSP通用寄存器R3 (91)5.7.5 DSP通用寄存器R4 (91)5.7.6 DSP通用寄存器R5 (91)5.7.7 DSP通用寄存器R6 (91)5.7.8 DSP通用寄存器R7 (91)5.7.9 X数据空间指针寄存器DP0 (92)5.7.10 Y数据空间指针寄存器DP1 (92)5.7.11 DSP程序地址指针寄存器PC (92)5.7.12 乘法及乘加结果寄存器A (92)5.7.13 LINK寄存器 (92)5.7.14 状态寄存器PSR (92)5.7.15 模式寄存器PMR (93)5.7.16 硬件循环次数寄存器LOOP (93)5.7.17 硬件循环指令个数寄存器LIR (94)5.8JMT51访问DSP寄存器 (94)5.8.1 DSP配置寄存器(DSP_CFG) [0xD4] (95)5.8.2 DSP运行状态寄存器(DSP_STA) [0xD1] (95)5.8.3 PC寄存器低字节(DSP_PCL) [0xD2] (96)5.8.4 PC寄存器高字节(DSP_PCH) [0xD3] (96)5.8.5 R0寄存器低字节(DSP_R0L) [0xD9] (96)5.8.6 R0寄存器高字节(DSP_R0H) [0xDA] (96)5.8.7 R1寄存器低字节(DSP_R1L) [0xDB] (96)5.8.8 R1寄存器高字节(DSP_R1H) [0xDC] (97)5.8.9 R2寄存器低字节(DSP_R2L) [0xDD] (97)5.8.10 R2寄存器高字节(DSP_R2H) [0xDE] (97)5.8.11 R3寄存器低字节(DSP_R3L) [0xDF] (97)5.8.12 R3寄存器高字节(DSP_R3H) [0xE1] (97)5.8.13 R4寄存器低字节(DSP_R4L) [0xE2] (97)3微控制器JMT1808R45.8.14 R4寄存器高字节(DSP_R4H) [0xE3] (97)5.8.15 R5寄存器低字节(DSP_R5L) [0xE4] (98)5.8.16 R5寄存器高字节(DSP_R5H) [0xE5] (98)5.8.17 R6寄存器低字节(DSP_R6L) [0xE6] (98)5.8.18 R6寄存器高字节(DSP_R6H) [0xE7] (98)5.8.19 R7寄存器低字节(DSP_R7L) [0xE9] (98)5.8.20 R7寄存器高字节(DSP_R7H) [0xEA] (98)5.8.21 DP0寄存器低字节(DSP_DP0L) [0xEB] (98)5.8.22 DP0寄存器高字节(DSP_DP0H) [0xEC] (99)5.8.23 DP1寄存器低字节(DSP_DP1L) [0xED] (99)5.8.24 DP1寄存器高字节(DSP_DP1H) [0xEE] (99)5.8.25 A寄存器7~0比特(DSP_A0L) [0xEF] (99)5.8.26 A寄存器15~8比特(DSP_A0H) [0xF1] (99)5.8.27 A寄存器23~16比特(DSP_A1L) [0xF2] (99)5.8.28 A寄存器31~24比特(DSP_A1H) [0xF3] (99)5.8.29 A寄存器39~32比特(DSP_A2) [0xF4] (100)5.8.30 LNKR寄存器低字节(DSP_LNKRL) [0xF5] (100)5.8.31 LNKR寄存器高字节(DSP_LNKRH) [0xF6] (100)5.8.32 PSR寄存器低字节(DSP_PSRL) [0xF7] (100)5.8.33 PSR寄存器高字节(DSP_PSRH) [0xF9] (101)5.8.34 PMR寄存器低字节(DSP_PMRL) [0xFA] (101)5.8.35 PMR寄存器高字节(DSP_PMRH) [0xFB] (101)5.8.36 LOOP寄存器低字节(DSP_LOOPL) [0xFC] (101)5.8.37 LOOP寄存器高字节(DSP_LOOPH) [0xFD] (101)5.8.38 LIR寄存器低字节(DSP_LIRL) [0xFE] (102)5.8.39 LIR寄存器高字节(DSP_LIRH) [0xFF] (102)6中断 (103)6.1概述 (103)6.2外部中断(INT0/INT1) (105)6.3中断优先级 (105)6.4中断处理过程 (106)6.5中断响应时间 (106)6.6中断寄存器 (107)微控制器JMT1808R6.6.1 中断使能寄存器0(IEN0) [0xA8] (107)6.6.2 中断使能寄存器1(IEN1) [0xB8] (108)6.6.3 中断使能寄存器2 (IEN2) [0xC0] (109)6.6.4 中断优先级寄存器0 (IP0) [0xB9] (109)6.6.5 中断优先级寄存器1(IP1) [0xBA] (110)6.6.6 中断优先级寄存器2(IP2) [0xBB] (111)7存储器 (112)7.1JMT51存储器 (112)7.1.1 程序存储器 (112)7.1.2 外部数据存储器 (113)7.1.3 内部数据存储器 (113)7.1.4 特殊功能寄存器 (115)7.2JMT018存储器 (120)7.3存储器访问冲突说明 (121)7.4JMT51核寄存器 (122)7.4.1 ACC寄存器(A) [0xE0] (122)7.4.2 B寄存器(B) [0xF0] (122)7.4.3 堆栈指针(SP) [0x81] (122)7.4.4 程序状态字寄存器(PSW) [0xD0] (123)7.4.5 数据指针低字节(DPL) [0x82] (124)7.4.6 数据指针高字节(DPH) [0x83] (124)7.4.7 MOVX指令设置寄存器(MOVXCON) [0x86] (124)7.5P AGE堆栈寄存器 (125)7.5.1 SFR PAGE寄存器(SFRPAGE) [0x84] (125)7.5.2 PAGE堆栈使能寄存器(SFRPGEN) [0x85] (126)7.5.3 PAGE堆栈寄存器0(PGSTACK0) [0x91] (126)7.5.4 PAGE堆栈寄存器1(PGSTACK1) [0x92] (126)7.5.5 PAGE堆栈寄存器2(PGSTACK2) [0x93] (126)7.5.6 PAGE堆栈寄存器3(PGSTACK3) [0x94] (127)8Flash存储器 (128)8.1概述 (128)8.2FLASH操作 (128)8.2.1 FLASH数据读取 (128)5微控制器JMT1808R68.2.2 FLASH扇区擦除 (129)8.2.3 FLASH编程 (129)8.3FLASH寄存器 (130)8.3.1 FLASH控制寄存器(FLSC) [0xF9] (130)8.3.2 FLASH关键字寄存器(FLSK) [0xFA] (130)9看门狗定时器(WDT) (131)9.1概述 (131)9.2功能描述 (131)9.3寄存器 (131)9.3.1 看门狗分频系数寄存器(WDTCKDIV) [0xD9] (131)9.3.2 看门狗比较值寄存器(WDTINT) [0xDA] (132)9.3.3 看门狗中断标志寄存器(WDTINTF) [0xDB] (132)9.3.4 看门狗喂狗寄存器(WDTLD) [0xDC] (133)9.3.5 看门狗启停寄存器(WDTST) [0xDD] (133)10实时时钟(RTC) (134)10.1概述 (134)10.2实时时钟 (134)10.3闹钟 (136)10.4RTC时钟调校 (136)10.5实时时钟寄存器更新 (137)10.6实时时钟寄存器读取 (137)10.7RTC中断 (137)10.8RTC寄存器 (138)10.8.1 RTC控制寄存器0(RTCCON0) [0xA9] (138)10.8.2 RTC控制寄存器1(RTCCON1) [0xAA] (139)10.8.3 RTC时标控制寄存器(RTCTMC) [0xAB] (140)10.8.4 RTC秒寄存器(RTCSEC) [0xAC] (140)10.8.5 RTC分钟寄存器(RTCMIN) [0xAD] (141)10.8.6 RTC小时寄存器(RTCHOUR) [0xAE] (141)10.8.7 RTC星期寄存器(RTCWEEK) [0xAF] (141)10.8.8 RTC日寄存器(RTCDAY) [0xB1] (141)10.8.9 RTC月寄存器(RTCMON) [0xB2] (141)微控制器JMT1808R10.8.10 RTC年寄存器(RTCYEAR) [0xB3] (142)10.8.11 闹钟0秒寄存器(AL0SEC) [0xB4] (142)10.8.12 闹钟0分钟寄存器(AL0MIN) [0xB5] (142)10.8.13 闹钟0小时寄存器(AL0HOUR) [0xB6] (142)10.8.14 闹钟0星期寄存器(AL0WEEKS) [0xB7] (142)10.8.15 闹钟1分钟寄存器(AL1MIN) [0xB9] (143)10.8.16 闹钟1小时寄存器(AL1HOUR) [0xBA] (143)10.8.17 闹钟1日寄存器(AL1DAY) [0xBB] (143)10.8.18 闹钟1月寄存器(AL1MON) [0xBC] (144)10.8.19 RTC时钟调校寄存器0(RTCADJ0) [0xBD] (144)10.8.20 RTC时钟调校寄存器1(RTCADJ1) [0xBE] (144)10.8.21 RTC中断使能寄存器(RTCIE) [0xBF] (144)10.8.22 RTC中断标志寄存器(RTCIF) [0xC7] (145)11定时器/计数器(TIMER) (146)11.1概述 (146)11.2TIMER管脚配置 (146)11.3Timer0工作模式 (146)11.3.1 模式0(13位定时器/计数器) (146)11.3.2 模式1(16位定时器/计数器) (147)11.3.3 模式2(8位自动重装定时器/计数器) (147)11.3.4 模式3(两个8比特定时器) (148)11.4Timer1工作模式 (149)11.4.1 模式0(13位定时器/计数器) (149)11.4.2 模式1(16位定时器/计数器) (149)11.4.3 模式2(8位自动重装定时器/计数器) (150)11.5Timer2工作模式 (150)11.5.1 模式0(13位定时器/计数器) (150)11.5.2 模式1(16位定时器/计数器) (151)11.5.3 模式2(16位自动重装定时器/计数器) (151)11.5.4 模式3(1个8比特定时器/计数器) (152)11.6TIMER寄存器 (152)11.6.1 Timer0/1控制寄存器(TCON) [0x88] (153)11.6.2 Timer0/1模式寄存器(TMOD) [0x89] (154)7微控制器JMT1808R811.6.3 Timer0低8位(TL0) [0x8A] (155)11.6.4 Timer1低8位(TL1) [0x8B] (155)11.6.5 Timer0高8位(TH0) [0x8C] (155)11.6.6 Timer1高8位(TH1) [0x8D] (155)11.6.7 Timer0/1预分频控制器(TPSC) [0x8E] (155)11.6.8 Timer2控制寄存器(T2CON) [0xD1] (156)11.6.9 Timer2重载寄存器低8位(RL2) [0xD2] (156)11.6.10 Timer2重载寄存器高8位(RH2) [0xD3] (156)11.6.11 Timer2低8位(TL2) [0xD4] (157)11.6.12 Timer2高8位(TH2) [0xD5] (157)11.6.13 Timer2预分频控制器(T2PSC) [0xD6] (157)12高级定时器(PWM) (158)12.1概述 (158)12.2特性 (158)12.3框图 (160)12.4输入输出引脚配置 (160)12.5功能描述 (160)12.5.1 计数器 (161)12.5.2 输入捕获功能 (173)12.5.3 从模式控制 (175)12.5.4 输出比较功能 (181)12.5.5 主模式控制 (207)12.5.6 中断 (209)12.5.7 高级定时器同步 (211)12.6寄存器描述 (216)12.6.1 TIMx控制寄存器0 (TIMx_CONR0) [TIM0:0xBB/TIM1:0xFB] (221)12.6.2 TIMx控制寄存器1 (TIMx_CONR1) [TIM0:0x89/TIM1:0xC9] (223)12.6.3 TIMx控制寄存器2 (TIMx_CONR2) [TIM0:0x8A/TIM1:0xCA] (224)12.6.4 TIMx控制寄存器3 (TIMx_CONR3) [TIM0:0x8B/TIM1:0xCB] (225)12.6.5 TIMx从模式控制寄存器0 (TIMx_TGICR0) [TIM0:0x8C/TIM1:0xCC] (226)12.6.6 TIMx从模式控制寄存器1 (TIMx_TGICR1) [TIM0:0x8D/TIM1:0xCD] (228)12.6.7 TIMx中断使能寄存器0 (TIMx_IER) [TIM0:0x8E/TIM1:0xCE] (230)12.6.8 TIMx中断使能寄存器1(TIMx_IER_NOCMP)[TIM0:0xB7/TIM7:0xF7] 23112.6.9 TIMx通道CC0输入捕获/输出比较模式控制寄存器(TIMx_CC0MR)[TIM0:0x8F/TIM1:0xCF] (231)12.6.10 TIMx通道CC1输入捕获/输出比较模式控制寄存器(TIMx_CC1MR)[TIM0:0x91/TIM1:0xD1] (236)12.6.11 TIMx通道CC2输入捕获/输出比较模式控制寄存器(TIMx_CC2MR)[TIM0:0x92/TIM1:0xD2] (241)12.6.12 TIMx通道CC3输入捕获/输出比较模式控制寄存器(TIMx_CC3MR)[TIM0:0x93/TIM1:0xD3] (245)12.6.13 TIMx通道使能控制寄存器(TIMx_CCENR) [TIM0:0x94/TIM1:0xD4] (249)12.6.14 TIMx通道极性控制寄存器(TIMx_CCPS) [TIM0:0x95/TIM1:0xD5] (251)12.6.15 TIMx死区时间寄存器(TIMx_DTG) [TIM0:0x96/TIM1:0xD6] (252)12.6.16 TIMx周期值自动装载寄存器的低8位(TIMx_ARRL) [TIM0:0x97/TIM1:0xD7]25212.6.17 TIMx周期值自动装载寄存器的高8位(TIMx_ARRH) [TIM0:0x99/TIM1: 0xD9]25312.6.18 TIMx预分频寄存器的低8位(TIMx_PSCL) [TIM0:0x9A/TIM1: 0xDA] (253)12.6.19 TIMx预分频寄存器的高8位(TIMx_PSCH) [TIM0:0x9B/TIM1:0xDB] (253)12.6.20 TIMx重复计数寄存器(TIMx_RCR) [TIM0:0x9C/TIM1:0xDC] (254)12.6.21 TIMx通道CC0捕获/向上计数比较寄存器的低8位(TIMx_CC0RUL)[TIM0:0x9D/ TIM1:0xDD] (254)12.6.22 TIMx通道CC0捕获/向上计数比较寄存器的高8位(TIMx_CC0RUH)[TIM0:0x9E/TIM1:0xDE] (255)12.6.23 TIMx通道CC0向下计数比较寄存器的低8位(TIMx_CC0RDL) [TIM0:0x9F/ TIM1:0xDF] (256)12.6.24 TIMx通道CC0向下计数比较寄存器的高8位(TIMx_CC0RDH) [TIM0:0xA1/ TIM1:0xE1] (257)12.6.25 TIMx通道CC1捕获/向上计数比较寄存器的低8位(TIMx_CC1RUL)[TIM0:0xA2/TIM1:0xE2] (258)12.6.26 TIMx通道CC1捕获/向上计数比较寄存器的高8位(TIMx_CC1RUH)[TIM0:0xA3/TIM1:0xE3] (259)12.6.27 TIMx通道CC1向下计数比较寄存器的低8位(TIMx_CC1RDL)[TIM0:0xA4/TIM1:0xE4] (260)12.6.28 TIMx通道CC1向下计数比较寄存器的高8位(TIMx_CC1RDH)[TIM0:0xA5/TIM1:0xE5] (260)12.6.29 TIMx通道CC2捕获/向上计数比较寄存器的低8位(TIMx_CC2RUL)[TIM0:0xA6/TIM1:0xE6] (261)12.6.30 TIMx通道CC2捕获/向上计数比较寄存器的高8位(TIMx_CC2RUH)[TIM0:0xA7/TIM1:0xE7] (262)12.6.31 TIMx通道CC2向下计数比较寄存器的低8位(TIMx_CC2RDL)[TIM0:0xA9/TIM0:0xE9] (263)12.6.32 TIMx通道CC2向下计数比较寄存器的高8位(TIMx_CC2RDH)[TIM0:0xAA/TIM1:0xEA] (264)12.6.33 TIMx通道CC3捕获/向上计数比较寄存器的低8位(TIMx_CC3RUL)[TIM0:0xAB/TIM1:0xEB] (265)12.6.34 TIMx通道CC3捕获/向上计数比较寄存器的高8位(TIMx_CC3RUH)[TIM0:0xAC/TIM1:0xEC] (266)12.6.35 TIMx通道CC3向下计数比较寄存器的低8位(TIMx_CC3RDL)[TIM0:0xAD/TIM1:0xED] (267)12.6.36 TIMx通道CC3向下计数比较寄存器的高8位(TIMx_CC3RDH)[TIM0:0xAE/TIM1:0xEE] (268)12.6.37 TIMx刹车控制寄存器(TIMx_BRKC) [TIM0:0xAF/TIM1:0xEF] (269)12.6.38 TIMx事件产生寄存器(TIMx_EGR) [TIM0:0xB1/TIM1:0xF1] (271)12.6.39 TIMx互补模式控制寄存器(TIMx_CMPLMTARY) [TIM0:0xB2/TIM1:0xF2]27312.6.40 TIMx中断标志寄存器0 (TIMx_ISR0) [TIM0:0xB3/TIM1:0xF3] (273)12.6.41 TIMx中断标志寄存器1 (TIMx_ISR1) [TIM0:0xB4/TIM1:0xF4] (274)12.6.42 TIMx中断标志寄存器2 (TIMx_ISR2) [TIM0:0xB9/TIM1:0xF9] (275)12.6.43 TIMx计数器的低8位(TIMx_CNTL) [TIM0:0xB5/TIM1:0xF5] (276)12.6.44 TIMx计数器的高8位(TIMx_CNTH) [TIM0:0xB6/TIM1:0xF6] (276)13CORDIC协处理器 (277)13.1概述 (277)13.2功能描述 (278)13.2.1 输入数据格式 (278)13.2.2 结果数据归一化 (278)13.2.3 CORDIC调度 (279)13.2.4 CORDIC中断 (280)13.2.5 CORDIC精度 (280)13.3CORDIC 寄存器 (281)13.3.1 JMT51 MCU调度寄存器 (281)13.3.2 JMT018 DSP指令调度寄存器 (284)14通用异步收发传输器(UART) (287)14.1概述 (287)14.2框图 (287)14.3UART管脚配置 (288)14.4UART工作模式 (288)14.4.1 标准UART工作模式0:同步移位寄存器 (288)14.4.2 标准UART工作模式1:8位UART,波特率可变 (289)14.4.3 标准UART工作模式2:9位UART,波特率固定 (290)14.4.4 标准UART工作模式3:9位UART,波特率可变 (290)14.4.5 38KHz红外调制发送 (291)14.4.6 IrDA(SIR)红外通信 (292)14.5UART多机通信 (292)14.6UART奇偶校验 (293)14.7UART波特率计算 (293)14.8UART寄存器 (302)14.8.1 UART0控制寄存器(S0CON) [0x98] (302)14.8.2 UART0数据缓冲寄存器(S0BUF) [0x99] (303)14.8.3 UART0波特率重载寄存器低8位(S0RELL) [0x9A] (303)14.8.4 UART0波特率重载寄存器高2位(S0RELH) [0x9B] (304)14.8.5 UART0红外控制寄存器(S0IRCON) [0x9C] (304)14.8.6 UART1控制寄存器(S1CON) [0xF1] (305)14.8.7 UART1数据缓冲寄存器(S1BUF) [0xF2] (305)14.8.8 UART1波特率重载寄存器低8位(S1RELL) [0xF3] (306)14.8.9 UART1波特率重载寄存器高2位(S1RELH) [0xF4] (306)14.8.10 UART1红外控制寄存器(S1IRCON) [0xF5] (306)15I2C接口 (308)15.1概述 (308)15.2框图 (308)15.3I2C管脚配置 (308)15.4I2C模块连接 (308)15.5I2C数据格式 (309)15.5.2 读写控制比特 (309)15.5.3 反馈(ACK) (310)15.5.4 起始条件和结束条件 (310)15.5.5 数据格式 (310)15.5.6 时钟同步 (311)15.5.7 仲裁 (311)15.6I2C时钟产生 (312)15.7I2C工作模式 (313)15.7.1 从机模式 (313)15.7.2 主机模式 (315)15.8I2C中断 (318)15.9I2C寄存器 (319)15.9.1 I2C控制寄存器(I2CCON) [0xE1] (319)15.9.2 I2C从机地址寄存器低8位(I2CSADDRL) [0xE2] (320)15.9.3 I2C从机地址寄存器高2位(I2CSADDRH) [0xE3] (320)15.9.4 I2C本机地址寄存器低8位(I2COADDRL) [0xE4] (321)15.9.5 I2C本机地址寄存器高2位(I2COADDRH) [0xE5] (321)15.9.6 I2C工作时钟分频控制寄存器(I2CDIV) [0xE6] (321)15.9.7 I2C时钟SCL低电平时间配置寄存器(I2CDUTYL) [0xE7] (322)15.9.8 I2C时钟SCL高电平时间配置寄存器(I2CDUTYH) [0xE9] (322)15.9.9 I2C数据SDA保持时间配置寄存器(I2CHOLD) [0xEA] (322)15.9.10 I2C数据写缓冲寄存器(I2CWBUF) [0xEB] (323)15.9.11 I2C数据读缓冲寄存器(I2CRBUF) [0xEC] (323)15.9.12 I2C状态寄存器(I2CSTS) [0xED] (323)15.9.13 I2C中断标志寄存器(I2CISC) [0xEE] (324)15.9.14 I2C中断使能寄存器(I2CIEN) [0xEF] (325)16串行外设接口(SPI) (326)16.1概述 (326)16.2框图 (326)16.3SPI管脚配置 (326)16.4SPI主/从机互连 (327)16.4.1 4线互连模式 (327)16.5SPI时序设置 (328)16.6数据发送和接收过程 (329)16.6.1 主机模式 (329)16.6.2 从机模式 (331)16.7SPI中断 (332)16.8SPI寄存器 (333)16.8.1 SPI控制寄存器(SPICON) [0xC9] (333)16.8.2 SPI中断使能寄存器(SPIIE) [0xCA] (334)16.8.3 SPI中断标志寄存器(SPIIF) [0xCB] (335)16.8.4 SPI波特率控制寄存器(SPIBR) [0xCC] (335)16.8.5 SPI数据缓冲寄存器(SPIBUF) [0xCD] (336)17模拟/数字转换(ADC)和可编程增益放大器(PGA) (337)17.1概述 (337)17.2ADC转换结果访问方式 (338)17.3ADC输入端口配置 (338)17.4可编程增益放大器(PGA)说明 (339)17.5ADC参考电压配置 (341)17.6ADC转换功能 (341)17.7ADC转换结果数据格式 (342)17.8ADC转换时序 (342)17.9模拟看门狗 (343)17.10外部触发事件 (344)17.11特殊通道序列管理 (346)17.12ADC工作模式 (347)17.12.1 单次转换+非扫描模式 (347)17.12.2 单次转换+扫描模式 (348)17.12.3 连续转换+非扫描模式 (350)17.12.4 连续转换+扫描模式 (351)17.13双ADC协同工作模式 (353)17.13.1 独立模式 (353)17.13.2 普通同步模式 (353)17.13.4 普通交叉模式 (355)17.13.5 特殊交替触发模式 (355)17.13.6 普通同步+特殊同步模式 (356)17.13.7 普通同步+特殊交替触发模式 (357)17.13.8 普通交叉+特殊同步模式 (358)17.14中断处理 (359)17.15ADC寄存器 (360)17.15.1 JMT51访问ADC寄存器 (360)17.15.2 JMT018访问ADC寄存器 (391)18模拟比较器(CMP) (393)18.1模拟比较器概述 (393)18.2低压检测 (394)18.2.1 低压检测保护程序示例 (395)18.3模拟比较器寄存器 (396)18.3.1 模拟比较器使能寄存器(CMPEN) [0x91] (396)18.3.2 模拟比较器中断寄存器(CMPINT) [0x92] (397)18.3.3 模拟比较器比较结果寄存器(CMPFLAG) [0x93] (397)18.3.4 模拟比较器滤波选择寄存器(CMPFT) [0x94] (398)18.3.5 模拟比较器VDD分压寄存器(CMPVDD) [0x95] (398)18.3.6 模拟比较器参考电压选择寄存器(CMPREF) [0x96] (398)19通用输入/输出(GPIO) (400)19.1管脚设置 (400)19.2管脚功能复用 (403)19.3PWM管脚特殊复用 (407)19.3.1 PWM输出复用 (407)19.3.2 PWM刹车复用 (407)19.4管脚数据寄存器读写 (408)19.5外设管脚复用配置 (408)19.6管脚滤波 (415)19.7INT0中断 (415)19.8INT1中断 (418)19.9P A0唤醒 (421)19.10GPIO寄存器 (421)19.10.1 PA0数字I/O控制寄存器(PA0CTRL) [0x99] (424)19.10.2 PA1数字I/O控制寄存器(PA1CTRL) [0x9A] (425)19.10.3 PA2数字I/O控制寄存器(PA2CTRL) [0x9B] (426)19.10.4 PA3数字I/O控制寄存器(PA3CTRL) [0x9C] (427)19.10.5 PA4数字I/O控制寄存器(PA4CTRL) [0x9D] (428)19.10.6 PA5数字I/O控制寄存器(PA5CTRL) [0x9E] (428)19.10.7 PA6数字I/O控制寄存器(PA6CTRL) [0x9F] (429)19.10.8 PA7数字I/O控制寄存器(PA7CTRL) [0xC3] (430)19.10.9 PB0数字I/O控制寄存器(PB0CTRL) [0xA1] (431)19.10.10 PB1数字I/O控制寄存器(PB1CTRL) [0xA2] (432)19.10.11 PB2数字I/O控制寄存器(PB2CTRL) [0xA3] (432)19.10.12 PB3数字I/O控制寄存器(PB3CTRL) [0xA4] (433)19.10.13 PB4数字I/O控制寄存器(PB4CTRL) [0xA5] (434)19.10.14 PB5数字I/O控制寄存器(PB5CTRL) [0xA6] (435)19.10.15 PB6数字I/O控制寄存器(PB6CTRL) [0xA7] (436)19.10.16 PB7数字I/O控制寄存器(PB7CTRL) [0xC4] (436)19.10.17 PC0数字I/O控制寄存器(PC0CTRL) [0xA9] (437)19.10.18 PC1数字I/O控制寄存器(PC1CTRL) [0xAA] (438)19.10.19 PC2数字I/O控制寄存器(PC2CTRL) [0xAB] (439)19.10.20 PC3数字I/O控制寄存器(PC3CTRL) [0xAC] (440)19.10.21 PC4数字I/O控制寄存器(PC4CTRL) [0xAD] (440)19.10.22 PC5数字I/O控制寄存器(PC5CTRL) [0xAE] (441)19.10.23 PC6数字I/O控制寄存器(PC6CTRL) [0xAF] (442)19.10.24 PC7数字I/O控制寄存器(PC7CTRL) [0xC5] (443)19.10.25 PD0数字I/O控制寄存器(PD0CTRL) [0xB1] (444)19.10.26 PD1数字I/O控制寄存器(PD1CTRL) [0xB2] (444)19.10.27 PD2数字I/O控制寄存器(PD2CTRL) [0xB3] (445)19.10.28 PD3数字I/O控制寄存器(PD3CTRL) [0xB4] (446)19.10.29 PD4数字I/O控制寄存器(PD4CTRL) [0xB5] (447)19.10.30 PD5数字I/O控制寄存器(PD5CTRL) [0xB6] (448)19.10.31 PD6数字I/O控制寄存器(PD6CTRL) [0xB7] (448)19.10.32 PD7数字I/O控制寄存器(PD7CTRL) [0xC6] (449)19.10.33 PE0数字I/O控制寄存器(PE0CTRL) [0xB9] (450)19.10.34 PE1数字I/O控制寄存器(PE1CTRL) [0xBA] (451)19.10.35 PE2数字I/O控制寄存器(PE2CTRL) [0xBB] (452)19.10.36 PE3数字I/O控制寄存器(PE3CTRL) [0xBC] (452)19.10.37 PE4数字I/O控制寄存器(PE4CTRL) [0xBD] (453)19.10.38 PE5数字I/O控制寄存器(PE5CTRL) [0xBE] (454)19.10.39 PE6数字I/O控制寄存器(PE6CTRL) [0xBF] (455)19.10.40 PE7数字I/O控制寄存器(PE7CTRL) [0xC7] (456)19.10.41 PG0数字I/O控制寄存器(PG0CTRL) [0xC1] (456)19.10.42 PG1数字I/O控制寄存器(PG1CTRL) [0xC2] (457)19.10.43 PA转换速率寄存器(PASR) [0xC9] (458)19.10.44 PB转换速率寄存器(PBSR) [0xCA] (459)19.10.45 PC转换速率寄存器(PCSR) [0xCB] (460)19.10.46 PD转换速率寄存器(PDSR) [0xCC] (461)19.10.47 PE转换速率寄存器(PESR) [0xCD] (461)19.10.48 PG转换速率寄存器(PGSR) [0xCE] (462)19.10.49 PA驱动能力寄存器(PADR) [0xD1] (463)19.10.50 PB驱动能力寄存器(PBDR) [0xD2] (464)19.10.51 PC驱动能力寄存器(PCDR) [0xD3] (464)19.10.52 PD驱动能力寄存器(PDDR) [0xD4] (465)19.10.53 PE驱动能力寄存器(PEDR) [0xD5] (466)19.10.54 PG驱动能力寄存器(PGDR) [0xD6] (467)19.10.55 模拟管脚使能寄存器0(AIOEN0) [0xCF] (467)19.10.56 模拟管脚使能寄存器1(AIOEN1) [0xD7] (469)19.10.57 复位管脚滤波选择寄存器(NRSTFQS) [0xD9] (470)19.10.58 唤醒使能寄存器(WKUPEN) [0xDB] (470)19.10.59 INT0上升沿中断使能寄存器(INT0PE) [0xDC] (471)19.10.60 INT0下降沿中断使能寄存器(INT0NE) [0xDD] (471)19.10.61 INT0中断使能寄存器(INT0EN) [0xDE] (472)19.10.62 INT0中断控制寄存器(INT0CON) [0xDF] (473)19.10.63 INT1上升沿中断使能寄存器(INT1PE) [0xE1] (474)19.10.64 INT1下降沿中断使能寄存器(INT1NE) [0xE2] (475)19.10.65 INT1中断使能寄存器(INT1EN) [0xE3] (476)19.10.66 INT1中断控制寄存器(INT1CON) [0xE4] (477)19.10.67 INT1中断管脚选择寄存器0(INT1SEL0) [0xE5] (478)19.10.68 INT1中断管脚选择寄存器1(INT1SEL1) [0xE6] (479)19.10.69 INT1中断管脚选择寄存器2(INT1SEL2) [0xE7] (480)19.10.70 INT1中断管脚选择寄存器3(INT1SEL3) [0xE9] (480)19.10.71 PWM刹车选择寄存器(PWMBKS) [0xEA] (481)19.10.72 PWM特殊复用输出分组选择寄存器(PWMOSEL) [0xF1] (481)19.10.73 PWM特殊复用输出选择寄存器0(PWMOSEL0) [0xF2] (482)19.10.74 PWM特殊复用输出选择寄存器1(PWMOSEL1) [0xF3] (483)19.10.75 PWM特殊复用输出选择寄存器2(PWMOSEL2) [0xF4] (483)19.10.76 PWM特殊复用输出使能寄存器0(PWMOMUX0) [0xF5] (484)19.10.77 PWM特殊复用输出使能寄存器1(PWMOMUX1) [0xF6] (485)19.10.78 PWM特殊复用输出使能寄存器2(PWMOMUX2) [0xF7] (486)19.10.79 PA输入缓冲使能寄存器(PAIE) [0xF9] (487)19.10.80 PB输入缓冲使能寄存器(PBIE) [0xFA] (488)19.10.81 PC输入缓冲使能寄存器(PCIE) [0xFB] (489)19.10.82 PD输入缓冲使能寄存器(PDIE) [0xFC] (489)19.10.83 PE输入缓冲使能寄存器(PEIE) [0xFD] (490)19.10.84 PG输入缓冲使能寄存器(PGIE) [0xFE] (491)19.10.85 PA数据寄存器(P0) [0x80] (492)19.10.86 PB数据寄存器(P1) [0x90] (492)19.10.87 PC数据寄存器(P2) [0xA0] (492)19.10.88 PD数据寄存器(P3) [0xB0] (492)19.10.89 PE数据寄存器(P4) [0xC8] (492)19.10.90 PG数据寄存器(P6) [0x98] (492)20电气特性 (493)20.1极限参数 (493)20.2工作条件 (493)20.2.1 芯片供电 (493)20.2.2 功耗特性 (493)20.2.3 I/O特性 (494)20.2.4 REGC引脚特性 (495)20.2.5 NRST引脚特性 (495)20.2.6 上电/掉电条件 (495)20.2.7 时钟特性 (496)20.2.8 通信接口 (498)20.2.9 FLASH特性 (501)20.2.10 ADC特性 (501)20.2.11 PGA特性 (502)20.2.12 CMP特性 (502)20.2.13 内部参考电压特性 (503)20.2.14 电气敏感性 (503)21封装特性 (504)21.1LQFP32L (504)21.2LQFP48L (505)21.3QFN32L (507)21.4TSSOP28L (508)1产品概述1.1功能描述JMT1808R是一款内置MCU和DSP的双核SOC芯片。

PCM1808PWR24位立体声音频ADC

PCM1808PWR24位立体声音频ADC192 kHz 、24bit 立体声音频ADC概述是一款高性能、低成本立体声音频模数转换器。

其集成了64倍过采样率Δ-Σ调制器、数字梳状滤波器、数字高通滤波器。

支持主、从机和两种串行音频数据格式。

支持掉电和时钟检测低功耗模式。

封装形式采用TSSOP14,温度支持-40° 到+85° C 。

特点● 24bit Δ-Σ立体声ADC ● +5.0 V 模拟电源(VA) ● +3.3 V 数字电源 (VDD)● 单端电压输入:3Vp-p ● 高性能THD+N :-93dB (典型值) SNR :99dB (典型值)动态范围:99dB (典型值)● 过采样抽取滤波器过采样频率:x64 通带纹波:±0.05 dB片上高通滤波器:0.91 Hz (48 kHz)● PCM 音频接口可选主机和从机模式数据格式:24-Bit I 2S, 24-Bit 左对齐● 集成模拟低通抗混叠滤波器● 采样率:8 kHz–96 kHz● 系统时钟:256 fs ,384 f S , 512 f S ● 精度:24bit ● 封装:TSSOP14Applications● 家庭影院和电视● 语音控制设备● 蓝牙?扬声器● 麦克风阵列处理器PCM1808PWR PCM1808PWR PCM1808PCM1808内部框图1. PIN脚描述PCM18082. 性能和参数极限工作条件推荐工作条件电学参数测试条件为T时序参数系统时钟时序图上电时序图时钟检测掉电和复位时序图音频数据接口时序图(从机模式:LRCK和BCK做为输入)音频数据接口时序图(主机模式:LRCK和BCK做为输出)音频时钟接口时序图(主机模式:BCK做为输出)3. 典型曲线图(条件是TA = 25°C, VCC=5 V, VDD=3.3 V,主机模式, fs = 48 kHz,系统时钟 = 512 fs, 24-bit数据)4. 详细描述PCM1808PWR 是一款高性能、低成本、单芯片立体声音频模数转换器,其采用单端模拟输入,里面集成了64倍过采样的Δ-Σ调制器、数字抽取滤波器、数字高通滤波器,支持主机和从机模式,可以检测系统时钟来掉电和复位芯片。

CRIO-4010 单相、三相全参数交流 电量采集模块 用户手册说明书

CRIO-4010单相、三相全参数交流电量采集模块用户手册版本号:Q7-30-02修订日期:2016-11-1国控精仪(北京)科技有限公司2016年版权所有本软件文档及相关套件均属国控精仪(北京)科技有限公司所有,包含专利信息,其知识产权受国家法律保护,除非本公司书面授权许可,其他公司、组织不得非法使用和拷贝。

为提高产品的性能、可靠性,本文档中的信息如有完善或修改,恕不另行通知,客户可从公司网站下载或致电我们通过电子邮件索取,制造商无需作成承诺和承担责任。

客户使用产品和软件文档进行设备调试和生产时,应进行可靠性、功能性等全面测试,方可进行整体设备的运行或交付。

我们提供7*24电话技术支持服务,及时解答客户问题。

如何从国控精仪获得技术服务我们将为客户提供满意全面的技术服务。

请您通过以下信息联系我们。

国控精仪公司信息网址: 英文中文销售服务: **************销售分机:801 电话: 400 9936 400 ************传真: ************地址: 北京市海淀区安宁庄东路18号2号办公楼420-423室请将您下列的信息通过邮件或传真发送给我们1概述...................................................................................................................................... - 1 -1.1产品特性.................................................................................................................. - 1 -1.2产品应用.................................................................................................................. - 1 -1.3产品详细指标.......................................................................................................... - 2 -1.3.1电量参数...................................................................................................... - 2 -1.3.2系统稳定时间.............................................................................................. - 2 -1.3.3物理特征...................................................................................................... - 3 -1.3.4产品功耗(典型值) ..................................................................................... - 3 -1.3.5工作环境...................................................................................................... - 3 -1.3.6存储环境...................................................................................................... - 3 -1.4软件支持.................................................................................................................. - 3 -2设备安装.............................................................................................................................. - 5 -2.1产品开箱.................................................................................................................. - 5 -2.2软件安装.................................................................................................................. - 5 -2.3产品布局图.............................................................................................................. - 6 -3信号连接说明...................................................................................................................... - 7 -3.1连接器管脚分配...................................................................................................... - 7 -3.2电源与通讯连接...................................................................................................... - 8 -3.3信号连接.................................................................................................................. - 9 -4 模拟量输入(AI)模块功能码........................................................................................ - 10 -4.1读保持寄存器........................................................................................................ - 10 -4.2读输入寄存器........................................................................................................ - 11 -4.3设置单个保持寄存器............................................................................................ - 13 -4.4设置多个保持寄存器............................................................................................ - 13 -5产品注意事项、保修、校准............................................................................................ - 15 -图2-1 CRIO4010产品图................................................................................................... - 6 -图3-1 电源与通讯接线图 ................................................................................................ - 8 -图3-2 单相电示意图 ........................................................................................................ - 9 -图3-3 三相电示意图 ........................................................................................................ - 9 -表3-1 16P端子标注 .......................................................................................................... - 8 -1概述CRIO-4010是基于RS485的高性能通信模块。

康宁LANscape

康宁LANscape®铜缆布线产品手册大对数铜缆........................................................................................................................................... 2铜缆系列................................................................................................................................................. 3铜缆跳线................................................................................................................................................ 12RJ45模块................................................................................................................................................ 21铜缆配线架........................................................................................................................................... 24信息面板系列 (26)目录康宁公司成立于1851 年,总部位于美国纽约州康宁市,是一家全球性多元化的高科技公司。

综合布线及配件产品介绍1808 【海康威视】

网线

经销产品配件 超五类网线 六类网线 监控专用网线

电源线

经销产品配件 电源线

电源线

电源线

产品亮点 用料讲究,阻燃性能好!

100米电源线: DS-1LPRVV-2C075 DS-1LPRVV-2C100 DS-1LPRVV-2C150

200M/Reel电源线: DS-1LPRVV-2C150/2B DS-1LPRVV-2C100/2B DS-1LPRVV-2C075/2B

✓ 摄像机安装座可垂直、水平自由旋转,方便摄像机角度 调整

✓ 采用精密钢板整体成形工艺,高强度,安全可靠

多角度 调整

支架

【球机】 DS-1602ZJ系列

三大 优势

无需转 接头

✓ 快速安装,无需螺纹转接头 ✓ 自带安全绳锁扣 ✓ 新增调试口,有利后续接线,调试维护

安全绳 锁扣

调试口

4寸球机专用嵌入式支架

耐用:采用优质器件,智能负载能耗管理,有效延长电源寿命,同 时耐低温,适合多种复杂恶劣环境。

适配器

DS-2FA1202-B

12V/2A 防水电源

DS-2FA1202-B

亮点

✓ 具备短路保护、过流保护、输出过压保护等多种保护功能 ✓ 海康威视品牌认证,性价比高的同时更兼容海康摄像机,保

证摄像机的供电稳定、可靠 ✓ 具备3C认证证书,安全性能远高于市场水平

✓ 体积小巧,外观新颖,应用

✓ 海康威视品牌认证,性价比高的同时更兼容海康摄像机,保

于摄像机、路由器等音视频、

证摄像机的供电稳定、可靠

数据通讯类产品

✓ 具备3C认证证书,安全性能远高于市场水平

UPS

经销产品配件 UPS

BP1808系统应用指南

30.6 37.5 42.3 46.7 51.6 56.9

应用实例

BUCK Dim PWM调光

Dim frequent=200Hz

Dim Duty(%)

1

2

3

Io(mA) 1(不闪) 11

19

Dim Duty(%)

10

20

30Leabharlann Io(mA)71143

216

4

5

6

27

34

41

等等。。。

典型应用 BP1808基本原理

CS A

VOUT

LDO

VDD

1.2V

OVP

PWM Logic OSC

COMP SW GND

DIM

EN/ Dimm in g

BP1808以固定频率400KHz模式工作。通过采集接在CS引脚和VOUT引脚 之间采样电阻上的电压(V-),与内部基准0.2V(V+)比较,通过误差放 大器(EA),控制Comp的电压( V+ ),Comp电压与内部振荡产生的固定 锯齿波(V-)比较,来决定导通时间。当输出电流减小时,采样电阻上的 电压小于0.2V,通过EA把Comp电压拉高,导通时间增大,从而使采样电阻 上的电压维持在0.2V,输出电流维持设定值,反之亦然。

18

设计注意事项 BOOST应用电感选取计算方法

先计算系统工作在零界模式下的电感量:

L

(Vo-Vin) *Vin2 2*Vo2 * Io*f

一般选取以上计算得到的感量的2~4倍。电感选的太小,会使峰值 电流变大,流过MOS和二极管的有效值变大,加大了导通损耗。但是 电感太大,首先,在相同尺寸下感量越大,饱和电流会越小;其次, 感量越大所需的铜线匝数增加,阻抗增加,损耗也增加;最后,加大 电感量会使环路的响应时间变慢。

MPC100中文资料

MPC100 is designed for wide-bandwidth systems, including high-definition television and broadcast equipment. Although it is primarily used to route video signals, the harmonic and dynamic attributes of the MPC100 make it appropriate for other analog signal routing applications such as radar, communications, computer graphics, and data acquisition systems.

q VIDEO ROUTING AND MULTIPLEXING (CROSSPOINTS)

q RADAR SYSTEMS q DATA ACQUISITION q INFORMATION TERMINALS q SATELLITE OR RADIO LINK IF ROUTING

DESCRIPTION

©1991 Burr-Brown Corporation

PDS-1133F

Printed in U.S.A. March, 1995

元器件交易网

SPECIFICATIONS

At VCC = ±5V, RL = 10kΩ, RSOURCE = 50Ω, and TA = +25°C, unless otherwise noted.

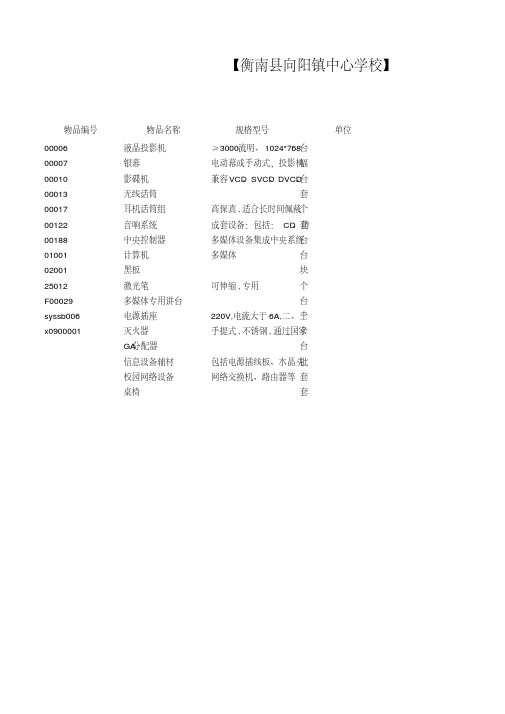

多功能教室设备值

【衡南县向阳镇中心学校】

物品编号物品名称规格型号单位

00006液晶投影机≥3000流明、1024*768台

00007银幕电动幕或手动式,投影机幅

00010影碟机兼容VCD、SVCD、DVCD、台

00013无线话筒套

00017耳机话筒组高保真,适合长时间佩戴个

套

00122音响系统成套设备:包括:CD、功

00188中央控制器多媒体设备集成中央系统台

01001计算机多媒体台

02001黑板块

25012激光笔可伸缩,专用个

F00029多媒体专用讲台台

syssb006电源插座220V,电流大于6A,二、三个

x0900001灭火器手提式,不锈钢,通过国家个

GA分配器台

信息设备辅材包括电源插线板、水晶头批

校园网络设备网络交换机、路由器等套

桌椅套。

NAP-100AC 商品说明书

20121018NAP-100AC(C A T A L Y T I C T Y P E G A S S E N S O R)Handling manualNemoto Sensor Engineering Co., Ltd.4-10-9, Takaido-higashi, Suginami-ku, TokyoTEL. 03-3333-2760FAX. 03-3333-7344E-mail:*****************.jpURL : http://www.nemoto.co.jpNAP-100AC is a catalytic type gas sensor employed for mainly commercial or semi-industrial applications. Since this sensor does not have an explosion proof structure, it is recommended to install into an intrinsic explosion proof enclosure for actual application.1.Features and application of NAP-100AC1)Features・Good stability・Excellent repeatability and detection accuracy・Good linearity against gas concentration・Quick response・Down sizing for design flexibility of gas alarm or detector2)Applications・Gas alarm or detector for general combustible gases・Gas densitometer・Driving module for gas leakage detector2.Maximum ratings・Supply voltage to sensor AC 3.3V (50 - 60Hz)DC 3.3V・Ambient temperature and humidity in operationTemperature -40 ~ +80℃Humidity less than 99%RH(without dew condensation)・Ambient temperature and humidity in storageTemperature -40 ~ +80℃Humidity less than 99%RH(without dew condensation)3.Ratings・Supply voltage to sensor AC 2.6 ± 0.13V(50-60Hz)DC 2.6 ± 0.13V・Current(when 2.5V is supplied) AC 160 ~ 180mA(50-60Hz)DC 160 ~ 180mA・Ambient temperature and humidity in operationTemperature -20 ~ +60℃Humidity less than 95%RH(without dew condensation)・Ambient temperature and humidity in storageTemperature -30 ~ +70℃Humidity less than 99%RH(without dew condensation)4.Detection rangeIt can measure/detect overall combustible gases less than 100%LEL within +/-10% accuracy, however the measurement accuracy is little lower if in over 50%LEL.5.Response and recovery timeFrom clean air to 10%LEL T90 : less than 20sec.From gas to clean air T90 : less than 30sec.(This time is dependent on ambient conditions.)6.Specifications・Detected gases General combustible gases・Measuring range 2 - 100%LEL・Gas sensitivity More than 35mV/% of methane ・Repeatability in the same day Less than 2%・Methane sensitivity stability Less than 1%/month・Zero offset stability Less than 1mV/month・Resolution 300ppm of methane・Zero offset value -35 - +35mV in clean air7.Relative sensitivityGases Chemical formula LEL (%) Relative sensitivity1 Methane CH4 5.0 1002 Propane C3H8 2.2 703 Iso-Butane C4H10 1.8 654 n-Pentane C5H12 1.4 655 n-Hexane C6H14 1.2 656 n-Heptane C7H16 1.05 557 Iso-Octane C8H18 0.95 508 Methanol CH3OH 6.7 1109 Ethanol C2H5OH 3.3 8010 Iso-Propanol C3H7OH 2.2 7011 Acetone (CH3)2CO 2.6 7512 Toluene C6H5CH3 1.2 55acetate CH3COOC2H5 2.2 6513 Ethyl14 Hydrogen H2 4.0 9515 Ammonia NH3 15.0 16016 Cyclohexane C6H12 1.3 6517 Ethylene C2H4 2.7 75 Note ) This sensor is not applicable for the detection of acetylene.The previous table can be used for quick reference as below.Example)In case 50%LEL ethanol is measured by detection equipment calibrated with 0 – 100%LEL of methane, the following conversion is made from the table.(80 x 50)/100=40%LEL by methane scale8.Typical sensitivity characteristics9.Structure and dimensionNo.Part name Material Remarks1 Mount base Phenol resin2 Cap Ni coated brass3 Pins Pure Ni 0.8 mmDiameter4 Filament coil PT 0.03 mmDiameter5 Separator SUS 304CSP t = 0.16 Sensor7 Compensator2040608010012014000.51 1.52 2.5Sensitivityvalue(mV)Gas concentration (%)MethaneIso-ButaneHydrogenEthanol10.Recommended circuitNote)Fixed resistors in the above circuit have to be metal film resistor, and variable resistor has to be cermet or metal film type. If the carbon type is employed, zero offset value is not stable because the resistance values of them are varied.11. Evaluation method of sensor(1)Test equipmentOutline of test equipment is shown as below.Remarks)1) Test chamber・ Material of test chamber is to be like as metal or glass which does not exhale and adsorb gases.・ Volume of test chamber is to be 1 litter per 1pc. of sensor.2) Circumstance・ Clean air is to be available. Dirty air in a factory which contains combustible gases or organic solvent vapor is not to be supplied to test chamber.3) Gas densitometer・ IR gas densitometer is suitable.4) Air agitation in test chamber・ Air agitation in test chamber is to be noticed in order not to flow air to sensor directly. Air velocity is to be less than 0.5m/sec.5) Power supply・ Sensor is available by AC power and DC power, but DC power supply is to be recommended for more accurate measurement.6) Digital volt meter・ Since the impedance of sensor is fairly low, general digital volt meter having over 100kohm as input impedance is recommended.7) Ventilation・ Ventilator with ventilation ability of over 10 times per minute of the volume of test chamber is to be necessary for the next measurement.8) Installation position of sensor in test chamber・ When the sensor is installed in test chamber, it should be noticed that every sensor is to be in constant position because output signal is changed in case that position of sensor is changed. If the rough evaluation is enough, such notice is not needed.(2) Adjustment of gas concentrationAdjustment of gas concentration is to be conducted by volume method or by using IR gas densitometer. In case of volume method, gas volume of injection to chamber is obtained from the calculation formula described as below.V m Vi C Tr Tc() =++-・・102732736V;Gas volume to be injectedVi;Inner volume of test chamber(m )C;Target gas concentration(ppm)Tc;Temperature in test chamber(℃)Tr;Room temperature(℃)(3) Evaluation method1) Preliminary aging・ Before evaluation of sensor, preliminary aging at rated voltage for over 1 hr. is to be necessary.2) Measurement・ At first, output voltage in clean air is to be measured. It should be confirmed that output voltage has to be stable, not fluctuated.・ Output voltage is to be measured after the designated volume of gas is injected into a test chamber.・ After measurement, air in test chamber is to be exhaled compulsory.(4) Notice on handling・ Sensor is to be gently handled without drop or shock.・ Handling is to be avoided in a location which corrosive gases and poisoned gases exist.・ Sensor is not to be dipped in wate。

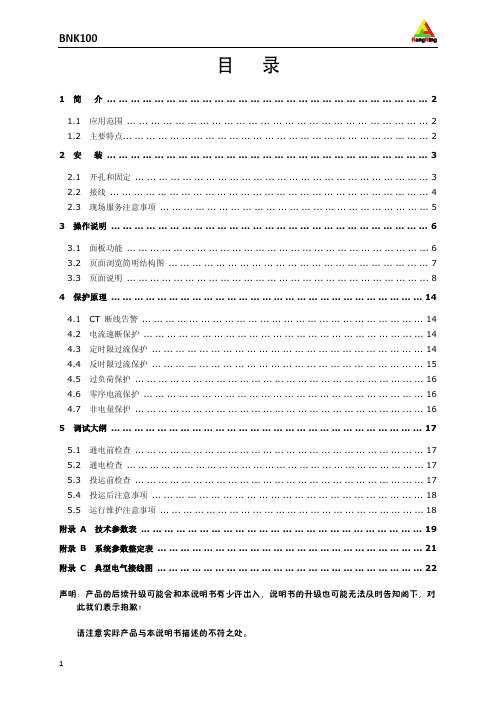

BNK100说明书

4 保护原理 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 14 4.1 4.2 4.3 4.4 4.5 4.6 4.7 CT 断线告警 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 14 电流速断保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 14 定时限过流保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 14 反时限过流保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 15 过负荷保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 16 零序电流保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 16 非电量保护 ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... ... 16

安拓 IN1808 系列 设置指南说明书

1I M P w w w .e x t r o n .c o m t a l l a t i o n i n s t r u c t i oo n n e c t i n g t h e e .IN1808 Series • Setup Guide4K @ 60 Hz at 4:4:4. They feature DisplayPort, HDMI, and DTP2 inputs, HDMI output and a mirrored Extron DTP2 outputextension to send video, audio, and control signals up to 330 feet (100 meters) over a shielded CATx cable. The IN1808 IPCP SA and IN1808 IPCP MA 70 models each have a built-in Extron IPCP Pro 355M IP Link Pro Control Processor, and an integrated 100 watt class D power amplifier. The IN1808 Series delivers high image quality, fast and reliable switching, Extron ProDSP audio processing, seamless video transition effects, logo keying, and HDMI loop out. The scalers can be controlled and configured over Ethernet, RS-232, or USB.This guide provides instructions for an experienced user to set up and configure the IN1808 (base model), IN1808 IPCP SA, and IN1808 IPCP MA 70 scalers. It covers how to perform basic operations using the front panel controls and selected Simple Instruction Set (SIS™) commands.NOTES:•For full installation, configuration, menus, connector wiring, and operation details, see the IN1806 and IN1808 Series User Guide at . For installation, configuration, and operation details of the embedded IPCP Pro 355M, see the IPCP Pro Series User Guide .•The IN1808 Series products can also be configured via the Extron Product Configuration Software (PCS), available at . For information on using PCS, see the IN1806 and IN1808 Series Help File.InstallationIN1808 Series Rear Panel ConnectorsFigure 1 shows the rear panel of the IN1808 IPCP SA rear panel. The IN1808 IPCP MA 70 rear panel is the same except that the embedded amplifier is mono while the SA model amplifier is stereo. The IN1808 base model rear panel does not have an embedded IPCP Pro 355M module (see figure 1, P ) or amplifier module (N ).Figure 1.Rear Panel Connectors, IN1808 IPCP SAA AC power connectorB DisplayPort input connector (input 1)C HDMI (with CEC) loop out connectorD DTP2/XTP input connectors (inputs 7 and 8)E HDMI (with CEC) output connector (1A)FDTP2/XTP/HDBaseT (with CEC) output connector (1B)G Over TP IR pass-through connectorH Analog line audio inputs 3 and 4I Analog mic/line audio inputs 1and 2 and adjacent phantom power LEDs J Analog line audio outputs 1 through 4K Remote RS-232 port L Reset LED M Reset buttonN Amplified audio output (IPCP modelsonly)o Aux mono or stereo analog lineaudio input connector P IPCP Pro 355M Control Processor (IPCP models only)Q HDMI inputs 2 through 6R LAN connector (IN1808 base modelonly, see the note and illustration below)IN1808 • Setup Guide (Continued)Mounting and CablingStep 1 — Mount the devicea. Turn off or disconnect all equipment power sources.b. Mount the IN1808 to a rack using the pre-installed side mounting brackets, or remove the brackets and use an optional19-inch rack under-desk mounting kit (see the mounting instructions provided with the kit, available at ).The IN1808 base model has a 1U high, full rack wide enclosure. The IN1808 IPCP models have 2U, full rack enclosures.Step 2 — Connect inputsMake the following input connections as needed:• Connect a DP source to the Input 1 DisplayPort connector (see figure 1, B, on the previous page).• Connect HDMI or DVI (with an appropriate adapter) sources to HDMI input connectors 2 through 6 (Q).• Connect DTP transmitters to the DTP2/XTP RJ-45 input connectors 7 and 8 (D). These connectors allow for remote powering of DTP transmitters. You can configure the TP inputs for XTP mode via SIS commands, the on-screendisplay (OSD), or PCS (see the IN1808 Series Help File). For cable wiring and recommendations, see Twisted PairRecommendations for DTP, XTP, and HDBaseT Communication on the next page.• Connect analog audio sources to:• The 5-pole captive screw line audio input connectors 3 and 4 (H) and the Aux connector (O) for balanced or unbalanced stereo audio. The Aux Line input is shared and can be associated with one or more video inputs.• Connect balanced or unbalanced mic or line level inputs to 3-pole Mic/Line captive screw connectors 1 and 2 (I).These inputs support optional +48 VDC phantom power, which is indicated by the LEDs at the left of the connectors.Step 3 — Connect outputsMake the following output connections as needed:• Connect an HDMI, or DVI with an appropriate adapter, display to HDMI/CEC output connector 1A (E).• Connect a DTP/XTP matrix switcher/HDBaseT compatible receiver to output connector 1B (F). For cable wiring and recommendations, see Twisted Pair Recommendations for DTP, XTP, and HDBaseT Communication.• To pass infrared data, connect a control device to the 3-pole IR Over DTP captive screw connector (see IR Over TP Wiring on the next page). Alternatively, insert RS-232 communication to a DTP/HDBaseT endpoint via Ethernet (see the IN1808Series User Guide for more information).• Connect balanced or unbalanced analog audio output devices to one or both 5-pole captive screw output connector pairs1 and2 or3 and4 (J). See Audio Wiring on the next page for more information.• For IPCP models, connect speakers to the amplifier module via the 5 mm 4-pole stereo (IN1808 IPCP SA) or 2-pole mono (IN1808 IPCP MA 70) Amplified Output connector (N).Step 4 — Connect control devices• To control the base model through Ethernet, connect a LAN or WAN to the LAN connector (R). To wire the RJ-45 connector to the cable, see Twisted Pair Recommendations for DTP, XTP, and HDBaseT Communication.For the IPCP models, connect a LAN or WAN to any of the AV LAN connectors on the IPCP Pro control processor (P). The default IP address of the scaler is 192.168.254.254. The default subnet mask is 255.255.255.0. The default gateway address is 0.0.0.0.• For serial RS-232 control, connect a host device to the 3-pole captive screw connector (K). The default baud rate is 9600.• For control through USB, connect a host device to the front panel USB mini-B port (see figure 2, H on page 4).Step 5 — Set up the IPCP Pro 355M control processor (IPCP models only)The Extron IPCP Pro 355M control processor (see figure 1, P) provides monitoring and control of a variety of external devices, such as projectors and lights. See the IPCP Pro Series Setup Guide, available at , for installation details.Step 6 — Connect powerConnect a 100 to 240 VAC, 50-60 Hz power source to the AC power connector (A).23Twisted Pair Recommendations for DTP , XTP , and HDBaseT CommunicationExtron recommends using the following practices to achieve full transmission distances and reduce transmission errors:•Use Extron XTP/DTP 24 SF/UTP cable for the best performance. At a minimum, Extron recommends 24 AWG, solid conductor, STP cable with a minimum bandwidth of 400 MHz.• Terminate cables with shielded connectors to the TIA/EIA-T568B standard (shown at right).•Limit the use of more than two pass-through points, which may include patch points, punch down connectors, couplers, and power injectors. If these pass-through pointsare required, use shielded couplers and punch down connectors.NOTE:When using shielded twisted pair cable in bundles or conduits, consider the following:• Do not exceed 40% fill capacity in conduits.• Do not comb the cable for the first 20 meters, where cables are straightened, aligned, and secured in tight bundles.• Loosely place cables and limit the use of tie wraps or hook-and-loop fasteners.•Separate twisted pair cables from AC power cables.Audio WiringWire the audio input and output connectors as shown at right. Use the supplied tie wrap to strap the audio cable to the extended tail of the connector. This does not apply to the amplified audio outputconnector on the SA and MA models.NOTE: The length of exposed wires is critical. The ideal length is 3/16 inch (5 mm).IR Over TP WiringTo transmit and receive IR signals, connect a control device to the three-pole Over TP IR connector (G, Tx, and Rx).NOTE: RS-232 data can be inserted via Ethernet only (see the IN1806 and IN1808 Series User Guide for details).TIA/EIA-T568B Pin Wire Color 1White-orange 2Orange 3White-green 4Blue 5White-blue 6Green 7White-brown 8BrownRJ-45ConnectorInsert Twisted Pair WiresPins:Balanced Audio OutputUnbalanced Audio OutputUnbalanced Audio InputBalanced Audio InputDo not tin the wires!Audio Inputs and Outputs 1 – 4 and AuxMic/Line Inputs 1 and 2Balanced Audio Input Unbalanced Audio Input4IN1808 • Setup Guide (Continued)Front Panel OverviewFigure 2 shows the front panel of the IN1808 IPCP SA and IPCP MA 70. The IN1808 base model is 1U high and has no IPCP Pro LEDs (H).Figure 2.Front Panel Features, IN1808 IPCP SA and IN1808 IPCP MA 70A Config portB Input selection buttons (1 through 8)C Logo buttonD Signal and Status LEDsE Menu and Enter buttonsF Navigation buttonsG Mic and Volume knobs and LEDsH IPCP Pro LEDs (IPCP models only)A Front panel configuration port — Connect a host device to the USB mini-B port for device configuration, control, and firmware upgradesB Input selection buttons (1 through 8) — Press one of these buttons to select an input. The buttons light amber for audioand video, green for video only, or red for audio only.C Logo button — Press this button to enable or disable the most recently selected logo slot. Press and hold the button toselect logo slot 1 through 8 using the input selection buttons (slots 9-16 are available via SIS commands only). See the IN1806 and IN1808 Series User Guide at for more information about logos.D Status LED indicators• Input signal LEDs — These eight LEDs light green for their corresponding inputs when active video content is detected on that input.• Output signal LEDs — Output LEDs 1A, 1B, and Loop light green when active video is being output, and blink amber when output video and sync are disabled.• Input HDCP LEDs — These eight LEDs light green for each input signal that is HDCP-encrypted. • Output HDCP LEDs — These three LEDs light green for an output when it is currently HDCP-encrypted.• DTP2 and DTP Input LEDs — These two LEDs light green if DTP or DTP2 power has been enabled on the corresponding input.•DTP2 and DTP Output LEDs — These Output LEDs light green if DTP or DTP2 power has been enabled on DTP output 1B.E Menu and Enter buttons — Press these buttons to access and navigate the on-screen display menu system.F Navigation buttons — Press these buttons to navigate through the on-screen display menu system or change settings.G Mic and Volume knobs and LED indicators — Rotate the Mic knob to adjust the microphone level. Rotate the Volumeknob to adjust the program or output volume level (configurable, see the IN1806 and IN1808 Series PCS Help File for more information). The eight LED indicators for each knob light according to the level being adjusted. The LEDs light in order from bottom to top to indicate steps from 1% (-99 dB) to 99% (-1 dB). The bottom LED blinks when the volume is muted. The top LED blinks when the volume is at 100% (12 dB).H IPCP Pro LED indicators — IPCP models only (see the IPCP Pro Series Setup Guide for details).Firmware UpdatesDownload firmware updates from the Extron website and upload them via the internal web pages or PCS.IN1808 Series Configuration Array To configure IN1808 Series, use the front panel controls, theon-screen display (OSD) menu, internal web pages, PCS, or SIScommands.On-screen Display (OSD) Menu SystemTo configure IN1808 Series using the OSD menu, connect a displayto either HDMI output 1A or to a DTP/XTP matrix switcher/HDBaseTcompatible device. The OSD menu consists of eight submenus accessedusing the front panel Menu or Enter button (see the example at right).Extron Product Configuration SoftwareTo configure IN1808 scalers using PCS, install the software (available onthe Extron website, ) to a PC connected to the scalervia Ethernet or front panel USB Config port. After the installation, start theprogram. For full instructions, press <F1> on the keyboard or click the ?button in the software and select Help File.Internal Web PagesTo configure the IN1808 Series using the factory-installed web pages in a web browser (see the example at right), connect the AV LAN connector (IPCP models) or LAN connector (base model) on the IN1808 to a LAN or WAN. The default IP address is 192.168.254.254.Basic SIS Command TableTo configure IN1808 Series with specific SIS commands via an RS-232, USB, or Ethernet connection, use the Extron DataViewer utility or a control system to send and receive SIS commands. The table below lists a selection of SIS commands. For a full list ofSIS commands and variables, see the IN1806 and IN1808 Series User Guide at .5668-3131-51 Rev. A02 19© 2019 Extron Electronics — All rights re served. All trademarks mentioned are the property of their respective owners. Worldwide Headquarters: Extron USA West, 1025 E. Ball Road, Anaheim, CA 92805, 800.633.9876For information on safety guidelines, regulatory compliances, EMI/EMF compatibility, accessibility, and related topics, see the Extron Safety and Regulatory Compliance Guide on the Extron website.。

PCM1808用户指南

DEM-DAI1808August2006DAPSLEU078DEM-DAI1808 User's GuideLiterature Number:SLEU078August20061Description (5)1.1Block Diagram (6)1.2Basic Connection and Operation (7)1.2.1Basic Connections and Configurations (7)1.2.2Configuration Controls (7)1.3Typical Performance and Measurement Example (12)2Schematics and Printed Circuit Boards (15)2.1DEM-DAI1808Schematics (16)2.2DEM-DAI1808Bill of Materials(BOM) (19)2.3DEM-DAI1808Printed Circuit Boards (22)SLEU078–August2006Contents3 Submit Documentation FeedbackList of Figures1-1DEM-DAI1808Block Diagram (6)1-2External Interfaces (11)2-1DEM-DAI1808Digital Section(Digital Audio Interface) (16)2-2DEM-DAI1808Regulator and Connector (17)2-3DEM-DAI1808ADC Section (17)2-4DEM-DAI1808Analog Section (18)2-5DEM-DAI1808Silkscreen (22)2-6DEM-DAI1808—Top View (23)2-7DEM-DAI1808—Bottom View (24)List of Tables1-1System Clock Source Selection (7)1-2Master/Slave Interface Mode Selection (7)1-3Interface Format Selection (8)1-4System Clock Rate Selection (8)1-5Sampling Frequency and System Clock Frequency Selection (9)1-6Analog Input Level/Path Selection (9)1-7S/PDIF Transmitter Format(Channel Status)Setting for DIT4096 (10)1-8Mode and Format Control for PCM1808 (11)4List of Figures SLEU078–August2006Submit Documentation FeedbackChapter1SLEU078–August2006The DEM-DAI1808is an evaluation board for the PCM1808,a96-kHz,24-bit PCMaudio analog-to-digital converter(ADC),with digital audio transmitter,optical andcoaxial interface,onboard multiple clock generator,–6-dB amplifier with LPF,andswitches or jumpers for mode or clock control.Related documentation includes the DIT409696-kHz Digital Audio Transmitter datasheet(literature number SBOS225)and the PLL1707,PLL1708 3.3-V Dual PLLMulticlock Generator data sheet(literature number SLES065)The DEM-DAI1808operates under5-V and±15-V analog power supplies,with1-Vrmsor2-Vrms unbalanced analog signal input.Topic PageSLEU078–August2006Description5 Submit Documentation Feedback Block Diagram1.1Block DiagramFigure1-1.DEM-DAI1808Block DiagramDescription6SLEU078–August2006Submit Documentation Feedback1.2Basic Connection and Operation1.2.1Basic Connections and Configurations1.2.2Configuration Controls1.2.2.1System Clock Source Selection1.2.2.2Master/Slave(M/S)Interface Mode Selection Basic Connection and Operation•Connect the5-V and±15-V power supplies to V CC,±AV CC,and GND on CN051–CN055.The±15-V power supplies only are required for2-Vrms input.•Connect the SPDIF output to CN003(coaxial)or U001(optical).•Select the system clock source from256/512fs or384fs generated by on-board clock generator (PLL1707),or external clock input connector(CN001)using JP001,and ensure the presence ofsystem clock on it.•Set the interface mode(master or slave)using SW002M/S for board and SW004MD1/0for PCM1808.•Set the interface format(LJ-24or I2S-24)using SW002FMT0for board and SW004FMT for PCM1808.•Select the combination of sampling frequency(16kHz to96kHz)and system clock rate(256fs, 384fs,512fs),using SW002CLK1/0,SR,FS2/1for board and SW004for PCM1808.•Set the channel status for DIT4096if required.(It is not required for PCM1808evaluation.)The system clock(master clock)source for the evaluation module(EVM)including the PCM1808,which is associated with sampling frequency,can be selectable by the JP001setting as follows.Table1-1.System Clock Source SelectionJP001DESCRIPTION256Internal,256/512times of sampling frequency(default)384Internal,384times of sampling frequencyEXT External,TTL interface level,up to25MHzThe audio interface mode of the PCM1808and EVM can be selectable as follows.In slave mode,audio interface clock,BCK,and LRCK are generated in the DIT4096and supplied to the PCM1808through a buffer.In master mode,they are generated in the PCM1808and supplied to theDIT4096.Mode control to the PCM1808can be performed by the SW004setting.Table1-2.Master/Slave Interface Mode SelectionSW004,MD1/0(1)SW002,M/S(1)DESCRIPTIONMD1MD0OFF(High)ON(Low)ON(Low)Slave modeON(Low)ON(Low)OFF(High)Master mode,512fs(default)ON(Low)OFF(High)ON(Low)Master mode,384fsON(Low)OFF(High)OFF(High)Master mode,256fs(1)Other inconsistent combinations between SW002M/S and SW004MD1/0selection are notavailable.SLEU078–August2006Description7 Submit Documentation Feedback1.2.2.3Interface Format Selection1.2.2.4Sampling Frequency and System Clock Frequency SelectionBasic Connection and OperationThe audio interface format of the PCM1808and EVM can be changed as follows.Table 1-3.Interface Format SelectionSW002,FMT0(1)SW004,FMT (1)DESCRIPTIONOFF (High)ON (Low)I 2S 24bits (default)ON (Low)OFF (High)Left-justified 24bits(1)Other inconsistent combinations between SW002FMT0and SW004FMT selection are not available.The sampling frequency and the system clock frequency for the PCM1808and EVM can be selectable as shown in Table 1-4and Table 1-5by setting JP001,SW002,and SW004.Sampling frequencies of 16kHz to 96of 256fs,384fs,and 512fs are available for the EVM.The settings of JP001,CLK1/0of SW002,and MD1/0of SW004(see Table 1-4)determine the system clock rate.The settings of SR and FS2/1of SW002(see Table 1-5)sampling clock and system clock frequencies.The possible combinations of sampling clock and system clock frequencies appear in the right-most column of Table 1-5.Table 1-4.System Clock Rate SelectionSW002(2)SW004(3)JP001(1)SYSTEM CLOCK RATE CLK1CLK0MD1MD0–ON/Low ON/Low ––Reserved 256ON/Low OFF/High OFF/High OFF/High 256fs 384OFF/High ON/Low OFF/High ON/Low 384fs 256OFF/HighOFF/HighON/LowOFF/High512fs (default)(1)Other inconsistent combinations between SW002CLK1/0and SW004MD1/0selection are not available.(2)Select the DIT4096master clock rate.(3)Select the PCM1808system clock rate if master-mode operation of the PCM1808is required.If slave-mode operation of the PCM1808is required,the combination of MD1=ON/Low and MD0=ON/Low is available for all three rates:256fs,384fs,and 512fs.8DescriptionSLEU078–August 2006Submit Documentation Feedback1.2.2.5Analog Input Level/Path Selection 1.2.2.6Reset Control Basic Connection and OperationTable1-5.Sampling Frequency and System Clock Frequency SelectionSW002(1)FREQUENCIESSAMPLING CLOCK(kHz)/SYSTEM CLOCK(MHz) SR FS2FS1256-fs OperationOFF/Low ON/High OFF/Low32/8.192OFF/Low OFF/Low ON/High44.1/11.2896OFF/Low OFF/Low OFF/Low48/12.288ON/High ON/High OFF/Low64/16.384ON/High OFF/Low ON/High88.2/22.5792ON/High OFF/Low OFF/Low96/24.576 384-fs OperationOFF/Low ON/High OFF/Low32/12.288OFF/Low OFF/Low ON/High44.1/16.9344OFF/Low OFF/Low OFF/Low48/18.432ON/High ON/High OFF/Low64/24.576ON/High OFF/Low ON/High88.2/33.8688(2)ON/High OFF/Low OFF/Low96/36.864(2) 512-fs OperationOFF/Low ON/High OFF/Low16/8.192(3)OFF/Low OFF/Low ON/High22.05/11.2896OFF/Low OFF/Low OFF/Low24/12.288ON/High ON/High OFF/Low32/16.384ON/High OFF/Low ON/High44.1/22.5792ON/High OFF/Low OFF/Low48/24.576(default)(1)Select the clock output frequency of the PLL1707SCKOx;the combination of FS2=ON/High and FS1=ON/High is reserved.(2)Not applicable through the SPDIF interface due to a limitation of the DIT4096.Frequencies are applicable for PCM directinterface between the PCM1808and externals.(3)May not be applicable through the SPDIF interface due to interface receiver limitations of digital-domain measurementequipment,like Audio Precision.This frequency is applicable for PCM direct interface between the PCM1808and externals.The DEM-DAI1808supports1-Vrms and2-Vrms input for full scale of analog input signal by the JP101, JP102setting.For2-Vrms input selection,an onboard100-kHz LPF and–6-dB attenuator is applied on the input signal.The default setting is2-Vrms input.Table1-6.Analog Input Level/Path SelectionJP101,JP102DESCRIPTION1Vrms1-Vrms full-scale analog input is fed to ADC directly.2Vrms2-Vrms full-scale analog input is fed to ADC through100kHz LPF and–6-dB attenuator(default).The DEM-DAI1808supports Reset Control for DIT4096by SW003.SLEU078–August2006Description9 Submit Documentation Feedback Basic Connection and Operation1.2.2.7S/PDIF Transmitter Format(Channel Status)Setting for DIT4096The extended configurations of the digital audio interface transmitter,DIT4096,and the channel status of SPDIF can be set using the DIP switches,SW001.The individual switch settings and their functions are described in Table1-7.For general evaluation or test of function and performance of the PCM1808,the change from default setting of this SW001is not needed.This is provided for evaluation of the DIT4096 function,mainly related to channel status information.Table1-7.S/PDIF Transmitter Format(Channel Status)Setting for DIT4096 SW001ON/OFF DESCRIPTIONChannel status data bits are set in serial fashion at the COPY/C input with clock input at the SYNC Off(High)input.CSSOn(Low)COPY/C,L,/AUDIO,and/EMPH inputs are used to set associated channel status data bits(default).Copy and generation status information with L input for CSS=Low,channel status data bit=1for Off(High)CSS=HighCOPY/C(1)Copy and generation status information with L input for CSS=Low,channel status data bit=0for On(Low)CSS=High(default)Off(High)User data input=1UOn(Low)User data input=0(default)Off(High)Validity data input=1VOn(Low)Validity data input=0(default)Off(High)Copy and generation status with COPY/C for CSS=LowL(1)On(Low)Copy and generation status with COPY/C for CSS=Low(default)Off(High)Audio data valid control input,not linear PCM/AUDIOOn(Low)Audio data valid control input,linear PCM(default)Off(High)Pre-emphasis status input,not applied pre-emphasis(default)/EMPHOn(Low)Pre-emphasis status input,applied pre-emphasisOff(High)BLS mode control input,BLS is an output(default)BLSMOn(Low)BLS mode control input,BLS is an inputOff(High)Block start input for BLSM=Low,output for BLSM=High(default)BLSOn(Low)Not block start(1)Copy and generation status information for CSS=LowCOPY/C L COPY AND GENERATION STATUSOn(Low)On(Low)Consumer mode,PRO=0,COPY=0,L=0(default)On(Low)Off(High)Consumer mode,PRO=0,COPY=0,L=1Off(High)On(Low)Consumer mode,PRO=0,COPY=1,L=0Off(High)Off(High)Professional mode,PRO=1,No copy protectionDescription10SLEU078–August2006Submit Documentation Feedback1.2.2.8Audio Interface Mode and Format Control for PCM18081.2.2.9DAI Bridge and Control BridgeSelectionSCLK BCK LRCK DATAGND SCLK BCK LRCK DATAGND DefaultInterface With DIT4096ExternalInterface With External Device/EquipmentBasic Connection and OperationThe audio interface mode and format control for the PCM1808can be performed by the SW004setting.The summary of the PCM1808pin configuration is given in Table 1-8.Table 1-8.Mode and Format Control for PCM1808MD1(#11)MD0(#10)DESCRIPTIONLow Low Slave modeLow High Master mode 512fs (default)High Low Master mode 384fs HighHighMaster mode 256fsFMT (#12)DESCRIPTIONLow I 2S 24bits (default)HighLeft-justified 24bitsThe DEM-DAI1808supports flexible PCM audio interface through a DAI bridge,so that the PCM1808can interface with external devices or equipment in place of an internal buffer and the DIT4096.Interfacing with externals can be done by changing JP052and JP053connections for SCLK,BCK,LRCK,DATA,and GND as shown in Figure 1-2.The DEM-DAI1808also supports flexible mode and format control to the PCM1808by redirection of the control port through the header setting of the control bridge,JP054.The default setting is interfaced with internal DIT4096and DIP switch,SW004.Figure 1-2.External InterfacesSLEU078–August 2006Description 11Submit Documentation Feedback1.3Typical Performance and Measurement ExamplePCM1808,Master,48 kHz/512 fs,–0.5 dB2020k501002005001k 2k 5k 10k Hzd B F STypical Performance and Measurement ExampleTypical performance of the DEM-DAI1808for default condition is as follows,and FFT results for full-scale input and –60-dB input are shown.THD+N @48kHz/512fs:–93.5dB D.Range @48kHz/512fs:99.3dBSNR @48kHz/512fs:99.3dB12DescriptionSLEU078–August 2006Submit Documentation FeedbackPCM1808,Master,48 kHz/512 fs,–60 dB2020k501002005001k 2k 5k 10k Hzd B F STypical Performance and Measurement ExampleSLEU078–August 2006Description 13Submit Documentation Feedback Typical Performance and Measurement Example14SLEU078–August2006 DescriptionSubmit Documentation FeedbackChapter2SLEU078–August2006This chapter presents the DEM-DAI1808schematics,Bill of Materials(BOM),andprinted circuit boards.Topic PageSLEU078–August2006Schematics and Printed Circuit Boards15 Submit Documentation Feedback DEM-DAI1808Schematics2.1DEM-DAI1808SchematicsFigure2-1.DEM-DAI1808Digital Section(Digital Audio Interface)16Schematics and Printed Circuit Boards SLEU078–August2006Submit Documentation FeedbackCC -CC +CN051banana jack (orange)CN053banana jack (blue)jack CN052banana jack (gray)CN056B2P-VHAGNDAGND DGNDDEM-DAI1808SchematicsFigure 2-2.DEM-DAI1808Regulator and ConnectorFigure 2-3.DEM-DAI1808ADC SectionSLEU078–August 2006Schematics and Printed Circuit Boards 17Submit Documentation Feedback DEM-DAI1808SchematicsFigure2-4.DEM-DAI1808Analog SectionSchematics and Printed Circuit Boards18SLEU078–August2006Submit Documentation FeedbackDEM-DAI1808Bill of Materials(BOM) 2.2DEM-DAI1808Bill of Materials(BOM)REF.PART NAME SPEC-1SPEC-2PART NO.SUPPLIER REMARKS NO.Parts List1/4(Digital Portion)C001Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC002Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC003Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC004Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC005Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC006Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC007Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC008Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC009Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC010Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC011Electrolytic Capacitor100uF/16V ROA-16V101M ELNA Unmounted C012Ceramic Capacitor0.1uF/25V PRE132F104Z50Murata Unmounted C013Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC014Ceramic Capacitor15pF/50V PRE131CH150J50MurataC015Ceramic Capacitor15pF/50V PRE131CH150J50MurataC016Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC017Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC018Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataR001Metal Film Resistor1/8W,47k JR002Metal Film Resistor1/8W,470JR003Metal Film Resistor1/8W,75JR004Metal Film Resistor1/8W,75JR005Metal Film Resistor1/8W,360JR006Metal Film Resistor1/8W,91JRA001Resistor Array47k×9JRA002Resistor Array47k×4JRA003Resistor Array47k×4JL001Micro Inductor47uH J EL0606SKI-470J TDKFIL001Filter Unmounted D001Diode1S133ROHMD002Diode1S133ROHMD003Diode1S133ROHMU001Optical Transmitter TOTX-179P ToshibaU002SPDIF Transmitter DIT4096PW TIU003Buffer SN74LV244A TIU004Buffer SN74LV244A TIU005PLL Clock Generator PLL1707DB TIU006One Gate Device Inverter SN74LVC1G04DBV TITR001Pulse Transformer DA-02JPCX001Crystal Resonator27MHz±50ppm HC-49/U-S,27MHz KinsekiSW001DIP Switch DSS110Fujisoku DITSW002DIP Switch DSS108Fujisoku DIT&PLLSLEU078–August2006Schematics and Printed Circuit Boards19 Submit Documentation Feedback DEM-DAI1808Bill of Materials(BOM)REF.PART NAME SPEC-1SPEC-2PART NO.SUPPLIER REMARKS NO.SW003Push Switch FP1F-2M Fujisoku Reset DITSW004DIP Switch DSS104Fujisoku Mode DUTJP0016-Pin Connector FFC-6BMEP1Honda256/384/ExtCN001BNC Connector BNC-LR-PC4Right AngleCN00248-Pin Connector FFC-48BMEP1Honda UnmountedCN003RCA Connector Yellow LPR6520-0804SMKCN004Connector57LE-40360-7700DDK UnmountedCN005Test Terminal LC-2-G Mac8GNDShort Plug×1DIC-130Honda JP001 Parts List2/4(Power Portion)C051Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC052Electrolytic Capacitor100uF/16V ROA-16V101M ELNAC053Electrolytic Capacitor100uF/16V ROA-16V101M ELNAC054Electrolytic Capacitor100uF/16V ROA-16V101M ELNAC055Ceramic Capacitor0.1uF/25V PRE132F104Z50MurataC056Electrolytic Capacitor10uF/16V R3A-16V100M ELNAU051 3.3-V Regulator REG1117-3.3TIJP0512-Pin Connector FFC-2AMEP1HondaCN051Banana Jack OrangeCN052Banana Jack GrayCN053Banana Jack BlueCN054Banana Jack RedCN055Banana Jack BlackCN056VH Connector B2P-VH Nihon-Accyaku-TanshiShort Plug×1DIC-130Honda JP051 Parts List3/4(DUT Portion)C061Ceramic Capacitor0.1uF/25V1608type GRM39F104Z25PT Murata Chip typeC062Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC063Ceramic Capacitor0.1uF/25V1608type GRM39F104Z25PT Murata Chip typeC064Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC065Ceramic Capacitor0.1uF/25V1608type GRM39F104Z25PT Murata Chip typeC066Electrolytic Capacitor10uF/16V R3A-16V100M ELNAR051Metal Film Resistor1/8W,100J Chip typeR052Metal Film Resistor1/8W,100J Chip typeR053Metal Film Resistor1/8W,100J Chip typeR054Metal Film Resistor1/8W,100J Chip typeR055Metal Film Resistor1/8W,100J Chip typeR056Metal Film Resistor1/8W,100J Chip typeR057Metal Film Resistor1/8W,100J Chip typeU052A/D Converter(DUT)PCM1808DB TIJP05212-Pin Connector FFC-12BMEP1HondaJP05312-Pin Connector FFC-12BMEP1HondaJP05410-Pin Connector FFC-10BMEP1Honda20Schematics and Printed Circuit Boards SLEU078–August2006Submit Documentation FeedbackDEM-DAI1808Bill of Materials(BOM)REF.PART NAME SPEC-1SPEC-2PART NO.SUPPLIER REMARKS NO.CN057Test Terminal LC-2-G Mac8GNDShort Plug×10DIC-130Honda JP052,3,4 Parts List4/4(Analog Portion)C101Electrolytic Capacitor10uF/16V ROA-16V100M ELNAC102Electrolytic Capacitor10uF/16V ROA-16V100M ELNAC103Film Capacitor1800pF J APSF0100J182NisseiC104Film Capacitor1800pF J APSF0100J182NisseiC105Film Capacitor330pF J APSF0100J331NisseiC106Film Capacitor330pF J APSF0100J331NisseiC107Film Capacitor100pF J APSF0100J101NisseiC108Film Capacitor100pF J APSF0100J101NisseiC109Electrolytic Capacitor10uF/16V ROA-16V100M ELNAC110Electrolytic Capacitor10uF/16V ROA-16V100M ELNAC111Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC112Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC113Electrolytic Capacitor10uF/16V R3A-16V100M ELNAC114Electrolytic Capacitor10uF/16V R3A-16V100M ELNAR101Metal Film Resistor1/8W,2.4k FR102Metal Film Resistor1/8W,2.4k FR103Metal Film Resistor1/8W,3.3k FR104Metal Film Resistor1/8W,3.3k FR105Metal Film Resistor1/8W,1.2k FR106Metal Film Resistor1/8W,1.2k FR107Metal Film Resistor1/8W,4.7k FR108Metal Film Resistor1/8W,4.7k FR109Metal Film Resistor1/8W,4.7k FR110Metal Film Resistor1/8W,4.7k FR111Metal Film Resistor1/8W,47k FR112Metal Film Resistor1/8W,47k FU101Dual Op Amp DIP OPA2134PA TIU102Dual Op Amp DIP OPA2134PA TIJP1014-Pin Connector FFC-4BMEP1HondaJP1024-Pin Connector FFC-4BMEP1HondaCN101RCA Connector White LPR6520-0803SMKCN102RCA Connector Red LPR6520-0802SMKCN103Test Terminal LC-2-G Mac8GNDCN104Test Terminal LC-2-G Mac8GNDIC Socket DIP8pin U101IC Socket DIP8pin U102Short Plug×2DIC-130Honda JP101,102DEM-DAI1808Printed Circuit Boards2.3DEM-DAI1808Printed Circuit BoardsFigure2-5.DEM-DAI1808Silkscreen22Schematics and Printed Circuit Boards SLEU078–August2006DEM-DAI1808Printed Circuit BoardsFigure2-6.DEM-DAI1808—Top ViewDEM-DAI1808Printed Circuit BoardsFigure2-7.DEM-DAI1808—Bottom View24SLEU078–August2006 Schematics and Printed Circuit BoardsDEM-DAI1808Printed Circuit BoardsEVM TERMS AND CONDITIONST exas Instruments (TI) provides the enclosed Evaluation Module and related material (EVM) to you, the user, (you or user) SUBJECTTO the terms and conditions set forth below. By accepting and using the EVM, you are indicating that you have read, understand andagree to be bound by these terms and conditions. IF YOU DO NOT AGREE TO BE BOUND BY THESE TERMS ANDCONDITIONS, YOU MUST RETURN THE EVM AND NOT USE IT.This EVM is provided to you by TI and is intended for your INTERNAL ENGINEERING DEVELOPMENT OR EVALUATIONPURPOSES ONLY. It is provided “AS IS” and “WITH ALL FAULTS.” It is not considered by TI to be fit for commercial use. As such,the EVM may be incomplete in terms of required design−, marketing−, and/or manufacturing−related protective considerations,including product safety measures typically found in the end product. As a prototype, the EVM does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may not meet the technical requirements of the directive.Should this EVM not meet the specifications indicated in the EVM User’s Guide, it may be returned within 30 days from the date ofdelivery for a full refund of any amount paid by user for the EVM, which user agrees shall be user’s sole and exclusive remedy. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY TI TO USER, AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESSFOR ANY PARTICULAR PURPOSE OR NON−INFRINGEMENT.TI shall have no obligation to defend any claim arising from the EVM, including but not limited to claims that the EVM infringes thirdparty intellectual property. Further, TI shall have no liability to user for any costs, losses or damages resulting from any suchclaims. User shall indemnify and hold TI harmless against any damages, liabilities or costs resulting from any claim, suit orproceeding arising from user’s handling or use of the EVM, including but not limited to, (I) claims that the EVM infringes a third party’s intellectual property, and (ii) claims arising from the user’s use or handling of the EVM. TI shall have no responsibility to defend anysuch claim, suit or proceeding.User assumes all responsibility and liability for proper and safe handling and use of the EVM and the evaluation of the EVM. TI shallhave no liability for any costs, losses or damages resulting from the use or handling of the EVM. User acknowledges that the EVMmay not be regulatory compliant or agency certified (FCC, UL, CE, etc.). Due to the open construction of the EVM it is the user’s responsibility to take any and all appropriate precautions with regard to electrostatic discharge.EXCEPT TO THE EXTENT OF THE USER’S INDEMNITY OBLIGATIONS SET FORTH ABOVE, NEITHER PARTY SHALL BELIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES WHETHER TI IS NOTIFIED OF THE POSSIBILITY OR NOT.TI currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive.TI assumes no liability for applications assistance, customer product design, software performance, or infringement ofpatents or services described herein.User agrees to read the EVM User’s Guide and, specifically, the EVM warnings and Restrictions notice in the EVM User’s Guide priorto handling the EVM and the product. This notice contains important safety information about temperatures and voltages.It is user’s responsibility to ensure that persons handling the EVM and the product have electronics training and observe goodlaboratory practice standards.By providing user with this EVM, product and services, TI is NOT granting user any license in any patent or other intellectualproperty right.Mailing Address: T exas Instruments, Post Office Box 655303, Dallas, T exas 75265Copyright © 2006, T exas Instruments IncorporatedDEM-DAI1808Printed Circuit BoardsEVM WARNINGS AND RESTRICTIONSIt is important to operate this EVM within the input voltage range and the output voltage range that is less than 120% of thecorresponding nominal voltage ranges described in the EVM user’s guide.Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there arequestions concerning the input range, please contact a TI field representative prior to connecting the input power.Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to theEVM. Please consult the EVM User’s Guide prior to connecting any load to the EVM output. If there is uncertainty as to the loadspecification, please contact a TI field representative.During normal operation, some circuit components may have case temperatures greater than 50°C. The EVM is designed tooperate properly with certain components above 50°C as long as the input and output ranges are maintained. These componentsinclude but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types ofdevices can be identified using the EVM schematic located in the EVM User’s Guide. When placing measurement probes nearthese devices during operation, please be aware that these devices may be very warm to the touch.Mailing Address: T exas Instruments, Post Office Box 655303, Dallas, T exas 75265Copyright 2006, T exas Instruments Incorporated26SLEU078–August2006 Schematics and Printed Circuit BoardsIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third−party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:ProductsAmplifiersData Converters DSPInterfaceLogicPower Mgmt MicrocontrollersApplicationsAudioAutomotiveBroadbandDigital ControlMilitaryOptical NetworkingSecurityTelephonyVideo & ImagingWireless/audio/automotive/broadband/digitalcontrol/military/opticalnetwork/security/telephony/video/wirelessMailing Address: T exas Instruments, Post Office Box 655303, Dallas, T exas 75265Copyright © 2006, T exas Instruments IncorporatedDEM-DAI1808Printed Circuit Boards。

pcm1808