一种NANDFlash控制器验证平台的设计

NandFlash+ECC原理和实现

c >>= 2; a >>= 1; } c = 0x80; for (i=0; i<4; i++) { if (d2 & c)

add |= a; c >>= 2; a >>= 1; } bit = 0; b = 0x04; c = 0x80; for (i=0; i<3; i++) { if (d3 & c)

/* Initialize variables */ a = b = 0x80; tmp1 = tmp2 = 0;

/* Calculate first ECC byte */

for (i = 0; i < 4; i++) {

if (reg3 & a) tmp1 |= b;

b >>= 1; if (reg2 & a)

bit |= b; c >>= 2; b >>= 1; } b = 0x01; a = dat[add]; a ^= (b << bit); dat[add] = a; return 1; } else { i = 0; while (d1) { if (d1 & 0x01)

NAND FLASH ECC 校验原理与实现

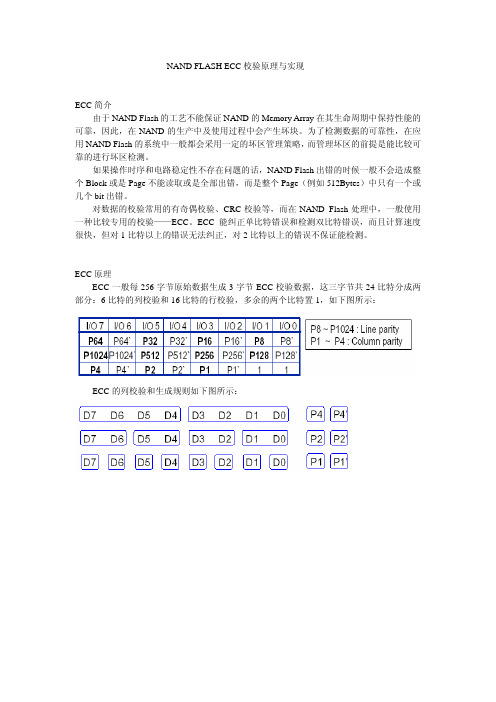

ECC 简介 由于 NAND Flash 的工艺不能保证 NAND 的 Memory Array 在其生命周期中保持性能的

可靠,因此,在 NAND 的生产中及使用过程中会产生坏块。为了检测数据的可靠性,在应 用 NAND Flash 的系统中一般都会采用一定的坏区管理策略,而管理坏区的前提是能比较可 靠的进行坏区检测。

基于FPGA的星载NANDFLASH控制器的设计

Abstract: In order to achieve efficient data storage in orbit satellite,this paper designs a NAND FLASH controller based on FPGA. The controller is compatible with commonly used asynchronous NAND FLASH,support for multiple NAND FLASH array ;support NAND FLASH operation timeout anomaly detection;support FLASH reset,read data,program,block erase,read ID and other commonly used functions. Select AHB bus,an efficient on- chip bus proposed by ARM Company. Design the AHB interface module and mount the FPGA module to the AHB bus. Through the Cortex-M3,transfer related commands and data to the underlying FPGA and achieve CPU + FPGA architecture. By simulation and board debugging,the design performance is stable,reducing power consumption,reaching the data storage rate of millisecond requirements. Key words: NAND FLASH;controller;AHB BUS;FPGA

基才AMBAAPB总线NandFlash控制器的设计研究

ta h e i n c n s t f et n q ie n f n f s . h t ed sg a ai y t mi g r u r me t d a h t s h i e o Na l

Ke r s Na d ls o tol r y wo d : n F a h c n r l ;AMB AP u ;smu a in;Na d l h t n e A B b s i l t o n F a mi g s i

AB F 总线 ——— 寄存器

1 N n F ah简 介 a d ls

关 键 词 : ad 1 h控 制 器 ; MB P N n Fa s A A A B总 线 ; 真 ; a d ah时 序 仿 N nF s l

中图分类号 : N 9 T 42 文献标识码 : A 文 章 编 号 :1 7 - 2 6 2 1 ) 0 0 6 — 3 6 4 6 3 (0 1 2 — 1 6 0

王 洋 ,刘 卫 东 ,于 岗

(. 1中国 海 洋 大 学 信 息科 学 与 工 程 学 院 , 东 青 岛 2 1 ; . 信 电 器股 份 有 限公 司 山 东 青 岛 2 6 7 ) 山  ̄ 0 2海 6 0 1 摘 要 : 绍 了基 于 A A A B 总线 N n Fah控 制 器 的 设 计 . 先 简单 介 绍 了 N n Fah的 一 些 特 点 , 介 MB P ad l 8 首 ad l s 然后 详 细 介 绍

可信芯片验证平台的设计与实现

可信芯片验证平台的设计与实现随着信息技术的快速发展,芯片在现代社会中的应用越来越广泛。

然而,由于芯片内部的复杂电路结构和功能的多样化,芯片在设计和制造过程中往往容易受到各种攻击,如仿真、非法复制和篡改等。

因此,为了确保芯片的可信性和安全性,可信芯片验证平台的设计和实现变得尤为重要。

可信芯片验证平台是一种基于硬件和软件的综合平台,用于验证芯片的安全性和可信度。

该平台由硬件部分和软件部分组成,各具特定功能。

硬件部分是平台的核心,主要包括多种检测电路、信号处理电路和接口电路等。

检测电路用于检测芯片在运行过程中可能存在的安全隐患,如电压异常、电流波动等。

信号处理电路负责对从芯片输出的信号进行分析和处理,以判断芯片是否受到攻击。

接口电路则用于与外部设备进行连接和数据传输,方便后续的数据处理和分析。

软件部分是平台的灵魂,主要包括验证算法、数据处理算法和用户界面等。

验证算法是核心部分,用于分析和判断芯片是否符合安全性要求。

数据处理算法负责对从硬件部分采集到的数据进行处理和分析,提取有用信息,并生成相应的报告。

用户界面则提供了一个友好的操作界面,方便用户进行参数设置、数据查看和结果分析等操作。

可信芯片验证平台的实现需要经过以下几个步骤:首先,确定验证平台的功能和性能要求,明确验证的目标和指标。

其次,设计硬件部分,选择合适的电路和器件,并进行布局和连接。

然后,编写软件部分的验证算法和数据处理算法,并进行测试和调试。

最后,将硬件和软件部分进行整合,进行系统测试和性能评估。

通过可信芯片验证平台的设计和实现,可以有效提高芯片的可信度和安全性。

验证平台可以对芯片进行全面、细致的检测和分析,及时发现并阻止各种安全威胁。

同时,验证平台还可以为芯片的设计和制造提供重要的参考和指导,指出潜在的安全隐患和改进方向。

总之,可信芯片验证平台的设计与实现是保障芯片可信度和安全性的重要手段。

这一平台的设计需要充分考虑硬件和软件的相互配合和协同工作,确保整个验证过程的准确性和有效性。

NAND FLASH在S3C2440A平台的驱动设计

序可 以直接 在 f s l h闪存 内运行 , 必 再 把代 码读 到 系 a 不

统 R M 中。N R F A H 的传 输 效 率很 高 , 1 A O L S 在 MB~ 4 MB的 小容量 时 具有 很 高 的成 本效 益 , 是 写入 和擦 但 除速 度慢 , 大大 影 响了 它 的性 能 。 N N L S 结 构 A DFA H

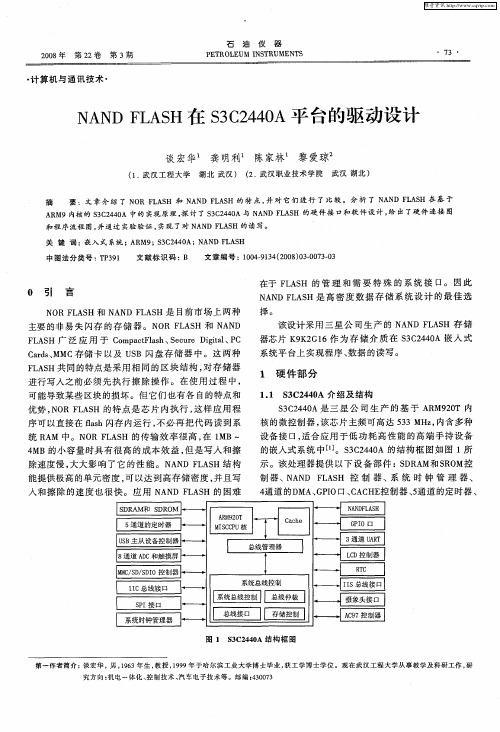

A M9内核 的 ¥ C 4 0 中 的 实 现 原 理 , 讨 了 ¥ C 40 与 N N L S 的硬 件 接 口和 软 件 设 计 , 出了硬 件 连 接 图 R 3 24A 探 324A A DFA H 给 和程 序 流 程 图 , 通过 实验 验证 , 并 实现 了对 N N L S 的读 写 。 A DF A H

设备 接 口 , 合应 用 于嵌入 式系 统 中[ 。s C 4 0 的结 构 框 图如 图 1所 3 24 A

示 。该 处理 器提 供 以下 设 备 部 件 : D A S R M和 S O R M控

制 器 、N N F A H 控 制 器 、系 统 时 钟 管 理 器 、 A D LS 4 通道 的D MA、 P0口、 A H 控 制器 、 通道 的定时 器 、 G1 CCE 5

F A H 广 泛 应 用 于 C m att h S cr i t 、 C LS o p c a 、 eue D g a P F s il

该设计 采用 三 星公 司生 产 的 N N L S 存 储 A DFA H 器芯 片 K K G 6作 为 存 储 介 质 在 ¥ C 4 0 92 1 3 2 4 A嵌 入 式

能提 供极高 的单元 密 度 , 以达 到高存 储 密度 , 可 并且 写

入和 擦 除 的速 度 也很 快 。 应 用 N N L S 的 困难 A DFA H

基于Xilinx FPGA的SPI Flash控制器设计与验证

备 , FG 使 P A一方面 与电脑 串 口通信获得数据 , 另一方面对 S IFah进行控制 , P ls 这样就完成了 F G P A配置数据 的控制 和存储 。

关 键词 : 可编程逻辑门阵列; 串行接口F s;el D ;i lhV ro H LIm仿真 a ig s

中图分 类号 : P 3 . T 3 21

( oi E e et , L gc lm n) 3 2个 1 bt BokR M模 块 , 8k ye的 lc A l 6个 1  ̄ 8b 嵌入式乘 法器 , 8 1 i t 2个锁 相环 ( L ) 4 PL和 个时钟管 理模 块 ( C 。在这 款 14针 tg封 装 的 D M) 4 q F G 中. PA 用户可用 I0为 12个 _ , / 0 3 可以满足本 系统 ] 的需求 。 Fah芯 片采 用 的 配置 芯 片 是 Wi o d公 司 的 l s n n b

关珊 珊 . 洁 敏 周

( 南京航空航天大学 民航学院 , 南京 2 0 1 ) 10 6

摘 要 : 基于 Xlx P A的SI lh i G i F n P a 控制器实现了一种在线配置Fa 的方法。由于 F s 芯片本身功能指令较多, Fs lh s lh a 使得对

它进行直接操作变得非常 困难 , 而利用 F G P A丰富的逻辑资源以及 产生精确 时序 的能力 , F G 以 P A为主设备 ,P l h为从设 SI a Fs

( il v t nClg ,a n n esyo eoats& At n ui ,aj g20 1 ) Cv i i o eeN g U irt iA a o l v i fA rn ui c s oatsN ni 10 6 r c n

Ab t a t S ls o tol rb s d o ln s r c : PIF a h c n r l a e n Xi x FPGA u sfr r id o n—i e c n iu a in meh d o l s e i p t o wa d a kn fo ln o fg r to to fF a h. Th l s h p i ef h s to mo e f cin i sr c in h tma e is ee t o e ain b c me v r d岱 c t b t e F a h c i t l a o r un to n tu t s t a k t d r c p r to e o e y i ul. u s o F PGA c u is rc o i e o r e n r d c sa c r t i n b lt . GA a e u e s ma t re u p n o c p e ih l gc r s u c s a d p o u e c u ae tmi g a iiy FP c n b s d a se q i me t a d S l s s sa e. PGA o n c si e iswih c mp trf rc mmun c to a a a q iiin a d c n r l h n PIF a h a l v F c n e t n s re t o u e o o iain d t c u sto n o to st e S l s n oh rh n h ti GA o fg r t n frc n r la d so a e h s b e mp e n e . PIF a h i t e a d t a t FP s c n u ai o o to n tr g a e n i lme t d i o Ke r s: GA; PIF a h; rlg HDL;i l t n y wo d FP S l s Ve io smu a i o

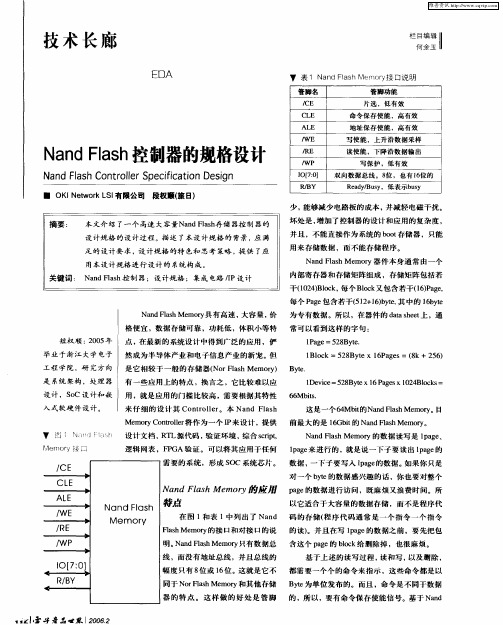

NandFlash控制器的规格设计

内部寄存器和 存储 矩阵组成 ,存储矩阵包括若

干 (0 4Bo k 每 个 Bo k 包 含 若 干(6P g, 12 )lc , l 又 c 1)ae 每 个 P g 包 含若 干 (1+ 6bt 其 中的 1b t ae 5 2 1)ye , 6ye Nad s moy 有 高速 , 容 量 , n h Ha Me r 具 大 价 为 专 有 数 据 。所 以 ,在 器件 的 dtset ,通 a e上 ah 格 便 宜 ,数 据 存 储 可 靠 ,功 耗 低 ,体 积 小 等 特 常 可 以 看 到这 样 的 字 句 :

含这 个 pg 的 bok 删除 掉 ,也 很 麻 烦 。 ae l 给 c

基 于上 述 的 读 写 过 程 , 和 写 , 读 以及 删除 ,

幅 度 只 有 8 或 1 位 。 就 是 它不 都需 要一 个 个 的 命 令 来 指 示 ,这 些命 令 都 是 以 位 6 这 同于 N r ahMe o 和其 他 存储 B t为单 位发 布 的 。而且 ,命 令 是 不 同 于数 据 oF s l mr y ye

Me o o t lr 作 为 一个 I 来设 计 ,提 供 前 最 大 的 是 1G i的 N n ah mo 。 m r C n ol 将 y r e I ) 6 bt adF s l Me r y

V 1 Na 】 Ⅲ h

设计文档 , T R L源 代 码 , 证 环境 , 合 sr t 验 综 ci , p

短 权 顺 :2 0 o 5年

点 ,在最 新 的 系统 设计 中得 到 广 泛 的 应 用 ,俨

1 g Pa e= 52 8Byt e.

毕 业 于浙 江 大 学 电子 然 成 为 半 导 体 产 业和 电子 信 息 产 业 的 新 宠 。但

Nandflash中的ECC原理及实现

Nandflash中的ECC原理及实现ECC的全称是Error Checking and Correction,是一种用于Nand的差错检测和修正算法。

如果操作时序和电路稳定性不存在问题的话,NAND Flash出错的时候一般不会造成整个Block或是Page不能读取或是全部出错,而是整个Page(例如512Bytes)中只有一个或几个bit出错。

ECC能纠正1个比特错误和检测2个比特错误,而且计算速度很快,但对1比特以上的错误无法纠正,对2比特以上的错误不保证能检测。

校验码生成算法:ECC校验每次对256字节的数据进行操作,包含列校验和行校验。

对每个待校验的Bit位求异或,若结果为0,则表明含有偶数个1;若结果为1,则表明含有奇数个1。

列校验规则如表1所示。

256字节数据形成256行、8列的矩阵,矩阵每个元素表示一个Bit位。

screen.width*0.7) {this.resized=true; this.width=screen.width*0.7; this.alt='Click here to open new window\nCTRL+Mouse wheel to zoom in/out';}" border=0>其中CP0 ~ CP5 为六个Bit位,表示Column Parity(列极性),CP0为第0、2、4、6列的极性,CP1为第1、3、5、7列的极性,CP2为第0、1、4、5列的极性,CP3为第2、3、6、7列的极性,CP4为第0、1、2、3列的极性,CP5为第4、5、6、7列的极性。

用公式表示就是:CP0=Bit0^Bit2^Bit4^Bit6,表示第0列内部256个Bit位异或之后再跟第2列256个Bit位异或,再跟第4列、第6列的每个Bit位异或,这样,CP0其实是256*4=1024个Bit位异或的结果。

CP1 ~ CP5 依此类推。

NANDFLASHECC校验原理与实现

NANDFLASHECC校验原理与实现NAND闪存(NAND Flash)是一种非易失性存储设备,常见于各种电子设备中,如手机、平板电脑和固态硬盘等。

由于其高集成度和大容量的特性,NAND闪存已成为主流存储介质之一、然而,由于各种原因(如电压波动、位反转和噪声等),在数据传输过程中可能会出现错误。

为了确保数据的可靠性和完整性,NAND闪存通常使用纠错码(ECC)进行校验和纠正。

ECC校验原理:ECC校验是一种基于算法的校验方法,通过对数据进行编码和校验位的添加,以检测和纠正传输过程中的错误。

在NAND闪存中,常用的ECC算法包括BCH(Bose-Chaudhuri-Hocquenghem)和RS(Reed-Solomon)等。

BCH编码:BCH编码是一种强大的纠错编码方法,可以用于检测和纠正多个错误位。

对于数据块大小为N的NAND闪存,BCH编码将数据块划分为多个子块,每个子块的大小为K,其中n=N/K是编码的重复次数。

在每个子块中,BCH编码器计算校验位,并将其添加到子块的末尾(通常称为附加码字)。

然后,这些附加码字组成了整个数据块的校验位。

BCH解码:BCH解码基于错误位置定位和纠正位计算。

在读取NAND闪存时,ECC解码器首先读取数据块和校验位,并计算其校验位。

然后,对于每个校验位错误的数据块,解码器使用BCH解码算法确定错误的位置。

一旦错误位置确定,解码器可以使用纠正位计算算法修复错误数据,并输出正确的数据块。

ECC实现:NAND闪存的ECC实现通常是在芯片级别进行的。

在芯片内部,有专门的ECC电路来执行编码和解码操作。

编码器:编码器通常包括一个BCH编码器和一个输出缓冲区。

BCH编码器接收数据块并计算校验位,然后将结果存储在输出缓冲区中。

输出缓冲区的大小通常与数据块的大小相等。

解码器:解码器通常包括一个BCH解码器、一个错误检测和位置确定单元以及一个错误修复单元。

BCH解码器接收数据块和校验位,并计算校验位。

支持ONFI与toggle协议的NAND flash控制器设计

支持ONFI 与toggle 协议的NAND flash 控制器设计**基金项目:国家重点研发计划子课题(2018YFB2003302)王菊湘1,施恒壮1,陈昕1,贺林1,21.南京邮电大学电子与光学工程学院、微电子学院;2.南京邮电大学射频集成与微组装技术国家地方联合工程实验室摘要:设计的NAND 型Flash 控制器兼容ONFI3.0模式与toggle2.0模式,对以DDR 方式进行数据传输的方法进行了优化,提出使用分频的方法去完成读写操作数据的传输以及信号的移相。

使得控制器在移相信号时,不再完全依赖于锁相环,提高了设计的集成度。

相比于锁相环,该方法电路实现简单,占用硬件资源更少。

使用两种不同模式的nand flash 对设计的控制器进行功能仿真验证,验证结果表明,控制器各时序要求满足ONFI 协议与toggle 协议要求。

关键词:NAND Flash ;控制器;分频器;锁相环Design of NAND flash controller supporting ONFI and toggle protocolWANG Ju-xiang,SHI Heng-zhuang,CHEN Xin,HE Lin1.School of Electronic and Optical Engineering,School of Microelectronics,Nanjing University of Posts and Telecommunications;2.National and Local Joint Engineering Laboratory of Radio Frequency Integration and Micro Assembly Technology,Nanjing University of Posts and TelecommunicationsAbstract:The designed NAND flash controller is compatible with ONFI3.0mode and toggle2.0mode.The method of data transmission in DDR mode is optimized.It is proposed to use the method of frequency division to complete thedata transmission of the read-write operation and the phase shift of the signal.The controller no longer completely de-pends on the phase-locked loop when shifting the phase signal,which improves the integration of the -pared with the phase-locked loop,this method has a simple circuit implementation and uses less hardware resources. Two different modes of nand flash are used to verify the designed controller.The verification results show that the tim-ing requirements of the controller meet the requirements of the ONFI protocol and the toggle protocol. Keywords:NAND Flash;controller;frequency divider;phase locked loop0介绍NAND flash是现在主流的存储芯片,相比于NOR flash存储容量更大,成本更低,读写数据以及擦除速度更快,这使得NAND flash市场需求量持续增长[1]。

基于SOPC的NANDFLASH测试平台

0 引言

NAND FLASH 作为非易失半导体存储介质,具 有容量大、体积小、读写速度高、应用广泛等优点。 由于其制造工艺的特殊性,导致该芯片在生产时就 可能坏块,同时在使用过程中也会不断产生新的坏 块,必须建立一种 FLASH 检测方式。故开发基于 SOPC 的具有 USB2.0 接口的高效 NAND FLASH 检 测器,以高效地将不良的 NAND FLASH 芯片从原 料中剔除,确保产品生产流程源头的可靠。

摘要:一种基于 SOPC 可编程片上系统的 NAND FLASH 测试平台的实现方法。采用嵌入式软处理器核 MicroBlaze 以及基于 PicoBlaze 的 NAND FLASH 控制器,可以兼容多种类型的 NAND FLASH,内置 DMA 逻辑,可实现高效测 试。采用 USB 与 PC 连接,具有很好的通用性。

操作 NAND FLASH 所需要的时序和状态逻辑 通过对 PicoBlaze 编程实现。PicoBlaze 是可集成在 Xilinx 公司的 FPGA 内部的 8 位嵌入式微控制器 IP 核,与 MicroBlaze 实现高低搭配。PicoBlaze 提供 49 个不同的指令,16 个寄存器,256 个直接或间接 的可设定地址的端口,1 个中断。作为可编程状态 机,具有固定的程序执行周期和延迟(执行 1 条指 令需要 2 个时钟周期)。其性能超过了传统的外部 独立微控制器,而且占用的逻辑资源紧凑和简单, 具 有 低 成 本 的 优 势 。 程 序 存 储 在 FPGA 内 部 的 BRAM 中,无需外部程序存储器,程序执行效率高。

基于AMBAAPB总线的NandFlash控制器的设计

些特 点 , 然后 详 细 介 绍 了 N a n d F l a s h控 制 器的 整 体 框 架 、 具 体 功 能 及 其 内部 的 数 据 通 路 。 该 控 制 器 通 过 Mo d e l S i m 进 行 了仿 真 及 F P G A 板 级 验证 , 结 果证 明 能 够 满足 N a n d F l a s h时 序 要 求 。

( 1 . E l e c t r o n i c I n f o r m a t i o n a n d C o n t r o l E n g i n e e r i n g C o l l e g e , B e i j i n g U n i v e r s i t y o f T e c h n o l o g y ,B e i j i n g 1 0 0 1 2 4 , C h i n a ;

积 U盘 等 [ 3 1 。

De s i g n o f Na n d F l a s h c o n t r o l l e r b a s e d o n AM BA APB b u s

Wa n g X i n j u n 。 , Z h a n g We i ,F e n g S h i w e i , Hu J i e

F l a s h i s p r e s e n t e d s i mp l y f o l l o we d b y t h e d e t a i l e d i n t r o d u c t i o n o f s y s t e m a r c h i t e c t u r e a n d t h e e x a c t f u n c t i o n i n c l u d i n g i n t e r n a l d a t a p a t h o f t h e c o n t r o l l e r .T h e d e s i g n w i t h Mo d e l S i m i s s i mu l a t e d a n d v e r i f i e d wi t h F P GA b o a r d.T h e t e s t r e s u l t s h o w s t h a t t h e d e s i g n c a l l s a t i s f y t h e t i mi n g r e q u i r e me n t o f Na n d F l a s h.

一种基于BCH码的NAND+Flash控制器的研究与设计

学位论文作者签名: 日期: 年 月 日

学位论文版权使用授权书

本学位论文作者完全了解学校有关保留、使用学位论文的规定,即: 学校有权保留并向国家有关部门或机构送交论文的复印件和电子版,允 许论文被查阅和借阅。本人授权华中科技大学可以将本学位论文的全部 或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复 制手段保存和汇编本学位论文。 保 本论文属于 不保密□。 (请在以上方框内打“√” ) 密□,在______年解密后适用本授权书。

II

华 中 科 技 大 学 硕 士 学 位 论 文 目录

摘 要............................................................................................................. I

Abstract ........................................................................................................... II 目录.................................................................................................................III 1 绪论 1.1 课题背景和意义 .................................................................................. (1) 1.2 NAND Flash 存储器介绍 ....................................................................... (1) 1.3 常用纠错码分析 ..................................................................................... (3) 1.4 NAND Flash 控制器研究现状 ............................................................... (3) 1.5 本文的主要内容及结构安排 ................................................................ (4) 2 BCH 码和 NAND Flash 存储器的理论基础 2.1 有限域和线性分组码 ............................................................................ (7) 2.2 BCH 码 .................................................................................................... (9) 2.3 NAND Flash 的存储架构和外部接口 ................................................. (12) 2.4 NAND Flash 的操作时序 ..................................................................... (15) 2.5 本章小结 .............................................................................................. (19) 3 BCH 编译码模块设计 3.1 BCH 码参数设计 .................................................................................. (20) 3.2 并行 BCH 编码器设计 ........................................................................ (21) 3.3 并行 BCH 译码器设计 ........................................................................ (24) 3.4 本章小节 .............................................................................................. (33) 4 NAND Flash 控制器主控模块设计 4.1 NAND Flash 控制器的总体架构 ......................................................... (35) 4.2 主控模块设计 ...................................................................................... (36) 4.3 控制器的主要操作 .............................................................................. (41) 4.4 本章小节 ............................................................................................... (44) 5 仿真验证与综合版图 5.1 功能仿真 .............................................................................................. (45)

FLASH控制器IP的功能验证研究的开题报告

FLASH控制器IP的功能验证研究的开题报告一、选题背景随着智能手机等设备的普及,闪存控制器已成为非易失性存储器市场上的重要组成部分,且具有很高的发展潜力。

因此,针对FLASH控制器IP进行功能验证研究具有重要意义。

然而,目前市面上的闪存控制器IP种类繁多,而且功能各异,因此对其功能验证的研究也显得极为必要。

二、研究内容本次研究的目标是实现对特定闪存控制器IP的功能验证,主要研究内容包括:1.对闪存控制器IP制定一系列基础测试计划,即制定闪存控制器IP 在各种情况下需要执行的测试程序。

2.设计和开发支持测试计划的工具,即测试工具,以保证测试的规格性和准确性。

3.开展闪存控制器IP的仿真验证,即利用Verilog等硬件描述语言来设计和实现闪存控制器IP的仿真验证平台,从而验证闪存控制器IP所具备的各项功能和性能。

4.开展闪存控制器IP的现场测试,即通过现场测试来验证闪存控制器IP的功能和性能,从而进一步验证其在实际应用中的可靠性和稳定性。

三、研究意义本次研究将对FLASH控制器IP的功能验证进行深入探究,不仅有助于提高闪存控制器IP的稳定性和可靠性,同时也有助于提高闪存控制器IP的性能和功耗等方面的优化。

此外,本研究还可以为相关企业提供开发和生产高质量非易失性存储器控制器IP的技术支撑,从而为相关企业带来更好的商业机会和市场竞争力。

四、研究方法本次研究综合采用文献调研、理论分析和实验验证等方法,重点思考如何设计科学合理的测试计划、设计功能强大的测试工具、实现闪存控制器IP的仿真验证平台,并开展现场测试等操作。

五、预期成果本次研究预计将实现对特定闪存控制器IP的功能验证,具体成果包括:1.完善的测试计划,即能够通过测试计划的执行验证闪存控制器IP 的功能性和规格性。

2.高效可靠的测试工具,即能够辅助进行规模化测试的工具。

3.仿真验证平台,即能够实现闪存控制器IP的仿真验证平台,以验证闪存控制器IP的性能和功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在该结 构 中 , 有一个 顶层作 为测试 向量 模块 , 一 个

或 多个 顶层 是一 些 公用 的子 程序 , 这 些 子 程序 由于 完 成一 些通用 的功 能被定 义成任 务和 函数等 被公 用 。还

有 一种称 为 h a r n e s s的顶层 , 该 层 由待测设 计 ( D U V) 和

c o mp r e h e n s i v e f u n c t i o n a l v e r i f i c a t i o n p r o c e s s or f t h e c o n t r o l l e r . S i mu l a t i o n r e s u l t s v e r i f y t h e c o r r e c t n e s s o f t h i s d e — s i g n, wh i c h c a n i mp r o v e t h e v e if r i c a t i o n e ic f i e n c y a n d s h o te r n t h e d e v e l o p me n t c y c l e . Ke y wo r d s NAND F l a s h u ' l e mo y r c o n t r o l l e r ;t e s t b e n c h; s e l f — c h e c k

ห้องสมุดไป่ตู้

摘

要

讨 论 了验 证 平 台的 设 计 理 论 、 功 能 以及 结 构 几 方 面 问 题 ,并 使 用 硬 件 描 述 语 言搭 建 了 自检 查 的 N A N D

F l a s h控 制 器验 证 平 台 ,在 此 基 础 上 对控 制 器 进 行 了 全 面 的 功 能 验 证 过 程 。仿 真 结 果 验 证 了该 方 法 的 正 确 性 .此 方 法 提 高 了验 证 效 率 、 缩短 了芯 片 的研 发 周 期 。 关键词 N A N D F l a s h控 制 器 ;验 证 平 台 ; 自动检 测 T P 3 3 2 . 3 文献标识码 A 文章编号 1 0 0 7— 7 8 2 0 ( 2 0 1 3 ) 0 7—1 4 2— 0 3 中图 分 类 号

验证 是芯 片设 计 过 程 中的重 要 环节 , 无 缺 陷 芯 片 不仅 要依 靠设 计 , 更 需 要 通过 验 证 。文 中介 绍 了一 种 基 于仿真 器 的 N A N D F l a s h控制 器逻辑验 证平 台 。

再将所有的模块实例化。与树结构相 似, 只有一个模块有 子结点而无父节点 , 而其他模块均有父节点 。测试模 块是 些接 口 模 型, 其 还可能包含一些激励在内 ] 。测试模块

De s i g n o f a n NAND Fl a s h Co n t r o l l e r Te s t Be n c h

W EI Gu o

( E l e c t r o n i c S c i e n c e a n d A p p l i e d P h y s i c s ,H e f e i U n i v e r s i t y o f T e c h n o l o g y ,H e f e i 2 3 0 0 0 9 ,C h i n a )

厂——]——]

测试模 块1 D U V

…

测试 模块2

广十]

厂

图 2 单顶 层 结构

网表 到版图 ( L a y o u t ) 等 。验证 则 要 保证 每 一 步 的设 计 转换 过程正确无误 _ 1 ≈J 。图 1 为设计 和验证 的关系 。

设 计 过 程

1 . 2 . 2 多 顶层 结 构

F l a s h me mo y r c o n t r o l l e r .T h e h a r d wa r e d e s c r i p t i o n l a n g u a g e i s u s e d t o b u i l d a s e l f — c h e c k t e s t b e n c h t o p e r f o r m a

Abs t r a c t r h e a r t i c l e d i s c u s s e s t h e d e s i g n t h e o r y. f u n c t i o n a l a n d s t r u c t u r a ]o f t h e t e s t b e n c h f o r a n NAND

a 叶拭 2 0 1 3 年 第 2 6 卷 第 7 期

E l e c t r o n i c S c i . &T e c h . / J u l y . 1 5. 2 0 1 3

一

种 N A N D F l a s h控 制器 验 证 平 台的设 计

魏 国

( 合 肥 工 业 大 学 电子 科 学 与 应 用 物 理 学 院 ,安徽 合 肥 2 3 0 0 0 9 )

一

1 验证 平 台 的设 计 理 论

1 . 1 验证原 理

和D U V之间通过端 口映射进行互连 , 如图 2 所示 。

ToP I

验证是确定设 计在功能上 完全正 确的过程 。通常 ,

设计 和验证均 有一个 起 点 和终 点 。设计 的过程 实 际上 是从 一种形 式 到 另 一种 形 式 的转 换 , 比如从 设 计 规 格 ( S p e c i i f c a t i o n ) 到R T L代码 ; 从R T L代码 到门级 网表 ; 从