DRV8842PWP;DRV8842PWPR;中文规格书,Datasheet资料

QX6104中文规格书

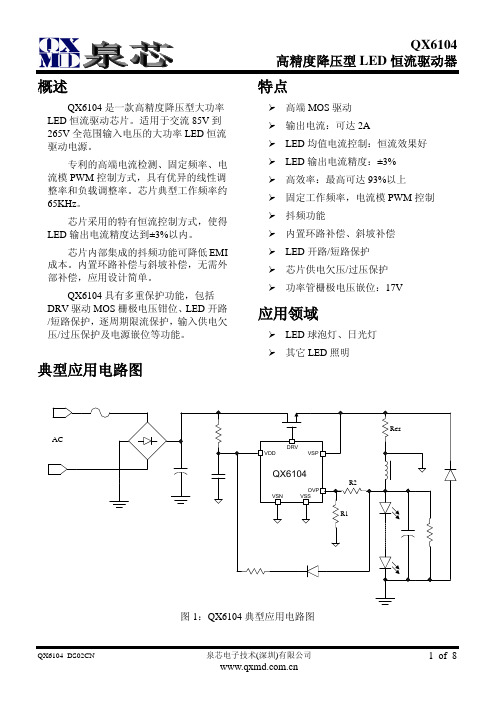

.典型应用电路图图1:QX6104典型应用电路图概述 QX6104是一款高精度降压型大功率LED 恒流驱动芯片。

适用于交流85V 到265V 全范围输入电压的大功率LED 恒流驱动电源。

专利的高端电流检测、固定频率、电流模PWM 控制方式,具有优异的线性调整率和负载调整率。

芯片典型工作频率约65KHz 。

芯片采用的特有恒流控制方式,使得LED 输出电流精度达到±3%以内。

芯片内部集成的抖频功能可降低EMI 成本。

内置环路补偿与斜坡补偿,无需外部补偿,应用设计简单。

QX6104具有多重保护功能,包括DRV 驱动MOS 栅极电压钳位、LED 开路/短路保护,逐周期限流保护,输入供电欠压/过压保护及电源嵌位等功能。

特点高端MOS 驱动 输出电流:可达2ALED 均值电流控制:恒流效果好 LED 输出电流精度:±3%高效率:最高可达93%以上固定工作频率,电流模PWM 控制 抖频功能内置环路补偿、斜坡补偿 LED 开路/短路保护 芯片供电欠压/过压保护 功率管栅极电压嵌位:17V 应用领域 LED 球泡灯、日光灯 其它LED 照明订货信息产品型号QX6104丝印6104X批号封装及管脚分配DRVVSN VSPOVPVDD132645VSS6104XSOT23-6管脚描述内部电路方框图DRVVSPVSN图2:QX6104内部电路方框图极限参数(注1)注1:超过上表中规定的极限参数会导致器件永久性损坏。

而工作在以上极限条件下可能会影响器件的可靠性。

电气特性除非特别说明,T A =25o C电气特性(接上一页) 除非特别说明,T A =25o C应用指南概述QX6104是一款高精度降压型大功率LED 恒流驱动芯片,输出电流可达2A 以上。

芯片采用专利的高端电流检测、固定频率、电流模PWM 控制方式,具有优异的线性调整率和负载调整率。

芯片内置频率补偿与斜坡补偿,无需外部补偿。

QX6104还集成了抖频功能,以改善系统的EMI 特性。

Rockwell Automation Trusted 8 Channel Temperature

PD-T8840 TrustedTrusted 8 Channel Temperature FTAProduct OverviewThe Trusted® Temperature Field Termination Assembly (FTA) is designed to interface between a Trusted system and up to eight temperature, voltage or current devices using a range of available plug in conditioning units.Features:•Eight Input channels per Trusted Temperature FTA.•Flexible user defined conditioning.•Standard DIN rail compatibility.•Configurable 2 or 3 wire Resistance Temperature Detector (RTD) inputs.•Dual 24 V Supply.Trusted PD-T8840Page intentionally left blankPREFACEIn no event will Rockwell Automation be responsible or liable for indirect or consequential damages resulting from the use or application of this equipment. The examples given in this manual are included solely for illustrative purposes. Because of the many variables and requirements related to any particular installation, Rockwell Automation does not assume responsibility or reliability for actual use based on the examples and diagrams.No patent liability is assumed by Rockwell Automation, with respect to use of information, circuits, equipment, or software described in this manual.All trademarks are acknowledged.DISCLAIMERIt is not intended that the information in this publication covers every possible detail about the construction, operation, or maintenance of a control system installation. You should also refer to your own local (or supplied) system safety manual, installation and operator/maintenance manuals.REVISION AND UPDATING POLICYThis document is based on information available at the time of its publication. The document contents are subject to change from time to time. The latest versions of the manuals are available at the Rockwell Automation Literature Library under "Product Information" information "Critical Process Control & Safety Systems".TRUSTED RELEASEThis technical manual applies to Trusted Release: 3.6.1.LATEST PRODUCT INFORMATIONFor the latest information about this product review the Product Notifications and Technical Notes issued by technical support. Product Notifications and product support are available at the Rockwell Automation Support Centre atAt the Search Knowledgebase tab select the option "By Product" then scroll down and select the Trusted product.Some of the Answer ID’s in the Knowledge Base require a TechConnect Support Contract. For more information about TechConnect Support Contract Access Level and Features please click on the following link:https:///app/answers/detail/a_id/50871This will get you to the login page where you must enter your login details.IMPORTANT A login is required to access the link. If you do not have an account then you can create one using the "Sign Up" link at the top right of the web page.DOCUMENTATION FEEDBACKYour comments help us to write better user documentation. If you discover an error, or have a suggestion on how to make this publication better, send your comment to our technical support group at SCOPEThis manual specifies the maintenance requirements and describes the procedures to assist troubleshooting and maintenance of a Trusted system. WHO SHOULD USE THIS MANUALThis manual is for plant maintenance personnel who are experienced in the operation and maintenance of electronic equipment and are trained to work with safety systems. SYMBOLSIn this manual we will use these notices to tell you about safety considerations.SHOCK HAZARD: Identifies an electrical shock hazard. If a warning label is fitted, it can be on or inside the equipment.WARNING: Identifies information about practices or circumstances that can cause an explosion in a hazardous environment, which can cause injury or death, property damage or economic loss.ATTENTION: Identifies information about practices or circumstances that can cause injury or death.CAUTION: Identifies information about practices or circumstances that can cause property damage or economic loss.BURN HAZARD: Identifies where a surface can reach dangerous temperatures. If a warning label is fitted, it can be on or inside the equipment.This symbol identifies items which must be thought about and put in place when designing and assembling a Trusted controller for use in a Safety Instrumented Function (SIF). It appears extensively in the Trusted Safety Manual.IMPORTANTIdentifies information that is critical for successful application and understanding of the product.NOTE Provides key information about the product or service.TIP Tips give helpful information about using or setting up the equipment.WARNINGS AND CAUTIONSWARNING: EXPLOSION RISKDo not connect or disconnect equipment while the circuit is live or unless the area is known to be free of ignitable concentrations or equivalentAVERTISSEMENT - RISQUE D’EXPLOSIONNe pas connecter ou déconnecter l’équipement alors qu’il est sous tension, sauf si l’environnement est exempt de concentrations inflammables ou équivalenteMAINTENANCEMaintenance must be carried out only by qualified personnel. Failure to follow these instructions may result in personal injury.CAUTION: RADIO FREQUENCY INTERFERENCEMost electronic equipment is influenced by Radio Frequency Interference. Caution should be exercised with regard to the use of portable communications equipment around such equipment. Signs should be posted in the vicinity of the equipment cautioning against the use of portable communications equipment.CAUTION:The module PCBs contains static sensitive components. Static handling precautions must be observed. DO NOT touch exposed connector pins or attempt to dismantle a module.ISSUE RECORDIssue Date Comments1 July 052 Aug 06 Corrections3 Jun 08 Open circuit effects4 Apr 10 Change to sub-section 2.15 Apr 16 Rebranded, reformatted, Inclusion of IEEE symbols and correction oftypographical errorsPage intentionally left blankTrusted 8 Channel Temperature FTA Table of Contents Table of Contents1.Description (3)2.Installation (5)2.1. Cable Selection (5)2.2. Module Pin-out Connections (7)2.2.1. RTD1 to RTD8 (7)2.2.2. PWR (7)2.2.3. IOIF (8)3.Applications (9)3.1. Signal Conditioning units (9)3.1.1. Isolator Physical dimensions (9)3.1.2. Conditioning Unit Specification (10)3.1.3. Available Conditioning Units (10)3.1.4. Cold Junction Compensation (12)4.Specifications (13)Table of Contents Trusted 8 Channel Temperature FTAPage intentionally left blank1.DescriptionFigure 1 Trusted Temperature FTAThe Trusted Temperature FTA enables connection to 8 temperature, voltage or current devices using RTD, Thermocouple, Voltage and Current input conditioning units. The Trusted Temperature FTA excludes the conditioning units to allow maximum configurability. More than one type of conditioning unit can be used on the same FTA.Figure 2 Module Layout2. Installation2.1. Cable SelectionThe Trusted Temperature FTA can connect direct to an Analogue Input Module using either companion cables TC-211/212 or SmartSlot cables TC-511/512. The Output can also be connected to the Analogue Input module via a Versatile Field Termination Assembly (VFTA) if necessary to be compatible with an existing installation.Some isolator modules will float their output to 10 V on an open circuit field input. This will cause slice faults on the analogue input module. If the isolator output is connected to the module via a 250 Ω resistor on a VFTA, the voltage will be pulled down into the module’s operating range. Therefore even if the isolator output is a voltage signal, it is recommended to connect the input via a VFTA with the 250 Ω VFTA resistor in parallel.Figure 3 System Connectivity using 1-5 V Output DevicesAnalogue module 8431/ 8432Temperature FTA 8840Temperature FTA 8840 Temperature FTA 8840Temperature FTA 8840Temperature FTA 8840TC-211/212Typical Configuration using conditioning devices with 1-5 V outputUp to 8 temperature devicesFigure 4 System Connectivity using VFTAFor signal conditioning units that provide signals as 4 mA to 20 mA for low to highengineering range, a conversion is needed because the voltage measured by the module input is not exactly 1 V to 5 V.EU = ((count/4036.5) – 0.007828) x (HEU – LEU) + LEU Where:LEU = Low engineering unit range HEU = High engineering unit range Count = Raw value seen by input EU = Engineering unit valueFor signal conditioning units that provide a voltage signal of 1 V to 5 V, no special factors are required:EU = (count/4096) x (HEU – LEU) + LEU.VFTA 8842Temperature FTA 8840 Temperature FTA 8840 Temperature FTA 8840Temperature FTA 8840Temperature FTA 8840Typical Configuration using conditioning Devices with 1 to 5 V outputusing a VFTAUp to 8 temperature devicesAnalogue module 84312.2.Module Pin-out Connections 2.2.1.RTD1 to RTD8Terminal Description ConditioningModule Pin Thermocoupleor Voltage2 wireRTD3 wireRTD4 wireRTDR Sense Input (X) 0 Red Red R Input Low (-) 2 - Red Red Red W Input High (+) 1 + White White White/WhiteTable 1 Input TerminationsFigure 5 Temperature Input Schematic2.2.2.PWRTerminal Description+ 24 Vdc- 0 V- 0 V+ 24 VdcTable 2 Power TerminationsThere are no fuses fitted to the power rails on the Trusted Temperature FTA. External 2 A fuses should be fitted to the power wiring.2.2.3.IOIFTerminal Description1 0 V2 Output, channel 13 Output, channel 24 Output, channel 35 Output, channel 46 Output, channel 57 Output, channel 68 Output, channel 79 Output, channel 810 0 VTable 3 Temperature Signal Outputs3.ApplicationsThe Trusted Temperature FTA interfaces between a Trusted system and up to eight monitoring devices using, isolated RTD, Thermocouple, Voltage and Current input conditioning units. Compatible conditioning units must have 1 V to 5 V outputs.3.1.Signal Conditioning unitsCompatible conditioning unit include the 7B series of units from Analog Devices Inc and SCM7B series from Dataforth.3.1.1.Isolator Physical dimensionsFigure 6 Conditioning Unit Dimensions3.1.2.Conditioning Unit SpecificationThe following specification applies to all signal conditioning unit types Operating Voltage Range15 Vdc to 30 Vdc Power consumption 2 W maxOperating Temperature -40 °C to +85 °C Common mode Isolation 1500 Vac rms Continuous field voltage withstand 120 Vac rmsAccuracy ±0.3 % spanOutput Signal range +1 V to +5 V3.1.3.Available Conditioning UnitsInput Types Range ModelNumber (A)Model Number (B)Isolated Voltage0 mV to +10 mV7B30-01-1SCM7B30-010 mV to +100 mV7B30-02-1SCM7B30-020 V to +1 V7B30-03-1SCM7B30-03+1 V to +5 V7B30-05-1SCM7B30-04-10 mV to +10 mV7B30-06-1SCM7B30-05-100 mV to +100 mV7B30-07-1SCM7B30-06-1 V to +1 V7B30-08-1SCM7B30-070 V to 10 V Not available SCM7B30-08-5 V to +5 V Not available SCM7B31-01-10 V to +10 V Not available SCM7B31-020 V to 5 V Not available SCM7B31-03 Isolated Current 4 mA to 20 mA7B32-01-1SCM7B32-010 mA to 20 mA Not available SCM7B32-02 Isolated RTD-100 °C to +100 °C (-148 °F to +212 °F)7B34-01-1SCM7B34-01Number (A)Number (B) Pt 100 ΩLinearized0 °C to +100 °C (+32 °F to +21 2 °F)7B34-02-1SCM7B34-020 °C to +200 °C (+32 °F to +392 °F)7B34-03-1SCM7B34-030 °C to +600 °C (+32 °F to +1112 °F)7B34-04-1SCM7B34-04-50 °C to +350 °C (-58 °F to +662 °F)7B34-05-1SCM7B34-05Isolated RTD Ni 120 ΩLinearized 0 °C to +300 °C (+32 °F to +572 °F)7B34-N-01-1SCM7B34N-01 0 °C to +200 °C (+32 °F to +392 °F)7B34-N-02-1SCM7B34N-02Isolated 2 wireTransmitter(inc loop power)4 mA to 20 mA7B35-01-1SCM7B35-01Isolated Potentiometer 0 Ω to 100 ΩNot available SCM7B36-01 0 Ω to 200 ΩNot available SCM7B36-02 0 Ω to 500 ΩNot available SCM7B36-03 0 Ω to 1 KΩNot available SCM7B36-04 0 Ω to 5 KΩNot available SCM7B36-05 0 Ω to 10 KΩNot available SCM7B36-06Isolated Thermocouple Type J -100 °C to +760 °C (-148 °F to +1400 °F)7B37-J-01-1SCM7B37J-01 0 °C to +200 °C (+32 °F to +392 °F)7B37-J-10-1SCM7B37J-10 0 °C to +400 °C (+32 °F to +752 °F)7B37-J-11-1SCM7B37J-11 0 °C to +600 °C (+32 °F to +1112 °F)7B37-J-12-1SCM7B37J-12 +300 °C to +600 °C (+572 °F to +1112 °F)7B37-J-13-1SCM7B37J-13Isolated Thermocouple Type K -100 °C to +1350 °C (-148 °F to +2462 °F)7B37-K-02-1SCM7B37K-02 0 °C to +300 °C (+32 °F to +572 °F)7B37-K-20-1SCM7B37K-20 0 °C to +600 °C (+32 °F to +1112 °F)7B37-K-21-1SCM7B37K-21 0 °C to +1200 °C (+32 °F to +2192 °F)7B37-K-22-1SCM7B37K-22 +600 °C to +1200 °C (+1112 °F to +2192 °F)7B37-K-23-1SCM7B37K-23Number (A)Number (B)Isolated Thermocouple Type J Linearized 0 °C to +760 °C (+32 °F to +1400 °F)7B47-J-01-1SCM7B47J-01 -100 °C to +300 °C (-148 °F to +572 °F)7B47-J-02-1SCM7B47J-02Isolated Thermocouple Type K Linearized 0 °C to +1300 °C (+32 °F to +2372 °F)7B47-K-03-1SCM7B47K-03 0 °C to +600 °C (+32 °F to +1112 °F)7B47-K-04-1SCM7B47K-04Table 4 Available Conditioning UnitsAdditional standard ranges, including custom are available. Information and datasheets can be supplied upon request.3.1.4.Cold Junction CompensationThe Trusted Temperature FTA includes a Cold Junction Compensation (CJC) resistor for each of the inputs. This makes the FTA compatible with Thermocouple conditioning units. For information in determining compatible Thermocouple Units the CJC resistor specification is as follows:GE Thermometrics Part D95G104WNTC, 100 K at 25 °CFor further information see the manufacturer’s data sheet.Trusted 8 Channel Temperature FTA 4. Specifications 4.SpecificationsVoltage Range 15 Vdc to 30 VdcMaximum Input Current 2.5 ANumber of Inputs 8Input types Voltage, Current, RTD and Thermocoupledepending on chosen conditioning unit. Environmental Specifications Refer to Document 552517DimensionsHeight 110 mm (4.3 in)Width 145 mm (5.7 in)Depth 68 mm (2.6 in)Depth with conditioning unit fitted 90 mm (3.6 in)Weight 248 g (0.55 lb)Accuracy, resolution Dependant on conditioning unitRockwell Automation Publication PD-T8840 Issue 5 13。

XLSEMI XL8002 80V 1A高效降压PWM LED常电流驱动器说明书

80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002FeaturesOperation Voltage DC 12V~80V. 0.1V current sense voltage reference. Directly drive 1~18 Series 1W/3W LED. Excellent line and load regulation.Internal Optimize Power HV-MOSFET. Built in Thermal Shutdown Function. Built in Current Limiting Function.Built in Soft-Start Circuit.Available in TO263-5L package. Up to 98% efficiency. ApplicationsLED Lighting & LED LAMP General purpose LED lightingGeneral DescriptionThe XL8002 is a monolithic high voltage switching regulator with PFM that is specifically designed to operate from a 12V~80V DC power supply.The XL8002 is a high efficiency LED driver switching regulator. The LED string is driven at DC constant current rather than constant voltage, thus providing constant light output and enhanced reliability.Figure1. Package Type of XL800280V 1A High Efficiency Buck PFM LED Constant Current Driver XL800280V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002Figure4. XL8002 Typical Application80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002Figure5. Efficiency VS Output N*1W LEDFigure6. Output ILED Load Regulation VS Output N*1W LED80V 1A High Efficiency Buck PFM LED Constant Current Driver XL800280V 1A High Efficiency Buck PFM LED Constant Current Driver XL800280V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002 Figure7. XL8002 System Application at VIN=60V~80V Schematic Figure8. XL8002 System Application at VIN=60V~80V Efficiency Curve80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002 Figure9. XL8002 System Application at VIN=36V~60V Schematic80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002Figure10. XL8002 System Application at VIN=36V~60V Efficiency Curve Table2: Figure9 Input VIN=36V/48V system parameters table:80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002Figure11. XL8002 System Application at VIN=12V~36V SchematicFigure12. XL8002 System Application at VIN=12V~36V Efficiency CurveTable3: Figure11 Input VIN=12V/24V system parameters table:VIN=12V VIN=24VFOSC Pout Efficiency FOSC Pout Efficiency1.01W 82.3%1.96W 90.8%2.91W 94.1%47.25K 3.80W 95.5%42.17K 4.70W 96.6%31.13K 5.61W 97.2%80V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002 Figure13. XL8002 System Application at VIN=60V~80V Schematic Figure14. XL8002 System Application at VIN=60V~80V Efficiency Curve80V 1A High Efficiency Buck PFM LED Constant Current Driver XL800280V 1A High Efficiency Buck PFM LED Constant Current Driver XL8002。

RS PRO IPM 242 600A 电流探头测试仪说明书

ENGLSpecifications: (All at 23℃±5℃, ≦80% R.H.)DC/AC VoltageDC/AC VoltageFunction Range Accuracy*DCV 99.99V± (0.7% + 2dgt) 999.9VACV 99.99V ± (1.0% + 5dgt)50 ~ 500Hz 999.9VLPF ACV 99.99V 50 ~ 60Hz ± (1% + 5dgt)>60 ~ 400Hz ± (5% + 5dgt) 999.9V* DCV <1000dgt, add 6 dgt to the accuracy.ACV <1000dgt, add 3 dgt to the accuracy.Overload Protection: 1000VrmsInput Impedance:3.5MΩ // <100pFAC+DC V RMS Accuracy: same as ACV spec. +DCV spec.AC CurrentAC CurrentFunction Range AccuracyACA 99.99A 50 ~ 60Hz ± (1.5% + 5dgt) **>60 ~ 400Hz ± (2% + 5dgt) ** 599.9ALPF ACA 0.10A ~ 99.99A 50 ~ 60Hz ± (1.5% + 5dgt) **>60 ~ 400Hz ± (5% + 5dgt) ** 599.9A** The measured value <1000dgt, add 5 dgt to the accuracy. Overload Protection: 600ArmsPeak Hold (Peak MAX / Peak MIN)Peak Hold : Peak MAX / Peak MIN Function Range AccuracyACV 140.0V± (3.0% + 15dgt) 1400VACA 140.0A± (3.0% + 15dgt) 850AOverload Protection: 1000 V RMS, 600 Arms FrequencyFrequencyFunction Range AccuracyFrequency20.00 ~ 99.99Hz± (0.5% + 3dgt) 20.0 ~ 999.9Hz0.020 ~ 9.999KHzOverload Protection: 1000 V RMS, 600 Arms Harmonic DistortionTotal Harmonic DistortionFunction Range AccuracyACA /ACV 99.9% ± (3.0% + 10dgt)Harmonic distortion measurement Harmonic order Range AccuracyH01 ~ H1299.9% ± (5% + 10dgt)H13 ~ H25 ± (10% + 10dgt)Overload Protection: 1000 V RMS, 600 Arms-If ACV<10Vrms or ACA <10Arms, it will display “rdy”.-If the fundamental frequency out of range 45 ~ 65Hz, it will display “out.F”.Inrush CurrentInrush Current :Function Range AccuracyACA 99.99A ± (2.5% + 0.2A) 599.9A ± (2.5% + 5dgt)Overload Protection: 1000 V RMS, 600 ArmsAccuracy defined for:Sine wave, ACA≧10Arms, Freq. 50/60Hz- Integration time about 100m secActive Power (AC)Active Power (AC)Function Range AccuracyACW 9.999 kW**A,error×V,reading+V,error×A,reading 99.99 kW599.9KW** The measured value<1.000kW,add 10 dgt to the accuracy.Overload Protection: 1000 V RMS, 600 ArmsAccuracy defined for:ACW : Sine wave , ACV≧10 V RMS, ACA≧5 ArmsFreq. 50~60Hz, PF=1.00Power FactorPower FactorFunction Range Accuracy* PF-1.00 ~ 0.00 ~1.00 ±3°±1dgt * ACA<100A, add ±2° to the accuracyOverload Protection: 1000 V RMS, 600 ArmsResistance & Continuity & DiodeResistance & Continuity & Diode Function Range AccuracyResistance 999.9 Ω± (1.0% + 5dgt) 9.999 kΩ± (1.0% + 3dgt) 99.99 kΩContinuity 999.9 Ω± (1.0% + 5dgt)Diode 0.40~ 0.80V ± 0.1V Overload Protection: 1000VrmsMax. Test Current: Approx. 0.5mA.Continuity Check: <30Ω Beep On.>100Ω Beep OFF.Continuity Indicator: 2 KHz Tone BuzzerContinuity Response Time: < 100ms. CapacitanceCapacitanceFunction Range AccuracyCapacitance 3.999 μF± (1.9% + 8dgt) 39.99 μF399.9 μF3999 μFOverload Protection: 1000 V RMS TemperatureTemperatureFunction Range Accuracy°C-50 °C ~ 99.9 °C ± (1% + 2°C)100 °C ~ 399.9 °C400 °C ~ 1000 °C± (1% + 1°C)°F-58 °F ~ 211.9 °F ± (1% + 4°F)212.0 °F ~ 751.9 °F752 °F ~ 1832 °F± (1% + 2°F)Overload Protection: 1000 V RMS。

福禄克 884xa系列台式万用表手册

有限担保和有限责任

Fluke 担保在正常使用和保养的情况下,其产品没有材料和工艺上的缺陷。从寄送之日起,担保期为三年。部ቤተ መጻሕፍቲ ባይዱ件、产品修理和服务的担保期限为 90 天。本担保仅限于 Fluke 授权零售商的原购买人或最终用户,并且不适 用于一次性电池、电缆接头、电缆绝缘转换接头或 Fluke 认为由于误用、改装、疏忽、污染及意外或异常操 作或处理引起的任何产品损坏。Fluke 担保软件能依照功能规格正常运行 90 天,并且软件是记录在无缺陷的 媒介上。Fluke 并不担保软件毫无错误或在运行中不会中断。

Fluke Europe B.V. P.O. Box 1186 5602 BD Eindhoven The Netherlands

11/99

要在线 注册您的产 品,请 请 请 。

目录

章节 1

标题

页

章概述和技术指标.................................................................................. 1-1

®

8845A/8846A Digital Multimeter

用户手册

July 2006, Rev. 3, 3/11 (Simplified Chinese)

© 2006 - 2011 Fluke Corporation. Specifications subject to change without notice. All rights reserved. All product names are trademarks of their respective companies.

概述 ....................................................................................................... 1-3 用户文件 ................................................................................................ 1-3 关于本手册 ............................................................................................ 1-3 安全信息 ................................................................................................ 1-4

ISL8841AABZ资料

Features

• 1A MOSFET gate driver • 90μA start-up current, 125μA maximum • 35ns propagation delay current sense to output • Fast transient response with peak current mode control • 30V operation • Adjustable switching frequency to 2MHz • 20ns rise and fall times with 1nF output load • Trimmed timing capacitor discharge current for accurate deadtime/maximum duty cycle control • 1.5MHz bandwidth error amplifier • Tight tolerance voltage reference over line, load and temperature • ±3% current limit threshold • Pb-free plus anneal available and ELV, WEEE, RoHS Compliant

GND

2.5V

A = 0.5

CS

FB

+ -

ERROR AMPLIFIER

VF TOTAL = 1.15V

COMP

VREF

100k

2.9V 1.0V

150k

OSCILLATOR COMPARATOR <10ns

RTCT

+

8.4mA

ON

FN6320.3 April 18, 2007

ISL8844A中文资料

PART NUMBER ISL8840A ISL8841A ISL8842A ISL8843A ISL8844A ISL8845A

RISING UVLO 7.0 7.0

14.4V 8.4V 14.4V 8.4V

MAX. DUTY CYCLE 100% 50% 100% 100% 50% 50%

Pinout

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

deadtime/maximum duty cycle control • 1.5MHz bandwidth error amplifier • Tight tolerance voltage reference over line, load and

temperature • ±3% current limit threshold • Pb-free plus anneal available and ELV, WEEE, RoHS

ISL8843AMBZ 8843 AMBZ -55 to +125 8 Ld SOIC M8.15 (See Note)

ISL8843AMUZ 43AMZ (See Note)

-55 to +125 8 Ld MSOP M8.118

ISL8844AABZ 8844 AABZ -40 to +105 8 Ld SOIC M8.15 (See Note)

DRV8818PWP;DRV8818PWPR;DRV8818EVM;中文规格书,Datasheet资料

DRV8818 SLVSAX9A–SEPTEMBER2011–REVISED FEBRUARY2012STEPPER MOTOR CONTROLLER ICCheck for Samples:DRV8818FEATURES•Pulse Width Modulation(PWM)Microstepping Lower R ds(on)Motor Driver•Thermally Enhanced Surface Mount Package –Built-In Microstepping IndexerAPPLICATIONS–Up to2.5-A Current Per Winding•Printers–Microstepping Indexer Provides up to1/8-Step Operation•Textile Machinery–Low0.37-Ω(HS+LS)MOSFET•Positioning/TrackingOn-Resistance(at25°)•Factory Automation–Programmable Mixed Decay,Blanking,and•RoboticsOff Time•Pin-Compatible Upgrade to DRV8811WithDESCRIPTION/ORDERING INFORMATIONThe DRV8818provides an integrated stepper motor driver solution for printers,scanners,and other automated equipment applications.The device has two H-bridge drivers,as well as microstepping indexer logic to control a stepper motor.The output driver block for each consists of N-channel power MOSFETs configured as full H-bridges to drive the motor windings.A simple step/direction interface allows easy interfacing to controller circuits.Pins allow configuration of the motor in full-step,half-step,quarter-step,or eighth-step modes.Decay mode and PWM off time are programmable.Internal shutdown functions are provided for over current protection,short circuit protection,under-voltage lockout and overtemperature.The DRV8818is packaged in a PowerPAD™28-pin HTSSOP package with PowerPAD™(Eco-friendly:RoHS and no Sb/Br).ORDERING INFORMATION(1)PACKAGE(2)ORDERABLE PART NUMBER TOP-SIDE MARKINGReel of2000DRV8818PWPRPowerPAD™(HTSSOP)–PWP DRV8818Tube of50DRV8818PWP(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PowerPAD is a trademark of Texas Instruments.DRV8818SLVSAX9A–SEPTEMBER2011–REVISED FUNCTIONAL BLOCK DIAGRAMDRV8818 SLVSAX9A–SEPTEMBER2011–REVISED FEBRUARY2012TERMINAL FUNCTIONSNAME NO.I/O(1)DESCRIPTION EXTERNAL COMPONENTS OR CONNECTIONSPOWER AND GROUNDGND7,21-Device groundVMA28-Bridge A power supply Connect to motor supply(8V to35V).Both pins must be connectedto same supply.VMB15-Bridge B power supply Connect to motor supply(8V to35V).Both pins must be connectedto same supply.VCC10-Logic supply voltage Connect to3-V to5-V logic supply.Bypass to GND with a0.1-μFceramic capacitor.CP123IO Charge pump flying capacitor Connect a0.22-μF capacitor between CP1and CP2.CP224IO Charge pump flying capacitor Connect a0.22-μF capacitor between CP1and CP2.VCP22IO High-side gate drive voltage Connect a0.22-μF ceramic capacitor to V M.VGD20IO Low-side gate drive voltage Bypass to GND with a0.22-μF ceramic capacitor.CONTROLENABLEn26I Enable input Logic high to disable device outputs,logic low to enable outputs.Weak internal pullup to VCC.SLEEPn27I Sleep mode input Logic high to enable device,logic low to enter low-power sleep mode.Weak internal pulldown.DECAY5I Decay mode select Voltage applied sets decay mode-see motor driver description fordetails.Bypass to GND with a0.1-μF ceramic capacitor.Weakinternal pulldown.STEP19I Step input Rising edge causes the indexer to move one step.Weak internalpulldown.DIR3I Direction input Level sets the direction of stepping.Weak internal pulldown.USM013I Microstep mode0USM0and USM1set the step mode-full step,half step,quarterstep,or eight microsteps/step.Weak internal pulldown.USM112I Microstep mode1USM0and USM1set the step mode-full step,half step,quarterstep,or eight microsteps/step.Weak internal pulldown.RESETn17I Reset input Active-low reset input initializes the indexer logic and disables theH-bridge outputs.Weak internal pullup to VCC.SRn16I Sync.Rect.enable input When active low,synchronous rectification is enabled.Weak internalpulldown.VREF8I Current set reference input Reference voltage for winding current setRCA6I Bridge A blanking and off time adjust Connect a parallel resistor and capacitor to GND-see motor driverdescription for details.RCB9I Bridge B blanking and off time adjust Connect a parallel resistor and capacitor to GND-see motor driverdescription for details.ISENA1-Bridge A ground/Isense Connect to current sense resistor for bridge AISENB14-Bridge B ground/Isense Connect to current sense resistor for bridge BOUTPUTSAOUT14O Bridge A output1Connect to bipolar stepper motor windingAOUT225O Bridge A output2Positive current is AOUT1→AOUT2BOUT111O Bridge B output1Connect to bipolar stepper motor windingBOUT218O Bridge B output2Positive current is BOUT1→BOUT2HOMEn2O Home position Logic low when at home state of step table,logic high at other states (1)Directions:I=input,O=output,OZ=3-state output,OD=open-drain output,IO=input/outputISENAHOMEDIRAOUT1DECAYRCAGNDVREFRCBVCCBOUT1USM1USM0ISENBVMASLEEPnENABLEnAOUT2CP2CP1VCPGNDVGDSTEPBOUT2RESETnSRnVMBDRV8818SLVSAX9A–SEPTEMBER2011–REVISED ABSOLUTE MAXIMUM RATINGS(1)(2)(3)MIN MAX UNIT V MX Power supply voltage range–0.335VV CC Power supply voltage range–0.37V Digital pin voltage range–0.57VV REF Input voltage range–0.3V V CC V ISENSEx pin voltage range–0.30.5VI O(peak)Peak motor drive output current Internally limitedP D Continuous total power dissipation See Thermal Information table T J Operating junction temperature range–40150°CT stg Storage temperature range–60150°C (1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.(2)All voltage values are with respect to network ground terminal.(3)Power dissipation and thermal limits must be observed.THERMAL INFORMATIONDRV8818THERMAL METRIC(1)PWP UNITS28PINSθJA Junction-to-ambient thermal resistance(2)32.2θJCtop Junction-to-case(top)thermal resistance(3)16.3θJB Junction-to-board thermal resistance(4)14°C/WψJT Junction-to-top characterization parameter(5)0.5ψJB Junction-to-board characterization parameter(6)13.8θJCbot Junction-to-case(bottom)thermal resistance(7) 2.1(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953.(2)The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard,high-K board,asspecified in JESD51-7,in an environment described in JESD51-2a.(3)The junction-to-case(top)thermal resistance is obtained by simulating a cold plate test on the package top.No specificJEDEC-standard test exists,but a close description can be found in the ANSI SEMI standard G30-88.(4)The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCBtemperature,as described in JESD51-8.(5)The junction-to-top characterization parameter,ψJT,estimates the junction temperature of a device in a real system and is extractedfrom the simulation data for obtainingθJA,using a procedure described in JESD51-2a(sections6and7).(6)The junction-to-board characterization parameter,ψJB,estimates the junction temperature of a device in a real system and is extractedfrom the simulation data for obtainingθJA,using a procedure described in JESD51-2a(sections6and7).(7)The junction-to-case(bottom)thermal resistance is obtained by simulating a cold plate test on the exposed(power)pad.No specificJEDEC standard test exists,but a close description can be found in the ANSI SEMI standard G30-88.DRV8818 SLVSAX9A–SEPTEMBER2011–REVISED FEBRUARY2012RECOMMENDED OPERATING CONDITIONST A=25°C(unless otherwise noted)MIN NOM MAX UNITV M Motor power supply voltage range(1)835VV CC Logic power supply voltage range3 5.5VV REF VREF input voltage0V CC VR X R X resistance value4706801500kΩC X C X capacitance value1256100pF(1)All V M pins must be connected to the same supply voltage.ELECTRICAL CHARACTERISTICST A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Power SuppliesI VM V M operating supply current V M=35V,f PWM<50KHz710mAI VCC V CC operating supply current f PWM<50KHz0.44mAI VMQ V M sleep mode supply current V M=35V320μAI VCCQ V CC sleep mode supply current0.520μAV M undervoltage lockout voltage V M rising 6.77.5V UVLO V V CC undervoltage lockout voltage V CC rising 2.75 2.95VREF Input/Current Control AccuracyI REF VREF input current VREF=3.3V–33μAVREF=2.0V,70%to100%current–55%ΔI CHOP Chopping current accuracyVREF=2.0V,20%to56%current–1010% Logic-Level InputsV IL Input low voltage0.3×V CC VV IH Input high voltage0.7×V CC VV HYS Input hysteresis300mVI IL Input low current VIN=0.3×V CC–2020μAI IH Input high current VIN=0.3×V CC–2020μAR PU Pullup resistance1MΩR PD Pulldown resistance1MΩHOMEn OutputV OL Output low voltage I O=200μA0.3×VCC VV OH Output high voltage I O=–200μA0.7×VCC V Decay InputV IL Input low threshold voltage For fast decay mode0.21×VCC VV IH Input high threshold voltage For slow decay mode0.6×VCC VH-Bridge FETSR ds(on)HS FET on resistance V M=24V,I O=2.5A,T J=25°C0.220.30ΩR ds(on)LS FET on resistance V M=24V,I O=2.5A,T J=25°C0.150.24ΩI OFF–2020μA Motor Drivert OFF Off time Rx=56kΩ,Cx=680pF354453μst BLANK Current sense blanking time Rx=56kΩ,Cx=680pF90012501500nst DT Dead time SRn=010*******nst R Rise time1080nst F Fall time1080nsSTEP DIR,USMx SLEEPnDRV8818SLVSAX9A–SEPTEMBER2011–REVISED ELECTRICAL CHARACTERISTICS(continued)T A=25°C(unless otherwise noted)PARAMETER TEST CONDITIONS MIN TYP MAX UNIT Protection CircuitsT TSD Thermal shutdown temperature Die temperature150160180°CI OCP Overcurrent protection level 3.5At OCP OCP deglitch time 1.5µst RET OCP retry time800µsTIMING REQUIREMENTST A=25°C(unless otherwise noted)PARAMETER MIN MAX UNIT f STEP Step frequency500kHz t WH(STEP)Pulse duration,STEP high1μst WL(STEP)Pulse duration,STEP low1μst SU(STEP)Setup time,command to STEP rising200nst H(STEP)Hold time,command to STEP rising200nst WAKE Wakeup time,SLEEPn inactive to STEP 1.5msDRV8818 SLVSAX9A–SEPTEMBER2011–REVISED FEBRUARY2012FUNCTIONAL DESCRIPTIONPWM H-Bridge DriversDRV8818contains two H-bridge motor drivers with current-control PWM circuitry,and a microstepping indexer.A block diagram of the motor control circuitry is shown below.Figure1.Motor Control Circuitry8REFX CHOP ISENSEV I R =·OFF t R C=·1400BLANK t C=·DRV8818SLVSAX9A –SEPTEMBER 2011–REVISED FEBRUARY 2012Current RegulationThe PWM chopping current is set by a comparator,which compares the voltage across a current sense resistor,multiplied by a factor of 8,with a reference voltage.The reference voltage is input from the VREF pin.The full-scale (100%)chopping current is calculated as follows:(1)Example:If a 0.22-Ωsense resistor is used and the VREFx pin is 3.3V,the full-scale (100%)chopping current is 3.3V/(8*0.22Ω)=1.875A.The reference voltage is also scaled by an internal DAC that allows torque control for fractional stepping of a bipolar stepper motor,as described in the "Microstepping Indexer "section below.When a winding is activated,the current through it rises until it reaches the chopping current threshold described above,then the current is switched off for a fixed off time.The off time is determined by the values of a resistor and capacitor connected to the RCA (for bridge A)and RCB (for bridge B)pins.The off time is approximated by:(2)To avoid falsely tripping on transient currents when the winding is first activated,a blanking period is used immediately after turning on the FETs,during which the state of the current sense comparator is ignored.The blanking time is determined by the value of the capacitor connected to the RCx pin and is approximated by:(3)Decay ModeDuring PWM current chopping,the H-bridge is enabled to drive through the motor winding until the PWM current chopping threshold is reached.This is shown in Figure 2,Item 1.The current flow direction shown indicates positive current flow in the step table below.Once the chopping current threshold is reached,the H-bridge can operate in two different states,fast decay or slow decay.In fast decay mode,once the PWM chopping current level has been reached,the H-bridge reverses state to allow winding current to flow in a reverse direction.If synchronous rectification is enabled (SRn pin logic low),the opposite FETs are turned on;as the winding current approaches zero,the bridge is disabled to prevent any reverse current flow.If SRn is high,current is recirculated through the body diodes,or through external Schottky diodes.Fast-decay mode is shown in Figure 2,Item 2.In slow-decay mode,winding current is re-circulated by enabling both of the low-side FETs in the bridge.This is shown in Figure 2,Item 3.If SRn is high,current is recirculated only through the body diodes,or through external Schottky diodes.In this case fast decay is always used.Drive current Slow decay (brake)Fast decay (reverse)0.6CC FD DECAY V t R C In V æö·=··ç÷èøDRV8818SLVSAX9A –SEPTEMBER 2011–REVISED FEBRUARY 2012Figure 2.Decay ModeThe DRV8818also supports a mixed decay mode.Mixed decay mode begins as fast decay,but after a period of time switches to slow decay mode for the remainder of the fixed off time.Fast and mixed decay modes are only active if the current through the winding is decreasing;if the current is increasing,then slow decay is always used.Which decay mode is used is selected by the voltage on the DECAY pin.If the voltage is greater than 0.6x V CC ,slow decay mode is always used.If DECAY is less than 0.21x V CC ,the device operates in fast decay mode when the current through the winding is decreasing.If the voltage is between these levels,mixed decay mode is enabled.In mixed decay mode,the voltage on the DECAY pin sets the point in the cycle that the change to slow decay mode occurs.This time can be approximated by:(4)Mixed decay mode is only used while the current though the winding is decreasing;slow decay is used while thecurrent is increasing.Operation of the blanking,fixed off time,and mixed decay mode is illustrated in Figure 3.ONITRIPONPWM PWMWindingCurrentRCxVoltageDECAYDRV8818SLVSAX9A–SEPTEMBER2011–REVISED Figure3.PWMMicrostepping IndexerBuilt-in indexer logic in the DRV8818allows a number of different stepping configurations.The USM1and USM0 pins are used to configure the stepping format as shown in the table below:USM1USM0STEP MODE00Full step(2-phase excitation)011/2step(1-2phase excitation)101/4step(W1-2phase excitation)11Eight microsteps/stepsThe following table shows the relative current and step directions for different settings of USM1and USM0.At each rising edge of the STEP input,the indexer travels to the next state in the table.The direction is shown with the DIR pin high;if the DIR pin is low the sequence is reversed.Positive current is defined as xOUT1=positive with respect to xOUT2.Note that the home state is45degrees.This state is entered at power-up or device reset.The HOMEn output pin is driven low in this state.In all other states it is driven logic high.分销商库存信息:TIDRV8818PWP DRV8818PWPR DRV8818EVM。

DRV8840EVM;DRV8842EVM;中文规格书,Datasheet资料

User's GuideSLVU410–April2011CPG005_DRV88xx Evaluation Modules This document is provided as a supplement to the DRV8840and DRV8842datasheets.It details thehardware implementation of the CPG005_DRV88xxEVM Customer Evaluation Module(EVM).On thisdocument,DRV88xx will be used interchangeably to refer to any of the aforementioned devices.Contents1Block Diagram (2)1.1Power Connectors (2)1.2Test Stakes (2)1.3Jumpers (2)1.4Motor Outputs (3)2Installing Drivers And Software (4)2.1Installing the FTDI USB Driver (4)2.2Installing the CPG004_DRV88xx Evaluation Board Windows Application Software (4)2.3Running the Windows Application Software (4)3The Windows Application (4)3.1The Menu (7)3.2DRV88xx GPIO Control Signals (7)3.3Updating DAC Output for Current Control(VREFA and VREFB) (8)3.4DC Motor Speed Control(PWM) (8)4Schematic (9)List of Figures1AVREF Select Jumper Configuration (3)2DECAY Select Jumper Configuration (3)3DRV8840Tab (5)4DRV8842Tab (6)5GPIO Control Signals (7)6Current Control (8)7PWM Control (9)1 SLVU410–April2011CPG005_DRV88xx Evaluation ModulesSubmit Documentation FeedbackCopyright©2011,Texas Instruments Incorporated/Where DRV88xx stands for one of DRV8840 or DRV8842Block Diagram 1Block Diagram1.1Power ConnectorsThe CPG005_DRV88xx Customer EVM offers access to VM (Motor Voltage)power rail via a terminalblock (J1).A set of test clips in parallel with the terminal block allows for the monitoring of the input power rail.User must apply VM according to datasheet recommended parameters.NOTE:VDD for logic and microcontroller is derived from USB interface.1.2Test StakesEvery pin on the DRV88xx device has been brought out to a test stake.A label on the silkscreen identifies each signal.For those pins that change functionality depending on device flavor,a table is provided with corresponding function name on its particular column.1.3JumpersThere are only three jumpers the user must configure as detailed below.Default configuration assumes microcontroller resources are being utilized.As an alternative,a variable resistance is provided on the opposing jumper configuration.2CPG005_DRV88xx Evaluation ModulesSLVU410–April 2011Submit Documentation Feedback Copyright ©2011,Texas Instruments Incorporated /(a)(b)11From PotFrom DACTo configure the AVREF select jumper:(a) Use position JP2-1:2 to select the MSP430 DAC output (default).(b) Use position JP2-2:3 to select the respective variable resistancepotentiometer.This jumper should not be left open as lack ofreference voltage on the device will minimize current sourcinginto the respective H Bridge,resulting in very poor motion orno motion at all.(a)(b)11From PotFrom DACTo configure the DECAY select jumper:(a) Use position JP3-1:2 to select the MSP430 GPIO functionality (default).(b) Use position JP3-2:3 to select the respective variable resistancepotentiometer.Allowing the jumper to not be placed,will result in the device operating under mixed decay mode. Block Diagram1.3.1AVREF Select Jumper (JP2)Figure 1.AVREF Select Jumper Configuration1.3.2DECAY Select Jumper (JP3)Figure 2.DECAY Select Jumper Configuration1.4Motor OutputsThere are two ways of connecting the DC motor into the CPG005_DRV88xx Evaluation Module:two pin header (J4)or two position terminal block (J3).Although feasible,we do not recommend the connection of any motor into the test clips as these are Kelvin connections and not rated for high current output.3SLVU410–April 2011CPG005_DRV88xx Evaluation Modules Submit Documentation Feedback Copyright ©2011,Texas Instruments Incorporated /Installing Drivers And Software 2Installing Drivers And Software2.1Installing the FTDI USB DriverInstructions on how to install the FTDI USB driver on a Windows based computer are detailed in the“USB_Drivers_Install_Readme.pdf”file supplied with the CD inside the USB_Driver folder.2.2Installing the CPG004_DRV88xx Evaluation Board Windows Application SoftwareThe Windows application for the CPG005based EVM’s is the same Windows Application as for theCPG004based EVM’s.Copy the contents of the“WindowsApplication”folder provided within the CD,into your hard disk.2.3Running the Windows Application SoftwareTo run the application,double click the CPG004_DRV88xxEVM.exe application icon found on the samefolder the application was extracted into.3The Windows ApplicationThe CPG004_DRV88xxEVM Windows application is the software counterpart for the CPG004_DRV88xxEVM.It allows the PC computer to connect to the MSP430F1612microcontroller though an USB interfacechip.Once connection is established and commands are sent,microcontroller takes care of configuringcontrol signals and administering certain levels of automation,such as PWM output.The graphical user interface(GUI)has been designed to allow for all of the DRV88xx device’s functionalityto be tested without having to intervene with the hardware,except for the proper configuration of jumpers,when needed.Figure3shows the CPG004_DRV88xxEVM.exe main screen.The application is divided into several tabs:One for each one of the available devices.The menu contains items to configure and enable/disable theserial port.4CPG005_DRV88xx Evaluation Modules SLVU410–April2011Submit Documentation FeedbackCopyright©2011,Texas Instruments Incorporated/ The Windows ApplicationFigure3.DRV8840TabOn the CPG004DRV88xx EVM Windows Application there are two tabs usable with the CPG005basedEVMs.They are very similar and refer to the differences in the two devices,namely the ENABLE/PHASEinterface and the IN1/IN2interface.Everything else will operate in the same fashion.All the control signals needed to control motor enablement(ENABLE or INx),direction of rotation(PHASEor the respective combination of the INx pins),current control(through VREF)and PWM control for bothenablement and direction control signals are made available.Access to the DAC responsible of generating the VREF analog voltage is achieved by moving a simpleslider.A label offers information on what this reference voltage should be on a scale ranging from0V to2.5V.Similar sliders allow the control of PWM Duty Cycle on the ENABLE and PHASE pins(IN1and IN2on theDRV8842).This will allow for the control of both DC motor speed and direction.5 SLVU410–April2011CPG005_DRV88xx Evaluation ModulesSubmit Documentation FeedbackCopyright©2011,Texas Instruments Incorporated/The Windows Application Figure4.DRV8842TabA look at the DRV8842tab on the CPG004DRV88xx EVM Windows Application.This tab is virtually identical to the DRV8840tab.Only labels of respective signals differ:•ENABLE becomes IN1•PHASE becomes IN26CPG005_DRV88xx Evaluation Modules SLVU410–April2011Submit Documentation FeedbackCopyright©2011,Texas Instruments Incorporated/DRV8840DRV8842 The Windows Application3.1The MenuThe menu at the top of the application offers a series of quick options for how the COM port is to behave.File:Exit –Terminates the applicationSettings:Port –Selects from COM1to COM4.Default is COM4.The serial port's actual port number defaults to what we have specified on the“USB_Drivers_Install_Readme.pdf ”.However,any port between COM 1and COM 4are equally usable.Connect:Opens the serial port.When this menu item is pressed,its caption changes to “Disconnect ”.Disconnect:Closes the serial port.When this menu item is pressed,its caption changes to “Connect ”.After opening the application,the order of events should be:1.Go to Settings →Port and choose the COM Port where the FTDI device has been configured to work.If the COM port is 4,then this step can be skipped,as application defaults to COM4.2.Press Connect.If the port is available,the menu changes the “Connect “caption to “Disconnect “.PressDisconnect to disable the serial communications.3.After pressing any command button,<1><0><0>should return on the text box as an acknowledge.The text box also changes from red to green.4.The application is ready for use.3.2DRV88xx GPIO Control SignalsOnce the application is communicating with the interface board,the control signals can be actuated bychecking or un-checking check boxes on the Control Signals frame.Functionality of control signals is identical across the platform.A checked checkbox translates to a HI level on the respective control signal.Unchecked checkboxes translate to a LO level on the respective control signals.Both tabs (DRV8840and DRV8842)will have a very similar set of control signals.Changes to reflectcorrect signal naming have been incorporated.Figure 5.GPIO Control Signals7SLVU410–April 2011CPG005_DRV88xx Evaluation Modules Submit Documentation Feedback Copyright ©2011,Texas Instruments Incorporated /VREF = DAC_VALUE · 2.5V ¾4095The Windows Application 3.2.1About DECAYThe DECAY pin is in reality a triple state input.The GPIO operates as HI and LO according to thecheckbox.To have the DECAY pin floating,engaging mixed decay mode,simply remove the decayjumper JP3.3.3Updating DAC Output for Current Control (VREFA and VREFB)If the DRV88xx has been configured to accept VREF analog voltages through the microcontroller DAC outputs (refer to Jumpers section),then the slider bar on the Current Control frame can be used to set the VREF voltage.The label below the slider bar will inform the user what this analog voltage should be set to,if proper communications have been established with the EVM module.Figure 6.Current ControlThe 12-bit DAC channels 0/1are connected to the DRV88xx VREF analog inputs VREF.Changing the DAC digital value from 0to 4095,changes the analog voltage at the respective VREF pin from 0V to 2.5V respectively,following the equation:(1)Where:VREF is the output voltage.DAC_VALUE is a number from 0to 4095.3.4DC Motor Speed Control (PWM)For the purpose to control DC motor speed and direction,sliders have been provided which apply a PWM to the ENABLE and PHASE lines (IN1and IN2on the DRV8842variant).Each PWM slider consists of an 8-bit number so positions from 0to 255are obtained.A label below the slider bar informs the user what the obtained duty cycle should be,if proper communications have been established with the EVM module.The MSP430microcontroller directly transforms this 8-bit number into the respective duty cycle.PWMfrequency is around 31.25kHz.8CPG005_DRV88xx Evaluation ModulesSLVU410–April 2011Submit Documentation Feedback Copyright ©2011,Texas Instruments Incorporated / SchematicDRV8840DRV8842Figure7.PWM Control4SchematicA schematic is available in the form of a PDF file(“CPG005_Schematic.pdf”)inside the EVM_Relatedfolder on the supplied CD.9 SLVU410–April2011CPG005_DRV88xx Evaluation ModulesSubmit Documentation FeedbackCopyright©2011,Texas Instruments Incorporated/IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standardwarranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products andapplications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or awarranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,andacknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products arespecifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet militaryspecifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products aredesignated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and /automotiveAutomotiveMicrocontrollers Video and Imaging /videoRFID Wireless /wireless-appsRF/IF and ZigBee®Solutions /lprfTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated/分销商库存信息:TIDRV8840EVM DRV8842EVM。

艾森高压电路保护器产品说明书

Eaton MPN6203VEAXXSWEaton Magnum low voltage power circuit breaker, Magnum PXR,Narrow frame, 2000 A, 65 kA, Three-pole, Fixed vertical mounting,No trip unitGeneral specificationsEaton Magnum low voltage power circuitbreakerMPN6203VEAXXSW78668960224614.6 in16.8 in12.5 in95 lbNEMA Compliant CCC MarkedCE Marked SABA Listed ANSIUL ListedCSA CertifiedLloyd's Register Certified KEMA CertifiedABS CertifiedDNV GL CertifiedProduct Name Catalog NumberUPCProduct Length/Depth Product Height Product Width Product Weight Compliances CertificationsNarrow Three-pole Magnum PXR Narrow MagnumThree-pole2000 A65 kAIC65 kAIC 2000 A Zone selective interlocking application paperMagnum circuit breakers with Power Xpert Release trip units product aidSelevctive coordination application paper - IA0120000E3Magnum PXR and PD-SB standard and narrow frame UL Certificate of ComplianceMagnum PXR and PD-SB double and double narrow frame UL Certificate of CompliancePower Xpert Release trip unit for Magnum PXR circuit breakers PXR20/25 user manualMicrosoft Word - Power Xpert Protection Manager Quick StartGuide.docxMagnum PXR low voltage power circuit breakers user manualPower Xpert Protection Manager x32 22.06 1Power Xpert Protection Manager x64 22.6 1FrameNumber of poles Type FrameSeriesNumber of polesRated uninterrupted current (Iu)Interrupt ratingInterrupt ratingRated uninterrupted current (Iu)Application notesBrochuresCatalogsCertification reportsManuals and user guides Software, firmware, and applicationsEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All Rights Reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmediaEaton Specification Sheet - MPN6203VEAXXSW Low voltage circuit breakers guide spec Magnum PXR 20/25 electronic trip units time current curves Safer by design: arc energy reduction techniques Cyber security white paperMolded case and low-voltage power circuit breaker healthSpecifications and datasheetsTime/current curvesWhite papers。

CW1274 Datasheet说明书

CW1274 4~7节电池保护IC功能特性●过充电保护•阈值范围3.650V、3.850V、4.175V~4.350V,25mV步进,±25mV精度●过放电保护•阈值范围2.300V~2.800V,100mV步进,±30mV精度●放电过流保护•过流检测1阈值范围0.050V~0.100V,±5mV精度•过流检测2阈值范围0.100V~0.200 V,,±10mV精度•短路保护阈值范围0.200V~0.500V,±20mV精度●充电过流保护•阈值范围-0.010V~-0.050V,±5mV精度●温度检测功能充放电高低温保护,温度外部可设●均衡功能●断线检测功能●负载检测功能●级联功能●低功耗设计•工作状态20μA (25°C)•休眠状态5μA (25°C)●封装形式:SSOP24应用领域●吸尘器●电动工具●电动自行车●后备电源●锂离子及锂聚合物电池包基本描述CW1274系列产品是一款高度集成的4~7串锂离子电池或锂聚合物电池保护芯片。

CW1274为电池包提供过充、过放、充放电过流、断线、充放电过温保护以及均衡功能,并支持芯片级联使用。

CW1274 典型应用框图CW1274产品选择指南CW1274 X X X X封装形式,S: SSOP24参数类型,从A到Z电池类型,L:代表锂离子电池F:代表磷酸铁锂电池功能和版本信息,从A 到Z产品目录CW1274 引脚排列图CW1274CW1274 绝对最大额定值注意:绝对最大额定值是指无论在任何条件下都不能超过的额定值。

如果超过此额定值,有可能造成产品损伤。

ESD等级额定工作电压CW1274电气特性除特殊说明外T A=25°CCW1274*2充放电温度保护温度取决于不同电阻的设定,放电低温保护温度默认为充电过温保护温度-20℃,即充电低温保护温度为0℃,则放电低温保护温度为-20℃*3所有过电流保护(包括过流1,过流2和短路保护)解除延迟时间均为60msCW1274原理框图CW1274 功能描述正常状态所有电池电压处于过充检测电压(V OC)和过放检测电压(V OD)之间,且CS端子电压处于过流检测电压(V EC1)和充电过流检测电压(V COC)之间时,CW1274处于正常工作状态。

SC8804高效率,同步,升压充电降压放电双向控制器.pdf

上海南芯半导体科技有限公司SC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA SC8804 高效率, 同步, 升压充电降压放电双向控制器Copyright © 2016, 上海南芯半导体科技有限公司具体应用信息请联系application@SC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA 上海南芯半导体科技有限公司5应用电路图DIR = Low, 充电(charging)DIR = High, 反向放电(discharging)2具体应用信息请联系application@ Copyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd.SC8804 DATASHEET上海南芯半导体科技有限公司SOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDACopyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd. 具体应用信息请联系application@ 36 管脚设置及功能简介C P _HC P _LN CV B U SS N S 1N P G N DN CS N S 1PSC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA 上海南芯半导体科技有限公司4具体应用信息请联系application@ Copyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd.SC8804 DATASHEET 上海南芯半导体科技有限公司SOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDACopyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd. 具体应用信息请联系application@ 5SC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA 上海南芯半导体科技有限公司7电气规格7.1绝对最大耐压在通风温度范围之内(除非另外标注)(1)6具体应用信息请联系application@ Copyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd.SC8804 DATASHEET 上海南芯半导体科技有限公司SOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDACopyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd. 具体应用信息请联系application@ 7SC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA 上海南芯半导体科技有限公司7.4电气性能T J= 25°C and V BUS = 12V, V BAT = 5V, R SS1 = R SS2= 1kΩ unless otherwise noted.8具体应用信息请联系application@ Copyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd.SC8804 DATASHEET 上海南芯半导体科技有限公司SOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDACopyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd. 具体应用信息请联系application@ 9SC8804 DATASHEETSOUTHCHIP CONFIDENTIAL, DISCLOSURE UNDER NDA 上海南芯半导体科技有限公司10具体应用信息请联系application@ Copyright © 2016, Southchip Semiconductor Technology (Shanghai) Co., Ltd.8和截止电压的对应关系如下表所示:表格 1 CSEL 电阻设定充电截止电压SC8804通过R SNS1和R SNS2分别检测VBUS 端和VBAT 端充电电流,如下图所示:电池端充电电流RVRRR1)R SNSx需连接在MOS管和输入/输出电容之间2)R SS1/R SS1’为一对电阻对,阻值需相等,同理,R SS2/R SS2’也需相等,典型值为1 kΩ若需要调整R SNSx的阻值,则对应的R SSx/R SSx’阻值也需要),1) 2) 3) 4)SC8804支持充电自适应功能。

8845A编程手册中文完全版

配有 IEEE-488 接口的仪器通过一组标准的互相连接的电缆相互通信,详细信息请参见 IEEE-488.1 标准文档。

IEEE-488 接口连接器位于仪表的后面板上。

配置 RS-232 端口

译

翻 RS-232 通信接口允许万用表与主机或终端之间进行 ASCII、异步、串行通信。下文描述

了配置 RS-232 端口的过程。设置 RS-232 端口为程控的活动端口,请参阅上文的“选择程控

者 0. conf:volt:dc 0.1 将直流范围设置为手动和 100 mV。

3 volt:dc:nplc 0.02 将 NPLC 设置为更快的读取速率 4 1/2 位。

爱好 DT8 zero:auto 0

关闭自动归零。

表trig:sour imm 仪trig:del 0

trig:coun 1

设置立即触发。 将触发延迟设置为零。 将触发计数设置为 1 或指定更大的数字。

表或<BACKSPACE>键删除前一个字符。退格键被返回显示到主机终端。 注意

仪 ^C (CNTRL C)是 RS-232 中相当于 IEEE-488 DCI(设备清除)的命令,因此输出“1>”后 面跟着回车和换行。 当使用计算机程序控制万用表时时,采用计算机模式。在这种模式下,请求信息通过查

询方式返回,接口消息通过命令方式排队返回。字符不会在主机上回显,禁止使用命令提示

述。

者 0. 下表给出了适用于万用表的规范以及简短的说明。这些规范符合 IEEE-488.2 的要求。

3 IEEE-488.1 文档的附录 C 包含了每个规范的完整描述。

好 8IEEE-488 功能规范

T IEEE-488 子集 爱 D SH1

DRV8832电机驱动芯片及其应用

DRV8832电机驱动芯片及其应用作者:李旭东陆宇炯张彪来源:《科学与财富》2015年第07期摘要:DRV8832是一种针对电池供电的玩具、打印机和其他低电压供电的集成电机驱动芯片,驱动器具有一个H型桥,可驱动一个直流电机或一个单相步进电机的绕组。

文中介绍了该芯片的特点、引脚功能和工作原理。

并给出了一种基于DRV8832和单片机STC11F01的电机控制电路。

关键词:电机;DRV8832;驱动器;单片机中图分类号:TP29 文献标识码:B1 概述DRV8832[1]是美国TI公司生产的电机驱动专用芯片。

用于电池供电的玩具、打印机和其他低电压供电的移动控制的应用中对电机驱动的解决方案。

一片DRV8832中具有一个H型桥,可驱动一个直流电机或一个单相步进电机的绕组。

其工作电压范围为2.75V ~ 6.8V,电流可达1A。

为确保电池有更长的使用寿命并电机转速的恒定,DRV8832内部提供了PWM电压控制模式,可以通过输入脚编程控制电压。

并提供一个输出的参考电压。

DRV8832芯片还提供完善的保护措施,其中包括过流保护、短路保护、欠压保护和过热保护等功能。

同时,DRV8832具备电流限制功能用于电机启动或堵转时对电机的控制,此外,也可通过故障输出管脚向控制器发出一个故障信号。

2 引脚功能和主要特点2.1 引脚功能DRV8832有两种封装形式。

一种是10脚的MSOP封装DRV8832D GQ,另一种是10引脚的WSON封装DRV8832DRC,两种封装的电特性完全相同,图1为DRV8832的引脚排列图。

各引脚说明如下:Fig.1 DRV8832 pins diagram引脚1、3(OUT2、OUT1):两输出引脚,其中每一个分别与电机绕组的一端相连;引脚2(ISENSE):电流取样电阻输入端,用于检测负载电流;引脚4(VCC):电源端,通常接0.1μF旁路电容;引脚5(GND):接地端;引脚6(FAULTn):故障信号端;引脚7(VSET):电压设置输入端,用于控制输出电压;引脚8(VREF):参考电压输出端,用于输出参考电压;引脚9、10(IN1、IN2):输入控制端1、2,用于逻辑控制H电桥的输出1、2。

MB90F884APMC中文资料