HDL & Therapy

hdl的课程设计

hdl的课程设计一、课程目标知识目标:1. 让学生掌握hdl(假设为高级编程语言)的基本语法和结构,能够正确编写简单的程序。

2. 使学生了解hdl在工程领域的应用,理解其重要性和实用价值。

3. 帮助学生掌握hdl编程中的常见错误类型及其解决办法。

技能目标:1. 培养学生运用hdl进行程序设计的能力,能够独立完成指定任务。

2. 培养学生运用调试工具,对程序进行调试和优化的能力。

3. 培养学生通过查阅资料,解决编程过程中遇到的问题的能力。

情感态度价值观目标:1. 激发学生对编程的兴趣,培养其主动学习和探究的精神。

2. 培养学生团队协作意识,使其学会与他人共同解决问题。

3. 培养学生严谨、认真的学习态度,使其认识到编程在工程领域的重要作用。

课程性质:本课程为实践性较强的学科,结合理论知识与实际操作,使学生能够在实践中掌握hdl编程技能。

学生特点:学生处于高年级阶段,具备一定的编程基础和自学能力,但个体差异较大。

教学要求:结合学生特点,采用分层教学,注重个体差异,提高学生的实践操作能力和解决问题的能力。

在教学过程中,注重引导学生主动探究,培养学生的创新意识。

通过课程学习,使学生能够达到课程目标所要求的具体学习成果。

二、教学内容1. hdl基本概念与语法:包括hdl的数据类型、运算符、控制结构等基本知识,参照教材第一章内容。

2. hdl程序结构设计:学习如何构建模块化的程序结构,理解层次化设计方法,参考教材第二章。

- 任务分解与模块设计- 参数传递与信号连接3. hdl编程实践:通过实例分析,让学生动手编写简单的hdl程序,涵盖教材第三章内容。

- 基础程序设计:如计数器、序列检测器等- 简单算法实现:如排序、查找等4. hdl程序调试与优化:教授学生如何使用调试工具,分析程序中的错误,并进行优化,参照教材第四章。

- 常见错误类型与分析方法- 调试工具的使用技巧- 程序优化策略5. hdl应用案例分析:通过实际工程项目案例分析,让学生了解hdl的应用领域,参考教材第五章。

硬件描述语言VHDL基本概念

信号模式表示端口的数据流向,有以下五 种:IN(流入实体)、OUT(流出实体)、 INOUT(双向端口)、BUFFER(带有反馈的 输出端口,该端口只能有1个驱动源)和 LINKAG(无特定方向)。

20世纪70年代末至80年代初,美国国防部提出了 VHSIC(Very High Speed Integrated Circuit)计划, 其目标是为了开发新一代集成电路。

为了配合这一计划,1983年美国国防部与TI公司、 IBM公司和Intermerics公司联合签约,开发VHSIC HDL,即VHDL。在1985年开发小组发布了最后版本 VHDL V7.2,同时开始着手标准化工作,到1987年12月, VHDL经过多次修改后,被IEEE接受为第一个标准HDL, 即IEEE Std 1076-1987。

目前公布的最新VHDL标准版本是

IEEE Std 1076-2008。

2.2 1位全加器的描述实例

1位全加器有3个输入端a、b、c_in和 2个输出端sum、c_out。

它是由2个半加器和1个或门构成。

a

sum

b

全加器

a

temp_sum

sum

U1

U2

b 半加器

半加器 temp_c2

c_in

c_out c_in

1个设计实体由1个实体声明和若干个结构 体组成。实体声明是设计实体的接口部分,它 表示设计实体对外部的特征信息;结构体是设 计实体的实现方案描述。

1个设计实体中的若干个结构体,分别代表 同一实体声明的不同实现方案。

HDL简介与操作

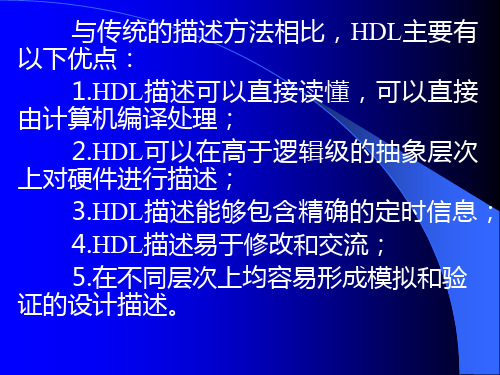

HDL简介与操作1、硬件描述语言(HDL)硬件描述语言(HDL)是相对于一般的计算机软件语言如C,Pascal而言的。

HDL是用于设计硬件电子系统的计算机语言,它描述电子系统的逻辑功能、电路结构和连接方式。

设计者可以利用HDL程序来描述所希望的电路系统,规定其结构特征和电路的行为方式;然后利用综合器和适配器将此程序变成能控制FPGA和CPLD内部结构、并实现相应逻辑功能的门级或更底层的结构网表文件和下载文件。

硬件描述语言具有以下几个优点:a.设计技术齐全,方法灵活,支持广泛。

b.加快了硬件电路的设计周期,降低了硬件电路的设计难度。

c.采用系统早期仿真,在系统设计早期就可发现并排除存在的问题。

d.语言设计可与工艺技术无关。

e.语言标准,规范,易与共享和复用。

就FPGA/CPLD开发来说,VHDL语言是最常用和流行的硬件描述语言之一。

下面将主要对VHDL语言进行介绍。

2、VHDL语言简介VHDL是超高速集成电路硬件描述语言的英文字头缩写简称,其英文全名是Very-High-Speed Integrated Circuit Hardware Description Language。

它是在70-80年代中由美国国防部资助的VHSIC(超高速集成电路)项目开发的产品,诞生于1982年。

1987年底,VHDL 被IEEE(The Institute of Electrical and产Electronics Engineers)确认为标准硬件描述语言。

自IEEE公布了VHDL的标准版本((IEEE std 1076-1987标准)之后,各EDA公司相继推出了自己的VHDL设计环境。

此后,VHDL在电子设计领域受到了广泛的接受,并逐步取代了原有的非标准HDL。

1993年,IEEE对VHDL进行了修订,从更高的抽象层次和系统描述能力上扩展VHDL的内容,公布了新版本的VHDL,即ANSI/IEEE std1076,1993版本。

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

hdl语言的层次概念

hdl语言的层次概念

VHDL语言的层次概念指的是VHDL代码的结构,包括实体、部件、组件、过程和程序结构。

实体是VHDL代码的顶级结构,它提供了一个完整的模型,描述了其中的所有细节。

部件是实体的基本组成部分,它们描述了不同的模型组件,如外设、存储器和多位运算器等。

组件是部件的抽象,用于简化VHDL模型。

它们不涉及具体模型中部件之间的连接,而只关注模型中各部分如何工作。

过程是VHDL中的一种指令,它指定了特定结构的操作。

程序结构是VHDL中执行特定任务的指令顺序,它决定了VHDL模型中各部分如何工作。

;。

高密度胆固醇(HDL) 直接测定法

目录1. 检测原理2. 标本采集与处理2.1 受检者的准备2.2 静脉采血2.3 抗凝剂2.4 标本处理3. 试剂3.1 试剂3.2 校准血清3.3 试剂与校准血清的稳定性4. 仪器5. 操作6. 计算7. 操作性能7.1 精密度7.2 准确度7.3 灵敏度7.4 可报告范围7.5 特异性7.6 干扰8. 参考值9. 临床意义附录A: 参数1. 检测原理1. 试剂1使血清中低密度脂蛋白和极低密度脂蛋白经化学反应被消除。

胆固醇酯酶胆固醇酯+ H2O -------------------- 胆固醇+ 脂肪酸胆固醇氧化酶胆固醇+ O2 ------------------------- 胆淄烯酮+ H2O2过氧化氢酶H2O2 ------------------ O2+H2O2. 试剂2中的变性剂释放出高密度脂蛋白后,对HDL进行测量。

胆固醇酯酶胆固醇酯+ H2O -------------------- 胆固醇+ 脂肪酸胆固醇氧化酶胆固醇+ O2 ------------------------- 胆淄烯酮+ H2O2过氧化物酶H2O2 + 4-氨基安替比林+ HDAOS -------------------- 醌染料+ 4H2O在600nm醌染料的吸光度的与胆固醇的含量相关。

2.标本采集与处理2.1 受检者的准备:病人空腹12h,不饮酒24h后采集血样。

体检对象抽血前应有两周的的正常状况记录。

妊娠后期各项血脂都会增高,应在产后或中哺乳后3个月检验才能反应其基本血脂水平。

注意有无应用影响血脂的药物,如降血脂药、避孕药等。

此外,对于体检者,采血的季节都应做相关记录,因为血脂水平有季节性变动,为了前后比较应在每年同一季节检验,应嘱体检对象在抽血前24小时内不做剧烈运动。

2.2 静脉采血:除非是卧床的病人,一般在采血时取坐位。

体位影响水分在血管内外的分布,会影响测试项目的浓度。

在采血前至少应静坐5分钟,一般从肘静脉取血,使用止血带的时间不超过1分钟,穿刺成功后立即松开止血带。

HDL简介

一、HDL不是硬件设计语言过去笔者曾碰到过不少VHDL或Verilog HDL的初学者问一些相似的问题,诸如如何实现除法、开根号,如何写循环语句等等。

在这个论坛上,也时常能看到一些网友提出这一类的问题。

对于这些问题,首先要明确的是VHDL和Veriglog并非是针对硬件设计而开发的语言,只不过目前被我们用来设计硬件。

HDL是Hardware Description Language的缩写,正式中文名称是“硬件描述语言”。

也就是说,HDL并不是“硬件设计语言(Hardware Design Langu age)”。

别看只差这一个单词,正是这一个单词才决定了绝大部分电路设计必须遵循RTL的模式来编写代码,而不能随心所欲得写仅仅符合语法的HDL代码。

二、HDL的来历之所以是“硬件描述语言”,要从HDL的来历说起。

VHDL于1980年开始在美国国防部的指导下开发,完成于1983年,并于1987年成为IEEE 的标准。

当初开发这种语言,是出于美国国防部采购电子设备的需要。

美军的装备采购自私人企业,时常要面对这样一种风险:如果某种武器大量装备部队,而其中某个零件的供应商却在几年后倒闭了,那这种武器的再生产、维修和保养都会出现大问题。

而电子设备、尤其是集成电路的内部结构较为复杂,若出现前面所说的情况要找其他公司生产代用品非常困难。

于是美国防部希望供应商能以某种形式留下其产品的信息,以保证一旦其破产后能由其他厂商迅速生产出代用品。

显然,当初的设计文档显然是不能交出来的,这在美国会涉及商业机密和知识产权问题。

于是美国防部就想出了一种折衷的方法——描述硬件的语言,也就是VHDL。

通过VHDL,供应商要把自己生产的集成电路芯片的行为描述出来:比如说,加了什么样的信号后过多少时间它能输出什么等等。

这样,如果有必要让其他厂商生产代用品,他们只需照着VHDL 文档,设计出行为与其相同的芯片即可。

这样的代用品相当于是新厂商在不了解原产品结构的情况下独立设计的,所以不太会涉及知识侵权。

HDL 第三方产品手册说明书

第三方产品手册目录公司简介背景音乐系统遮阳系统环境控制系统012325262728333437394243465254596530050608111503监测环境系统092129安防系统31照明系统357寸迷你主机/4寸迷你主机中央主机扬声器Kaiterra墙内检测仪睿石mini检测仪协议开合电机蛇形帘天棚帘转弯器、弯轨系列轨道安装技术支持中央空调网关/HOMEKIT 迷你家居款轨道条形格栅灯系列条形泛光灯系列90°可调格栅灯系列磁吸轨道灯系列吊线灯系列格栅射灯系列射灯系列212嵌入式射灯室内被动红外入侵探测器(嵌入式) S-one 智能门锁背景音乐系统高品质的音乐,不仅仅在手机、在PC端、在随身听、电视、在播放器,它更在我们人居的每一个角落中响起,同步我们最爱的歌曲,更有最恰到好处的人工语音,提醒我们家中的状态。

03页码04页码4x20W双分区 全无损格式解码专业DSP音频处理喜马拉雅网络电台超远距离蓝牙播放HD全双工对讲通话安卓6.x,7寸IPS显示屏Airplay/DLNA/Qplay推送WIFI连接,无线掌控,互联互通超强的无线实时对讲、音乐控制4英寸全面屏设计音源:本地音乐、喜马拉雅、第三方音乐APP、蓝牙、DLNA、AUX 完美适配QQ音乐、酷狗音乐等热门第三方音乐APP 支持Micro SD卡、U盘读取播放音乐支持对讲、呼叫功能,可与多台DM839或DM858进行对讲、呼叫支持AUX输入和输出功能支持RS485控制支持WIFI连接拥有定时功能三种情景播放模式和自定义模式选择:Party、Sleep、Relax、Customize 支持门铃联动DM858极简风格UI 超全的曲库最精准的推荐最懂你的音乐伴侣只因云雀之声便知流水雀鸟之音温馨的呼叫通话你我之间只是一键的距离有我就是幸福一家DM839因为相信 所以相遇 追梦路上 无所畏惧 每一段拼搏旅程都彰显着不平凡4寸迷你主机独特的气场 豪华的气质 丰富节目源 8-72分区殿堂级音质 8-12区自由点播与推送无线DLNA推送全无损格式解码2x100W+14x30W在线升级APP全宅无线控制4分区每分区2x30W/8Ω100-240V / 50/60Hz交换机/“手拉手”级联支持无线控制备注:AM8300只配套AM8328使用中央主机AM8328它,天生的王者 它,无限的潜力 它,殿堂级音质流畅的线条,磨砂的表面 你是别墅的主人 它是你一生的伴侣分区扩展机AM830006页码AUX168II功率:20W/8Ω 喇叭单元:6.5"x1,1" x1 最大声压级:102±2dB 有效频率范围:60Hz-20,000Hz 灵敏度:89±2dB规格:97×Ø233mm 开孔尺寸:205-210mm 净重:1.6kgAUX167II功率:20W/8Ω 喇叭单元:5"x1,1"x1 最大声压级:102±2dB 有效频率范围:100Hz-20,000Hz 灵敏度:87±2dB规格:78×Ø205mm 开孔尺寸:180-185mm净重:0.55kgAUX521功率:10W/8Ω 喇叭单元:6.5"x1, 0.75"x1 最大声压级:103±2dB 有效频率范围:90Hz-18KHz 灵敏度:93±2dB规格:70×Ø190mm 开孔尺寸:168-172mm净重:1.0kgAUX644功率:15W/8Ω 喇叭单元:5"x1 最大声压级: 98±2dB 有效频率范围:150Hz-20kHz 灵敏度:86±2dB 规格:280×225×298mm 净重:3.6kg室外全天候防水甲醛、TVOC等环境指标更加在意。

hdl的课程设计

hdl的课程设计一、教学目标本课程的教学目标是让学生掌握HDL(硬件描述语言)的基本语法、编写方法和应用技巧。

通过本课程的学习,学生将能够熟练使用HDL进行数字电路的设计和仿真,提高他们在电子工程领域的实际操作能力。

具体来说,知识目标包括:1.理解HDL的基本概念和特点。

2.掌握HDL的基本语法和编写规则。

3.了解HDL在数字电路设计中的应用。

技能目标包括:1.能够独立编写HDL代码,实现简单的数字电路功能。

2.能够使用HDL进行电路仿真,验证电路的正确性。

3.能够分析HDL代码的性能,进行优化和改进。

情感态度价值观目标包括:1.培养学生对电子工程的兴趣和热情。

2.培养学生团队合作精神和自主学习能力。

3.培养学生对新技术的敏感性和创新意识。

二、教学内容本课程的教学内容主要包括HDL的基本语法、编写方法和应用技巧。

具体安排如下:第1-2章:HDL的基本概念和特点,介绍HDL的发展历程、基本语法和编写规则。

第3-4章:HDL的基本数据类型和运算符,讲解HDL中的基本数据类型、运算符及其使用方法。

第5-6章:HDL的控制语句和函数,介绍HDL中的条件语句、循环语句、函数和过程等控制语句的使用。

第7-8章:HDL的模块化和层次化设计,讲解如何使用模块化和层次化设计方法进行数字电路的设计。

第9-10章:HDL的仿真和测试,介绍HDL仿真工具的使用方法,以及如何进行电路的测试和验证。

第11-12章:HDL在实际项目中的应用,分析HDL在实际项目中的应用案例,提高学生的实际操作能力。

三、教学方法为了提高教学效果,本课程将采用多种教学方法,包括:1.讲授法:教师讲解HDL的基本概念、语法和编写规则,引导学生理解和掌握相关知识。

2.案例分析法:分析实际项目中的应用案例,让学生了解HDL在实际工作中的应用。

3.实验法:安排实验室实践环节,让学生动手编写HDL代码,进行电路仿真和测试。

4.讨论法:学生进行分组讨论,分享学习心得和经验,提高团队合作精神和自主学习能力。

学习HDL的几点重要提示

学习HDL的几点重要提示(zz)学习HDL的几点重要提示1.了解HDL的可综合性问题:HDL有两种用途:系统仿真和硬件实现。

如果程序只用于仿真,那么几乎所有的语法和编程方法都可以使用。

但如果我们的程序是用于硬件实现(例如:用于FPGA设计),那么我们就必须保证程序“可综合”(程序的功能可以用硬件电路实现)。

不可综合的HDL语句在软件综合时将被忽略或者报错。

我们应当牢记一点:“所有的HDL描述都可以用于仿真,但不是所有的HDL描述都能用硬件实现。

”2. 用硬件电路设计思想来编写HDL:学好HDL的关键是充分理解HDL语句和硬件电路的关系。

编写HDL,就是在描述一个电路,我们写完一段程序以后,应当对生成的电路有一些大体上的了解,而不能用纯软件的设计思路来编写硬件描述语言。

要做到这一点,需要我们多实践,多思考,多总结。

3.语法掌握贵在精,不在多30%的基本HDL语句就可以完成95%以上的电路设计,很多生僻的语句并不能被所有的综合软件所支持,在程序移植或者更换软件平台时,容易产生兼容性问题,也不利于其他人阅读和修改。

建议多用心钻研常用语句,理解这些语句的硬件含义,这比多掌握几个新语法要有用的多。

选择VHDL还是verilog HDL?(zz)选择VHDL还是verilog HDL?这是一个初学者最常见的问题。

其实两种语言的差别并不大,他们的描述能力也是类似的。

掌握其中一种语言以后,可以通过短期的学习,较快的学会另一种语言。

选择何种语言主要还是看周围人群的使用习惯,这样可以方便日后的学习交流。

当然,如果您是集成电路(ASIC)设计人员,则必须首先掌握verilog,因为在IC设计领域,90%以上的公司都是采用verilog进行IC设计。

对于PLD/FPGA设计者而言,两种语言可以自由选择HDL与原理图输入法的关系(zz)HDL与原理图输入法的关系HDL和传统的原理图输入方法的关系就好比是高级语言和汇编语言的关系。

hdl硬件描述语言

hdl硬件描述语言

HDL是Hardware Description Language的缩写,即硬件描述语言。

它是一种用于描述数字电路的语言,包括了数字电路的功能、结构和行为等方面。

HDL 通常用于设计和模拟数字电路,以帮助工程师更好地理解数字电路的功能和性能,并在设计电路时提供一种有效的工具。

在HDL中,通常使用的是高级语言来描述电路的功能和行为,比如Verilog和VHDL。

这些语言提供了一些强大的特性,如模块化设计、层次结构、波形仿真等,使得电路的设计和测试变得更加高效、方便和准确。

HDL的设计流程通常包括以下几个步骤:首先,需要将所需的电路功能转化为模块化的设计,比如将复杂的电路分解为多个子模块;其次,需要使用HDL语言编写每个模块的描述,包括模块端口定义、内部逻辑和功能描述等;接下来,需要进行波形仿真以验证电路的功能和性能;最后,需要将HDL代码转化为实际的硬件电路,比如使用FPGA或ASIC等技术将代码烧入硬件芯片中。

总之,HDL是一种用于描述数字电路的语言,它可以帮助工程师更好地理解和设计数字电路,提高电路设计和测试的效率和准确性。

高HDL-胆固醇血症标准

高HDL-胆固醇血症标准

……

正常人血清HDL-胆固醇水平波动于1.1~1.6毫摩尔/升。

当HDL-胆固醇水平>1.6毫摩尔/升时称高HDL-胆固醇血症。

高HDL-胆固醇血症往往引起血清总胆固醇水平的轻度升高,因为血清总胆固醇水平是HDL-胆固醇、LDL-胆固醇和VLDL-胆固醇的总和,但此时其它脂蛋白一胆固醇水平均是正常的。

由于正常的HDL有结合并清除组织内胆固醇的功能,所以HDL-胆固醇水平升高可以防止冠心病的发生。

在美国,一些科学家发现有些家族,其家族成员血中HDL-胆固醇含量显著增高,并且可遗传两三代,他们很少发生冠心病,而且寿命比较长,故又将高HDL-胆固醇血症称为“长寿综合征”。

HDL-胆固醇水平升高最多见于妇女,尤其是接受雌激素治疗者。

HDL-胆固醇水平降低将增加冠心病的危险。

低HDL-胆固醇血症(HDL-胆固醇0.9毫摩尔/升)被列为冠心病的主要危险因素。

低HDL-胆固醇血症可伴有下列三种血清脂质改变:

(1)低HDL-胆固醇血症伴LDL-胆固醇水平升高;

(2)低HDL-胆固醇血症伴高甘油三酯血症;

(3)低HDL-胆固醇血症伴正常血清脂质,即孤立性低HDL-胆固醇血症。

低HDL-胆固醇血症常见于肥胖、吸烟、缺乏运动的人。

吸烟愈

多,HDL-胆固醇水平愈低。

当然也可见于某些疾病,如糖尿病、急性肝炎、肝硬化、肾病综合征、尿毒症和胰腺炎等。

饮食不当,如总热量和碳水化合物摄人过多,也可使HDL-胆固醇水平降低。

此外,长期素食者血清总胆固醇含量虽然不高,但有时可伴有HDL-胆固醇水平降低。

HDL的历史、现状与发展

HDL发展的历史、现状和发展成员:岳俊峰 3113032010 于洋 3113030021一、HDL简介HDL(Hardware Description Language),是一种硬件描述语言。

它是用来描述电子电路(特别是数字电路)功能、行为的语言,可以在寄存器传输级、行为级、逻辑门级等对数字电路系统进行描述。

随着自动化逻辑综合工具的发展,硬件描述语言可以被这些工具识别,并自动转换到逻辑门级网表,使得硬件描述语言可以被用来进行电路系统设计,并能通过逻辑仿真的形式验证电路功能。

设计完成后,可以使用逻辑综合工具生成低抽象级别(门级)的网表(即连线表)。

硬件描述语言在很多地方可能和传统的软件编程语言类似,但是最大的区别是,前者能够对于硬件电路的时序特性进行描述。

硬件描述语言是构成电子设计自动化体系的重要部分。

小到简单的触发器,大到复杂的超大规模集成电路(如微处理器),都可以利用硬件描述语言来描述。

二、HDL语言的发展历史广泛应用的硬件描述语言主要有:ABEL语言、Verilog语言、和VHDL语言,Superlog语言、SystemC等。

其中Verilog语言和VHDL语言最为流行。

下面是几种语言的发展历史。

2.1 VHDL早在1980年,因为美国军事工业需要描述电子系统的方法,美国国防部开始进行VHDL 的开发。

1982年VHDL正式诞生。

1987年,由IEEE(Institute of Electrical and Electro- nics Engineers)将VHDL制定为标准。

参考手册为IEEE VHDL语言参考手册标准草案1076/B版,于1987年批准,称为IEEE 1076-1987。

自IEEE公布了VHDL的标准版本,IEEE- 1076(简称87版)之后,各EDA公司相继推出了自己的VHDL设计环境,或宣布自己的设计工具可以和VHDL接口。

此后VHDL在电子设计领域得到了广泛的接受,并逐步取代了原有的非标准的硬件描述语言。

HDL和LDL检测方法学PPT课件

间接测定法是通过计算得出LDL水平, 不需要分离HDL和LDL。

常用的计算公式包括Friedewald公式、 Deutsch公式和Remington公式等, 这些公式基于总胆固醇、高密度脂蛋白 胆固醇和甘油三酯的测定结果来计算

LDL水平。

间接测定法的优点是操作简便,但结果 的准确性受到多种因素的影响,如甘油

THANKS FOR WATCHING

感谢您的观看

HDL和LDL检测在药物治疗监测中的作用

在药物治疗过程中,HDL和LDL的检测有助于监测治疗效果,及时调整治疗方案。

HDL和LDL检测在流行病学研究中的应用

大规模流行病学研究通过检测HDL和LDL水平,有助于揭示疾病发生发展的规律,为预防 和控制提供科学依据。

HDL和LDL检测方法的展望

1 2

自动化、标准化检测方法的研发

免疫法

利用特异性抗体与HDL结合,通过比浊法或荧光法进行定量 检测。

HDL检测新技术

高效液相色谱法

利用不同脂蛋白在高效液相色谱柱上 的保留时间不同,分离出HDL并测定 其浓度。

质谱分析法

利用质谱技术对HDL中的脂类和蛋白 质成分进行分析,提供更全面的HDL 组分信息。

03 LDL检测方法

LDL直接测定法

新技术的优点是准确度高、分辨率高、 无创等,但需要专业的技术人员和昂 贵的仪器设备,目前尚未普及应用。

04 HDL和LDL检测方法的比 较与选择

HDL和LDL检测方法的比较

准确性

不同检测方法在准确性上存在差异。一些方法可能更适用于大型实验 室,而另一些则更适合于小型实验室或现场检测。

特异性

不同的检测方法对HDL和LDL的特异性也不同。某些方法可能更容易 受到其他脂蛋白的干扰,而其他方法则具有更高的特异性。

硬件描述语言verilog_HDL基础

12

1.4 Verilog 目前的应用情况和适用的设计

Verilog 较为适合系统级(System)、算法 级(Alogrithem)、寄存器传输级(RTL)、逻辑 (Logic)、门级(Gate)和电路开关级(Switch)的

设计,而对于特大型(千万门级以上)的系 统级(System)设计,则VHDL更为合适。

2020/2/28

13

1.5 采用 Verilog HDL 设计复杂数字电路的优点

1.5.1 传统设计方法——电路原理图输入法

采用电路原理图输入法进行设计,周期长、需 要专门的设计工具、需手工布线等。这种低水平的 设计方法大大延长了设计周期。

2020/2/28

14

1.5.2 Verilog HDL 设计法与传统的电路 原理图输入法的比较

2020/2/28

3

什么是硬件描述语言

具有特殊结构能够对硬件逻辑电路的功能进行描述的一种高级 编程语言

这种特殊结构能够:

描述电路的连接 描述电路的功能 在不同抽象级上描述电路 描述电路的时序 表达具有并行性

HDL主要有两种:Verilog和VHDL

Verilog起源于C语言,因此非常类似于C语言,容易掌握 VHDL格式严谨 VHDL出现较晚,但标准化早。IEEE 1706-1985标准。

2020/2/28

24

概述

Verilog HDL行为描述语言具有以下功能:

• 可描述顺序执行或并行执行的程序结构。 • 用延迟表达式或事件表达式来明确地控制过程的启动时间。 • 通过命名的事件来触发其它过程里的激活行为或停止行为。 • 提供了条件如if-else、case、循环程序结构。 • 提供了可带参数且非零延续时间的任务(task)程序结构。 • 提供了可定义新的操作符的函数结构(function)。 • 提供了用于建立表达式的算术运算符、逻辑运算符、位运算 符。 • Verilog HDL语言作为一种结构化的语言也非常适合于门级 和开关级的模型设计。

HDL知识点总结

HDL 考前小结一、名词解释(专业术语的对应关系):可编程阵列逻辑(PAL)、可编程逻辑器件(PLD)、大规模可编程逻辑器件两种:复杂可编程逻辑器件(CPLD)、现场可编辑门阵列(FPGA);电子设计自动化(EDA)、电子设计系统自动化(EsDA)、自底向上(Bottom-Up)、自顶向下(Top-Down)、专用集成电路(ASIC)、可配置逻辑模块(CLB)、输入输出模块(IOB)、硬件描述语言(HDL)、寄存器传输级(RTL)、X(逻辑值不确定)、Z(高阻,浮动状态)、posedge(上升沿)、negedge(下降沿)、电路功能模块(IP)、TTL、仿真平台(Testbench)、UDP(用户自定义原语)二、选择题(语法、 EDA 的基本概念、课件)基础了解:1、标识符和关键字关键字是语言中预留的用于定义语言结构的特殊标识符。

Verilog 中关键字全部小写。

标识符是程序代码中对象的名字,程序员使用标识符来访问对象。

Verilog 中标识符由字母数字字符、下划线和美元符号组成,区分大小写。

其第一个字符必须是数字字符或下划线。

reg value;//reg 是关键字; value 是标识符2. FPGA技术概述与特点以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件的方式设计的电子系统到硬件系统并最终形成集成电子系统或专用集成芯片的一门新技术。

3 、FPGA 技术的特点用软件的方式设计硬件②设计过程中可用有关软件进行各种仿真③系统可现场编程,在线升级④片上系统,体积小、功耗低、可靠性高数字系统的设计准则①.分割准则②.系统的可观测性③.同步和异步电路④.最优化设计⑤ . 系统设计的艺术三、简答题1、串行、并行语句:verilog HDL 的 module 里一般由块语句组成,块语句既有并行块又有串行块 ,块与块之间是并行执行 ,顺序块内是串行执行,并行块内是并行执行 . 常用形式为 initial 和always 形式里插入块语句。

高密度脂蛋白与胆固醇逆转运

胆固醇逆转运过程详解

▪ 胆固醇逆转运的过程

1.胆固醇从外周细胞通过ABCA1/ABCG1转运到HDL颗粒中, 形成盘状HDL。 2.盘状HDL在血浆中被酯化酶修饰形成球状HDL,更加稳定并 能够更好地转运胆固醇。 3.球状HDL将胆固醇转运回肝脏,通过肝脏代谢和排泄,完成 胆固醇逆转运过程。

Байду номын сангаас

▪ 影响胆固醇逆转运的因素

▪ 改善高密度脂蛋白水平与心血管疾病风 险的干预措施

1.饮食、运动等生活方式干预可以提高高密度脂蛋白水平,降 低心血管疾病的风险。 2.目前已有一些药物(如CETP抑制剂)能够升高高密度脂蛋白 水平,并显示出对心血管疾病的保护作用。 3.未来仍需要更多研究以探索更有效、安全的改善高密度脂蛋 白水平的方法,以降低心血管疾病的风险。

▪ 高密度脂蛋白亚类与心血管疾病风险

1.高密度脂蛋白包含多种亚类,不同亚类在胆固醇逆转运中的效率不同,对心血管 疾病风险的影响也不同。 2.一些特定的高密度脂蛋白亚类可能更具保护作用,而其他亚类则可能无效或甚至 有害。 3.针对高密度脂蛋白亚类的研究有助于更精确地评估心血管疾病的风险,并为开发 新的治疗方法提供依据。

▪ 高密度脂蛋白与心血管疾病的风险

1.大量流行病学研究和临床试验表明,高密度脂蛋白水平升高 可以降低心血管疾病的风险。 2.高密度脂蛋白的水平是一个独立的预测心血管疾病的因素, 其预测价值独立于其他传统的心血管风险因素。 3.通过提高高密度脂蛋白水平来预防和治疗心血管疾病是当前 研究的热点之一,多种药物和治疗方法正在临床试验阶段。

▪ 身体活动

1.适度的身体活动可以提高高密度脂蛋白胆固醇的水平。 2.有氧运动和力量训练都可以对高密度脂蛋白胆固醇产生积极 影响。 3.长期久坐的生活方式会导致高密度脂蛋白胆固醇水平的下降 。

HDL机票打印机驱动行程单打印说明

HDL机票打印机驱动行程单打印说明一、概述HDL机票打印机是一种专为打印航班行程单而设计的打印机,具有高效、准确、稳定的打印功能。

该打印机支持热敏和针式打印两种方式,可根据实际需要选择合适的打印方式。

本篇文章将详细介绍HDL机票打印机的驱动安装及行程单打印方法。

二、安装步骤1、连接打印机:将HDL机票打印机通过USB接口或网络连接至电脑。

确保打印机电源已开启,并按照打印机说明书进行连接。

2、下载并安装驱动程序:访问HDL官方网站或从打印机附带的光盘中获取驱动程序。

根据操作系统的不同,选择相应的驱动程序进行下载。

下载完成后,双击安装文件,按照提示完成驱动程序的安装。

3、安装打印软件:打开HDL机票打印机的驱动光盘,找到并安装相应的打印软件。

该软件将帮助您在电脑中管理打印任务,并支持直接打印行程单。

三、行程单打印方法1、打开打印软件:在电脑中找到并打开已安装的打印软件。

该软件将显示与打印机相关的各种功能和选项。

2、导入行程单数据:在软件中找到“文件”或“导入”选项,选择要打印的行程单文件进行导入。

支持常见的数据格式,如CSV、Excel 等。

根据数据来源的不同,选择相应的导入方式。

3、设置打印参数:在软件中找到“设置”或“选项”选项,根据实际需要设置打印参数。

包括纸张大小、打印份数、打印质量等。

确保选择正确的打印方式和纸张类型。

4、开始打印:完成设置后,点击“打印”或“开始”按钮,等待打印机开始打印行程单。

请注意,打印过程中请勿随意移动打印机,以免影响打印效果。

5、确认打印结果:打印完成后,请检查每张行程单的内容是否清晰、完整。

如有需要,请根据实际情况调整打印参数并重新打印。

四、常见问题及解决方案1、无法找到打印机:请检查打印机是否已正确连接至电脑,驱动程序是否已成功安装。

如有问题,请重新连接打印机并安装驱动程序。

2、打印速度慢或卡顿:请检查打印机是否缺纸或墨水,如有需要请及时更换。

同时,检查电脑CPU使用情况,如过高请关闭一些不必要的程序。

hdl名词解释

hdl名词解释

hdl名词解释:高密度脂蛋白( high-density lipoprotein,HDL) 为血清蛋白之一,是由脂质和蛋白质及其所携带的调节因子组成的复杂脂蛋白,亦称为a1脂蛋白。

比较富含磷脂质,在血清中的含量约为200mg/dl。

其蛋白质部分,A-Ⅰ约为75%,A-Ⅱ约为20%。

由于可输出胆固醇促进胆固醇的代谢,所以作为动脉硬化预防因子而受到重视。

高密度脂蛋白运载周围组织中的胆固醇,再转化为胆汁酸或直接通过胆汁从肠道排出,动脉造影证明高密度脂蛋白胆固醇含量与动脉管腔狭窄程度呈显著的负相关。

所以高密度脂蛋白是一种抗动脉粥样硬化的血浆脂蛋白,是冠心病的保护因子。

俗称“血管清道夫”。

HDL语言

HDL语言浏览804次Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog HDL和VHDL是目前世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

前者由Gateway Design Automation 公司(该公司于1989年被Cadence公司收购)开发。

两种HDL均为IEEE标准。

目录用途选择VHDL还是verilog HDL?Verlog HDL的发展历史主要能力例子编辑本段用途Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具。

1985年Moorby 推出它的第三个商用仿真器Verilog-XL,获得了巨大的成功,从而使得V erilog HDL迅速得到推广应用。

1989年CADENCE公司收购了GDA公司,使得VerilogHDL成为了该公司的独家专利。

1990年CADENCE公司公开发表了V erilog HDL,并成立LVI组织以促进Verilog HDL 成为IEEE标准,即IEEE Standard 1364-1995.Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。

与之相比,VHDL的学习要困难一些。

但Verilog HDL较自由的语法,也容易造成初学者犯一些错误,这一点要注意。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LDL=100 HDL=25 LDL=220 HDL=45

3.0

Risk of 2.0 CHD After 1.0 4 Years

0.0 100

160

220

85

65

45

HDL-C

(mg/dL)

25

PLASMA COMPARTMENT

LDLR

CIII

ADIPOCYTE

C C BA-C ENTEROCYTE

LRP SR-BI ABCA1 PL UC

B 100

TG

CE

E

CII

AI C II AI AI AI

CE TG

E

TG

AI

MYOCYTE

CETP

CE PLTP PL(UC)

HDL2 ABCG5/8

Unpublished data: Vaisar T, Sinha A, Heinecke JW, Zhao XQ , 2011.

Sterol Efflux is Significantly Suppressed in CAD and ACS subjects

Total HDL Efflux (J774 cells) P=0.005 ABCA1 Specific Efflux (ABCA1-BHK cells)

Sterol Efflux Capacity is Independent Predictor of CAD

Khera, Rader NEJM 2011

HDL-C and Cholesterol Efflux

HDL Cholesterol Efflux Capacity Is Independent Of HDL-C (D. Rader, U Penn)

*: P value for overall model = 0.004 5400 patients from 18 reported trials

Brown BG, Stukovsky KH, Zhao X-Q: Current Opinion in Lipidology 2006,17:631-636

The in ApoA-1 in large alpha-1 HDL was significantly (p<0.01) related to lack of progression or regression of coronary stenosis in HATS If alpha-1 HDL apoA-I is to > 20mg, there was net regression, provided LDL-C <80mg/dl

Unpublished data: Vaisar T, Heinecke JW, Zhao XQ , 2011, UW CARL

HOCl modification of HDL: ABCA1 associated function

Cholesterol efflux activities

Bergt, Constanze et al. (2004) Proc. Natl. Acad. Sci. USA 101, 13032-13037

Reverse Cholesterol Transport

feces SR-BI

FC CE

ABCG1 HDL LCAT

FC

LDLR CETP

ABCA1

Foam cell

CE TG LDL

ApoA-I

Cholesterol Efflux: the 1st Step in Reverse Cholesterol Transport

High Density Lipoprotein (HDL) Related Therapy:

Where we are now Xue-Qiao Zhao, MD

Division of Cardiology, University of Washington

Coronary Heart Disease Risk

Heart Protection Study Collaborative Group: Lipids, lipoproteins and vascular events. Circulation May 2012

HDL Protein Composition: Percentage and Numbers

LDL-C (mg/dL)

Am J Med 1977;62:707-714

Meta-Analysis: Predictive Value of HDL-C

• Coronary Primary Prevention Trial (CPPT)

• Multiple Risk Factor Intervention Trial (MRFIT) • Lipid Research Clinics Prevalence Mortality Follow-up Study (LRCS) • Framingham Heart Study (FHS)

Increasing HDL-C to Reduce Coronary Heart Disease???

Linear Regression Analysis of % Coronary Stenosis

Model 1 2 3* Variables In model % HDL-C % LDL-C % HDL-C % LDL-C

After adjustment for LDL particle number, HR for major occlusive coronary event per one SD higher level were: •HDL-cholesterol: 0.91 (95%CI 0.86-0.96) •HDL particle number: 0.89 (0.85-0.93)

Linear Regression Analysis of % Relative Event Rate

Variables Model In model 4 5 6* ß Coefficient (95% CI) P value R2 0.53 0.70

% HDL-C -0.1853 (-3.601, -0.104) 0.04 % LDL-C +1.211 (0.428, 1.994) 0.01

Cheung MC, Brown BG, AC. Wolf, and . Albers JJ. J. Lipid Res. 1991. 32: 383-394. Cheung MC, Zhao XQ, . Brown BG. ATVB 2001;21:1320-1326.

HDL Particle Size

HDL

Antiapoptotic Activity Vasodilatory Activity

Antiinfectious Antithrombotic Activity Activity

Antioxidative Activity

Endothelial Repair

Chapman MJ, et al. Curr Med. Res Opin. 2004,20:1253-1268. Assmann G, et al. Annu Rev Med. 2003,53:321-41.

HL

CE TG

CE

TG

AI

AI

LDL

C

LYMPH

LPL

HDL3

HL

AI AI

PL UC

(PROTEOLYSIS)

SR-A CD-36

RENAL TUBULAR CELL

ABCA1 CUBULIN

Compiled by B.G. Brown and H. Bruggman

INTIMAL MACROPHAGE

CPPT MRFIT LRCS FHS

1 mg/dL Increase in HDL-C

LRCS FHS

2% CHD Risk in Men

Gordon DJ, et al. Circulation. 1989;79:8-15.

3% CHD Risk in Women

HEPATOCYTE

ABCG5/8

CAD: Plasma vs. Lesion Plasma: Healthy vs. CAD

HOCl modigt C, Proc Natl Acad Sci USA 118:1259, 2008

Levels of 3-chloroTyr192 are higher in CAD and ACS

ß Coefficient (95% CI)

-0.133 (-0.305, 0.038) +0.085 (0.007, 0.162) -0.076 (-0.199, 0.046) +0.060 (-0.011, 0.132)

P value 0.09 0.04 0.12 0.07

R2 0.67 0.80 0.96

P=0.001

P=0.035

P=0.036

P=NS

P=NS

Unpublished data: Vaisar T, Heinecke JW, Zhao XQ , 2011, UW CARL

Anti-atherogenic Actions of HDL

Reverse Cholesterol Transport Cellular Cholesterol Efflux Antiinflammatory Activity

Asztalos BF, ATVB 2003;23(5):847–852. Schaefer EJ, et al. Curr Opin Lipid. 2010;21(4):289-297