CC1210KKX5RGBB106中文资料

AD2S1210芯片手册-中文

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2008–2010 Analog Devices, Inc. All rights reserved.功能框图REFERENCE OSCILLATOR(DAC)EXCITATION OUTPUTSAD2S1210E N C O D E R E M U L A T I O NSYNTHETIC REFERENCE RESETDATA I/OINPUTS FROM RESOLVERENCODER EMULATION OUTPUTSVOLTAGE REFERENCEREFERENCEPINSINTERNAL CLOCK GENERATORCRYSTALTYPE IITRACKING LOOP FAULT DETECTIONFAULTDETECTION OUTPUTSPOSITION REGISTERADCADCCONFIGURATIONREGISTERMULTIPLEXERDATA BUS OUTPUTDATA I/OVELOCITY REGISTER07467-001图1.AD2S1210分辨率可变、10位至16位R/D转换器,内置参考振荡器产品特性完整的单芯片旋变数字转换器最大跟踪速率:3125 rps(10位分辨率) 精度:±2.5弧分分辨率:10/12/14/16位,由用户设置 并行和串行10位至16位数据端口 绝对位置与速度输出 系统故障检测可编程故障检测阈值 差分输入增量式编码器仿真内置可编程正弦波振荡器 兼容DSP 和SPI 接口标准电源电压:5 V ,逻辑接口电压2.3 V 至5 V 额定温度范围:−40°C 至+125°C应用直流和交流伺服电机控制 编码器仿真 电动助力转向 电动汽车集成的启动发电机/交流发电机 汽车运动检测与控制概述AD2S1210是一款10位至16位分辨率旋变数字转换器,集成片上可编程正弦波振荡器,为旋变器提供正弦波激励。

NUC100中文手册

5.4.1 概述.................................................................................................................................46

3.3.2 NuMicro™ NUC100 Low Density引脚定义 ......................................................................24

4

框图 ........................................................................................................................................... 30

5.2 系统管理器 .................................................................................................................... 34

5.2.1 概述.................................................................................................................................34 5.2.2 系统复位..........................................................................................................................34 5.2.3 系统电源分配 ..................................................................................................................35 5.2.4 系统内存映射 ..................................................................................................................37 5.2.5 系统定时器(SysTick) .......................................................................................................39 5.2.6 嵌套向量中断控制器(NVIC).............................................................................................40

MF10CCN资料

System Block Diagram

Connection Diagram

Surface Mount and Dual-In-Line Package

TL H 10399 – 4 NhomakorabeaTop View

Order Number MF10AJ or MF10CCJ See NS Package Number J20A Order Number MF10ACWM or MF10CCWM See NS Package Number M20B Order Number MF10ACN or MF10CCN See NS Package Number N20A

b 40 C s TA s 85 C b 55 C s TA s 125 C

Electrical Characteristics V a e a 5 00V and Vb e b5 00V unless otherwise specified Boldface limits apply for TMIN to TMAX all other limits TA e TJ e 25 C

mV mV mV mV

VOS3

DC Offset Voltage (Note 5)

元器件交易网

Electrical Characteristics (Continued) V a e a 5 00V and Vb e b5 00V unless otherwise specified Boldface limits apply for TMIN to TMAX all other limits TA e TJ e 25 C

Soldering Information N Package 10 sec J Package 10 sec SO Package Vapor Phase (60 Sec ) Infrared (15 Sec )

ioLogik E1200系列产品(E1210)更新说明书

Firmware for ioLogik E1200 Series (E1210) Release NotesSupported Operating SystemsNotesChangesApplicable ProductsBugs FixedN/A• Fixed inaccurate counter value when using Modbus to start a pulse (E1210/E1212/E1213).• Fixed opposite on/off pulse width display on web console (E1211/E1212/E1214).• Fixed that the offset scaling value will reset after changing the Alias name (E1260).• Fixed self-rebooting when entering URL in the browser for the configuration file.• Fixed EDS file import connection error.• Fixed failure when using save counter on power failure and reset counter at the same time (E1210/E1212/E1213).• Fixed inaccurate counter value when using high frequency (E1210/E1212/E1213).• Fixed that the trap community name is not included in the export file.• Fixed that EtherNet/IP cannot use the “Set Attribute Single” service.• Added an enable RESTful API setting in the configuration file.EnhancementsN/AioLogik E1210, ioLogik E1210-T• EtherNet/IP registration on Moxa’s licensing website is no longer required.• Added case insensitive content-length for RESTful API.New FeaturesN/AN/ASupported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• Added SNMP Trap Community Setting to the web console.• Added a note on the password settings page that passwords are limited to 16 characters.• Fixed DHCP lease time did not ask for extension when half of the lease time elapsed.• Closed IP forwarding function (Port 0).• Closed UDP Port 161 when SNMP agent is disabled.• Fixed RESTful API header case-sensitive issue.• Fixed invalid token issue on login page when using Firefox.EnhancementsN/AioLogik E1210-T, ioLogik E1210• Added OPTIONS method for RESTful API.• Added quick access URI for RESTful API.New FeaturesN/A• This version of the firmware only works with ioSearch v2.0 or later versions.• To prevent system failure, only update the next or the previous released firmware version to prevent from system failure.Supported Operating SystemsNotesChangesApplicable ProductsBugs FixedN/A• Fixed file transfer problems when using the Chrome browser (e.g., firmware update, configuration import or export).EnhancementsN/AioLogik E1210, ioLogik E1210-T• Added the EtherNet/IP protocol.• Added RESTful API.• Added new registers for the Modbus/TCP protocol.• Added new OIDs for the SNMP protocol.• Modbus, EtherNet/IP, and RESTful services can be disabled (enabled by default).• Added sending heartbeat to port 9500 of MX-AOPC UA Server after the heartbeat function is enabled.• Increased password length from 8 to 16 characters.• Added a function to check special characters to prevent Cross-Site Scripting.• Passwords are now sent using the POST method instead of the GET method.New FeaturesN/AN/ASupported Operating SystemsNotesChangesApplicable ProductsBugs FixedN/AN/AEnhancementsN/AioLogik E1210, ioLogik E1210-T• Improved protocol efficiency for the ioLogik 2500 Series.New FeaturesN/AN/ASupported Operating SystemsNotesChangesApplicable ProductsBugs FixedN/A• Unable to disable the P2P heartbeat interval.• When the P2P client heartbeat is larger than 256 the time interval is incorrect.EnhancementsN/AioLogik E1210, ioLogik E1210-T• Supports ioLogik 2500 expansion mode.• Supports setting an initial value for a counter.New FeaturesN/AN/ASupported Operating SystemsNotesChangesApplicable ProductsBugs FixedN/A• The counter storage is deleted when the power fails.EnhancementsN/AioLogik E1210-T, ioLogik E1210• Supports SNMP protocol.• Added P2P heartbeat function.New FeaturesN/A• This version of firmware only works with ioSearch v1.5 or later versions.• Use the web console when upgrading the firmware from v1.0 to v1.10.Supported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• Ensured that the system works properly after unstable power conditions.N/AEnhancementsN/AioLogik E1210, ioLogik E1210-TN/ANew FeaturesN/AN/ASupported Operating SystemsNotesChangesApplicable ProductsBugs Fixed• Improved firmware upgrading speed.• Removed Modbus/TCP ID checking mechanism.N/AEnhancementsN/AioLogik E1210, ioLogik E1210-T• Added "Locating I/O" function in General Settings.• Added Modbus address function code=0x08 for “ECHO” function.• Counter overflow status displayed in Channel Settings can be cleared manually.New FeaturesN/A• This version of the firmware only works with ioSearch v1.5 or later versions.• Use the web console when upgrading the firmware from v1.0 to v1.9.。

宝马宝·R12 电视机说明书

lockable cabinet capable of housing up to 7 AH batter-

ies.

OPTIONAL REMOTE ANNUNCIATOR

The RZA-5F is a five-zone Remote Annunciator for use with the FireWatch 5000 Series control/communicators. They mount to a single-gang box and offer slide-in zone identification labels. The RZA-5F provides the following:

Initiating Device Circuits (zones)

The MS-5012 includes five programmable Initiating Device Circuits (zones). Circuits 1, 2, 4, and 5 are Style B (Class B). Circuit 3 is Style D (Class A).

DF-51186 07/12/04 Page 1 of 3

SPECIFICATIONS

Single PC board design using Surface Mount Technology (SMT).

Two modular telephone jacks for connection to RJ31X/ Modules.

16-Event history buffer.

MS-5012

Accurate real-time clock.

Extensive built-in transient protection.

TMCM-1210 硬件手册说明书

TRINAMIC Motion Control GmbH & Co. KGHamburg, GermanyHardware Version V 1.10HARDWARE MANUAL+ +TMCM-12101-Axis steppercontroller/drivermax. 0.6A RMS / 24V DC STOP / HOME switch input hall sensorRS485++Table of contents1Life support policy (3)2Features (4)3Order codes (5)4Mechanical and Electrical Interfacing (6)4.1Dimensions and Mounting Holes (6)4.2Board mounting considerations (6)4.3Connectors (7)4.3.1Power, RS485 + HOME connector (8)4.3.2Motor connector (9)4.4Power supply (9)4.5RS485 (10)5Motor driver current (12)6On-Board LEDs (13)7Reset to Factory Default Values (13)8EMC considerations (14)9Operational Ratings (15)10Functional Description (16)11Revision History (17)11.1Document revision (17)11.2Hardware revision (17)12References (17)1Life support policyTRINAMIC Motion Control GmbH & Co. KG does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Motion Control GmbH & Co. KG.Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.© TRINAMIC Motion Control GmbH & Co. KG 2015 - 2019Information given in this data sheet is believed to be accurate and reliable. However neither responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties, which may result from its use.Specifications are subject to change without notice.2FeaturesThe TMCM-1210 is a highly compact 20mm x 20mm single axis stepper motor controller and driver board with RS485 interface. It has been designed in order to be mounted on the rear side of a NEMA8 (20mm flange size) stepper motor and offers an integrated hall-sensor based encoder IC in addition to a reference switch input for easy homing / search of reference position. The module supports motor currents up to 0.6A RMS and supply voltages up to 24V DC nominal. It is available with standard TMCL firmware and supports stand-alone operation (TMCL programs with auto-start stored on-board) and remote control via RS485 interface.MAIN CHARACTERISTICSMotion controller∙Motion profile calculation in hardware in real-time∙Motion controller supports linear and sixPoint™ ramps∙On the fly alteration of motor parameters (e.g. position, velocity, acceleration)∙High performance microcontroller (Cortex-M0+) for overall system control and serial communication protocol handlingBipolar stepper motor driver∙Up to 256 microsteps per full step∙Highly integrated and highly-efficient operation∙Dynamic current control∙stallGuard2™ feature for stall detectionInterfaces∙RS485 2-wire communication interface∙Digital input IN0 (+24V compatible), can be used as reference switch or left and/or right stop switch input, alsoOn board hall sensor∙Absolute sensor within one motor rotation∙12bit / 4096 steps / revolution max.∙Low-cost sensor - suitable for low velocity applications (few hundred rpm) –e.g. initial reference search (together with HOME sensor input) after power-upSoftware∙TMCL™ remote (direct mode) and standalone oper ation with memory for up to 876 TMCL commands∙Fully supported by TMCL-IDE (PC based integrated development environment)Electrical data∙Supply voltage: +7V… +30V DC∙Motor current: up to 0.6A RMS (programmable)Mechanical data∙Board size: 20mm x 20mm, overall height 9mm max. (without mating connectors and cables)∙Mounting holes compatible with NEMA 8 stepper motors (for mounting the board to the rear side of a NEMA8 stepper motor using two of the four existing screw)Please see separate TMCM-1210 Firmware Manual for additional information regarding firmware functionality and TMCL programming.3Order codesThe TMCM-1210 is available as:A cable loom set is available for this module, also:Table 3.2: Cable loom order code4 Mechanical and Electrical Interfacing4.1 Dimensions and Mounting HolesThe dimensions of the board are approx. 20mm x 20mm x 9 mm in order to fit on the back side of a 20mm (NEMA8) stepper motor. Maximum component height (height above PCB level) without mating connectors is around 6mm above PCB level and 2 mm below PCB level. There are two mounting holes for M2 screws for mounting to a NEMA8 stepper motor.2xFigure 4.1 Dimensions of TMCM-1210 and position of mounting holes (with comparison of size)4.2 Board mounting considerationsThe TMCM-1210 offers two metal plated mounting holes. Both mounting holes are connected to power supply ground. Please keep this in mind when mounting the board to the rear side of a motor.Figure 4.2: Example of TMCM-1210 mounted to NEMA 8 stepper motor4.3 ConnectorsThe TMCM-1210 offers two connectors including the motor connector which is used for attaching the motor coils to the electronics. The Power, RS485 and HOME connector is used for power supply, RS485 serial wire communication and offers one digital input.4115Power, RS485 + HOME connector HOME 5RS485+RS485-34VDD GND 12IN0STOP_L / STOP_R Motor connectorOA1OA234OB1OB212Figure 4.2 Overview connectorsOverview of connectors and mating connectors types:Table 4.1: Connectors and mating connectors, contacts and applicable wire4.3.1Power, RS485 + HOME connectorThe module offers one combined power, RS485 2-wire serial communication and digital input (HOME) connector (JST PH series).51Table 4.2: Power, RS485 + IN0 connector4.3.2 Motor connectorAs motor connector a 4pin JST PH-series 2mm pitch single row connector is available. The motor connector is used for connecting the four motor wires of the two motor coils of the bipolar stepper motor to the electronics. 14Table 4.4: Motor connector 4.4 Power supplyFor proper operation care has to be taken with regard to power supply concept and design. Due to space restrictions the TMCM-1210 includes just about 20µF/35V of supply filter capacitors. These are ceramic capacitors which have been selected for high reliability and long life time.4.5RS485For remote control and communication with a host system the TMCM-1210 provides a two wire RS485 bus interface. For proper operation the following items should be taken into account when setting up an RS485 network:1.BUS STRUCTURE:The network topology should follow a bus structure as closely as possible. That is, the connection between each node and the bus itself should be as short as possible. Basically, it should be short compared to the length of the bus.termination resistor (120 Ohm)termination resistor (120 Ohm)Figure 4.6: Bus structure2.BUS TERMINATION:Especially for longer busses and/or multiple nodes connected to the bus and/or high communication speeds, the bus should be properly terminated at both ends. The TMCM-1210 does not integrate any termination resistor. Therefore, 120 Ohm termination resistors at both ends of the bus have to be added externally.3.NUMBER OF NODES:The RS485 electrical interface standard (EIA-485) allows up to 32 nodes to be connected to a single bus.The bus transceiver used on the TMCM-1210 unit (SN65HVD3085E) has a significantly reduced bus load and allow a maximum of 255 units to be connected to a single RS485 bus using TMCL firmware. Please note: usually it cannot be expected to get reliable communication with the maximum number of nodes connected to one bus and maximum supported communication speed at the same time. Instead, a compromise has to be found between bus cable length, communication speed and number of nodes. MUNICATION SPEED:The maximum RS485 communication speed supported by the TMCM-1210 hardware is 1Mbit/s. Factory default is 9600 bit/s. Please see separate TMCM-1210 TMCL firmware manual for information regarding other possible communication speeds below the upper limit in hardware.5.NO FLOATING BUS LINES:Avoid floating bus lines while neither the host/master nor one of the slaves along the bus line is transmitting data (all bus nodes switched to receive mode). Floating bus lines may lead to communication errors. In order to ensure valid signals on the bus it is recommended to use a resistor network connecting both bus lines to well defined logic levels.There are actually two options which can be recommended:Add resistor (Bias) network on one side of the bus, only (120R termination resistor still at both ends):termination resistor(120R)RS485- / RS485Btermination resistor (120R)RS485+ / RS485AFigure 4.7: Bus lines with resistor (Bias) network on one side, onlyOr add resistor (Bias) network at both ends of the bus (like Profibus™ termination):termination resistor (220R)RS485- / RS485BRS485+ / RS485A termination resistor (220R)Figure 4.8: Bus lines with resistor (Bias) network at both endsCertain RS485 interface converters available for PCs already include these additional resistors (e.g. USB-2-485 with bias network at one end of the bus).5Motor driver currentThe on-board stepper motor driver operates current controlled. The driver current may be programmed in software with 32 effective scaling steps in hardware.Explanation of different columns in table below:Motor current setting in software (TMCL)These are the values for TMCL axis parameter 6 (motor run current) and 7 (motor standby current). They are used to set the run / standby current using the following TMCL commands:SAP 6, 0, <value> // set run currentSAP 7, 0, <value> // set standby current(read-out value with GAP instead of SAP. Please see separate TMCM-1210 firmware manual for further information)Motor currentI RMS [A]Resulting motor current based on motor current setting6On-Board LEDsThe board offers one LED in order to indicate board status. The function of the LED is dependent on the firmware version. With standard TMCL firmware the green LED should be flashing slowly during operation.GREEN LEDFigure 6.1 On-board LED7Reset to Factory Default ValuesIn order to reset all settings (e.g. incl. address and RS485 baud rate) to factory default values please follow instruction sequence below:1.Switch OFF power supply.2.Short programming pads on bottom of PCB as shown in figure 7.1.3.Switch ON power supply (on-board LED should start flashing fast).4.Switch OFF power supply.5.Remove short circuit.Figure 7.1 Reset to factory default values (bottom view of pcb)8EMC considerationsThe TMCM-1210 contains ferrite beads on-board in line with the positive supply input and all 4 motor windings connections in addition to filter capacitors.Tests have shown that it is possible to meet Class B emission standards using the bare TMCM-1210 (motor and power connected) with the motor running slowly at maximum current (0.7A RMS) and +24V supply voltage without additional / external filters.Figure8.1:SetupwithTMCM-1210andattachedmotor(***************************/24Vsupply,stand-alone mode using on-board TMCL-autostart-program)Figure 8.2: measurement results (example)Please note that these measurement results using a bare TMCM-1210 unit with only motor and power supply connected do not imply any guarantee for a complete system with one or more integrated TMCM-1210 with meeting any emission limits.9Operational RatingsThe operational ratings show the intended or the characteristic ranges and should be used as design values. In no case shall the maximum values be exceeded!Table 9.1 General operational ratings of modulePERATIONAL RATINGS OF SWITCHTable 9.2 Operational ratings of HOME + STOP switches / IN0 inputsPERATIONAL RATINGS OF INTERFACETable 9.3: Operational ratings of RS485 interface10Functional DescriptionThe TMCM-1210 is a highly integrated controller/driver module which can be controlled via several serial interfaces. Communication traffic is kept low since all time critical operations (e.g. ramp calculations) are performed on board. The nominal supply voltage of the unit is 12V or 24V DC. The module is designed for both, standalone operation and direct mode. Full remote control of device with feedback is possible. The firmware of the module can be updated via the RS485 serial interfaces.In Figure 10.1 the main parts of the TMCM-1210 are shown:∙microprocessor, which runs the TMCL operating system (connected to TMCL memory),∙motion controller (part of TMC2130), which calculates ramps and speed profiles internally by hardware, ∙driver (part of TMC2130) with stallGuard2™ and its energy efficient coolStep™ feature and stealthCh o p™ for extremely quiet operation∙hall sensor based encoder which delivers position feedback at low speed (few 100rpm max.) – can be used for reference search e.g. after power-up7…Figure 10.1 Main parts of the TMCM-121011Revision History11.1D ocument revisionTable 11.1: Document revision11.2H ardware revisionTable 11.2: Hardware revision12References[JST] JST connector[TMC2130] TMC2130 datasheetManual available on [TMCL-IDE] TMCL-IDE User ManualManual available on .。

CC1206KKX5R9BB106中文资料

物料编号:CC1206KKX5R9BB106的详细参数_易容网

MLCC即是多层陶瓷电容片式,是电子信息产品不可或缺的基本组件之一。

我国MLCC的生产起步在80年代初,行业早期主要是在外资企业的带动下发展起来的,近年来国内企业在技术上实现突破,行业国产化成效显著,并推动了MLCC产量迅速增长。

目前,MLCC的应用领域已从手机、电脑、电视机等消费电子领域,逐步拓展到新能源发电、新能源汽车、节能灯具、轨道交通、直流输变电、三网融合、高清电视、机顶盒、手机电视等多个行业。

对于这个悄悄活跃在人们生活中的元件你又知道多少呢.

本次易容网为大家推荐比较常用的MLCC国巨 | Yageo品牌的料号CC1206KKX5R9BB106的相关参数

易容网是深圳市易容信息技术有限公司独自研发的全球最大的MLCC搜索采购服务网站,2014年创立于深圳市南山区,全国首家电子元器件行业电容元件的搜索引擎及o2o商务服务平台。

易容网()现已建成全球最大的MLCC电容搜索引擎数据库,包含全球25家电容生产厂商超过28万组MLCC产品数据,用户可根据行业应用、物料编号、规格参数等信息快速的找到所有相关的MLCC电容数据。

易容网在搜索服务的前提下还提供村田、TDK、国巨、太阳诱电、风华高科等常见品牌产品的o2o商务服务,让企业客户实现询价、报价、在线订单、出库、实时物流、签收、账期服务等在线一站式商务服务体验。

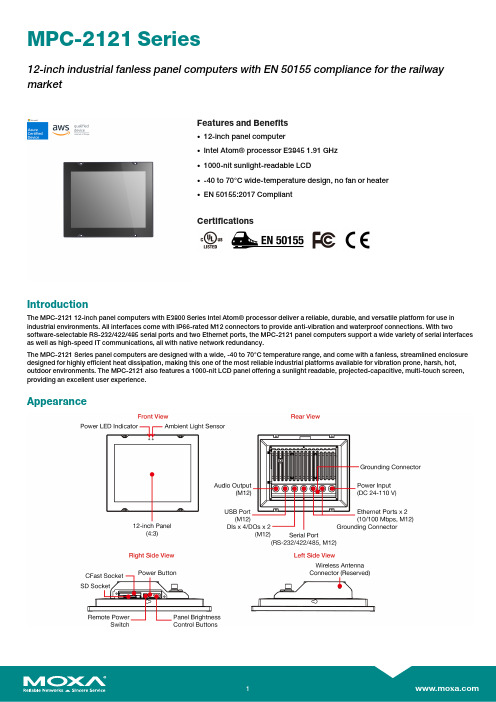

莫加 MPC-2121 系列 12英寸无风扇车辆面板计算机商品介绍说明书

MPC-2121Series12-inch industrial fanless panel computers with EN50155compliance for the railway marketFeatures and Benefits•12-inch panel computer•Intel Atom®processor E38451.91GHz•1000-nit sunlight-readable LCD•-40to70°C wide-temperature design,no fan or heater•EN50155:2017CompliantCertificationsIntroductionThe MPC-212112-inch panel computers with E3800Series Intel Atom®processor deliver a reliable,durable,and versatile platform for use in industrial environments.All interfaces come with IP66-rated M12connectors to provide anti-vibration and waterproof connections.With two software-selectable RS-232/422/485serial ports and two Ethernet ports,the MPC-2121panel computers support a wide variety of serial interfaces as well as high-speed IT communications,all with native network redundancy.The MPC-2121Series panel computers are designed with a wide,-40to70°C temperature range,and come with a fanless,streamlined enclosure designed for highly efficient heat dissipation,making this one of the most reliable industrial platforms available for vibration prone,harsh,hot, outdoor environments.The MPC-2121also features a1000-nit LCD panel offering a sunlight readable,projected-capacitive,multi-touch screen, providing an excellent user experience.AppearanceSpecificationsComputerCPU Intel Atom®Processor E3845(2M Cache,1.91GHz)Graphics Controller Intel®HD GraphicsSystem Memory Pre-installed4(8GB Max.)GB DDR3LSystem Memory Slot SODIMM DDR3/DDR3L slot x1Pre-installed OS MPC-2121-E4-LB-CT-T-W7E/MPC-2101-E4-CT-T-W7E:Windows Embedded Standard7(WS7P)64-bit pre-installedMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:Linux9pre-installedSupported OS Windows10Pro64-bitWindows10Embedded IoT Ent2019LTSC64-bitWindows10Embedded IoT Ent2016LTSBWindows7Pro for Embedded SystemsWindows Embedded Standard7(WS7P)64-bitLinux Debian9Expansion Slots Mini PCIeStorage Slot CFast slot x1SD slots x1,SD3.0(SDHC/SDXC)socketStorage Pre-installed MPC-2121-E4-LB-CT-T-W7E/MPC-2121-E4-CT-T-W7E:32GB CFast CardMPC-2121-E4-LB-CT-T-LX/MPC-2121-E4-CT-T-LX:32GB CFast CardComputer InterfaceEthernet Ports Auto-sensing10/100Mbps ports(M12D-coded4P)x2Serial Ports RS-232/422/485ports x1(M12A-code12P)USB2.0USB2.0hosts x1(M12A-coded5P)Digital Input DIs x4(M12A-code)Digital Output DOs x2(M12A-code)LED IndicatorsSystem Power x1DisplayActive Display Area245.76(H)x184.32(V)mmAspect Ratio4:3Contrast Ratio1000:1Light Intensity(Brightness)500/1000cd/m2Max.No.of Colors16.2M(8-bit/color)Panel Size12-inch viewable imagePixel Pitch(RGB)0.240(H)x0.240(V)mmPixels1024x768Response Time5ms(gray to gray)Viewing Angles176°/176°Touch FunctionTouch Type Capacitive Touch(PCAP)Touch Support Points4pointsGlove Support YesSerial InterfaceBaudrate50bps to115.2kbpsData Bits5,6,7,8Flow Control RTS/CTS,XON/XOFFParity None,Even,Odd,Space,MarkStop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GND RS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage24to110VDCPhysical CharacteristicsHousing MetalIP Rating IP66Dimensions297x238x59mm(11.69x9.37x2.32in) Weight2850g(6.28lb)Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to70°C(-40to158°F)Ambient Relative Humidity5to95%(non-condensing)Standards and CertificationsEMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFMechanical Protection Rating IEC60529,IP codeShock EN50155standardVibration EN50155standardEMC EN55032/35Safety IEC60950-1,IEC62368-1,UL62368-1 DeclarationGreen Product RoHS,CRoHS,WEEEWarrantyWarranty Period LCD:1yearSystem:3yearsDetails See /warrantyPackage ContentsDevice1x MPC-2121Series computerInstallation Kit6x screw,for panel-mounting1x M12-Phone jack power cable1x M12-Type A USB cable1x terminal block,2-pin(for remote power input) Documentation1x quick installation guide1x warranty cardDimensionsOrdering Information2.0MPC-2121-E4-LB-CT-T-W7E 12"(4:3)500nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-W7E12"(4:3)1,000nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T-LX 12"(4:3)500nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T-LX12"(4:3)1,000nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-LB-CT-T 12"(4:3)500nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°CMPC-2121-E4-CT-T12"(4:3)1,000nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M12)24to110VDCIP66-40to70°C©Moxa Inc.All rights reserved.Updated Jun28,2021.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

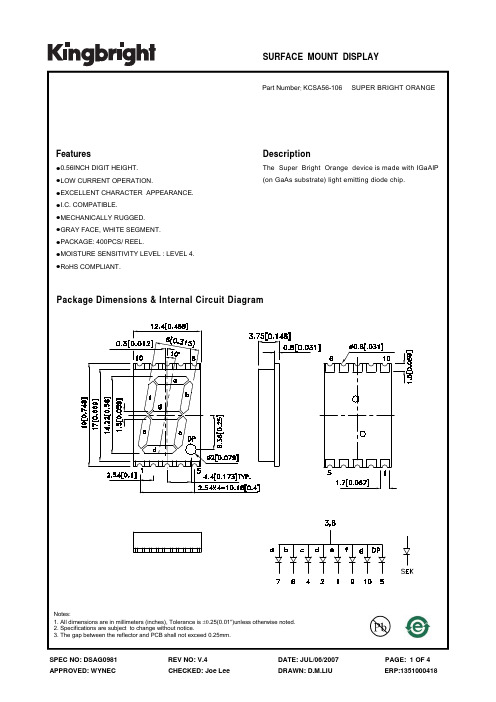

KCSC56-106中文资料

Super Bright Orange 75 30 195 5 -40°C To +85°C

Units mW mA mA V

SPEC NO: DSAG0981 APPROVED: WYNEC

REV NO: V.4 CHECKED: Joe Lee

Note: 1.Luminous Intensity / Luminous Flux: +/-15%.

Electrical / Optical Characteristics at TA=25°C

Symbol λpeak λD [1] Δλ1/2 C VF [2] IR Parameter Peak Wavelength Dominant Wavelength Spectral Line Half-width Capacitance Forward Voltage Reverse Current Device Super Bright Orange Super Bright Orange Super Bright Orange Super Bright Orange Super Bright Orange Super Bright Orange Typ. 610 601 29 15 2.1 2.5 10 Max. Units nm nm nm pF V uA Test Conditions IF=20mA IF=20mA IF=20mA VF=0V;f=1MHz IF=20mA VR = 5V

元器件交易网

SURFACE MOUNT DISPLAY

Part Number: KCSA56-106

SUPER BRIGHT ORANGE

TMX320C6211BGLW100资料

Table of Contents GHK BGA package (bottom view) . . . . . . . . . . . . . . . . . . . 3 description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 device characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 functional and CPU (DSP core) block diagram . . . . . . . . . 6 CPU (DSP core) description . . . . . . . . . . . . . . . . . . . . . . . . 7 memory map summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 signal groups description . . . . . . . . . . . . . . . . . . . . . . . . . . 10 signal descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . development support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . documentation support . . . . . . . . . . . . . . . . . . . . . . . . . . . . clock PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . power-down mode logic . . . . . . . . . . . . . . . . . . . . . . . . . . . power-supply sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . absolute maximum ratings over operating case temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . recommended operating conditions . . . . . . . . . . . . . . . . . recommended operating conditions (PCI only) . . . . . . . . electrical characteristics over recommended rangesof supply voltage and operating case temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . electrical characteristics over recommended ranges of supply voltage and operating case temperature (PCI only) . . . . . . . . . . . . . . . . . . . . . . . 13 22 25 26 28 31 32 32 32 33 33 parameter measurement information . . . . . . . . . . . . . . . 34 input and output clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 asynchronous memory timing . . . . . . . . . . . . . . . . . . . . . 37 synchronous-burst memory timing . . . . . . . . . . . . . . . . . 40 synchronous DRAM timing . . . . . . . . . . . . . . . . . . . . . . . . 42 HOLD/HOLDA timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 reset timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 external interrupt timing . . . . . . . . . . . . . . . . . . . . . . . . . . 49 PCI I/O timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 PCI reset timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 PCI serial EEPROM interface timing . . . . . . . . . . . . . . . 52 multichannel buffered serial port timing . . . . . . . . . . . . . 53 DMAC, timer, power-down timing . . . . . . . . . . . . . . . . . . 63 JTAG test-port timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Ccon102控制器手册v0.5

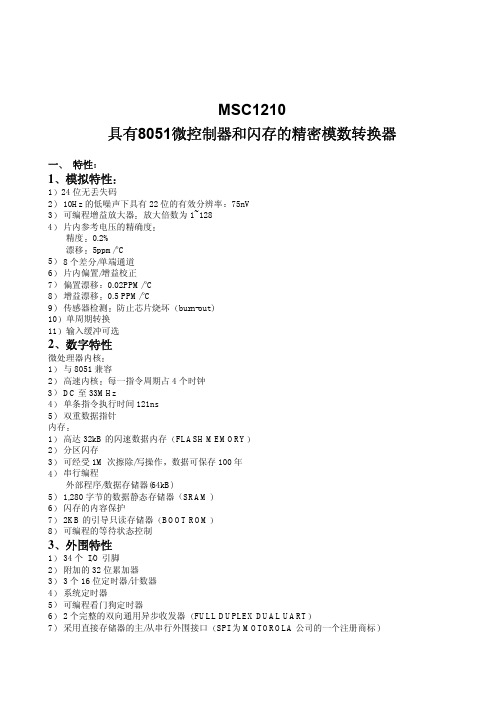

msc1210中文

参数

模拟输入 AIN0-AIN7 AINCOM 模拟输入范

围

全输入电压范围 差分输入阻抗

输入电流 带宽

快速沉积滤波器 Sinc2滤波器 Sinc2滤波器

可编程增益放大器 输入电容 输入漏电流 熔断电流

偏移DAC 偏移DAC范围 偏移DAC单调性 偏移DAC增益偏差 偏移DAC增益偏差漂移

条件

缓冲区关闭 缓冲区打开 IN+ - IN- 看图4 缓冲区关闭 缓冲区打开

256

内部 MOVX 静态随机存储器 字节 1024

1024

1024

1024

数

外部可存取存储器 字节数

程序 64K 数据 64K

程序 64K 数据 64K

程序 64K 数据 64K

程序 64K 数据 64K

注释 1 所有器件的外围特性相同 仅闪存容量不同 2 类型号的最后一位数字代表片内闪存容量 的大小= 2N KB

DC下 fCM = 60Hz, fDATA = 10Hz fCM = 50Hz, fDATA = 50Hz fCM = 60Hz, fDATA = 60Hz fSIG = 50Hz, fDATA = 50Hz fSIG = 60Hz, fDATA = 60Hz

DC下 dB =–20log( VOUT/ VDD)

MSC1210YX

最小值

典型值

最大值

单位

AGND-0.1 AGND

1

5/PGA 0.5

AVDD+0.1

AVDD-1.5

+VREF/PGA

0.469 • fDATA 0.318 • fDATA 0.262 • fDATA

9 0.5 +6

128

HP Color LaserJet CP1210 系列打印机 说明书

HP Color LaserJet CP1210 系列打印机用户指南版权和许可证© 2007 Copyright Hewlett-Packard Development Company, L.P.未经事先书面许可,严禁进行任何形式的复制、改编或翻译,除非版权法另有规定。

此处包含的信息如有更改,恕不另行通知。

HP 产品及服务的保修仅以随该产品及服务提供的书面保修声明为准。

本文所述任何内容不应被视为附加保修。

对任何技术或编辑错误或者本文所述内容的遗漏,HP 不承担任何责任。

部件号: CC376-90937Edition , 10/2007商标声明Adobe®、AdobePhotoShop® 和PostScript® 是 Adobe Systems Incorporated 的商标。

ENERGY STAR®和 ENERGY STAR 徽标®均为美国环保署在美国的注册标志。

Corel® 是 Corel Corporation 或 Corel Corporation Limited 的商标或注册商标。

Microsoft®、Windows® 和 Windows® XP是 Microsoft Corporation 在美国的注册商标。

Windows Vista™ 是 Microsoft Corporation 在美国和/或其它国家/地区的注册商标或商标。

2目录1 基本知识产品功能 (2)打印机视图 (3)前视图 (3)后视图和侧视图 (3)控制面板概览 (4)USB 连接 (4)型号和序列号 (5)2 软件支持的操作系统 (8)打印机驱动程序 (9)打印设置优先级 (10)打开打印机驱动程序并更改打印设置 (11)删除产品软件 (12)实用程序 (13)HP Color LaserJet CP1210 系列 Toolbox 软件 (13)状态警报软件 (13)3 纸张和打印介质了解纸张和打印介质的使用 (16)支持的纸张和打印介质的尺寸 (17)支持的纸张类型和纸盘容量 (19)特殊纸张或打印介质规格 (20)装入纸张和打印介质 (21)4 打印任务更改打印驱动程序以与介质类型和尺寸相匹配 (24)打印机驱动程序帮助 (25)取消打印作业 (26)在 Windows 中创建和使用打印快捷方式 (27)打印小册子 (28)打印质量设置 (29)在特殊介质上打印 (30)调整文档大小 (31)设置打印方向 (32)使用水印 (33)在页面两面打印(手动双面打印) (34)ZHCN iii在 Windows 中在一张纸上打印多个页面 (35)5 颜色管理颜色 (38)灰度打印 (38)自动或手动调整颜色 (38)手动颜色选项 (38)颜色主题 (39)使用高级颜色功能 (40)HP ImageREt 2400 (40)介质选择 (40)颜色选项 (40)标准红绿蓝 (sRGB) (40)匹配颜色 (41)使用 HP Color LaserJet CP1210 系列 Toolbox 打印 Microsoft Office 基色调色板 (41)6 管理和维护打印信息页 (44)使用 HP Color LaserJet CP1210 系列 Toolbox 软件 (45)查看 HP Color LaserJet CP1210 系列 Toolbox (45)状态 (45)事件记录 (46)帮助 (46)设备设置 (46)纸张处理 (46)打印质量 (47)打印浓度 (47)打印模式 (47)纸张类型 (48)系统设置 (48)设置状态警报 (48)服务 (48)购买耗材 (48)其它链接 (48)管理耗材 (50)打印碳粉盒存放 (50)HP 对非 HP 打印碳粉盒的策略 (50)HP 打假热线和网站 (50)碳粉盒碳粉耗尽时忽略 (50)更换打印碳粉盒 (52)清洁产品 (55)7 解决问题基本故障排除检查清单 (58)影响产品性能的因素 (58)状态指示灯模式 (59)状态警报消息 (63)卡纸 (66)卡塞恢复 (66)iv ZHCN卡纸常见原因 (66)清除卡纸 (67)纸盘 1 卡纸 (67)热凝器区域卡纸 (68)出纸槽卡纸 (69)打印质量问题 (70)提高打印质量 (70)识别和纠正打印缺陷 (70)打印质量检查表 (70)一般打印质量问题 (70)解决彩色文档问题 (74)使用 HP Color LaserJet CP1210 系列 Toolbox 解决打印质量问题 (75)校准产品 (76)执行问题 (77)产品软件问题 (78)附录 A 耗材和附件订购部件、附件和耗材 (80)直接从 HP 订购 (80)通过服务或支持提供商订购 (80)直接通过 HP Color LaserJet CP1210 系列 Toolbox 软件订购 (80)部件号 (81)附录 B 服务与支持Hewlett-Packard 有限保修声明 (84)打印碳粉盒有限保修声明 (85)HP 客户服务 (86)联机服务 (86)电话支持 (86)软件实用程序、驱动程序和电子信息 (86)直接订购 HP 附件或耗材 (86)HP 服务信息 (86)HP 服务协议 (86)HP Color LaserJet CP1210 系列 Toolbox (86)HP 维护协议 (87)HP Care Pack™ 服务和服务协议 (87)延长保修期 (87)重新包装产品 (88)服务信息表 (89)附录 C 规格物理规格 (92)操作环境规格 (93)电气规格 (94)能耗规格 (95)声发射 (96)纸张和打印介质规格 (97)歪斜规格 (98)ZHCN v附录 D 规范信息FCC 规则 (100)环境产品管理计划 (101)保护环境 (101)产生臭氧 (101)能耗 (101)纸张使用 (101)塑料 (101)HP LaserJet 打印耗材 (101)返回和回收说明 (101)美国和波多黎各 (101)多个返回(2 - 8 个碳粉盒) (102)单个返回 (102)货运 (102)美国以外返回 (102)纸张 (102)材料限制 (102)欧盟用户丢弃私人废弃设备的规定 (103)材料安全数据表 (MSDS) (103)更多信息 (103)一致性声明 (104)安全声明 (105)激光安全 (105)加拿大 DOC 规则 (105)VCCI 声明(日本) (105)电源线声明(日本) (105)EMI 声明(韩国) (105)芬兰激光声明 (105)有毒有害物质表(中国) (106)索引 (107)vi ZHCN1基本知识●产品功能●打印机视图ZHCN1产品功能打印●打印 Letter 尺寸和 A4 尺寸的页面时,彩色打印速度可达每分钟 8 页 (8 ppm),黑白打印速度可达每分钟 12 页 (12 ppm)。

NUC微控制器产品系列说明书

M251 Feature

。 Arm® Cortex®-M23 。 运行速度可达 48 MHz

M252 Feature

。 USB 2.0 全速设备无需外 挂晶振

M253 Feature

。 USB 2.0 全速设备无需外 挂晶振

。 高达五路 UART 。 CAN FD x1

2

Low Power

TrustZone

AEC-Q100

Market Trend

随着电子应用对低功耗或电池供电的需 求日益增加,现今的应用必须尽量降低 能源消耗,甚至在极端情况下,可能需 要倚赖单颗电池来维持长达 15 至 20 年 运转

低功耗应用情景包含手持式设备、居家、 AIoT、IIoT (工业物联网) 等应用情景, 使用范围十分广泛

(Programmable Serial I/O) • USB 2.0 全速装置无需外挂晶振 • 独立的 RTC 电源 VBAT 管脚

Highlight

• 支持 1.8 V ~ 5.5 V 串行接口,可连接不同电压 装置

*USCI: Universal Serial Control Interface Controller

C

1.8 3.3 5 M253

CU

3.3 5 M071

1.8 3.3 5 M252

U

3.3 5 M051

1.8 3.3 5 M251

3.3 5 Mini51

3.3 5 3.3 5

1.8 3.3 Nano100

M480 M460 M471 M453 M452 M451

E CU E CU

U C

U

Arm9™

1210使用说明书

HYP1210微机电容器保护装置使用说明书USERGUIDE®ZHEJIANG HUAYI ELECTRIC POWER AUTOMATION CO.,LTD ®ZHEJIANG HUAYI ELECTRIC POWER AUTOMA TION CO.,LTD目录1.适用范围 (4)2.装置功能及保护原理简述 (4)2.1 电气参数测量 (4)2.2 延时速断保护 (4)2.3 定时限过流保护 (4)2.4中性点不平衡电流保护(适用于电容器组双Y形接线) (4)2.5零序电压保护(开口三角电压,适用于单组电容器) (4)2.6过电压保护 (4)2.7低电压保护 (4)2.8 PT断线报警 (5)2.9定值错误报警 (5)2.10装置故障报警 (5)3、技术参数 (5)4.按键功能及操作方法 (6)4.1按键功能 (6)4.1.1“▼”搜索键与功能键 (6)4.1.2“◄►”显示、进入修改状态及移动、修改键 (6)4.1.3“▲”修改、操作键 (6)4.1.4“■信号复归”键 (6)4.2输入密码的方法: (6)4.3搜索方法(适用于定点显示和进入定值区的显示): (6)4.4密码种类 (6)5.数码管的显示种类 (6)5.1 数码管显示说明 (6)5.2几种显示列表 (6)5.2.1循环显示(供运行人员使用) (7)5.2.2定点显示 (7)5.2.3定值区的显示(输入密码1111) (7)5.2.4有报警或预告时的显示: (8)6.调试大纲(适用于调试人员及维护人员) (9)6.1查看、输入或修改保护定值: (9)6.2开关量的检查 (9)6.3保护继电器的出口检查 (9)6.4模拟量输入检查及精度检查 (9)6.4.1电流校准 (9)6.4.2电压校准 (9)6.4.3不平衡电流校准 (9)6.6保护试验 (10)6.6.1延时速断与定时限过流保护测试 (10)6.6.2过电压保护测试 (10)6.6.3低电压保护测试 (10)®ZHEJIANG HUAYI ELECTRIC POWER AUTOMA TION CO.,LTD®ZHEJIANG HUAYI ELECTRIC POWER AUTOMA TION CO.,LTD 36.6.4不平衡电流保护测试 (10)6.6.5零序电压保护测试 (10)6.6.6保护动作时间测试 (10)6.6.7 PT回路断线报警 (10)7.机箱结构及端子图 (11)7.1装置组成 (11)7.1机箱结构图与说明 (11)7.2安装与开孔图 (12)7.3装置端子图 (12)8.运行人员注意事项及要求 (13)9.检修及维护 (14)附录1:HYP1210微机电容器保护装置原理图 (1)附录2:HYP1210微机电容器保护装置原理接线图 (2)1.适用范围HYP1210微机电容器保护装置适用于6-66KV 中性点不接地系统,作为电容器的成套保护和监视报警装置,适用于高低压开关柜、箱式变电站等使用电容补偿的场合。

RGB七彩灯条控制IC

RGB七彩灯条控制芯片使用说明.按下遥控器上的按钮,实现对应按键功能:对应固定颜色、所有颜色循环跳变(FLASH/STROBE)、颜色渐变实现N多种颜色(FADE/SHOOTH)、亮度加减、开关机。

产品应用芯片应用于:LED光条,LED模组,LED灯箱,发光字等;具有价格低廉,接线方便,使用简单等优点;带有记忆存储功能,可通过红外遥控器进行静态亮度调节,静态颜色选择,动态速度调节等灯光变化效果。

终端产品广泛应用于:家居、商业、长廊、酒店、会议室,学校、博物馆、工业等室内,建筑照明。

功能说明(1)七彩灯主控芯片可以自动识别有无外接24C02,有24C02则是带记忆功能。

(2)不带记忆下上电默认:FLASH- STROBE- FADE- SHOOTH 循环,上电无闪烁!(3)按下颜色按钮,LED会发对应的颜色。

接收端解码成功率100%,无错码!(4)产品特点:可以改变任何单颜色亮度共32级。

跳变、渐变速度32级符号按键说明符号按键说明符号按键说明符号按键说明亮度、速度加(共32级)亮度、速度减(共32级)开闭输出开启输出静态红色静态绿色静态蓝色(红蓝静态白色(红绿蓝)静态橙色(红绿)静态淡绿色(绿蓝)静态深蓝色(红蓝所有单色跳变静态深黄色(红绿)静态青色(绿蓝)静态褐色(红蓝)七彩跳变静态黄色(红绿)静态浅蓝色(绿蓝)静态粉红(红蓝)七彩渐变静态淡黄色(红绿)静态淡蓝色(绿蓝)静态紫色(红蓝)全彩渐变典型应用引脚示意图引脚功能电气特性TA = 25°C, VDD = 5V , VSS = 0V引脚名称 引脚功能说明VDD 1 电源正极NC 2 带记忆接24C02的SDA AC 3 带记忆接24C02的SCLIR4 红外接收头输入 R5 接红色LED 驱动电路 G6 接绿色LED 驱动电路 B7 接蓝色LED 驱动电路VSS8电源负极参数 最小值 典型值 最大值 单位VDD 工作电压范围 2.5 5 5.5 V TA 商用级工作温度0 — 70 °C 工业级工作温度 -40 — 85 °C ICC 空载电流 — — 2 MA IOH RGB 输出口驱动电流10.5 17 — MA FCLK 时钟频率— 4 — MHZ FZ PWM 频率—100—HZ芯片封装信息。

cc1150中文

第 - 2 - 页 共 46 页

目录 1 缩写词 ......................................................................................................................................... 2 2 绝对最大等级 ............................................................................................................................. 5 3 工作条件 ..................................................................................................................................... 5 4 电气规范 ..................................................................................................................................... 5 5 常规特性 ..................................................................................................................................... 6 6 RF 传输环节 .............................................................

MC14106B中文资料

MC14106B 中文资料目录元件的最大额定值 (1)MC14106B功能介绍 (1)电气特性 (3)芯片转换特性 (4)芯片应用举例 (4)应用1 按键防抖 (4)应用2 积分电路 (5)MC14106B封装信息 (6)PDIP-14封装 (6)SOIC-14封装 (7)TSSOP-14封装 (8)元件的最大额定值条件之上进行功能操作。

长期暴露在高于推荐工作条件的环境下可能会影响器件的可靠性。

表中的电压值均为对地电压。

MC14106B功能介绍MC14106B共14个引脚,其中14号引脚为VDD(+),7号引脚为VSS (-),其余引脚为输入输出引脚,1,3,5,9,11,13号引脚为输入引脚,2,4,6,8,10,12号引脚为输出引脚。

内部逻辑如图1如所示,从图1中我们可以看出,MC14106B内部共有6组相同功能施密特触发器,每组施密特触发器的逻辑如图2所示。

图1图2下面通过图3所示施密特触发器讲解其工作过程。

其工作时序如图4所示。

当输入端输入低电平(VSS)时,输出端输出高电平(V OH)。

当输入端电平变为高电平(VDD)时,输出端电平经过一小段时间后也会发生变化,变为低电平(V OL)。

当输入端电平由VDD变为VSS后,一小段时间后,输出端电平变为高电平(V OH)。

施密特触发器最重要的是以下几个参数:从输入端电平由低到高变化到50%时,至输出端电平由高到低变化变化至50%时的时间记做t PHL;从输入端电平由高到低变化到50%时,至输出端电平由低到高变化变化至50%时的时间记做t PLH。

当输出端产生下调沿时,电平从90%变化至10%所用的时间t f;当输出端产生上跳沿时,电平从10%变化至90%所用的时间t r。

这些参数主要与VDD有关,可以通过下面提供的电气特性表格查出典型值。

图3图4通过图5进一步讲解施密特触发器的工作流程。

当输入端的电平达到V T+之后,输出端电平才会发生负跳变,当输入端平超过V T+之后,即使略低于该值,输出端不会发生负跳变,直到当输入端电平低于V T-,输出端才会发生正跳变。

DS1210中文资料

DS1210中文资料FEATURES Converts CMOS RAMs into nonvolatile memories Unconditionally write protects when V CC isout of toleranceAutomatically switches to battery when power-fail occursSpace saving 8-pin DIPConsumes less than 100 nA of battery current Tests battery condition on power up Provides for redundant batteries Optional 5% or 10% power-fail detection Low forward voltage drop on the V CC switch Optional 16-pin SOIC surface mount package Optional industrial temperature range of -40°C to +85°CPIN ASSIGNMENTPIN DESCRIPTIONV CCO - RAM Supply V BAT1- + Battery 1TOL - Power Supply Tolerance GND- GroundCE - Chip Enable Input CEO- Chip Enable Output V BAT2- + Battery 2V CCI - + Supply NC- No ConnectDESCRIPTIONThe DS1210 Nonvolatile Controller Chip is a CMOS circuit which solves the application problem of converting CMOS RAM into nonvolatile memory. Incoming power is monitored for an out-of-tolerance condition. When such a condition is detected, chip enable is inhibited to accomplish write protection and the battery is switched on to supply the RAM with uninterrupted power. Special circuitry uses a low-leakage CMOS process whichaffords precise voltage detection at extremely low battery consumption.The 8-pin DIP package keeps PC board real estate requirements to a minimum. By combining the DS1210 Nonvolatile Controller Chip with a CMOS memory and batteries, nonvolatile RAM operation can be achieved.DS1210Nonvolatile Controller ChipVCCOVCCI VBAT2CEO DS1210 8-pin DIP (300-mil)See Mech. Drawings Section NC VCCO NC NC TOL NC GND NC VCCI NC VBAT2NC CEO NC CESee Mech. Drawings SectionDS1210 OPERATIONThe DS1210 nonvolatile controller performs five circuit functions required to battery back up a RAM.First, a switch is provided to direct power from the battery or the incoming supply (V CCI) depending onwhich is greater. This switch has a voltage drop of less than 0.3V. The second function which thenonvolatile controller provides is power-fail detection. The DS1210 constantly monitors the incomingsupply. When the supply goes out of tolerance a precision comparator detects power-fail and inhibits chip enable (CEO). The third function of write protection is accomplished by holding the CEO output signal to within 0.2 volts of the V CCI or batterysupply. If CE input is low at the time power-fail detection occurs, the CEO output is kept in its present state until CE is returned high. The delay of write protection untilthe current memory cycle is completed prevents the corruption of data. Power-fail detection occurs in the range of 4.75 volts to 4.5 volts with the tolerance Pin 3 grounded. If Pin 3 in connected to V CCO, thenpower-fail detection occurs in the range of 4.5 volts to 4.25 volts. During nominal supply conditions CEO will follow CE with a maximum propagation delay of 20ns. The fourth function the DS1210 performs is a battery status warning so that potential data loss is avoided. Each time that the circuit ispowered up the battery voltage is checked with a precision comparator. If the battery voltage is less than2.0 volts, the second memory cycle is inhibited. Battery status can, therefore, be determined byperforming a read cycle after power-up to any location in memory, verifying that memory locationcontent. A subsequent write cycle can then be executed to the same memory location altering the data. Ifthe next read cycle fails to verify the written data, then the batteries are less than 2.0V and data is indanger of being corrupted. The fifth function of the nonvolatile controller provides for batteryredundancy. In many applications, data integrity is paramount. In these applications it is often desirable to use two batteries to ensure reliability. The DS1210 controller provides an internal isolation switch whichallows the connection of two batteries. During battery backup operation the battery with the highestvoltage is selected for use. If one battery should fail, the other will take over the load. The switch to aredundant battery is transparent to circuit operation and to the user. A battery status warning will occurwhen the battery in use falls below 2.0 volts. A grounded V BAT2 pin will not activate a battery-failwarning. In applications where battery redundancy is not required, a single battery should be connected tothe BAT1 pin. The BAT2 battery pin must be grounded. The nonvolatile controller contains circuitry toturn off the battery backup. This is to maintain the battery(s) at its highest capacity until the equipment is powered up and valid data is written to the SRAM. While in the freshness seal mode the CEO and V CCO will be forced to V OL. When the batteries are first attached to one or both of the V BAT pins, V CCO will not provide battery back-up until V CCI exceeds V CCTP, as set by the T OL pin, and then falls below V BAT. Figure 1 shows a typical application incorporating the DS1210 in a microprocessor-based system. Section A shows the connections necessary to write protect the RAM when V CC is less than 4.75 volts and to back up the supply with batteries. Section B shows the use of the DS1210 to halt the processor when V CC is less than 4.75 volts and to delay its restart on power-up to prevent spurious writes.DS1210 SECTION A - BATTERY BACKUP Figure 1BATTERY BACKUP CURRENT DRAIN EXAMPLECONSUMPTIONDS1210 I BAT100 nARAM I CC0210 μATotal Drain10.1 μASECTION B - PROCESSOR RESETABSOLUTE MAXIMUM RATINGS*Voltage on Any Pin Relative to Ground-0.3V to +7.0VOperating Temperature0°C to 70°CStorage Temperature-55°C to +125°CSoldering Temperature260°C for 10 seconds*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability. RECOMMENDED DC OPERATING CONDITIONS(0°C to 70°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Pin 3 = GND Supply Voltage V CCI 4.75 5.0 5.5V1Pin 3 = V CCO Supply Voltage V CCI 4.5 5.0 5.5V1 Logic 1 Input V IH 2.2V CC+0.3V1 Logic 0 Input V IL-0.3+0.8V12.0 4.0V1, 2 Battery Input V BAT1,V BAT2(0°C to 70°C; V CCI = 4.75 to 5.5V PIN 3 = GND)CAPACITANCE(T A = 25°C) PARAMETER SYMBOL MIN TYP MAX UNITS NOTES Input Capacitance C IN5pFOutput Capacitance C OUT7pF(0°C to 70°C; V CCI = 4.75V to 5.5V, PIN 3 = GND)NOTES:1.All voltages are referenced to ground.2.Only one battery input is required. Unused battery inputs must be grounded.3.Measured with V CCO and CEO open.4.I CC01is the maximum average load which the DS1210 can supply to the memories.5.Measured with a load as shown in Figure 2.6.I CC02is the maximum average load current which the DS1210 can supply to the memories in thebattery backup mode.7.t CE max. must be met to ensure data integrity on power loss.8.CEO can only sustain leakage current in the battery backup mode.TIMING DIAGRAM: POWER-UPTIMING DIAGRAM: POWER-DOWNOUTPUT LOAD Figure 2。

MPC106资料

Semiconductor Products SectorThis document contains information on a new product under development by Motorola.Motorola reserves the right to change or discontinue this product without notice.Technical DataMPC106 PCI Bridge/Memory Controller Hardware SpecificationsThe Motorola MPC106 PCI bridge/memory controller provides a PowerPC™ microprocessor common hardware reference platform (CHRP™) compliant bridge between the PowerPC microprocessor family and the Peripheral Component Interconnect (PCI) bus. In this document, the term ‘106’ is used as an abbreviation for the phrase ‘MPC106 PCI bridge/memory controller.’ This document contains pertinent physical characteristics of the 106. For functional characteristics, refer to the MPC106 PCI Bridge/Memory Controller User’s Manual .This document contains the following topics:TopicPageSection 1.1, “Overview”2Section 1.2, “Features”3Section 1.3, “General Parameters”5Section 1.4, “Electrical and Thermal Characteristics”5Section 1.5, “Pin Assignments”15Section 1.6, “Pinout Listings16Section 1.7, “Package Description”20Section 1.8, “System Design Information”22Section 1.9, “Document Revision History”27Section 1.10, “Ordering Information”27OverviewIn this document, the term ‘60x’ is used to denote a 32-bit microprocessor from the PowerPC architecture family that conforms to the bus interface of the PowerPC 601™, PowerPC 603™, or PowerPC 604™microprocessors. Note that this does not include the PowerPC 602™ microprocessor which has a multiplexed address/data bus. 60x processors implement the PowerPC architecture as it is specified for 32-bit addressing, which provides 32-bit effective (logical) addresses, integer data types of 8, 16, and 32 bits, and floating-point data types of 32 and 64 bits (single-precision and double-precision).To locate any published errata or updates for this document, refer to the website at /SPS/PowerPC/.1.1 OverviewThe MPC106 provides an integrated high-bandwidth, high-performance, TTL-compatible interface between a 60x processor, a secondary (L2) cache or additional (up to four total) 60x processors, the PCI bus, and main memory. This section provides a block diagram showing the major functional units of the 106 and describes briefly how those units interact.Figure 1 shows the major functional units within the 106. Note that this is a conceptual block diagram intended to show the basic features rather than how these features are physically implemented on the device.Figure 1. Block DiagramFeatures The 106 provides a PowerPC microprocessor CHRP-compliant bridge between the PowerPC microprocessor family and the PCI bus. CHRP documentation provides a set of specifications that define a unified personal computer architecture. PCI support allows the rapid design of systems using peripherals already designed for PCI and the other standard interfaces available in the personal computer hardware environment. The 106 integrates secondary cache control and a high-performance memory controller, uses an advanced, 3.3-V CMOS process technology, and is fully compatible with TTL devices.The 106 supports a programmable interface to a variety of PowerPC microprocessors operating at select bus speeds. The 60x address bus is 32 bits wide and the data bus is 64 bits wide. The 60x processor interface of the 106 uses a subset of the 60x bus protocol, supporting single-beat and burst data transfers. The address and data buses are decoupled to support pipelined transactions.The 106 provides support for the following configurations of 60x processors and L2 cache:•Up to four 60x processors with no L2 cache• A single 60x processor plus a direct-mapped, lookaside L2 cache using the internal L2 cache controller of the 106•Up to four 60x processors plus an externally controlled L2 cache (such as the Motorola MPC2605 integrated secondary cache)The memory interface controls processor and PCI interactions to main memory and is capable of supporting a variety of configurations using DRAM, EDO, SDRAM, ROM, or Flash ROM.The PCI interface of the 106 complies with the PCI Local Bus Specification, Revision 2.1, and follows the guidelines in the PCI System Design Guide, Revision 1.0,for host bridge architecture. The PCI interface connects the processor and memory buses to the PCI bus, to which I/O components are connected. The PCI bus uses a 32-bit multiplexed address/data bus, plus various control and error signals.The PCI interface of the 106 functions as both a master and target device. As a master, the 106 supports read and write operations to the PCI memory space, the PCI I/O space, and the PCI configuration space. The 106 also supports PCI special-cycle and interrupt-acknowledge commands. As a target, the 106 supports read and write operations to system memory.The 106 provides hardware support for four levels of power reduction: doze, nap, sleep, and suspend. The design of the MPC106 is fully static, allowing internal logic states to be preserved during all power-saving modes.1.2 FeaturesThis section summarizes the major features of the 106, as follows:•60x processor interface—Supports up to four 60x processors—Supports various operating frequencies and bus divider ratios—32-bit address bus, 64-bit data bus—Supports full memory coherency—Supports optional 60x local bus slave—Decoupled address and data buses for pipelining of 60x accesses—Store gathering on 60x-to-PCI writesFeatures•Secondary (L2) cache control—Configurable for write-through or write-back operation—Supports cache sizes of 256 Kbytes, 512 Kbytes, and 1 Mbyte—Up to 4 Gbytes of cacheable space—Direct-mapped—Supports byte parity—Supports partial update with external byte decode for write enables—Programmable interface timing—Supports pipelined burst, synchronous burst, or asynchronous SRAMs—Alternately supports an external L2 cache controller or integrated L2 cache module •Memory interface— 1 Gbyte of RAM space, 16 Mbytes of ROM space—Supports parity or error checking and correction (ECC)—High-bandwidth, 64-bit data bus (72 bits including parity or ECC)—Supports fast page mode DRAMs, extended data out (EDO) DRAMs, and synchronous DRAMs (SDRAMs)—Supports 1 to 8 banks of DRAM/EDO/SDRAM with sizes ranging from 2 Mbyte to 128 Mbytes per bank—ROM space may be split between the PCI bus and the 60x/memory bus (8 Mbytes each)—Supports 8-bit asynchronous ROM or 64-bit burst-mode ROM—Supports writing to Flash ROM—Configurable external buffer control logic—Programmable interface timing•PCI interface—Compliant with PCI Local Bus Specification, Revision 2.1—Supports PCI interlocked accesses to memory using LOCK signal and protocol—Supports accesses to all PCI address spaces—Selectable big- or little-endian operation—Store gathering on PCI writes to memory—Selectable memory prefetching of PCI read accesses—Only one external load presented by the MPC106 to the PCI bus—Interface operates at 20–33 MHz—Word parity supported— 3.3 V/5.0 V-compatible•Support for concurrent transactions on 60x and PCI buses•Power management—Fully-static 3.3-V CMOS design—Supports 60x nap, doze, and sleep power management modes and suspend mode •IEEE 1149.1-compliant, JTAG boundary-scan interface•304-pin ceramic ball grid array (CBGA) packageGeneral Parameters1.3 General ParametersThe following list provides a summary of the general parameters of the 106:Technology0.5 µm CMOS, four-layer metalDie size 5.8 mm x 7.2 mm (41.8 mm2)Transistor count250,000Logic design Fully-staticPackages Surface mount 304-lead C4 ceramic ball grid array (CBGA)Power supply 3.3 V ± 5% V DCMaximum input rating 5.0 V ± 10% V DC1.4 Electrical and Thermal CharacteristicsThis section provides both the AC and DC electrical specifications and thermal characteristics for the 106.1.4.1 DC Electrical CharacteristicsThe tables in this section describe the 106 DC electrical characteristics. Table 1 provides the absolute maximum ratings. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause it permanent damage.Table 1. Absolute Maximum RatingsCharacteristic Symbol Value Unit NotesSupply voltage Vdd–0.3 to 3.6V—PLL supply voltage AVdd–0.3 to 3.6V—Input voltage V in–0.3 to 5.5V1 Junction temperature T j0 to 105°C2 Storage temperature range T stg–55 to 150°C—Notes:1Caution: V in must not exceed Vdd by more than 2.5 V at all times including during power-on reset.2The extended temperature parts have die junction temperature of -40 to 105°C. See MPC106ARXTGPNS/D for more information.Table 2 provides the recommended operating conditions for the 106. Proper device operation outside of these recommended and tested conditions is not guaranteed.Electrical and Thermal CharacteristicsTable 3 provides the package thermal characteristics for the 106.Table 4 provides the DC electrical characteristics for the 106, assuming Vdd = A Vdd = 3.3 ± 5% V DC,GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 5 lists the power consumption of the 106.Table 2. Recommended Operating ConditionsCharacteristic Symbol Value Unit Notes Supply voltage Vdd 3.3 ± 165 mv V —PLL supply voltage AVdd 3.3 ± 165 mv V —Input voltageV in 0 to 5.5V —Die junction temperatureT j0 to 105°CThe extended temperature parts have die junction temperature of -40 to 105°CTable 3. Package Thermal CharacteristicsCharacteristicSymbol Value Rating CBGA package thermal resistance, junction-to-top of dieθ JC0.133°C/WNote : Refer to Section 1.8, “System Design Information,” for more details about thermal management.Table 4. DC Electrical SpecificationsCharacteristicSymbol Min Max Unit Input high voltage (all inputs except SYSCLK)V IH 2 5.5V Input low voltage (all inputs except SYSCLK)V IL GND 0.8V SYSCLK input high voltage CV IH 2.4 5.5V SYSCLK input low voltage CV IL GND 0.4V Input leakage current, V in =3.3 V 1I in —15.0µA Hi-Z (off-state) leakage current, V in = 3.3 V 1 I TSI —15.0µA Output high voltage, I OH = -7 mA 2 V OH 2.4—V Output low voltage, I OL = 7 mA 2V OL —0.5V PCI 3.3 V signaling output high voltage, I OH = -0.5 mA 2 V OH 2.7—V PCI 3.3 V signaling output low voltage, I OL = 1.5 mA 2 V OL —0.3V Capacitance, V in = 0 V , f = 1 MHz 3C in—7.0pFNotes:1 Excludes test signals (LSSD_MODE and JT AG signals).2 This value represents worst case 40-ohm drivers (default value for Processor/L2 control signals CI, WT , GBL, TBST , TSIZ[0–2], TT[0–4], TWE, and TV) only. Other signals have lower default driver impedance and will support larger I OH and I OL . All drivers may optionally be programmed to different driver strengths. 3Capacitance is periodically sampled rather than 100% tested.Electrical and Thermal Characteristics1.4.2 AC Electrical CharacteristicsThis section provides AC electrical characteristics for the 106. After fabrication, parts are sorted by maximum 60x processor bus frequency, as shown in Section 1.4.2.1, “Clock AC Specifications,” and tested for conformance to the AC specifications for that frequency. These specifications are for operation between 16.67 and 33.33 MHz PCI bus (SYSCLK) frequencies. The 60x processor bus frequency is determined by the PCI bus (SYSCLK) frequency and the settings of the PLL[0–3] signals. All timings are specified relative to the rising edge of SYSCLK.1.4.2.1 Clock AC SpecificationsTable 6 provides the clock AC timing specifications as shown in Figure 2, and assumes Vdd = A Vdd = 3.3± 5% V DC, GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 5. Power ConsumptionModeSYSCLK/Core 33/66 MHzSYSCLK/Core 33/83.3 MHzUnitFull-OnT ypical Maximum1.22.2W 1.42.4WDozeT ypical Maximum1.0 1.1W 1.21.4WNapT ypical Maximum1.0 1.1W 1.21.4WSleepT ypical Maximum260330mW 360450mWSuspendT ypical Maximum140220mW 190270mWNotes:•Power consumption for common system configurations assuming 50 pF loads •Suspend power-saving mode assumes SYSCLK off and PLL in bypass mode.•T ypical power is an average value measured at Vdd = AVdd = 3.30 V and T A = 25 °C. •Maximum power is measured at Vdd = AVdd = 3.45 V and T A= 25 °C.Electrical and Thermal CharacteristicsFigure 2 provides the SYSCLK input timing diagram.Figure 2. SYSCLK Input Timing Diagram1.4.2.2 Input AC SpecificationsTable 7 provides the input AC timing specifications for the 106 as defined in Figure 3 and Figure 4. These specifications are for operation between 16.67 and 33.33 MHz PCI bus clock (SYSCLK) frequencies.Assume Vdd = A Vdd = 3.3 ± 5% V DC, GND = 0 V DC, and 0 ≤ T j ≤ 105 °C.Table 6. Clock AC Timing SpecificationsNum Characteristic SYSCLK/Core 33/66 MHz SYSCLK/Core 33/83.3 MHz Unit NotesMinMax Min Max —60x processor bus (core) frequency 16.676616.6783.3MHz 1—VCO frequency 120200120200MHz 1, 2—SYSCLK frequency 16.6733.3316.6733.33MHz 11SYSCLK cycle time 30.060.030.060.0ns —2, 3SYSCLK rise and fall time— 2.0— 2.0ns 34SYSCLK duty cycle measured at 1.4 V 40604060%4—SYSCLK jitter—±200—±200ps 5—106 internal PLL relock time—100—100µ s4, 6Notes :1 Caution : The SYSCLK frequency and PLL[0–3] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL[0–3] signal description in Section 1.8, “System Design Information,” for valid PLL[0–3] settings, and to Section 1.9, “Document Revision History,” for available frequencies and part numbers.2 VCO operating range for extended temperature devices is different. Refer to MPC106ARXTGPNS/D for more information.3 Rise and fall times for the SYSCLK input are measured from 0.4 V to 2.4 V . 4 Timing is guaranteed by design and characterization and is not tested.5 The total input jitter (short-term and long-term combined) must be under ±200 ps.6PLL-relock time is the maximum time required for PLL lock after a stable Vdd, AVdd, and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled andsubsequently re-enabled during the sleep and suspend power-saving modes. Also note that HRST must be held asserted for a minimum of 255 bus clocks after the PLL-relock time (100 µs) during the power-on reset sequence.Electrical and Thermal CharacteristicsFigure 3 provides the input timing diagram for the 106.Table 7. Input AC Timing SpecificationsNumCharacteristic66 MHz83.3 MHzUnitNotesMinMaxMin Max10a Group I input signals valid to 60x Bus Clock (input setup) 4.0 3.5ns 1,2,310a Group II input signals valid to 60x Bus Clock (input setup) 3.5 3.5ns 1,2,410a Group III input signals valid to 60x Bus Clock (input setup) 3.0 2.5ns 1,2,510a Group IV input signals valid to 60x Bus Clock (input setup) 5.0 4.0ns 1,2,610b Group V input signals valid to SYSCLK (input setup)7.07.0ns 7,810b Group VI input signals valid to SYSCLK (input setup)7.07.0ns 7,911a 60x Bus Clock to group I–IV inputs invalid (input hold)0—0—ns 3,4,5,611b SYSCLK to group V–VI inputs invalid (input hold)–0.5—–0.5—ns8,9HRST pulse width255 x t sysclk + 100 µs —255 x t sysclk + 100 µs ——10c Mode select inputs valid to HRST (input setup) 3 x t sysclk— 3 x t sysclk—ns 10, 11,1211c HRST to mode select input invalid (input hold)1.0—1.0—ns10, 12Notes:1Input specifications are measured from the TTL level (0.8 or 2.0 V) of the signal in question to the 1.4 V of the rising edge of SYSCLK. Both input and output timings are measured at the pin (see Figure 3).2Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK).3Group I input signals include the following processor, L2, and memory interface signals: A[0–31], P AR[0–7]/AR[1–8], BR[0–4], BRL2, XA TS, LBCLAIM, ADS, BA0, TV and HIT (when configured for external L2)4Group II input signals include the following processor and memory interface signals: TBST , TT[0–4], TSIZ[0–2], WT , CI, GBL, AACK, and T A.5Group III input signals include the following processor and memory interface signals: DL[0–31] and DH[0–31].6Group IV input signals include the following processor and L2 interface signals: TS, ARTRY , DIRTY_IN, and HIT (when configured for internal L2 controller).7PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 3.0 V or V OL = 0.3 V . PCI 5 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 2.4 V or V OL = 0.55 V .8Group V input signals include the following bussed PCI interface signals: FRAME, C/BE[0–3], AD[0–31], DEVSEL, IRDY , TRDY , STOP , P AR, PERR, SERR, LOCK, FLSHREQ, and ISA_MASTER.9Group VI input signal is the point-to-point PCI GNT input signal.10The setup and hold time is with respect to the rising edge of HRST (see Figure 4). Mode select inputs include the RCS0, FOE, and DBG0 configuration inputs.11 tsysclk is the period of the external clock (SYSCLK) in nanoseconds (ns). When the unit is given as t sysclk , the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.12These values are guaranteed by design and are not tested.Electrical and Thermal CharacteristicsFigure 3. Input Timing DiagramFigure 4 provides the mode select input timing diagram for the 106.Figure 4. Mode Select Input Timing Diagram1.4.2.3 Output AC SpecificationsTable 8 provides the output AC timing specifications for 106 (shown in Table 5). Assume Vdd = A Vdd =3.3 ± 5% V DC, GND = 0 V DC, CL = 50 pF, and 0 ≤ T j ≤ 105 °C. Processor and memory interface signals are specified from the rising edge of the 60x bus clock (which is internally synchronized to SYSCLK). All units are nanoseconds.VM = Midpoint Voltage (1.4 V)HRSTMODE PINSElectrical and Thermal Characteristics Table 8. Output AC Timing SpecificationsNum Characteristic66 MHz83.3 MHzNotes Min Max Min Max12SYSCLK to output driven (outputenable time)2.0— 2.0—113a SYSCLK to output valid for TS andARTRY—7.0— 6.02, 3, 413b SYSCLK to output valid for all non-PCIsignals except TS, ARTRY, RAS[0–7],CAS[0–7], and DWE[0-2]—7.0— 6.02, 3, 514a SYSCLK to output valid (for RAS[0–7]and CAS[0–7])—7.0— 6.02, 3 14b SYSCLK to output valid for PCI signals—11.0—11.03, 615a SYSCLK to output invalid for allnon-PCI signals (output hold)1.0— 1.0—7, 1015b SYSCLK to output invalid for PCIsignals (output hold)1.0— 1.0—718SYSCLK to ARTRY high impedancebefore precharge (output hold)—8.0—8.0119SYSCLK to ARTRY precharge enable (0.4 *t sysclk) + 2.0—(0.4 xt sysclk) + 2.0—8, 121SYSCLK to ARTRY high impedance after precharge —(1.5 *t sysclk) + 8.0—(1.5 xt sysclk) + 8.08, 1Notes:1These values are guaranteed by design and are not tested.2Output specifications are measured from 1.4 V on the rising edge of the appropriate clock to the TTL level (0.8 V or 2.0 V) of the signal in question. Both input and output timings are measured at the pin (see Figure 5).3The maximum timing specification assumes C L = 50 pF.4The shared outputs TS and ARTRY require pull-up resistors to hold them negated when there is no bus master driving them.5When the 106 is configured for asynchronous L2 cache SRAMs, the DWE[0–2] signals have a maximum SYSCLK to output valid time of (0.5 x t PROC) + 8.0 ns (where t PROC is the 60x bus clock cycle time).6PCI 3.3 V signaling environment signals are measured from 1.65 V (Vdd ÷ 2) on the rising edge of SYSCLK to V OH = 3.0 V or V OL = 0.3 V.7The minimum timing specification assumes C L = 0 pF.8tsysclk is the period of the external bus clock (SYSCLK) in nanoseconds (ns). When the unit is given as t sysclk the numbers given in the table must be multiplied by the period of SYSCLK to compute the actual time duration (in nanoseconds) of the parameter in question.9PCI devices which require more than the PCI-specified hold time of Th = 0ns or systems where clock skewapproaches the PCI-specified allowance of 2ns may not work with the MPC106. For workarounds, see Motorola application note Designing PCI 2.1-Compliant MPC106 Systems (order number AN1727/D).Electrical and Thermal CharacteristicsFigure 5 provides the output timing diagram for the 106.Figure 5. Output Timing Diagram1.4.3 JTAG AC Timing SpecificationsTable 9 provides the JTAG AC timing specifications. Assume Vdd = A Vdd = 3.3 ± 5% V DC, GND = 0 V DC, CL = 50 pF, and 0 ≤ T j ≤ 105 °C.Table 9. JTAG AC Timing Specifications (Independent of SYSCLK)Num CharacteristicMin Max Unit Notes —TCK frequency of operation 025MHz —1TCK cycle time40—ns —2TCK clock pulse width measured at 1.4 V 20—ns —3TCK rise and fall times03ns 14TRST setup time to TCK rising edge 10—ns 25TRST assert time10—ns160x Bus ClockALL Non-PCI TSARTRYVM = Midpoint Voltage (1.4V)(Except TS andARTRY)SYSCLKALLOUTPUTS PCI OUTPUTSElectrical and Thermal CharacteristicsFigure 6 provides the JTAG clock input timing diagram.Figure 6. JTAG Clock Input Timing DiagramFigure 7 provides the TRST timing diagram.Figure 7. TRST Timing Diagram6Boundary-scan input data setup time 5—ns 37Boundary-scan input data hold time 15—ns 38TCK to output data valid 030ns 49TCK to output high impedance 030ns 410TMS, TDI data setup time 5—ns —11TMS, TDI data hold time 15—ns 112TCK to TDO data valid 015ns —13TCK to TDO high impedance15ns—Notes :1These values are guaranteed by design, and are not tested2TRST is an asynchronous signal. The setup time is for test purposes only.3Non-test signal input timing with respect to TCK.4Non-test signal output timing with respect to TCK.Table 9. JTAG AC Timing Specifications (Independent of SYSCLK) (Continued)Num CharacteristicMin Max Unit NotesTCKVM = Midpoint Voltage (1.4 V)TRSTTCKElectrical and Thermal CharacteristicsFigure 8 provides the boundary-scan timing diagram.Figure 9. Test Access Port Timing DiagramTCKData InputsData OutputsData OutputsData OutputsTCKTDI, TMSTDOTDOTDOPin Assignments1.5 Pin AssignmentsFigure 10 contains the pin assignments for the MPC106, and Figure 11 provides a key to the shading.Figure 11. Pin Assignments Shading Key16151413121110987654321WW V V U U TT R R P P N N M M L L K K J J H H G G F F E E D D C C B B AA16151413121110987654321Figure 10. Pin AssignmentsNo ConnectPower Supply GroundPower Supply PositiveAVddClock Power Supply Positive (K9)VIEWSignalsPinout Listings1.6 Pinout ListingsTable 10 provides the pinout listing for the MPC106. S ome signals have dual functions and are shown more than once.Table 10. Pinout ListingSignal Name Pin Number Active I/O60x Processor Interface SignalsHigh I/O A[0–31]R2, P2, N2, M2, L2, K2, J5, K4, K5, K6, J2, J6, J3, J4, H3,H4, H2, G2, F1, E1, E2, F4, E3, D1, C1, C2, B1, C3, B2, E4,D3, E5AACK D2Low I/OARTRY F2Low I/OBG0K3Low OutputBG1R4Low Output (DIRTY_OUT)R5Low Output BG2(TWE)T1Low Output BG3(DCS)BR0L3Low InputT3Low Input BR1(DIRTY_IN)T6Low Input BR2(TV)T5Low Input BR3(BA0)CI N3Low I/ODBG0L5Low OutputU4Low Output DBG1(TOE)DBG2P3Low Output (DWE0)H11Low Output DBG3(DWE1)DBGLBJ10Low Output (CKE)DH[0–31]T14, R13, R14, P13, P14, N13, U3, W1, V2, W2, V3, W3, V4,High I/OW4, V5, W5, V6, W6, V7, W7, V8, W8, N8, W9, V9, W10, V10,W11, V11, W12, V12, W13High I/O DL[0–31]U6, T7, U7, T8, U8, R8, P8, N9, P9, R9, U9, T9, U10, T10,U13, T13, R12, N14, M13, T2, U1, U2, V1, U15, V16, U14,W16, V15, W15, V14, W14, V13GBL M3Low I/OPinout ListingsLBCLAIM N4Low InputMCP J11Low OutputT A N1Low I/OTBST L4Low I/OTEA J1Low OutputTS R1Low I/O TSIZ[0–2]G3, G4, F3High I/OTT[0–4]G1, H1, K1, L1, M1High I/OWT M4Low I/OXA TS(SDMA1)P1Low InputL2 Cache Interface SignalsADS/DALE/BRL2R3Low I/O BA0(BR3)T5Low Output BA1/BAA/BGL2P4Low Output DBGL2/DOE U5Low Output DCS(BG3)T1Low OutputDIRTY_IN(BR1)T3Low InputDIRTY_OUT(BG1)R4Low OutputDWE0(DBG2)P3Low OutputDWE1(DBG3)H11Low OutputDWE2(CKO)L11Low Output HIT T4Low InputTOE(DBG1)U4Low OutputTV(BR2)T6High I/OTWE(BG2)R5Low Output Memory Interface SignalsBCTL[0–1]F16, F15Low OutputBERR (ISA_MASTER)B3Low Input Table 10. Pinout Listing (Continued)Signal Name Pin Number Active I/OPinout ListingsCAS/DQM[0–7]J15, H15, G16, E16, G14, G13, F14, E14Low Output CKE/DBGLBJ10High Output FOED13Low Output MA0/SDBA1/SDMA0/AR0N15High Output SDMA1(XA TS)P1High Output MA1/SDBA0/AR9U16High Output MA[2–12]/SDMA[2–12]/AR [10–20]T16, R16, P15, P16, N16, M15, M16, L15, K15, K16, J16High Output MDLE/SDCAS E13Low Output P AR[0–7]/AR[1–8]D16, D15, C16, C15, B16, C14, A16, B15High I/O PPEN J14Low Output RAS/CS[0–7]M14, L13, K13, K14, K12, L10, J12, K11Low Output RCS0R15Low I/O RCS1J13Low Output RTC G15High Input SDRAS (PIRQ)H10Low Output WET15LowOutputPCI Interface Signals1AD[31–0]A4, C13, B5, D12, A5, C12, B6, D11, C11, B7, D10, A7, C10, B8, D9, A8, B10, D8, A11, C7, B11, D7, A12, C6, B12, C5, A13, D5, A14, C4, B14, D4High I/OC/BE[3–0]A6, C9, C8, D6Low I/O DEVSEL F8Low I/O FLSHREQ A3Low Input FRAME A10Low I/O GNT A15Low Input IRDY E8Low I/O ISA_MASTER (BERR)B3Low Input LOCK G8Low Input MEMACK A2Low Output P AR G9High I/O PERR F9Low I/O PIRQ (SDRAS)H10Low Output REQB4LowOutputTable 10. Pinout Listing (Continued)Signal Name Pin NumberActive I/OPinout ListingsSERR E9Low I/O STOP A9Low I/O TRDYB9LowI/OInterrupt, Clock, and Power Management SignalsCKO (DWE2)L11High Output HRST L16Low Input NMI E15High Input QACK L14Low Output QREQ H16Low Input SYSCLK L6Clock Input SUSPENDH14LowInputTest/Configuration SignalsPLL[0–3]U11, T11, U12, T12High Input TCK F13Clock Input TDI B13High Input TDO E12High Output TMS D14High Input TRSTH13LowInputPower and Ground SignalsAVdd K9High Clock Power LSSD_MODE 2G11Low Input Vdd E10, E6, F11, F5, F7, G10, G12, G6, H5, H7, K10, K7, L12, M11, M5, M7, N10, N12, N6, P11, P5, P7, R10, R6, J8, L8High Power Vss E11, E7, F10, F12, F6, G5, G7, H12, H6, J7, L7, M10, M12, M6, N11, N5, N7, P10, P12, P6, R11, R7, K8, J9, L9Low Ground NCH8, H9, M8, M9——Note:1All PCI signals are in little-endian bit order.2This test signal is for factory use only. It must be pulled up to Vdd for normal device operation.Table 10. Pinout Listing (Continued)Signal NamePin NumberActive I/O。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

物料编号:CC1210KKX5RGBB106的详细参数_易容网

MLCC即是多层陶瓷电容片式,是电子信息产品不可或缺的基本组件之一。

我国MLCC的生产起步在80年代初,行业早期主要是在外资企业的带动下发展起来的,近年来国内企业在技术上实现突破,行业国产化成效显著,并推动了MLCC产量迅速增长。

目前,MLCC的应用领域已从手机、电脑、电视机等消费电子领域,逐步拓展到新能源发电、新能源汽车、节能灯具、轨道交通、直流输变电、三网融合、高清电视、机顶盒、手机电视等多个行业。

对于这个悄悄活跃在人们生活中的元件你又知道多少呢.

本次易容网为大家推荐比较常用的MLCC国巨 | Yageo品牌的料号CC1210KKX5RGBB106的相关参数

易容网是深圳市易容信息技术有限公司独自研发的全球最大的MLCC搜索采购服务网站,2014年创立于深圳市南山区,全国首家电子元器件行业电容元件的搜索引擎及o2o商务服务平台。

易容网()现已建成全球最大的MLCC电容搜索引擎数据库,包含全球25家电容生产厂商超过28万组MLCC产品数据,用户可根据行业应用、物料编号、规格参数等信息快速的找到所有相关的MLCC电容数据。

易容网在搜索服务的前提下还提供村田、TDK、国巨、太阳诱电、风华高科等常见品牌产品的o2o商务服务,让企业客户实现询价、报价、在线订单、出库、实时物流、签收、账期服务等在线一站式商务服务体验。