FPGA可编程逻辑器件芯片EP2S15F672C6N中文规格书

FPGA可编程逻辑器件芯片EP2S60F672I5N中文规格书

Stratix II GX Device Handbook, Volume 1Operating ConditionsTable 4–20 provides information on recommended input clock jitter foreach mode.Notes to Table 4–19:(1)Dedicated REFCLK pins were used to drive the input reference clocks.(2)Jitter numbers specified are valid for the stated conditions only.(3)Refer to the protocol characterization documents for detailed information.(4)HiGig configuration is available in a -3 speed grade only. For more information, refer to the Stratix II GX Transceiver Architecture Overview chapter in volume 2 of the Stratix II GX Device Handbook .(5)Stratix II GX transceivers meet CEI jitter generation specification of 0.3 UI for a V OD range of 400mV to 1000 mV . (6)The Sinusoidal Jitter Tolerance Mask is defined only for low voltage (LV) variant of CPRI.(7)The jitter numbers for SONET/SDH are compliant to the GR-253-CORE Issue 3 Specification.(8)The jitter numbers for Fibre Channel are compliant to the FC-PI-4 Specification revision 6.10.(9)The jitter numbers for XAUI are compliant to the IEEE802.3ae-2002 Specification.(10)The jitter numbers for PCI Express are compliant to the PCIe Base Specification 2.0.(11)The jitter numbers for Serial RapidIO are compliant to the RapidIO Specification 1.3.(12)The jitter numbers for GIGE are compliant to the IEEE802.3-2002 Specification.(13)The jitter numbers for HiGig are compliant to the IEEE802.3ae-2002 Specification.(14)The jitter numbers for (OIF) CEI are compliant to the OIF-CEI-02.0 Specification.(15)The jitter numbers for CPRI are compliant to the CPRI Specification V2.1.(16)The HD-SDI and 3G-SDI jitter numbers are compliant to the SMPTE292M and SMPTE424M Specifications.(17)The Fibre Channel transmitter jitter generation numbers are compliant to the specification at βT interoperability point.(18)The Fibre Channel receiver jitter tolerance numbers are compliant to the specification at βR interoperability point.Table 4–19.Stratix II GX Transceiver Block AC Specification Notes (1), (2), (3)(Part 19 of 19)Symbol/Description Conditions -3 SpeedCommercial SpeedGrade-4 Speed Commercial and Industrial Speed Grade -5 Speed Commercial Speed Grade Unit MinTyp MaxMin Typ Max Min Typ Max Table 4–20.Recommended Input Clock Jitter (Part 1 of 2)ModeReference Clock (MHz)Vectron LVPECL XO Type/Model Frequency Range (MHz)RMS Jitter (12 kHz to 20 MHz) (ps)Period Jitter (Peak to Peak) (ps)Phase Noise at 1 MHz (dB c/Hz)PCI-E100VCC6-Q/R 10 to 2700.323-149.9957(OIF) CEIPHY156.25VCC6-Q/R 10 to 2700.323-146.2169622.08VCC6-Q 270 to 800230Not available GIGE62.5VCC6-Q/R 10 to 2700.323-149.9957125VCC6-Q/R 10 to 2700.323-146.9957XAUI 156.25VCC6-Q/R 10 to 2700.323-146.2169Stratix II GX Device Handbook, Volume 1DC and Switching CharacteristicsI/O Standard SpecificationsTables 4–24 through 4–47 show the Stratix II GX device family I/Ostandard specifications.R CONF(4)Value of I/O pin pull-up resistor before and during configuration Vi = 0, V CCIO = 3.3V 102550KOhmVi = 0, V CCIO = 2.5V 153570KOhmVi = 0, V CCIO = 1.8V 3050100KOhmVi = 0, V CCIO = 1.5V 4075150KOhmVi = 0, V CCIO = 1.2V 5090170KOhmRecommended value ofI/O pin externalpull-down resistor before and duringconfiguration12KOhm Notes to Table 4–23:(1)Typical values are for T A = 25 °C, V CCINT = 1.2 V , and V CCIO = 1.5 V , 1.8 V , 2.5 V , and 3.3 V .(2)This value is specified for normal device operation. The value may vary during power-up. This applies for all V CCIO settings (3.3, 2.5, 1.8, and 1.5 V).(3)Maximum values depend on the actual TJ and design utilization. See PowerPlay Early Power Estimator (EPE) and Power Analyzer or the Quartus II PowerPlay Power Analyzer and Optimization Technology (available at ) for maximum values. See the section “Power Consumption” on page 4–59 for more information.(4)Pin pull-up resistance values will lower if an external source drives the pin higher than V CCIO .Table 4–23.Stratix II GX Device DC Operating Conditions (Part 2 of 2)Note (1)SymbolParameter Conditions Device Minimum Typical Maximum Unit Table 4–24.LVTTL Specifications (Part 1 of 2)SymbolParameter Conditions Minimum Maximum Unit V CCIO (1)Output supply voltage 3.135 3.465V V IHHigh-level input voltage 1.7 4.0V V ILLow-level input voltage –0.30.8V V OH High-level output voltage I OH = –4mA (2) 2.4VOperating ConditionsTable4–35.SSTL-18 Class I SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit V CCIO Output supply voltage 1.71 1.8 1.89V V REF Reference voltage0.8550.90.945V V TT Termination voltage V REF – 0.04V REF V REF + 0.04V V IH (DC)High-level DC input voltage V REF + 0.125V V IL (DC)Low-level DC input voltage V REF – 0.125V V IH (AC)High-level AC input voltage V REF + 0.25V V IL (AC)Low-level AC input voltage V REF – 0.25V V OH High-level output voltage I OH = –6.7mA (1)V TT + 0.475V V OL Low-level output voltage I OL = 6.7mA (1)V TT – 0.475V Note to Table4–35:(1)This specification is supported across all the programmable drive settings available for this I/O standard as shownin the Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook.Table4–36.SSTL-18 Class II SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit V CCIO Output supply voltage 1.71 1.8 1.89V V REF Reference voltage0.8550.90.945V V TT Termination voltage V REF – 0.04V REF V REF + 0.04V V IH (DC)High-level DC input voltage V REF + 0.125V V IL (DC)Low-level DC input voltage V REF – 0.125V V IH (AC)High-level AC input voltage V REF + 0.25V V IL (AC)Low-level AC input voltage V REF – 0.25V V OH High-level output voltage I OH = –13.4mA (1)V CCIO – 0.28V V OL Low-level output voltage I OL = 13.4mA (1)0.28V Note to Table4–36:(1)This specification is supported across all the programmable drive settings available for this I/O standard as shownin the Stratix II GX Architecture chapter in volume 1 of the Stratix II GX Device Handbook.Stratix II GX Device Handbook, Volume 1Document Revision HistoryStratix II GX Device Handbook, Volume 1。

FPGA可编程逻辑器件芯片EP1S25F672C8N中文规格书

1.000 1.750 1.782 1.988 1.882 1.891 1.793 2.009 1.897 1.948 ns

-0.677

-0.714 -1.296 -1.312 -1.465 -1.390 -1.380 -1.312 -1.475 -1.395 -1.433 ns

-1.155

-1.244 -1.839 -1.835 -1.972 -1.905 -2.351 -1.844 -1.981 -1.925 -2.394 ns

1.009 1.765 1.794 2.086 1.972 1.796 1.779 2.110 1.988 1.846 ns

-0.658

-0.723 -1.311 -1.326 -1.562 -1.478 -1.295 -1.301 -1.574 -1.482 -1.338 ns

-1.141

-1.232 -1.824 -1.825 -1.954 -1.887 -2.333 -1.833 -1.964 -1.908 -2.377 ns

VCCL= 0.9V

VCCL= 1.1V

VCCL= 1.1V

VCCL= 1.1V

VCCL= Units 0.9V

-1.241

-1.332 -1.956 -1.963 -2.136 -2.070 -2.514 -1.972 -2.143 -2.088 -2.556 ns

1.367

1.471 2.169 2.184 2.379 2.301 2.749 2.203 2.396 2.328 2.794 ns

-0.632

-0.688 -1.273 -1.297 -1.557 -1.473 -1.287 -1.267 -1.567 -1.475 -1.327 ns

FPGA可编程逻辑器件芯片EP2S15F672C6中文规格书

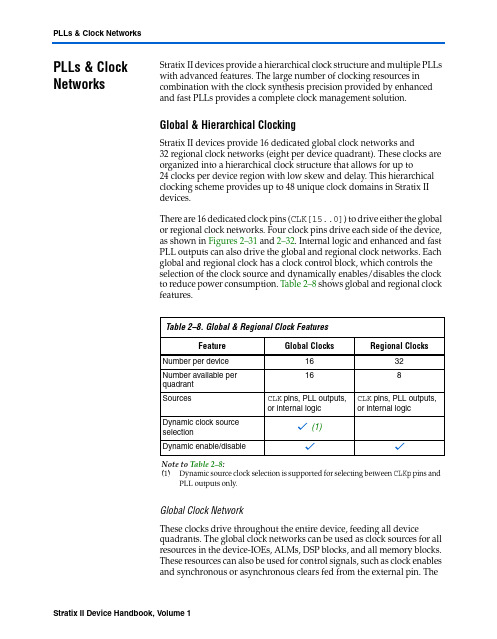

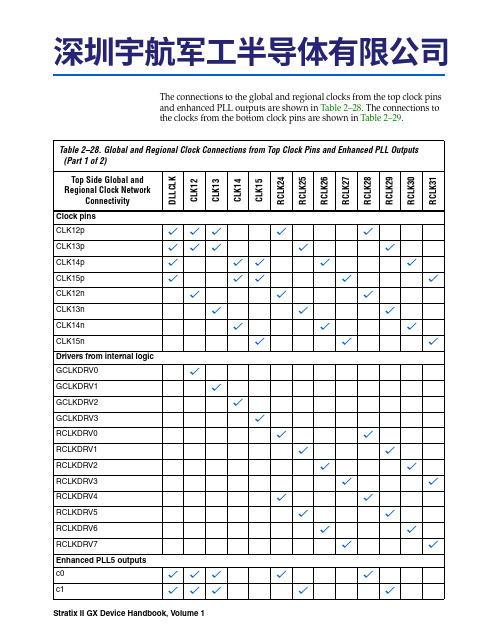

PLLs & Clock NetworksPLLs & Clock Networks Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution. Global & Hierarchical ClockingStratix II devices provide 16 dedicated global clock networks and32regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to24clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.There are 16 dedicated clock pins (CLK[15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table2–8 shows global and regional clock features.Global Clock NetworkThese clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The Table2–8.Global & Regional Clock FeaturesFeature Global Clocks Regional Clocks Number per device1632Number available perquadrant168Sources CLK pins, PLL outputs,or internal logicCLK pins, PLL outputs,or internal logic Dynamic clock sourceselectionv (1)Dynamic enable/disable v vNote to Table2–8:(1)Dynamic source clock selection is supported for selecting between CLKp pins andPLL outputs only.Figure2–55.Output TIming Diagram in DDR ModeThe Stratix II IOE operates in bidirectional DDR mode by combining theDDR input and DDR output configurations. The negative-edge-clockedOE register holds the OE signal inactive until the falling edge of the clock.This is done to meet DDR SDRAM timing requirements.External RAM InterfacingIn addition to the six I/O registers in each IOE, Stratix II devices also havededicated phase-shift circuitry for interfacing with external memoryinterfaces. Stratix II devices support DDR and DDR2 SDRAM, QDR IISRAM, RLDRAM II, and SDR SDRAM memory interfaces. In everyStratix II device, the I/O banks at the top (banks 3 and 4) and bottom(banks 7 and 8) of the device support DQ and DQS signals with DQ busmodes of ×4, ×8/×9, ×16/×18, or ×32/×36. Table2–14 shows the numberof DQ and DQS buses that are supported per device.Table2–14.DQS & DQ Bus Mode Support(Part 1 of2)Note(1)Device Package Number of×4GroupsNumber of×8/×9 GroupsNumber of×16/×18 GroupsNumber of×32/×36 GroupsEP2S15484-pin FineLine BGA8400 672-pin FineLine BGA18840 EP2S30484-pin FineLine BGA8400 672-pin FineLine BGA18840 EP2S60484-pin FineLine BGA8400 672-pin FineLine BGA188401,020-pin FineLine BGA361884I/O StructureA compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of theircorresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK[15..12]p feed the phase circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.EP2S90484-pin Hybrid FineLine BGA 8400780-pin FineLine BGA 188401,020-pin FineLine BGA 3618841,508-pin FineLine BGA361884EP2S130780-pin FineLine BGA188401,020-pin FineLine BGA 3618841,508-pin FineLine BGA361884EP2S1801,020-pin FineLine BGA3618841,508-pin FineLine BGA361884Notes to Table 2–14:(1)Check the pin table for each DQS/DQ group in the different modes.Table 2–14.DQS & DQ Bus Mode Support (Part 2 of 2)Note (1)DevicePackageNumber of ×4GroupsNumber of ×8/×9 GroupsNumber of ×16/×18 Groups Number of ×32/×36 Groups。

FPGA可编程逻辑器件芯片EP1S25F672C6中文规格书

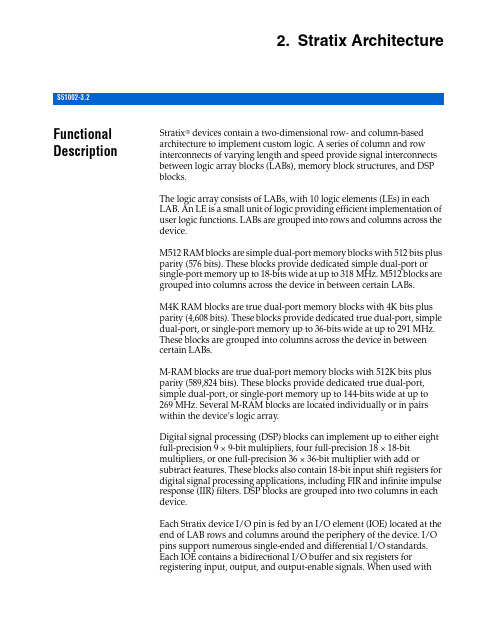

2.Stratix ArchitectureFunctional Description Stratix® devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.The logic array consists of LABs, with 10 logic elements (LEs) in each LAB. An LE is a small unit of logic providing efficient implementation of user logic functions. LABs are grouped into rows and columns across the device.M512 RAM blocks are simple dual-port memory blocks with 512 bits plus parity (576 bits). These blocks provide dedicated simple dual-port or single-port memory up to 18-bits wide at up to 318MHz. M512 blocks are grouped into columns across the device in between certain LABs.M4K RAM blocks are true dual-port memory blocks with 4K bits plus parity (4,608 bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 36-bits wide at up to 291MHz. These blocks are grouped into columns across the device in between certain LABs.M-RAM blocks are true dual-port memory blocks with 512K bits plus parity (589,824bits). These blocks provide dedicated true dual-port, simple dual-port, or single-port memory up to 144-bits wide at up to 269MHz. Several M-RAM blocks are located individually or in pairs within the device’s logic array.Digital signal processing (DSP) blocks can implement up to either eight full-precision 9×9-bit multipliers, four full-precision 18 × 18-bit multipliers, or one full-precision 36×36-bit multiplier with add or subtract features. These blocks also contain 18-bit input shift registers for digital signal processing applications, including FIR and infinite impulse response (IIR) filters. DSP blocks are grouped into two columns in each device.Each Stratix device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used withStratix Device Handbook, Volume 1Stratix ArchitectureFigure 2–7.LE in Dynamic Arithmetic ModeStratix Device Handbook, Volume 1MultiTrack InterconnectTable 2–2 shows the Stratix device’s routing scheme.Table 2–2.Stratix Device Routing SchemeSourceDestinationL U T C h a i nR e g i s t e r C h a i nL o c a l I n t e r c o n n e c tD i r e c t L i n k I n t e r c o n n e c tR 4 I n t e r c o n n e c tR 8 I n t e r c o n n e c tR 24 I n t e r c o n n e c tC 4 I n t e r c o n n e c tC 8 I n t e r c o n n e c tC 16 I n t e r c o n n e c tL EM 512 R A M B l o c kM 4K R A M B l o c kM -R A M B l o c kD S P B l o c k sC o l u m n I O E R o w I O ELUT Chain v Register Chain v LocalInterconnect vvvvvvvDirect Link Interconnect v R4 Interconnect v vvvvR8 Interconnect vvvR24Interconnect vvv v C4 Interconnect v vvC8 Interconnect vvvC16Interconnect vvv vLEvvv v v v v v M512 RAM Blockv v v v v v M4K RAM Block v v v v v v M-RAM Block v v DSP Blocks vv vv v v Column IOE v v v v Row IOEvvvvvvStratix Device Handbook, Volume 1Stratix ArchitectureTriMatrix MemoryTriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity,including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.Table 2–3.TriMatrix Memory Features (Part 1 of 2)Memory FeatureM512 RAM Block (32×18Bits)M4K RAM Block (128×36Bits)M-RAM Block (4K ×144Bits)Maximum performance (1)(1)(1)T rue dual-port memory vv Simple dual-port memoryv v v Single-port memoryvvvStratix Device Handbook, Volume 1TriMatrix MemoryConfigurations512×1256×2128×464×864×932×1632×184K ×12K ×21K ×4512×8512×9256×16256×18128×32128×3664K ×864K ×932K ×1632K ×1816K ×3216K ×368K ×648K ×724K ×1284K ×144Table 2–3.TriMatrix Memory Features (Part 2 of 2)Memory FeatureM512 RAM Block (32×18Bits)M4K RAM Block (128×36Bits)M-RAM Block (4K ×144Bits)。

FPGA可编程逻辑器件芯片EP2S35F672C8ES中文规格书

GP Timer Programming ConceptsFigure 21-9: EXTCLK Mode Control FlowThe waveform applied to the input pin is not required to have a 50% duty cycle. The minimum input pulse low time, high time, and total period specifications are available in the product data sheet. Program the period to any value from 1 to (232 – 1), inclusive.After the timer has started, it resets the TIMER_TMR[n]_CNT register to 0x0 and then waits for the first leading edge on the input pin. This edge causes TIMER_TMR[n]_CNT to be incremented to the value 0x1, and every subse-quent leading edge increments it by one. After the TIMER_TMR[n]_CNT register reaches the value programmed in the TIMER_TMR[n]_PER register, the corresponding TIMER_DATA_ILAT bit is set, and an interrupt and trigger are both generated (if enabled). The next leading-edge reloads the TIMER_TMR[n]_CNT register with 0x1, and the timer continues counting until it is disabled.GP Timer Programming ConceptsUsing the features, operating modes, and event control for the GP timer to their greatest potential requires an un-derstanding of some GP timer-related concepts.Setting Up Constantly Changing Timer ConditionsThis task shows how to use different period, pulse width, and delay settings for each of the first three timer periods after the timer starts.1.Program the first set of TIMER_TMR[n]_PER, TIMER_TMR[n]_WID, and TIMER_TMR[n]_DLY register val-ues.2.Enable the timer using the TIMER_RUN register.3.Immediately program the second set of TIMER_TMR[n]_PER, TIMER_TMR[n]_WID, andTIMER_TMR[n]_DLY register values, as needed.4.Wait for the first timer interrupt.5.Program the third set of TIMER_TMR[n]_PER, TIMER_TMR[n]_WID, and TIMER_TMR[n]_DLY register val-ues.measurement report. A measurement report occurs, at most, once per input signal period. The currentTIMER_TMR[n]_CNT value is always copied to the width buffer and period buffer registers at the trailing and lead-ing edges of the input signal, respectively. But, these values are not visible to software. A measurement report event samples the captured values into visible registers and sets the timer interrupt to signal that the TIMER_TMR[n]_PER and the TIMER_TMR[n]_WID registers are ready to be read.When the TIMER_TMR[n]_CFG.TMODE bit =b#1011, the measurement report occurs just after the width buffer register captures its value at a falling edge. Then, the TIMER_TMR[n]_WID register reports the pulse width meas-ured in the pulse that has ended, but the TIMER_TMR[n]_PER register reports the pulse period measured at the end of the previous period. If only the first trailing edge has occurred, then the first period value has not yet been meas-ured at the first measurement report. So, the period value is not valid. A read of the TIMER_TMR[n]_PER value in this case returns 0. See the Example of Width Capture Deasserted Mode (TMODE=b#1011) figure for more infor-mation.SCLK 1TMRx, PULSE_HI =TMRx, PULSE_HI =12356834347121X 843TIMENx212043812X 0X 0X 0X 0COUNTING REPORT REPORT REPORTNOTE: FOR SIMPLICITY, THE SYNCHRONIZATION DELAY BETWEEN TMRx EDGES AND BUFFERREGISTER UPDATES IS NOT SHOWN.TIMER_TMRn_CNT TIMER_TMRn_PER BUFFER TIMER_TMRn_WID BUFFER TIMER_TMRn_PER TIMER_TMRn_WID TIMER_STAT_ILATTIMER_ERR_TYPEFigure 21-3: Example of Width Capture Deasserted Mode (TMODE=b#1011)NOTE :SCLK in the Example of Width Capture Deasserted Mode (TMODE=b#1011) figure is SCLK0.When the TIMER_TMR[n]_CFG.TMODE bit =b#1010, the measurement report occurs just after the period buffer register captures its value at a leading edge. Then, the TIMER_TMR[n]_PER and TIMER_TMR[n]_WID registers re-port the pulse period and pulse width measured in the period that has ended. Refer to the Example of Width Cap-ture Asserted Mode (TMODE=b#1010) figure for more information.GP Timer Operating ModesAfter enabling the timer in this mode, it always starts counting at the asserting edge of the input signal. Any pulse that is already active when the timer is enabled is ignored.With the TIMER_TMR[n]_CFG.IRQMODE bit =b#11, the timer generates an interrupt if the timed pulse width ex-ceeds p MAX , or if the pulse width is less than p MIN . After attaining p MAX , the pulse stays at an active level, and the counter keeps on counting until it sees a de-asserting edge. When the input pulse is not active, the counter holds its current value until it again sees an asserting edge, or it restarts. An interrupt can also be generated for when the pulse occurs within the specified window condition, by setting TIMER_TMR[n]_CFG.IRQMODE =b#10.In this mode, a trailing edge on the input pin triggers capturing of pulse width into the TIMER_TMR[n]_WID regis-ter. During the inactive portion of the input signal, the internal counter does not increment. The Watchdog Width Mode Timing figure shows the signal flow in this mode.TIMER_RUNTMR INTMR_CNTSCLKPmin/TMR_DL Y = 2Pmax/TMR_PER = 5TMR_WID Figure 21-7: Watchdog Width Mode TimingNOTE :SCLK in the Watchdog Width Mode Timing figure is SCLK0.To check only the upper limit on pulse width (p MAX but not p MIN ), then program p MIN as 0 or 1. In such a case, it is better to use TIMER_TMR[n]_CFG.IRQMODE =b#11. With TIMER_TMR[n]_CFG.IRQMODE = b#10, a pulse width of 1 clock cycle results in an interrupt. For details, see the Windowed Watchdog Width Mode Interpretation table.Windowed Watchdog (WATCHDOG) Modes。

FPGA可编程逻辑器件芯片EP2S30F672C5中文规格书

Table 6–5 shows the summary of input register modes for the DSP block.Multiplier StageThe multiplier stage supports 9 × 9, 18 × 18, or 36 × 36 multipliers as well as other smaller multipliers in between these configurations. See“Operational Modes” on page 6–21 for details. Depending on the data width of the multiplier, a single DSP block can perform many multiplications in parallel.Each multiplier operand can be a unique signed or unsigned number. Two signals, signa and signb , control the representation of eachoperand respectively. A logic 1 value on the signa signal indicates that data A is a signed number while a logic 0 value indicates an unsigned number. Table 6–6 shows the sign of the multiplication result for the various operand sign representations. The result of the multiplication is signed if any one of the operands is a signed value.There is only one signa and one signb signal for each DSP block.Therefore, all of the data A inputs feeding the same DSP block must have the same sign representation. Similarly, all of the data B inputs feeding the same DSP block must have the same sign representation. The multiplier offers full precision regardless of the sign representation.1When the signa and signb signals are unused, the Quartus ® IIsoftware sets the multiplier to perform unsigned multiplication by default.Table 6–5.Input Register ModesRegister InputMode9 × 918 × 1836 × 36Parallel inputv v vShift register input v v Table 6–6.Multiplier Sign RepresentationData A (signa Value)Data B (signb Value)Result Unsigned (logic 0)Unsigned (logic 0)Unsigned Unsigned (logic 0)Signed (logic 1)Signed Signed (logic 1)Unsigned (logic 0)Signed Signed (logic 1)Signed (logic 1)SignedAccumulatorWhen the adder/subtractor/accumulator is configured as an accumulator, the output of the adder/output block feeds back to the accumulator as shown in Figure6–7. The accumulator can be set up to perform addition only, subtraction only or the addnsub signal can be used to dynamically control the accumulation direction. A logic 1 value on the addnsub signal indicates that the accumulator is performing addition while a logic 0 value indicates subtraction.Each accumulator can be cleared by either clearing the DSP block output register or by using the accum_sload signal. The accumulator clear using the accum_sload signal is independent from the resetting of the output registers so the accumulation can be cleared and a new one can begin without losing any clock cycles. The accum_sload signal controls a feedback multiplexer that specifies that the output of the multiplier should be summed with a zero instead of the accumulator feedback path. The accumulator can also be initialized/preloaded with a non-zero value using the accum_sload signal and the accum_sload_upper_data bus with one clock cycle latency. Preloading the accumulator is done by adding the result of the multiplier with the value specified on the accum_sload_upper_data bus. As in the case of the accumulator clearing, the accum_sload signal specifies to the feedback multiplexer that the accum_sload_upper_data signal should feed the accumulator instead of the accumulator feedback signal. Theaccum_sload_upper_data signal only loads the upper 36-bits of the accumulator. To load the entire accumulator, the value for the lower16-bits must be sent through the multiplier feeding that accumulator with the multiplier set to perform a multiplication by one.The overflow signal will go high on the positive edge of the clock when the accumulator detects an overflow or underflow. The overflow signal will stay high for only one clock cycle after an overflow or underflow is detected even if the overflow or underflow condition is still present. A latch external to the DSP block has to be used to preserve the overflow signal indefinitely or until the latch is cleared.The DSP blocks support Q1.15 input format saturation and rounding in each accumulator. The following signals are available that can control if saturation or rounding or both is performed to the output of the accumulator:■accum_round■accum_saturation■accum_is_saturated outputDSP Blocks in Stratix II and Stratix II GX Devices Each DSP block has two sets of accum_round and accum_saturation signals which control if rounding or saturation is performed on the accumulator output respectively (one set of signals for each accumulator). Rounding and saturation of the accumulator output is only available when implementing an 16 × 16 multiplier-accumulator to conform to the bit widths required for Q1.15 input format computation.A logic 1 value on the accum_round and accum_saturation signal indicates that rounding or saturation is performed while a logic 0 indicates that no rounding or saturation is performed. A logic 1 value on the accum_is_saturated output signal tells you that saturation has occurred to the result of the accumulator.Figure6–10 shows the DSP block configured to perform multiplier-accumulator operations.Adder/SubtractorThe addnsub1 or addnsub3 signals specify whether you are performing addition or subtraction. A logic 1 value on the addnsub1 or addnsub3 signals indicates that the adder/subtractor is performing addition while a logic 0 value indicates subtraction. These signals can be dynamically controlled using logic external to the DSP block. If the first stage is configured as a subtractor, the output is A – B and C – D.The adder/subtractor block share the same signa and signb signals as the multiplier block. The signa and signb signals can be pipelined with a latency of one or two clock cycles or not.The DSP blocks support Q1.15 input format rounding (not saturation) after each adder/subtractor. The addnsub1_round andaddnsub3_round signals determine if rounding is performed to the output of the adder/subtractor.The addnsub1_round signal controls the rounding of the topadder/subtractor and the addnsub3_round signal controls the rounding of the bottom adder/subtractor. Rounding of the adder output is only available when implementing an 16 × 16 multiplier-adder to conform to the bit widths required for Q1.15 input format computation.A logic 1 value on the addnsub_round signal indicates that rounding is performed while a logic 0 indicates that no rounding is performed. Summation BlockThe output of the adder/subtractor block feeds an optional summation block, which is an adder block that sums the outputs of bothadder/subtractor blocks. The summation block is used when more than two multiplier results are summed. This is useful in applications such as FIR filtering.。

FPGA可编程逻辑器件芯片EP1S25F1020C6N中文规格书

Fast PLLs

Stratix II GX devices contain up to four fast PLLs with high-speed serial interfacing ability. The fast PLLs offer high-speed outputs to manage the high-speed differential I/O interfaces. Figure 2–75 shows a diagram of the fast PLL.

regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL. (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the serializer/deserializer (SERDES) circuitry. Stratix II GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode. (3) This signal is a differential I/O SERDES control signal. (4) Stratix II GX fast PLLs only support manual clock switchover.

FPGA可编程逻辑器件芯片EP2S15F672I3N中文规格书

Symbol

Parameter

Conditions

Minimum Maximum Unit

VOL

Low-level output voltage

IOL = 4 mA (2)

0.45

V

Notes to Tables 5–5: (1) Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard,

Figure 2–58. Stratix II Transmitter Channel

Data from R4, R24, C4, or direct link interconnect

10

10

+

Up to 1 Gbps

–

refclk

Local Interconnect

diffioclk

Fast PLL

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the Stratix II Architecture chapter in volume 1 of the Stratix II Device Handbook.

JESD8-B. (2) This specification is supported across all the programmable drive strength available for this I/O standard as

FPGA可编程逻辑器件芯片EP1S10F672C6N中文规格书

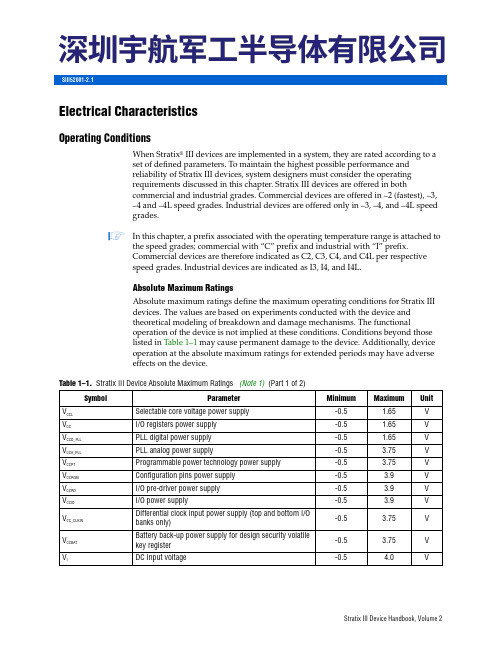

Stratix III Device Handbook, Volume 2Electrical CharacteristicsOperating ConditionsWhen Stratix ®III devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Stratix III devices, system designers must consider the operating requirements discussed in this chapter. Stratix III devices are offered in bothcommercial and industrial grades. Commercial devices are offered in –2 (fastest), –3, –4 and –4L speed grades. Industrial devices are offered only in –3, –4, and –4L speed grades.1In this chapter, a prefix associated with the operating temperature range is attached to the speed grades; commercial with “C” prefix and industrial with “I” prefix.Commercial devices are therefore indicated as C2, C3, C4, and C4L per respective speed grades. Industrial devices are indicated as I3, I4, and I4L.Absolute Maximum RatingsAbsolute maximum ratings define the maximum operating conditions for Stratix III devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functionaloperation of the device is not implied at these conditions. Conditions beyond those listed in Table 1–1 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods may have adverse effects on the device.Table 1–1.Stratix III Device Absolute Maximum Ratings (Note 1)(Part 1 of 2)Symbol ParameterMinimum Maximum Unit V CCL Selectable core voltage power supply -0.5 1.65V V CC I/O registers power supply -0.5 1.65V V CCD_PLL PLL digital power supply -0.5 1.65V V CCA_PLL PLL analog power supply-0.5 3.75V V CCPT Programmable power technology power supply -0.5 3.75V V CCPGM Configuration pins power supply -0.5 3.9V V CCPD I/O pre-driver power supply -0.5 3.9V V CCIO I/O power supply-0.5 3.9V V CC_CLKIN Differential clock input power supply (top and bottom I/O banks only)-0.5 3.75V V CCBAT Battery back-up power supply for design security volatile key register -0.5 3.75V V IDC Input voltage-0.54.0VSIII52001-2.1Chapter 1:Stratix III Device Data Sheet: DC and Switching Characteristics I/O TimingStratix III Device Handbook, Volume 2DIFFERENTIAL 1.5-V HSTL CLASS I4mAGCLKt co 3.070 3.293 4.650 5.057 5.572 5.431 5.660 5.184 5.700 5.560 5.727ns GCLK PLL t co 1.356 1.540 1.957 2.048 2.254 2.266 2.202 2.162 2.369 2.384 2.189ns 6mAGCLKt co 3.065 3.289 4.650 5.057 5.573 5.432 5.661 5.185 5.702 5.562 5.729ns GCLK PLL t co 1.351 1.536 1.957 2.048 2.255 2.267 2.203 2.163 2.371 2.386 2.191ns 8mAGCLKt co 3.063 3.287 4.649 5.056 5.571 5.430 5.659 5.184 5.701 5.561 5.728ns GCLK PLL t co 1.349 1.534 1.956 2.047 2.253 2.265 2.201 2.162 2.370 2.385 2.190ns 10m A GCLK t co 3.055 3.278 4.639 5.046 5.562 5.421 5.650 5.174 5.691 5.551 5.718ns GCLK PLL t co 1.341 1.525 1.946 2.037 2.244 2.256 2.192 2.152 2.360 2.375 2.180ns 12m AGCLK t co 3.056 3.280 4.645 5.053 5.570 5.429 5.658 5.182 5.700 5.560 5.727ns GCLK PLL t co 1.342 1.527 1.952 2.044 2.252 2.264 2.200 2.160 2.369 2.384 2.189ns DIFFERENTIAL 1.5-V HSTL CLASS II16m AGCLK t co 3.055 3.277 4.628 5.034 5.548 5.407 5.636 5.161 5.676 5.536 5.703ns GCLK PLL t co 1.341 1.524 1.935 2.025 2.230 2.242 2.178 2.139 2.345 2.360 2.165ns DIFFERENTIAL 1.8-V HSTL CLASS I4mAGCLKt co 3.067 3.290 4.646 5.052 5.566 5.425 5.654 5.180 5.695 5.555 5.722ns GCLK PLL t co 1.353 1.537 1.953 2.043 2.248 2.260 2.196 2.158 2.364 2.379 2.184ns 6mAGCLKt co 3.063 3.287 4.647 5.054 5.570 5.429 5.658 5.182 5.699 5.559 5.726ns GCLK PLL t co 1.349 1.534 1.954 2.045 2.252 2.264 2.200 2.160 2.368 2.383 2.188ns 8mAGCLKt co 3.053 3.276 4.636 5.043 5.558 5.417 5.646 5.171 5.687 5.547 5.714ns GCLK PLL t co 1.339 1.523 1.943 2.034 2.240 2.252 2.188 2.149 2.356 2.371 2.176ns 10m A GCLK t co 3.051 3.274 4.634 5.040 5.556 5.415 5.644 5.169 5.685 5.545 5.712ns GCLK PLL t co 1.337 1.521 1.941 2.031 2.238 2.250 2.186 2.147 2.354 2.369 2.174ns 12m AGCLK t co 3.051 3.275 4.637 5.045 5.561 5.420 5.649 5.173 5.691 5.551 5.718ns GCLK PLL t co 1.337 1.522 1.944 2.036 2.243 2.255 2.191 2.151 2.360 2.375 2.180ns DIFFERENTIAL 1.8-V HSTL CLASS II16m AGCLK t co 3.055 3.278 4.634 5.040 5.555 5.414 5.643 5.168 5.684 5.544 5.711ns GCLK PLLt co1.3411.5251.9412.031 2.237 2.249 2.185 2.146 2.353 2.368 2.173nsTable 1–109.EP3SE50 Column Pins Output Timing Parameters (Part 2 of 4)I/O StandardC u r r e n t S t r e n g t hClock P a r a m e t e rFast Model C2C3C4C4LI3I4I4L Units IndustrialCommercialV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VChapter 1:Stratix III Device Data Sheet: DC and Switching CharacteristicsI/O TimingStratix III Device Handbook, Volume 2DIFFERENTIAL 1.5-V SSTL CLASS I4mAGCLKt co 3.081 3.307 4.679 5.088 5.605 5.464 5.693 5.216 5.734 5.594 5.761ns GCLK PLL t co 1.367 1.554 1.986 2.079 2.287 2.299 2.235 2.194 2.403 2.418 2.223ns 6mAGCLKt co 3.067 3.293 4.667 5.077 5.595 5.454 5.683 5.206 5.725 5.585 5.752ns GCLK PLL t co 1.353 1.540 1.974 2.068 2.277 2.289 2.225 2.184 2.394 2.409 2.214ns 8mAGCLKt co 3.055 3.280 4.650 5.059 5.577 5.436 5.665 5.188 5.707 5.567 5.734ns GCLK PLL t co 1.341 1.527 1.957 2.050 2.259 2.271 2.207 2.166 2.376 2.391 2.196ns 10m A GCLK t co 3.055 3.280 4.653 5.063 5.581 5.440 5.669 5.192 5.712 5.572 5.739ns GCLK PLL t co 1.341 1.527 1.960 2.054 2.263 2.275 2.211 2.170 2.381 2.396 2.201ns 12m AGCLK t co 3.051 3.276 4.646 5.055 5.574 5.433 5.662 5.185 5.704 5.564 5.731ns GCLK PLL t co 1.337 1.523 1.953 2.046 2.256 2.268 2.204 2.163 2.373 2.388 2.193ns DIFFERENTIAL 1.5-V SSTL CLASS II8mAGCLK t co 3.055 3.278 4.639 5.046 5.562 5.421 5.650 5.174 5.691 5.551 5.718ns GCLK PLL t co 1.341 1.525 1.946 2.037 2.244 2.256 2.192 2.152 2.360 2.375 2.180ns 16m AGCLK t co 3.056 3.280 4.647 5.056 5.573 5.432 5.661 5.184 5.703 5.563 5.730ns GCLK PLL t co 1.342 1.527 1.954 2.047 2.255 2.267 2.203 2.162 2.372 2.387 2.192ns DIFFERENTIAL 1.8-V SSTL CLASS I4mAGCLKt co 3.084 3.310 4.678 5.086 5.603 5.462 5.691 5.215 5.732 5.592 5.759ns GCLK PLL t co 1.370 1.557 1.985 2.077 2.285 2.297 2.233 2.193 2.401 2.416 2.221ns 6mAGCLKt co 3.073 3.298 4.666 5.074 5.591 5.450 5.679 5.203 5.720 5.580 5.747ns GCLK PLL t co 1.359 1.545 1.973 2.065 2.273 2.285 2.221 2.181 2.389 2.404 2.209ns 8mAGCLKt co 3.068 3.294 4.666 5.075 5.592 5.451 5.680 5.204 5.722 5.582 5.749ns GCLK PLL t co 1.354 1.541 1.973 2.066 2.274 2.286 2.222 2.182 2.391 2.406 2.211ns 10m A GCLK t co 3.054 3.279 4.648 5.056 5.573 5.432 5.661 5.185 5.704 5.564 5.731ns GCLK PLL t co 1.340 1.526 1.955 2.047 2.255 2.267 2.203 2.163 2.373 2.388 2.193ns 12m AGCLK t co 3.052 3.277 4.646 5.054 5.571 5.430 5.659 5.183 5.701 5.561 5.728ns GCLK PLL t co 1.338 1.524 1.953 2.045 2.253 2.265 2.201 2.161 2.370 2.385 2.190ns DIFFERENTIAL 1.8-V SSTL CLASS II8mAGCLK t co 3.056 3.279 4.638 5.044 5.559 5.418 5.647 5.172 5.688 5.548 5.715ns GCLK PLL t co 1.342 1.526 1.945 2.035 2.241 2.253 2.189 2.150 2.357 2.372 2.177ns 16m AGCLK t co 3.056 3.280 4.646 5.054 5.571 5.430 5.659 5.183 5.701 5.561 5.728ns GCLK PLLt co1.3421.5271.9532.045 2.253 2.265 2.201 2.161 2.370 2.385 2.190nsTable 1–109.EP3SE50 Column Pins Output Timing Parameters (Part 3 of 4)I/O StandardC u r r e n t S t r e n g t hClock P a r a m e t e rFast Model C2C3C4C4LI3I4I4L Units IndustrialCommercialV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VChapter 1:Stratix III Device Data Sheet: DC and Switching Characteristics I/O TimingStratix III Device Handbook, Volume 2DIFFERENTIAL 1.8-VHSTL CLASS II16mAGCLKt co 3.051 3.283 4.668 5.081 5.604 5.462 5.665 5.216 5.743 5.598 5.735ns GCLKPLL t co1.373 1.5652.011 2.110 2.324 2.336 2.247 2.234 2.451 2.460 2.235ns DIFFERENTIAL 1.5-VSSTL CLASS I4mAGCLKt co3.100 3.3364.7395.154 5.680 5.538 5.741 5.290 5.819 5.674 5.811ns GCLKPLL t co1.422 1.6182.082 2.183 2.400 2.412 2.323 2.308 2.527 2.536 2.311ns 6mAGCLKt co3.076 3.3124.7215.137 5.663 5.521 5.724 5.273 5.804 5.659 5.796ns GCLKPLL t co1.398 1.5942.064 2.166 2.383 2.395 2.306 2.291 2.512 2.521 2.296ns 8mAGCLKt co3.058 3.2934.6995.115 5.641 5.499 5.702 5.251 5.782 5.637 5.774ns GCLKPLL t co1.380 1.5752.042 2.144 2.361 2.373 2.284 2.269 2.490 2.499 2.274ns DIFFERENTIAL 1.8-VSSTL CLASS I4mAGCLKt co3.104 3.3394.7395.154 5.679 5.537 5.740 5.290 5.819 5.674 5.811ns GCLKPLL t co1.426 1.6212.082 2.183 2.399 2.411 2.322 2.308 2.527 2.536 2.311ns 6mAGCLKt co3.089 3.3244.7255.139 5.664 5.522 5.725 5.275 5.804 5.659 5.796ns GCLKPLL t co1.411 1.6062.068 2.168 2.384 2.396 2.307 2.293 2.512 2.521 2.296ns 8mAGCLKt co3.078 3.3134.7205.136 5.661 5.519 5.722 5.272 5.802 5.657 5.794ns GCLKPLL t co1.400 1.5952.063 2.165 2.381 2.393 2.304 2.290 2.510 2.519 2.294ns 10mAGCLKt co3.058 3.2934.6975.112 5.638 5.496 5.699 5.249 5.778 5.633 5.770ns GCLKPLL t co1.380 1.5752.040 2.141 2.358 2.370 2.281 2.267 2.486 2.495 2.270ns 12mAGCLKt co3.055 3.2894.6935.109 5.634 5.492 5.695 5.245 5.775 5.630 5.767ns GCLKPLL t co1.377 1.5712.036 2.138 2.354 2.366 2.277 2.263 2.483 2.492 2.267ns DIFFERENTIAL 1.8-VSSTL CLASS II8mAGCLKt co3.060 3.2934.6845.097 5.620 5.478 5.681 5.232 5.759 5.614 5.751ns GCLKPLL t co1.382 1.5752.027 2.126 2.340 2.352 2.263 2.250 2.467 2.476 2.251ns 16mAGCLKt co3.053 3.2864.6835.098 5.623 5.481 5.684 5.235 5.764 5.619 5.756ns GCLKPLL t co1.375 1.5682.026 2.127 2.343 2.355 2.266 2.253 2.472 2.481 2.256ns DIFFERENTIAL 2.5-V SSTL CLASS I8mAGCLKt co3.081 3.3154.7115.125 5.649 5.507 5.710 5.261 5.789 5.644 5.781ns GCLKPLL t co1.413 1.6072.064 2.164 2.379 2.391 2.302 2.289 2.507 2.516 2.291ns 12mAGCLKt co3.063 3.2984.6965.110 5.634 5.492 5.695 5.246 5.774 5.629 5.766ns GCLKPLLt co1.3951.5902.049 2.149 2.364 2.376 2.287 2.274 2.492 2.501 2.276nsTable 1–110.EP3SE50 Row Pins output Timing Parameters (Part 3 of 4)I/O StandardC u r r e n t S t r e n g t hClockP a r a m e t e rFast Model C2C3C4C4LI3I4I4L Units IndustrialCommercialV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VV CCL =1.1VV CCL =1.1VV CCL =1.1VV CCL =0.9VChapter 1:Stratix III Device Data Sheet: DC and Switching CharacteristicsI/O TimingStratix III Device Handbook, Volume 2。

FPGA可编程逻辑器件芯片EP1S20F672C7中文规格书

Table 1–19. Clock Tree Performance for Stratix III Devices

Device

EP3SL50 EP3SL70 EP3SL110 EP3SL150 EP3SL200 EP3SE260 EP3SL340 EP3SE50 EP3SE80 EP3SE110

C2

Clock Tree Specifications

Table 1–19 lists the clock tree performance specifications for the logic array, DSP blocks, and TriMatrix Memory blocks for Stratix III devices.

Table 1–13 through Table 1–18 list the Stratix III device family I/O standard specifications. Refer to “Glossary” on page 1–326 for an explanation of terms used in the Table 1–14 through Table 1–18.

Switching Characteristics

This section provides performance characteristics of Stratix III core and periphery blocks for commercial grade devices.

These characteБайду номын сангаасistics can be designated as Preliminary and Final and each designation is defined below.

FPGA可编程逻辑器件芯片EP1S25F672I6N中文规格书

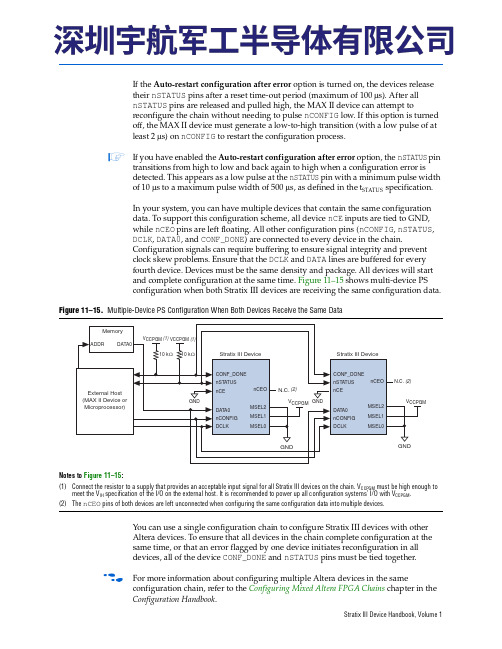

If the Auto-restart configuration after error option is turned on, the devices release their nSTATUS pins after a reset time-out period (maximum of 100μs). After all nSTATUS pins are released and pulled high, the MAX II device can attempt toreconfigure the chain without needing to pulse nCONFIG low. If this option is turned off, the MAX II device must generate a low-to-high transition (with a low pulse of at least 2μs) on nCONFIG to restart the configuration process.1If you have enabled the Auto-restart configuration after error option, the nSTATUS pin transitions from high to low and back again to high when a configuration error is detected. This appears as a low pulse at the nSTATUS pin with a minimum pulse width of 10μs to a maximum pulse width of 500μs, as defined in the t STATUS specification.In your system, you can have multiple devices that contain the same configuration data. To support this configuration scheme, all device nCE inputs are tied to GND, while nCEO pins are left floating. All other configuration pins (nCONFIG , nSTATUS , DCLK , DATA0, and CONF _DONE ) are connected to every device in the chain.Configuration signals can require buffering to ensure signal integrity and prevent clock skew problems. Ensure that the DCLK and DATA lines are buffered for every fourth device. Devices must be the same density and package. All devices will start and complete configuration at the same time. Figure 11–15 shows multi-device PS configuration when both Stratix III devices are receiving the same configuration data.You can use a single configuration chain to configure Stratix III devices with other Altera devices. To ensure that all devices in the chain complete configuration at the same time, or that an error flagged by one device initiates reconfiguration in all devices, all of the device CONF _DONE and nSTATUS pins must be tied together.fFor more information about configuring multiple Altera devices in the sameconfiguration chain, refer to the Configuring Mixed Altera FPGA Chains chapter in the Configuration Handbook .Figure 11–15.Multiple-Device PS Configuration When Both Devices Receive the Same DataNotes to Figure 11–15:(1)Connect the resistor to a supply that provides an acceptable input signal for all Stratix III devices on the chain. V CCPGM must be high enough tomeet the V IH specification of the I/O on the external host. It is recommended to power up all configuration systems’ I/O with V CCPGM .(2)The nCEO pins of both devices are left unconnected when configuring the same configuration data into multiple devices.Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationPS Configuration TimingFigure 11–16 shows the timing waveform for PS configuration when using a MAX II device as an external host.Table 11–10 defines the timing parameters for Stratix III devices for PS configuration.Figure 11–16.PS Configuration Timing Waveform (Note 1)Notes to Figure 11–16:(1)The beginning of this waveform shows the device in user-mode. In user-mode, nCONFIG , nSTATUS , and CONF_DONE a re at logic high levels.When nCONFIG is pulled low, a reconfiguration cycle begins.(2)Upon power-up, the Stratix III device holds nSTATUS low for the time of the POR delay.(3)Upon power-up, before and during configuration, CONF_DONE is low .(4)Do not leave DCLK floating after configuration. You should drive it high or low, whichever is more convenient. DATA[0] is available as a userI/O pin after configuration. The state of this pin depends on the dual-purpose pin settings.(5)Two DCLK falling edges are required after CONF_DONE goes high to begin the initialization of the device.nCO N FIGnSTATUS (2)CO N F_DO N E (3)DCLK DATAUser I/OI N IT_DO NEt Table 11–10.PS Timing Parameters for Stratix III Devices (Part 1 of 2)Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationTable11–10.PS Timing Parameters for Stratix III Devices (Part 2 of 2)Notes to Table11–10:(1)This value is applicable if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.(2)The minimum and maximum numbers apply only if you choose the internal oscillator as the clock source for starting the device.f Device configuration options and how to create configuration files are discussedfurther in the Device Configuration Options and Configuration File Format s chapters involume 2 of the Configuration Handbook.PS Configuration Using a MicroprocessorIn this PS configuration scheme, a microprocessor can control the transfer ofconfiguration data from a storage device, such as flash memory, to the target Stratix IIIdevice.f You can do a PS configuration using MicroBlaster™ Passive Serial Software Driver.For more information, refer to AN423: Configuring the MicroBlaster Passive SerialSoftware Driver.1For all configuration and timing information, refer to “PS Configuration Using a MAX II Device as an External Host” on page11–27. This section is also applicablewhen using a microprocessor as an external host.PS Configuration Using a Download CableIn this section, the generic term download cable includes the Altera USB-Blaster USBport download cable, MasterBlaster™ serial/USB communications cable,ByteBlaster II parallel port download cable, ByteBlasterMV™ parallel port downloadcable, and the EthernetBlaster download cable.In PS configuration with a download cable, an intelligent host (such as a PC) transfersdata from a storage device to the device by using the USB-Blaster, MasterBlaster,ByteBlaster II, EthernetBlaster, or ByteBlasterMV cable.Chapter 11:Configuring Stratix III DevicesPassive Serial ConfigurationChapter 11:Configuring Stratix III DevicesJTAG ConfigurationJTAG ConfigurationThe JTAG has developed a specification for boundary-scan testing. Thisboundary-scan test (BST) architecture offers the capability to efficiently testcomponents on PCBs with tight lead spacing. The BST architecture can test pinconnections without using physical test probes and capture functional data while adevice is operating normally. You can also use the JTAG circuitry to shiftconfiguration data into the device. The Quartus II software automatically generatesSOFs that can be used for JTAG configuration with a download cable in the Quartus IIsoftware programmer.f For more information about JTAG boundary-scan testing and commands availableusing Stratix III devices, refer to the following documents:■IEEE 1149.1 (JTAG) Boundary Scan Testing in Stratix III Device chapter of theStratix III Device Handbook■AN 425: Using the Command-Line Jam STAPL Solution for Device ProgrammingStratix III devices are designed such that JTAG instructions have precedence over anydevice configuration modes. Therefore, JTAG configuration can take place withoutwaiting for other configuration modes to complete. For example, if you attempt JTAGconfiguration of Stratix III devices during PS configuration, PS configuration isterminated and JTAG configuration begins.1You cannot use the Stratix III decompression or design security features if you are configuring your Stratix III device when using JTAG-based configuration.1 A device operating in JTAG mode uses four required pins, TDI, TDO, TMS, and TCK,and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor,while the TDI, TMS, and TRST pins have weak internal pull-up resistors (typically25kΩ). JTAG output pin TDO and all JTAG input pins are powered by thepower supply of I/O bank 1A. All the JTAG pins support2.5V/3.0V/3.3V VCCPDonly LVTTL I/O standard.All user I/O pins are tri-stated during JTAG configuration. Table11–11 explains eachJTAG pin's function.f The TDO output is powered by the Vpower supply of I/O bank 1A. ForCCPDrecommendations on how to connect a JTAG chain with multiple voltages across thedevices in the chain, refer to the IEEE 1149.1 (JTAG) Boundary Scan Testing in Stratix IIIDevices chapter of the Stratix III Device Handbook.。

FPGA可编程逻辑器件芯片EP2A25F672I6中文规格书

UART E VENT C ONTROLFigure 19-10: Receive InterruptsThe UART_STAT.DR, UART_STAT.ADDR, UART_STAT.ASTKY, UART_STAT.PE, UART_STAT.FE, and UART_ STAT.BI bits are updated along with UART_RBR register. The UART_STAT.OE bit updated as soon as an over-flow condition occurs (for example when a frame’s stop bit is received and the receive FIFO is full). When the UART_RBR register is not read in time, the received data is protected from being overwritten by new data until the UART_STAT.OE bit is cleared by software. Only the content of the UART_RSR register can be over-written in the overrun case.The state of the 8-deep receive FIFO can be monitored by the UART_STAT.RFCS bit. The buffer’s behavior is controlled by the UART_CTL.RFIT bit. If UART_CTL.RFIT is zero, the UART_STAT.RFCS bit is set when the receive buffer holds four or more words. If UART_CTL.RFIT is set, the UART_STAT.RFCS bit is set when the receive buffer holds seven or more words. The UART_STAT.RFCS bit is cleared by hardware when a core or DMA reads the UART_RBR register and when the buffer is flushed below the level of four (UART_CTL.RFIT=0) or seven (UART_CTL.RFIT=1). If the associated interrupt bit UART_IMSK.ERFCI is enabled, a status interrupt is reported when the UART_STAT.RFCS bit is set.If errors are detected during reception, an interrupt can be requested from the status interrupt output. This status interrupt request goes directly to the SEC. Status interrupt requests are enabled by the bit.The controller detects the following error conditions, shown with their associated bits in the UART_STAT register.•Overrun error (UART_STAT.OE bit)•Parity error (UART_STAT.PE bit)•Framing error/invalid stop bit (UART_STAT.FE bit)•Break indicator (UART_STAT.BI bit)ADSP-BF60X UART R EGISTER D ESCRIPTIONS23 (R/W)RPOLC IrDA RX Polarity Change.The UART_CTL.RPOLC bit selects the active low/high polarity forIrDA communications. This bit only is effective in IrDA mode. If set,in IrDA mode, the UART_RX pin idles high. In UART or MDB mode,it is inverted-NRZ. If cleared, in IrDA mode, the UART_RX pin idleslow. In UART or MDB mode, it is NRZ.0Active-low RX polarity setting1Active-high RX polarity setting22 (R/W)FCPOL Flow Control Pin Polarity.The UART_CTL.FCPOL select the polarities of the UART_CTS andUART_RTS pins. When UART_CTL.FCPOL is cleared, the UART_RTS andUART_CTS pins are active low, and UART is halted when the UART_RTS and UART_CTS pin state is high. When UART_CTL.FCPOL is set,the UART_RTS and UART_CTS pins are active high, and UART is haltedwhen the UART_RTS and UART_CTS pin state is low.0Active low CTS/RTS1Active high CTS/RTS19 (R/W)SB Set Break.If set, the UART_CTL.SB bit forces the UART_TX pin to lowasynchronously, regardless of whether or not data is currentlytransmitted. This bit functions even when the UART clock isdisabled. Because the UART_TX pin normally drives high, it can beused as a flag output pin, if the UART is not used. (For example, ifUART_CTL.TPOLC is cleared, drive UART_TX pin low; or if UART_CTL.TPOLC is set, drive UART_TX pin high.)0No force1Force TX pin to 018 (R/W)FFE Force Framing Error on Transmit.The UART_CTL.FFE bit is intended for test purposes. This bit is usefulfor debugging software, especially in loopback mode.0Normal operation1Force errorTable 19-10:UART_CTL Register Fields (Continued)Bit No.(Access)Bit Name Description/EnumerationU NIVERSAL A SYNCHRONOUS R ECEIVER/T RANSMITTER (UART)ADSP-BF60X UART R EGISTER D ESCRIPTIONSTable 19-9:ADSP-BF60x UART Register List (Continued)Name DescriptionUART_CLK Clock Rate RegisterUART_IMSK Interrupt Mask RegisterUART_IMSK_SET Interrupt Mask Set RegisterUART_IMSK_CLR Interrupt Mask Clear RegisterUART_RBR Receive Buffer RegisterUART_THR Transmit Hold RegisterUART_TAIP Transmit Address/Insert Pulse RegisterUART_TSR Transmit Shift RegisterUART_RSR Receive Shift RegisterUART_TXCNT Transmit Counter RegisterUART_RXCNT Receive Counter RegisterControl RegisterThe UART_CTL register provides enable/disable control for internal UART and for the IrDA mode of oper-ation. This register also provides UART line control, permitting selection of the format of received and transmitted character frames. Modem feature control also is available from this register, including partial modem functionality to allow for hardware flow control and loopback mode.。

FPGA可编程逻辑器件芯片EP2S60F672C5中文规格书

Operating ConditionsStratix ®II devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grades and commercial devices are offered in -3 (fastest), -4, -5 speed grades.Tables 5–1 through 5–32 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II devices.Absolute Maximum RatingsTable 5–1 contains the absolute maximum ratings for the Stratix II device family.Table 5–1.StratixII Device Absolute Maximum Ratings Notes (1), (2), (3)SymbolParameterConditionsMinimumMaximumUnitV CCINT Supply voltage With respect to ground –0.5 1.8V V CCIO Supply voltage With respect to ground –0.5 4.6V V CCPD Supply voltageWith respect to ground –0.5 4.6V V CCA Analog power supply for PLLsWith respect to ground–0.5 1.8V V CCD Digital power supply for PLLs With respect to ground –0.5 1.8V V I DC input voltage (4)–0.5 4.6V I OUT DC output current, per pin –2540mA T STG Storage temperature No bias–65150°C T J Junction temperatureBGA packages under bias–55125°CNotes to Tables 5–1(1)See the Operating Requirements for Altera Devices Data Sheet .(2)Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.(3)Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.(4)During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100mA and periods shorter than 20ns.SII51005-4.5Stratix II Device Handbook, Volume 1DC & Switching Characteristics1.8-V HSTL Class II 1.6600.830 1.6600.831.5-V HSTL Class I1.3750.688 1.3750.68751.5-V HSTL Class II 1.3750.688 1.3750.68751.2-V HSTL with OCT 1.1400.570 1.1400.570Differential SSTL-2 Class I2.3251.1632.3251.1625Table 5–35.Timing Measurement Methodology for Input Pins (Part 2 of 2)Notes (1)–(4)I/O StandardMeasurement Conditions Measurement PointV CCIO (V)V REF (V)Edge Rate (ns)V M E A S (V)Timing Model1The performance numbers in Table5–36 are extracted from theQuartus II software version 5.1 SP1.Table5–36.Stratix II Performance Notes(Part 1 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitLE16-to-1multiplexer(4)2100654.87625.0523.83460.4MHz32-to-1 multiplexer (4)3800519.21473.26464.25384.17MHz16-bit counter1600566.57538.79489.23421.05MHz64-bit counter6400244.31232.07209.11181.38MHzT riMatrix Memory M512 block Simple dual-port RAM32 × 18 bit010500.00476.19434.02373.13MHz FIFO 32 x 18 bit 2210500.00476.19434.78373.13MHzT riMatrix Memory M4K block Simple dual-port RAM128 x 36 bit (8)010540.54515.46469.48401.60MHzT rue dual-port RAM128 × 18 bit (8)010540.54515.46469.48401.60MHzFIFO128 × 36 bit2210530.22499.00469.48401.60MHzSimple dual-port RAM128 × 36 bit (9)010475.28453.30413.22354.10MHzT rue dual-port RAM128 × 18 bit (9)010475.28453.30413.22354.10MHzStratix II Device Handbook, Volume 1DC & Switching CharacteristicsT riMatrix Memory M-RAM block Single portRAM 4K × 144 bit010349.65333.33303.95261.09MHzSimple dual-portRAM 4K × 144 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 4K × 144 bit010349.65333.33303.95261.09MHzSingle portRAM 8K × 72 bit010354.60337.83307.69263.85MHzSimple dual-portRAM 8K × 72 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 8K × 72 bit010349.65333.33303.95261.09MHzSingle portRAM 16K × 36 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 16K × 36 bit010420.16400.00364.96313.47MHzT rue dual-portRAM 16K × 36 bit010359.71342.46313.47268.09MHzSingle portRAM 32K × 18 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 32K × 18 bit010420.16400.0364.96313.47MHzT rue dual-portRAM 32K × 18 bit010359.71342.46313.47268.09MHzSingle portRAM 64K × 9 bit010364.96347.22317.46271.73MHzSimple dual-portRAM 64K × 9 bit010420.16400.0364.96313.47MHzT rue dual-portRAM 64K × 9 bit010359.71342.46313.47268.09MHzTable5–36.Stratix II Performance Notes(Part 2 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitStratix II Device Handbook, Volume 1Timing ModelDSP block 9 × 9-bit multiplier(5) 001430.29409.16373.13320.10MHz 18 × 18-bitmultiplier(5)001410.17390.01356.12305.06MHz18 × 18-bitmultiplier(7)001450.04428.08391.23335.12MHz36 × 36-bitmultiplier(5)001250.00238.15217.48186.60MHz36 × 36-bit multiplier(6)001410.17390.01356.12305.06MHz18-bit, four-tap FIRfilter001410.17390.01356.12305.06MHzLarger designs 8-bit,16-tap parallelFIR filter5804259.06240.61217.15185.01MHz8-bit, 1024-point,streaming, threemultipliers and fiveadders FFT function2976229398.72364.03355.23306.37MHz8-bit, 1024-point,streaming, fourmultipliers and twoadders FFT function27812212398.56409.16347.22311.13MHz8-bit, 1024-point,single output, oneparallel FFT engine,burst, three multipliersand five adders FFTfunction98453425.17365.76346.98292.39MHz8-bit, 1024-point,single output, oneparallel FFT engine,burst, four multipliersand two adders FFTfunction91954427.53378.78357.14307.59MHzTable5–36.Stratix II Performance Notes(Part 3 of6)Note(1)ApplicationsResources Used PerformanceALUTsTriMatrixMemoryBlocksDSPBlocks-3SpeedGrade(2)-3SpeedGrade(3)-4SpeedGrade-5SpeedGradeUnitStratix II Device Handbook, Volume 1。

FPGA可编程逻辑器件芯片EP2S15F672I6N中文规格书

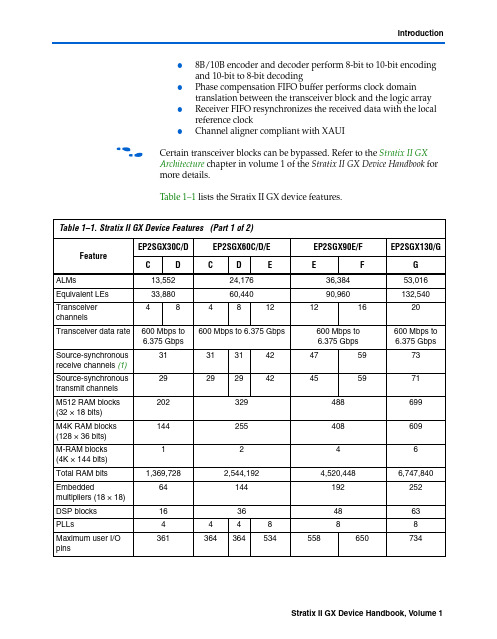

Introduction●8B/10B encoder and decoder perform 8-bit to 10-bit encodingand 10-bit to 8-bit decoding●Phase compensation FIFO buffer performs clock domaintranslation between the transceiver block and the logic array●Receiver FIFO resynchronizes the received data with the localreference clock●Channel aligner compliant with XAUIf Certain transceiver blocks can be bypassed. Refer to the Stratix II GXArchitecture chapter in volume 1 of the Stratix II GX Device Handbook formore details.Table1–1 lists the Stratix II GX device features.Table1–1.Stratix II GX Device Features (Part 1 of2)Feature EP2SGX30C/D EP2SGX60C/D/E EP2SGX90E/F EP2SGX130/G C D C D E E F GALMs13,55224,17636,38453,016 Equivalent LEs33,88060,44090,960132,540 Transceiverchannels484812121620Transceiver data rate600 Mbps to6.375Gbps 600 Mbps to 6.375Gbps600 Mbps to6.375 Gbps600 Mbps to6.375 GbpsSource-synchronousreceive channels (1)31313142475973Source-synchronoustransmit channels29292942455971M512 RAM blocks(32×18bits)202329488699M4K RAM blocks(128×36bits)144255408609M-RAM blocks(4K×144 bits)1246 Total RAM bits1,369,7282,544,1924,520,4486,747,840 Embeddedmultipliers (18×18)64144192252 DSP blocks16364863 PLLs444888 Maximum user I/Opins361364364534558650734Document Revision Historyload acts as a preset when the asynchronous load data input is tied high.When the asynchronous load/preset signal is used, the labclkena0signal is no longer available.The LAB row clocks [5..0] and LAB local interconnect generate theLAB-wide control signals. The MultiTrack™ interconnects haveinherently low skew. This low skew allows the MultiTrack interconnectsto distribute clock and control signals in addition to data.Figure2–34 shows the LAB control signal generation circuit.Figure2–B-Wide Control SignalsAdaptive Logic ModulesAdaptive Logic Modules The basic building block of logic in the Stratix II GX architecture is the ALM. The ALM provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure2–35 shows a high-level block diagram of the Stratix II GX ALM while Figure2–36 shows a detailed view of all the connections in the ALM.Figure2–35.High-Level Block Diagram of the Stratix II GX ALM。

FPGA可编程逻辑器件芯片EP2A15F672I8N中文规格书

WROSRLMT and EMAC_DMA_BMMODE.RDOSRLMT bits. Maximum outstanding requests=EMAC_DMA_ BMMODE.WROSRLMT + 1 (or) EMAC_DMA_BMMODE.RDOSRLMT + 1.•Allowed burst sizes. The allowed burst sizes are 4 (EMAC_DMA_BMMODE.BLEN4), 8 (EMAC_DMA_BMMODE.BLEN8), 16 (EMAC_DMA_BMMODE.BLEN16) and the SINGLE burst. Only those burst sizes configured by the program (via the EMAC_DMA_BMMODE register) are used for data transfer through the SCB bus.However, SINGLE burst is available by default, when the EMAC_DMA_BMMODE.UNDEF bit in the is cleared.Data transfers are restricted to the maximum burst size from this list of programmed burst sizes.•Burst splitting and burst selection. The EMAC-SCB splits the DMA requests into multiple bursts on the SCB system bus. Splitting is based on DMA count and software controllable burst enable bits (shown in the Allowed burst sizes) as well as burst types (INCR and INCR_ALIGNED) which are also controllable through the software. SINGLE burst is enabled when the EMAC_DMA_BMMODE.UNDEF bit is not set. Burst length select priority is in the sequence: UNDEF, 16, 8, and 4.•INCR burst type–If the EMAC_DMA_BMMODE.UNDEF bit is set, then the EMAC-SCB always chooses the maximum allowed burst length based on the EMAC_DMA_BMMODE.BLEN16, EMAC_DMA_BMMODE.BLEN8, EMAC_ DMA_BMMODE.BLEN4 bits. In cases where the DMA requests are not multiples of the maximumallowed burst length, the SCB may also choose a burst-length of any value less than the maximum enabled burst-length (all lesser burst-length enables are redundant). For example, when length bits are enabled and the DMA requests a burst transfer size of 42 beats, then the SCB splits it into three bursts of 16, 16 and 10 beats respectively.–If EMAC_DMA_BMMODE.UNDEF is not enabled, then the burst length is based on the priority of the enabled bits in the following order EMAC_DMA_BMMODE.BLEN16, EMAC_DMA_BMMODE.BLEN8, EMAC_ DMA_BMMODE.BLEN4. When the DMA requests a burst transfer, the SCB interface splits therequested bursts into multiple transfers using only the enabled burst lengths. This splitting can occur when the requested burst is not a multiple of the maximum enabled burst. If it cannot choose any of the enabled burst lengths then it selects the burst length as 1.For example, when EMAC_DMA_BMMODE.BLEN16, EMAC_DMA_BMMODE.BLEN8, EMAC_DMA_BMMODE.BLEN4 are enabled and the DMA requests a burst transfer of 42 beats, then the SCB interface splits it into multiple bursts of size 16, 16, 8, 1 and 1 beats respectively (the sequence is in decreasing burst sizes). •INCR_ALIGNED burst type. When the address-aligned burst-type is enabled (EMAC_DMA_BMMODE.AAL), then in addition to the burst splitting conditions explained in the INCR Burst type, the SCB inter-face splits the DMA requested bursts such that each burst-size is aligned to the least significant bits of the start address. The SCB interface initially generates smaller bursts so that the remaining transfers can be transferred with the maximum possible (enabled) fixed burst lengths.For example, in the same setting as explained earlier for EMAC_DMA_BMMODE.UNDEF set (EMAC_DMA_ BMMODE.BLEN16, EMAC_DMA_BMMODE.BLEN8, and EMAC_DMA_BMMODE.BLEN4 are enabled), DMA requests a burst size of 42 beats at the start address of 0x000003A4. The SCB starts the first transfer withTable 23-6:Core Receive Engine Sub-Blocks (Continued)CORE Receive Engine sub block Functionality overviewReceive Frame Controller Module–Packs incoming 8-bit input stream to 32-bit datainternally.–Performs Frame filtering, for uni-cast/multi-cast/broadcast frames.–Attaches the calculated IP Checksum input fromChecksum Offload Engine.–Updates the Receive Status to Bus Interface. Receive Flow Control Module–Detects the receiving Pause frame and pauses theframe transmission for the delay specified within thereceived Pause frame.–Works in Full Duplex mode.Receive IP Checksum Offload Engine–Calculates IPv4 header checksums and verify againstthe received IPv4 header checksums.–Identifies a TCP, UDP or ICMP payload in thereceived IP datagrams.Receive Bus Interface Unit Module Interface to the FIFO.Address Filtering Module Performs Destination Address Filtering based onUnicast/ Multi-cast/Broadcast frames.–Provides CRC hash filtering.EMAC PHY InterfaceThe EMAC can interface to the PHY via the RMII interface standard. The tables below indicate the RMII pins available in the EMAC in terms of their generic names. Please refer to the data sheet for exact pin names.Table 23-7:RMII PinsSl. No.Generic Signal Name (IEEE Standards)RMII Pin functionality.1. TXD0RMII transmit data pin D0 (di-bit lower)2. TXD1RMII transmit data pin D1 (di-bit higher)3. RXD0RMII receive data pin D0 (di-bit lower)4. RXD1RMII receive data pin D1 (di-bit higher)5. RMII CLK RMII common clock (for Tx and Rx), also calledreference clock6. TXEN RMII transmit enable pin (Tx valid)7. CRS RMII Carrier Sense / receive data valid8. MDC Serial management clock driven by EMACE THERNET M EDIA A CCESS C ONTROLLER (EMAC)EMAC F UNCTIONAL D ESCRIPTIONthis. With this option available, programs are not always restricted to a contiguous memory loca-tion in ring mode.DMA Related RegistersA summary of DMA registers relative to their function is provided in the table below. Please refer to the“Register Descriptions” sections for complete bit descriptions of each of these registers.Table 23-10:Summary of DMA Related Registers.Register Name DescriptionBus Mode1Establishes the bus operating modes for the DMA with respect to theSCB master interface.Transmit Poll Demand Enables the transmit DMA to check whether or not the currentdescriptor is owned by DMA. The transmit poll demand command isgiven to wake up the TxDMA if it is in suspend mode. The TxDMAcan go into suspend mode because of an underflow error in atransmitted frame or because of the unavailability of descriptors ownedby transmit DMA. This command can be issued anytime and theTxDMA resets this command once it starts re-fetching the currentdescriptor from host memory.Receive Poll Demand Enables the receive DMA to check for new descriptors. This commandis given to wake-up the RxDMA from the SUSPEND state. TheRxDMA can go into SUSPEND state only because of the unavailabilityof descriptors owned by it.Receive Descriptor List Address Points to the start of the receive descriptor list. The descriptor listsreside in the application memory space and must be word-aligned (32-bit data bus). The DMA internally converts the descriptor list to a buswidth aligned address by making the corresponding LSBs low. Transmit Descriptor List Address Points to the start of the transmit descriptor list. The descriptor listsreside in the application memory space and must be word-aligned (for32-bit data bus). The DMA internally converts it to bus width alignedaddress by making the corresponding LSB to low.DMA Status Contains all the status bits that the DMA reports to the application.The software driver reads this register during an interrupt serviceroutine or during polling. Most of the fields in this register cause thehost to be interrupted.Operation Mode Establishes the transmit and receive operating modes and commands.The operation mode register should be the last control register to bewritten as part of DMA initialization.Interrupt Enable Enables the interrupts reported by DMA status register. After ahardware or software reset, all interrupts are disabled.。

FPGA可编程逻辑器件芯片EP1C25F672C8N中文规格书

System Reset and BootingTWI Master Boot ModeIn TWI master boot mode (BMODE = 0101) the boot kernel reads boot data from I2C memory connected to the TWI0 interface. The Blackfin proces-sor selects the slave EEPROM with the unique ID 0xA0, submitssuccessive read commands to the device starting at internal address0x0000, and begins clocking data to the processor. The EEPROM’s device select bits A2–A0 must be 0s (tied low) when present. The I2C EPROM device should comply with Philips I2C Bus Specification version 2.1 and should have the capability to auto increment its internal address counter such that the contents of the memory device can be read sequentially.Connections are shown in Figure17-21“TWI Master Boot Mode Con-nections” on page17-77.On the Blackfin processor, in both TWI master and slave boot modes, the upper 512 bytes starting at address 0xFF903E00 eithermust not be used or must be booted last. The boot ROM code usesthis space for the TWI boot modes to temporarily hold the serialdata which is then transferred to L1 instruction memory usingDMA. All boot blocks that target the L1 instruction memory orexternal memories must have the BFLAG_INDIRECT bit set. Initcodescan alter the placement of the temporary buffer by modifying thepTempBuffer and dTempByteCount variables in the ADI_BOOT_DATAstructure.Figure 17-21. TWI Master Boot Mode ConnectionsADSP-BF54x Blackfin Processor Hardware ReferenceProgramming ExamplesR0 = ( SYSCTRL_VRCTL | SYSCTRL_INTVOLTAGE | SYSCTRL_WRITE );R1 = FP;R1 += -sizeof(ADI_SYSCTRL_VALUES);R2 = 0 (z);IMM32(P4,BFROM_SYSCONTROL);call(P4);SP += 12;(R7:0,P5:0) = [SP++];unlink;rts;__voltage.end:The previous sequence must also be executed when the V DDINT voltage is applied externally to ensure internal timings can appropriately be adjusted for the constant or changing V DDINT voltage. In this case, replace the SYSCTRL_INTVOLTAGE flag with the SYSCTRL_EXTVOLTAGE flag.ADSP-BF54x Blackfin Processor Hardware Reference。

FPGA可编程逻辑器件芯片EP1C12F256I7N中文规格书

ADSP-BF54x Blackfin Processor Hardware ReferenceSecure Digital HostSDH Data Length Register (SDH_DATA_LGTH)The SDH_DATA_LGTH register contains a 16-bit value for the number of data bytes to be transferred before generating the DAT_END event. The value loaded to this register is copied into the SDH_DATA_CNT register when the data path state machine is enabled and starts the transfer.SDH Data Control Register (SDH_DATA_CTL)The SDH_DATA_CTL register controls the data path state machine. The state machine becomes enabled once the DTX_E bit is set. The direction of the transfer is determined by DTX_DIR . If the DMA channel is to be used for the data transfer then the DTX_DMA_E bit must be set. Otherwise the SDH FIFO would only be accessible through the core. For block transfers, the block length must be specified by DTX_BLK_LGTH , where the block length is2DATA_BLK_LGTH . After a data write, data cannot be written to this regis-ter for five SCLK cycles.Figure 27-13. SDH Data Length Register 15141312111098765432100000000000000000SDH Data Length Register (SDH_DATA_LGTH)DATA_LENGTH(Number of bytes to transfer)Reset = 0x0000Read0xFFC03928ADSP-BF54x Blackfin Processor Hardware ReferenceSecure Digital Host SDH_RESPONSE20xFFC0391C R 32-bit “SDH Response Registers (SDH_RESPONSEx)” on page 27-59SDH_RESPONSE30xFFC03920R32-bit “SDH Response Registers (SDH_RESPONSEx)” on page 27-59SDH_DATA_TIMER 0xFFC03924R/W 32-bit “SDH Data Timer Register(SDH_DATA_TIMER)” onpage 27-60SDH_DATA_LGTH 0xFFC03928R/W 16-bit “SDH Data Length Register(SDH_DATA_LGTH)” onpage 27-61SDH_DATA_CTL 0xFFC0392C R/W 16-bit “SDH Data Control Register(SDH_DATA_CTL)” on page 27-61SDH_DATA_CNT 0xFFC03930R 16-bit “SDH Data Counter Register(SDH_DATA_CNT)” on page 27-62SDH_STATUS 0xFFC03934R 32-bit “SDH Status Register(SDH_STATUS)” on page 27-63SDH_STATUS_CLR 0xFFC03938W1A 16-bit “SDH Status Clear Register(SDH_STATUS_CLR)” onpage 27-65SDH_MASK00xFFC0393C R/W 32-bit “SDH Interrupt Mask Registers(SDH_MASKx)” on page 27-66SDH_MASK10xFFC03940R/W 32-bit “SDH Interrupt Mask Registers(SDH_MASKx)” on page 27-66SDH_FIFO_CNT 0xFFC03948R 16-bit “SDH FIFO Counter Register(SDH_FIFO_CNT)” on page 27-68SDH_FIFOx0xFFC03980R/W 32-bit “SDH Data FIFO Register(SDH_FIFO)” on page 27-69SDH_E_STATUS0xFFC039C0R/W1C 16-bit “SDH Exception Status Register (SDH_E_STATUS)” on page 27-69SDH_E_MASK 0xFFC039C4R/W 16-bit “SDH Exception Mask Register(SDH_E_MASK)” on page 27-70Table 27-10. SDH Functional Registers (Cont’d)RegisterNameAddress Type Access Description。

FPGA可编程逻辑器件芯片EP1C12F256C6N中文规格书

Secure Digital HostWAIT StateIn the WAIT state, the SDH waits for a response to be received on the SD_CMD signal. Upon entering this state, an internal timer starts. If the response is not received within 64 SD_CLK cycles, the CMD_TIMEOUT flag is set and the CMD_ACT flag is cleared. The state machine then enters theIDLE state, awaiting the next action.A response, sent back from the card and indicated by the "0" start bit onthe SD_CMD signal, transitions the SDH to the RECEIVE state where it is ready to receive a short or long response.The WAIT state can also detect card interrupts. This is an optional feature that applies only to MMC cards. The feature is enabled by setting the CMD_INT_E bit in the SDH_COMMAND register. When CMD_INT_E is set, the timeout timer that is normally started upon entry to the WAIT state is disabled. The SDH remains in this state until a card interrupt is detected.Cards that implement this feature may have functions with a delayedresponse that is triggered by an internal event in the card. Once the event is triggered the card sends the response. The SDH then detects this start bit of the response and proceeds to the RECEIVE state.RECEIVE StateIn the RECEIVE state the SDH reads the response on the SD_CMD signal from the card. Upon receiving either the short or long response, if the response passes the CRC check, the CMD_ACT flag is cleared and theCMD_RSP_END flag is set. If the CRC check fails, the CMD_CRC_FAIL flag is set. In either case, the state machine then goes to the IDLE state.ADSP-BF54x Blackfin Processor Hardware ReferenceADSP-BF54x Blackfin Processor Hardware ReferenceSecure Digital HostSDH Data Path CRCThe data CRC generator of the SDH calculates the 16-bit CRC checksum for all bits sent or received for a given block transaction. The data path CRC generator is not enabled for stream based data transfers. For a 1-bit bus configuration, the 16-bit CRC is calculated for all data sent on the SD_DATA0 signal. For a 4-bit wide data bus, the 16-bit CRC is calculated separately for each SD_DATAx signal. The data path CRC checksum is a 16-bit value calculated as follows.with:where:SDH Data FIFOThe data FIFO is a 32-bit wide, 16-word deep data buffer with transmit and receive logic. The FIFO configuration depends on the state of the TX_ACT and RX_ACT flags. If TX_ACT is set, the FIFO operates as a transmit FIFO, supplying data to the SDH for transfer to the card. If RX_ACT is set, the FIFO operates as a receive FIFO, where the SDH writes data received from the card. If neither TX_ACT nor RX_ACT flags are set, then the FIFO is disabled.CRC[15:0]Remainder x 16M x ()⨯G x ()-------------------------=G x ()x 16x 12x 51+++=M x ()x 8(DTX_BLK_LGTH )⨯1–(first data bit)⨯...x 0(last data bit)⨯++=。

FPGA可编程逻辑器件芯片EPXA1F672C2ES中文规格书

Figure 15-11: PKTE_CONT Register Diagram

Table 15-33: PKTE_CONT Register Fields

Bit No. (Access)

Bit Name

31:0 VALUE (RX/W)

Description/Enumeration

Continue Operating. The PKTE_CONT.VALUE bit field releases the packet engine from a halt state when written with any value in halt mode.

ADSP-BF70x PKTE Register Descriptions

PKTE Continue Register

A write to the PKTE_CONT register (with any value) releases the packet engine from a halt state when in halt mode.

ADSP-BF70x Blackfin+ Processor Hardware Reference

0 Do Not Clear Ownership Bits. The packet engine does not clear the ownership bits in the command descriptor when it completes an operation. The host application must clear the ownership bits in "old descriptors" before the packet engine is allowed to wrap around the CDR to re-encounter these "old descriptors". This setting has the advantage of eliminating a separate DMA write to the CDR.

FPGA可编程逻辑器件芯片EP2A25F672I8N中文规格书