数字式相位差测量仪设计方案

相位测量仪报告

相位测量仪摘要:本设计以单片机和可编程逻辑器件FPGA为控制核心,实现数字信号的产生、逻辑信号的采集和示波器的显示。

系统主要由三个模块组成:信号发生,数据采集与波形显示。

本设计经过单片机产生逻辑信号,利用FPGA作为数据处理器和DAC控制器,能准确、清晰的在模拟示波器上显示出逻辑波形、触发标记、光标。

利用键盘输入和液晶显示,能实现逻辑预设和触发模式设置。

经验证,本方案完成了全部基本功能和扩展功能。

关键词:逻辑分析仪可编程逻辑器件单片机Abstract:The design of the microcontroller and FPGA programmable logic devices for the control of the core, digital signal generation, logic signal acquisition and oscilloscope display. System consists of three modules: signal, data acquisition and waveform display. After the microcontroller generates the logic signal design , as a data processor using FPGA and DAC controllers , accurate, clearly shows the logic waveforms. The use of keyboard and LCD display , and to achieve pre-trigger mode logic. Proven, the program completed all the basic features and extensions. Keywords:logical link control Programmable logic devices MCU一、方案设计与论证1、数字式移相信号发生器方案一:采用FPGA实现DDS直接频率合成技术。

相位差检测电路

课程设计报告课程电子测量与虚拟仪器题目相位差检测电路系别物理与电子工程学院年级08级专业电子科学与技术班级08电科(3)班学号*******(02 14 23 24)学生姓名崔雪飞陈祥刘刚李从辉指导教师徐健职称讲师设计时间2011-4-25~2011-4-29目录第一章绪论 (2)第二章题目及设计要求 (3)2.1题目要求 (3)2.2设计要求 (3)第三章方案设计与论证 (4)3.1移相电路设计 (4)3.2检测电路设计 (4)3.3显示电路设计 (5)第四章结构框图等设计步骤 (6)4.1设计流程图 (6)4.2模块分析 (7)4.2.1 移相电路 (7)4.2.2 检测电路 (7)4.2.3 显示电路 (8)4.3结果显示 (9)4.4总电路图 (11)第五章误差分析 (12)第六章总结体会 (13)第七章参考文献 (14)附录 (15)第一章绪论随着电子技术和计算机技术的发展,电子设计自动化(E-DA) 技术使得电子电路设计人员在计算机上能完成各种电路的设计,性能分析和有关参数的测试等大量的工作。

Multi-sim2001是加拿大InteractiveImageTechnologies公司2001年推出的Multisim最新版本,是一个专门用于仿真与设计的工具软件,它丰富的元件库中提供数千种电路元件,随时可以调用;它提供了多种测试仪器仪表,可方便的对电路参数进行测试和分析。

移相器在新一代移动通信、电子战、有源相控阵和智能天线等系统中获得广泛的应用。

移相器在电子系统中的主要作用是调整系统接收 /发射时电路中的信号相位。

本文将介绍用Multisim软件的部分集成电路和控制部件等各种元件来完成移相电路的设计和仿真。

使用Multisim交互式地搭建电路原理图,并对电路进行仿真。

Multisim提炼了SPICE仿真的复杂内容,这样无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。

数字相位差课程设计 中北大学

测控电路设计专业:测控技术与仪器班级:11050341姓名:学号:数字相位差测量仪的设计1.设计思路相位差测量仪主要是由锁相环PLL产生3600倍频基准信号和移相网络的基准信号与待测信号进行异或后的信号作为计数显示器的控制信号。

2.设计方案2.1方案设计将被测信号送入移相网络,经RC移相、LM324隔离放大,产生两路信号,一路为基准信号经过波形转换,另一路为移相后的信号。

分别经过波形转换、整形、二分频送给相位测量模块。

基准信号fr经过放大整形后加到锁相环的输入端,锁相环的反馈环路中设置一个N=3600的分频器构成一个3600倍频器,使输入的基准信号fr经过锁相环后频率变为原来的3600倍,但相位与基准信号fr 相同,输出信号用做计数器的时钟基准信号。

被测信号fs经过放大整形并二分频得到的二分频信号与基准信号fr的二分频信号经过二输入异或门得到的输出信号作为计数控闸门制信号,使计数器仅在基准信号fr与被测信号的相位差间隔内计数,计数器计的数值即为基准信号fr与被测信号fs的相位差。

2.2 设计原理框图图1 原理框图由原理方框图可以看出,所要设计的电路的主要由移相网络、放大整形、倍频、计数显示四大部分构成。

下面将从这三大部分着手设计电路3.电路设计3.1移相网络部分图2 移相电路移相网络是由二节RC超前或滞后移相网络、集成运算放放大器组成的电压跟器和运放组成的。

一节RC电路如图所示。

由它的相量图可知超一个相角φ,,当f →0时,φ→90°;f →∞时,φ→0。

这说明:一节RC 电路最大相移不超过90°,不能满足相位平衡条件。

若两节RC电路最大相移虽可接近180°,但此时频率必须很低,从而容抗很大,致使输出电压接近于零,所以本电路又加了电压跟随器和放大器。

3.2放大整形电路在设计这个部分的电路时,要考虑到不能使基准信号和被测信号不发生相对相位移动的问题,基准信号和被测信号在设计的放大整形电路中所引起的附加移相是相等的,所以原理方框图A1和A2要用相同的电路。

电气电子毕业设计100竞赛论文——低频数字式相位测量仪

电子竞赛——低频数字式相位测量仪目录摘要 (1)一.设计任务与设计要求 (2)1.1 设计任务 (2)1.2 设计要求 (2)1.2.1 基本要求 (2)1.2.2 发挥部分 (2)二.相位测量 (2)2.1相位测量方案选择与论证 (3)2.2相位测量框图 (3)2.3相位测量硬件电路设计与器件选择 (3)2.3.1 相位比较电路 (4)2.3.2 CPU与外围电路 (5)2.3.3键盘与显示电路 (6)2.3.4直流稳压电源电路 (6)2.4 测试方法与测试结果 (7)2.4.1 相位测试方法 (7)2.4.2相位测试结果 (7)2.4.3测量工具 (7)三.频率测量方案 (7)3.1 方案选择与论证 (7)3.2 硬件电路设计 (9)3.3 频率测量测试及结果 (9)3.4 测量工具 (10)四.移相网络电路参数计算 (10)4.1移相网络电路框图 (10)4.2移相网络电路参数计算 (10)4.3 移相网络测试 (12)4.4 测量工具 (12)五.发挥部分数字移相信号发生器 (12)5.1方案论证 (12)六.系统软件设计 (15)七.总的结果分析 (16)八.结论 (16)附录:移相信号发生器电路 (17)10-03设计题目:低频数字式相位测量仪参赛队员:刘传登韩春鹏王忠杰指导教师:车新生摘要本设计实现的是对两列信号的相位差的精确测量并数字显示测量结果。

为达到要求的精度本设计采用了将相位转换为直流电压的间接测量方法。

用16位A/D对输出的直流电压进行采样,送入单片机进行相位显示。

这样就使得相位差就具有足够高的分辨度,完成了任务要求。

在单片机P89C51实现以上功能的同时,利用单片机中的多位计数器/定时器对输入信号进行等精度频率测量。

为测量方便,又制作了移相网络电路,设计了移相信号电路和应用程序。

整个装置具有原理简单,测量精度高,测量范围宽,测量结果显示直观的特点。

关键词:相位测量等精度测量移相网络一.设计任务与要求1.1设计任务设计并制作一台低频相位测量系统,包括相位测量仪,数字式移相信号发生器和移相网络三部分。

CPLD低频数字相位测量仪的设计

包括数字移相信 号发生 器和相位 测量仪 2 部分 , 分别 完成移相信号的发生 、 频率 与相位差 的预置、 数字显示、 号的移相 以 信

及移相后信 号相位差和频率 的测量 与相识 等功能。 中数字 式移 相信号发生 器可 以产 生预置频率 的差值 ; 其 相位 测量仪可

以测量和显 示相位信 号的频率 、 位 差。 相

厂一

后, 将波形整形电路的2 0 ] 厂 厂 厂 厂 ] ]

图 1 波形变换 示意 图

的功能, 用以产生相位测量仪所需的输入正弦信号 。 其

技术 要 求 指标 : 率 范 围2 Hz~ 0 Hz 频 率 步进 为 频 0 2k ,

2H , 0 z 输出频率可预置; 相位差范围为0 3 9 , ~ 5 。相位差

( 具有设定保存功能。 5)

实现相位 、 频率的测量, 并且具有独 自的控制功能和数

字显示 功能。

11系统硬件 结构 .

首 先 将 被 测 2列 正

弦 信号 A 、 B经平 滑 滤 波

后 , 入 过 零 比较 电路 , 输

A

1系统硬件设计

总体要求 : ( ) 有相 位 测量 功 能 , 1具 即相 位 测量 仪 的 功 能 。 其

传 感 及 检 测 仪 表

C L 低频 数 字 相 位 测 量 仪 的设 计 PD

朱 红梅 , 美 君 潘

( 海西部矿 业铅业 摘

要: 绍 了一种基 于复杂的可编程逻辑 器件( L 和 高速 单片机s c8 c 8 介 CP D) T 9 5 的低频数字 相位 测量仪 。 该测量仪

京航 天航 空 大 学 出版 社 【] 白英 彩 . 型 计 算 机 常 用 芯 片 手 册 【 . 海 : 海科 学 3 微 M】 上 上

第3章+低频数字式相位测量仪的设计

图3.3 用测周期的方法获得信号频率

第3章 低频数字式相位测量仪的设计

2) 鉴相器就是异或门,在鉴相器的输出波形IV中, 正脉冲宽度就是要测量的I和V 相位差所对应的时间差 Tθ ,如图3.4所示。

第3章 低频数字式相位测量仪的设计

I V

IV

图3.4 鉴相器的输入、输出波形图

第3章 低频数字式相位测量仪的设计

F INT1(P 3.3)

图3.6 MCU测量时间差、周期的电路图

第3章 低频数字式相位测量仪的设计

(2) 时序图如图3.7所示。需要说明的是,由软 件创建一标志位2FH.1,当输入引脚P3.6=0时,CPU置 位标志位2FH.1,而当P3.6=1时,CPU在读取时间差数 据后清零标志位2FH.1。

第3章 低频数字式相位测量仪的设计

2) (1)电路图如图3.6所示,该电路由单片机、整 形电路、门电路等组成。由定时器/计数器T0、T1分别 测量周期、时间差。

第3章 低频数字式相位测量仪的设计

待测信号 1 待测信号 2

A

D

整形 电路

2分 频

=1 C

&

整形 电路 B

MCU -51 INT0(P 3.2) ≥1 E P3.6

SUB1入 口 R4=4(R4是计 数器 )

P3.6= 1?

N

Y

2FH.1= 1?

N

Y

R4= 4?

Y

N

保存 周期 TH0、TL0 保存 时间 差 TH1、TL1

SETB 2FH.1

清零 定时 器 T0、T1 清0标志 位 2FH.1

R4- 1送 R4

N

R4= 0?

Y SUB1出 口

数字式相位差计

数字式相位差计数字式相位差计是一种专业的测量设备,用于精确测量电路中的相位差。

相位差是指两个信号之间的时间差或相位角度差。

在许多电子和通信应用中,准确测量相位差对于确保系统的稳定性和性能至关重要。

数字式相位差计的工作原理基于数字信号处理技术,它将输入信号转换为数字形式,并利用数字处理算法来计算相位差。

相比于传统的模拟相位差计,数字式相位差计具有更高的精度和稳定性。

数字式相位差计通常由两个主要部分组成:输入模块和数字处理单元。

输入模块负责接收和转换输入信号,通常采用模拟到数字转换器(ADC)将模拟信号转换为数字形式。

数字处理单元则利用数字信号处理算法来计算相位差,并将结果显示在数字显示屏上。

在数字处理单元中,常用的相位差计算算法包括FFT(快速傅里叶变换)算法和相关算法。

FFT算法通过将信号转换到频域进行计算,可以获得较高的精度和频率分辨率。

相关算法则通过计算信号的相关性来确定相位差,适用于某些特定的应用场景。

数字式相位差计的优势在于其高精度和灵活性。

由于数字处理算法的优化和数字信号处理器的高速运算能力,数字式相位差计可以实现非常高的测量精度。

另外,数字式相位差计通常具有更多的功能和选项,例如自动测量、数据存储和通信接口等,可以满足不同应用的需求。

数字式相位差计在许多领域中得到广泛应用,特别是在通信和雷达系统中。

在通信系统中,数字式相位差计可以用于测量信号的传输延迟和相位偏移,以确保数据的准确传输。

在雷达系统中,数字式相位差计可以用于测量目标的距离和速度,以实现精确的目标追踪和定位。

总之,数字式相位差计是一种专业的测量设备,具有高精度和灵活性。

它通过数字信号处理技术来实现对电路中相位差的准确测量,广泛应用于通信、雷达等领域。

随着技术的不断进步,数字式相位差计将在更多领域中发挥重要作用,并为电子和通信系统的发展提供支持。

数字相位测量系统设计

数字相位测量系统设计摘要本论⽂针对在个⼯业和民⽤场合,为了对各种低频信号进⾏分析,常常引⼊相位测量,⽽典型的传统⽅法是通过显⽰器测量,这种⽅法误差⽐较⼤﹑读数不⽅便等问题,本论⽂就此问题设计了⼀种数字相位测量仪对其进⾏相位时间间隔测量。

以单⽚机AT89C51为核⼼,⽤零⽐较器LM393将正弦波信号转换为⽅波,通过由D触发器组成的双稳态触发器实现两⽅波信号的相位差,将得到的信号经过模拟开关进⾏整幅,使之⾼电平为基准电压4.98V,低电平为0V,整幅后的波形经整流滤波形成直流电压,对不同的占空⽐输⼊直流电压在0V~4.98V,⽤16位A/D7705进⾏采样,可使其精度远⼤于设计要求的0.1°。

显⽰采⽤七段LED数码管,并⽤MAX7219作为显⽰器的驱动,对LED的亮度进⾏调节。

论⽂设计了相位⽐较电路、移相电路、显⽰电路、直流稳压电路。

系统采⽤软硬件结合的⽅式,测量精度⾼、稳定性好、操作简单,适合使⽤于各种需要的低频相位测量场合。

关键词:相位测量、相位时间间隔测量、单⽚机(AT89C51)Abstractanalyzed, This paper in a industrial and civil occasions, in order to all kinds of low frequency signal is often introducing phase measurement, the typical and traditional way is through display measuring, this kind of method error is bigger, reading is convenient wait for a problem of this issue, this paper designs a digital phasic measuring instrument for its phase time-interval measurement.With single-chip microcomputer AT89C51 as the core, with zero comparator LM393 will sine signals converts square-wave by D flip-flop, composed of bi-stable flip-flop reach two square wave signal of phase, will receive the signal for the whole picture after analog switch, make high level for the datum voltage 4.98 V, low level for 0V, whole picture after the formation of the waveform dc voltage rectifying filtering for different 390v input dc voltage in 0V ~ 4.98 V, with 16 A/D7705 sampling, can make its precision far outweigh the design requirements of 0.1 °. LED digital display using seven section, and MAX7219 as monitor tube to drive, LED the brightness of the adjusted. Paper designed a phase comparison circuit, phase shifting circuit, display circuit, dc voltage circuit. System adopts hardware and software combination way, high accuracy, good stability, simple operation, and suitable for use in various needs of low-frequency phase difference measurement occasion.keywords: Phase difference measurement Phase time-interval measurement SCM(AT89C51)⽬录1.绪论 (5)1.1 国内外相位检测技术的发展现状 (5)1.2 本课题研究的主要内容 (6)1.3 本课题研究的⽬的和意义 (7)2.低频数字相位测量系统的总体⽅案设计 (8)2.1相位的基本概念 (8)2.2相位测量的技术指标 (8)2.3系统任务需求分析 (9)2.3.1课题要求 (9)2.3.2发挥部分 (9)2.4相位测量的原理 (9)2.5 设计⽅案的⽐较论证 (10)2.6单⽚机AT89C51功能简介 (12)2.6.1主要性能功能参数 (12)2.6.2 AT89C51特性功能概述 (13)3.相位测量硬件的设计 (14)3.1 系统总体结构的设计 (14)3.2 相位⽐较电路的设计 (14)3.3 A/D转换电路的设计 (15)3.4 键盘与显⽰电路的设计 (16)3.4.1主要性能 (16)3.4.2引脚功能 (16)3.4.3⼯作时序及转换原理 (16)3.4.4 AD7705数字接⼝及电路 (17)3.4.5⽚内寄存器 (18)3.5直流电源电路的设计 (20)3.6芯⽚MAX7219的简介 (20)3.6.1MAX7219的性能 (20)3.6.2管脚配置 (20)3.6.3典型应⽤电路 (22)3.6.5读写时序说明 (23)3.7直流电源电路的设计 (23)4.移相⽹络电路设计与参数计算 (25)5.1移相⽹络电路 (25)5.2移相⽹络参数设计 (25)5.3数字移相信号发⽣器 (27)5.系统软件流程设计 (30)结论 (31)致谢 (32)参考⽂献 (33)1. 绪论1.1国内外相位测量技术的发展现状现代相位测量技术的发展可分为三个阶段:第⼀阶段是在早期采⽤的如李沙育法、阻抗法、和差法、三电压法等,这些测量⽅法通常采⽤⽐对法和平衡法,虽然⽅法简单,但测量精度较低;第⼆阶段是利⽤数字专⽤电路、微处理器等来构成测试系统,使测量精度得以⼤⼤提⾼;第三阶段是充分利⽤计算机及智能化测量技术,从⽽⼤⼤简化设计程序,增强功能,使得响应的产品精度更⾼、功能更全。

基于单片机和CPLD的数字相位测量仪设计

测 量输 入 与输 出信 号 问 的相 差 △p以便 确 定 线性 控 制 的 范 围 。 ( , 常用 到的 一 般 测

量 工具 , 比如 在 电力 系统 中 电 网 并 网合 闸时 , 求 两 电 网 的电 信 要

号 相 同 , 就 要 求精 确 的 测 量 两工 频 信 号 之 间 的相 位 差 。 有 测 这 还

形, 电路 图如 图 2所 示 。 密 特触 发 器 在单 门限 电压 比较 器 的基 施

础 上 加 入 了 正反 馈 网 络 , 以 有 效提 高抗 干 扰 能 力 , 而 避 免 信 可 从

的 相位 。通 常所 谓 相 位 测量 是 指 对 两 个 同 频 率 信号 之 间 相 位 差

的 测量 。相 位 的 测 量很 重 要 , 测 某元 件 的阻 抗 Z 厶 因 此 如 = ,

姚 晖 李 伟 季上 满 沈科杰 胡 娅 ( 浙江理工大学信息电子学院, 浙江 杭州 30 1 ) 10 8

摘 要

介 绍 了数 字 式低 频 相 位 测量 仪 的 组成 、 作原 理 , 出 了一 种基 于单 片机 和 可编 程 逻辑 器件 的 低频 数 字相 位 测 量 仪 的 工 提 设 计 方 案。 系统 以 A 8 C 2单 片机 小 系统 及 Al r 司 的 E M7 2 S C8 — 5 C L 为核 心 , 频 率 为 2 H T9 5 t a公 e P 18 L 4 1 P D 对 0 z到 2 k z 0H 的 正 弦 波信 号 实现 精 确 测 频 、 相 , 用 以 8 7 测 并 2 9为 核 心 的键 盘 显 示 电路 给 以显 示 。 对 测 周 误 差进 行 了改进 分 析 。 设 计 还 该

Ke wors: a e m e s e, y d ph s a ur MCU, CPL f D,equ nc ,ror r e ye r

模电课程设计——数字式相位差测量仪

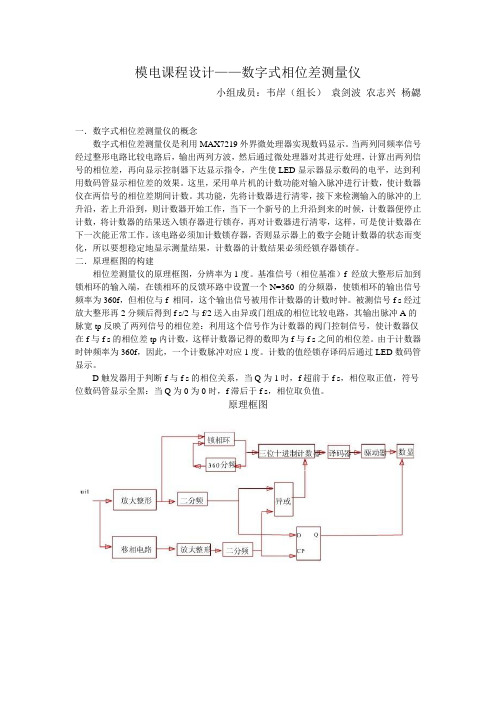

模电课程设计——数字式相位差测量仪小组成员:韦岸(组长)袁剑波农志兴杨勰一.数字式相位差测量仪的概念数字式相位差测量仪是利用MAX7219外界微处理器实现数码显示。

当两列同频率信号经过整形电路比较电路后,输出两列方波,然后通过微处理器对其进行处理,计算出两列信号的相位差,再向显示控制器下达显示指令,产生使LED显示器显示数码的电平,达到利用数码管显示相位差的效果。

这里,采用单片机的计数功能对输入脉冲进行计数,使计数器仪在两信号的相位差期间计数。

其功能,先将计数器进行清零,接下来检测输入的脉冲的上升沿,若上升沿到,则计数器开始工作,当下一个新号的上升沿到来的时候,计数器便停止计数,将计数器的结果送入锁存器进行锁存,再对计数器进行清零,这样,可是使计数器在下一次能正常工作。

该电路必须加计数锁存器,否则显示器上的数字会随计数器的状态而变化,所以要想稳定地显示测量结果,计数器的计数结果必须经锁存器锁存。

二.原理框图的构建相位差测量仪的原理框图,分辨率为1度。

基准信号(相位基准)f 经放大整形后加到锁相环的输入端,在锁相环的反馈环路中设置一个N=360 的分频器,使锁相环的输出信号频率为360f,但相位与f 相同,这个输出信号被用作计数器的计数时钟。

被测信号f s经过放大整形再2分频后得到f s/2与f/2送入由异或门组成的相位比较电路,其输出脉冲A的脉宽tp反映了两列信号的相位差:利用这个信号作为计数器的阀门控制信号,使计数器仅在f与f s的相位差tp内计数,这样计数器记得的数即为f与f s之间的相位差。

由于计数器时钟频率为360f,因此,一个计数脉冲对应1度。

计数的值经锁存译码后通过LED数码管显示。

D触发器用于判断f与f s的相位关系,当Q为1时,f超前于f s,相位取正值,符号位数码管显示全黑:当Q为0为0时,f滞后于f s,相位取负值。

原理框图三.电路原理图四.使用元件原理介绍(1)放大电路本设计采用的是LM324运算放大器,如下图:通过使用LM324运放器,我们可以使正弦波转变为方波。

基于DSP的低频数字式相位测量仪的设计

随着科学技 术的突飞猛进的发展, , 电 技 T 30 C 4 2 A 8S 2 MS 2 V 50 和 T 9 5 芯片的集成度高 、

智能 程 度 高 、功 能 强 大 ,使得 它实 现 起 来 比较

教 ,研 究方 向 为移 动 术 广 泛 的 应用 T工 、 、农 、 、交通 运 输 、航 I I

究网络 、系统的频率特性 中具有重 受意义。近 果。系统框 图如图 i 所示。

图 1低 频 数 字 式 相位 该 系统 以T 30 C 4 2 核心 , 待 测 MS 2 V 5 0 为 对

测量仪 系统框图

量信 号进行 采集 和处理 ,包括 栏彤和移 相电

路 ,把 采 集米 的 模 拟 信 号转换 为数 字 信 。其

湖南工学院 俞斌 贾雅琼 汤群芳 摘 要: 本 文提 出了一种 基于 T 3 0 C 4 2的低 频数字 式相位测 年来 ,随着科学技术的迅速发展 ,很多测量仪 MS 2 V 5 0

量仪 的设计方法。

逐渐 向 “ 智能仪器”和 “ 自动测试 系统”发展 , 这使得仪 器的使 _ 比较简单 ,功能越来越多。 } H

本低 频 数 字 式 相 位 测 量 仪 由 T 30 C 4 2 MS 2 V 5 0 、

关键 词 : DS ;低频 ;数字 式;相位 测量 ;S M P C

苯 06 文20 年

月2日收到。 俞斌 : 助

0 吉 |

AT8 2和 小 规 模 集 成 电 路 构 成 。 由 于 9S 5

通信、单片机和 DS 航天、国防建设 等国民经济的诸 多领域 中,而 简单 ,而且 ,具有体积小 、性价比高、性能稳 P

应 用。 电子 测量 技 术 又 是 电子 技 术 中进 行 信 息 检 测 的 定 的特 点 。

低频率数字相位差测量仪设计

引言相位差测量数字化的优点在于硬件成本低、适应性强、对于不同的测量对象只需要改变程序的算法,且精度一般优于模拟式测量。

在电工仪表、同步检测的数据处理以及电工实验中,常常需要测量两列同频率信号之间的相位差。

例如,电力系统中电网并网合闸时,需要求两电网的电信号的相位差。

相位差测量的方法很多,典型的传统方法是通过示波器测量,这种方法误差较大,读数不方便。

为此,我们设计了一种基于锁相环倍(分)频的相位差测量仪,该仪器以锁相环倍(分)频电路为核心,实现了工频信号相位差的自动测量及数字显示。

论文摘要本系统为低频数字式相位/频率测量仪,由移相网络模块、相位差测量模块及频率测量模块三大部份构成,其系统功能主要是进行相位差测量及频率测量。

移相网络主要是由RC移相电路和LM324运放电路组成,将被测信号送入移相网络,经RC移相、LM324隔离放大,产生两路信号,一路为基准信号经过波形转换,另一路为移相后的信号。

分别经过波形转换、整形、二分频送给相位测量模块及频率测量模块。

相位差测量仪主要是由锁相环PLL(Phase Lock Loop)产生360倍频基准信号和移相网络的基准信号与待测信号进行异或后的信号作为显示器的闸门电路和控制信号。

频率测量模块主要是用计数法测量频率的,它是有某个已知标准时间间隔Ts内,测出被测信号重复出现的次数N,然后计算出频率f=N/Ts.显示电路模块主要是由计数器、锁存器、译码器和数码管组成。

低频率数字相位测量仪目录1设计任务书 (3)2设计方案概述 (3)3系统的组成………………………………………………………………………………4.3.1总体框图 (4)3.2移相网络部分 (4)3.3相位测量部分 (6)1)波形转换、整形放大 (8)2)锁相环倍频 (9)3)闸门电路 (11)4)控制门 (11)5)计数器 (11)6)锁存器 (11)7)显示译码器与数码管 (11)3.4频率测量部分 (12)1)数字频率计的基本原理 (12)2)系统框图 (12)4附录………………………………………………………………………一、设计任务书(一)任务设计仿真一数字相位计(二)主要技术指标与要求:(1)输入信号频率为1KHZ~20KHZ可调(2)输入信号的幅度为10mV(3)采用数码管显示结果,相位精确到0.1°(4)采用外部5V直流电源供电(三)对课程设计的成果的要求(包括图表)设计电路,安装调试或仿真,分析实验结果,并写出设计说明书。

数字式相位差测量系统(基于51单片机)

数字相差检测仪的制作专业:电气班级:XX班学号:XXXXXXXXXX 学生姓名:XXX指导教师:XX目录摘要: ............................................................................................................... 错误!未定义书签。

Abstract: ............................................................................................................. 错误!未定义书签。

第一章绪论. (5)1.1 测量相位差的作用和意义 (5)1.2 相位差测量的研究现状 (5)1.3本课题研究的主要内容 (7)第一章:最小二乘法以及快速傅里叶变换简介 (8)1.1:最小二乘法简介 (8)2.1 主程序流程图 (12)2.2位倒序算法实现 (12)2.4 FFT算法的实现 (13)2.5 AD采样的使用 (14)2.6 定时器的使用 (15)第三章:硬件电路设计 (17)3.1 移相电路的设计 (17)3.2 电压跟随器模块 (17)3.4 电源电路 (18)3.4.1 变压器简介 (18)3.4.2 单相全桥整流电路 (19)结论 (20)致谢 ................................................................................................................... 错误!未定义书签。

参考文献(Reference).. (21)附录: (22)基于最小二乘法的低频数字相位差检测仪的研究摘要:常见的相位差检测方法一般是过零法,通过外部硬件电路对正弦信号的零点进行检测,产生的脉冲信号出发MCU的外部中断,通过MCU的定时器计算出信号的频率以及相位差。

相位差测量电路设计

本科毕业设计( 2015 届 )题目:相位差测量电路的设计学院:机电工程学院专业:自动化学生姓名:学号:指导教师:职称(学位):讲师合作导师:职称(学位):完成时间:2015 年 5 月 28日成绩:黄山学院教务处制原创性声明兹呈交的设计作品,是本人在指导老师指导下独立完成的成果。

本人在设计中参考的其他个人或集体的成果,均在设计作品文字说明中以明确方式标明。

本人依法享有和承担由此设计作品而产生的权利和责任。

声明人(签名):年月日目录摘要 (1)英文摘要 (2)1 绪论 (2)1.1 研究背景及意义 (3)1.2 发展现状和发展趋势 (3)1.2.1 国外发展状况 (3)1.2.2 国内发展状况 (4)1.2.3 发展趋势 (5)2 相位差测量的基本原理 (5)2.1 相位的基本概念 (5)2.2 相位差测量原理 (5)2.3 电路设计原理 (6)3 设计与分析 (6)3.1 移相电路 (6)3.1.1 方案分析 (6)3.1.2 移相电路设计 (8)3.2 检测电路 (8)3.2.1 方案分析 (8)3.2.2 检测电路设计 (11)3.2.3 LM339特性分析 (12)3.2.4 双稳态触发器 (13)3.3 计数显示电路 (14)3.3.1 方案分析 (14)3.3.2 计数显示电路设计 (14)3.3.3 数码管工作原理 (15)4 仿真与调试 (16)5 实验分析 (18)总结 (19)参考文献 (20)致谢.................................................................................................错误!未定义书签。

附录 (21)相位差测量电路设计机电工程学院自动化专业指导老师:(讲师)摘要: 随着计算机以及电子技术的发展,相位差测量技术作为常用的信号测量技术,得到了快速发展,已经成为现代科学研究不可或缺的一部分。

数字式相位测量仪

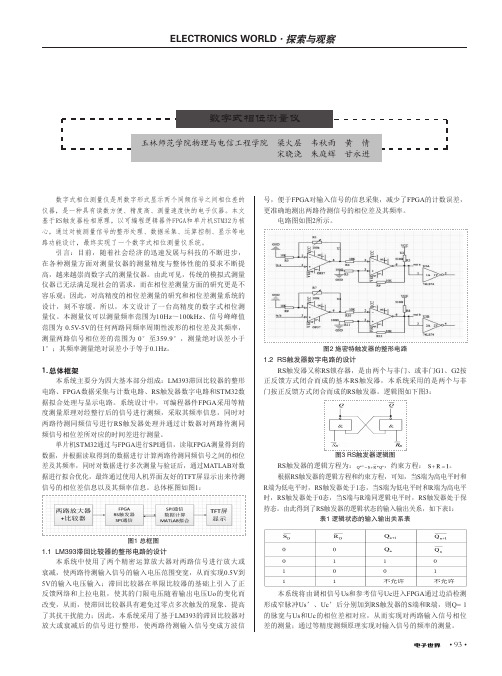

• 93•数字式相位测量仪是用数字形式显示两个同频信号之间相位差的仪器,是一种具有读数方便、精度高、测量速度快的电子仪器。

本文基于RS触发器检相原理,以可编程逻辑器件FPGA和单片机STM32为核心,通过对被测量信号的整形处理、数据采集、运算控制、显示等电路功能设计,最终实现了一个数字式相位测量仪系统。

引言:目前,随着社会经济的迅速发展与科技的不断进步,在各种测量方面对测量仪器的测量精度与整体性能的要求不断提高,越来越崇尚数字式的测量仪器。

由此可见,传统的模拟式测量仪器已无法满足现社会的需求,而在相位差测量方面的研究更是不容乐观;因此,对高精度的相位差测量的研究和相位差测量系统的设计,刻不容缓。

所以,本文设计了一台高精度的数字式相位测量仪。

本测量仪可以测量频率范围为10Hz ~100kHz 、信号峰峰值范围为 0.5V-5V 的任何两路同频率周期性波形的相位差及其频率,测量两路信号相位差的范围为 0°至359.9°,测量绝对误差小于1°;其频率测量绝对误差小于等于0.1Hz 。

1.总体框架本系统主要分为四大基本部分组成:LM393滞回比较器的整形电路、FPGA 数据采集与计数电路、RS 触发器数字电路和STM32数据拟合处理与显示电路。

系统设计中,可编程器件FPGA 采用等精度测量原理对经整行后的信号进行测频,采取其频率信息,同时对两路待测同频信号进行RS 触发器处理并通过计数器对两路待测同频信号相位差所对应的时间差进行测量。

单片机STM32通过与FPGA 进行SPI 通信,读取FPGA 测量得到的数据,并根据读取得到的数据进行计算两路待测同频信号之间的相位差及其频率,同时对数据进行多次测量与验证后,通过MATLAB 对数据进行拟合优化,最终通过使用人机界面友好的TFT 屏显示出来待测信号的相位差信息以及其频率信息。

总体框图如图1:图1 总框图1.1 LM393滞回比较器的整形电路的设计本系统中使用了两个精密运算放大器对两路信号进行放大或衰减,使两路待测输入信号的输入电压范围变宽,从而实现0.5V 到5V 的输入电压输入;滞回比较器在单限比较器的基础上引入了正反馈网络和上拉电阻,使其的门限电压随着输出电压Uo 的变化而改变,从而,使滞回比较器具有避免过零点多次触发的现象、提高了其抗干扰能力;因此,本系统采用了基于LM393的滞回比较器对放大或衰减后的信号进行整形,使两路待测输入信号变成方波信号,便于FPGA 对输入信号的信息采集,减少了FPGA 的计数误差,更准确地测出两路待测信号的相位差及其频率。