数字相位差测量仪的设计

相位差测量电路的设计

Abs t r a c t

Th e t r adi t i on a l m u l t i -ph as e me t e r n ee d t o f i l m a s ma l l s c al e i n t egr a t e d ci r cu i t s , n o t on l y t he ac cu r a c y of ph a s e di fer — e n ce mea s ur emen t c i r cu i t co m pl e xi t y i s n ot h i gh , an d t h e n ar r o w r an ge of f r equ en ci e s u s ed, S O i n pr a c t i c e t h er e ar e dr a w—

时 刻 和终 了 时刻 的准 确 性 上 存 在 有 问 题 。 主 要表 现在 : 定 时 器 从 应 该 开始 计 时到 实 际开 始 计 时 存 在 有 时 间差 ,即 出 现 了计 时 延

图 2 带 通滤 波器

2 . 2 信 号 比较 环 节 信 号 经过 带通 滤 波 器 滤 掉 高 频 干 扰 和 低 频 漂 移 信 号 并 进 行

1 3 2 相 位 差源自测 量 电 路 的 设 计 相位差测量 电路的设计

De s i gn o f Ci r c u i t i n Ph a s e Di f f e r e n c e Me a s u r e me n t

刘龙 飞 王根 岭 肖培 如 ( 浙江理工大学信息电子学院, 浙江 杭州 3 1 0 0 1 8 )

摘 要

传 统 的相 位 差 测 量仪 需要 采 用 多片 中 小规 模 集成 电路 , 不 仅 电路 复 杂 , 测 量 相 位 差 的精 度 不 高 , 而且 使 用 的 频 率 范 围

数字相位差课程设计 中北大学

测控电路设计专业:测控技术与仪器班级:11050341姓名:学号:数字相位差测量仪的设计1.设计思路相位差测量仪主要是由锁相环PLL产生3600倍频基准信号和移相网络的基准信号与待测信号进行异或后的信号作为计数显示器的控制信号。

2.设计方案2.1方案设计将被测信号送入移相网络,经RC移相、LM324隔离放大,产生两路信号,一路为基准信号经过波形转换,另一路为移相后的信号。

分别经过波形转换、整形、二分频送给相位测量模块。

基准信号fr经过放大整形后加到锁相环的输入端,锁相环的反馈环路中设置一个N=3600的分频器构成一个3600倍频器,使输入的基准信号fr经过锁相环后频率变为原来的3600倍,但相位与基准信号fr 相同,输出信号用做计数器的时钟基准信号。

被测信号fs经过放大整形并二分频得到的二分频信号与基准信号fr的二分频信号经过二输入异或门得到的输出信号作为计数控闸门制信号,使计数器仅在基准信号fr与被测信号的相位差间隔内计数,计数器计的数值即为基准信号fr与被测信号fs的相位差。

2.2 设计原理框图图1 原理框图由原理方框图可以看出,所要设计的电路的主要由移相网络、放大整形、倍频、计数显示四大部分构成。

下面将从这三大部分着手设计电路3.电路设计3.1移相网络部分图2 移相电路移相网络是由二节RC超前或滞后移相网络、集成运算放放大器组成的电压跟器和运放组成的。

一节RC电路如图所示。

由它的相量图可知超一个相角φ,,当f →0时,φ→90°;f →∞时,φ→0。

这说明:一节RC 电路最大相移不超过90°,不能满足相位平衡条件。

若两节RC电路最大相移虽可接近180°,但此时频率必须很低,从而容抗很大,致使输出电压接近于零,所以本电路又加了电压跟随器和放大器。

3.2放大整形电路在设计这个部分的电路时,要考虑到不能使基准信号和被测信号不发生相对相位移动的问题,基准信号和被测信号在设计的放大整形电路中所引起的附加移相是相等的,所以原理方框图A1和A2要用相同的电路。

电气电子毕业设计100竞赛论文——低频数字式相位测量仪

电子竞赛——低频数字式相位测量仪目录摘要 (1)一.设计任务与设计要求 (2)1.1 设计任务 (2)1.2 设计要求 (2)1.2.1 基本要求 (2)1.2.2 发挥部分 (2)二.相位测量 (2)2.1相位测量方案选择与论证 (3)2.2相位测量框图 (3)2.3相位测量硬件电路设计与器件选择 (3)2.3.1 相位比较电路 (4)2.3.2 CPU与外围电路 (5)2.3.3键盘与显示电路 (6)2.3.4直流稳压电源电路 (6)2.4 测试方法与测试结果 (7)2.4.1 相位测试方法 (7)2.4.2相位测试结果 (7)2.4.3测量工具 (7)三.频率测量方案 (7)3.1 方案选择与论证 (7)3.2 硬件电路设计 (9)3.3 频率测量测试及结果 (9)3.4 测量工具 (10)四.移相网络电路参数计算 (10)4.1移相网络电路框图 (10)4.2移相网络电路参数计算 (10)4.3 移相网络测试 (12)4.4 测量工具 (12)五.发挥部分数字移相信号发生器 (12)5.1方案论证 (12)六.系统软件设计 (15)七.总的结果分析 (16)八.结论 (16)附录:移相信号发生器电路 (17)10-03设计题目:低频数字式相位测量仪参赛队员:刘传登韩春鹏王忠杰指导教师:车新生摘要本设计实现的是对两列信号的相位差的精确测量并数字显示测量结果。

为达到要求的精度本设计采用了将相位转换为直流电压的间接测量方法。

用16位A/D对输出的直流电压进行采样,送入单片机进行相位显示。

这样就使得相位差就具有足够高的分辨度,完成了任务要求。

在单片机P89C51实现以上功能的同时,利用单片机中的多位计数器/定时器对输入信号进行等精度频率测量。

为测量方便,又制作了移相网络电路,设计了移相信号电路和应用程序。

整个装置具有原理简单,测量精度高,测量范围宽,测量结果显示直观的特点。

关键词:相位测量等精度测量移相网络一.设计任务与要求1.1设计任务设计并制作一台低频相位测量系统,包括相位测量仪,数字式移相信号发生器和移相网络三部分。

CPLD低频数字相位测量仪的设计

包括数字移相信 号发生 器和相位 测量仪 2 部分 , 分别 完成移相信号的发生 、 频率 与相位差 的预置、 数字显示、 号的移相 以 信

及移相后信 号相位差和频率 的测量 与相识 等功能。 中数字 式移 相信号发生 器可 以产 生预置频率 的差值 ; 其 相位 测量仪可

以测量和显 示相位信 号的频率 、 位 差。 相

厂一

后, 将波形整形电路的2 0 ] 厂 厂 厂 厂 ] ]

图 1 波形变换 示意 图

的功能, 用以产生相位测量仪所需的输入正弦信号 。 其

技术 要 求 指标 : 率 范 围2 Hz~ 0 Hz 频 率 步进 为 频 0 2k ,

2H , 0 z 输出频率可预置; 相位差范围为0 3 9 , ~ 5 。相位差

( 具有设定保存功能。 5)

实现相位 、 频率的测量, 并且具有独 自的控制功能和数

字显示 功能。

11系统硬件 结构 .

首 先 将 被 测 2列 正

弦 信号 A 、 B经平 滑 滤 波

后 , 入 过 零 比较 电路 , 输

A

1系统硬件设计

总体要求 : ( ) 有相 位 测量 功 能 , 1具 即相 位 测量 仪 的 功 能 。 其

传 感 及 检 测 仪 表

C L 低频 数 字 相 位 测 量 仪 的设 计 PD

朱 红梅 , 美 君 潘

( 海西部矿 业铅业 摘

要: 绍 了一种基 于复杂的可编程逻辑 器件( L 和 高速 单片机s c8 c 8 介 CP D) T 9 5 的低频数字 相位 测量仪 。 该测量仪

京航 天航 空 大 学 出版 社 【] 白英 彩 . 型 计 算 机 常 用 芯 片 手 册 【 . 海 : 海科 学 3 微 M】 上 上

数字式相位测量仪

• 93•数字式相位测量仪是用数字形式显示两个同频信号之间相位差的仪器,是一种具有读数方便、精度高、测量速度快的电子仪器。

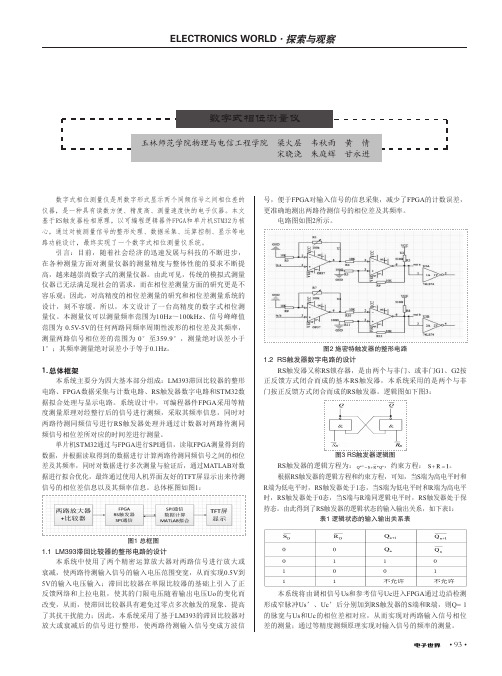

本文基于RS触发器检相原理,以可编程逻辑器件FPGA和单片机STM32为核心,通过对被测量信号的整形处理、数据采集、运算控制、显示等电路功能设计,最终实现了一个数字式相位测量仪系统。

引言:目前,随着社会经济的迅速发展与科技的不断进步,在各种测量方面对测量仪器的测量精度与整体性能的要求不断提高,越来越崇尚数字式的测量仪器。

由此可见,传统的模拟式测量仪器已无法满足现社会的需求,而在相位差测量方面的研究更是不容乐观;因此,对高精度的相位差测量的研究和相位差测量系统的设计,刻不容缓。

所以,本文设计了一台高精度的数字式相位测量仪。

本测量仪可以测量频率范围为10Hz ~100kHz 、信号峰峰值范围为 0.5V-5V 的任何两路同频率周期性波形的相位差及其频率,测量两路信号相位差的范围为 0°至359.9°,测量绝对误差小于1°;其频率测量绝对误差小于等于0.1Hz 。

1.总体框架本系统主要分为四大基本部分组成:LM393滞回比较器的整形电路、FPGA 数据采集与计数电路、RS 触发器数字电路和STM32数据拟合处理与显示电路。

系统设计中,可编程器件FPGA 采用等精度测量原理对经整行后的信号进行测频,采取其频率信息,同时对两路待测同频信号进行RS 触发器处理并通过计数器对两路待测同频信号相位差所对应的时间差进行测量。

单片机STM32通过与FPGA 进行SPI 通信,读取FPGA 测量得到的数据,并根据读取得到的数据进行计算两路待测同频信号之间的相位差及其频率,同时对数据进行多次测量与验证后,通过MATLAB 对数据进行拟合优化,最终通过使用人机界面友好的TFT 屏显示出来待测信号的相位差信息以及其频率信息。

总体框图如图1:图1 总框图1.1 LM393滞回比较器的整形电路的设计本系统中使用了两个精密运算放大器对两路信号进行放大或衰减,使两路待测输入信号的输入电压范围变宽,从而实现0.5V 到5V 的输入电压输入;滞回比较器在单限比较器的基础上引入了正反馈网络和上拉电阻,使其的门限电压随着输出电压Uo 的变化而改变,从而,使滞回比较器具有避免过零点多次触发的现象、提高了其抗干扰能力;因此,本系统采用了基于LM393的滞回比较器对放大或衰减后的信号进行整形,使两路待测输入信号变成方波信号,便于FPGA 对输入信号的信息采集,减少了FPGA 的计数误差,更准确地测出两路待测信号的相位差及其频率。

第3章+低频数字式相位测量仪的设计

图3.3 用测周期的方法获得信号频率

第3章 低频数字式相位测量仪的设计

2) 鉴相器就是异或门,在鉴相器的输出波形IV中, 正脉冲宽度就是要测量的I和V 相位差所对应的时间差 Tθ ,如图3.4所示。

第3章 低频数字式相位测量仪的设计

I V

IV

图3.4 鉴相器的输入、输出波形图

第3章 低频数字式相位测量仪的设计

F INT1(P 3.3)

图3.6 MCU测量时间差、周期的电路图

第3章 低频数字式相位测量仪的设计

(2) 时序图如图3.7所示。需要说明的是,由软 件创建一标志位2FH.1,当输入引脚P3.6=0时,CPU置 位标志位2FH.1,而当P3.6=1时,CPU在读取时间差数 据后清零标志位2FH.1。

第3章 低频数字式相位测量仪的设计

2) (1)电路图如图3.6所示,该电路由单片机、整 形电路、门电路等组成。由定时器/计数器T0、T1分别 测量周期、时间差。

第3章 低频数字式相位测量仪的设计

待测信号 1 待测信号 2

A

D

整形 电路

2分 频

=1 C

&

整形 电路 B

MCU -51 INT0(P 3.2) ≥1 E P3.6

SUB1入 口 R4=4(R4是计 数器 )

P3.6= 1?

N

Y

2FH.1= 1?

N

Y

R4= 4?

Y

N

保存 周期 TH0、TL0 保存 时间 差 TH1、TL1

SETB 2FH.1

清零 定时 器 T0、T1 清0标志 位 2FH.1

R4- 1送 R4

N

R4= 0?

Y SUB1出 口

应用8051单片机IP设计相位测量仪

应用8051单片机IP设计相位测量仪摘要:本设计应用SOPC和8051单片机IP技术,设计一个高精度的相位差测量仪。

通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机,既节省了成本又充分利用FPGA内部资源。

关键词:相位测量仪SOPC 8051单片机IPAbstract:The design of Frequency Phase Measurement System is presented based on 8051 IP Core and FPGA.8051 IP Core,which embed in the FPGA,to replace the extra 8051 of the existing MCU+FPGA solution,saving the cost and make full use of FPGA internal resources.Key Words:Frequency Phase Measurement System;SOPC;8051 IP Core相位差测量技术发展至今已深入到电子技术、工业自动化、智能控制及通信等众多领域。

因此,设计一个高精度的相位差测量仪显得十分重要。

当前国内的一般的解决方案是单片机+FPGA方案,其中FPGA完成高速的脉冲计数功能,而单片机则进行脉冲计数后的有关计算和LCD显示等的控制。

此方案中的FPGA内部资源往往利用不足,造成比较大的浪费。

本设计应用SOPC和8051单片机IP技术,通过在FPGA中嵌入8051单片机IP来取代单片机+FPGA方案中的实际的单片机。

既少用一个实际的单片机又充分利用FPGA内部资源,大大节省了硬件的成本。

1 8051单片机IP核简介常见的8051单片机IP有开源免费的和工业级收费的两类,一般都具有以下特点。

脉宽测量模块用来测量占空比待测信号的高、低电平脉宽时间,用VHDL语言设计,由FPGA实现。

低频数字式相位测试仪的设计与实现

低频数字式相位测试仪的设计与实现尹晓慧;陈劲;张宝菊;王为【摘要】基于过零检测法,以微控制器ATmega 128和可编程逻辑器件EPM1270为核心,设计并实现了对双路同频低频信号的相位差和频率进行测量的系统.在一个可编程逻辑器件(Complex Programmable Logic Device,CPLD)内实现了数字式相位差和频率的数据采集,简化了系统设计.系统可以对200 Hz~10 kHz频率范围内的信号进行相对精确的测量,与传统相位测量仪相比,具有硬件电路简单、测量速度快和易于实现等优点.【期刊名称】《天津师范大学学报(自然科学版)》【年(卷),期】2012(032)001【总页数】4页(P39-42)【关键词】相位测量;频率测量;CPLD;微控制器;液晶显示【作者】尹晓慧;陈劲;张宝菊;王为【作者单位】天津师范大学物理与电子信息学院,天津300387;天津师范大学物理与电子信息学院,天津300387;天津师范大学物理与电子信息学院,天津300387;天津师范大学物理与电子信息学院,天津300387【正文语种】中文【中图分类】TM932在电子测量技术中,相位测量是最基本的测量手段之一,相位测量仪是电子领域的常用仪器.随着相位测量技术广泛应用于国防、科研和生产等各个领域,对相位测量的要求也逐步向高精度、高智能化方向发展.在低频范围内,相位测量在电力和机械等部门具有非常重要的意义[1],目前相位测量主要运用等精度测频和锁相环(Phase Locked Loop,PLL)测相等方法.研究发现,等精度测频法具有在整个测频范围内保持恒定高精度的特点,但该原理不能用于测量相位[2].PLL测相可以实现等精度测相,但电路调试较复杂.因此,本研究选择直接测相法作为低频测相仪的测试方法.对于低频相位的测量,使用传统的模拟指针式仪表显然不能满足所需的精度要求,随着电子技术和微机技术的发展,数字式仪表因其高精度的测量分辨率以及高度智能化、直观化的特点得到越来越广泛的应用因此,本研究设计并实现了以CPLD和微控制器(Micro Control Unit,MCU)为核心的低频数字式相位测量仪.相位差测量的基本原理有3种:对信号波形的变换比较、对傅氏级数的运算和对三角函数的运算[2-3].3种原理分别对应过零检测法、倍乘法和矢量法3种测量相位差的方法.过零点检测法是一种将相位测量变为时间测量的方法,其原理是将基准信号的过零时刻与被测信号的过零时刻进行比较,由二者之间的时间间隔与被测信号周期的比值推算出两信号之间的相位差.这种方法的特点是电路简单,且对启动采样电路要求不高,同时还具有测量分辨率高、线性好和易数字化等优点.任何一个周期函数都可以用傅氏级数表示,即用正弦函数和余弦函数构成的无穷级数来表示,倍乘法测量相位差所用的运算器是一个乘法器,2个信号是频率相同的正弦函数,相位差为φ,运算结果经过一个积分电路,可以得到一个直流电压V=k cosφ,电路的输出和被测信号相位差的余弦成比例,因此其测量范围在45°以内,为使测量范围扩展到360°,需要附加一些电路才可以实现.倍乘法由于应用了积分环节,可以滤掉信号波形中的高次谐波,有效抑制了谐波对测量准确度的影响. 任何一个正弦函数都可以用矢量来表示,如各个正弦信号幅度相等、频率相同,运算器运用减法器合成得到矢量的模V=2E sinφ/2.矢量法用于测量小角度范围时,灵敏度较好,可行度也较高;但在180°附近灵敏度降低,读数困难且不准确.由于系统输出为一余弦或正弦函数,因此这种方法适用于较宽的频带范围[1].上述3种测量相位的方法各有优势,从测量范围、灵敏度、准确度、频率特性和谐波的敏感性等技术指标来看,过零检测法的输出正比于相位差的脉冲数,且易于实现数字化和自动化,故本研究采用过零检测法.采用过零检测法需要对被测信号的周期进行测量,由于信号的周期与频率之间呈倒数关系,本研究采用测量被测信号频率的方法实现对其周期的测量.频率测量的方法很多,可分为2大类:第1类是单位时间内测量脉冲周期的方法,这种方法的优势是能够用标准的基准单位时间对被测信号时钟进行脉冲测量,简单方便,容易实现,但是由于使用了基准的单位时间,所以测量脉冲时,如果被测信号的周期接近基准时钟的周期,测量的准确度就会下降,精度难以得到保障,所以这种方法只适合于测量高频信号,或者说这种方法只适合于基准时钟周期比被测信号周期大得多的情况;第2类测量方法是使用高频时钟对被测信号的单个时钟周期进行高频计数,这种方法的优点是使用高频时钟对被测信号的单个时钟周期进行高频计数可以在一个被测信号周期内完成对频率的测量,对于低频被测信号具有较高的精度,但设计较为复杂.本研究所涉及的频率测量范围为200 Hz~10 k Hz,属于低频信号,因此可以采用高频时钟的方法对频率进行测量.每种测量方法均存在2种具体的测量手段:一种是利用专用频率计模块来测量频率,如ICM7216芯片,其内部自带放大整形电路可以直接输入正弦信号,外部振荡电路部分选用由一块高精度晶振和2个低温度系数电容构成的10 MHz振荡电路,其转换开关具有0.01 s、0.1 s、1 s和10 s共4种闸门时间,量程可以自动切换,待计数过程结束时显示测频结果;另一种方法是利用CPLD和MCU来实现频率的测量,将被测信号通过模拟电路转换为方波信号输入EPM1270的某一I/O端口,在CPLD内部实现频率的采集,最后将计数值送入MCU处理并输出至液晶予以显示.比较2种测量手段,利用实验室现有条件,本研究采用CPLD和MCU实现对被测信号频率的测量.利用单片机控制计数器工作,硬件简单且频率测量精度高,这是目前较为成熟的一种高精度测频方案.系统的设计目标是实现双路同频率正弦波信号相位差和频率的测量.本研究采用数字鉴相技术在保持模拟式相位测试优势的同时,提出并实现了一种基于CPLD的低频数字式相位测试仪.该系统主要由数据采集电路、数据运算控制电路和数据显示电路3部分构成,采用CPLD和AVR单片机相结合构成整个系统的测控整体.CPLD主要负责数据采集,单片机负责读取CPLD采集的数据,再根据这些数据作出相应计算,并通过液晶将结果显示出来.系统在保持模拟式相位测试优点的同时,具有抗干扰能力强、外围电路简单和易于实现等优点[4-5].测量相位差的具体方法为:先通过比较电路将两路同频率正弦信号分别转换为相应的脉冲信号将其中一路信号直接送入D触发器,作为触发信号;另一路信号通过反相器取反后与复位信号相与,将得到的结果送入D触发器的清零端,由D触发器输出一脉冲信号,此脉冲波形的脉宽为t,经过微处理器进行相应计算处理后得到两信号的相位差[6-7].设计中频率测量的具体方法是:被测信号转换后形成脉冲信号,利用其上升沿触发计数器对基准时钟开始计数,处于下降沿时则停止计数,所得计数为N,利用t=N×T/2,f=1/t,其中T为所用晶振的时钟周期,利用单片机系统编程实现该运算式,即可求得频率,并将运算结果送液晶显示.系统的原理框图如图1所示.3.2.1 模拟部分模拟电路部分要将同频率的两路正弦信号转换为方波输出,电路采用电压比较器LM393.LM393内有2个电压比较器,两路信号分别接2个比较器同相输入端,将反相输入端接地,即构成过零比较电路.前级的射随器采用LM353,其作用是提高输入阻抗,提高负载.过零比较器使用芯片LM393来实现,该芯片性能较好,能够有效提取正弦波的过零点.选择使用过零点这种判断方法是因为正弦波在过零点的时候,斜率具有极大值,即使两列正弦波幅度略有不同,也不会对测量结果造成过大影响,所以芯片上输出口的上拉电阻主要用于控制高低电平输出的大小.图2和图3分别是A、B两路同频率正弦信号经过模拟电路转化为方波的电路图,其中W31和W32同时接通时构成跟随器,W32和W34同时接通时构成比例放大器.3.2.2 部分参数选择整个电路设计中,参数的选取至关重要,CPLD中计数器的时钟频率要选择恰当,时钟的脉宽要保证输入方波信号的高电平时间Δt最小时存在计数值,即系统能够采集Δt最小时的输入信号;同时,还要保证Δt最大时,计数器存在计数值,即能够采集到最大的相位差360°.根据相位误差范围的要求,计算Δφ=Δt/T×360°=0.5°,当 T=10 k Hz时,Δt=0.139μs,分频系数=0.139/0.05=2.78,故本设计采用2分频.由于AVR单片机数据位的限制,最终得到下限频率取200 Hz,此时,系统测量的展伸不确定度范围符合设计要求.系统的软件设计流程图如图4所示.本研究使用模块化的设计方法,所以软件模块和硬件模块均首先各自独立进行调试,独立调试通过后,再进行系统的软硬件综合调试.在调试输入波形整形模块时,首先检查该模块所有芯片的工作电压是否正常,调整工作电压后,再测试射随器的输出电压,如果其输出电压正常,则测试过零比较器的输出端,看其电压是否正常;如果不正常,可以稍微调整负载电阻,使其输出电压正常.实验所得数据均为正常情况下于实验室中测试得出,测试结果如表1所示.由表1数据可知,系统可以测量一定频率范围内2个同频正弦信号之间的相位差,并能达到稳定的测量精度(理论推算为0.5°,实际可达±3°).测试结果存在的误差来源于所选基准时钟的准确性以及采用软件计数存在一定的延时.在实际应用中,CPLD可采用更高的晶振频率来增加频率的测量范围,并提高测量精度.本研究以微控制器ATmega 128和可编程逻辑器件EPM1270为核心,将单片机控制技术和电子设计自动化(Electronic Design Automation,EDA应用技术有机结合在一起,完成了低频数字式相位测试仪的设计与制作.由于可编程逻辑器件可以完成较大且较为复杂的逻辑处理任务,而且它灵活方便,易于移植,可通用性强,因此系统主要的逻辑功能均在可编程逻辑器件内部完成.本研究所设计的低频数字式相位测试仪采用CPLD,外围电路较为简单,工作可靠,电路调试和维护简单易行.【相关文献】[1]田秀丰,何继爱,李敏.低频数字式相位测量仪的设计[J]无线电通信技术,2008(2):55-61.[2]陈明杰.低频数字相位(频率)测量的CPLD实现[J].微计算机信息,2008,24(32):224-225.[3]缪晓中.基于MCU+CPLD的相位差和频率的测量方法研究及实现[J].国外电子元器件,2008(7):10-12.[4]姚远,王丽婷,郭佳静.低频数字式相位测量仪[J].电子世界,2004(5):39-41. [5]潘洪明,邹立华,方燕红.同频正弦信号间相位差测量的设计[J].电子工程师,2003,29(3):41-42.[6]欧冰洁,段发阶.超声波隧道风速测量技术研究[J].传感技术学报,2008,21(10):1804-1807.[7]车惊春,韩晓东.Protel DXP印制电路板设计指南[M].北京:中国铁道出版社,2004:94-110.[8]龙腾科技.Protel DXP循序渐进教程[M].北京:科学出版社,2005:22-52.。

数字相位测量系统设计

数字相位测量系统设计摘要本论⽂针对在个⼯业和民⽤场合,为了对各种低频信号进⾏分析,常常引⼊相位测量,⽽典型的传统⽅法是通过显⽰器测量,这种⽅法误差⽐较⼤﹑读数不⽅便等问题,本论⽂就此问题设计了⼀种数字相位测量仪对其进⾏相位时间间隔测量。

以单⽚机AT89C51为核⼼,⽤零⽐较器LM393将正弦波信号转换为⽅波,通过由D触发器组成的双稳态触发器实现两⽅波信号的相位差,将得到的信号经过模拟开关进⾏整幅,使之⾼电平为基准电压4.98V,低电平为0V,整幅后的波形经整流滤波形成直流电压,对不同的占空⽐输⼊直流电压在0V~4.98V,⽤16位A/D7705进⾏采样,可使其精度远⼤于设计要求的0.1°。

显⽰采⽤七段LED数码管,并⽤MAX7219作为显⽰器的驱动,对LED的亮度进⾏调节。

论⽂设计了相位⽐较电路、移相电路、显⽰电路、直流稳压电路。

系统采⽤软硬件结合的⽅式,测量精度⾼、稳定性好、操作简单,适合使⽤于各种需要的低频相位测量场合。

关键词:相位测量、相位时间间隔测量、单⽚机(AT89C51)Abstractanalyzed, This paper in a industrial and civil occasions, in order to all kinds of low frequency signal is often introducing phase measurement, the typical and traditional way is through display measuring, this kind of method error is bigger, reading is convenient wait for a problem of this issue, this paper designs a digital phasic measuring instrument for its phase time-interval measurement.With single-chip microcomputer AT89C51 as the core, with zero comparator LM393 will sine signals converts square-wave by D flip-flop, composed of bi-stable flip-flop reach two square wave signal of phase, will receive the signal for the whole picture after analog switch, make high level for the datum voltage 4.98 V, low level for 0V, whole picture after the formation of the waveform dc voltage rectifying filtering for different 390v input dc voltage in 0V ~ 4.98 V, with 16 A/D7705 sampling, can make its precision far outweigh the design requirements of 0.1 °. LED digital display using seven section, and MAX7219 as monitor tube to drive, LED the brightness of the adjusted. Paper designed a phase comparison circuit, phase shifting circuit, display circuit, dc voltage circuit. System adopts hardware and software combination way, high accuracy, good stability, simple operation, and suitable for use in various needs of low-frequency phase difference measurement occasion.keywords: Phase difference measurement Phase time-interval measurement SCM(AT89C51)⽬录1.绪论 (5)1.1 国内外相位检测技术的发展现状 (5)1.2 本课题研究的主要内容 (6)1.3 本课题研究的⽬的和意义 (7)2.低频数字相位测量系统的总体⽅案设计 (8)2.1相位的基本概念 (8)2.2相位测量的技术指标 (8)2.3系统任务需求分析 (9)2.3.1课题要求 (9)2.3.2发挥部分 (9)2.4相位测量的原理 (9)2.5 设计⽅案的⽐较论证 (10)2.6单⽚机AT89C51功能简介 (12)2.6.1主要性能功能参数 (12)2.6.2 AT89C51特性功能概述 (13)3.相位测量硬件的设计 (14)3.1 系统总体结构的设计 (14)3.2 相位⽐较电路的设计 (14)3.3 A/D转换电路的设计 (15)3.4 键盘与显⽰电路的设计 (16)3.4.1主要性能 (16)3.4.2引脚功能 (16)3.4.3⼯作时序及转换原理 (16)3.4.4 AD7705数字接⼝及电路 (17)3.4.5⽚内寄存器 (18)3.5直流电源电路的设计 (20)3.6芯⽚MAX7219的简介 (20)3.6.1MAX7219的性能 (20)3.6.2管脚配置 (20)3.6.3典型应⽤电路 (22)3.6.5读写时序说明 (23)3.7直流电源电路的设计 (23)4.移相⽹络电路设计与参数计算 (25)5.1移相⽹络电路 (25)5.2移相⽹络参数设计 (25)5.3数字移相信号发⽣器 (27)5.系统软件流程设计 (30)结论 (31)致谢 (32)参考⽂献 (33)1. 绪论1.1国内外相位测量技术的发展现状现代相位测量技术的发展可分为三个阶段:第⼀阶段是在早期采⽤的如李沙育法、阻抗法、和差法、三电压法等,这些测量⽅法通常采⽤⽐对法和平衡法,虽然⽅法简单,但测量精度较低;第⼆阶段是利⽤数字专⽤电路、微处理器等来构成测试系统,使测量精度得以⼤⼤提⾼;第三阶段是充分利⽤计算机及智能化测量技术,从⽽⼤⼤简化设计程序,增强功能,使得响应的产品精度更⾼、功能更全。

数字电路课程设计(5篇)

数字电路课程设计(5篇)第一篇:数字电路课程设计数字电路课程设计要求:1.结合所学知识设计一简单实用电路(建议选多功能数字钟),并在实验室里完成实物电路的连接调试。

2.每人独立完成一篇课程论文,论文至少2000字,可手写,也可打印(打印稿的格式另附)。

3.要求写出设计背景,理论基础,设计思路,设计过程,调试过程,仿真过程(可选),最终电路等。

4.总结所设计电路的优点,缺点,改进方向。

5.严禁抄袭,所有雷同论文均以0分计。

6.选多功能数字钟的同学在数字电路实验室完成实验。

选其它题目的同学所需软硬件资源请自行解决。

第二篇:数字电路课程设计一、设计报告书的要求: 1.封面2.课程设计任务书(题目,设计要求,技术指标等)3.前言(发展现状、课程设计的意义、设计课题的作用等方面)。

3.目录4.课题设计(⑴ 写出你考虑该问题的基本设计思路,画出一个实现电路功能的大致框图。

⑵ 画出框图中的各部分电路,对各部分电路的工作原理应作出说明。

⑶ 画出整个设计电路的原理电路图,并简要地说明电路的工作原理。

⑷ 用protel画原理电路图。

(5)用Multisim或者Proteus画仿真图。

5.总图。

6.课题小结(设计的心得和调试的结果)。

7.参考文献。

二、评分依据:①设计思路,②单元电路正确与否,③整体电路是否完整,④电路原理说明是否基本正确,⑤报告是否清晰,⑥答辩过程中回答问题是否基本正确。

三、题目选择:(三人一组,自由组合)(设计要求,技术指标自己选择)1、基于DC4011水箱水位自动控制器的设计与实现水箱水位自动控制器,电路采用CD4011四与非门作为处理芯片。

要求能够实现如下功能:水箱中的水位低于预定的水位时,自动启动水泵抽水;而当水箱中的水位达到预定的高水位时,使水泵停止抽水,始终保持水箱中有一定的水,既不会干,也不会溢,非常的实用而且方便。

2、基于CD4011声控、光控延时开关的设计与实现要求电路以CD4011作为中心元件,结合外围电路,实现以下功能:在白天或光线较亮时,节电开关呈关闭状态,灯不亮;夜间或光线较暗时,节电开关呈预备工作状态,当有人经过该开关附近时,脚步声、说话声、拍手声等都能开启节电开关。

低频数字式相位测量仪

低频数字式相位测量仪设计报告目录1方案设计与论证2 1.1移相网络设计方案2 1.2相位测量仪设计方案3 2系统设计3 2.1总体设计32.1.1系统框图3 2.1.2模块说明4 2.2各模块设计及参数计算4 2.2.1移相网络设计及R、C参数设定4 2.2.2相位测量仪设计52.2.3软件系统63.结论64.参考文献75.附录7系统设计图7摘要本系统以单片机为核心,辅以必要的模拟电路,构成了一个基于具有高速处理能力的低频数字式相位测量仪。

该系统由相位测量仪和移相网络组成;移相网络能够产生-45~45°相位差的两路信号;相位测量仪能够测量出具有0°~359°的两路信号的相位差,绝对误差小于2°,具有频率测量及数字显示功能。

经过实验测试,以上功能均可以准确实现。

关键字:单片机移相相位差数字显示1方案设计与论证1.1移相网络设计方案本设计的核心问题是信号的模拟移相程控问题,其中包括波形相位以及波形幅度的程控。

在设计过程中,我们首先考虑了赛题中提供的方案。

如图1-1所示:V1VV2图1-1该模拟电路主要采用高、低通电路的临界截止点来产生极值相位的偏移。

当高、低通电路的截止频率等于输入信号频率时,根据其幅频特性,信号波形所产生的相位分别为45°和-45°,恰好满足赛题要求的连续相移范围-45°~45°的调节。

由于高、低通电路在截止点时会产生幅度的衰减,故电路在后级加了放大电路,且采用了电压串联负反馈的方式提高了输入阻抗并降低了输出阻抗,电路最后还设计有调幅装置,能够很好地满足A、B输出的正弦信号峰—峰值可分别在0.3V—5V范围内变化。

综上所述,该移相网络能够满足赛题的所有要求,且电路设计简单、易行,故我们直接采用了这种方式来产生模拟的相移输出。

1.2相位测量仪设计方案方案一:检相器可以利用正弦波形的正半周和负半周的对称特性。

模电课程设计——数字式相位差测量仪

模电课程设计——数字式相位差测量仪小组成员:韦岸(组长)袁剑波农志兴杨勰一.数字式相位差测量仪的概念数字式相位差测量仪是利用MAX7219外界微处理器实现数码显示。

当两列同频率信号经过整形电路比较电路后,输出两列方波,然后通过微处理器对其进行处理,计算出两列信号的相位差,再向显示控制器下达显示指令,产生使LED显示器显示数码的电平,达到利用数码管显示相位差的效果。

这里,采用单片机的计数功能对输入脉冲进行计数,使计数器仪在两信号的相位差期间计数。

其功能,先将计数器进行清零,接下来检测输入的脉冲的上升沿,若上升沿到,则计数器开始工作,当下一个新号的上升沿到来的时候,计数器便停止计数,将计数器的结果送入锁存器进行锁存,再对计数器进行清零,这样,可是使计数器在下一次能正常工作。

该电路必须加计数锁存器,否则显示器上的数字会随计数器的状态而变化,所以要想稳定地显示测量结果,计数器的计数结果必须经锁存器锁存。

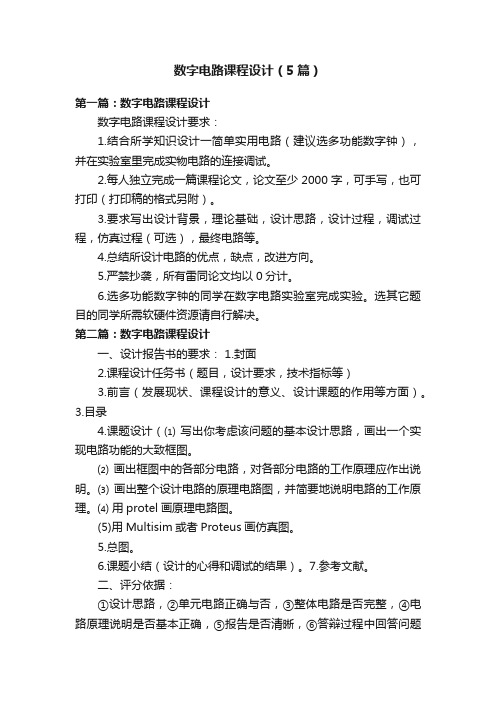

二.原理框图的构建相位差测量仪的原理框图,分辨率为1度。

基准信号(相位基准)f 经放大整形后加到锁相环的输入端,在锁相环的反馈环路中设置一个N=360 的分频器,使锁相环的输出信号频率为360f,但相位与f 相同,这个输出信号被用作计数器的计数时钟。

被测信号f s经过放大整形再2分频后得到f s/2与f/2送入由异或门组成的相位比较电路,其输出脉冲A的脉宽tp反映了两列信号的相位差:利用这个信号作为计数器的阀门控制信号,使计数器仅在f与f s的相位差tp内计数,这样计数器记得的数即为f与f s之间的相位差。

由于计数器时钟频率为360f,因此,一个计数脉冲对应1度。

计数的值经锁存译码后通过LED数码管显示。

D触发器用于判断f与f s的相位关系,当Q为1时,f超前于f s,相位取正值,符号位数码管显示全黑:当Q为0为0时,f滞后于f s,相位取负值。

原理框图三.电路原理图四.使用元件原理介绍(1)放大电路本设计采用的是LM324运算放大器,如下图:通过使用LM324运放器,我们可以使正弦波转变为方波。

基于DSP的低频数字式相位测量仪的设计

随着科学技 术的突飞猛进的发展, , 电 技 T 30 C 4 2 A 8S 2 MS 2 V 50 和 T 9 5 芯片的集成度高 、

智能 程 度 高 、功 能 强 大 ,使得 它实 现 起 来 比较

教 ,研 究方 向 为移 动 术 广 泛 的 应用 T工 、 、农 、 、交通 运 输 、航 I I

究网络 、系统的频率特性 中具有重 受意义。近 果。系统框 图如图 i 所示。

图 1低 频 数 字 式 相位 该 系统 以T 30 C 4 2 核心 , 待 测 MS 2 V 5 0 为 对

测量仪 系统框图

量信 号进行 采集 和处理 ,包括 栏彤和移 相电

路 ,把 采 集米 的 模 拟 信 号转换 为数 字 信 。其

湖南工学院 俞斌 贾雅琼 汤群芳 摘 要: 本 文提 出了一种 基于 T 3 0 C 4 2的低 频数字 式相位测 年来 ,随着科学技术的迅速发展 ,很多测量仪 MS 2 V 5 0

量仪 的设计方法。

逐渐 向 “ 智能仪器”和 “ 自动测试 系统”发展 , 这使得仪 器的使 _ 比较简单 ,功能越来越多。 } H

本低 频 数 字 式 相 位 测 量 仪 由 T 30 C 4 2 MS 2 V 5 0 、

关键 词 : DS ;低频 ;数字 式;相位 测量 ;S M P C

苯 06 文20 年

月2日收到。 俞斌 : 助

0 吉 |

AT8 2和 小 规 模 集 成 电 路 构 成 。 由 于 9S 5

通信、单片机和 DS 航天、国防建设 等国民经济的诸 多领域 中,而 简单 ,而且 ,具有体积小 、性价比高、性能稳 P

应 用。 电子 测量 技 术 又 是 电子 技 术 中进 行 信 息 检 测 的 定 的特 点 。

低频率数字相位差测量仪设计

引言相位差测量数字化的优点在于硬件成本低、适应性强、对于不同的测量对象只需要改变程序的算法,且精度一般优于模拟式测量。

在电工仪表、同步检测的数据处理以及电工实验中,常常需要测量两列同频率信号之间的相位差。

例如,电力系统中电网并网合闸时,需要求两电网的电信号的相位差。

相位差测量的方法很多,典型的传统方法是通过示波器测量,这种方法误差较大,读数不方便。

为此,我们设计了一种基于锁相环倍(分)频的相位差测量仪,该仪器以锁相环倍(分)频电路为核心,实现了工频信号相位差的自动测量及数字显示。

论文摘要本系统为低频数字式相位/频率测量仪,由移相网络模块、相位差测量模块及频率测量模块三大部份构成,其系统功能主要是进行相位差测量及频率测量。

移相网络主要是由RC移相电路和LM324运放电路组成,将被测信号送入移相网络,经RC移相、LM324隔离放大,产生两路信号,一路为基准信号经过波形转换,另一路为移相后的信号。

分别经过波形转换、整形、二分频送给相位测量模块及频率测量模块。

相位差测量仪主要是由锁相环PLL(Phase Lock Loop)产生360倍频基准信号和移相网络的基准信号与待测信号进行异或后的信号作为显示器的闸门电路和控制信号。

频率测量模块主要是用计数法测量频率的,它是有某个已知标准时间间隔Ts内,测出被测信号重复出现的次数N,然后计算出频率f=N/Ts.显示电路模块主要是由计数器、锁存器、译码器和数码管组成。

低频率数字相位测量仪目录1设计任务书 (3)2设计方案概述 (3)3系统的组成………………………………………………………………………………4.3.1总体框图 (4)3.2移相网络部分 (4)3.3相位测量部分 (6)1)波形转换、整形放大 (8)2)锁相环倍频 (9)3)闸门电路 (11)4)控制门 (11)5)计数器 (11)6)锁存器 (11)7)显示译码器与数码管 (11)3.4频率测量部分 (12)1)数字频率计的基本原理 (12)2)系统框图 (12)4附录………………………………………………………………………一、设计任务书(一)任务设计仿真一数字相位计(二)主要技术指标与要求:(1)输入信号频率为1KHZ~20KHZ可调(2)输入信号的幅度为10mV(3)采用数码管显示结果,相位精确到0.1°(4)采用外部5V直流电源供电(三)对课程设计的成果的要求(包括图表)设计电路,安装调试或仿真,分析实验结果,并写出设计说明书。

数字式相位差测量系统(基于51单片机)

数字相差检测仪的制作专业:电气班级:XX班学号:XXXXXXXXXX 学生姓名:XXX指导教师:XX目录摘要: ............................................................................................................... 错误!未定义书签。

Abstract: ............................................................................................................. 错误!未定义书签。

第一章绪论. (5)1.1 测量相位差的作用和意义 (5)1.2 相位差测量的研究现状 (5)1.3本课题研究的主要内容 (7)第一章:最小二乘法以及快速傅里叶变换简介 (8)1.1:最小二乘法简介 (8)2.1 主程序流程图 (12)2.2位倒序算法实现 (12)2.4 FFT算法的实现 (13)2.5 AD采样的使用 (14)2.6 定时器的使用 (15)第三章:硬件电路设计 (17)3.1 移相电路的设计 (17)3.2 电压跟随器模块 (17)3.4 电源电路 (18)3.4.1 变压器简介 (18)3.4.2 单相全桥整流电路 (19)结论 (20)致谢 ................................................................................................................... 错误!未定义书签。

参考文献(Reference).. (21)附录: (22)基于最小二乘法的低频数字相位差检测仪的研究摘要:常见的相位差检测方法一般是过零法,通过外部硬件电路对正弦信号的零点进行检测,产生的脉冲信号出发MCU的外部中断,通过MCU的定时器计算出信号的频率以及相位差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录1.设计任务书。

2.设计方案概述。

3.V/f变换测量相位差角的工作原理。

4.电路的组成及参数选择。

4.1整形电路及信号C的形成。

4.2滤波电路的参任务计划书。

4.3V/f变换电路的设计。

4.4 89C52内部资源的利用。

5.应用实例。

6.结论。

7.总结。

一、设计任务书(一)任务设计仿真一数字相位计(二)主要技术指标与要求:(1)输入信号频率为0HZ~250HZ可调(2)输入信号的幅度为0.5V(3)采用数码管显示结果,相位精确到0.1°(4)采用外部5V直流电源供电(三)对课程设计的成果的要求(包括图表)设计电路,安装调试或仿真,分析实验结果,并写出设计说明书。

要求图纸布局合理,符合工程要求,所有的器件的选择要有计算依据。

二、设计方案概述根椐设计任务书的要求,我们参考了一些相关资料书,经过小组的讨论分析,提出了一种用v/f变换测量交流电的相位差的新方法:首先产生出其幅度正比与相位差大小的直流电,再有v/f变换器转换成反映相位差大小的频率信号,在单片机的配合下,最终得到相位差。

这种方法具有分辨率高,适应与大范围的各种输入频率等优点。

正弦交流电电信号相位差的测量可以用多种方法实现。

比较直接的数字式测量方法是在已知信号周期的前提下用定时的方法测得相位差角对应的时间,然后根据已知的周期将其换算成相位差角度。

但是,这种方法的测量精度依赖于定时器的精度和分辨率。

在信号频率较高或频率虽不高但相位差较小时,都可以出现较大的误差。

另外,由于直接测量得到的是时间,相位差角要由这一中间结果与信号的周期运算后才能得到,所以周期的测量不可缺少,其测量的精度也将影响相位差的精度。

在此用一种新的思路进行相位差的测量,用v/f变换器把相位差转换成一个其频率与之成正比的脉冲列,通过计算在一定时间内的脉冲个数测量相位差角。

这种测量方法与信号的周期无关,可以得到较高的精度。

题达到了0.1的测量精度,与此同时工业运行控制中现场操作,修改和设置等问题也得到了很好的解决,以上这些都在工业运行中得到了厂方的认可。

存在的问题主要是本仪器通用性很不强,很难在更大的范围应用和推广,只能运用与某些特定的企业。

今后的工作主要硬件和软件的改进上,列入增加一些通用行很强的功能模块。

3.V/f变换测量相位差角的工作原理首先将输入的两个同频率但存在着相位差的信号进行整形,使之变成方波。

如图1示A和B 再对A,B进行异或处理, 异或输出信号C 的脉冲宽度则反映相位差角.C 的脉宽T1对应的电角度是相位差角,C 的周期T2 是信号周期T 的1/2.如果信号角频率为w 则T1= /w. C为幅值为U 的方波其平均值Ud=UT1/T2=U由此可见,C 的平均值( 亦即直流分量)仅与相位差角和脉冲幅度有关与信号周期无关通过一个RC 低通滤波器将C 中的交流成分滤除在滤波器的输出端就可得到单纯的直流成分如果保持C的脉冲幅度U 不变那么就能够很好地反映出相位差角的大小.为了进行数字化处理将在滤波器输出端得到的作为V/f 变换器的电压输入。

它的输出将是一列脉冲,其频率正比于这样在一定时间里通过对的脉冲个数的计数,只需简单的标度变换,就可以换算出相位差角相位差角测量电路原理图如图2。

在得到V/f变换输出信号后利用单片机进行定时,计数运算,显示等处理非常方便,不仅可以大大地简化硬件电路,也有利于增加功能和提高精度。

本电路采用89C52单片机,充分发挥其定时,计数,中断并行输出等资源的效用,组成一个功能强,结构紧凑,价格低廉的相位测量专用装置由于单片机的灵活性,该电路的硬件稍加改造,就可以增加频率测试功能。

对于信号A与B之间的超前/滞后关系的判断,可以遵循以下原则由图1可以看出,如果方波A上跳后,C出现高电平,则说明A超前于B.否则如果A上跳后C出现低电平,则是A滞后于B;可以通过一个锁存器来记录A上跳后C的状态。

信号A经微分电路后接锁存器的控制端(上跳沿锁入),当信号A出现上跳时,微分电路输出一个正脉冲,C的状态被从D端传向Q端保存! 而后无论A保持高,低电平还是从高电平跳变到低电平,微分电路均不输出正脉冲!锁存器处于保持状态。

直到下一次A的上跳锁存器的内容才得以刷新。

输出端Q 的状态随时可以被读取,Q=1说明信号A超前于信号B;Q=0信号A滞后于信号B。

4.电路的组成及参数选择。

4.1 整形电路及信号C的形成两路被测输入信号分别经耦合电容与两路整形电路连。

整形电路由电压比较器构成,在此采用LM311.。

该比较器可用+5V单电源供电!可以简化电路结构!同时它的输出也更容易与后面的逻辑电路连接,另外LM311的转换速度很快,能够保证对信号整形的质量%值得注意的是,输入的两路信号可能有公共端,但也可能不允许有公共端!而两路整形电路共地。

所以每一路的两个端子都必须接耦合电容,以免在输入信号在没有公共端时经整形电路形成短路。

另外,在整形电路的输入端还应设置限幅电路以保护电压比较器。

2个LM311的输出即为两路方波信号A和B.由于采用+5V单电源供电,这些信号可以直接与逻辑异或门连接,得C信号。

电路图4.2滤波器电路的参数选择滤波电路采用阻容滤波,其输入端直接与异或门的输出(即C信号)连接.滤波器的输出又接V/f变换器的输入端,该端口输入阻抗很大,可视为开路. 异或门采用74HC系列,当其输出高电平时,输出级的一个接正电源的MOS管导通,电源经滤波电路电阻R向C充电,如果忽略异或门的输出阻抗,其时间常数为t=RC.异或门输出低电平时,经C和异或门输出级的接地的MOS管放电,COM管的等效电阻很小可以忽略,时间常数t=RC.时间常数越大,滤波效果越好,但时间常数过大会影响电路的响应速度.如果R=10k则,C=100uF,则t=1s.即使对于10Hz 的输入信号6t是异或门输出脉冲周期的20倍,电容两端电压的波动已经很小了.4.3 V/f变换电路的设计V/f变换电路采用V/f变换芯片LM311.采用该芯片的单+5V电源供电的典型应用电路。

采用这种做法,输入电压与输出频率成正比关系。

输入电压从0到10V,输入频率从0到10kHz.本电路的输入电压是滤波电路的输出,其变化范围是0到5kHz.不难看出,相位差每变化1度,频率变化27.78Hz,或者说,频率输出的每一个脉冲对应0.036度的相位差。

0.036度即为本测量电路的分频率。

3.489C52内部资源的利用489C52内部有两个定时计数器C/T1和C/T0.本电路中C/T1设定为计数模式,计数器输入引脚接V/f变换器的频率输出Ui.工作在定时模式,定时时间为1s.电路工作时,先将C/T1清零,然后同时启动C/T1和C/T0在1s定时终了时,停止C/T1计数.这样,C/T1中累计的数值X即为V/f 变换器输出Ui的频率值,将X乘以180再除以5000即可得到相位差角的度数.储存超前/滞后状态的锁存器的输出端可接在89C52的P口的某一位上,CPU随时可以读取其状态。

测量结果通过LED进行显示,相位差角最大可能为180度,而在角度较小时,为保证精度又应显示小数位。

本电路保留两位小数,因此,完整地显示相位差需要6位LED,即整数3位,小数2位,表示超前/滞后的符号1位.每一个LED与一个锁存/驱动电路相连接,对应一个独立的I/O, CPU通过MPVX指令向其传送数据。

微分电路模块5.应用实例以图2所示电路为基础,增加少量元器件即可组成一台数字式频率/相位测试仪。

具体的做法是两路同频率被测信号经大容量无极性电容耦合到两个LM311比较器的输入端,为能够测量较低的频率6应选择较大容量的电容,选样1000uF;图2中信号A与89C52的定时/计数输入端C/T1连接,作为频率试用。

6位LED轮流显示“频率”和“相位”的测量结果。

实际使用表明,该仪器在输入信号频率为几 Hz到几十kHz 范围均能很好地工作,用高级别仪表校正,相位测量误差不超过0.05度,该精度完全满足一般电气测量和高等学校教学实验的要不同相位的波整形后的输出电波相同相位的波整形后的输出电波异或后的输出电波1.测量相位差角的方法适合于较大频率范围的输入信号,只要整形电路能够输出较好的方波,滤波电路能够输出较平稳的直流电压,V/f变换的输出是一串反映相位差的脉冲列。

对相位差可能出的整个范围(0-180度)均能测量,理论上在测试死角。

2.测量辨率高,且测量分辨率与频率无关。

对任何频率的信号分辨率均可0.036度这为提高测量精度创造了条件。

7.总结通过这次实验我们在设计思想,设计方法和设计技能等方面得到良好的训练,并且更加熟悉了proteus的操作与使用,通过多次失败,最终获得实验结果,使大家养成了严谨的科学态度,在课程设计的过程中得到技能上的洗礼和经验上的积累。

参考文献:【1】韩有望,采用555定时电路的测温方法[J],电子与自动化.1995.43【2】贾振,DS1820及其高精度温度测量的实现[J],电子技术应用.【3】景小宁,智能热电测温技术及其实现[J],微型机与应用,2001(1)【4】刘少强, 新型精密铂电阻测温方法[J],传感器技术1999,18(2)【5】李爱莲,解韶峰,夏利蜂,基于单片的实用测温的实现[J],微计算机信息(工控,仪表,自动化)2001(9);26【6】张庆玲,热电偶传感器测温系统的设计应用[J],西北轻工业学院学报,2000(5);18【7】罗志坤,徐植坚,温度检测系统[J],仪表技术1999(1)【8】曹辉,胡俊,黄均鼐数字式温差测量电路的设计及其实现[J]微电子学,2003,31(3)【9】灰承峰,李黎,张润宇,热电阻温度测量方法[Z]【10】孙涵芳,16位单片机[M],北京,北京航空航天大学出版社,1998【11】汪建,孙开放,章述汉,MCS-96系列单片机原理及应用技术[M],华中理工大学出版社,2000【12】颜荣江,朱无清,侯文军,PSD系列可编程单片机通用外围接口[M],芯片原, 编程及应用. 北京;人民邮电出版社.1995【13】窦振中,单片机外围器件实用手册;存储器分册[M].北京;北京航空航空航天大学出版社,1999。