基于PCI局部总线硬件加密卡的设计

基于PCI总线的CAN接口卡设计

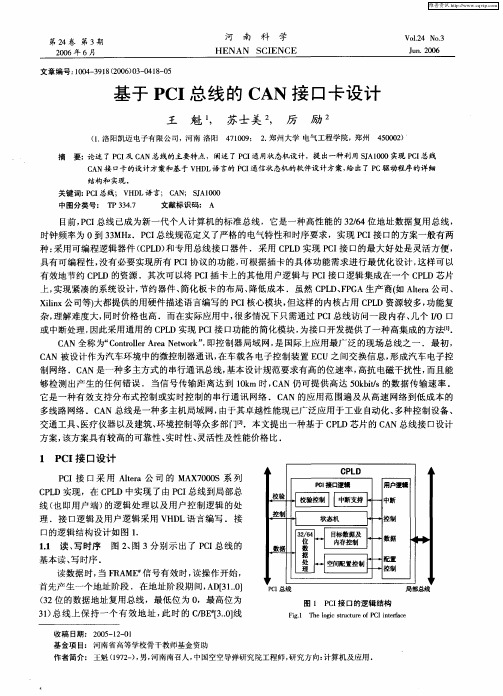

1 P 接 口设计 CI

P I接 口 采 用 A ea公 司 的 MA 70 S系 列 C hr X 00 CL P D实 现 ,在 C L 中实现 了由 P I PD C 总线 到局 部 总

线 ( 即用 户 端) 也 的逻辑 处 理 以及 用 户控 制 逻 辑 的处

CPLD PI c 接口逻辑 用户逻辑

一

控制

数 位 4 制 据 据 卜数 - 数 r ・. _ _ 一 一

理 空 置 配 据 I配 制 控 处 间控 置 忡 制

P1 c 总线 局部总线

基本 读 、 写时序 .

读 数据 时 , F A 当 R ME 信号有 效 时 , 读操 作 开始 , 首先产 生 一个地 址阶 段 .在地 址阶 段 期 间, D 3 .1 A [10 . (2位 的数 据地 址复 用总 线 ,最低 位 为 0 3 ,最 高位 为 3) 线 上 保 持 一 个 有 效 地 址 , 时 的 CB 一】 1总 此 / E [ O线 3

它是 一种 有效 支持 分布 式控 制 或实 时控 制 的串行 通 讯 网络 .C N 的应用 范 围遍 及 从 高速 网络 到低 成本 的 A 多线路 网络 .C N 总线 是一种 多主机 局 域 网, A 由于其 卓越 性 能现 已广 泛应 用 于工业 自动化 、 多种 控 制设 备 、 交通工 具 、 医疗仪 器 以及 建筑 、 环境 控制 等众 多部 门罔 .本文提 出一种基 于 C L P D芯 片 的 C N总线接 口设计 A 方 案 , 方案 具有较 高 的可靠 性 、 时性 、 该 实 灵活 性及 性能价 格 比 .

制 网络 .C N是一种 多主方式 的串行通 讯总 线 , 本设 计规 范要求 有 高 的位 速 率 , A 基 高抗 电磁 干扰 性 , 且能 而

基于PCI总线的智能双通道CAN通信卡设计

Z A G T o E G Z ii,G O Q ag H N a ,D N h-e A i j n

( a zo i — n nvr t,L nh u7 0 7 ,C ia L nhuJ ot gU iesy a zo 30 0 hn ) a o i

ABS TRACT: Th ril i l nr du e i t ro tu tr n p r to h oy o 9 5 ih i e a tce man y i to c n e rsr cu e a d o e ain t e r fPCI 0 2 wh c sa i b d e t rd e c i n o b e c n e i r g o b g h p a d d u l —ha n lRAM , p o wad d sg ln o a d r a e n me ha i utf r r e in p a fh r wae b s d o c - n s o ma ipo i g, a d p o o e h h u h n o c ee meho fa h e e n o o t r e im fs r d s sn t n r p s s te t o g ta d c n r t t d o c iv me tfr s f wa e d - sg i n. F n l e p t t n p o e sfrh g p e o i a , x ai e o r c s o i h s e d c mmun c to fs r o b e c a ne a iai n o ma d u l — h n lCAN o t c mmu i n— c t n c r a e n PCIb s ai a d b s d o o u . KEY ORDS: PCIb ; PCI 0 2; RAM ; S r W us 95 ma tCAN o c mmu iai n c r nc t ad o

基于PCI总线的四通道CAN通讯卡的设计

中图 分 类 号 : T P 2 7 4 . 2

文 献标 识 码 : A

文章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 5 ) 1 4 — 0 1 8 6 — 0 4

De s i g n a n d a p p l i c a t i o n o f f o u r c h a n n e l CAN c o mmu n i c a t i o n c a r d b a s e d o n PCI b u s

4期 第2 3卷 第 1

V0 1 . 2 3

No . 1 4

电 子 设 计 工 程

E l e c t r o n i c De s i t m E n g

2 0 1 5年 7月

J u 1 . 2 0 1 5

基才 P C I总线的四通道 C A N 通讯 卡 的设计

王 海 霞

Ab s t r a c t : I n o r d e r t o c o mp l e t e t h e d a t a t r a n s mi s s i o n b e t we e n n u c l e a r p o we r s i t e I / O mo d u l e s a n d c o n t r o l s t a t i o n,d e s i g n i n g a f o u r c h a n n e l CAN c o mmu n i c a t i o n c a r d b a s e d o n P CI b u s .e a c h C AN c h a n n e l c o n n e c t 3 2 s i n g l e c h a n n e l I / O mo d u l e , a c q u i s i t i o n t h e d a t a o f I / O mo d u l e e v e r y 2 5 s e c o n d s , a n d t h e t o t a l d a t a a c q u i s i t i o n o f t h i s s y s t e m i s 4 0 0 a n a l o g nd a 1 1 2 s w i t c h q u a n t i t y . T h i s d e s i n g u s e t wo CP U, ma k i n g t h e p e r c e n t a g e o f t a k i n g u p i n t e r r u p t i n t e r v l a i n e a c h i n t e r r u p t s e r v i c e i n c r e a s i n g b y 1 9 %. T h i s p a p e r f o c u s i n g o n h a r d w re a c i r c u i t s d e s i g n i n d e t a i l ,i n c l u d i n g p r i n c i p l e d e s i n ,c g h i p s e l e c t i o n a n d P CB d e s i g n , w i t h t h e a d v a n t a g e s o f h i g h s p e e d a n d l o w c o s t . Ke y wo r d s : P C I B US;d a t a a c q u i s i t i o n ;CAN c o mmu n i c a t i o n;Du a l - P o r t RAM

PCI-E 密码卡 SM2 算法侧信道攻击缓解技术设计与研究

近年来,随着市场对高安全性的愈发重视,国家密码管理局颁布了安全三级密码模块相关标准,增加了对物理安全、环境失效性检测、抗侧信道攻击3 个方面的要求。

其中,抗侧信道攻击涉及对国密算法的研究和改造,因而难度较大,而国密算法中,又以非对称算法SM2 的原理和实现最为复杂。

行业内典型设计架构的外设组件互联高速总线(Peripheral Component Interconnect Express,PCI-E)密码卡一般采用多芯片设计架构,即采用一颗专用安全一级算法芯片来负责SM2 算法加速,一颗主控芯片来负责任务调度和敏感数据管理。

该架构下,多数算法专用芯片没有针对侧信道攻击进行加固,且密码卡在进行密码算法运算时,存在关键安全参数在芯片间传输等问题。

因此,研究缓解侧信道攻击的典型架构PCI-E 密码卡的SM2 算法设计,可使得现存的典型架构的PCI-E 密码卡在未来的市场应用上继续发挥作用。

本文首先简要地介绍PCI-E 密码卡的典型设计架构以及架构面临侧信道攻击时可能存在的风险;其次分别从SM2 算法的攻击原理[2]、抗侧信道攻击的针对性改造方法、Inspetor 工具验证3 个方面详细说明缓解技术的设计。

通过本文的介绍,可以填补典型架构的PCI-E密码卡在抗侧信道攻击方面的设计空缺,也可以指导安全二级PCI-E 密码卡的升级改造,使其具有安全三级的实用价值,满足国密检测规范和市场需求。

1典型PCI-E 密码卡设计架构因此,典型PCI-E 密码卡在更高级别安全要求下存在架构上的缺陷,可能导致关键安全参数在跨芯片传输时存在泄露的风险。

2SM2 算法攻击原理分析标准SM2 数字签名算法流程如图3 所示。

在签名过程中,设待签名的消息为M,它的数字签名(r,s),签名者A 的公私钥分别为为长度为v 比特的密码杂凑算法,G 为椭圆曲线的一个基点,其阶为素数,k 为临时私钥。

同时,攻击者也可以通过计时攻击,构建不同比特序列的伪密钥k' 对相同的消息M 进行签名运算,由于点乘运算中的点加运算次数与k 中比特1的位数相关,所以可以通过统计k'p 与kp 运算的时间来推测k 中1 的比特位,进而推断出密钥k。

基于PCI总线的GP—IB接口电路设计

_

T r e du : a g t b s 三态 数据输 入 / 出总线 。 输

_

S

电路优化设计

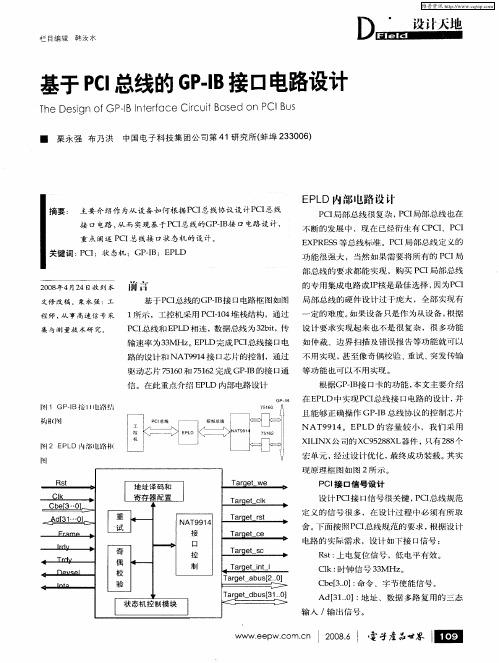

图 2给 出 了 P 总 线 接 口 电 路 的 原 理 框 CI 图, 由于 E L P D容 量 较 小 , 设 计 时 必 须 尽 量 在

NAT9 1 9 4。E LD 的容 量较 小 ,我们 采 用 P

X LNX公 司 的 XC 5 8 XL器件 , 有 2 8 II 9 28 只 8 个

2 PL 『 ;U 车 E D q I 路 I

宏单 元 , 经过设 计优化 , 最终成 功装载 。 其实

现原 理框 图如 图 2 示 。 所

一

修 改稿 。栗永 强 : 工

蛳 , 事 高速 信 号 采 1 示 , 工 控 机 采 用 P I 0 堆 栈 结 构 ,通 过 从 所 C一 4 1

:

定的难 度 。 果 设备 只是 作为从设 备 , 据 如 根

与测 量技 术研 究 。

P I 线和 E L C总 P D相 连 , 据 总 线 为 3 bt 传 设 计 要 求 实 现 起 来 也 不 是 很 复 杂 ,很 多 功 能 数 2 i, 输 速 率 为 3 MHz E L 3 。 P D完 成 P 总 线 接 口电 如 仲裁 、边界 扫描 及错误 报告 等功 能就可 以 [ C 甚 重 突 路 的 设 计 和 NAT 9 4接 口芯 片 的 控 制 ,通 过 不 用 实 现 , 至 像 奇 偶 校 验 、 试 、 发 传 输 91 驱 动 芯 片 7 1 0 7 12完 成 GPI 接 口通 等 功 能 也 可 以 不 用 实 现 。 56 和 56 _ B的

基于PCI总线的信令采集卡的硬件设计

总线是一种不依附于某个具 体处理器的

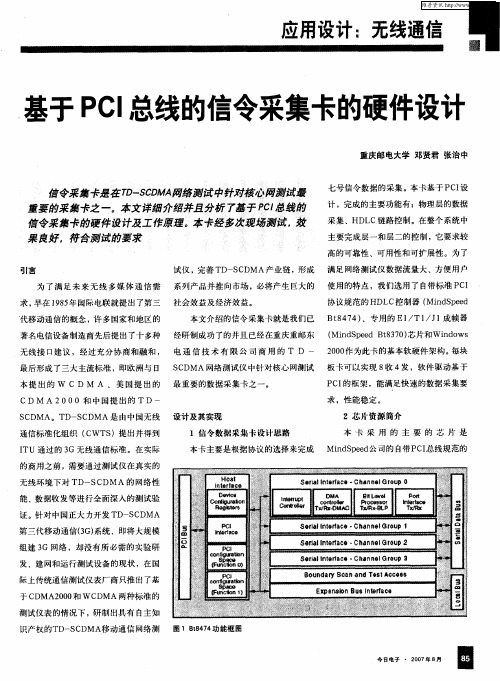

( )一个主接 口( s n efc ) 1 Ho tItra e:

局部总线 ,基于 P 的系统 不受处理 器 主接 口又 由四个部分组成 :设备配置寄 CI 升级的影响 。每个典型 的PC 可以支持 存器、P I I C 功能 0 的配置空 间、 I PC 功能 大约 1 个 电气负载。它支持 3 位或 6 1 0 2 4 的配置空 间、 C 接 口。主接 口主要提 P I 位 的 总 线 宽 度 , 支 持 的 工 作 频 率 为 供 B 4 4 P T8 7 与 C之间的接 口, 完成设备

果 良好 .符合测 试 的要求

弓 害 l

七号信令数据 的采集 。本卡基于 PC 设 I

计 ,完成 的主 要功 能有 :物 理层的数据

采集 、HDL C链路控制 。在 整个系统 中 主要完成层一和层二 的控制 ,它要求较 高 的可靠性 、可用性 和可扩展性 。为了

试仪 ,完善 T S DMA产业链 ,形成 满足 网络 测试 仪数据流量大 、方 便用户 D— C

图 2 B8 7 的 串口功能设计原 理图 t4 4

完成和其他设备之 间的通信控制 。 ( 2)接 收 / 发送 线 性 接 口单 元 ( I T I 。 RL U/ L U) 数 字发送 器 ( XMT 。 R) 数据接收 器 ( VR) RC 。 发送 系统总线 ( S 。 T B) 接收 系统总线 ( B) RS 。 时钟 速率 适配器 ( AD) CL 。 边界 扫描 接 口 (T J AG) 。 其功能 图如 图 3 、图 4 所示 。

维普资讯

应用设计 无线通信

基于 P I C 总线的信令采集卡的硬件设计

重庆邮 电大学 邓贤君 张治 中

基于硬件加密技术的信息安全应用设计

基于硬件加密技术的信息安全应用设计随着科技的发展,信息技术的广泛应用已成为现代社会的基础,信息安全也成为了一种无法忽视的重要问题。

在当前信息化快速发展的背景下,通过硬件加密技术来保障信息安全已经成为了主流的解决方案,本文将对基于硬件加密技术的信息安全应用设计进行探讨。

一、硬件加密技术的基础概念1、加密原理加密是指把明文通过一定的算法变为密文,以达到保护数据免受黑客等非法侵入和窃取的目的。

加密过程实质上就是利用密钥改变数据的组织形式,通过改变信息的形式保证信息的安全。

2、密钥密钥是加密过程最关键的部分,密钥的保密性和长度直接影响到加密过程的安全性。

密钥长短不同,加密强度也不同,一般情况下其长度越长,破解难度越大。

目前常用的密钥长度为128位或256位。

3、对称加密和非对称加密对称加密指加密和解密时采用相同密钥的方式,简单、快速、有效,但缺点是密钥需要保证传输的安全性。

而非对称加密则是采用两个密钥(公钥和私钥),其中公钥作为加密密钥,私钥则作为解密密钥。

非对称加密具有更高的安全性,但加密运算比对称加密要慢得多。

二、基于硬件加密技术的信息安全应用1、硬件加密技术的优势硬件加密技术利用专门的安全芯片来进行加密操作,其优势在于硬件加密加速器处理速度快、保密性高、外部软件不能对其进行操作且支持对不同数据类型的加密。

相对于软件加密来说,硬件加密技术更加安全、可靠和实用。

2、硬件加密的应用范围硬件加密已经广泛应用于多种领域,例如安全存储、加密通信、数字身份验证、支付系统、移动安全等领域。

其中,安全存储是一种常见的应用场景,基于硬件加密的USB加密锁、硬盘加密等产品已经被广泛使用。

3、硬件加密的实现方式实现基于硬件加密的信息安全应用有多种方式,从传统的卡片式智能卡、USB口式加密锁等产品到近年来发展的联合终端芯片、智能存储芯片、SOC芯片等产品,比如华为公司发布的麒麟芯片系列,就实现了智能存储加密、SIM卡加密、指纹定位等多种应用。

基于单片机的PCI总线通信功能设计

基于单片机的PCI总线通信功能设计————————————————————————————————作者:————————————————————————————————日期:郑州大学毕业设计(论文)题目:基于ARM的PCI总线通信功能设计指导教师:职称:学生姓名:学号:专业:院(系):完成时间:2011年5月25日年月日摘要本文详细介绍了基于AT91RM9200单片机的PCI总线通信功能的设计,包括硬件设计和软件设计两部分.通信功能的设计着重于单片机与上位机之间通过PCI总线进行的数据传送.本次设计在于用比较容易掌握的单片机来实现PCI控制器的功能,在PCI总线的简单运用场合,大大简化了设计的复杂程度。

设计的实现是利用单片机的I/O口与PCI 总线的控制信号线以及地址/数据信号线等直接相连,用对单片机的编程来控制数据的传输.文中介绍了PCI总线的基本概念,一些重要信号的定义,以及PCI总线事务的时序。

单片机部分介绍了型号的选择,选择了AT91RM9200单片机的理由和AT91RM9200单片机的基本知识.本次设计选择AM29LV160和57V561620作为AT91RM9200外接存储器。

设计的结果是成功的完成了原理图绘制和PCB版图的设计,和实验仿真。

关键词:PCI总线单片机AbstractThis paper introduces in detail the communication function design of the PCI bus based on AT91RM9200 MCU, including hardware design and software design。

Communication function design focuses on the data transfer between SCM and PC by PCI bus。

The design is to use MCU to realize the function of PCI controller,which is easier to master。

PCI总线接口模块的硬件设计

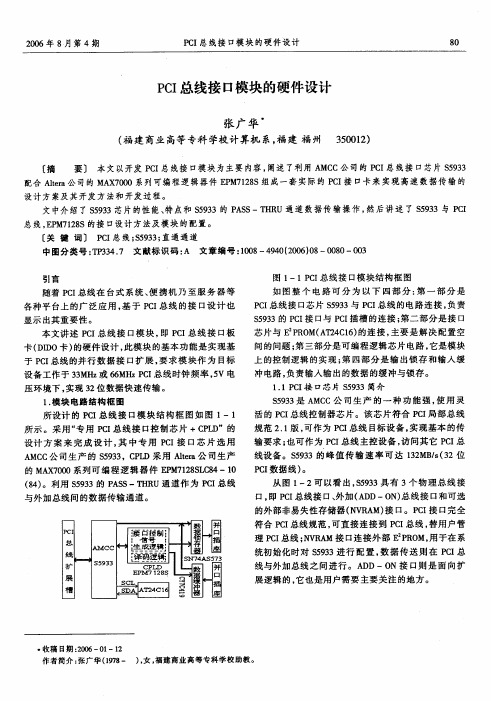

S5933 是 AM 公司生产的一种功能强, CC 使用灵

活的 PCI 总线控制器芯片。该芯片符合 PCI 局部总线

规范 2. 1 版, 可作为 PCI 总线目 标设备, 实现基本的传 输要求;也可作为 PCI 总线主控设备, 访问其它 PCI 总 线设备。55933 的峰值传输速率可达 132M ( 32 位 B/s PCI 数据线) 。 从图 1 一 可以看出, 2 S5933 具有 3 个物理总线接 口, PCI 总线接口、 即 外加(ADD- ON) 总线接口和可选 的外部非易失性存储器(NVRAM)接口。PCI 接口完全 符合 PCI 总线规范, 可直接连接到 PCI 总线, 替用户管 理 PCI 总线;NVRAM接口连接外部 扩PROM, 用于在系 统初始化时对 55933 进行配置, 数据传送则在 PCI 总 线与外加总线之间进行。ADD 一ON 接 口则是面向扩 展逻辑的, 它也是用户需要主要关注的地方。

通道 。

图 1' - 3 串行存储器 AT24C16 与 S5933 的接 口 连接上事先已经设置好内容的 NVRAM, 在整个系 统上电开始运行的时候 , 55933 根据 SNV 引脚上的电 平来探测外部 EzPROM 的类型。当 SNV 为低电平 , 表

明是用的是 8 位宽度的 r PROM; 如果是高电平, 则表 明没有使用 甘PROM总线接口模块结构框图 1 如图整个 电路可分为以下 四部分: 第一部分是 PCI 总线接口 芯片 55933 与 PCI 总线的电路连接, 负责 55933 的 PCI 接口与 PCI 插槽的连接;第二部分是接口 芯片与 EZPROM( AT24C16) 的连接, 主要是解决配置空 间的问题 ;第三部分是可编程逻辑芯片电路 , 它是模块 上的控制逻辑的实现;第 四部分是输 出锁存和输人缓 冲电路, 负责输人输出的数据的缓冲与锁存。 1. 1 PCI 接 口芯片 55933 简介

基于PCI总线和DSP的步进电机运动控制卡的设计和实现

~ ~

■ 电子 科 技 大 学 电子 工 程学 院 夏 勇 韩 春 林 何 子 述

基于 P CI总 线 和 DS P的

步进 电机 运 动控 制卡 的设 计 和 实 现

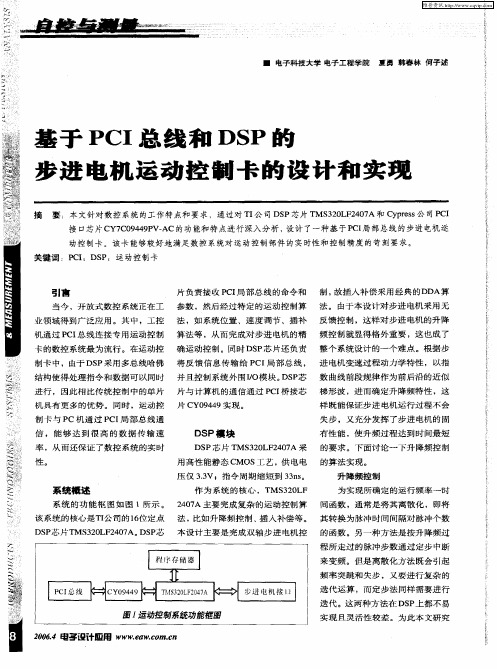

摘 要 :本 文针 对 数控 系 统 的工 作 特 点 和 要 求 ,通 过 对 TI 司 DS 公 P芯 片 T S 2 L 2 0 A 和 C pe s 司 P I M 30 F47 y rs 公 C

制卡 中 ,由于 DS P采 用 多 总 线哈 佛 将 反 馈 信 息 传 输 给 P I 部 总 线 , 进 电机 变 速 过 程 动 力学 特性 ,以指 C 局 结 构 使 得 处 理 指 令 和 数据 可 以 同 时 并且 控 制 系 统 外 围 I / 块。 P O模 DS 芯 数 曲 线 前段 规 律 作 为 前 后 沿 的 近似 CI 进行 , 因此 相 比传 统 控 制 中的单 片 片 与 计 算 机 的 通 信 通 过 P 桥 接 芯 梯 形 波 ,进 而 确 定 升 降频 特 性 ,这 机 具 有 更 多 的优 势 。 同时 ,运动 控 片 CY0 4 9实 现 。 94 制卡与 P C机 通 过 P 局 部 总 线 通 CI 样 既 能保 证 步 进 电机 运 行 过 程 不 会 失 步 ,又 充分 发挥 了步 进 电机 的 固

C卡 CY 0 4 9 码 器 就 输 出 两相 相 差 为 9 。 的脉 冲 驱 动 器 上 驱 动 器 将 检 测不 到 该 信 P I 的功 率 。 9 4 在使 用 时 , 0

迭 代 运 算 ,而 定 步法 同样 需 要 进 行 迭 代 。这 两种 方法 在 D P 都 不 易 S上

实 现 且 灵 活 性 较 差 。 为此 本 文研 究

PCI Bridge芯片IP核的设计与仿真验证

PCI Bridge芯片IP核的设计与仿真验证PCI Bridge芯片是PCI技术的实现基础,使得不同的PCI设备可以进行完整的互联互通,并通过总线仲裁的方式高效管理总线资源,使整个数据传输系统高效稳定。

在本论文的研究中,对PCI Bridge芯片的实现技术和具体设计做了较为细致的分析和验证。

通过在Testbench中设置各种异常情况的出现来模拟现实情况,进行全面的仿真验证。

完成了PCI总线从接口IP核设计、综合和仿真。

关键字:PCI Bridge芯片IP核,设计,仿真验证第一章绪论1.1引言近年来,计算机技术和电子设备的不断发展,特别是各类CPU速度与效率的高,多核处理器的出现,多级高速缓冲的普遍采用等,这使得需要高速总线传送数据的需求日益增加,与此同时通过多总线结构让不同速度的设备可以挂在不同的总线上,以较低总线竞争,以此使得系统的效率速度大大提高。

在多总线结构中,Local Bus(局部总线)的发展最激动人心。

PCI总线就是目前应用最为广泛的,也是比较领先的高性能局部总线。

在结构上,PCI总线采用地址和数据总线二合一的复用结构、32/64位2种总线带宽、具有多处理器(Multi core processor)功能却又相对独立,同时与其他类别的总线联合工作的结构扩展功能;在电气性能指标上,PCI总线采用33/66MHz 两种主频、5.0/3.3 V两种电压;在通讯协议上,PCI总线采用Burst(猝发传输模式)为缺省模式。

PCI技术具有这么多高端性能,无疑在众多总线中具有压倒性的优势,成为PC 机局部总线和高速设备数据传输的首选。

PCI Bridge芯片是PCI技术的实现基础,使得不同的PCI设备可以进行完整的互联互通,并通过总线仲裁的方式高效管理总线资源,使整个数据传输系统高效稳定。

从应用角度看,PCI技术是计算机系统数据交互的基础,也是嵌入式设备和工业系统与微机系统互联的重要实现方式,研究PCI Bridge规范及其实现具有重要的理论和应用意义。

基于PCI局部总线的1553B总线接口卡设计

基于PCI局部总线的1553B总线接口卡设计作者:赵明阳朱岩张建东史国庆来源:《现代电子技术》2012年第10期摘要:根据1553B数据总线协议及其接口技术要求,设计了一种基于PCI局部总线的1553B总线接口卡。

系统使用PLX公司的PCI9052和DDC公司的1553B协议芯片,通过FPGA芯片EP1C12B进行PCI协议和1553B协议的转换,使用DSP控制器TMS320F2812作为下位机的主控单元,并编制了接口卡驱动程序,实现了1553B总线和PCI 总线的转换。

关键词:PCI局部总线; 1553B总线;总线接口卡;数据总线协议中图分类号:文献标识码:A 文章编号:基金项目:航空科学基金资助项目(2010zc53036) 在航电系统的研制初期,通常要先在地面以微型计算机为基础做各种仿真实验。

这使得用于各仿真系统的接口板的研制和革新工作便同时成为航电系统发展的一个重点。

接口板的主要任务是实现航电系统的数据总线与PC机的数据总线之间的通信功能,这使PC机可以模拟航电系统数据总线上所挂接的实际子系统。

PCI(Peripheral Component Interconnect)总线,即外围部件互连总线,是一种先进的高性能32/64位地址数据复用局部总线,可同时支持多组外围设备。

PCI局部总线不受制于处理器,为中央处理器及调整外围设备提供一座桥梁,更可作为总线之间的交通指挥员,提高数据吞吐量,具有支持线性突发传输、极小的存取延误、采用总线主控和同步操作、兼容性强等优点。

本文设计了一种基于PCI总线的接口板,其服务对象是总线,并编写其在Windows下的驱动程序。

1 1553B总线协议是一个关于数据总线电器特性和协议规范的军事标准,这个标准规定了飞机内部数字式的命令/响应时分制多路数据总线的技术要求,也规定了多路数据总线的操作方式和总线上的信息流的格式以及电气要求。

其作用是提供一个在不同系统之间的传输数据和信息的媒介。

一种基于PCI总线接口芯片的设计

A bs r t t ac :PC ILoc lBusi a soneoft oc he l al bus st a s e h ti w i l e n PC sa o k s a i ns de y us d o nd w r t to , a s be om e a n nd ha c n i dus r t nda d.I hi pe ,an A SI ba e t y sa r n t s pa r C s d on PCI Loc lB us Spe i c ton a cf ai i V 2. s de i 2 i s gne d,a t unc i nd is f ton,tm i ha ac e i tc a i ng c r t r s i nd desgn f o r l o pr e e i l w a e a s es nt d.

维普资讯

裔 奠巨 鲁麓 E c C r 计 实 D Th o Fu Ae e o 加 y m设 与

一

种 基 于 PGI 线 接 口芯 片 的 设 计 总

夏 晓 骏 , 许 永 生 , 赖 宗 声

(华 东 师 范 大 学 微 电子 电 路 与 系 统研 究 所 , 上 海 20 6 0 0 2)

以 及 几 个 控 制 信 号 , 就 能 实 现 P 总 线 与 P I 户 CI C 用

设 备 之 间 的 连 接 , 这 种 方 法 简 单 方 便 , 已经 被 越

来越 多 的设计 者所 采 用 。

容 性 和 预 置 的 发 展 空 间 , 被 计 算 机 届 认 为 是 最 具 发 展潜 力 的局 部 总线 标准 。 随 着 计 算 机 技 术 的 发 展 , 对 高 速 高 性 能 的 各 种 扩 展 卡 的要 求 越 来 越 高 ,因 此 符 合 P 总 线 规 范 CI

基于PCI总线的ARINC429接口卡设计

Vo .0 1 2

No7 பைடு நூலகம்

电子 设 计 工 程

El cr n c De in En i e r e to i sg g n e i

21 0 2年 4月

Ap .2 2 r 01

基矛 P CI总线 的 ARI 4 9接 口卡设计 NC 2

王德 周 .李 登科

图 1 A IC 2 R N 4 9电 平 定 义

Fi.1 ARI 42 e e e nto g NC 9 lv ld f i n i i

1 A砒 NC 2 4 9总 线 简 介

A IC 2 R N 4 9是 一 种 单 向式 广 播 式 数 字 总 线 ,传 输 的介 质

: : — — ——

一

j

P92 实 。 C∞ 来 现

作者 简介 : 王德 周 (9 0 ) 男 , 苏徐 州人 , 士 , 程 师 。研 究方 向 : 空 导 弹 飞 行 试 验 。 18 一 . 江 硕 工 空 1 4- 8

王德 周 , 等

21 CP 模 块 的选 择 . U

( 中国 空 空 导 弹 研 究 院 河 南 洛 阳 4 10 ) 7 0 9 摘 要 :利 用 P I 用接 口芯 片 P I0 2和 D I 0 64 9总 线 收 发 芯 片设 计 了 A I C 2 C 专 C9 5 E 1 1 2 R N 4 9接 1 卡 , 用 D P作 为 主 控 : 2 采 S

D I0 6和 B 4 9为 核 心 设 计 了 A I C 2 E11 D2 R N 4 9总 线 通 讯 模 块 来 完 成 数 据 的 收 发 任 务 ;P 与 计 算 机 数 据 交 换 采 用 P I CU C 总 线 , 为 了 缩 短 开 发 时 间 与 难 度 ,选 用 P I 用 接 口 芯 片 C 专

PCI总线协议的FPGA实现及驱动设计

PCI总线协议的FPGA实现及驱动设计

PCI总线协议是一种用于计算机内部设备之间进行数据传输的高速总线协议。

FPGA (Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程来实现不

同的电路功能。

通过将PCI总线协议的功能实现在FPGA中,可以方便地进行硬件开

发和测试。

在FPGA中实现PCI总线协议,一般需要完成以下几个主要步骤:

1. 确定设计需求:根据具体应用需求,确定需要实现哪些PCI总线功能和特性。

2. 设计PCI控制器:在FPGA中设计实现一个PCI控制器,该控制器负责处理来自主

机的PCI总线请求,包括地址映射、数据传输等。

可以使用硬件描述语言(如VHDL

或Verilog)来描述和设计该控制器。

3. 实现PCI控制器:基于设计的描述,使用FPGA开发工具将其编译成硬件配置文件,然后将该配置文件下载到FPGA芯片中进行实际逻辑实现。

4. 驱动程序设计:设计和实现一个合适的驱动程序,该驱动程序在主机上运行,用于

控制PCI设备和FPGA之间的数据传输。

这个驱动程序可以使用C或其他编程语言来

编写,并且需要遵循PCI总线协议规范。

需要注意的是,PCI总线协议涉及到许多复杂的细节和规范,因此在实现过程中可能需要参考相关的PCI规范和文档。

另外,为了确保PCI设备与主机兼容,并保证正确的

数据传输和控制,驱动程序和FPGA实现需要进行充分的测试和验证。

以上是一个简要的描述,具体的实现细节和步骤可能因应用需求和具体平台而有所不同。

一种基于PCI接口的1394B总线的设计与实现

一种基于PCI接口的1394B总线的设计与实现一、引言随着数字设备的不断发展,人们对数据接口的要求也越来越高。

在实时数据传输和多媒体设备连接方面,1394B总线已经成为一种非常理想的选择。

1394B总线的传输速度快、可靠性高,是连接数字摄像机、音频设备、外部存储设备等的理想选择。

随着1394B总线技术的不断完善,其在各种应用领域中的应用也越来越广泛。

本文将介绍一种基于PCI接口的1394B总线的设计与实现。

我们将介绍1394B总线的基本原理和特点,然后将介绍基于PCI接口的1394B总线的设计方案,并通过实际案例进行验证和实现。

二、1394B总线的基本原理和特点1394B总线是一种高速串行总线,也称为FireWire总线,它是一种用于连接外围设备的通信协议和总线。

1394B总线具有如下特点:1. 高速传输:1394B总线支持最高800Mbps的传输速率,远高于USB接口。

这使得它非常适合实时数据传输和多媒体设备连接。

2. 灵活性:1394B总线可以连接多个设备,支持热插拔和点对点连接,能够满足不同外围设备的连接需求。

3. 稳定性高:1394B总线采用了差分传输技术,具有较强的抗干扰能力,能够保证数据传输的稳定性和可靠性。

三、基于PCI接口的1394B总线设计方案基于PCI接口的1394B总线设计方案,主要包括以下几个部分:1. PCI接口芯片:PCI接口芯片是连接1394B总线和主机的关键部件,它负责将主机的命令和数据传输到1394B总线上,同时将外围设备的数据传输给主机。

PCI接口芯片通常由PCI总线控制器、1394B总线控制器和DMA引擎组成。

它不仅要能够支持高速传输,还要对1394B的特性有一个良好的支持。

3. 物理层接口:物理层接口主要包括电气接口和连接器,它负责将1394B总线的数据传输到外部设备上。

电气接口一般由差分传输技术组成,能够提供较高的抗干扰能力;连接器一般为6针或9针接口,能够满足不同外围设备的连接需求。

一种支持国密算法的miniPCI-E密码卡设计

一种支持国密算法的miniPCI-E密码卡设计王玉净;杜君;李延;刘立宗;王大伟;郭艳鹏;汪海燕【摘要】针对目前信息安全领域中数据安全传输和存储的应用需求,以数字信号处理器为载体,设计了基于miniPCI-E总线的密码卡方案.方案实现了数据加解密、数据签名和验证等算法功能,也提供了密钥生成和管理、用户访问权限控制等管理功能,实践表明,其可用于计算机网络系统和其它安全应用系统,解决终端设备中数据通信的安全防护问题,具有加解密速度快、安全性高的特点,且具有良好的通用性.%In view of the application requirements of data security in transmission and storage in the field of information security,a cryp-tography card based on miniPCI-E bus is designed with a Digital Signal Processor(DSP)as the carrier.The design achieves the algorithm functions such as data encryption and decryption,digital signature and inspection keys creation and management,user access control and so on.The practice results show that the card can be used in the computer network systems and other application systems to solve the se-curity problem of data communication in the terminal equipment.Meanwhile,the design has the good characteristics of fast speed,high safety and universality.【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2018(018)001【总页数】4页(P34-37)【关键词】DSP;miniPCI-E;RSA;国密算法【作者】王玉净;杜君;李延;刘立宗;王大伟;郭艳鹏;汪海燕【作者单位】北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;北京智芯微电子科技有限公司国家电网公司重点实验室电力芯片设计分析实验室,北京 100192;北京智芯微电子科技有限公司北京市电力高可靠性集成电路设计工程技术研究中心;国网宁夏电力公司电力科学研究院【正文语种】中文【中图分类】TP309.2引言随着信息革命的兴起和信息时代的到来,许多国家纷纷确立以推进信息化为特征的发展战略。

pcie加密卡工作原理

pcie加密卡工作原理

PCIE加密卡是一种可插入式设备,通过其与计算机的PCI Express(PCIe)插槽相连接,来提供硬件加密的功能。

PCIE加密卡的工作原理如下:

1. 数据传输

在使用PCIE加密卡进行数据加密操作之前,需要将需要加密的数据发送给加密卡。

通过其他硬件设备或网络通信,将需要加密的数据传输到PCIE加密卡上。

2. 硬件加密处理

在PCIE加密卡上,数据传输到达后,PCIE加密卡内部的加密处理器开始对数据进行加密处理。

加密处理器使用先进的加密算法,将需要加密的数据进行加密处理,以保证数据的安全性和私密性。

当数据加密处理完成后,PCIE加密卡将加密后的数据返回到计算机内部。

返回的数据可以被其他程序或设备继续处理,但该数据已被加密处理,只有经过解密才能得到原始数据。

4. 加密密钥保护

在加密处理过程中,PCIE加密卡使用的加密密钥起着至关重要的作用。

为保证加密密钥的安全性,PCIE加密卡将加密密钥保护在内部存储器中,并采用多种保护措施来保护密钥不被非法获取或破解。

5. 维护和管理

为了保证PCIE加密卡能够保持高效的加密操作,其需要得到适时的维护和管理。

管理员可以使用特定的软件来监控加密卡的状态和性能,以便在必要时进行维护和调整。

6. 兼容性

总之,PCIE加密卡是一种高效的数据加密设备,可提供强大的硬件加密能力。

它的工作原理简单、易于理解,并具有良好的兼容性和可扩展性,是保护数据安全的重要手段之一。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

L

加密卡的软件设计

计算机对 #8956 总线接口的读写是通过对内存 映像的读取, 内存地址的确定由 //"@7; 的初始化 内容。主 机 启 动 时, "%&’()* 将 首 先 检 测 //"@7; 的存在完成对它的初始化。 (下转第 CL 页) — C! —

当前的网络, 这是 !"#$ 和最佳化网络服务成功的 重要的问题。 切换是一个处理过程, 通过它, 用户的无线链路 在网络中两个基站之间转换而没有任何用户连接的 中断。当用户在相邻单元间移动时, 切换能为用户 最小化干扰, 也能保证无线连接的完整性和统一性。 简单的说, 切换在移动网络中起到很重要的作用。 它能使用户在无线规定区域限制范围外自由的移动 和通信。在切换的情况下, !"#$ 网络中的用户终 端的连接需要重新路由。网络和无线层是切换事件 的组成部分。 移动路由选择协议 ($%&) 规定怎样把消息发送 到移动主机。它需要知道源和基站地址, 这些都由 位置服务器保存。 互用性和适应性是 !"#$ 网络设计中至关重 要的问题, 因为这些必须提供能通过任何其他网络 基本设施进行自由移动的能力。带有最佳 ’() 标准 化方式的 !"#$ 技术的适应性面对的主要的困难 是无线链路的高误比特率和介质访问协议的约束。 这些问题的解决是通过引入附加的开销完成, 这些 开销用于链路组织, 访问控制和错误保护。协议的 具体特征, 如可允许的带宽限制 (错误保护冗余, 开 销, 保护时间) 、 帧结构、 对上行下行信元业务的不同 处理等, 导致对一些接纳控制的公认方法进行重新 审查。 在错误控制体系的设计中, 希望能根据 !"#$ 信元的不同的灵敏度提供 *+& (不等错误保护) 。这 就引起质量 (编码效率) 和能力 (编码速率) 的交易 (相互交换) 。另外, 在性能要求上不同的 "#$ 服务 必须能被数据链路层协议 ( ,-.) 满足。因此, 基于 ,-. 协 议 能 忽 视 这 些 障 碍, ,-. 协 议 主 要 能 提 高 !"#$ 网络的传送质量。 /0/ 应用 !"#$ 的 !.,$" 系统网络结构 引入 !"#$,在 !.,$" 网 络 主 要 要 增 加 !"#$ 交换机和 !"#$ 复接器。其构成的网络系 统结构简图如图 1。

中图分类号: -8%;% 5 $#

文献标识码: >

文章编号: (!$$%) =$$; ? !::! $# ? $$%$ ? $!

!"# $#%&’( )* +"# #(,-./+ ,0-$ 10%#$ )( 234 5),05 16%

@A /BCDEFBG7

(7#,"0(&,05 0($ 85#,+-&,05 8(’&(##-&(’ 9#/0-+:#(+ )* ;"#(’<")6 4(%+&+6&+# )* !#,"()5)’. 9:$$:!,3"&(0)

!!!!!!!!!!!!!!!!!!!!!!

(上接第 29 页)

"S% 单片机的软件设计主要是加密算法子程序和 单片 &. 机之间的数据传输子程序以及密码的存放, 机的程序由汇编语言编写。 &. 机主程序的设计主要是商用软件以及和加 密卡之间的数据交换。需要加密的商业软件是期货 在线查询系统, 此系统是采用 S. 完成的, 相应的加 密软件只要内嵌入此商业软件即可。

R

结束语

根据本文所述方案, 开发了基于 &.5 总线的加 密卡, 用 3. 编制了上位机的接口程序, 用汇编编写 了单片机程序。该加密卡已通过了各项性能测试, 实现了从 5)" 加密卡到 &.5 加密卡的平稳过度, 为 进一步的产品化打下基础。 参 考 文 献:

[9] 曾凡太, 陈美金 0 &.5 总线产品的开发 0 计算机世界, (U) : 9FFT, 9GF 0 [/] 林勇, 周晓雁 0 微机总线及其发展 0 微型机与应用, (R) : 9FFR, 9T 0 [2] 李贵山, 戚德虎 0 &.5 局部总线开发者指南 0 西安电子科技大学 出版社, 9FFU 0 [1] 宋建国 0 "S% 单片机原理及应用 0 北京航空航天大学出版社, 9FFV 0 责任编辑: 张棣

图1 应用 !"#$ 的 !.,$" 网络结构简图

信要求, 应用还是艰巨和漫长的过程, 还需要广大的 通信科研工作者不断努力。 参 考 文 献:

[9] 陈浩 0 "#$ 无线传输 0 :;;<: ==>>>0 ;?@?0 A(B0 AC[ +3=D-] 0 [/] 马丁 ・ 德 ・ 普瑞克著 0 程时瑞, 刘斌译 0 异步传递方式 4 宽带 5)E ,6 技术 0 人民邮电出版社, 9FFF 0 99 0 [2] 吴伟陵 0 移动通信中的关键技术 0 北京邮电大学出版社, /GG9 0 99 0 [1] $(HI@? BJ@;IAKL;ICM IC >IN?@?LL " #$ C?;>(NOL ,0 4 P0 PIB KCQ .0 4 P0 (R) : #(:$(HI@? 6?;>(NOL KCQ "<<@IAK;I(CL0 /GGG, 9G2 4 99G 0 责任编辑: 张荣香

图!

"%&’()* 结构示意图

*

板上 %". 和 //"@7;

板上 %". 采用 ,12A6 公司的新一代 ,B@ 单片

图* 加密卡的硬件原理图

机 ,>’(+*C;?D 时钟下, 且大多数指令执行时间是单 )(4E; !*( 条精简指令, 时钟周期; 片内有 *F- <65EG 程序存储器, !*H IJ12 和 (使用寿命达 万次) 。采 !*H IJ12 //"@7; !( @,; 用此单片机的意义不在于该机的各项功能强大, 主

第 !" 卷 第 # 期 !$$% 年 # 月

信 息 技 术 &’()*+,-&)’ -./0’)1)23

4)15 !" ’)5 # ,67 5 !$$%

基于 8/& 局部总线硬件加密卡的设计

吴才章

(郑州工程学院机电系,郑州 9:$$:!)

摘

要:介绍了 8/& 专用接口芯片 8/&;$:! 的基本结构,给出了基于 8/& 接口的硬件加密卡的一 种设计方案。,4* 单片机 ,-;$<!%=% 的使用使得此设计方案具有加密性能好,硬件设计比较简 单等优点。 关键词:8/& 协议;,4* 单片机;加密卡

!

"#$"%&’()* 控制器

在众 多 通 用 的 "%& 接 口 芯 片 中, "#$ 公 司 的 "%&’()* 芯片是从 &+, 到 "%& 总线平台平滑过渡的 提 最佳选择。此芯片实现了 "%& 目标设备的功能, 供了与 &+, 总线信号兼容或时序相似的本地总线信 号, 通过这个逻辑接口可以完成由 &+, 到 "%& 的平 滑转换。 图 ! 为 "%&’()* 结构框图。它提供了 "%& -.+、 /0123456 -&7+ 及 #8956 -.+ 三个接口。复杂的 "%& 接 口规范完全由 "%&’()* 实现, 的任务是设计所需的 #8956 -.+ 接口电路及编制 /0123456 -&7+ 代码。 "%& 总线和外加总线的数据传送有四种: :;,、 、 、 直通 。 ;,&#-7$ <&<7 ",++ = = = = >?@. ",++ = 此方 = = = >?@. 主要用于从方式下数据的传送, 式下 "%& 总线可以实时直接读写 #8956 -.+ 接口总 线的数据, 考虑到产品的兼容性和连续性, 本系统采 用直通方式。

$

引言

商业软件防盗常用的加密措施有两种: 一种是

取而代之的是 8/& 总线。如何在原有 &<, 卡的基础 上开发基于 8/& 总线的适配加密卡, 显得很迫切。 8/& 总线是一种能为主 /8A 及外设提供高性能 数据交换的局部总线最高数据传送速率达 =%!+>XO (%! 位) 。 8/& 总线具有严格的规范, 使它具有良好 的兼容性, 符合 8/& 规范的扩展卡可插入任何 8/& 系统可靠的工作。 8/& 总线的协议非常复杂。一般有两种实现方 法: 可编程逻辑器件和 8/& 专用接口芯片。如果开 发 8/& 扩展板使用可编程逻辑器件来完成 8/& 协 议, 要满足大量的时序要求并进行大量的逻辑验证, 其工作量和难度都是巨大的, 这对于时间要求紧的 开发项目是不合适的。选择了 8/& 专用芯片, 复杂 的 8/& 接口规范完全由 8/& 接口芯片来完成。我们 设计 1MKBL >A< 接口电路和编制 .YJHIGBL >&)< 即可, 从而大大加快了设计进程。

C

加密卡的硬件设计

本系统主要由 "%& 接口芯片 "%&’)(* 和 ,B@ 单

片机 ,>’(+*C!C 组成。 "%&’)(* 芯片完成接口卡和 "%& 总线的连接, "%& 的 -&7+ 和 "7+> 由外扩非易失 //"@7; K;’C%LM 完成。采用串行 //"@7; 方法配 置, 对 于 &+, 模 式 #@/+> N 必 须 始 终 为 高 电 平, 处于非复用模式。 ,B@ 单片机 ;7:/ 引脚应接地, 单 ,>’(+*C!C 完成和 "%& 的通信并内置加密算法, 片机中的 //"@7; 用于加密钥匙的存放。系统采 用 ,#>/@, 公 司 <#/$HMCM 可 编 程 芯 片 实 现 设 计 两 片 OL?%*LL 和 两 片 #7%,# 的 接 口 译 码 电 路, OL?%COL 用于实现 ,>’(+*C!C 和 "%& 总线之间数据 交换, 一片 OL?%*LL 接单片机的 - 口, 用于单片机 八位数据的读取, 另一片 OL?%*LL 和单片机的 : 口 相连, 作为控制信号; 一片 OL?%COL 同样接单片机 的 - 口用于向单片机传送数据, 另一片和单片机的 : 口相连作为控制信号。如图 * 所示。