第三章 MCS-51单片机的硬件结构

MCS-51单片机的内部结构及引脚

2021/2/4

1

10

谢谢

2021/2/4

1

11

谢谢!

1

5

结构特点:

MCS-51系列单片机为哈佛结构(而非普林斯顿结构) 1)内ROM:4KB 2)内RAM:128B 3)外ROM:64KB 4)外RAM:64KB 5)I / O线: 32根(4埠,每埠8根) 6)定时/计数器:2个16位可编程定时/计数器 7)串行口:全双工,2 根 8)寄存器区:工作寄存器区、在内128B RAM中,分4个区, 9)中断源:5源中断,2级优先 10)堆栈:最深128B 11)布尔处理机:位处理机,某位单独处理 12)指令系统:五大类,111条

MCS-51单片机的内部结 构及引脚

一、单片机硬件结构

内部结构 引脚功能 内存的配置 CPU时序 I / O接口

2021/2/4

1

2

二、 概述

Intel MCS-51 系列单片机三个版本:8031、8051、 8751(8位机)

Intel MCS-96系列机:8096 (16位机) 除此之外,Motorla公司、Zilog公司、Mcrochip相 继推出产品, 各系列产品内部功能、单元组成、指令系统不尽相 同。 Intel公司单片机问世早,系列齐全,兼容性强,所 以得到广泛使用。

作系统总线、扩展外存、I / O接口芯片

2021/2/4

1

4

5、串行输入/输出口(2条) 串行通信、扩展I / O接口芯片

6、定时/计数器(16位、加1计数) 计满溢出、中断标志置位、向CPU提出中断请求,与 CPU之间独立工作

7、时钟电路 内振、外振。 8、中断系统 五源中断、2级优先。

2021/2/4

2021/2/4

MCS-51单片机的逻辑结构及

2.1 MCS-51单片机的逻辑结构及 信号引脚

MCS-51单片机结构框图 MCS-51芯片内部逻辑结构 MCS-51的信号引脚

MCS-51单片机结构框图

MCS-51芯片内部逻辑结构

1.中央处理器(CPU ) 中央处理器CPU是单片机的核心,完成运算和控 制操作。它包括运算器和控制器电路。 1 )运算器电路 运算器主要用来实现对操作数的算术、逻辑运算 和位操作的。 主要包括算术逻辑运算单元ALU、累加器ACC (A )、暂存寄存器、B 寄存器、程序状态字PSW、 两个暂存器以及BCD码运算修正电路。

其地址为0003h0023h是五个中断源的中断地址区0003h000ah外部中断0中断地址区000bh0012h定时器计数器0中断地址区0013h001ah外部中断1中断地址区001bh0022h定时器计数器1中断地址区0023h002ah串行中断地址区中断服务程序超过8个字节时在中断地址区的首地址存放一条无条件转移指令转移到中断服务程序

专用寄存器地址表

MCS-51的堆栈操作

后进先出 入栈PUSH 出栈POP 1.堆栈的功用 保护断点 保护现场

2.堆栈的开辟 MCS-51的堆栈只能开辟在芯片内部的数据存储器中。 3.堆栈指示器SP 专用寄存器地址81H SP的内容是堆栈栈顶的地址 系统复位后SP的内容是07H 4.堆栈类型

5.堆栈的使用方法 自动方式 调用子程序或中断时 指令方式 使用堆栈操作指令 PUSH、POP

PSW.7 PSW.6 PSW.5 PSW.4 PSW.3 PSW.2 PSW.1 PSW.0

CY AC F0 RS1 RS0 OV 未用 P

进位标志 辅助进位标志 用户标志 寄存器组选择 寄存器组选择 溢出标志 带符号数加减运算 溢出; 乘法积超过8位;除数为0 奇偶标志

MCS-51单片机系统结构

*提供驱动外设的电压或电流; *DMA(直接存储器存取)控制和中断控制。

16

1.1 单片微型计算机

一、单片机的发展历史

第一阶段(1976-1978):单片机的探索阶段。探索

计算机的单芯片集成,单片机(Single Chip Microcomputer) 的定名即缘于此。产品以Intel公司的MCS-48为代表。

9

➢数据总线 DB:CPU与存储器、I/O接口之间 (双向)传送数据的公共通路。 * 数据总线的条数决定CPU一次最多可以传送的

数据宽度(位数)。 如:8位机的DB有8条,CPU一次可读写8位数据

16位机的DB有16条,CPU一次可读写16位

➢控制总线 CB:用来传送各种控制或状态信号 * CPU送出和接受的对存储器、I/O接口读写

运算器 控制器 寄存器组

内存储器

输入输出 接口电路

总线

外部设备

软件

7

二、微型计算机的结构

AB: Address Bus DB: Data Bus CB: Control Bus

微

处

内

存

理

储

器

器

CPU

地址总线 AB

I/O

输

I/O

接

入

接

口

设口备源自输 出 设 备I/O 接 口

数据总线 DB

控制总线 CB

特点: • 以微处理器(CPU)为核心 • CPU与其他部件间通过三总线连接

BUS

I/O接口

C/T

4

系统级——微型计算机系统

• 以微型计算机为中心,配以相应的外围设 备以及控制微型计算机工作的软件,就构 成了完整的微型计算机系统。

MCS-51系列单片机的结构与原理

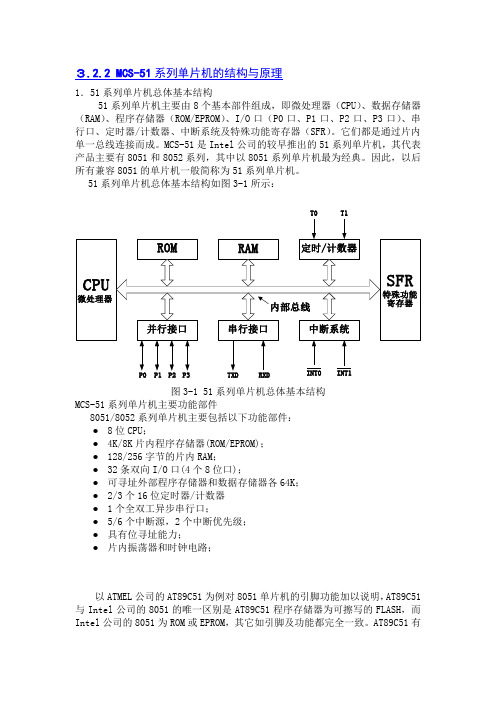

3.2.2 MCS-51系列单片机的结构与原理1.51系列单片机总体基本结构51系列单片机主要由8个基本部件组成,即微处理器(CPU )、数据存储器(RAM )、程序存储器(ROM/EPROM )、I/O 口(P0口、P1口、P2口、P3口)、串行口、定时器/计数器、中断系统及特殊功能寄存器(SFR )。

它们都是通过片内单一总线连接而成。

MCS-51是Intel 公司的较早推出的51系列单片机,其代表产品主要有8051和8052系列,其中以8051系列单片机最为经典。

因此,以后所有兼容8051的单片机一般简称为51系列单片机。

51系列单片机总体基本结构如图3-1所示:CPU微处理器ROM RAM定时/计数器并行接口串行接口中断系统SFR特殊功能寄存器P0P1P2P3TXD RXDINT0INT1T0T1内部总线图3-1 51系列单片机总体基本结构MCS-51系列单片机主要功能部件8051/8052系列单片机主要包括以下功能部件: ● 8位CPU ;● 4K/8K 片内程序存储器(ROM/EPROM); ● 128/256字节的片内RAM ;● 32条双向I/O 口(4个8位口);● 可寻址外部程序存储器和数据存储器各64K ; ● 2/3个16位定时器/计数器 ● 1个全双工异步串行口;● 5/6个中断源,2个中断优先级; ● 具有位寻址能力;● 片内振荡器和时钟电路;以ATMEL 公司的AT89C51为例对8051单片机的引脚功能加以说明,AT89C51与Intel 公司的8051的唯一区别是AT89C51程序存储器为可擦写的FLASH ,而Intel 公司的8051为ROM 或EPROM ,其它如引脚及功能都完全一致。

AT89C51有PDIP 、PQFP 、TQFP 、 PLCC 、LCC 等多种封装形式,图3-3 为AT89C51双列直插式封装PDIP 的引脚图。

RST P3.1P3.2P3.3P3.5P3.4P3.6P3.7P3.0XTAL1GNDXTAL223465781911121315141617101819203938373536343340323029282627252431232221P1.1P1.2P1.3P1.5P1.4P1.6P1.7P1.0P0.1P0.2P0.3P0.5P0.4P0.6P0.7P0.0P2.6P2.5P2.4P2.2P2.3P2.1P2.0P2.7VCCALE/PROG PSENEA/VPP (TXD)(INT0)(INT1)(T1)(T0)(WR)(RD)(RXD)(AD1)(AD2)(AD3)(AD5)(AD4)(AD6)(AD7)(AD0)(A14)(A13)(A12)(A10)(A11)(A9)(A8)(A15)P0口P2口P1口P3口8051图3-2 AT89C51双列直插式封装PDIP 的引脚图● GND (20):接地。

51单片机的基本结构

51单片机的基本结构51单片机是一种高性能、低功耗的微控制器,是嵌入式系统中常用的一种芯片。

它具有集成度高、易编程、可编程性强等特点,在各种电子设备中广泛应用,包括家电、工业控制、汽车电子、智能仪器等领域。

51单片机的基本结构主要包括CPU、存储器、输入输出端口、定时计数器和串口通信等部分。

1.CPU51单片机的CPU是其核心部分,负责执行指令、进行运算处理。

它通常采用哈佛结构,即指令和数据分开存储。

51单片机的CPU主要由ALU (算术逻辑单元)、寄存器组、指令寄存器、程序计数器等部分组成,能够完成基本的运算和控制功能。

2.存储器51单片机的存储器包括ROM(只读存储器)和RAM(随机存储器)。

ROM用于存储程序代码和常量数据,是只读的;RAM用于存储变量数据和临时结果,是可读写的。

在51单片机中,通常ROM用于存储程序代码和初始化数据,RAM用于存储运行时数据和临时结果。

3.输入输出端口51单片机的输入输出端口用于与外部设备进行数据交换。

它可以通过不同的接口与外部设备连接,比如并行口、串行口、通用输入输出口等。

通过输入输出端口,51单片机可以与外部设备进行数据传输和通信,实现各种功能。

4.定时计数器51单片机的定时计数器可以用于计时和计数,通常用于控制时序和频率。

在51单片机中,定时计数器可以生成各种定时中断,实现定时控制功能。

定时计数器可以根据需要设定不同的时钟源和计数模式,实现灵活的定时控制。

5.串口通信51单片机的串口通信功能可以用于与外部设备进行串行通信,比如与PC机、外围设备等进行数据传输。

串口通信包括串行口和UART(通用异步收发器),可以通过串行口进行双向数据传输。

串口通信在51单片机中广泛应用于各种通信设备和控制系统中。

总的来说,51单片机的基本结构包括CPU、存储器、输入输出端口、定时计数器和串口通信等部分,通过这些部分的组合和协作,可以实现各种功能和应用。

在实际应用中,设计人员可以根据需要对这些部分进行配置和扩展,实现更丰富的功能和性能要求。

MCS51单片机的结构

MCS51单片机的结构MCS-51单片机是Intel公司设计开发的一种高度集成的8位微控制器(microcontroller),主要应用于嵌入式系统中。

它采用了Harvard 架构,包含一个CPU核心、片内存储器、外围接口和定时器/计数器等功能模块。

在本文中,我将详细介绍MCS-51单片机的结构。

MCS-51单片机的结构主要分为以下几个部分:1.中央处理器(CPU)核心:MCS-51单片机的CPU核心采用了8位的数据总线和地址总线,以及一组功能强大的指令集。

该CPU支持多种指令,包括数据传送指令、算术逻辑指令、位操作指令和条件跳转指令等。

它还包括一个累加寄存器和标志寄存器,用于存储操作数和标志位信息。

2.存储器部分:MCS-51单片机包含片内存储器和片外存储器。

片内存储器主要用于存储程序代码和数据,包括ROM(只读存储器)和RAM(随机存储器)。

ROM用于存储程序代码,RAM用于存储数据和临时变量。

片外存储器通过地址线和数据线与单片机连接,可以扩展存储器容量。

3.输入输出(I/O)接口:MCS-51单片机通过多个I/O口与外部世界进行数据交互。

每个I/O 口包含一组引脚,可以用作输入或输出。

这些引脚可以通过配置寄存器来选择其功能。

MCS-51单片机还支持中断输入,可以用于实现外部设备的中断功能。

4.定时器/计数器(Timer/Counter):MCS-51单片机内置了多个定时器/计数器模块,用于生成精确的时间延迟或测量外部事件的时间间隔。

定时器可以产生周期性的中断信号,用于实现定时任务。

计数器可以计数外部事件的脉冲数量,用于测量时间间隔。

5.串行通信接口:MCS-51单片机内置了一个串行通信接口,可以用于与其他设备进行数据传输。

该接口支持异步串行通信协议,如UART(通用异步收发器)或SPI(串行外围接口)等。

它可以通过配置寄存器来设置通信参数,如波特率和数据格式等。

6.时钟电路:MCS-51单片机需要一个精确的时钟源来驱动内部运算和外设操作。

3单片机原理与应用(同济出版社魏鸿磊):第三章 MCS-51单片机结构与原理

送。 中断控制系统: 用于响应中断源的中断请求; 时钟电路:为单片机产生时钟脉冲序列,使其正常工作。

DATE: 2019/6/25

PAGE: 5

二、8051单片机引脚

电 源 引 脚 : VCC (40 脚 ) 和 VSS(20脚)分别接供电电源正极 和负极。

P2口结构与工作原理

P2口可以作为通用I/O口 使用,也可在存储器扩展时 作高位地址线使用。

当P2口作为高位地址线使 用时,多路转换开关接通“ 地址”端,从而在P2口的引 脚上输出高8位地址(A8-A15 )。

当P2口作为通用的I/O口 使用时多路转换开关接锁存 器输出端,输出过程与P1口 基本相同。

PAGE: 15

三、并行输入/输出端口结构

P3口做通用I/O口使用

输 出 : “ 第 二 输 出 功 能 ” 信 号线保持高电平,使与非门的 输出由锁存器输出端决定,使 输出信号由锁存器经与非门控 制场效应管的通断得到。

输入:锁存器置“1”且使“ 第二输出功能”线保持高电平 ,从而使场效应管截止,使输 入 数 据 通 过 三 态 缓 冲 器 G2 的 输 出端得到。

由于P1口只能作为通用的I/O 口使用,其输入和输出都由总 线 经 锁 存 器 控 制 , 过 程 与 P0 口 相似。

由 于 电 路 中 已 有 上 拉 电 阻 , 使引脚可获得高电平输出,所 以在使用时无需再外接上拉电 阻。

DATE: 2019/6/25

PAGE: 13

三、并行输入/输出端口结构

4.EA的作用是什么?

5.RST 的作用是什么?

6.ALE 的作用是什么?

51单片机的内部结构

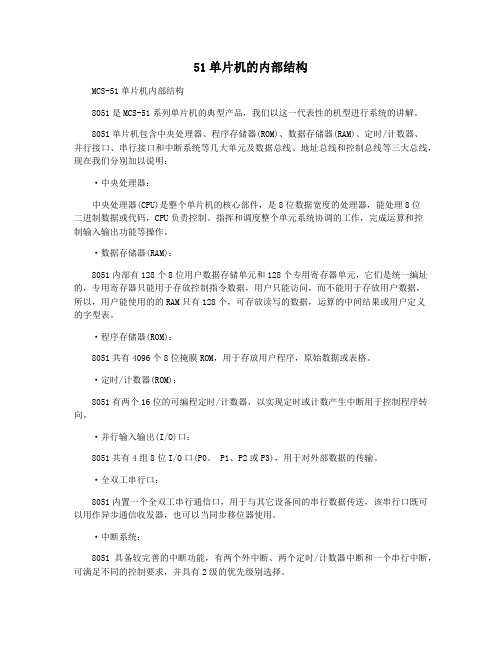

51单片机的内部结构MCS-51单片机内部结构8051是MCS-51系列单片机的典型产品,我们以这一代表性的机型进行系统的讲解。

8051单片机包含中央处理器、程序存储器(ROM)、数据存储器(RAM)、定时/计数器、并行接口、串行接口和中断系统等几大单元及数据总线、地址总线和控制总线等三大总线,现在我们分别加以说明:·中央处理器:中央处理器(CPU)是整个单片机的核心部件,是8位数据宽度的处理器,能处理8位二进制数据或代码,CPU负责控制、指挥和调度整个单元系统协调的工作,完成运算和控制输入输出功能等操作。

·数据存储器(RAM):8051内部有128个8位用户数据存储单元和128个专用寄存器单元,它们是统一编址的,专用寄存器只能用于存放控制指令数据,用户只能访问,而不能用于存放用户数据,所以,用户能使用的的RAM只有128个,可存放读写的数据,运算的中间结果或用户定义的字型表。

·程序存储器(ROM):8051共有4096个8位掩膜ROM,用于存放用户程序,原始数据或表格。

·定时/计数器(ROM):8051有两个16位的可编程定时/计数器,以实现定时或计数产生中断用于控制程序转向。

·并行输入输出(I/O)口:8051共有4组8位I/O口(P0、 P1、P2或P3),用于对外部数据的传输。

·全双工串行口:8051内置一个全双工串行通信口,用于与其它设备间的串行数据传送,该串行口既可以用作异步通信收发器,也可以当同步移位器使用。

·中断系统:8051具备较完善的中断功能,有两个外中断、两个定时/计数器中断和一个串行中断,可满足不同的控制要求,并具有2级的优先级别选择。

·时钟电路:8051内置最高频率达12MHz的时钟电路,用于产生整个单片机运行的脉冲时序,但8051单片机需外置振荡电容。

单片机的结构有两种类型,一种是程序存储器和数据存储器分开的形式,即哈佛(Harvard)结构,另一种是采用通用计算机广泛使用的程序存储器与数据存储器合二为一的结构,即普林斯顿(Princeton)结构。

第3章 MCS-51单片机指令系统

(1)内部数据存储器的低128个字节单元 (00H~7FH)。例: MOV A, 40H ,表示把内 部RAM 40H单元的内容传送给A。 假设40H单元中的内容为2BH,结果是将直接地 址40H单元中的数据2BH传送到累加器A中。

第三章 MCS-51单片机指令系统

3.2.2 直接寻址

(2)特殊功能寄存器。 特殊功能寄存器只能用直接寻址方式进行访问。 对于特殊功能寄存器,在助记符指令中可以直接 用符号来代替地址。例: MOV A, P0 ,表示把 P0口(地址为80H)的内容传送给A。

3.3.1 内部数据存储器传送指令

1.立即数传送指令

MOV A,#data ;A←data MOV Rn,#data ;Rn←data,n=0~7 MOV direct,#data ;direct←data MOV @Ri,#data ;(Ri)←data,i=0,1 MOV DPTR,#data16 ;DPTR←data16 前四条指令将8位立即数传送到指定的存储单元中。 最后一条指令将16位立即数传送到数据指针 DPTR中,其中高8位送入DPH,低8位送入DPL。

(3)三字节指令 编码格式为:

例如数据传送指令MOV 20H,#3AH的编码格式为:

3.2 寻址方式

第三章 MCS-51单片机指令系统

所谓寻址,就是寻找操作数的真正地址,寻址方 式,就是指寻找操作数地址的方式。

在用汇编语言编程时,数据的存放、传送、运算 都要通过指令来完成。 编程者必须自始至终都要 十分清楚操作数的位置, 以及如何将它们传送到适 当的寄存器去参与运算。每一种计算机都具有多 种寻址方式。寻址方式的多少是反映指令系统优 劣的主要指标之一。

2. 汇编语言

汇编语言就是用助记符表示的指令,汇编语言与 机器语言一一对应。用汇编语言编写程序,每条 指令的意义一目了然,给程序的编写、阅读和修 改带来很大方便。而且用汇编语言编写的程序占 用内存少,执行速度快,尤其适用于实时应用场 合的程序设计。因此,在单片机应用系统中主要 是用汇编语言来编写程序。 汇编语言的缺点:缺乏通用性,程序不易移植, 是一种面向机器的低级语言。使用汇编语言编写 程序时,必须熟悉机器的指令系统、寻址方式、 寄存器的设置和使用方法。每种计算机系统都有 它自己的汇编语言。不同计算机的汇编语言之间 不能通用。

MCS-51单片机的硬件结构

MCS-51单⽚机的硬件结构MCS-51单⽚机的基本组成MCS-51是Intel公司⽣产的⼀个单⽚机系列的总称.在功能上,该系列单⽚机有基本型和增强型两⼤类,通常以芯⽚型号的末位数字来区别。

末位数字位“1”的型号是基本型,为“2”的信号是增强型。

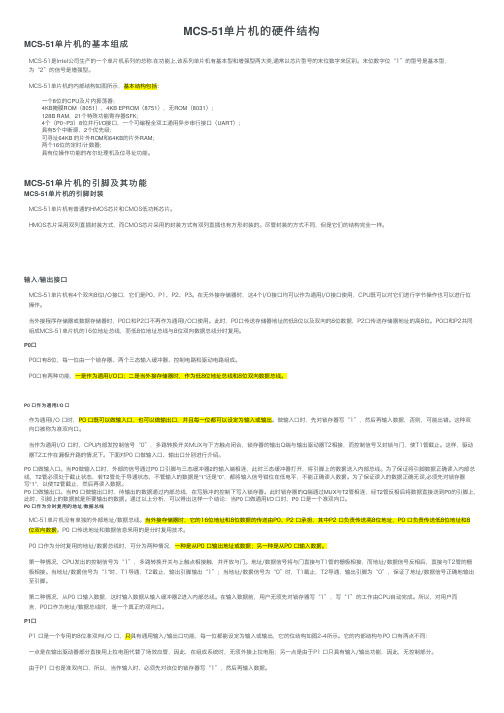

MCS-51单⽚机的内部结构如图所⽰,基本结构包括:⼀个8位的CPU及⽚内振荡器;4KB掩膜ROM(8051),4KB EPROM(8751),⽆ROM(8031);128B RAM,21个特殊功能寄存器SFK;4个(P0~P3)8位并⾏I/O接⼝,⼀个可编程全双⼯通⽤异步串⾏接⼝(UART);具有5个中断源,2个优先级;可寻址64KB 的⽚外ROM和64KB的⽚外RAM;两个16位的定时/计数器;具有位操作功能的布尔处理机及位寻址功能。

MCS-51单⽚机的引脚及其功能MCS-51单⽚机的引脚封装MCS-51单⽚机有普通的HMOS芯⽚和CMOS低功耗芯⽚。

HMOS芯⽚采⽤双列直插封装⽅式,⽽CMOS芯⽚采⽤的封装⽅式有双列直插也有⽅形封装的。

尽管封装的⽅式不同,但是它们的结构完全⼀样。

输⼊/输出接⼝MCS-51单⽚机有4个双向8位I/O接⼝,它们是P0、P1、P2、P3。

在⽆外接存储器时,这4个I/O接⼝均可以作为通⽤I/O接⼝使⽤,CPU既可以对它们进⾏字节操作也可以进⾏位操作。

当外接程序存储器或数据存储器时,P0⼝和P2⼝不再作为通⽤I/O⼝使⽤。

此时,P0⼝传送存储器地址的低8位以及双向的8位数据,P2⼝传送存储器地址的⾼8位。

P0⼝和P2共同组成MCS-51单⽚机的16位地址总线,⽽低8位地址总线与8位双向数据总线分时复⽤。

P0⼝P0⼝有8位,每⼀位由⼀个锁存器、两个三态输⼊缓冲器、控制电路和驱动电路组成。

P0⼝有两种功能,⼀是作为通⽤I/O⼝;⼆是当外接存储器时,作为低8位地址总线和8位双向数据总线。

P0 ⼝作为通⽤I/O ⼝作为通⽤I/O ⼝时,P0 ⼝既可以做输⼊⼝,也可以做输出⼝,并且每⼀位都可以设定为输⼊或输出。

2MCS51单片机的基本结构与工作原理

第二章MCS51单片机的基本结构与工作原理一、8051单片机内部包含哪些主要逻辑功能部件?提示:(1)CPU—包括运算器和控制器。

其中运算器主要有运算逻辑部件ALU(实质上就是一个全加器)、累加器A、暂存器TMP(如B寄存器、数据指针DPTR)、程序状态字PSW(寄存程序运行的状态信息);控制器主要有程序计数器PC(实质是加1计数器)、指令寄存器IR(存放指令操作码的专用寄存器)、指令译码器、定时控制逻辑电路(按指令的性质发出一系列定时信号)、条件转移逻辑电路。

(2)内部RAM。

共有256个RAM单元。

其中低128个单元(00H—7FH)供用户使用,高128个单元(80H—FFH)是专用寄存器,有着特殊逻辑功能(又名特殊功能寄存器SFR)。

(3)内部ROM。

8031内部无ROM,8051有4KB掩膜ROM。

(4)定时/计数器。

MCS51共有2个16位的定时/计数器(T0、T1)。

(5)并行I/O口。

MCS51共有4个8位并行I/O口(P0、P1、P2、P3)。

(6)串行口。

MCS51有1个全双工的串行口。

(7)中断控制系统。

MS51共有5个中断源,且分两个优先级别。

(8)时钟电路。

系统允许的最高晶振频率为12MHz(主要用于通信)。

二、MCS51问片内RAM、片外提示:(1(2)(片内外统一编址空间共64KB)、128个单元中的21个单元SFR,高128个单元中的107个空闲地址,用户不能使用。

切记!)、片外数据存储器(寻址空间64KB)。

(3)从功能上划分为程序存储器、内部数据存储器、特殊功能寄存器、位地址空间、外部数据存储器。

访问片内RAM的指令助记符是MOV;如MOV P1,A访问片外RAM的指令助记符是MOVX;如MOVX @DPTR ,A访问片外ROM的指令助记符是MOVC;如MOVC A,@A+PC三、MCS51单片机片内RAM按用途可以划分几个区域?各有什么作用?(片内RAM低128单元划分哪三个主要部分?各部分主要功能是什么?)提示:片内RAM是最灵活的地址空间,在物理上分成两个独立的功能不同的区域,即低128个单元(00H —7FH)的数据RAM区、高128个单元(80H—FFH)的特殊功能寄存器SFR区(见下一题的回答)。

MCS-51单片机的硬件结构

XTAL1 19

VSS

20

8031 8051 8751

40 VCC 39 P0.0 38 P0.1 37 P0.2 36 P0.3 35 P0.4 34 P0.5 33 P0.6 32 P0.7 31 EA/Vpp 30 ALE/PROG 29 PSEN 28 P2.7

27 P2.6 26 P2.5 25 P2.4 24 P2.3

P1.0 1 P1.1 2 P1.2 3 P1.3 4

P1.4 5 P1.5 6 P1.6 7 P1.7 8 RST/VPD 9

RXD/P3.0

10

TXD/P3.1

11

INT0/P3.2

12

INT1/P3.3

13

T0/P3.4

14

T1/P3.5

15

WR/P3.6

16

RD/P3.7

17

XTAL2 18

17

RD(外部数据存储器读脉

P3.7

冲)

返回本节

2.2 MCS-51单片机的引脚及片外总线结构

2.2.1 MCS-51单片机芯片引脚描述 2.2.2 MCS-51单片机的片外总线结构

返回本章首页

2.2.1 MCS-51单片机芯片引脚描述

图2-7为MCS-51单片机的引脚配置图。 1.主电源引脚VCC和VSS 2.外接晶振引脚XTAL1和XTAL2 3.控制或其他电源复用引脚RST/ VPD、ALE/、 和/VPP 4.输入/输出引脚P0、P1、P2、P3(共32根)

VCC

P2.7 PP22..56 P2.4 P2.3 P2.2 P2.1 P2.0 PPP000...756

P0.3 P0.2 P0.1 P0.0

ALE

MCS51单片机的硬件结构

S3 S4 S5 S6 S1

例:MOV A,#09H

3、指令周期 是执行一条指令所需时间. 指令分为:单字节、双字节、三字节指令. 执行一条指令的时间:简单的1个机器周期,复杂的需2个或多

个机器周期.〔单、双字节指令为单机器周期;三字节都是双机器 周期;乘、除为4个机器周期〕

4、指令时序 执行指令,分为取指阶段和执行指令阶段.

2拍P1、P2,一个时钟周期时钟脉冲可表示为:S1P1,…S6P2〕 〔fosc=6MHz时,Tcy=2μs; fosc=12MHz时,Tcy=1μs 〕

一个机器周期

S1 S2 S3 S4 S5 S6 S1 S2 S3 S4 S5 S6

P1 P2

P1 P2

ALE

读操作码 S1 S2

读下一个操作码(丢弃 ) 单字节单周期指令

*输出电路有上拉电阻〔输出不是三态的,为准双向口〕,在输入数据时, 应先向其锁存器写入1,使输出驱动电路的FET截止.

P2口的位结构电路原理图

四、P3端口 字节地址B0H,位地址B0H~B7H. 作用:通用I/O口;第二功能口.

P3口的位结构电路原理图

2.6 时钟电路与时序

时钟电路→产生时钟控制信号→ 控制单片机严格地按照时序执 行指令.

一、P0端口 字节地址80H,位地址80H~87H. 结构:锁存器,输出驱动电路,输入缓冲器 工作过程: *地址/数据线;

*通用I/O口〔输入时,应先向锁存器写入1;输入分有读引脚、读端口; 输出时须外接上拉电阻〕;

读锁存器

地址/数据 控制 &

内部总线 写入

D锁存器Q CP Q

MUX

VCC P0.x

时序:单片机内的各种操作都是在一系列脉冲〔控制信号〕 控制下进行的,而各个脉冲〔控制信号〕在时间上是有先后顺序的, 这种顺序就称为时序.

2 MCS-51系列单片机的结构和原理

0023H~002AH

地址去执行程序

串行中断地址区

中断响应后,系统能按中断种类,自动转到各中断区的首

但8个单元难以存下一个完整的中断服务程序, 故一般在中断地址区首地址开始存放一条无条件转移指令

JMP、 AJMP以便中断响应后,通过中断地址区,转到

中断服务程序的实际入口地址去

2.3.4 堆栈操作 堆栈只允许在其一端进行数据插入和数据删除操作的线性表 数据写入堆栈称为插入运算(入栈),PUSH 从堆栈中读出数据称为删除运算(出栈),POP

地址:80H~FFH 存放相应功能部件 的控制命令、状态 或数据 21个专用寄存器

(SFR)

(1)累加器A (Accumulator) 累加器A是8位寄存器,又记做ACC,是一个最常用的专用 寄存器。在算术/逻辑运算中用于存放操作数或结果。

(2)寄存器B 寄存器B 是8位寄存器,是专门为乘除法指令设计的,也 作通用寄存器用。

I/O口P0、P1、P2、P3集数据输入缓冲、数据输出驱动及锁

存等多项功能于一体

• 字节地址为90H,位地址为90H~97H,只作通用I/O口使用. • 由一个数据输出锁存器、两个三态输入缓冲器和输出驱动电 路组成。 内有电阻, 输出时无需 外接上拉电 阻 P1口作输出口 使用时: 内部总线 输出数据给输 出数据锁存器 的输入数据线 D.

1. 芯片封装形式

双列直插式DIP(Dual In line Package) 44引脚方形扁平式QFP(Quad Flat Package)

2. 芯片引脚介绍

1)输入/输出口线 4个8位双向口线

2)ALE 地址锁存控制信号 • 在系统扩展时,用于控制把P0口输出的低8位地址

送入锁存器锁存起来,以实现低位地址和数据的分

MCS-51单片机的基本组成

RST/VP D(9脚)

EA/VPP (31脚)

电源端,接+5 V。

RST即为RESET,VPD为 备用电源。

2)晶体振荡器接入或外部振荡信号输入引脚 (1)XTAL1(19脚):晶体振荡器接入的一个引脚。采用外部

振荡器时,此引脚接地。 (2)XTAL2(18脚):晶体振荡器接入的另一个引脚。采用外

方式可以分成两大类:一类是随机存取存储器(random access memory, RAM),主要用于存放暂存数据及调试程序,所以又称为数据存储器;另 一类是只读存储器(read only memory,ROM),主要用于存放常数及固 定程序,又称为程序存储器。

存储器内部结构

Hale Waihona Puke 3.定时器/计数器 8051单片机有两个16位的可编程定时器/计数器T0和T1,用于精

部振荡器时,此引脚作为外部振荡信号的输入端。 3)地址锁存及外部程序存储器编程脉冲信号输入引脚

ALE/PROG(30脚):地址锁存允许信号输出/编程脉冲输入引 脚。ALE为地址锁存允许信号输出引脚,当8051单片机上电正常工 作时,自动在该引脚上输出六分之一晶振频率(fOSC/6)的脉冲序 列。当CPU访问外部存储器时,此信号作为锁存低8位地址的控制信 号。PROG为编程脉冲输入引脚,在对片内ROM编程写入时,作为编 程脉冲输入端。

1.2 单片机的片外总线与引脚功能

1.MCS-51单片机的引脚分布

MCS-51系列单片机引脚图和逻辑图

2.MCS-51单片机的引脚功能 1)电源及复位引脚

接地端。

VCC(40 脚)

VSS(20 脚)

EA为片内外程序存储器选用端。 该引脚为低电平时,只选用片外 程序存储器;该引脚为高电平 时,先选用片内程序存储器,然 后选用片外程序存储器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.2 MCS-51的微处理器

A.程序计数器PC(Program Counter)

一个16位的专用寄存器,用来存放下一 条指令的地址。它具有自动加1的功能。 特点:

▼ 它是16位的按机器周期自动加1计数器。

▼总指向下一条指令所在首地址(当前PC值)

▼ 转移指令可强行改变PC的内容;一切分 支/跳转/调用/中断/复位 等操作的本质就 是:改变 PC 值。

3.2 MCS-51的微处理器

P:奇偶标志位 该标志位始终跟踪累加器A中内容的奇偶 性,每个指令周期由硬件来臵位或清零用以 表示累加器A中1的个数的奇偶性,若累加器 A中1的个数为奇数则P=1,否则P=0。

3.2 MCS-51的微处理器

2.控制器 组成:由程序计数器 PC、指令寄存器 、指令译码器、时序控制与条件转移逻辑电 路等组成。 功能:对来自存储器中的指令进行译 码,通过时序控制电路,在规定的时刻发出 各种操作所需的全部内部和外部控制信号, 协调各功能元件的工作,完成指令所规定的 功能。

可编程全双工 串行口

/ 串行输入 串行输出

8051单片机结构框图

3.1 MCS-51单片机的结构

MCS-51单片机包含的部件: 一个8位CPU 一个片内振荡器及时钟电路 4KB或8KB的程序存储器(ROM) 128B或256B的数据存储器(RAM) 2个16位定时器/计数器 4个8位可编程并行I/O端口 一个可编程全双工串行口 UART 64KB外部数据存储器和64KB外部程序存 储器扩展控制电路 五个中断源/两个优先级嵌套中断结构

3.1 MCS-51单片机的结构

(1)复位信号输入端。 当出现两个机器周 期高电平时,单片机复位 。 (2)备用电源输入端。 Vcc掉电后此引脚可 接备用电源,保护片内RAM中的内容不丢失。 • 复位使单片机进入某种确定的初始状态 • 退出处于节电工作方式的停顿状态、退出 一切程序进程、退出程序的死循环,从头 开始。 • 无论是HMOS型还是CHMOS型的单片机,复 位是靠在RST引脚上施加持续2个机器周期 的高电平来实现的。

3.1 MCS-51单片机的结构

3.1 MCS-51单片机的结构

2. MCS-51单片机的引脚功能

P1.0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7 RST / VPD RXD / P3.0 TXD / P3.1 INT0 / P3.2 INT1 / P3.3 T0 / P3.4

3.2 MCS-51的微处理器

PSW的各状态位定义

位序 位标志 PSW.7 CY PSW.6 AC PSW.5 F0 PSW.4 RS1 PSW.3 RS0 PSW.2 OV PSW.1 PSW.0 P

CY:进位标志位 在执行某些算术和逻辑指令时,可以被 硬件或软件臵位或清零。在算术运算时,如 操作结果的最高位D7有进位或借位时, CY臵 1;否则臵0。在位运算中,它作累加器C使用 ,在位传送、位与和位或等位操作中,都要 使用进位标志位。

3.2 MCS-51的微处理器

D.数据指针DPTR 是一个16位的地址指针寄存器。它主要 用来存放16位地址,作间接地址寄存器使用。 可用来访问64K外部数据存储器和I/O端口。 DPTR也可以拆成两个独立8位寄存器, 即DPH(高8位字节)和DPL(低8位字节), 分别占据83H和82H两个地址。

3.2 MCS-51的微处理器

E. 定时控制部件与时序 功能:在规定的时刻发出各种操作所需 的全部内部和外部的控制信号,协调各 功能元件工作,完成指令所规定的功能。 主要任务:产生单片机工作所需要的基 本时钟。

3.2 MCS-51的微处理器

AC:辅助(半)进位标志 进行加法或减法操作时,当发生低四 位向高四位进位或借位时,AC由硬件臵位 ,否则AC位被臵“0”。在进行十进制调整 指令时,将借助AC状态进行判断。 F0:用户标志位 该位为用户定义的状态标记,用户根 据需要用软件对其臵位或清零,也可以用 软件测试F0来控制程序的跳转。

3.1 MCS-51单片机的结构

1. MC5-51单片机内部功能结构

频率基准源 外部计数器 振荡器及 定时电路 4K字节 程序存储器 内部总线 8051 CPU 128/256字节 数据存储 2个16位 / 定时器/计数器

64K字节总线 扩展控制器

可编程I/O口

内部中断

外部中断 控ห้องสมุดไป่ตู้ 并行I/O口

第三章 MCS-51单片机的硬件结构

MCS-51单片机的结构 MCS-51的微处理器 MCS-51的存储器 MCS-51单片机的并行口结构 I/O端口的直接输入/输出 MCS-51单片机的片外总线结构 简单I/O端口的扩展 MCS-51单片机最小系统 CMOS型单片机的低功耗方式

3.1 MCS-51单片机的结构

+5V

Vcc 10uF RST 10k GND 10k GND

1k

+5V

10uF Vcc RST

上电复位

上电+按钮复位

简单复位电路

3.1 MCS-51单片机的结构

ALE/PROG(30):地址锁存控制端。 (1)地址锁存允许:当单片机访问外部ROM 时,用来锁存由P0口送出的低8位地址。不 访问外部ROM时,提供1/6 fosc振荡频率, 可用于定时或对外输出脉冲。 (2)为8751片内的EPROM输入编程脉冲。 PSEN(29):输出信号,外部程序存储 器ROM的读选通信号端。 执行访问外部ROM指令时,会自动产生 PSEN信号。访问内部ROM或数据存储器RAM指 时,不产生PSEN。

3.1 MCS-51单片机的结构

EA/Vpp (31):内/外ROM选择端 。复 用端 EA=1时,访问内部程序存储器,即内部ROM EA=0时,访问外部程序存储器,即外部ROM 对于8031来说,由于无内部ROM,所以 该引脚必须接地。 对于8751单片机EPROM编程时,Vpp端施 加+21V编程电压。 4)多功能I/O引脚

3.2 MCS-51的微处理器

变址寄存器使用。在MCS-51中由于只有一 个累加器,而单片机中的大部分数据操作都 是通过累加器进行的,故累加器的使用是十 分频繁的。 • B寄存器 B寄存器为8位寄存器,主要用于乘除指 令中。乘法指令的两个操作数分别取自累加 器 A 和寄存器 B,其中 B 为乘数,乘法结果的 高8位存放于寄存器B中。除法指令中,被除 数取自A,除数取自B,除法的结果商数存放

3.1 MCS-51单片机的结构

3.MCS-51系列单片机类型

3.2 MCS-51的微处理器

CPU即中央处理器的简称,是单片机的 核心部件,它完成各种运算和控制操作。 CPU的组成: 运算器 控制器 主要功能: 产生各种控制信号,控制存储器、输入 /输出端口的数据传送、数据的算术运算、 逻辑运算以及位操作处理等。

3.2 MCS-51的微处理器

RS1和RS0:寄存器组选择控制位 该两位通过软件臵“ 0 ”或“ 1 ”来选 择当前工作寄存器组 OV:溢出标志位 当执行算术指令时,由硬件臵位或清 零来指示溢出状态。在带符号的加减运算 中, OV=1表示加减运算结果超出了累加器 A 所能表示的符号数有效范围(- 128 ~+ 127),即运算结果是错误的,反之,OV= 0表示运算正确,即无溢出产生。

Vcc P0.0 P0.1 P0.2 P 0 .3 P0.4 P0.5 P0.6 P0.7 EA / Vpp ALE / PROG PSEN P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

Vcc Vss RST / VPD

XTAL1

8031

P0 口

地 址 数 据 总 线

3.1 MCS-51单片机的结构

• P3口(P3.0~P3.7):P3口同样是内部带上 拉电阻的8位准双向I/O口,P3口除了作为一 般的I/O口使用之外,其还具有特殊功能。 P3口每位的第二功能:

P3.0(RXD):串行输入端。

P3.1(TXD):串行输出端。

P3.2(INTO):外部中断0输入端,低电平有效。 P3.3(INT1):外部中断1输入端,低电平有效。 P3.4(T0):定时/计数器0外部事件计数输入端。 P3.5(T1):定时/计数器1外部事件计数输入端。 P3.6(WR):外部数据存储器写选通信号,低电平有效。 P3.7(RD ):外部数据存储器读选通信号,低电平有效。

3.1 MCS-51单片机的结构

• MCS-51单片机通常采用的简单复位电路有: 上电自动复位、外部脉冲复位、上电+按钮 电平复位、程序运行监视复位等方式。 • 程序运行监视复位 • 程序运行监视复位通常是由各种类型的程 序监视定时器WDT(Watchdog Timer)俗称 为“看门狗”实现。WDT可保证程序非正常 运行(如程序“飞逸”、“死机”)时,能 及时进入复位状态,恢复程序正常运行。

3.2 MCS-51的微处理器

1.运算器 组成:由算术逻运算部件ALU、累加器 ACC、寄存器B、2个8位暂存器、程序状态字 PSW、贝尔处理器等组成 。 功能:对数据完成算术运算,逻辑运 算、循环移位、位处理。 A.算术逻辑单元ALU ALU由加法器和其它逻辑电路等组成。 功能是完成各种算术运算和逻辑运算。

3.2 MCS-51的微处理器

于A,余数存放于 B中。在其它指令中,B寄 存器也可作为一般的数据单元来使用。 • 程序状态字PSW 程序状态字是一个8位寄存器,它包含 程序的状态信息。在状态字中,有些位状 态是根据指令执行结果,由硬件自动完成 设臵的,而有些状态位则必须通过软件方 法设定。PSW中的每个状态位都可由软件读 出,PSW的各位定义如下表所示。

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

8031