第3章 32 Bit RISC微处理器 S3C2410A

s3c2410简介

B Host 2个端口的usb host 遵从OHCI Rev 1.0 和USB规范1.1版兼容 B Device 1个端口的USB Device 可带5个节点的USB Device 和USB规范1.1版兼容

6.SD Host 接口 和SD存储卡1.0版协议兼容 和SDIO存储卡1.0版协议兼容 带64个字节的FIFO存储器支持Tx/Rx 基于DMA或基于中断的操作 和多媒体卡2.11版协议兼容

字符型指针(int *)问。

S3C2410实例

1.和诸多元器件组合在一起供平时学习、实 验、开发等使用。 2.宏分布数字化工业测控系统 3.数码汽车音响和汽车综合信息监测系统 4.煤矿远程数字化测控安全系统 5.视频监控系统

s3c2410引脚介绍

S3C2410共有272引脚,采 用FBGA封装,主要分为 总线控制信号、各类元器 件接口信号以及电源时钟 控制信号。引脚分布底视 图如图所示。各引脚名称 如书中表所示。

s3c2410特殊功能寄存器

寄存器的状态决定硬件如何工作,为了使硬件工作于某 种状态,可以通过修改寄存器的值来实现。 例如:S3C2410X处理器的工作频率可达203MHz,但决不是只 能工作于该频率。可以通过修改内部寄存器的值,使处理器 工作在不同的频率下,通常所说的超频就是通过修改CPU的 时钟相关的寄存器的值来实现的。 在S3C2410的地址空间0x48000000~0x60000000之间, 存有大量的SFR(Special Function Registers,特殊功能 寄存器)用于实现对内部外围模块的控制。

三星ARM2410简介

1.S3C2410 概述 2.S3C2410主要特性 3.s3c2410引脚介绍 4.s3c2410特殊功能寄存器 5.S3C2410实例

《计算机硬件技术基础(第三版)》第3章 32位微处理器

(1)总线接口部件 总线接口部件与片内Cache外部总线接口实行的是逻辑接口连接。当访问 Cache出现没命中、或需更改系统存储器内容、或需向Cache写入某些信 息时,就要通过总线接口从外部存储器系统中取出一批数据。 (2)预取缓冲部件 预取缓冲部件 取指令是指从高速缓冲存储器Cache内或从内存储器中取出指令代码, 以备译码之用的操作。 (3)指令译码部件 指令译码部件 译码操作, 一是检查一条指令的格式, 二是确定它是哪种类型操作的指令,并给出这条指令所需的操作数。 (4)控制部件 控制部件 Pentium微处理器控制部件的作用是,负责解释来自指令译码部件的 指令字和控制ROM的微代码。控制部件的输出控制着整数流水线部件和 浮点部件。 (5)执行部件 执行部件 是微处理器用于执行指令所规定的具体操作的CPU的核心硬件部分。 这些非常具体的操作是指诸如数值运算、逻辑操作以及分支转移处理等。

为了支持在Pentium内采用的分支转移预测新技术,芯片内装备有两个 预取缓冲存储器,一个是以线性方式来预取代码,另一个则是根据分支转 移目标缓冲器(BTB)预取代码。这样就可以保证在执行之前将所需用的 指令从存储器预取出来。 由于Pentium采用了这项技术,可以在无延迟的情况下正确地预测各 种转移。另外,V流水线中的条件转移指令可以与一条比较类指令成对执 行,当然也可以与U流水线中的置标志指令配合执行。但Pentium作到了 与现有软件是完全兼容,所以不必修改现有软件。

计算机硬件技术基础

3.1 .

CISC和RISC 和

1 复杂指令系统计算机 复杂指令系统计算机—CISC 每一种微处理器的CPU都有属于它自己的指令系统。 CPU正是通过执行一系列的特定的指令来实现应用程序 的某种功能。像Intel x86系列,为了增加新的功能, 就必须增加新的指令;另一方面,为了保持向上兼容, 又必须保留原有的指令。每条指令又有若干个不同的操 作字段,用来说明要操作的数据类型,以及存放的位置。 这就意味着一个较大的指令系统和复杂的寻址技术。以 这样的微处理器为平台的计算机系统就是“复杂指令系 统计算机”(CISC)。 CISC也有许多优点,如指令经编译后生成的指令程 序较小执行起来较快,节省硬件资源。像存取指令的次 数少,占用较少的存储器等。

星S3C2440微处理器

应用实例一:嵌入式系统开发

嵌入式系统开发

星S3C2440微处理器适用于嵌入 式系统开发,其强大的处理能力 和丰富的外设接口使其成为嵌入 式领域的理想选择。

实时操作系统

星S3C2440微处理器支持实时操 作系统(RTOS)的开发,RTOS 能够提供实时任务调度和多任务 处理能力,满足实时系统的需求。

3

APB和ASB总线

APB和ASB总线用于连接低速外设,如GPIO、 UART等。

03

星S3C244ห้องสมุดไป่ตู้微处理器的指令集 架构

指令集架构概述

ARM架构

01

S3C2440微处理器采用ARM架构,属于精简指令集(RISC)的

范畴。

指令集发展历程

02

ARM架构的指令集经过多年的发展,已成为移动设备和嵌入式

指令集功能

数据处理指令

用于执行算术、逻辑、移位等基本操 作。

控制流程指令

用于控制程序的执行流程,如条件判 断、跳转等。

内存访问指令

用于读写内存和访问外部存储器。

协处理器指令

用于执行特定功能,如浮点运算、加 密等。

指令集实现方式

汇编语言

使用汇编语言编写程序,通过汇编器将汇编代码转换 为机器码。

C/C语言

星S3C2440微处理器

• 星S3C2440微处理器概述 • 星S3C2440微处理器的体系结构 • 星S3C2440微处理器的指令集架构

• 星S3C2440微处理器的编程模型 • 星S3C2440微处理器的应用实例

01

星S3C2440微处理器概述

定义与特点

定义

S3C2440是一款由三星公司开发的 ARM920T核的微处理器。

S3C2410A芯片及其应用(嵌入式大作业)

论文题目:S3C2410A芯片及其应用姓名:学号:论文要求:针对某一个或一类嵌入式芯片,提出以其为核心的嵌入式系统完整开发方案。

论文结构要求: 1 相应控制器芯片介绍2 硬件开发平台选择与介绍3 软件开发平台选择与介绍4 典型应用实例介绍5 相关参考文献摘要随着计算机技术和通信技术的迅速发展以及Internet的不断扩展,嵌入式系统得到了越来越广泛的应用,成为当前IT产业的焦点之一,呈现出巨大的市场需求。

但同时大量的嵌入式应用也对嵌入式设备的性能和功能提出了更高的要求。

ARM(Advanced RISC Machines)公司的32位RISC处理器,以其高速度、低功耗、低成本、功能强、特有16/32位双指令集等诸多优异的性能,己成为移动通信、手持计算、多媒体数字消费等嵌入式解决方案中的首选处理器。

随着国内嵌入式应用领域的发展,ARM芯片也必然会获得广泛的重视和应用。

在各种嵌入式操作系统中,Linux凭借其在结构清晰、源代码开放等方面的优势,成为了基于监控系统、手持设备等嵌入式系统领域应用中的技术热点。

本文基于ARM9芯片S3C2410A,详细介绍了其芯片功能和结构特点,提出了其硬件开发平台设计方案和软件开发平台设计方案。

并结合智能家居数据采集系统设计实例,重点阐述了利用S3C2410A功能,完成数据采集、数据显示、数据存储以及数据传输(网络控制)的任务。

关键词:嵌入式系统;S3C2410A;开发平台;数据采集1 S3C2410A芯片介绍S3C2410A,是韩国Samsung公司推出的16/32位RISC处理器,它是一颗主频高达203MHz,基于ARM920T内核的高性能微处理器,独立的16KB指令cache和16KB数据cache,MMU虚拟内存管理单元,使得程序运行以及数据存储更加高效,并可以支持,Linux和uCOS-II等多种业内主流的操作系统。

它的低功耗、精简和出色的全静态设计特别适合于低成本和功耗敏感的应用。

利泰恒通 LT-A2410A 嵌入式 RISC 控制板及开发系统套件 使用说明书

LT—A2410 A型嵌入式RISC控制板及开发系统套件使用说明书北京利泰恒通科技发展有限公司一、 简述LT—2410A我公司最新设计的,是采用SAMSUNG2410(ARM9内核)作为微处理器的嵌入式RISC控制板,外形为标准的3.5吋嵌入式主板的设计形式,同时采用底板与核心板分离的设计架构,便于用户扩展,固定可靠,可直接应用在工业、医疗、网络、智能终端,特别是音/视频处理等嵌入式设备的设计和制造中,同时也可作为上述产品的开发、评估及测试使用。

1、系统简述SAMSUNG2410是一款16-32位精减指令(RISC)微处理器,采用ARM920T内核,主频高达400—533MHZ。

处理器本身支持虚拟内存单元管理(MMU)、NAND/NOR FLASH 启动、SDRAM管理、LCD驱动。

同时支持4通道DMA、3通道UART、4路定时器、RTC 实时时钟、IIC总线接口、IIS数字音频接口、8路10位AD及多路I/O控制。

此外,同时支持多路USB主从设备、SPI总线。

是一款速度块、高集成、底功耗的嵌入式处理器。

LT—2410A是以该款处理器为核心的核心板,扩展了形成了最小的核心系统,使之可具备各种用户所需要的通用功能,使用户可以以此为基础,根据需要自行开发扩展板,快速开发出相应的产品。

也可直接将LT—2410A嵌入应用到产品当中,已缩短开发时间。

2、技术特性处理器:S3C2410 处理器,32 位处理器,203MHz内存: 64MB SDRAM64MB NandFlash(或16MB NorFlash)-最高支持12.1寸TFT 800*600 64K色LCD以及触摸屏-10M以太网接口(10/100M可选)-3通道UART(支持IRDA红外线数据通讯口)-4个USB主机接口及1个USB设备接口-SD卡控制器接口-Embedded-ICE调试接口-RTC实时时钟(具备后备锂电池)-IIC总线接口(驱动AT24C04-SC27)-ADC模数转换接口-SPI接口-IIS数字音频输入/输出接口-EINT外部中断接口二、 配置说明LT—A2410A开发套件分为由以下几部分组成:1、LT—2410A 嵌入式控制板一块2、显示部件一套,其中包括:(1)10.4吋TFT液晶一块,分辨率为640*480。

嵌入式系统开发3S3C2410主要外设功能部件

ARM汇编指令

UART异步串口通信

通用I/O端口

Nand Flash控制器

NOR Flash接口电路

1. ARM汇编指令

加载/存储指令

LDR:LDR{条件}目的寄存器,<存储器地址> 用于将存储器中的一个32位的字数据传送到 目的寄存器中;常用于从存储器中读取32为 的字数据到通用寄存器。 ldr r0,=rPCONE //寄存器地址存放到通用寄存器中

GPxCON寄存器:它用于配置引脚的功能 端口A与端口B-H在功能上有所不同,GPACON中每一位对应

一根引脚(共23根引脚);GPACON通常被设为全1,以便访问 外部存储设备;

端口B-H在寄存器操作上完全相同,GPxCon中每两位控制一 根引脚,00表示输入,01表示输出,10表示特殊功能,11保留 不用 GPxDAT寄存器:用于读写引脚

UART LINE CONTROL REGISTER

奇偶模式 停止位数 字节长度

UART CONTROL REGISTER

UART TX/RX STATUS REGISTER

发送器为空 发送缓存器为空 接收缓存器准备

UART TRANSMIT BUFFER REGISTER

UART RECEIVE BUFFER REGISTER

UART TTL电平 3.3V 正逻辑 RS232 +5~+12为低,-12~-5为高 负逻辑 RS485 +2~+6为高,-2~-6为低 正逻辑

电平为线间压差、10Mbps、3000m MAX232、MAX485

UART异步串口的传输格式:

以字符为传输单位 字符间的时间间隔不定,字符内的时间间隔固定 空闲位、起始位、资料位、奇偶校验位、停止位

第3章 32 Bit RISC微处理器 S3C2410A

18

15.看门狗定时器

● 16位看门狗定时器; ● 定时器溢出时产生中断请求或系统复位。 16.I2C总线接口 ● 1通道多主机I2C总线; ● 串行、8位、双向数据传送,在标准模式下数据传 送速率可达100kb/s,在快速模式下可达400kb/s。

19

17.I2S总线接口

● 1通道音频I2S总线接口,可基于DMA方式操作;

17

14. TFT(Thin Film Transistor,薄膜 场效应晶体管)彩色显示特性

● 彩色TFT支持1、2、4或8bpp(bit per pixel,每像素所 占位数)调色显示; ● 支持16bpp无调色真彩显示; ● 在24bpp模式下支持最大16M彩色TFT; 支持多种屏幕尺寸,典型的屏幕尺寸有:640×480, 320×320,160×160或者其它尺寸; ● 最大虚拟屏大小是4 MB; ● 在64彩色模式下支持的最大虚拟屏幕尺寸是:2 048×1 024或者其它尺寸。

4

● 2个USB主设接口/1个USB从设接口(版本1.1); ● 4通道PWM定时器和1通道内部定时器; ● 看门狗定时器; ● 117位通用I/O口和24通道外部中断源; ● 电源控制模式有正常、慢速、空闲和电源关断4种模式; ● 8通道10位ADC和触摸屏接口; ● 具有日历功能的RTC; ● 使用PLL的片上时钟发生器。 S3C2410A的内部结构方框图如图3.1.1所示。

10

5.时钟和电源管理

●

片上MPLL和UPLL:

UPLL产生用于USB主机/设备操作的时钟; MPLL产生操作MCU的时钟,时钟频率最高可达266 MHz (2.0V内核电压)。

● 通过软件可以有选择地为每个功能模块提供时钟。 ● 电源模式包括正常、慢速、空闲和掉电模式: ①正常模式为正常运行模式; ②慢速模式为不加PLL的低时钟频率模式; ③空闲模式只停止CPU的时钟; ④掉电模式切断所有外设和内核的电源。 ● 可以通过EINT[15:0]或RTC报警中断从掉电模式中唤醒处理器。

第3章 ARM的内部资源

• •

3.2.1 bank0总线宽度 总线宽度

•

bank0的数据总线(nGCS0)必须首先设置成 位或 的数据总线( 的数据总线 )必须首先设置成16位或 32位的。因为 位的。 通常作为引导ROM区(映射到地 位的 因为bank0通常作为引导 通常作为引导 区 ),在复位时 址0x0000-0000),在复位时,系统将检测 ),在复位时,系统将检测OM[1:0]上 上 的逻辑电平,并依据这个电平来决定bank0区存储器的 的逻辑电平,并依据这个电平来决定 区存储器的 总线宽度。 总线宽度。

3.1.3 体系结构

• S3C2440处理器为手持设备和通用嵌入式应用提供了丰 处理器为手持设备和通用嵌入式应用提供了丰 富片上集成系统解决方案,包括: 富片上集成系统解决方案,包括: 16/32 位RISC体系结构和 体系结构和ARM920T内核强大的指令集; 内核强大的指令集; 体系结构和 内核强大的指令集 加强的ARM体系结构 体系结构MMU,用于支持 加强的 体系结构 ,用于支持WinCE和Linux; 和 ; 采用ARM920T CPU 内核支持 内核支持ARM调试体系结构; 调试体系结构; 采用 调试体系结构 内部高级微控制总线( 内部高级微控制总线(AMBA)体系结构 )体系结构(AMBA2.0, , AHB/APB); ; 支持高速总线模式和异步总线模式, 支持高速总线模式和异步总线模式,支持外部等待信号 延长总线周期。 延长总线周期。

3.3 S3C2440内部资源详解 内部资源详解

•

S3C2440的内部资源十分丰富,所集成的接口能使得 的内部资源十分丰富, 的内部资源十分丰富 S3C2440方便的运用于各种场合,比如移动设备,工 方便的运用于各种场合, 方便的运用于各种场合 比如移动设备, 业控制设备以及医疗设备中。同时, 业控制设备以及医疗设备中。同时,这些接口使用非常 方便,硬件连接简单, 方便,硬件连接简单,操作上一般通过软件控制寄存器 的方式实现。相信读者看过下面的内容以后, 的方式实现。相信读者看过下面的内容以后,能很快的 进入ARM的内部,为后续的开发工作奠定良好的基础 的内部, 进入 的内部 。

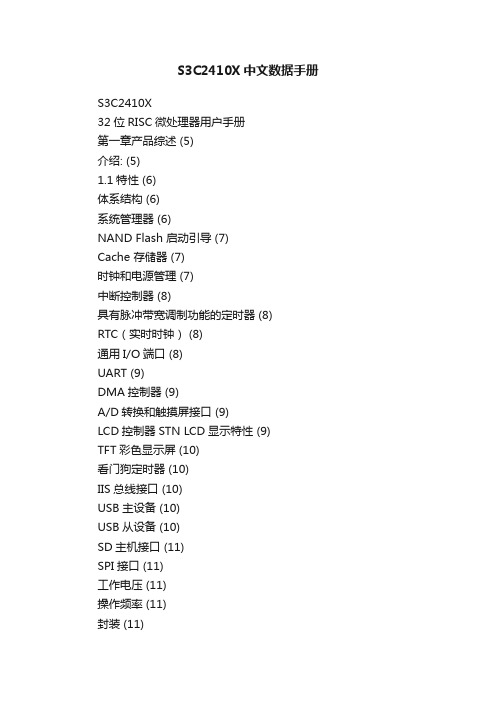

S3C2410X中文数据手册

S3C2410X中文数据手册S3C2410X32位RISC微处理器用户手册第一章产品综述 (5)介绍: (5)1.1特性 (6)体系结构 (6)系统管理器 (6)NAND Flash 启动引导 (7)Cache 存储器 (7)时钟和电源管理 (7)中断控制器 (8)具有脉冲带宽调制功能的定时器 (8)RTC(实时时钟) (8)通用I/O端口 (8)UART (9)DMA控制器 (9)A/D转换和触摸屏接口 (9)LCD控制器STN LCD显示特性 (9)TFT彩色显示屏 (10)看门狗定时器 (10)IIS总线接口 (10)USB主设备 (10)USB从设备 (10)SD主机接口 (11)SPI接口 (11)工作电压 (11)操作频率 (11)封装 (11)1.2 内部结构图 (12)表1-1 272-FBGA引脚分配及顺序 (14)表1-2 272-FBGA封装的引脚分配 (16)表1-3 S3C2410X信号描述 (24)表1-4 S3C2410X特殊功能寄存器 (30)第二章处理器工作模式 (45)2.1 概述 (46)2.2 处理器工作状态 (46)2.3 切换状态 (47)2.4指令长度 (48)2.5操作模式 (48)2.6 寄存器 (49)2.7程序寄存器状态 (51)2.8 异常 (53)第三章 ARM指令集 (59)3.1 指令格式 (60)3.2 条件码 (62)3.3 分支和转换指令(BX) (63)3.4转移及带链接的转移指令(B,BL) (64)3.5 数据处理指令 (65)3.6 PSR 转移指令(MRS,MSR) (71)3.7 乘法及乘加指令(MUL,MLA) (75)3.8 长乘及长乘加指令(MULL,MLAL) (77)3.9单数据传输指令(LDR,STR) (79)3.10半字和带符号的数据传输(LDRH/STRH/LDRSB/LDRSH) (82) 3.11块数据传输(LDM,STM) (87)3.12 单数据传输指令(SWP) (94)3.13 软件中断指令(SWI) (95)3.14 协处理器数据操作(CDP) (97)3.15 协处理器数据传输指令(LDC,STC) (98)3.16 协处理器寄存器传输指令(MRC,MCR) (99)3.17 未定义指令 (99)第五章存储器控制器 (99)5.1 概述 (99)5.2 功能描述 (101)5.2.1 bank0总线宽度 (101)5.2.2 nWAIT引脚的作用 (103)5.2.3 nXBREQ/nXBACK引脚操作 (104)5.3 存储器接口举例 (105)5.4 特殊功能寄存器 (111)5.4.1 总线宽度和等待控制寄存器(BWSCON) (111)5.4.2 总线控制寄存器(BANKCONN:nGCS0-nGCS5) (113)5.4.3 BANK控制寄存器(BANKCONn:nGCS6-nGCS7) (114) 5.4.4 刷新控制寄存器 (115)5.4.5 BANKSIZE 寄存器 (115)5.4.6 SDRAM模式寄存器集寄存器(MRSR) (116)第六章 NAND FLASH寄存器 (117)6.1 概述 (117)6.2 特性 (117)6.2.1 自动导入模式步骤 (118)6.2.3 NAND FLASH存储器时序 (119)6.2.4 管脚配置 (119)6.2.6 NAND Flash存储空间分布 (121)6.3 专用寄存器 (122)6.3.1 NAND FLASH 配置(NFCONF)寄存器 (122)6.3.2 NAND FLASH命令设置(NFCMD)寄存器 (122)6.3.3 NAND flash地址设置(NFADDR)寄存器 (123)6.3.4 NAND FLASH 数据(NFDATA)寄存器 (123)6.3.5 NAND FLASH ECC(NFECC)寄存器 (123)第七章时钟与电源管理 (124)7.1概述: (124)7.2 功能描述 (125)7.2.1 时钟结构: (125)7.2.2锁相环(PLL): (126)7.2.3时钟控制逻辑: (128)7.2.4 加电重启:(XTIpll) (128)7.2.5 USB时钟控制: (130)7.2.7电源管理: (131)7.3 特殊功能寄存器 (138)第8章DMA (141)8.1 概述 (141)8.2 DMA工作过程 (142)8.3 DMA特殊功能寄存器 (146)第九章I/O端口 (152)9.1 概述 (152)9.2 端口功能控制描述 (156)9.3 I/O端口控制专用寄存器 (156)第十章PWM Timer (172)9.1 概述 (172)9.2特性 (173)预定标器和分割器 (174)定时器基本操作 (175)自动加载和双缓冲模式 (175)用手动更新位和逆变器位对定时器进行初始化 (176) 定时器操作步骤: (176)脉宽调制 (177)输出电平控制 (178)死区发生器 (178)DMA请求模式 (179)9.3 PWM定时器专用寄存器 (180)第十一章UART (185)11.1 概述 (185)11.2 UART操作: (186)数据传输: (187)2. 数据接收: (187)3.自动流控制 (187)4.非自动流控制实例(软件控制nRTS及nCTS) (188)5. 中断/DMA请求的产生 (188)6.UART错误状态FIFO (189)7.波特率的产生 (190)8.回环模式 (190)9.红外模式 (191)11.3 UART特殊功能寄存器 (192)第十四章中断控制器 (198)14.1 S3C2410X 中断概述 (198)14.2S3C2410X 中断控制器的操作 (199)14.3S3C2410X 中断源 (199)14.4S3C2410X 中断控制器的特殊功能寄存器 (202) 第十七章RTC (210)17.1 概述 (210)17.2 实时时钟操作 (211)17.3 RTC特殊功能寄存器 (212)第十八章看门狗 (216)18.1 概述 (216)18.2 看门狗定时器特殊功能寄存器 (216)第十九章SD接口 (218)19.1 概述 (218)19.2 SDI特殊功能寄存器 (219)第二十章 IIC (226)20.1 概述 (226)20.2 IIC总线接口 (227)20.3 IIC总线接口特殊功能寄存器 (233)第二十一章IIS总线接口 (235)21.1 概述: (235)21.2 功能描述 (236)21.3 S3C2410X 音频串行接口格式 (236)21.4 S3C2410X IIS接口特殊功能寄存器 (238)第二十二章 SPI (241)22.1 概述 (241)22.2 SPI特殊功能寄存器 (245)第二十三章总线优先权 (248)23.1 概述 (248)23.2 总线优先权 (248)第一章产品综述介绍:本手册描述了三星公司推出的16/32位RISC微处理器S3C2410X。

03 32Bit RISC微处理器S3C2410A

17、IIS总线接口 1通道基于DMA操作的IIS总线音频接口; 串行数据传输,每通道8位或16位; 传送和接收各有64字节的FIFO; 改善音频失真

24

S3C2410特点

18、USB HOST接口 2个USB HOST端口

兼容OHCI标准V1.0

支持USB规范V1.1

输入/输出

输入/输出 输入/输出

nXDREQ1

nXDACK1 nXBREQ

–

– –

GPB5

GPB4 GPB3~GPB0

输入/输出

输入/输出 输入/输出

nXBACK

TCLK0 TOUT3 ~TOUT0

–

– –

45

I/O口

I/O口寄存器

(1)端口配置寄存器(GPACON-GPHCON)

在S3C2410中,大部分的引脚是复用的。所以,对 于每个引脚要求定义一个功能。端口配制寄存器(PnCON) 定义每一个引脚的功能。

35

复位、时钟和电源管理

36

复位、时钟和电源管理

2.时钟电路 S3C2410的主时钟由外部晶振或者外部时钟提供,选择后 可以产生3种时钟信号,分别是CPU使用的FCLK、AHB 总线使用的HCLK和APB总线使用的PCKL。

时钟管理模块同时拥有两个锁相环,一个称为MPLL,用 于FCLK、HCLK和PCLK;另一个称为UPLL,用于USB 设备

25

S3C2410特点

19、USB Device接口 1个USB Device端口 5个USB Device节点 支持USB规范V1.1

26

S3C2410特点

20、SD卡接口(secure digital memory card) 支持SD存储卡协议V1.0 传送和接收均有FIFO 基于中断和DMA操作

第三部分ARM芯片S3C2410简介及硬件系统结构设计

8通道10位ADC;

实时时钟及看门狗定时器等。

两个USB主/一个USB从;

9

S3C2410A特性

内核:1.8V I/O及存储器 : 3.3V

电源管理模式: Normal、Slow、Idle、Power off 272-FBGA

10

本节提要

1 S3C2410A概述 2 3 4 最小系统

13

存储器系统的层次结构

寄存器 高速缓存 Cache

主存储器 SDRAM 本地存储器 Flash、 ROM、磁盘

0

时 钟 周 期

1—10 50—100 20000000

网络存储器 Flash、 ROM、磁盘

14

一个实验箱的存储系统

8M NAND FLASH

32M NOR FLASH

64M SDRAM

AHB

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。 APB APB主要用于低带宽的周边外设之间的连接,例如UART等

6

总线和总线桥

CPU

低速设备

高速总线

桥

低速总线

存储器

高速设备

数据

低速设备

7

S3C2410A的内部结构

8

S3C2410A片上资源

ARM920T核、工作频率203MHz; 16KB 数据Cache, 16KB 指令Cache,MMU,外部存储器控制器; LCD控制器(支持黑白、灰度、Color STN、TFT屏),触摸屏接口; NAND FLASH控制器,SD/MMC接口支持,4个DMA通道; 3通道UART、1个多主I2C总线控制器、1个IIS总线控制器; 4通道PWM定时器及一个内部定时器; 117个通用I/O口; 24个外部中断源;

三星 S3C2410X 32位RISC微处理器 说明书 Revision 1

S3C2410X 32位RISC微处理器用户手册Revision 1修订版1第一章产品概述第一章产品概述 (3)简介 (3)特性 (4)方框图 (8)引脚分配 (9)第一章产品概述简介这个手册描述了SAMSUNG公司的S3C2410X16/32位RISC微处理器。

这个产品计划用于低成本、低功耗和高性能手持设备和一般应用的单片微处理器解决方案。

为了降低系统成本,S3C2410X包含了如下部件:独立的16KB指令和16KB数据缓存,用于虚拟内存管理的MMU 单元,LCD控制器(STN & TFT),非线性(NAND)Flash引导单元,系统管理器(包括片选逻辑和SDRAM控制器),3通道的异步串行口(UART),4个通道的DMA,4个通道的带脉宽调制器(PWM)的定时器,输入输出端口,实时时钟单元(RTC),带有触摸屏接口的8通道10位AD 转换器,IIC总线接口,IIS总线接口,USB的主机(Host)单元,USB的设备(Device)接口,SD卡和MMC(Multi-Media Card)卡接口,2通道SPI接口和锁相环(PLL)时钟发生器。

S3C2410X微处理器是使用ARM920T核、采用0.18um 工艺CMOS标准宏单元和存储编译器开发的。

它的低功耗精简和出色的全静态设计特别适用于对成本和功耗敏感的应用。

应用中,它采用了一种新的总线结构,即高级微控制器总线结构(AMBA)。

S3C2410X的杰出特性是它的CPU核,采用了由ARM公司设计的16/32位ARM920T RISC 处理器。

ARM920T实现了MMU、AMBA总线和独立的16KB指令和16KB数据哈佛结构的缓存,每个缓存均为8个字长度的流水线。

S3C2410X通过提供全面的、通用的片上外设,使系统的全部成本降到最低,并且不需要配置额外的部件。

这个文档将包含以下完整的在片功能的介绍。

1.8V ARM920T内核,1.8V/2.5V/3.3V存储系统,带有3.3V16KB指令和16KB数据缓存及MMU单元的外部O接口的微处理器外部存储器控制(SDRAM控制和芯片选择逻辑)LCD控制器(支持4K颜色的STN或256K色TFT的LCD),带有1个通道的LCD专用DMA控制器 4通道DMA,具有外部请求引脚3通道UART(支持IrDA1.0,16字节发送FIFO及16字节接收FIFO)/2通道SPI接口1个通道多主IIC总线控制器/1通道IIS总线控制器1.0版本SD主机接口及2.11版本兼容的MMC卡协议2个主机接口的USB口/1个设备USB口(1.1版本)4通道PWM定时器/1通道内部计时器看门狗定时器117位通用目的I/O口/24通道外部中断源电源控制:正常、慢速、空闲及电源关闭模式带触摸屏接口的8通道10位ADC带日历功能的实时时钟控制器具有PLL的片上时钟发生器特性体系结构z集成了手持设备和通用嵌入式系统的解决方案z32/16位结构体系和ARM920T CPU核的强大指令体系z增强的ARM MMU体系结构支持WinCE, EPOC 32 和 Linux操作系统z指令缓存、数据缓存、写缓冲器和RAM物理地址标签减少了主存储器带宽和潜在性能的影响 z ARM920T CPU核支持ARM调试体系结构z内置的高级微控制总线体系结构(AMBA)(AMBA2.0,AHB/APB)系统管理器z支持小/大端模式z寻址空间:每个bank 128M字节(总共1G字节)z支持每个bank可编程的8/16/32位数据总线宽度z bank0到bank6具有固定的bank起始地址z bank7具有可编程的bank起始地址和bank大小z共有8个存储器bank:—6个存储器bank用于ROM,SRAM及其它—2个存储器bank用于ROM/SRAM/同步DRAMz所有的存储器bank具有可编程的操作周期z支持外部等待信号延长总线周期z支持掉电时的SDRAM自刷新模式z支持多种类型的引导ROM(NOR/NAND Flash,EEPROM及其它)NAND Flash 引导装载器z支持从NAND flash存储器引导z4KB内置缓冲存储器用于引导z支持引导后从NAND flash存储器向内存加载缓冲存储器z带有指令缓存(16KB)和数据缓存(16KB)的联合缓存装置z每线8字长度,其中每线带有1个有效位和2个无效位z伪随机的或循环移位算法z写通过或写返回缓存来更新主存储器z新缓冲区能够保持16字的数据和4个地址时钟和电源管理z在片MPLL和UPLL:UPLL时钟发生器用于主/从USB操作MPLL时钟发生器用于MCU在极限203MHz@1.8V运行z每一个功能块可以用软件选择时钟z电源模式:正常,慢速,空闲和掉电正常模式:正常操作模式满速模式:不带PLL的低频时钟空闲模式:始终仅使CPU停止下来掉电模式:所有外围设备全部掉电仅内核电源供电z可以从掉电模式借助于EINT[15:0]或RTC报警中断唤醒过来中断控制z55个中断源(1个看门狗定时器,5个定时器,9个通用异步串行口,24个外部中断,4个DMA,2个RTC,2个USB,1个LCD和1个电池故障)z外部中断源具有电平/边沿模式z可编程极性的边沿触发或电平触发z在非常紧急中断的情况下支持快中断请求(FIQ)带脉冲宽度调制器(PWM)的定时器z4通道16位带PWM的定时器/1通道16位基于DMA或基于中断操作的内部定时器z可编程的占空比,频率和极性z失效区发生器z支持外部时钟源RTC(实时时钟)z全部时钟特点:毫秒,秒,分钟,小时)z32.768KHz操作z报警中断z定时中断通用输入输出口:z24个外部中断口z多路输入输出口通用串行异步通讯口(UART)z3通道基于DMA或基于中断操作的UARTz支持5位、6位、7位或8位串行数据发送/接收(Tx/Rx)z可编程的波特率z支持IrDA 1.0z具有测试回送功能z每个通道有内置的16字节发送FIFO和16字节接收FIFODMA控制器z4通道DMA控制器z支持存储器到存储器、IO到存储器、存储器到IO和IO到IO传输z突发传输模式增强了传输速率带触摸屏接口的A/D转换器z8通道多路ADCz最大500KSPS转换速率10位分辨率LCD控制器 STN LCD显示特点z支持3中类型STN LCD面板:4位双屏、4位单屏、8位单屏显示z支持单色模式、4级灰度、16级灰度、256色和4096色STN LCDz支持多种屏幕像素—典型的流行屏幕像素:640x480, 320x240,160x160等—极限虚屏像素:4Mbytes—极限虚屏像素在256色下z显示模式:4096x1024, 2048x2048, 1024x4096等TFT彩色显示特点z支持彩色TFT模式1、2、4或8bpp(位/像素)带调色板彩色显示z支持彩色TFT模式16bpp不带调色板真彩色显示z支持24bpp下最大16M 彩色TFT模式z支持多种屏幕像素—典型的流行屏幕像素:640x480、 320x240、160x160等—极限虚屏像素:4Mbytes—极限虚屏像素在64K色下2048 x1024等看门狗定时器z16位看门狗定时器z超时时发出中断请求或系统复位IIC总线接口z1通道多主IIC总线z串行,能够在标准模式下达到100 Kbit/s或快速模式下达到400 Kbit/s 的8位单向和双向数据传输IIS总线接口z1通道基于DMA的IIS总线用于音频接口z串行,8-/16位每通道数据传输z128字节(64字节+64字节)FIFO用于发送/接收z支持IIS格式和MSB验证数据格式USB主机z2个USB主机口z遵守OHCI 1.0版z兼容USB1.1版本规范USB设备z1个USB设备口z5端点USB设备z兼容USB1.1版本规范SD主接口z与SD存储卡协议1.0版本兼容z与SDIO卡协议1.0版本兼容z具有字节FIFO用于发送/接收z基于DMA或基于中断模式操作z与多媒体卡2.11版本兼容SPI接口z与2通道串行外部接口2.11版本协议兼容z 2 x8位移位寄存器用于发送/接收 z基于DMA或基于中断模式操作工作电压范围z内核1.8Vz存储器:2.5V/3.3Vz输入/输出口:3.3V工作频率z最大203MHZ封装z272-FBGA方框图引脚分配表1-1 272脚FBGA引脚分配——按引脚编号排序(图表3-1)引脚号引脚名引脚号引脚名引脚号引脚名A1DATA19B14ADDR0/GPA0D10ADDR19/GPA4 A2DATA18B15nSRAS D11VDDiA3DATA16B16nBE1:nWBE1:DQM1D12ADDR10A4DATA15B17VSSi D13ADDR5A5DATA11C1DATA24D14ADDR1A6VDDMOP C2DATA23D15VSSMOPA7DATA6C3DATA21D16SCKEA8DATA1C4VDDi D17nGCS0A9ADDR21/GPA6C5DATA12E1DATA31A10ADDR16/GPA1C6DATA7E2DATA29A11ADDR13C7DATA4E3DATA28A12VSSMOP C8VDDi E4DATA30A13ADDR6C9ADDR25/GPA10E5VDDMOPA14ADDR2C10VSSMOP E6VSSMOPA15VDDMOP C11ADDR14E7DATA3A16nBE3:nWBE3:DQM3C12ADDR7E8ADDR26/GPA11A17nBE0:nWBE0:DQM0C13ADDR3E9ADDR23/GPA8B1DATA22C14nSCAS E10ADDR18/GPA3 B2DATA20C15nBE2:nWBE2:DQM2E11VDDMOPB3DATA17C16nOE E12ADDR11B4VDDMOP C17VDDi E13nWEB5DATA13D1DATA27E14nGCS3/GPA14 B6DATA9D2DATA25E15nGCS1/GPA12 B7DATA5D3VSSMOP E16nGCS2/GPA13 B8DATA0D4DATA26E17nGCS4/GPA15 B9ADDR24/GPA9D5DATA14F1TOUT1/GPB1 B10ADDR17/GPA2D6DATA10F2TOUT0/GPB0 B11ADDR12D7DATA2F3VSSMOPB12ADDR8D8VDDMOP F4TOUT2/GPB2 B13ADDR4D9ADDR22/GPA7F5VSSOP引脚号引脚名引脚号引脚名引脚号引脚名F6VSSi H4nXDREQ1/GPB8K13TXD2/nRTS1/GPH6 F7DATA8H5nTRST K14RXD1/GPH5F8VSSMOP H6TCK K15TXD0/GPH2F9VSSi H12CLE/GPA17K16TXD1/GPH4F10ADDR20/GPA5H13VSSOP K17RXD0/GPH3F11VSSi H14VDDMOP L1VD0/GPC8F12VSSMOP H15VSSi L2VD1/GPC9F13SCLK0H16XTOpll L3LCDVF2/GPC7F14SCLK1H17XTIpll L4VD2/GPC10F15nGCS5/GPA16J1TDI L5VDDiarmF16nGCS6:nSCS0J2VCLK:LCD_HCLK/GPC1L6LCDVF1/GPC6F17nGCS7:nSCS1J3TMS L7IICSCL/GPE14G1nXBACK/GPB5J4LEND:STH/GPC0L9EINT11/nSS1/GPG3 G2nXDACK1/GPB7J5TDO L11VDDi_UPLLG3TOUT3/GPB3J6VLINE:HSYNC:CPV/GPC2L12nRTS0/GPH1G4TCLK0/GPB4J7VSSiarm L13UPLLCAPG5nXBREQ/GPB6J11EXTCLK L14nCTS0/GPH0 G6VDDalive J12nRESET L15EINT6/GPF6 G7VDDiarm J13VDDi L16UCLK/GPH8 G9VSSMOP J14VDDalive L17EINT7/GPF7 G11ADDR15J15PWREN M1VSSiarmG12ADDR9J16nRSTOUT/GPA21M2VD5/GPC13 G13nWAIT J17nBATT_FLT M3VD3/GPC11 G14ALE/GPA18K1VDDOP M4VD4/GPC12 G15nFWE/GPA19K2VM:VDEN:TP/GPC4M5VSSiarmG16nFRE/GPA20K3VDDiarm M6VDDOPG17nFCE/GPA22K4VFRAME:VSYNC:STV/GPC3M7VDDiarmH1VSSiarm K5VSSOP M8IICSDA/GPE15 H2nXDACK0/GPB9K6LCDVF0/GPC5M9VSSiarmH3nXDREQ0/GPB10K12RXD2/nCTS1/GPH7M10DP1/PDP0引脚号引脚名引脚号引脚名引脚号引脚名M11EINT23/nYPON/GPG15P8SPICLK0/GPE13T5I2SLRCK/GPE0M12RTCVDD P9EINT12/LCD_PWREN/GPG4T6SDCLK/GPE5M13VSSi_MPLL P10EINT18/GPG10T7SPIMISO0/GPE11 M14EINT5/GPF5P11EINT20/XMON/GPG12T8EINT10/nSS0/GPG2 M15EINT4/GPF4P12VSSOP T9VSSOPM16EINT2/GPF2P13DP0T10EINT17/GPG9M17EINT3/GPF3P14VDDi_MPLL T11EINT22/YMON/GPG1 4N1VD6/GPC14P15VDDA_ADC T12DN0N2VD8/GPD0P16XTIrtc T13OM3N3VD7/GPC15P17MPLLCAP T14VSSA_ADCN4VD9/GPD1R1VDDiarm T15AIN1N5VDDiarm R2VD14/GPD6T16AIN3N6CDCLK/GPE2R3VD17/GPD9T17AIN5N7SDDAT1/GPE8R4VD18/GPD10U1VD15/GPD7N8VSSiarm R5VSSOP U2VD19/GPD11N9VDDOP R6SDDAT0/GPE7U3VD21/GPD13N10VDDiarm R7SDDAT3/GPE10U4VSSiarmN11DN1/PDN0R8EINT8/GPG0U5I2SSDI/nSS0/GPE3N12Vref R9EINT14/SPIMOSI1/GPG6U6I2SSDO/I2SSDI/GPE4 N13AIN7R10EINT15/SPICLK1/GPG7U7SPIMOSI0/GPE12N14EINT0/GPF0R11EINT19/TCLK1/GPG11U8EINT9/GPG1N15VSSi_UPLL R12CLKOUT0/GPH9U9EINT13/SPIMISO1/G PG5N16VDDOP R13R/nB U10EINT16/GPG8N17EINT1/GPF1R14OM0U11EINT21/nXPON/GPG 13P1VD10/GPD2R15AIN4U12CLKOUT1/GPH10 P2VD12/GPD4R16AIN6U13NCONP3VD11/GPD3R17XTOrtc U14OM2P4VD23/nSS0/GPD15T1VD13/GPD5U15OM1P5I2SSCLK/GPE1T2VD16/GPD8U16AIN0P6SDCMD/GPE6T3VD20/GPD12U17AIN2P7SDDAT2/GPE9T4VD22/nSS1/GPD14--引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型C3DATA21DATA21Hi-z Hi-z I t12 B1DATA22DATA22Hi-z Hi-z I t12 C2DATA23DATA23Hi-z Hi-z I t12 D3VSSMOP VSSMOP P P P s3o E5VDDMOP VDDMOP P P P d3o C1DATA24DATA24Hi-z Hi-z I t12 D2DATA25DATA25Hi-z Hi-z I t12 D4DATA26DATA26Hi-z Hi-z I t12 D1DATA27DATA27Hi-z Hi-z I t12 E3DATA28DATA28Hi-z Hi-z I t12 E2DATA29DATA29Hi-z Hi-z I t12 E4DATA30DATA30Hi-z Hi-z I t12 E1DATA31DATA31Hi-z Hi-z I t12 F3VSSMOP VSSMOP P P P s3o F5VSSOP VSSOP P P P s3o F2TOUT0/GPB0GPB0–/–O(L)/–I t8 F1TOUT1/GPB1GPB1–/–O(L)/–I t8 F4TOUT2/GPB2GPB2–/–O(L)/–I t8 G3TOUT3/GPB3GPB3–/–O(L)/–I t8 G4TCLK0/GPB4GPB4–/––/–I t8 G1nXBACK/GPB5GPB5–/––/–I t8 G5nXBREQ/GPB6GPB6–/––/–I t8 G2nXDACK1/GPB7GPB7–/––/–I t8 G6VDDalive VDDalive P P P d1i G7VDDiarm VDDiarm P P P d1c H1VSSiarm VSSiarm P P P s3i H4nXDREQ1/GPB8GPB8–/––/–I t8 H2nXDACK0/GPB9GPB9–/––/–I t8 H3nXDREQ0/GPB10GPB10–/––/–I t8 H5nTRST nTRST I I I is H6TCK TCK I I I is J1TDI TDI I I I is J3TMS TMS I I I is引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型J5TDO TDO O O O ot J4LEND:STH/GPC0GPC0–/–O(L)/–I t8 J2VCLK:LCD_HCLK/GPC1GPC1–/–O(L)/–I t8 J6VLINE:HSYNC:CPV/GPC2GPC2–/–O(L)/–I t8 K3VDDiarm VDDiarm P P P d1c J7VSSiarm VSSiarm P P P s3i K2VM:VDEN:TP/GPC4GPC4–/–O(L)/–I t8 K4VFRAME:VSYNC:STV/GPC3GPC3–/–O(L)/–I t8 K1VDDOP VDDOP P P P d3o K5VSSOP VSSOP P P P s3o K6LCDVF0/GPC5GPC5–/–O(L)/–I t8 L6LCDVF1/GPC6GPC6–/–O(L)/–I t8 L3LCDVF2/GPC7GPC7–/–O(L)/–I t8 L1VD0/GPC8GPC8–/–O(L)/–I t8 L2VD1/GPC9GPC9–/–O(L)/–I t8 L4VD2/GPC10GPC10–/–O(L)/–I t8 M3VD3/GPC11GPC11–/–O(L)/–I t8 L5VDDiarm VDDiarm P P P d1c M1VSSiarm VSSiarm P P P s3i M4VD4/GPC12GPC12–/–O(L)/–I t8 M2VD5/GPC13GPC13–/–O(L)/–I t8 N1VD6/GPC14GPC14–/–O(L)/–I t8 N3VD7/GPC15GPC15–/–O(L)/–I t8 N2VD8/GPD0GPD0–/–O(L)/–I t8 N4VD9/GPD1GPD1–/–O(L)/–I t8 P1VD10/GPD2GPD2–/–O(L)/–I t8 P3VD11/GPD3GPD3–/–O(L)/–I t8 P2VD12/GPD4GPD4–/–O(L)/–I t8 R1VDDiarm VDDiarm P P P d1c M5VSSiarm VSSiarm P P P s3i T1VD13/GPD5GPD5–/–O(L)/–I t8 R2VD14/GPD6GPD6–/–O(L)/–I t8 U1VD15/GPD7GPD7–/–O(L)/–I t8引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型T2VD16/GPD8GPD8–/–O(L)/–I t8 R3VD17/GPD9GPD9–/–O(L)/–I t8 R4VD18/GPD10GPD10–/–O(L)/–I t8 U2VD19/GPD11GPD11–/–O(L)/–I t8 T3VD20/GPD12GPD12–/–O(L)/–I t8 U3VD21/GPD13GPD13–/–O(L)/–I t8 T4VD22/nSS1/GPD14GPD14–/–O(L)/–I t8 P4VD23/nSS0/GPD15GPD15–/–O(L)/–I t8 N5VDDiarm VDDiarm P P P d1c U4VSSiarm VSSiarm P P P s3i M6VDDOP VDDOP P P P d3o R5VSSOP VSSOP P P P s3o T5I2SLRCK/GPE0GPE0–/–O(L)/–I t8 P5I2SSCLK/GPE1GPE1–/–O(L)/–I t8 N6CDCLK/GPE2GPE2–/–O(L)/–I t8 U5I2SSDI/nSS0/GPE3GPE3–/–/––/–/–I t8 U6I2SSDO/I2SSDI/GPE4GPE4–/–/–O(L)/–/–I t8 T6SDCLK/GPE5GPE5–/–O(L)/–I t8 P6SDCMD/GPE6GPE6–/–Hi-z/–I t8 R6SDDAT0/GPE7GPE7–/–Hi-z/–I t8 N7SDDAT1/GPE8GPE8–/–Hi-z/–I t8 P7SDDAT2/GPE9GPE9–/–Hi-z/–I t8 R7SDDAT3/GPE10GPE10–/–Hi-z/–I t8 T7SPIMISO0/GPE11GPE11–/–Hi-z/–I t8 U7SPIMOSI0/GPE12GPE12–/–Hi-z/–I t8 P8SPICLK0/GPE13GPE13–/–Hi-z/–I t8 M7VDDiarm VDDiarm P P P d1c N8VSSiarm VSSiarm P P P s3i L7IICSCL/GPE14GPE14–/–Hi-z/–I d8 M8IICSDA/GPE15GPE15–/–Hi-z/–I d8 R8EINT8/GPG0GPG0–/––/–I t8 U8EINT9/GPG1GPG1–/––/–I t8 T8EINT10/nSS0/GPG2GPG2–/–/––/–/–I t8引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型L9EINT11/nSS1/GPG3GPG3–/–/––/–/–I t8 P9EINT12/LCD_PWREN/GPG4GPG4–/–/––/O(L)/–I t8 U9EINT13/SPIMISO1/GPG5GPG5–/–/––/Hi-z/–I t8 R9EINT14/SPIMOSI1/GPG6GPG6–/–/––/Hi-z/–I t8 T9VSSOP VSSOP P P P s3o N9VDDOP VDDOP P P P d3o N10VDDiarm VDDiarm P P P d1c M9VSSiarm VSSiarm P P P s3i R10EINT15/SPICLK1/GPG7GPG7–/–/––/Hi-z/–I t8 U10EINT16/GPG8GPG8–/––/–I t6 T10EINT17/GPG9GPG9–/––/–I t6 P10EINT18/GPG10GPG10–/––/–I t6 R11EINT19/TCLK1/GPG11GPG11–/–/––/–/–I t12 P11EINT20/XMON/GPG12GPG12–/–/––/O(L)/–I t12 U11EINT21/nXPON/GPG13GPG13–/–/––/O(L)/–I t12 T11EINT22/YMON/GPG14GPG14–/–/––/O(L)/–I t12 M11EINT23/nYPON/GPG15GPG15–/–/––/O(L)/–I t12 R12CLKOUT0/GPH9GPH9–/–O(L)/–I t12 U12CLKOUT1/GPH10GPH10–/–O(L)/–I t12 M10DP1/PDP0DP1––AI us N11DN1/PDN0DN1––AI us P13DP0DP0––AI us T12DN0DN0––AI us U13NCON NCON––I is R13R/nB R/nB––I is T13OM3OM3––I is U14OM2OM2––I is U15OM1OM1––I is R14OM0OM0––I is P12VSSOP VSSOP P P P s3oT14VSSA_ADC VSSA_ADCP P P s3tN12Vref Vref––AI ia U16AIN0AIN0––AI r10引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型T15AIN1AIN1––AI r10 U17AIN2AIN2––AI r10 T16AIN3AIN3––AI r10 R15AIN4AIN4––AI r10 T17AIN5AIN5––AI r10 R16AIN6AIN6––AI r10 N13AIN7AIN7––AI r10P15VDDA_ADC VDDA_ADCP P P d3tR17XTOrtc XTOrtc––AO gp P16XTIrtc XTIrtc––AI gp M12RTCVDD RTCVDD P P P d1iP14VDDi_MPLL VDDi_MPLLP P P d1cM13VSSi_MPLL VSSi_MPLLP P P s3iP17MPLLCAP MPLLCAP––AI gpL11VDDi_UPLL VDDi_UPLLP P P d1cN15VSSi_UPLL VSSi_UPLLP P P s3iL13UPLLCAP UPLLCAP––AI gp N16VDDOP VDDOP P P P d3o N14EINT0/GPF0GPF0–/––/–I t8 N17EINT1/GPF1GPF1–/––/–I t8 M16EINT2/GPF2GPF2–/––/–I t8 M17EINT3/GPF3GPF3–/––/–I t8 M15EINT4/GPF4GPF4–/––/–I t8 M14EINT5/GPF5GPF5–/––/–I t8 L15EINT6/GPF6GPF6–/––/–I t8 L17EINT7/GPF7GPF7–/––/–I t8 L16UCLK/GPH8GPH8–/––/–I t8 L14nCTS0/GPH0GPH0–/––/–I t8 L12nRTS0/GPH1GPH1–/–O(H)/–I t8 K15TXD0/GPH2GPH2–/–O(H)/–I t8 K17RXD0/GPH3GPH3–/––/–I t8 K16TXD1/GPH4GPH4–/–O(H)/–I t8 K14RXD1/GPH5GPH5–/––/–I t8引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型K13TXD2/nRTS1/GPH6GPH6–/–O(H)/–I t8 K12RXD2/nCTS1/GPH7GPH7–/––/–I t8J17nBATT_FLT nBATT_FLT––I isJ16nRSTOUT/GPA21nRSTOUT–/–O(L)/–O b8 J15PWREN PWREN O(H)O(L)O b8 J12nRESET nRESET––I isJ14VDDalive VDDalive P P P d1i J11EXTCLK EXTCLK––AI isJ13VDDi VDDi P P P d1c H17XTIpll XTIpll––AI m26 H16XTOpll XTOpll––AO m26 H15VSSi VSSi P P P s3i H13VSSOP VSSOP P P P s3o H14VDDMOP VDDMOP P P P d3o G17nFCE/GPA22nFCE O(H)/–O(H)/–O b8 G16nFRE/GPA20nFRE O(H)/–O(H)/–O b8 G15nFWE/GPA19nFWE O(H)/–O(H)/–O b8 G14ALE/GPA18ALE O(L)/–O(L)/–O b8 H12CLE/GPA17CLE O(L)/–O(L)/–O b8 G13nWAIT nWAIT––I isF17nGCS7:nSCS1nGCS7Hi-z O(H)O ot F16nGCS6:nSCS0nGCS6Hi-z O(H)O ot F15nGCS5/GPA16nGCS5Hi-z O(H)/–O ot E17nGCS4/GPA15nGCS4Hi-z O(H)/–O ot E14nGCS3/GPA14nGCS3Hi-z O(H)/–O ot E16nGCS2/GPA13nGCS2Hi-z O(H)/–O ot E15nGCS1/GPA12nGCS1Hi-z O(H)/–O ot D17nGCS0nGCS0Hi-z O(H)O ot D16SCKE SCKE Hi-z O(L)O ot D15VSSMOP VSSMOP P P P s3o F14SCLK1SCLK1Hi-z O(L)O t16 C17VDDi VDDi P P P d1c F13SCLK0SCLK0Hi-z O(L)O t16引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型B17VSSi VSSi P P P s3i E13nWE nWE Hi-z O(H)O(H)ot C16nOE nOE Hi-z O(H)O(H)ot A17nBE0:nWBE0:DQM0DQM0Hi-z O(H)O(H)ot B16nBE1:nWBE1:DQM1DQM1Hi-z O(H)O(H)ot C15nBE2:nWBE2:DQM2DQM2Hi-z O(H)O(H)ot A16nBE3:nWBE3:DQM3DQM3Hi-z O(H)O(H)ot B15nSRAS nSRAS Hi-z O(H)O(H)ot C14nSCAS nSCAS Hi-z O(H)O(H)ot A15VDDMOP VDDMOP P P P d3o F12VSSMOP VSSMOP P P P s3o B14ADDR0/GPA0ADDR0Hi-z/–O(L)/–O(L)ot D14ADDR1ADDR1Hi-z O(L)O(L)ot A14ADDR2ADDR2Hi-z O(L)O(L)ot C13ADDR3ADDR3Hi-z O(L)O(L)ot B13ADDR4ADDR4Hi-z O(L)O(L)ot D13ADDR5ADDR5Hi-z O(L)O(L)ot A13ADDR6ADDR6Hi-z O(L)O(L)ot C12ADDR7ADDR7Hi-z O(L)O(L)ot B12ADDR8ADDR8Hi-z O(L)O(L)ot G12ADDR9ADDR9Hi-z O(L)O(L)ot A12VSSMOP VSSMOP P P P s3o E11VDDMOP VDDMOP P P P d3o D12ADDR10ADDR10Hi-z O(L)O(L)ot E12ADDR11ADDR11Hi-z O(L)O(L)ot D11VDDi VDDi P P P d1c F11VSSi VSSi P P P s3i B11ADDR12ADDR12Hi-z O(L)O(L)ot A11ADDR13ADDR13Hi-z O(L)O(L)ot C11ADDR14ADDR14Hi-z O(L)O(L)ot G11ADDR15ADDR15Hi-z O(L)O(L)ot A10ADDR16/GPA1ADDR16Hi-z O(L)/–O(L)ot B10ADDR17/GPA2ADDR17Hi-z O(L)/–O(L)ot引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型C10VSSMOP VSSMOP P P P s3o E10ADDR18/GPA3ADDR18Hi-z/–O(L)O(L)ot D10ADDR19/GPA4ADDR19Hi-z/–O(L)O(L)ot F10ADDR20/GPA5ADDR20Hi-z/–O(L)O(L)ot A9ADDR21/GPA6ADDR21Hi-z/–O(L)O(L)ot D9ADDR22/GPA7ADDR22Hi-z/–O(L)O(L)ot E9ADDR23/GPA8ADDR23Hi-z/–O(L)O(L)ot B9ADDR24/GPA9ADDR24Hi-z/–O(L)O(L)ot C9ADDR25/GPA10ADDR25Hi-z/–O(L)O(L)ot E8ADDR26/GPA11ADDR26Hi-z/–O(L)O(L)ot C8VDDi VDDi P P P d1c F9VSSi VSSi P P P s3i D8VDDMOP VDDMOP P P P d3o G9VSSMOP VSSMOP P P P s3o B8DATA0DATA0Hi-z Hi-z Hi-z t12 A8DATA1DATA1Hi-z Hi-z Hi-z t12 D7DATA2DATA2Hi-z Hi-z Hi-z t12 E7DATA3DATA3Hi-z Hi-z Hi-z t12 C7DATA4DATA4Hi-z Hi-z Hi-z t12 B7DATA5DATA5Hi-z Hi-z Hi-z t12 A7DATA6DATA6Hi-z Hi-z Hi-z t12 C6DATA7DATA7Hi-z Hi-z Hi-z t12 A6VDDMOP VDDMOP P P P d3o F8VSSMOP VSSMOP P P P s3o F7DATA8DATA8Hi-z Hi-z Hi-z t12 B6DATA9DATA9Hi-z Hi-z Hi-z t12 D6DATA10DATA10Hi-z Hi-z Hi-z t12 A5DATA11DATA11Hi-z Hi-z Hi-z t12 C5DATA12DATA12Hi-z Hi-z Hi-z t12 B5DATA13DATA13Hi-z Hi-z Hi-z t12 D5DATA14DATA14Hi-z Hi-z Hi-z t12 A4DATA15DATA15Hi-z Hi-z Hi-z t12 B4VDDMOP VDDMOP P P P d3o博创科技第21页共21页表1-2 272脚FPGA引脚分配(图表9-9)引脚号引脚名默认功能I/O状态@BUS REQI/O状态@PWR-offI/O状态@nRESETI/O类型E6VSSMOP VSSMOP P P P s3o C4VDDi VDDi P P P d1c F6VSSi VSSi P P P s3i A3DATA16DATA16Hi-z Hi-z Hi-z t12 B3DATA17DATA17Hi-z Hi-z Hi-z t12 A2DATA18DATA18Hi-z Hi-z Hi-z t12 A1DATA19DATA19Hi-z Hi-z Hi-z t12 B2DATA20DATA20Hi-z Hi-z Hi-z t12备注:1. The @BUS REQ. shows the pin states at the external bus, which is used by the other bus master.2.“- ”标志说明在总线请求模式下引脚状态没有变化。

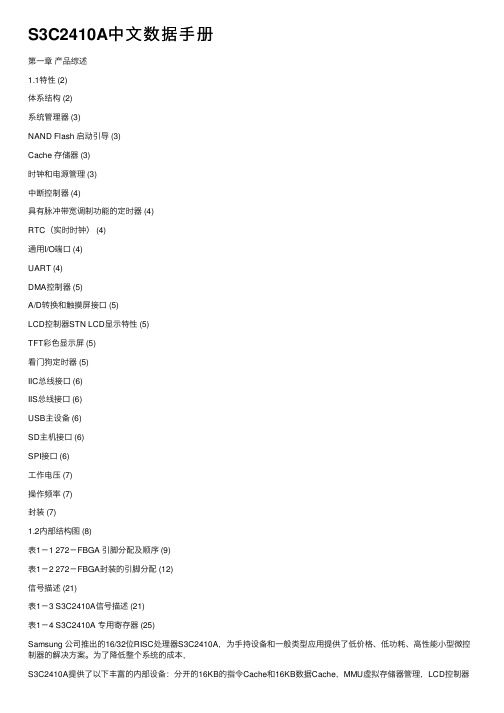

S3C2410A中文数据手册

S3C2410A中⽂数据⼿册第⼀章产品综述1.1特性 (2)体系结构 (2)系统管理器 (3)NAND Flash 启动引导 (3)Cache 存储器 (3)时钟和电源管理 (3)中断控制器 (4)具有脉冲带宽调制功能的定时器 (4)RTC(实时时钟) (4)通⽤I/O端⼝ (4)UART (4)DMA控制器 (5)A/D转换和触摸屏接⼝ (5)LCD控制器STN LCD显⽰特性 (5)TFT彩⾊显⽰屏 (5)看门狗定时器 (5)IIC总线接⼝ (6)IIS总线接⼝ (6)USB主设备 (6)SD主机接⼝ (6)SPI接⼝ (6)⼯作电压 (7)操作频率 (7)封装 (7)1.2内部结构图 (8)表1-1 272-FBGA 引脚分配及顺序 (9)表1-2 272-FBGA封装的引脚分配 (12)信号描述 (21)表1-3 S3C2410A信号描述 (21)表1-4 S3C2410A 专⽤寄存器 (25)Samsung 公司推出的16/32位RISC处理器S3C2410A,为⼿持设备和⼀般类型应⽤提供了低价格、低功耗、⾼性能⼩型微控制器的解决⽅案。

为了降低整个系统的成本,S3C2410A提供了以下丰富的内部设备:分开的16KB的指令Cache和16KB数据Cache,MMU虚拟存储器管理,LCD控制器(⽀持STN&TFT),⽀持NAND Flash系统引导,系统管理器(⽚选逻辑和SDRAM控制器),3通道UART,4通道DMA,4通道PWM定时器,I/O 端⼝,RTC,8通道10位ADC和触摸屏接⼝,IIC-BUS接⼝,IIC-BUS接⼝,USB主机,USB 设备,SD主卡&MMC卡接⼝,2通道的SPI以及内部PLL时钟倍频器。

S3C2410A采⽤了ARM920T内核,0.18um⼯艺的CMOS标准宏单元和存储器单元。

它的低功耗、精简和出⾊的全静态设计特别适⽤于对成本和功耗敏感的应⽤。

嵌入式技术应用教程——基于S3C2410第三章

第三章汇编语言与C语言3.1 C语言与汇编语言的比较本课程全程使用C语言来开发S3C2410A。

目前很少有用汇编语言来开发ARM系统了。

相比较而言汇编语言的优势是执行效率高,但其劣势是代码效率较低,而C语言正好相反,其代码效率较高,执行效率较低。

什么是执行效率?什么是代码效率?在嵌入式设计领域,一般执行效率就是程序的执行时间可以精确控制,从而可以使程序高效率的运行。

采用汇编语言编写ARM程序,每一条指令的执行时间都是固定不变的(外部时钟确定),所以写出的程序每一步的执行时间都是可以精确控制的。

这是采用汇编语言的优势所在。

但是,相信有过用汇编语言进行程序设计经验的读者在读别人用汇编语言写的程序时都会觉得十分吃力,尤其在碰到一些编程习惯不好的coding,整个程序注释寥寥或者干脆没有,那么对于一般的设计人员来讲,这样的程序就是天书一卷了。

这也就是所谓的程序可读性不高,不便于维护和移植重用。

这也可以说是代码效率底下。

C语言编写的程序相对来说可读性高,便于移植重用,结构灵活。

一个注释完全,结构完整的C程序很容易就读懂了,而且我们还可以把一些常用的代码封装成函数,这样就可以根据需要来直接调用这些函数。

C语言有了这些性质,相对于汇编语言其代码效率就较高了。

C语言有其优点,必然在嵌入式领域内还有其不足的地方。

采用C语言编写的ARM驱动代码需要经过编译器编译而生成相对应的汇编代码,最后生成可下载执行的二进制文件。

在这个过程中,所生成的汇编代码完全由编译器所决定,这样一来对于一条C语句来讲预先不知道所生成的汇编代码有几多,所以也就无从精确判断程序执行的时间,这种特质也就是所谓的执行效率相对较低。

在嵌入式控制领域,有一些设计对于程序的执行时间需要精确的把握,大多数设计对于程序的时间要求没有那么精确。

故此,一般情况下C语言完全能够胜任开发任务。

如果在设计中碰到了需要严格把握程序执行时间的地方,可以根据需要采取C语言和汇编语言混合编程的方法来处理。

第3章RISC微处理器S3C2410A

● 内部采用先进的微控制器总线体系结构(AMBA)(AMBA2.0 ,AHB/APB)。

PPT文档演模板

2020/11/26

第3章RISC微处理器S3C2410A

为降低系统成本,S3C2410A片上集成了16KB指令Cache和 16KB数据Cache、用于虚拟存储器管理的MMU、支持STN和TFT 的LCD控制器、NAND Flash BootLoader、系统管理器(片选 逻辑和SDRAM控制器)、3通道UART、4通道DMA、4通道PWM定 时器、I/O口、RTC、8通道10位ADC和触摸屏接口、I2C总线接口 、I2S总线接口、USB主设备、USB从设备、SD主卡和MMC(多媒体 卡)卡接口、2通道的SPI(串行外围设备接口)以及PLL时钟发生 器。S3C2410A的CPU内核采用的是16/32位ARM920T内核,还 PPT文采档演模用板 了AMBA(先进的微20控20/11制/26 器总线体系结构第)新3章R型ISC微总处理线器S结3C2构410。A

2个用于ROM、SRAM和同步DRAM;

● 所有的存储器bank都具有可编程的访问周期;

● 支持使用外部等待信号来填充总线周期;

● 支持掉电时的SDRAM自刷新模式;

● 支持各种类型的ROM启动(booting),包括NOR/NAND Flash和 EEPROM等。

PPT文档演模板

2020/11/26

● 支持多种屏幕尺寸,典型的屏幕尺寸有:640×480, 320×240,160×160;

● 最大虚拟屏幕大小是4MB; ● 在256彩色模式下支持的最大虚拟屏幕尺寸是:4096×1024

S3C2410简介-文档资料

4

S3C2410X和S3C2410A的区别

(1) A/D 9位升到10位; (2) MMC 的接口频率从10M 升到 20M。 其他功能一样!管脚兼容,封装一样。

S3C2410A可以替代S3C2410X。 S3C2410X01已经停产。

2021/4/21

5

2.7.1 内部结构

UARTS USB Devices SDI/MMC Watchdog Timer BUS Cont.

— 可通过软件选择大小端 — 地址空间:每个Bank 128Mbytes (总共 1GB) —除 bank0 (16/32-bit) 外,所有的Bank都可以通过编程选择总线宽度 = (8/16/32-bit) — 共 8 个banks

前6个Bank用于控制 ROM, SRAM, etc. 最后2个Bank用于控制 ROM, SRAM, SDRAM, etc . — 7个Bank固定起始地址; — 最后一个Bank可调整起始地址; — 最后两个Bank大小可编程; —所有Bank存储周期可编程控制。

OM [1:0] = 00

从Nand Flash 启动;

OM [1:0] = 01

从16位宽的动;

OM [1:0] = 10

从32位宽的ROM启动;

OM [1:0] = 11

TEST模式。

2021/4/21

8

2.7.3 存储器控制器

FLASH ROM属于真正的单电压芯片,在使用上很类似 EPROM,因此,有些书籍上便把FLASH ROM作为EPROM的一 种。事实上,二者还是有差别的。

2021/4/21

12

2021/4/21

13

2.7.3 存储器控制器(续2)

S3C2410A介绍

5.1.4 时钟和电源管理

时钟和电源管理模块包括三部分:

内蒙古大学电子信息工程学院

第5章 基于S3C2410的系统硬件设计

时钟控制:CPU所需的FCLK时钟信号、AHB总线外围设备所需的 HCLK时钟信号,以及APB总线外围设备所需的PCLK时钟信号 。 USB控制:产生USB 主接口和USB 从接口都需要的48Mhz 时钟 电源控制 正常模式 空闲模式 慢速模式 掉电模式

23

内蒙古大学电子信息工程学院

第5章 基于S3C2410的系统硬件设计

主要内容

1 S3C2410简介 2 I/O口 3 中断 4 DMA

5

6

UART A/D接口

7 键盘和LED控制 8 9

LCD 触摸屏

10 音频录放 11 USB设备的数据收发

24

5.2.1 S3C2410A的I/O口工作原理

内蒙古大学电子信息工程学院

内蒙古大学电子信息工程学院

第5章 基于S3C2410的系统硬件设计

S3C2410是Samsung公司推出的16/32位RISC处理器,主要 面向手持设备以及高性价比、低功耗的应用。 CPU内核采用 的是ARM公司设计的16/32位ARM920T RISC处理器。 S3C2410A提供一组完整的系统外围设备:

第5章 基于S3C2410的系统硬件设计

S3C2410A共有117个多功能复用输入输出口(I/O口),分为8组 PORT A~PORT H。PORT A除了作为功能口外,它只作为输出口使用; 其余的PORT B~PORT H都可以作为输入输出口使用。8组I/O口按照 其位数的不同,可分为: 1个23位的输出口(PORT A) 2个11位的I/O口(PORT B 和PORT H) 4个16位的I/O口(PORT C、PORT D、PORT E、PORT G) 1个8位的I/O口(PORT F)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

20.SD主机接口 ● 兼容SD存储卡协议1.0版; ● 兼容SDIO卡协议1.0版;发送和接收采用字节FIFO; ● 基于DMA或中断模式操作; ● 兼容MMC卡协议2.11版。 21.SPI接口 ● 兼容2通道SPI协议2.11版; ● 发送和接收采用2字节的移位寄存器; ● 基于DMA或中断模式操作。 22.工作电压 ● 内核电压:1.8V,最高工作频率200 MHz(S3C2410A-20); 2.0 V,最高工作频率266 MHz(S3C2410A-26)。 ● 存储器和I/O电压:3.3 V。 23.封装 ● 采用272-FBGA封装。

15.看门狗定时器 ● 16位看门狗定时器; ● 定时器溢出时产生中断请求或系统复位。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

16.I2C总线接口 ● 1通道多主机I2C总线; ● 串行、8位、双向数据传送,在标准模式下数据传送速率可达100kb/s, 在快速模式下可达400kb/s。 17.I2S总线接口 ● 1通道音频I2S总线接口,可基于DMA方式操作; ● 串行,每通道8/16位数据传输; 串行,每通道8/16位数据传输; ● 发送和接收(Tx/Rx)具备128字节FIFO(64字节发送FIFO+64字节接 收FIFO); ● 支持I2S格式和MSB-justified数据格式。 18.USB主设备 ● 2个USB主设接口; ● 遵从OHCI Revl.0标准; ● 兼容USB Verl.1标准。 19.USB从设备 ● 1个USB从设接口; ● 具备5个USB设备端口; ● 兼容USB Verl.1标准。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

4.Cache存储器 ● I-Cache(16 KB)和D-Cache(16 KB)为64路组相联Cache。 ● 每行8字长度,其中每行带有一个有效位和两个脏位(dirty bits)。 ● 采用伪随机数或循环替换算法。 ● 采用写直达(Write-through)或写回(Write-back)Cache操作来更新 主存储器。 ● 写缓冲器可以保存16个字的数据值和4个地址值。 5.时钟和电源管理 ● 片上MPLL和UPLL: 一UPLL产生用于USB主机/设备操作的时钟; 一MPLL产生操作MCU的时钟,时钟频率最高可达266 MHz(2.0V内核电压)。 ● 通过软件可以有选择地为每个功能模块提供时钟。 ● 电源模式包括正常、慢速、空闲和掉电模式: 一正常模式为正常运行模式; 一慢速模式为不加PLL的低时钟频率模式; 一空闲模式只停止CPU的时钟; 一掉电模式切断所有外设和内核的电源。 ● 可以通过EINT[15:0]或RTC报警中断从掉电模式中唤醒处理器。

3.1.1 S3C2410A内部结构

S3C2410是Samsung公司推出的16/32位RISC处理器,主要面向高 性价比、低功耗的手持设备应用。S3C2410有S3C2410X和S3C2410A两 个型号,A型是X型的改进型,具有更好的性能和更低的功耗。 为了降低系统的成本,S3C2410A在片上集成了单独的16KB指令 Cache和16KB数据Cache、用于虚拟存储器管理的MMU、支持STN和TFT 的LCD控制器、NAND Flash Boot Loader、系统管理器(片选逻辑和 SDRAM控制器)、3通道UART、4通道DMA、4通道PWM定时器、I/O口、 RTC、8通道10位ADC和触摸屏接口、I2C总线接口、I2S总线接口、USB 主设备、USB从设备、SD主卡和MMC(多媒体卡)卡接口、2通道的SPI (串行外围设备接口)以及PLL时钟发生器。S3C2410A的CPU内核采用 的是16/32位ARM920T 内核,同时还采用了AMBA(先进的微控制器总 线体系结构)新型总线结构。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

嵌入式系统设计

—基于ARM9微处理器S3C2410A

第3章 32 Bit RISC微处理器 S3C2410A

南阳师范学院 张帅

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

3.1微处理器 S3C2410A

《嵌入式系统设计》

13.LCD控制器STN LCD显示特性 ● 支持3种类型的STN LCD显示屏:4位双扫描、4位单扫描和8位单扫描显示类型; ● 对于STN LCD支持单色模式、4级灰度、16级灰度、256彩色和4 096彩色; ● 支持多种屏幕尺寸,典型的屏幕尺寸有:640×480,320×240,160×160; ● 最大虚拟屏幕大小是4 MB; ● 在256彩色模式下支持的最大虚拟屏幕尺寸是:4 096×1 024,2 048×2 048, 1 024×4 0960或者其它尺寸。 14. TFT(Thin Film Transistor,薄膜场效应晶体管)彩色显示特性 ● 彩色TFT支持1、2、4或8bpp(bit per pixel,每像素所占位数)调色显示; ● 支持16bpp无调色真彩显示; ● 在24bpp模式下支持最大16M彩色TFT; 支持多种屏幕尺寸,典型的屏幕尺寸有:640×480,320×320,160×160或者其 它尺寸; ● 最大虚拟屏大小是4 MB; ● 在64彩色模式下支持的最大虚拟屏幕尺寸是:2 048×1 024或者其它尺寸。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

S3C2410A的引脚分布图

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

3.2

S3C2410A存储器控制器

3.2.1 S3C2410A的存储器控制器特性

S3C2410A的存储器控制器提供访问外部存储器所需要的存储器控制信号, 具有以下特性: ● 支持小/大端(通过软件选择)。 ● 地址空间:每个bank有128 MB(总共有8个bank,共1 GB)。 ● 除bank0只能是16/32位宽之外,其他bank都具有可编程的访问位宽 (8/16/32位)。 ● 总共有8个存储器bank(bank0~bank7): 一其中6个用于ROM,SRAM等; 一剩下2个用于ROM,SRAM,SDRAM等。 ● 7个固定的存储器bank(bank0~bank6)起始地址。 ● 最后一个bank(bank7)的起始地址是可调整的。 ● 最后两个bank(bank6和bank7)的大小是可编程的。 ● 所有存储器bank的访问周期都是可编程的。 ● 总线访问周期可以通过插入外部等待来扩展。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

10.UAR ● 3通道UART,可以基于DMA模式或中断模式操作; ● 支持5位、6位、7位或者8位串行数据发送/接收(Tx/Rx); ● 支持外部时钟作为UART的运行时钟(UEXTCLK); ● 波特率可编程; ● 支持IrDA 1.0; ● 支持回环(Loopback)测试模式; ● 每个通道内部都具有16字节的发送FIFO和16字节的接收FIFO 。 11.DMA控制器 ● 4通道的DMA控制器; ● 支持存储器到存储器、I/O到存储器、存储器到I/O和I/O到I/O 的传送; ● 采用突发传送模式提高传送速率。 12.A/D转换和触摸屏接口 ● 8通道多路复用ADC; ● 转换速率最大为500 KSPS(Kilo Samples Per Second,每秒采 样千点),10位分辨率。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

S3C2410A提供一组完整的系统外围设备接口,从而大大减少了整个系统的成 本,省去了为系统配置额外器件的开销。S3C2410A集成的片上功能包括: ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● 内核电压1.8V/2.0V,存储器电压3.3V,外部I/O电压3.3V; 具有16KB的I-Cache和16KB的D-Cache以及MMU; 外部存储器控制器(SDRAM控制和片选逻辑); LCD控制器(最大支持4K彩色STN和256K彩色TFT)提供1通道LCD专用DMA; 4通道DMA并有外部请求引脚端; 3通道UART(IrDAl.0,16字节Tx FIFO和16字节Rx FIFO)/2通道SPI; 1通道多主设I2C总线和1通道I2S总线控制器; 版本1.0SD主接口和2.11兼容版MMC卡协议; 2个USB主设接口/1个USB从设接口(版本1.1); 4通道PWM定时器和1通道内部定时器; 看门狗定时器; 117位通用I/O口和24通道外部中断源; 电源控制模式有正常、慢速、空闲和电源关断4种模式; 8通道10位ADC和触摸屏接口; 具有日历功能的RTC; 使用PLL的片上时钟发生器。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》

6.中断控制器 ● 55个中断源(1个看门狗定时器、5个定时器、9个UART、24个外部中断、4个 DMA、2个RTC、2个ADC、1个I2C、2个SPI、1个SDI、2个USB、1个LCD和1个电池故 障); ● 支持电平/边沿触发模式的外部中断源; ● 可编程的电平/边沿触发极性; ● 为紧急中断请求提供快速中断服务(FIQ)支持。 7.具有脉冲宽度调制(PWM)的定时器 ● 具有PWM功能的4通道16位定时器,可基于DMA或中断操作的1通道16位内部定 时器; ● 可编程的占空比周期、频率和极性; ● 能产生死区; ● 支持外部时钟源。 8.RTC(实时时钟) ● 完整的时钟特性:秒、分、时、日期、星期、月和年; ● 工作频率32.768 kHz; ● 具有报警中断; ● 具有时钟滴答中断。 9.通用I/O口 ● 24个外部中断口; ● 多路复用的I/O口。

第3章 32 Bit RISC微处理器 S3C2410A

《嵌入式系统设计》