MPC564MZP40中文资料

PCM56中文资料

®

PCM56

2

元器件交易网

ABSOLUTE MAXIMUM RATINGS

DC Supply Voltages ...................................................................... ±16VDC Input Logic Voltage ............................................................ –1V to +VS/+VL Power Dissipation .......................................................................... 850mW Operating Temperature ..................................................... –25°C to +70°C Storage Temperature ...................................................... –60°C to +100°C Lead Temperature (soldering, 10s) ................................................ +300°C

Reference 16-Bit IOUT DAC

RF

16-Bit Input Latch

Audio Output

16-Bit Serial-to-Parallel Conversion Clock LE Data

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

LNK562-564中文资料

LNK562-564

4B

2 4.90 (0.193) BSC

A

4

8

5

SO-8C

0.10 (0.004) C A-B 2X

D

2 3.90 (0.154) BSC

0.10 (0.004) C D

2X

Pin 1 ID

1

1.27 (0.050) BSC

1.35 (0.053) 1.75 (0.069)

0.10 (0.004) 0.25 (0.010)

4. 在靠近塑料封装体表面的引脚8(源极)测量。

(θ ) ............................ 100 °C/W(3); 80 °C/W(4) JA

(θ )(2) .................................................... 30 °C/W JC

15

版本H 11/08

LNK562-564

了解最新信息,请访问我们的网站: Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

MPC5644A学习纪要

MPC5644A学习纪要Nichmean@2016-09-26 11:05:411SPC5644A简介学些资料:数据手册(datasheet):5644A – MPC5644A.pdf。

参考手册:MPC5644ARM.pdf使用/查询寄存器的依据内核手册:e200z3RM.pdf和e200z4RM.pdf查询汇编指令。

特性:●150MHz e200z4 Power架构内核-可变长度指令编码(VLE)-有两个可执行单元的大范围架构-每周期最多两个整形或浮点型指令运算-每周期最多四个乘法或加法运算●存储器组成-具有ECC和写时读功能的片内4MB Flash存储器-具有standby和ECC功能的片内192KB SRAM-可配置为2路或4路的带有线锁功能(line locking)8KB指令cache-14 + 3KB eTPU代码和数据RAM-5×4交叉开关(XBAR)-24端口的MMU-具有主从功能的外部总线接口(EBI)●故障安全保护-16端口的存储器保护单元(MPU)-带有3个子模块(sub-modules)的CRC单元-结温传感器●中断-带有NMI的可配置中断控制器-64通道的DMA●串行通道-3路eSCI-3路DSPI(有两路支持downstream MicroSecond Channel[MSC])-每路64个消息窗口的3路FlexCAN-1路搞到10Mbits/s的FlexRay模块(V2.1),可配置单通道或双通道,具有128个消息对象,具有ECC功能。

●1路eMIOS,具有24个未定义通道●1路eTPU2(第二代eTPU)-32个标准通道-1个反射模块(reaction module)(6通道,每通道3路输出)●两路增强型AD转化器(eQADCs)-40路12位输入通道(基于2个AD转化器切换),并且可通过外部选择器扩展到56路-6个命令队列-支持触发和DMA-最小转换时间688ns●带有启动辅助模块(BAM)的片内CAN/SCI/FlexRay启动引导●Nexus-Class 3+的e200z4内核-Class 1的eTPU●JTAG(5针)●Development Trigger Semaphore(DTS)-32位的信号量寄存器,一个唯一识别码寄存器-参与数据采集的触发器组成-用于与外部工具通讯的EVTO引脚●时钟产生-片内4-40 MHz的主振荡器-片内FMPLL(相位锁定的频率模块)●最多120个通用I/O口-可独立配置为输入、输出或特殊功能-可配置阈值●低功耗模式:slow,stop和stand-by模式●灵活的供电方式-使用外部ballast的5V单电源供电-多路外部供电:5V、3.3V和1.2V●封装-176 LQFP-208 MAPBGA-324 TEPBGA2环境2.1硬件平台北京龙邱智能科技公司的开发板LQ-56xx-EVB,主控芯片为SPC5644AMLU。

Canon imagePROGRAF iPF MFP M40系统技术文档说明书

imagePROGRAFTECHNICALDOCUMENTSMFP LARGE-FORMAT IMAGINGIntroducing the imagePROGRAF iPF MFP M40 SystemThe Canon imagePROGRAF iPF MFP M40 systems are multicomponent, multifunction solutions for architects, engineers, construction, GIS, and other professionals who need to scan, edit, save, share,and print large-format documents easily and efficiently.FEATURES• M40 Scanner with SingleSensor assemblytechnology* delivers incredibly fast and accurate scan speeds.• SmartWorks MFP scan to copy/file/sharesoftware includes new custom presets, imageenhancements, and all new cloud integration.• Direct Print & Share is Canon’s Cloud Portalsoftware for file sharing.• A customizable system–choose between 36”or 44” printers for maximum versatility.• Touch-Screen Monitor and Stand are included in the system.* SingleSensor assembly technology means that multiple sensors are contained in oneassembly device.2VERSATILITYChoose the printer that best fits your workflow—and budget. With five imagePROGRAF models in the MFP M40 system line-up, it’s easy to customize your system.iPF765/iPF760• 36” 5-color large-format printers• Flat stacker/basket neatly stacks up to 20 plain paper prints, 24” x 36” in size • Interface lock system allows you to password-protect all user interfaces • Built-in 250GB hard drive (iPF765 only)iPF765iPF760iPF825/iPF815• 44” 5-color large-format printers • Dual-roll capability with automatic switching for enhanced production (iPF825 only)• Large-capacity ink tanks(330ml and 700ml tanks available)• Built-in 160GB hard drive • Sub ink tank systemiPF815iPF750• 36” 5-color large-format printer • Borderless printing• Bundled with a variety of softwaresolutions to help enhance your workflow •Entry-level, low-cost solution3iPF825M40 SCANNERThe M40 scanner with SingleSensor assembly technology brings the MFP solution to a wholenew level. You have the ability to scan documentsat incredible speeds and, with the included USB 3 connection, experience data transfer speeds of upto 10 times faster than on previous MFP models! The intuitive control panel embedded on the scanner helps make operation of the device incredibly easy, and its compact design helps space become a non-issue when using and storing the device.• Optical resolution of 1200 dpi• Scan speeds of 13 inches per secondmonochrome and 3 inches per second color • Capability to accept media of differentthickness (up to 2mm)SMARTWORKSThe included SmartWorks MFP scan-to-copy/file/ share software has been enhanced and now helps you to be more efficient than ever before.• New user interface for easy navigation• Ability to add custom presets with one-touchretrieval for those often-used settings• New image enhancements for white point adjust, black point adjust, sharpen, mirror,and invert• Full integration with Direct Print & ShareCloud Portal software SYSTEMExperience the vast customization options that come with your MFP system. The Canon imagePROGRAFiPF MFP M40 large-format imaging system is designed to be a complete scan-to-copy, file, andshare solution. The system includes an imagePROGRAF iPF large-format printer, M40 large-format scanner, MFP stand, SmartWorks MFP software, and a large touch-screen monitor. This solution provides a fast and effective system for printing, copying, archiving, and distributing maps, drawings, renderings, site and facilities management plans, design and layout proofs, posters, and more.With the iPF765 or iPF760 printer, the integratedstand allows the user to position the monitorin a variety of configurations to provide optimal functionality and comfort, as well as allowing theuser to mount the stand onto the printer for a trueall-in-one structure, or keep them separate for easy maneuverability. The MFP solution includes atouch-screen monitor, and users now have the optionof selecting to have their scanned documents come straight out the back of the scanner, or rewind to the front for easy retrieval. Customization is truly broughtto a whole new level with the iPF MFP M40 system.• Integrated stand for structural customization(iPF765 and iPF760 printers only)MARKETSThe iPF MFP M40 system is designed to help bring a fully operational work solution to you out in the field and provide you with all the tools to help enhanceyour technical document productivity. Whetheryou have a low-volume architecture firm or a high production enterprise environment, you can choosethe right printing solution to meet your workflow requirements. See how the MFP solution can bringyour business to the next level. This solution’s capability to help you produce high image qualityat impressive speeds—and achieve remarkable productivity—help make it a welcome addition for anyone looking to advance in the AEC, GIS, andother technical industries.imagePROGRAF iPF MFP M40 SYSTEM 4Touch-Screen MonitorSmartWorks MFP SoftwareFeaturing one-touch “green button”M40 Large-Format Scanner• SingleSensor assembly technologyLarge-Format Ink-Jet PrinterFive models to choose fromMFP Stand5Canon’s Direct Print & Share * is a cloud-based portal service that allows users to expand their workflow. Through a Google ** account, users are given the ability to scan and upload documents to their own cloud storage space and have those documents printed from almost anywhere!Easily print PDFs, TIFFs, and JPEGs through the user-friendly interface, and even have the ability to do batch printing. To help further integrate with your Canon printer and software, Direct Print & Share comes with a print plug-in for SmartWorks MFP V3 (also included) and AutoCAD ® (sold separately) tomake cloud use through this software incredibly easy. Scan, upload, download, and print directly from these software solutions to help streamline your workflow.FEATURES• Accessible from almost anywhere in the world • 5GB of free storage• Batch printing of multiple files• Integration with software solutions, such as SmartWorks MFP V3 and AutoCAD• Drag-and-drop TIFF, JPEG, and PDF files toshortcut iconDIRECT PRINT & SHARE SOFTWARE*Direct Print & Share is also available as a free download at /downloads.**You must open a Google Cloud account to take advantage of the cloud functionality. Storage capacity and any pricing thereof is based on Google’s current offering and is atGoogle’s discretion. Your Google Cloud account is subject to Google’s terms and conditions, which is subject to change at Google’s discretion. Neither Canon Inc., nor Canon U.S.A., Inc. represents or warrants any third-party product, service or feature referenced hereunder.Cloud StorageCloud Service IntegrationiPF Direct Print & Share1. Select a file2. Right-click to sendmanagementPrint settings6Output Width44” WideNumber of Ink Tanks6Color SetDye: Cyan, Magenta, Yellow, BlackPigment: Matte BlackInk TypeDye/Pigment Reactive InkInk Tank Size330ml and 700mlMaximum Print Resolution (dpi)2400 x 1200Total Number of Nozzles15,360Ink DropletConsistent 4plMaximum Print Speed(1200 x 1200 dpi on Plain Paper)688 sq.ft. per hr.*Print Speed Best Quality Mode (2400 x 1200 dpi on Photo Gloss Paper)89 sq.ft. per hr.*Software/Utilities/Applications• Canon Printer Driver• HDI Driver• Print Plug-in for Microsoft Office• Digital Photo Front-Access• Remote User Interface• Media Configuration Tool• Supports HP-GL/2, HP RTL Files• PosterArtist Lite• PosterArtist (optional) (PC only)• Third-Party RIPs (optional)Special Features• Dual Media Rolls (iPF825 only)• Accounting Manager (PC only)• Economy Color Mode• Sub Ink Tank System• Independent Rotary CutterPrinter Dimensions ( H x W x D)iPF825: 45” x 74.5” x 50.9” (with basket)iPF815: 45” x 74.5” x 38.4Printer WeightiPF825: Approx. 417 lb.iPF815: Approx. 305 lb.Printer Memory384MB RAM32GB Dedicated File Processing MemoryHard Drive160GBConnectivityUSB 2.0: 10/100Base-T/TXOperating SystemW indows®,** Macintosh®*** O S: Windows XP SP2, CPU: Pentium 4 3.2GHz, RAM:1GB, Application: Adobe Photoshop 7.0, Interface: USB2.0 Hi-Speed, Data used: ISO/JIS-SCID No.5, Outputimage size: A1 (580mm x 724.9mm) for iPF655/650/610,A2 (410mm x 512.5mm) for iPF510 using optional Roll Feed.Measured by Canon Inc. Each print time does not includedata transfer time. The print speed may vary depending onthe data volume and size, PC, application, software, mediatype, and interface.**Please visit /download for availability.Output Width36” WideNumber of Ink Tanks6Color SetDye: Cyan, Magenta, Yellow, BlackPigment: Matte Black, Matte Black Ink TypeDye/Pigment Reactive InkInk Tank Size130ml†Maximum Print Resolution (dpi)2400 x 1200Total Number of Nozzles15,360Ink DropletConsistent 4plMaximum Print Speed(1200 x 1200 dpi on Plain Paper)733 sq.ft. per hr.*Print Speed Best Quality Mode (2400 x 1200 dpi on Photo Gloss Paper)79 sq.ft. per hr.*Software/Utilities/ApplicationsiPF765/760• Canon Printer Driver• Optimization Module for AutoCAD(PC only)• Print Plug-in for Microsoft Office• Remote User Interface• Media Configuration Tool• PosterArtist Lite• PosterArtist (optional) (PC only)• Third-Party RIPs (optional)iPF750• Canon Printer Driver• HDI Driver• Digital Photo Front-Access• Print Plug-in for Microsoft Office• Remote User Interface• Media Configuration Tool• Supports HP-GL/2, HP RTL• PosterArtist Lite• PosterArtist (optional) (PC only)• Third-Party RIPs (optional)Printer Dimensions (H x W x D)41.8” x 51.3” x 34.5”41.8” x 51.3” x 43.3 (when Basket is in the extendedposition for flatbed stacking, iPF765/760 only)Printer WeightApprox. 141.3 lb.Special FeaturesiPF765/760• Flat Stacker/Basket• Interface Lock• Accounting Manager (PC only)• Sub Ink Tank System• Top-loading Roll FeediPF750• Accounting Manager (PC only)• Sub Ink Tank System• Top-loading Roll Feed• Gigabit Ethernet Support• Intuitive Operation PanelPrinter Memory256MB (32GB iPF765 only)Hard Drive250GB (iPF765 only)ConnectivityUSB 2.0: 10/100/1000Base-T/TXOperating SystemW indows,** Macintosh**† The starter ink tanks in the package with the printer are not the samecapacity as the replacement ink tanks specified here.*OS: Windows XP SP2, CPU: Pentium 4 3.2GHz, RAM: 1GB, Applica-tion: Adobe Photoshop 7.0, Interface: USB 2.0 Hi-Speed, Data used:ISO/JIS-SCID No.5, Output image size: A0 (827mm x 1033.8mm).Measured by Canon Inc. Each print time does not include data trans-fer time. The print speed may vary depending on the data volume andsize, PC, application, software, media type, and interface.**P lease visit /download for availability.7Canon Latin America, Inc.703 Waterford Way Suite400Miami, FL 33126The imagePROGRAF iPF MFP M40 systems contain multiple components, some of which are manufactured by third parties. To the extent that such third party offerings come with limited warranties, such limited warranties are hereby passed to the purchaser, and Canon shall have no obligation or any liability with respect to such third party offerings.As an ENERGY STAR ® Partner, Canon U.S.A., Inc. has determined that this product meets the ENERGY STAR guidelines for energy efficiency. ENERGY STAR and the ENERGY STAR mark are registered U.S. marks. CANON, IMAGEPROGRAF, and the GENUINE logo are registered trademarks of Canon Inc. in the United States and may also be registered trademarks or trademarks in other countries. IMAGEANYWARE is a trademark of Canon. All other referenced product names and marks are trademarks of their respective owners and are hereby acknowledged. Some items may not be available at this time; please check for availability. Specifications and availability subject to change without notice. All printer output images and effects are simulated. MFP shown with iPF825 and iPF765 printer. ©2013 Canon U.S.A., Inc. All rights reserved.0176W631Scan Speed* • 48-bit Full Color @ 200 dpi: 3” (per second) • 8-bit Grayscale and Monochrome @ 200 dpi:13” (per second)Scan Modes • 16.7-million Color RGB (24-bit) • 256 color RGB Adaptive Indexed Color Palette (8-bit) • 256-level Grayscale (8-bit) • Black and White (1-bit)Color Space Normalized RGB Resolution • 9600 dpi (maximum interpolated) • 1200 dpi (optical)Scan Accuracy** +/- 0.1% ; +/- 1 pixel Maximum Image Width 40”Maximum Media Width 42”Maximum Scan Length 96”Maximum Media Thickness 0.079” (2mm)Media Feed System S ingle large diameter precision ground drive roller;adaptive CIS media focus management and media guide mechanism; intuitive face-up, front-loading, and front/rear-exit media path with side justification; automatic media size detection with reliable optical media sensorsDigital Imaging Technology C ontact Image Sensor (CIS) Technology (SingleSensorAssembly) • 5x close-spaced “deep focus” CIS (25,000 pixels) • 48-bit RGB digital color image capture (50,400 pixels) • 16-bit grayscale image capture • Panchromatic monochrome and black and white • B i-directional extra long-life LED light system foroptimum object illumination and instant-on scanning capabilityDigital Image Processing • 2D Intelligent Adaptive Thresholding (IAT) (1-bit mode) • Fixed Threshold Black and White (1-bit mode) • D ynamic Normalization Application (DNA) with16-bit Super SamplingUser Status and One-Touch Operation Center mounted LCD scanner control panel; walk-up operation and user selection of scanner mode with stop, forward, rewind, scan, and copy buttons; local language options, panel overlay, and Magnetic Media Guide Included Software • SmartWorks MFP Scan-to-file, Copy, E-mail with Real-time Image Viewer. Supports TIFF, JPEG, TIFFG4, and PDF. • Direct Print & Share Cloud Portal Solution Operating System Windows 7 Professional (64-bit)User Maintenance Installable Plug-and-Play Scanner; Simple Cleaning Scanner Interface Kit S uperspeed USB 3.0 ( PC Connector Compatible withUSB 2.0 and USB 3.0 sockets ) Operating Environments 10 – 35°C, 35-80% RH, Non-condensing External Power Supply 100-250 VAC Autosensing +/- 10%, 50-60Hz Scanner Power Consumption • 53Wh (scanning) • 5Wh (stand-by)Compliances VCCL, CB, CE, FCC, UL, RoHS, ENERGY STAR ®Stand and Scanner Dimensions Height: Swing Arm: 57.5” Straight Arm (max): 66” Width: Swing Arm (max): 69.9” Straight Arm: 53.6 Depth: 31.5”Stand and Scanner Weight Approx. 120.4 lb.What’s In The Box? • M40 Scanner with Power Cord and USB 3.0 and USB 2.0 Cables (scanner to server) • 2 Meter USB Cable (server to printer) • M40 MFP Stand • M40 MFP Stand Assembly Instructions • SmartWorks MFP Software • Flat Panel Touch-screen Display • Installation and Operation Manual • Operator Manual on CD-ROM • Document Return Guide • Magnetic Paper Guide* T he scan rate is proportional across the full range ofresolutions supported by the scanner. Actual scan times will depend on the host system performance. Quoted top speeds may be limited by the effective bandwidth of the USB 2 and is not guaranteed for all media types. ** T he quoted scan accuracy may vary depending on theoperating environment and the thickness of the media.。

MPC40电脑操作说明书

(3)按游标键 ,选择需要修改的参数。按输入数值,再按 完成设定。

3.2.6中子和绞牙

图07

(1)按 ,即出现图07所示之画面。

(2)此画面下可以设定三组中子参数。各项参数可以先通过按 进行激活,然后按数字键,再按 完成设定。

(3)第一组可以设定为:中子1、绞牙1、不动作。可以通过按 或 进行选择。

吹风3时间:吹风3所需的时间。

吹风3延时:从“吹风3开始的开模位置”到吹风3启动时的延时时间。

2、顶针加减速的设定

画面06

(1)在画面05下按 + ,进入密码输入画面,输入正确密码后。则显示画面06。在这个画面下可以进行顶针加减速参数设定

(2)可以设定顶针和调模顶针的加减数参数。调模顶针是特别功能。

震雄MPC40多功能电脑

特性:

日本原装计算机控制器,符合JIS各类检验标准。640×480彩色超大液晶显示屏,电源适用范围AC110V~AC280V 50/60HZ。稳定性高,储存资料在停电状态下可达5年以上,安全可靠。并备有中、英、日三种语言字幕可自由选择切换,方便学习操作。

基本性能:

1,特大容量内存,可储存150组模具成型资料,如时间、次数、压力、速度、行程、计量、模具厚度、模号批注、选择条件、原料温度,亦可选择存入软盘及个人PC。

3.1.1

电脑面板图

………

4

3.1.3

成形条件控制按键

………

6

3.1.3

成形条件数字资料按键

………

6

3.1.4

手动操作按键及说明

………

8

3.1.5

电源开关

………

8

3.2计算机画面操作说明

Canon PIXMA MX系列打印机功能介绍说明书

• Powerful and productive Office All-In-One• 35-page 2-sided Auto Document Feeder for scanning,copying and faxing• Superior prints using 5 individual ink system with optionalXL capacity ink tanks• Print up to 1000 monochrome pages with optional XXLmonochrome ink• Convenient, high-capacity 250-sheet paper tray• Large, user-friendly 7.5cm (3.0") colour TFT display withDual Function Panel• Fast printing with A4 ISO ESAT 15 ipm mono/10 ipmcolour• Print from, and scan to, smartphones/tablets. AppleAirPrint supported• Google Cloud Print support and internet printing usingPIXMA Cloud Link• Advanced media handling with Direct Disc Print and2-sided printingPIXMA MX925 PIXMA MX525 PIXMA MX455 PIXMA MX395yGeneral Specifications Footnotes[1]Ink droplets can be placed with a minimum pitch of 1/9600 inch. [2]Document print speed on plain paper is measured based on average of ESAT in Office Category Test of ISO/IEC 24734 standard. [3]Photo print speed is based on default driver setting using ISO/JIS-SCID N2 standard on Canon Photo Paper Plus Glossy II and does not take intoaccount data processing time on host computer. [4]Some features available in Windows driver only. [5]Declared yield value in accordance with ISO/IEC 24711 standard. Values obtained by continuous printing.[6]Actual transmission speed may vary depending on document complexity, fax settings at receiving end, and line conditions. [7]Optical resolution is a measure of maximum hardware sampling resolution based on ISO 14473 standard. When scanning in high resolution, the scan size is restricted (maximum optical resolution for A4 scan is 600dpi). [8]Colour document scan speed is measured with ISO/IEC 24735 Annex C Test Chart A. Scan speed indicates the time measured between pressing the scan button of the scanner driver and the on-screen status display turns off. [9]Colour document copyspeed is measured based on average of sFCOT and sESAT in Performance Test of ISO/IEC 29183 standard. [10]Requires connection over Wi-Fi network and installation of free Canon application: EPP for Android, Windows RT and iEPP for iOS. Not available in certain countries or regions. [11]Full HD Movie Print is available for MOV and MP4 movie files created by select Canon digital cameras and camcorders. Requires installation of software bundled with Canon video or digitalcamera, from which the movie was captured. MOV files require: ZoomBrowser EX / ImageBrowser (version 6.5 or later), MP4 files require: ImageBrowser EX (version 1.0 or later). [12]Easy-WebPrint EX requires Internet Explorer 7 or later[13]When printing ISO/JIS-SCID N2 pattern on 10x15cm Photo Paper Plus Glossy II using default settings. [14]When copying ISO/JIS-SCID N2 (printed by inkjet printer) on A4 size plain paper using default settings.Standard disclaimersAll specifications subject to change without notice.Print speed may vary depending on system configuration, interface, software, document complexity, print mode, page coverage, type of paper used etc. Ink yield may vary depending on texts/photos printed, applications software used, print mode and type of paper used. For yield information see /ink/yield . Scan speed may vary depending on system configuration, interface, software, scan mode settings and document size etc. Copy speed may vary depending on document complexity, copy mode, page coverage; type of paper used etc. and does not take into account warming up time. All brand and product names are trademarks of their respective companies. Microsoft,Windows and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries. For more information on ChromaLife100+ please visit High productivity, powerful Office All-In-One with Wi-Fi andXXL ink optionPowerful and productive 5-ink All-In-One offering XL and XXL ink options, Wi-Fi, Ethernet and 35-page2-sided ADF. Advanced media handling with 250-sheet paper tray, 2-sided printing and Direct Disc Print.Sales start date: March 2013Positioning: Powerful 5-ink Wi-Fi All-In-One with XL and XXL inks for high productivity officesRecommended Retail Price MX925 EUR 6992B008AA 4960999922751 £179.00Recommended Retail Price PGI-550 PGBK 6496B001AA 4960999904580 £12.99CLI-551 BK 6508B001AA 4960999905235 £10.99CLI-551 C 6509B001AA 4960999905556 £10.99CLI-551 M 6510B001AA 4960999905242 £10.99CLI-551 Y 6511B001AA 4960999905563 £10.99Recommended Retail Price PGI-555PGBK XXL 8049B001AA 4960999965376 TBCPGI-550PGBK XL 6431B001AA 4960999904504 £15.99CLI-551BK XL 6443B001AA 4960999904948 £14.99CLI-551C XL 6444B001AA 4960999904931 £14.99CLI-551M XL 6445B001AA 4960999904924 £14.99CLI-551Y XL 6446B001AA 4960999904917 £14.99CLI-551 C/M/Y/BK Multipack 6509B009AA 8714574584416 £38.99Glossy Photo Paper ‘Everyday Use’ GP-501 (A4) 0775B001AB 4960999293929 £19.99Glossy Photo Paper ‘Everyday Use’ GP-501 (4"X6") 0775B003AA 4960999293967 £8.99High Resolution Paper HR-101N A4 200 SH 1033A001AB 4960999869131 £22.99High Resolution Paper HR-101N A4 50 SH 1033A002AB 4960999867090 £6.99Luster Paper LU-101 A4 20 SH 6211B006AA 4960999843995 £16.99Matte Photo Paper MP-101 A4 50 SH 7981A005AB 4960999174839 £11.99Photo Paper Plus Glossy II PP-201 4"X6" 50 SH 2311B003BA 4960999484198 £8.99Photo Paper Plus Glossy II PP-201 5"X7" 20 SH 2311B018BA 4960999537276 £5.99Photo Paper Plus Glossy II PP-201 A4 20 SH 2311B019BA 4960999537269 £9.99yPhoto Paper Plus Semi-gloss SG-201 4"X6" 50 SH 1686B015AA 4960999405339 £8.99Photo Paper Plus Semi-gloss SG-201 8"X10" 20 SH 1686B018AA 4960999405353 £11.99Photo Paper Plus Semi-gloss SG-201 A4 20 SH 1686B021AA 4960999405377 £11.99Photo Paper Pro Platinum PT-101 4"X6" 20 SH 2768B013AB 4960999575254 £7.99Photo Paper Pro Platinum PT-101 A4 20 SH 2768B016AB 4960999575285 £15.99Photo Stickers PS-101 4"x6" 5 SH 0001C001AA 4960999252957 £4.99T-Shirt Transfers TR-301 8938A001AA 4960999195186 £10.99Pro Variety Pack PVP-101 A4 10 SH TBC TBC TBCMix Variety Pack MVP-101 4"x6" & A4 20 SH TBC TBC TBCVariety Pack VP-101 4"X6" 20 SH TBC TBC TBCPhoto Frame/Calendar Pack PFC-101 5"x7" 20 SH 2311B054AA 8714574595597 TBCGreeting Card Pack GCP-101 4"x6" 10 SH 0775B077AA 8714574595559 TBCLogistics informationWeight (Net/Gross in kg) Individual 1 570.5 x 308 x 520.5 14.5/11.7Pallet (Upper) 12 1147 x 930 x 1045 175.8/174Pallet (Bottom) 12 1147 x 930 x 1045 175.8/174What’s in the box?• Printer • Multilingual set-up guides, set-up software and • Inks: 5 individual ink tanks PGI-550PGBK (Pigment user manualBlack), CLI-551BK (Black), CLI-551C (Cyan), • Software: My Image Garden and CREATIVE PARK CLI-551M (Magenta), CLI-551Y (Yellow) PREMIUM• CD tray • Warranty Sheet• Power cord • Ink Leaflet• Telephone cabley。

理光5627-5632-5640-5840维修代码

1-801 每分钟复印量下降选择┿

1-902 齐纸板间隔调整(侧挡板)┿

1-905 齐纸板间隔调整(反挡板)┿

5-812 电话号码输入┿(仅指a207复印机)

5-816 仅在日本使用。不要改变工厂设定。

5-817 仅在日本使用。不要改变工厂设定。

5-905 aps a4/lt横送优先┿

4-902 aps 8k/16k检测(仅指a4机器)┿

操作

5-001 全部显示点亮┿

5-002 优先纸路选择┿

5-003 aps优先选择┿

5-504 仅在日本使用。不要改变工厂设定。

5-505 仅在日本使用。不要改变工厂设定。

5-507 仅在日本使用。不要改变工厂设定。

5-801 内存全清┿

2-801 搅拌显影剂

2-802 鼓充电辊湿度┿

2-812 鼓反转调整┿

2-901 鼓充电辊清洁间隔时间┿

2-902 未使用

3-801 自动过程控制方式选择┿

3-901 空运转(曝光灯熄灭)

3-902 强制性过程控制

光学

4-001 曝光灯电压调整┿

5-906 手动装订复位时间设定┿

5-907 封页方式选择┿

5-908 图象移动/删除选择┿

5-909 数字键变倍/尺寸倍率┿

5-910 操作指导的语种设定(仅指a207复印机上)

2-208-001 初粉方式选择┿

2-208-002 补粉率(td传感器补粉方式)┿

2-208-003 补粉率(定量补粉方式)┿

2-214 td传感器初期设定

鼓周围

2-001 鼓充电电压调整(供复印)

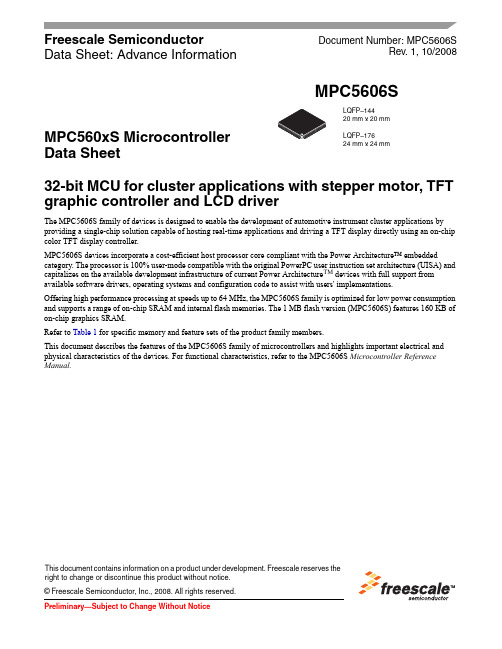

MPC5606S中文资料

This document contains information on a product under development. Freescale reserves the right to change or discontinue this product without notice.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Offering high performance processing at speeds up to 64 MHz, the MPC5606S family is optimized for low power consumption and supports a range of on-chip SRAM and internal flash memories. The 1 MB flash version (MPC5606S) features 160 KB of on-chip graphics SRAM.

2 Pinout and Signal Descriptions. . . . . . . . . . . . . . . . . . . . . . . . .9 2.1 144 LQFP Package Pinout . . . . . . . . . . . . . . . . . . . . . .10 2.2 176 LQFP Package Pinout . . . . . . . . . . . . . . . . . . . . . .11 2.3 208 MAPBGA Package Pinout . . . . . . . . . . . . . . . . . . .11 2.4 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 2.4.1 Pad Configuration during Reset Phases . . . . . .13 2.4.2 Voltage Supply Pins. . . . . . . . . . . . . . . . . . . . . .13 2.4.3 Pad Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 2.4.4 System Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . .15 2.4.5 Nexus Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 2.4.6 Functional Ports A, B, C, D, E, F, G, H, I, J, K . .18 2.4.7 Signal Details. . . . . . . . . . . . . . . . . . . . . . . . . . .36

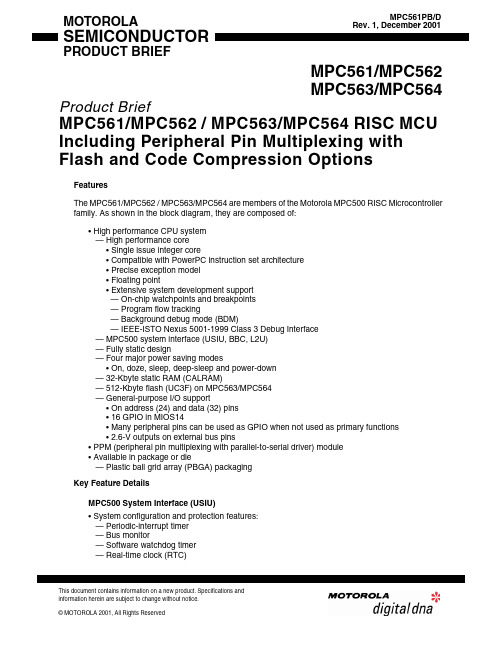

MPC561中文资料

MOTOROLA SEMICONDUCTOR PRODUCT BRIEFThis document contains information on a new product. Specifications and information herein are subject to change without notice.MPC561PB/DRev. 1, December 2001MPC561/MPC562 MPC563/MPC564Product BriefMPC561/MPC562 / MPC563/MPC564 RISC MCUIncluding Peripheral Pin Multiplexing withFlash and Code Compression OptionsFeaturesThe MPC561/MPC562 / MPC563/MPC564 are members of the Motorola MPC500 RISC Microcontrollerfamily. As shown in the block diagram, they are composed of:• High performance CPU system— High performance core• Single issue integer core• Compatible with PowerPC instruction set architecture• Precise exception model• Floating point• Extensive system development support— On-chip watchpoints and breakpoints— Program flow tracking— Background debug mode (BDM)— IEEE-ISTO Nexus 5001-1999 Class 3 Debug Interface— MPC500 system interface (USIU, BBC, L2U)— Fully static design— Four major power saving modes• On, doze, sleep, deep-sleep and power-down— 32-Kbyte static RAM (CALRAM)— 512-Kbyte flash (UC3F) on MPC563/MPC564— General-purpose I/O support• On address (24) and data (32) pins• 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• PPM (peripheral pin multiplexing with parallel-to-serial driver) module• Available in package or die— Plastic ball grid array (PBGA) packagingKey Feature DetailsMPC500 System Interface (USIU)• System configuration and protection features:— Periodic-interrupt timer— Bus monitor— Software watchdog timer— Real-time clock (RTC)元器件交易网— Decrementer— Time base• Clock synthesizer• Power management• Reset controller• External bus interface that tolerates 5-V inputs, provides 2.6-V outputs and supports multiple-mas-ter designs• Enhanced interrupt controller that supports up to eight external and 40 internal interrupts, simpli-fies the interrupt structure and decreases interrupt processing time• USIU supports dual mapping to map part of one internal/external memory to another external memory• USIU supports dual mapping of flash on MPC563 and MPC564 to move part of internal flash mem-ory to external bus for development• External bus, supporting non-wraparound burst for instruction fetches, with up to 8 instructions per memory cycleBurst Buffer Controller (BBC) Module• Support for enhanced interrupt controller (EIC)• Support for enhanced exception table relocation feature• Branch target buffer• Contains 2-Kbytes of decompression RAM (DECRAM) for code compression. This RAM may also be used as general-purpose RAM when code compression feature not used.Flexible Memory Protection Unit• Flexible memory protection units (MPU) in BBC and L2U• Default attributes available in one global entry• Attribute support for speculative accesses• Up to eight memory regions are supported, four for data and four for instructionsMemory Controller• Four flexible chip selects via memory controller• 24-bit address and 32-bit data buses• 4-Kbyte to one 16-Mbyte (data) or four-Gbyte (instruction) region size support• Supports enhanced external burst• Up to eight-beat transfer bursts, two-clock minimum bus transactions• Use with SRAM, EPROM, flash and other peripherals• Byte selects or write enables• 32-bit address decodes with bit masks• Four regions512-Kbytes of CDR3 Flash EEPROM Memory (UC3F) – MPC563 Only• One 512-Kbyte module• Page read mode• Block (64 Kbytes) erasable• External 4.75- to 5.25-V VFLASH power supply for program, erase, and read operations32-Kbyte static RAM (CALRAM)• Composed of one 32-Kbyte CALRAM module— 28-Kbyte static RAM— 4-Kbyte calibration (overlay) RAM feature that allows calibration of flash-based constants • Eight 512-byte overlay regions• One clock fast accesses• Two-clock cycle access option for power saving• Keep-alive power (VDDSRAM) for data retentionGeneral-Purpose I/O Support• 24 Address pins and 32 data pins can be used for general-purpose I/O in single-chip mode • 16 GPIO in MIOS14• Many peripheral pins can be used as GPIO when not used as primary functions• 2.6-V outputs on external bus pins• 5-V outputs with slew rate controlNEXUS Debug Port (Class 3)• Compliant with Class 3 of the IEEE-ISTO Nexus 5001-1999• Program trace via branch trace messaging (BTM)• Data trace via data write messaging (DWM) and data read messaging (DRM)• Ownership trace via ownership trace messaging (OTM)• Run-time access to on-chip memory map and MPC5xx special purpose registers (SPRs) via the READI read/write access protocol• Watchpoint messaging via the auxiliary port• Reduced-port mode (1 MDI, 2 MDO) or full-port mode (2 MDI. 8 MDO)• All features configurable and controllable via the auxiliary port• Security features for production environment• Supports the RCPU debug mode via the auxiliary port• READI module can be reset independent of system resetIntegrated I/O SystemTwo Time Processor Units (TPU3)• True 5-V I/O• Two time processing units (TPU3) with16 channels each• Each TPU3 is a micro-coded timer subsystem• Eight-Kbytes of dual port TPU RAM (DPTRAM) shared by two TPU3 modules for TPU micro-code22-Channel Modular I/O System (MIOS14)• Six modulus counter sub-modules (MCSM)• 10 double-action sub-modules (DASM)• 12 dedicated PWM sub-modules (PWMSM)• One MIOS14 16-bit parallel port I/O sub-modules (MPIOSM)Two Enhanced Queued Analog-to-Digital Converter Modules (QADC64E)• Two queued analog-to-digital converter modules (QADC64_A, QADC64_B) providing a total of 32 analog channels• 16 analog input channels on each QADC64E module using internal multiplexing• Directly supports up to four external multiplexers• Up to 41 total input channels on the two QADC64E modules with external multiplexing• Software configurable to operate in Enhanced or Legacy (MPC555 compatible) mode• Unused analog channels can be used as digital input/output pins— GPIO on all channels in Enhanced mode• 10-bit A/D converter with internal sample/hold• Typical conversion time of less than 5 µs (>200 K samples/second)• Two conversion command queues of variable length• Automated queue modes initiated by:— External edge trigger— Software command— Periodic/interval timer within QADC64E module, that can be assigned to both queue 1 and 2— External Gated trigger (queue 1only)• 64 result registers— Output data is right- or left-justified, signed or unsigned• Alternate reference input (ALTREF), with control in the conversion command word (CCW)Three CAN 2.0B Controller (TouCAN) Modules• Three TouCAN modules (TOUCAN_A, TOUCAN_B, TOUCAN_C)• Each TouCAN provides the following features:— 16 message buffers each, programmable I/O modes— Maskable interrupts— Independent of the transmission medium (external transceiver is assumed)— Open network architecture, multi-master concept— High immunity to EMI— Short latency time for high-priority messages— Low-power sleep mode, with programmable wake-up on bus activity— TOUCAN_C pins are shared with MIOS14 GPIO or QSMCMQueued Serial Multi-Channel Module (QSMCM)• One queued serial module with one queued SPI and two SCIs (QSMCM)• QSMCM matches full MPC555 QSMCM functionality• Queued SPI— Provides full-duplex communication port for peripheral expansion or inter-processor commu-nication— Up to 32 preprogrammed transfers, reducing overhead— Synchronous serial interface with baud rate of up to system clock / 4— Four programmable peripheral-selects pins:— Support up to 16 devices with external decoding— Support up to eight devices with internal decoding— Special wrap-around mode allows continuous sampling of a serial peripheral for efficient inter-facing to serial analog-to-digital (A/D) converters• SCI— UART mode provides NRZ format and half- or full-duplex interface— 16 register receive buffers and 16 register transmit buffers on one SCI— Advanced error detection and optional parity generation and detection— Word-length programmable as eight or nine bits— Separate transmitter and receiver enable bits, and double buffering of data— Wake-up functions allow the CPU to run uninterrupted until either a true idle line is detected, or a new address byte is receivedPeripheral Pin Multiplexing (PPM) PPM• Synchronous serial interface between the microprocessor and an external device• Four internal parallel data sources can be multiplexed through the PPM— TPU3_A: 16 channels— TPU3_B: 16 channels— MIOS14: 12 PWM channels, 4 MDA channels— Internal GPIO: 16 general-purpose inputs, 16 general-purpose outputs• Software configurable stream size• Software configurable clock (TCLK) based on system clock• Software selectable clock modes (SPI mode and TDM mode)• Software selectable operation modes— Continuous mode— Start-transmit-receive (STR) mode• Software configurable internal modules interconnect (shorting)MPC561/MPC562 / MPC563/MPC564 Optional FeaturesThe following are optional features of the MPC561/MPC562 / MPC563/MPC564:• 56-MHz operation (40 MHz is default)• Code compression supported on the MPC562 and the MPC564— Compression reduces instruction memory requirements by 40-50%— Compression optimized for automotive (non-cached) applications • 512 Kbytes flash (available on the MPC563/MPC564 only)— Single array— Page mode read— Block (64 Kbytes) erasable— External 4.75- to 5.25-V VFLASH program, erase, and read power supplyFigure 1 MPC561/MPC562 / MPC563/MPC564 Block DiagramE-BUSMPC5xx Core L-BUSU-BUSIMB3+FPUSIUBuffer Burst Int.L2U I/FUIMB QSMCM MIOS14DPTRAM8-Kbyte READIQADC64JTAGTPU3QADC64TPU332-Kbyte CALRAM 28-Kbyte (No Overlay)4-Kbyte OverlayTou CAN Tou CANPPMSRAM Tou CAN Controller512 Kbytes Flash (on MPC563/MPC564 only)Figure 2 MPC561 / MPC563 Internal Memory Map4-Kbyte Overlay Section0x30 7FFF 0x2F FFFF 0x30 00000x00 00000x38 00000x38 3FFF 0x3F FFFF0x2F C0000x2F BFFF 0x30 80000x37 FFFF 0x38 40000x07 FFFF 0x3F 7FFF 0x3F 80000x08 00000x38 00FF 0x38 01000x2F 80000x2F 7FFF UC3F Flash*512 KbytesReserved for Flash 2,605 KbytesBBC DECRAM 2 Kbytes USIU & Flash Control16 KbytesUIMB I/F & IMB Modules 32 KbytesReserved for IMB 491 Kbytes CALRAM/READI Control 256 bytes Reserved (L-bus Control)~32 KbytesReserved (L-bus Mem)464 KbytesCALRAM 32 Kbytes*NOTE: Only available on MPC563/MPC564.0x3F F0000x30 00000x30 7FFFDPTRAM (8 Kbytes)QSMCM (1 Kbyte)MIOS14 (4 Kbytes)TOUCAN_A (1 Kbyte)TOUCAN_B (1 Kbyte)UIMB Registers (128 bytes)TPU3_A (1 Kbyte)TPU3_B (1 Kbyte)QADC64_A (1 Kbyte)QADC64_B (1 Kbyte)DPTRAM Control (32 bytes)USIU Control Registers0x2F C0000x30 7C000x30 70000x30 60000x30 54000x30 50000x30 4C000x30 48000x30 44000x30 40000x30 20000x30 7400Reserved (8160 bytes)Reserved (2 Kbytes)Reserved (896 bytes)0x30 78000x2F C8000x30 7F80TOUCAN_C (1 Kbyte)0x30 5C00PPM (64 bytes)0x30 5C80Reserved (960 bytes) 0x30 0020UC3F Control Registers*0x2F 8800 Reserved for BBC 0x2F A000 BBC CONTROLFigure 3 MPC561 / MPC563 Ball Map1234567891011121314151617181920212223242526AVDDVSSVSSVSSA_TPUCH3A_TPUCH7A_TPUCH11A_TPUCH15VSSAVRLA_AN3_A NZ_PQB3A_AN51_P QB7A_AN55_PQA3A_AN56_P QA4B_AN0_AN W_PQB0B_AN48_PQB4B_AN52_M A0_PQA0B_AN56_P QA4VSSETRIG2_PCS7MDA13MDA28VSSVSSVDDVSSAB VSS VDD VSS VSS A_TPUCH2A_TPUCH6A_TPUCH10A_TPUCH14VSSA ALTREF A_AN2_A NY_PQB2A_AN50_P QB6A_AN54_MA2_PQ A2A_AN58_P QA6B_AN1_AN X_PQB1B_AN49_PQB5B_AN53_M A1_PQA1B_AN57_P QA5VSSETRIG1_PCS6MDA14MDA29VSSVDDVSSQVDDLBC VSS VSS VDD VSS A_TPUCH1A_TPUCH4A_TPUCH8A_TPUCH12NVDDL VRH A_AN0_A NW_PQB 0A_AN48_P QB4A_AN52_MA0_PQ A0A_AN59_P QA7B_AN2_AN Y_PQB2B_AN50_PQB6B_AN54_M A2_PQA2B_AN58_P QA6VDDH MDA11MDA15VDDH VDD VSS QVDDL VSS CD VSS VSS VSS VDD VSS A_TPUCH5A_TPUCH9A_TPUCH13NVDDL VDDA A_AN1_A NX_PQB1A_AN49_P QB5A_AN53_MA1_PQ A1A_AN57_P QA5B_AN3_AN Z_PQB3B_AN51_PQB7B_AN55_P QA3B_AN59_P QA7VDDH MDA12MDA27VDD VSS QVDDL VSS VSS DE VDDH VSS VSS VSS QVDDL VSS VSS VSS EF B_T2CLK_P CS4A_T2CLK_PCS5A_TPUCH 0QVDDL VDDH MDA30MDA31MPWM0_MDI1F GB_TPUCH12B_TPUCH13B_TPUCH 14B_TPUCH15MPWM1_MDO2MPWM16MPWM3_PP M_RX1MPWM2_PP M_TX1GH B_TPUCH8B_TPUCH9B_TPUCH 10B_TPUCH11MPWM17_M DO3MPWM18_MD O6MPWM19_MDO7MPIO32B5_MDO5HJ B_TPUCH4B_TPUCH5B_TPUCH6B_TPUCH7MPIO32B6_MPWM4_MDO6MPIO32B7_MP WM5MPIO32B8_MPWM20MPIO32B9_MPWM21JK B_TPUCH0B_TPUCH1B_TPUCH2B_TPUCH3MPIO32B12_C_CNTX0MPIO32B11_C _CNRX0MPIO32B10_PPM_TSYNC MPIO32B13_PPM_TCLK KLJCOMP_RS TI_B TCK_DSCK_MCKI B_CNRX0B_CNTX0VSS VSS VSS VSS VSS VSS VF0_MPIO32B0_MDO1VF1_MPIO32B 1_MCKO MPIO32B15_PPM_TX0MPIO32B14_PPM_RX0LM TDI_DSDI_MDI0TMS_EVTI _B VDDSRA MTDO_DSDO_MDO0VSS VSS VSS VSS VSS VSS A_CNTX0VF2_MPIO32B2_MSEI_B VFLS0_MPIO32B3_MSEO_BVFLS1_MPIO 32B4M N IRQ3_B_KR_B_RETRY _B_SGPIO C3IWP0_VFL S0IWP1_VFL S1SGPIOC6_FRZ_PTR_BVSS VSS VSS VSS VSS VSSPCS2_QGPI O2PCS1_QGPIO1PCS0_SS_B_QGPIO0A_CNRX0NP IRQ4_B_AT 2_SGPIOC4IRQ2_B_CR_B_SGPIOC2_MDO5_MTSIRQ0_B_S GPIOC0_MDO4IRQ1_B_RSV_B_SGPIOC1VSS VSS VSS VSS VSS VSSSCK_QGPIO 6MOSI_QGPIO5MISO_QGPIO4PCS3_QGPIO3PR SGPIOC7_IRQOUT_B_LWP0BB_B_VF2_IWP3BG_B_VF 0_LWP1BR_B_VF1_IWP2VSS VSS VSS VSS VSS VSSRXD1_QGPI 1TXD2_QGPO2_C_CNTX0TXD1_QGPO1PULL-SEL RTWE_B_AT0WE_B_AT1WE_B_AT 2WE_B_AT 3VSS VSS VSS VSS VSS VSS EPEE BOEPEE VDDHRXD2_QGPI2_C_CNRX0TU CS0_B CS1_B CS2_BCS3_BCLKOUT VSSF VDDF VFLASH UV RD_WR_B OE_B TEA_B TSIZ0VDD EXTCLK VSS ENGCLK_BUCLK VW TSIZ1TS_B TA_B BDIP_B HRESET_B SRESET_B PORESET_B _TRST_BKAPWRWY BURST_BBI_B_STS_B ADDR_SG PIOA12ADDR_SG PIOA11NVDDLIRQ7_B_MODC K3RSTCONF_B_TEXPVDDSYN YAA VSS VSS VSS QVDDL VSS VSS VSS XFC AA ABVSSVSSQVDDLVSSQVDDLVSSVSSVSSSYNABAC VSS QVDDL VSS NVDDL VSS ADDR_SGP IOA10ADDR_SG PIOA18ADDR_SGPI OA20ADDR_SGPIOA23NVDDL ADDR_S GPIOA26DATA_SG PIOD1DATA_SG PIOD5DATA_SGPIOD7NVDDL DATA_SG PIOD9DATA_SGP IOD11DATA_SGPIOD12NVDDL DATA_SGPIOD14VSS VDD VSS QVDDL VSS EXTAL ACAD QVDDL VSS NVDDL VSS VSS QVDDLADDR_SG PIOA13ADDR_SGPI OA16ADDR_SG PIOA19ADDR_SGP IOA21ADDR_S GPIOA24ADDR_SG PIOA25DATA_SG PIOD0DATA_SG PIOD28DATA_SGP IOD26DATA_SG PIOD24DATA_SGP IOD22DATA_SG PIOD13DATA_SGPI OD15DATA_SGPIOD16IRQ5_B_SGPIOC5_MODCK1VSS VDD VSS QVDDL XTAL ADAE VSS NVDDL VSS VSS VSS QVDDL ADDR_SG PIOA14ADDR_SGPI OA17ADDR_SG PIOA31ADDR_SGP IOA30ADDR_S GPIOA28ADDR_SG PIOA29DATA_SG PIOD30DATA_SG PIOD29DATA_SGP IOD27DATA_SG PIOD25DATA_SGP IOD23DATA_SG PIOD21DATA_SGPI OD19DATA_SGPIOD17IRQ6_B_MODCK2VSS VSS VDD VSS QVDDL AEAF NVDDL VSS VSS VSS VDDH VSS ADDR_SG PIOA15ADDR_SGPI OA9ADDR_SG PIOA8ADDR_SGP IOA22ADDR_S GPIOA27DATA_SG PIOD31DATA_SG PIOD3DATA_SG PIOD2DATA_SGP IOD4DATA_SG PIOD6DATA_SGP IOD8DATA_SG PIOD10DATA_SGPI OD20DATA_S GPIOD18VDDH VSS VSS VSS VDD VSS AF1234567891011121314151617181920212223242526MPC561 / MPC563 Ball Map(As viewed from top, through the package and silicon)NOTE: The flash balls are only available on the MPC563 and MPC564. These are no connect balls onthe MPC561 and MPC562. Flash supplies and inputs are located on the following balls: T23, T24, U24, U25. U26.Ordering InformationTable 2 lists the documents that provide a complete description of the MPC561/563 and are required to design properly with the part. Documentation is available from a local Motorola distributor, a Motorola semiconductor sales office, a Motorola Literature Distribution Center, or through the Motorola Semicon-ductor documentation page on the Internet (the source for the latest information).Table 1 MPC561/562 / MPC563/564Device Name Order Part Number 1NOTES:1. Add R2 suffix for parts shipped in tape and reel media.Package Info Temperature Range Maximum Frequency Code CompressionMPC561MPC561MZP40388 PBGA -40 – 125° C 40 MHz No MPC561MPC561CZP40388 PBGA -40 – 85° C 40 MHz No MPC561MPC561MZP56388 PBGA -40 – 125° C 56 MHz No MPC561MPC561CZP56388 PBGA -40 – 85° C 56 MHz No MPC562MPC562MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC562MPC562CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC562MPC562MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC562MPC562CZP56388 PBGA -40 – 85° C 56 MHz Yes MPC563MPC563MZP40388 PBGA -40 – 125° C 40 MHz No MPC563MPC563CZP40388 PBGA -40 – 85° C 40 MHz No MPC563MPC563MZP56388 PBGA -40 – 125° C 56 MHz No MPC563MPC563CZP56388 PBGA -40 – 85° C 56 MHz No MPC564MPC564MZP40388 PBGA -40 – 125° C 40 MHz Yes MPC564MPC564CZP40388 PBGA -40 – 85° C 40 MHz Yes MPC564MPC564MZP56388 PBGA -40 – 125° C 56 MHz Yes MPC564MPC564CZP56388 PBGA-40 – 85° C56 MHzYesTable 2 Available DocumentationDocument Number TitleMPC561_3RM/ADMPC561/MPC563 Reference ManualAN1821/D Exception Table Relocation and Multi-Processor Address Mapping in the Embedded MPC5XX Family AN2109/D MPC555 Interrupts.AN2127/DEMC Guidelines for MPC500-Based Automotive Powertrain SystemsMPC561/MPC563 PRODUCTBRIEF MOTOROLA11Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty,representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers,employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.OnCE, DigitalDNA, and the DigitalDNA logo are trademarks of Motorola, Inc.Order Number MPC561PB/DHow to reach us:USA/EUROPEMotorola Literature DistributionP.O. Box 5405Denver, Colorado 802171-303-675-21401-800-441-2447Technical Information Center1-800-521-6274JAPAN Motorola Japan Ltd.SPS, Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569ASIA/PACIFICMotorola Semiconductors H.K. Ltd.Silicon Harbour Centre2 Dai King StreetTai Po Industrial EstateTai Po, N.T., Hong Kong852-********Home Page /semiconductors。

RiCoh MP 4054 MP 5054 MP 6054 多功能黑白复印机打印机传真扫描仪说明书

CopierPrinterFacsimileScannerMP 6054ppmmonochrome60MP 4054ppmmonochrome40MP 5054ppmmonochrome50Manage information — and new opportunities — effortlessly You’re the expert. But what good is having all that information if you can’t share it with anybody? With the RICOH®MP 4054/MP 5054/MP 6054, you can produce and share your best ideas with more people in more locations. Whether you need to print important documents and fax them to a client, scan an invoice to your mailbox or simply copy notes from a morning meeting, you can move information quickly and intuitively from this multifunction device. Create shortcuts for frequent tasks to save time. Use your smartphone to print documents whether you’re at your desk, down the hall or outof the office. Take advantage of user authentication tools to ensure key information gets to the right people. You can even monitor user activity and energy consumption remotely, so you know if you’re making the right decisions along the way.• Print up to 60 black-and-white prints/copies per minute• Use mobile printing to produce documents from anywhere• Perform more everyday tasks using less space• Protect documents and intellectual property with user authentication• Minimize operating costs with energy-saving featuresPerform ordinary tasks with extraordinary precisionImprove the way you manage informationWork faster, make better decisionsHow quickly can you get information in the hands of those who need it themost? Use the Ricoh MP 4054/MP 5054/MP 6054 to transition from one jobto the next with ease. With recovery from sleep mode in only 4.9 seconds, youcan start moving information almost as soon as you think of it. Use the intuitive,one-touch controls to produce up to 60 black-and-white pages per minuteon a wide range of media. Convert paper documents into digital format forfaster retrieval and distribution with the standard 220-Sheet Single PassDocument Feeder (SPDF), which scans up to 180 color or black-and-whiteimages per minute. You can also use the optional OCR scanning featureto create PDF files that can be accessed simply by searching for key wordsin the document.Work from more locationsYou never know where your workday will take you. Be ready for anything— from anywhere. Print directly to the Ricoh MP 4054/MP 5054/MP 6054using Ricoh HotSpot Enterprise. Use your smartphone to connect to theMFP and print network documents at your convenience and save yourselfa long trek back to your desk. You can also bring your work with you viaa USB drive or SD card. Simply plug it into the networked MFP and printor scan documents right from the device. With the Ricoh Smart DeviceConnector app, you can copy, print, scan and fax directly from your smartdevice. Simply touch your smart device to the NFC tag on the optionalSmart Operation Panel or scan the QR Code to automatically connect tothe MFP and access these functions.Minimize steps, maximize productivityNobody knows your job better than you do — so you know how to makeit better. With the Ricoh MP 4054/MP 5054/MP 6054, you can customizeworkflows to simplify how you work. Use icons on the Home Screen asshortcuts to frequently used tasks and skip repetitive steps with a singletouch. Take advantage of embedded software like Ricoh GlobalScan NX toscan and convert paper documents to digital files quickly so you gain easieraccess to important information across the enterprise. Add other third-partyvendor solutions to simplify content management and other business-criticaltasks so you can work with fewer manual touchpoints and minimize errors.Impress with high-quality documentsCapture the attention of your audience with a wider range of professional-looking documents. It’s easy with the icon-driven, preset PCL6 interfacedriver. With a single click, you can produce eye-catching black-and-whitedocuments at up to 1200 dpi. Print on more types of stocks, includingthicker paper, sizes up to 11" x 17" and even envelopes from thestandard tray. Plus, you can choose between several automatedfinishers for end-to-end document production with incredible qualityin fewer steps.Simplify your workday with a wider range of capabilitiesAccess key functions convenientlyYou use your smartphone or tablet every day because it’s convenientand keeps you connected. Now you can say the same about the MFPin your office. With the Ricoh MP 4054/MP 5054/MP 6054, you cansimplify routine actions like printing, copying, scanning and faxingwith the same intuitive drag-and-drop, pinch-and-flick and swipescrolling you use on your personal devices. Navigate between keyfunctions with ease via the optional 10.1" Wide Super VGA SmartOperation Panel. You’ll have fewer steps, so you can access andshare information in only moments.Move information in more ways,from more placesYou have enough to do. Let us handle some of it for you. After all,our legacy includes finding fast, affordable ways to automate routine tasks to simplify the way you work. Need to grab an important document to share with an offsite client? Want to share newly captured information with people who may be away from the office? Use the optional Ricoh Integrated Cloud Environment (ICE) solution to manage information in the Cloud — and be spared expensive servers, equipment and maintenance. Visitors to your office can have the same convenience. They can send emails with attachments directly to the MFP for fast, easy printing without downloading print drivers. Protect what’s most importantYou have something in high demand — information. It’s important that you protect it to ensure it gets to the right people. With the Ricoh MP 4054/MP 5054/MP 6054, you can store documents atthe device for safekeeping. Release them by swiping an authorizedID card at the optional card reader or by entering a passcode on the control panel. Add watermarks to documents and mask copy when unauthorized users try to duplicate them. You can also use PDF encryption to scramble data on confidential PDFs to keep information safe. Worried about information you leave behind? With the DataOverwriteSecurity System (DOSS), images and data on thehard drive are rendered unreadable automatically.SCANCLOUD SERVICESPC/TABLET /SMARTPHONE MFPUSER INTERFACESCAN/PRINTSCANDATASCANDATAPRINTDATAPRINTUPLOAD/DOWNLOADOCRINTEGRATED CLOUD ENVIRONMENTDiscover an easier way to handle more types of jobsImprove collaboration with digital deliveryYou can’t predict when you’re going to get a great idea. But youcan know exactly when the next person gets it. Send importantinformation — including black-and-white or color images anddocuments — in PDF, TIFF or JPEG formats via Scan-to-File/Folder/URL/FTP/Email without wasting paper or time. You can compresslarger or more complex graphics files and send them just as easilywithout compromising quality. When you need to send contracts,invoices or other paper documents, use Internet Faxing, LAN Faxingor IP Fax for fast delivery. You can even use the Ricoh MP 4054/MP 5054/MP 6054 as a conduit for remote faxing and minimizethe need for additional phone lines and fax boards.Expedite everyday tasksYou’re facing enough challenges. Your office MFP shouldn’t be yournext one. On other systems, a single paper jam can derail productivityfor an entire workgroup before the problem is even discovered. Withthe Ricoh MP 4054/MP 5054/MP 6054, you only need to follow theon-screen animation and LED guide (inside the MFP) and you cantrace the source of the problem in moments. Reloading paper is justas easy. Expand capacity to 4,700 sheets with optional paper traysand print for extended runs without interruptions. In addition, you canautomate meter reads, access system settings, streamline firmwareupdates and more — all from the convenience of your desktop —so you can spend more time on core, revenue-generating tasks.Conserve energy to reduce operating costsYou’ll find just the opposite to be true with the Ricoh MP 4054/MP 5054/MP 6054. It offers low cost-per-page and best-in-classtypical electricity consumption (TEC) values so you can reduce costswhile meeting your sustainability goals. With a shorter recoverytime of less than 5 seconds from sleep mode, the Ricoh MP 4054/MP 5054/MP 6054 keeps up with today’s fast-paced businessenvironment. You can program the device to power on or off duringspecified times to conserve energy for even greater savings. Plus, thedevice meets EPEAT® Gold* criteria — a global environmental ratingsystem for electronic products — and is certified with the latestENERGY STAR™ specifications.Eco-Friendly Indicator Screen as shown on the Smart Operation Panel. *EPEAT Gold rating is applicable only in the USA.tasks in small offices and workgroups123457635Ricoh MP 6054 shown with optional one-Bin Tray, 2,000-Sheet Tandem Large Capacity Tray, 1,500-Sheet Side Large Capacity Tray and 3,000-Sheet Stapler Finisher.R3533Ricoh Americas Corporation, 70 Valley Stream Parkway, Malvern, PA 19355, 1-800-63-RICOHRicoh and the Ricoh Logo are registered trademarks of Ricoh Company, Ltd. All other trademarks are the property of their respective owners. ©2015 Ricoh Americas Corporation. All rights reserved. The content of this document, and the appearance, features and specifications of Ricoh products and services are subject to change from time to time without notice. Products are shown with optional features. While care has been taken to ensure the accuracy of this information, Ricoh makes no representation or warranties about the accuracy, completeness or adequacy of the information contained herein, and shall not be liable for any errors or omissions in these materials. Actual results will vary depending upon use of the products and services, and the conditions and factors affecting performance. The only warranties for Ricoh products and services are as set forth in the express warranty statements accompanying them.。

Addressing SR SIL3 and ASIL-D with MPC5643L

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorIQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

►Note:

No hands-on programming session

Wed. 14:00; Gene Fortanely, Multicore Initiation: System Initialization for the MPC5643L

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorIQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

MPC565MZP40中文资料

MOTOROLA

MPC565PB/D Rev. 2, 5 DNDUCTOR

PRODUCT BRIEF

MPC565/MPC566

Product Brief

MPC565/MPC566 RISC MCU with Code Compression Option

Features The MPC565 / MPC566 key features are as follows. The information inside boxes are optional features. • 40 MHz / 56 MHz operation • 56 MHz operation is available as an option. — -40° – 125 °C ambient temperature — 2.6 V ± 0.1 V external bus • External bus is compatible with external memory devices operating from 2.5 V to 3.4 V. • Extended voltage range (2.7 – 3.4 V) degrades data drive timing by 1.1 ns on date writes. — 2.6 ± 0.1 V internal logic — 5-V I/O (5.0 ± 0.25 V) • High performance RISC CPU system — High performance core • Single issue integer core • Instruction set compatible with PowerPC instruction set architecture • Precise exception model • Floating point • Code compression supported on the MPC566 — Compression reduces usage of internal or external flash memory — Compression optimized for automotive (non-cached) applications — New compression scheme increases compression performance to 40% – 50% compression — 4-Kbyte static DECRAM can be used as memory if Compression is not used. — General-purpose I/O support • On address (24) and data (32) pins • 16 GPIO in MIOS14 • Many peripheral pins can be used as GPIO when not used as primary functions • 2.6-V outputs on external bus pins • Extensive system development support — On-chip watchpoints and breakpoints — Program flow tracking — Background debug mode (BDM) Key Feature Details MPC500 System Interface (USIU, BBC, L2U) • Periodic interrupt timer, bus monitor, clocks, decrementer and time base • Clock synthesizer, power management, reset controller • External bus tolerates 5-V inputs, provides 3.3-V outputs • Enhanced interrupt controller supports a separate interrupt vector for up to eight external and 40 Internal interrupts

SPC560P34x SPC560P40x串行引导自动波特率自动扫描参考手册补充说明说明书

TN0837Technical note SPC560P34x/SPC560P40x Serial Boot with Autobaud Autoscanreference manual addendumIntroductionThe aim of this document is to give a supplementary description for serial boot modes inaddition to the description in RM0046, rev. 3 (see Section Appendix A). It is described thehardware configuration to allow the right selection of the serial boot mode with autobaud bymeans of autoscan and the RX pins configuration of serial communication peripherals(FlexCAN and LINFlex).September 2013Doc ID 022359 Rev 21/11Contents SPC560P34x, SPC560P40x Contents1Hardware configuration to select boot mode . . . . . . . . . . . . . . . . . . . . . 51.1SPC560P34x/SPC560P40x boot pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51.2Autobaud feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Appendix A Reference document. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102/11Doc ID 022359 Rev 2SPC560P34x, SPC560P40x List of tables List of tablesTable 1.Hardware configuration to select boot mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Table 2.SPC560P34x/SPC560P40x boot pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Table 3.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10Doc ID 022359 Rev 23/11List of figures SPC560P34x, SPC560P40x List of figuresFigure 1.BAM Autoscan code flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 4/11Doc ID 022359 Rev 2SPC560P34x, SPC560P40x Hardware configuration to select boot modeDoc ID 022359 Rev 25/111 Hardware configuration to select boot modeThe SPC560P34x/SPC560P40x devices detect the serial boot mode based on external pins.To enter boot mode via FlexCAN or LINFlex, the device must be forced into an Alternate Boot Loader Mode via the FAB (Force Alternate Boot Mode), which must be asserted before initiating the reset sequence. The type of alternate boot mode is selected according to the ABS (Alternate Boot Selector) pins (see Table 1).Boot configuration pins are:●PAD A[2] - ABS[0],●PAD A[3] - ABS[1],●PAD A[4] - FABNote:PAD A[2] - ABS[0] is not bonded on SPC560P34x/SPC560P40x LQFP64 so for thispackage the option 'FlexCAN without Autobaud ' is not available and the internal pull-down on PAD A[2] assures that it is at low logical value at reset."1.1 SPC560P34x/SPC560P40x boot pinsThe TX/RX pin (LINFlex_0 and FlexCAN_0) used for serial boot and configuration boot pins to select the serial boot mode are described in the Table 2 for LQFP64 and LQFP100 packages.Table 1.Hardware configuration to select boot modeFAB (1)1.During reset the boot configuration pins are weak pull down.ABS[1,0]Standby-RAM boot flagBoot IDBoot mode1000-Serial Boot via LINFlex without autobaud 1010-Serial Boot via FlexCAN without autobaud 110-Scan of both serial interfaces (FlexCAN and LINFlex) for Serial Boot with autobaudTable 2.SPC560P34x/SPC560P40x boot pinsPort pinFunctionPin64-pin100-pin A[2](1)ABS[0]-57A[3](1)ABS[1]4164A[4](1)FAB 4875B[0]CAN_0 TX 4976B[1]CAN_0 RX 5077B[2]LIN_0 TX5179Hardware configuration to select boot modeSPC560P34x, SPC560P40x6/11Doc ID 022359 Rev 21.2 Autobaud featureSPC560P34x/SPC560P40x devices implement the autobaud feature via FlexCAN orLINFlex selecting the active serial communication peripheral by means of an autoscan routine.When autobaud configuration is selected by ABS and FAB pins, the autoscan routine starts and listens to the active bus protocol. Initially the LinFlex_0 RX pin and FlexCAN_0 RX pin are configured as GPIO inputs:●for LQFP100 internal weak pull-up enabled for both RX pins,●for LQFP64 internal weak pull-up enabled only for FlexCAN_0 RX pin.The autoscan routine waits in polling for the first LOW level to select which routine will be executed:●FlexCAN Autobaud routine ●LinFlex Autobaud routineThen the measurement baud rate is computed to configure the serial communication at the right rate. In the end of baud rate measurement, LinFlex_0 RX pin and FlexCAN_0 RX pin switches to work as dedicated pin.Baud rate measurement is using the System Timer Module (STM) which is driven by the system clock. Measurement itself is performed by software polling the related inputs as general purpose IO’s, resulting in a detection granularity that is directly related to the execution speed of the software.One main difference of the autobaud feature is that the system clock is not driven directly by the external oscillator, but it is driven by the FMPLL output. The reason is that to have an optimum resolution for baud rate measurement, the system clock needs to be nearer to the maximum allowed device’s frequency.This is achieved with the following two steps:ing the Clock Monitor Unit (CMU) and the internal RC oscillator (IRC), the external frequency is measured using the IRC as reference to determine this frequency.2.Based on the result of this measurement, the FMPLL is programmed to generate a system clock that is configured to be near, but lower, to the maximum allowed frequency.After setting up the system clock, the BAM autoscan code configures the FlexCAN RX pin (B[1] on all packages) and LINFlex RX pin (B[3] on LQFP100 or B[7] on LQFP64) as GPIO inputs and searches for FlexCAN RX pin level to verify if CAN is connected or not.B[3](2)LIN_0 RX -80(2)B[7](3)LIN_0 RX20(3)291.Weak pull down during reset.2.SPC560P34x/SPC560P40x LQFP100 package uses only PAD B[3] - pin 80 for boot via LINFLEX3.SPC560P34x/SPC560P40x LQFP64 package uses only PAD B[7] - pin 20 for boot via LINFLEXTable 2.SPC560P34x/SPC560P40x boot pins (continued)Port pinFunctionPin64-pin100-pinSPC560P34x, SPC560P40x Hardware configuration to select boot mode Then continuously waits in polling on change of RX pins level.The FlexCAN RX pin leveltakes precedence. First signal found at low level selects the serial boot routine that will beexecuted.In case a low level is detected on any input, the corresponding autobaud measurementfunctionality is started:●when FlexCAN RX (corresponds to pin B[1]) level is low, the CAN autobaudmeasurement starts and then sets up the FlexCAN baud rate accordingly;●when UART RX (corresponds to pin B[3] on LQFP100 or B[7] on LQFP64) level is low,the UART autobaud measurement starts and then sets up the LINFlex baud rateaccordingly.After performing the autobaud measurement and setting up the baud rate, thecorresponding RX input is reconfigured and the related standard download process isstarted; in case of a detected CAN transmission a download using the CAN protocol asdescribed in section “Bootstrap with FlexCAN— autobaud disabled”of RM0046, rev. 3 (seeSection Appendix A), and in case of a detected UART transmission a download using theUART protocol as described in Section” Boot from UART— autobaud disabled” of RM0046,rev.3 (see Section Appendix A).The following Figure1 identifies the corresponding flow and steps.Note:When autobaud scan is selected, initially both LINFlex_0 RX pin and FlexCAN_0 RX pin should be at high level. No external circuity should pull-down them to allow right autoscan.Doc ID 022359 Rev 27/11Hardware configuration to select boot modeSPC560P34x, SPC560P40x8/11Doc ID 022359 Rev 2Figure 1.BAM Autoscan code flowFlexCAN RX and LINFlex RX configured as GPIO inputsFlexCAN RX== 1FlexCAN RX== 0LINFlex RX== 0C A N A u t o b a u dSet matching baud rate for FlexCANAutobaud measurement Continue with FlexCANL I N F l e x A u t o b a u dSet matching baud rate for LINFlexAutobaud measurement downloadContinue with LINFlexdownloadNOYESdetecteddetectedLINFlex RX== 0detectedBoth RDX pins have to be at high level.Avoid to connect them to external pull-down resistor.If CAN is connected, after reset CAN_RX has to be at high levelSPC560P34x, SPC560P40x Reference document Appendix A Reference document1.SPC560P34/SPC560P40 32-bit MCU family built on the embedded PowerArchitecture® (RM0046, rev.3 - Doc ID 16912)Doc ID 022359 Rev 29/11Revision history SPC560P34x, SPC560P40x Revision historyTable 3.Document revision historyDate Revision Changes12-Oct-20111Initial release.18-Sep-20132Updated disclaimer.10/11Doc ID 022359 Rev 2SPC560P34x, SPC560P40xPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER’S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR “AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL” INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2013 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of AmericaDoc ID 022359 Rev 211/11。

MPC5565_08资料