On the Performance of Parallel Concatenated Joint Source-Channel Coding with Variable-Lengt

ORACLEparallel3个层面的影响

ORACLEparallel3个层⾯的影响有⼀些数据库性能问题可能是因为同时启动的并⾏进程过多造成的,特别常见于RAC节点重启,很多时候是因为瞬间启动了⼏百个并⾏进程,导致OS各项指标“彪⾼”,后台进程失去响应。

最近遇到的⼀个,是因为SQL语句中写了/*+ parallel a,8*/ ,但是在RAC的两个节点上各启动了512个并⾏进程,⼀共启动了1024个并⾏进程,导致⽹络⼼跳丢失。

因为问题可以通过执⾏这个语句重现,⽽使⽤parallel_force_local=true可以workaround这个问题,所以基本可以确定是跨节点并⾏导致的。

抛开这个问题背后的其他因素不谈,我们单来讨论⼀下:⼀条SQL语句究竟会产⽣多少个并⾏进程?⼀条SQL语句使⽤的并⾏度受3个层⾯的数值影响:1)hint中指定的并⾏度select /*+ parallel(a,8) */ * from scott.emp a order by ename;2)表的并⾏度,也就是表的degree:select owner,table_name,degree from dba_tables where table_name='EMP';OWNER TABLE_NAME DEGREE------------------------------ ------------------------------ ----------SCOTT EMP 23)auto DOP单节点:auto DOP = PARALLEL_THREADS_PER_CPU x CPU_COUNTRAC:auto DOP = PARALLEL_THREADS_PER_CPU x CPU_COUNT x INSTANCE_COUNT他们的优先级是hint>degree>auto DOP,也就是说:1)如果hint指定了并⾏度,会忽略表的degree。

samples_for_parallel_programming -回复

samples_for_parallel_programming -回复什么是并行编程?并行编程是一种编程方法,用于同时运行多个计算任务以提高程序的执行速度和性能。

它使得程序能够有效地利用多个处理器、内核或计算资源,以在同一时间内完成多个任务。

为什么需要并行编程?随着计算机硬件的发展,一台计算机不再只有单个处理器或核心。

现代计算机往往具有多个处理器或核心,这为程序的并行执行提供了机会。

并行编程可以将任务分解为多个子任务,并使它们在不同的处理器或核心上同时运行,从而提高程序的性能。

什么是并行计算?并行计算是指在多个处理器或核心上同时执行计算任务。

这种计算方式可以加速任务的完成,提高计算性能。

并行计算可以采用多种方法,例如数据并行、任务并行和流水线并行等。

数据并行是指将数据分成多个部分,然后将这些数据部分分配给不同的处理器或核心进行计算。

每个处理器或核心独立地处理自己的数据部分,最后将结果合并。

这种方式适用于需要对大量数据进行计算的任务。

任务并行是指将计算任务分成多个子任务,并将这些子任务分配给不同的处理器或核心进行执行。

每个处理器或核心独立地执行自己的子任务,最后将结果合并。

这种方式适用于需要同时执行多个独立任务的情况。

流水线并行是指将计算任务分成多个阶段,并将每个阶段分配给不同的处理器或核心进行处理。

每个处理器或核心按照一定的顺序执行自己的阶段,然后将结果传递给下一个处理器或核心。

这种方式适用于需要按照一定的顺序进行计算的任务。

并行编程的优势是什么?并行编程的优势在于提高程序的执行速度和性能。

通过将任务并行化,程序能够更有效地利用计算机的硬件资源,从而加速程序的执行。

并行编程还可以解决一些计算问题,如大规模数据处理、复杂模拟和高性能计算等。

并行编程也可以提高程序的可扩展性和灵活性。

随着计算机硬件的发展,我们可以通过增加处理器或核心的数量来提高计算性能。

通过并行编程,程序可以利用这些额外的处理器或核心,从而实现更好的可扩展性。

c++ vector 选择题

c++ vector 选择题英文回答:1. Which of the following is not a member function of the vector class?(A) push_back.(B) pop_back.(C) front.(D) reverse.2. What is the time complexity of inserting an element at the beginning of a vector?(A) O(1)。

(B) O(log n)。

(C) O(n)。

(D) O(n^2)。

3. Which of the following iterators can be used to iterate over a vector in reverse order?(A) begin()。

(B) end()。

(C) rbegin()。

(D) rend()。

4. What is the default capacity of a vector?(A) 0。

(B) 1。

(C) The size of the vector.(D) The maximum possible size of the vector.5. Which of the following is not an advantage of usinga vector over an array?(A) Dynamic size.(B) Faster access.(C) More efficient memory usage.(D) Easier to iterate over.中文回答:1. 以下哪些不是 vector 类的成员函数?(A) push_back.(B) pop_back.(C) front.(D) reverse.2. 在向量的开头插入一个元素的时间复杂度是多少?(A) O(1)。

AD9528

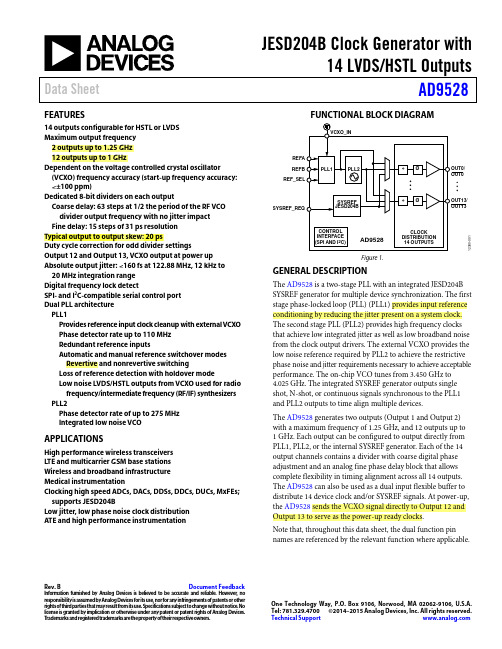

JESD204B Clock Generator with14 LVDS/HSTL OutputsData SheetAD9528Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2014–2015 Analog Devices, Inc. All rights reserved. Technical Support FEATURES14 outputs configurable for HSTL or LVDS Maximum output frequency2 outputs up to 1.25 GHz 12 outputs up to 1 GHzDependent on the voltage controlled crystal oscillator(VCXO) frequency accuracy (start-up frequency accuracy: <±100 ppm)Dedicated 8-bit dividers on each outputCoarse delay: 63 steps at 1/2 the period of the RF VCO divider output frequency with no jitter impact Fine delay: 15 steps of 31 ps resolution Typical output to output skew: 20 psDuty cycle correction for odd divider settingsOutput 12 and Output 13, VCXO output at power up Absolute output jitter: <160 fs at 122.88 MHz, 12 kHz to 20 MHz integration range Digital frequency lock detectSPI- and I 2C-compatible serial control port Dual PLL architecture PLL1Provides reference input clock cleanup with external VCXO Phase detector rate up to 110 MHz Redundant reference inputsAutomatic and manual reference switchover modes Revertive and nonrevertive switchingLoss of reference detection with holdover modeLow noise LVDS/HSTL outputs from VCXO used for radio frequency/intermediate frequency (RF/IF) synthesizers PLL2Phase detector rate of up to 275 MHz Integrated low noise VCOAPPLICATIONSHigh performance wireless transceivers LTE and multicarrier GSM base stations Wireless and broadband infrastructure Medical instrumentationClocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs; supports JESD204BLow jitter, low phase noise clock distribution ATE and high performance instrumentationFUNCTIONAL BLOCK DIAGRAMFigure 1.GENERAL DESCRIPTIONThe AD9528 is a two-stage PLL with an integrated JESD204B SYSREF generator for multiple device synchronization. The first stage phase-locked loop (PLL) (PLL1) provides input reference conditioning by reducing the jitter present on a system clock. The second stage PLL (PLL2) provides high frequency clocks that achieve low integrated jitter as well as low broadband noise from the clock output drivers. The external VCXO provides the low noise reference required by PLL2 to achieve the restrictive phase noise and jitter requirements necessary to achieve acceptable performance. The on-chip VCO tunes from 3.450 GHz to 4.025 GHz. The integrated SYSREF generator outputs single shot, N-shot, or continuous signals synchronous to the PLL1 and PLL2 outputs to time align multiple devices.The AD9528 generates two outputs (Output 1 and Output 2) with a maximum frequency of 1.25 GHz, and 12 outputs up to 1 GHz. Each output can be configured to output directly from PLL1, PLL2, or the internal SYSREF generator. Each of the 14 output channels contains a divider with coarse digital phase adjustment and an analog fine phase delay block that allows complete flexibility in timing alignment across all 14 outputs. The AD9528 can also be used as a dual input flexible buffer to distribute 14 device clock and/or SYSREF signals. At power-up, the AD9528 sends the VCXO signal directly to Output 12 and Output 13 to serve as the power-up ready clocks.Note that, throughout this data sheet, the dual function pin names are referenced by the relevant function where applicable.REFA REFB REF_SELSYSREF_REQAD9528 Data Sheet TABLE OF CONTENTSFeatures (1)Applications (1)Functional Block Diagram (1)General Description (1)Revision History (3)Specifications (4)Conditions (4)Supply Current (4)Power Dissipation (5)Input Characteristics—REFA, REFA, REFB, REFB,VCXO_IN, VCXO_IN, SYSREF_IN, and SYSREF_IN (6)PLL1 Characteristics (6)VCXO_VT Output Characteristics (7)PLL2 Characteristics (7)Clock Distribution Output Characteristics (7)Output Timing Alignment Characteristics (8)SYSREF_IN, SYSREF_IN, VCXO_IN, and VCXO_IN Timing Characteristics (8)Clock Output Absolute Phase Noise—Dual Loop Mode (8)Clock Output Absolute Phase Noise—Single Loop Mode (9)Clock Output Absolute Time Jitter (10)Clock Output Additive Time Jitter (Buffer Mode) (12)Logic Input Pins—RESET, REF_SEL, and SYSREF_REQ (12)Status Output Pins—STATUS0 and STATUS1 (12)Serial Control Port—Serial Port Interface (SPI) Mode (13)Serial Control Port—I2C Mode (14)Absolute Maximum Ratings (15)Thermal Resistance (15)ESD Caution (15)Pin Configuration and Function Descriptions (16)Typical Performance Characteristics (19)Input/Output Termination Recommendations (22)Typical Application Circuit (23)Terminology .................................................................................... 24Theory of Operation . (25)Detailed Block Diagram (25)Overview (25)Component Blocks—PLL1 (26)Component Blocks— PLL2 (27)Clock Distribution (29)SYSREF Operation (32)SYSREF Signal Path (32)SYSREF Generator (34)Serial Control Port (35)SPI/I2C Port Selection (35)SPI Serial Port Operation (35)I2C Serial Port Operation (38)Device Initialization and Calibration Flowcharts (41)Power Dissipation and Thermal Considerations (46)Clock Speed and Driver Mode (46)Evaluation of Operating Conditions (46)Thermally Enhanced Package Mounting Guidelines (47)Control Register Map (48)Control Register Map Bit Descriptions (52)Serial Control Port Configuration (Register 0x0000 to Register 0x0001) (52)Clock Part Family ID (Register 0x0003 to Register 0x0006) (53)SPI Version (Register 0x000B) (53)Vendor ID (Register 0x000C to Register 0x000D) (53)IO_UPDATE (Register 0x000F) (53)PLL1 Control (Register 0x0100 to Register 0x010B) (54)PLL2 (Register 0x0200 to Register 0x0209) (56)Clock Distribution (Register 0x300 to Register 0x0329) (59)Power-Down Control (Register 0x0500 to Register 0x0504) (63)Status Control (Register 0x0505 to Register 0x0509) (65)Outline Dimensions (67)Ordering Guide (67)Rev. B | Page 2 of 67Data Sheet AD9528REVISION HISTORY4/15—Rev. A to Rev. BChanges to Serial Control Port Section and Table 24 (35)3/15—Rev. 0 to Rev. AMoved Revision History (3)Changes to Table 8 (7)Changes to Voltage Parameter, Table 15 (12)Changes to Figure 2 (16)Added Figure 13, Renumbered Sequentially (20)Deleted Figure 17 (21)Added Figure 15 (21)Changes to Figure 16 Caption (21)Changes to Figure 27 (25)Changes to SYSREF Generator Section (34)Changes to Serial Control Port Section and ImplementationSpecific Details Section (35)Changes to Table 36 (48)Changes to Table 37 (52)10/14—Revision 0: Initial VersionRev. B | Page 3 of 67AD9528 Data Sheet SPECIFICATIONSThe AD9528 is configured for dual loop mode. The REFA differential input is enabled at 122.88 MHz, f VCXO = 122.88 MHz and single-ended, f VCO = 3686.4 MHz, VCO divider = 3. Doubler and analog delay are off, SYSREF generation is on, unless otherwise noted. Typical is given for VDDx = 3.3 V ± 5%, and T A = 25°C, unless otherwise noted. Minimum and maximum values are given over the full VDDx and T A (−40°C to +85°C) variation, as listed in Table 1.CONDITIONSTable 1.Parameter Min Typ Max Unit Test Conditions/CommentsSUPPLY VOLTAGEVDDx1 3.135 3.3 3.465 V 3.3 V ± 5%TEMPERATUREAmbient Temperature−40 +25 +85 °CRange, T AJunction Temperature, T J+115 °C Refer to the Power Dissipation and Thermal Considerations section tocalculate the junction temperature1 VDDx includes the VDD pins (Pin 1, Pin 10, Pin 16, Pin 20, and Pin 72) and the VDD13 pin through the VDD0 pin, unless otherwise noted. See the Pin Configuration and Function Descriptions for details.SUPPLY CURRENTTable 2.Parameter Min Typ Max Unit Test Conditions/CommentsSUPPLY CURRENT Excludes clock distribution section; clock distribution outputs running as follows:7 HSTL device clocks at 122.88 MHz, 7 LVDS SYSREF clocks (3.5 mA) at 960 kHz Dual Loop Mode PLL1 and PLL2 enabledVDD (Pin 1, Pin 72) 19 21 mAVDD (Pin 10) 29 32 mAVDD (Pin 16) 34 37 mAVDD ( Pin 20) 64 71 mASingle Loop Mode PLL1 off and REFA and REFB inputs offVDD (Pin 1, Pin 72) 7 9 mA 122.88 MHz reference source applied to the VCXO inputs (input to PLL2)VDD (Pin 10) 29 32 mAVDD (Pin 16) 34 37 mAVDD (Pin 20) 64 71 mABuffer Mode PLL1 and PLL2 off, REFA and REFB inputs disabled; 122.88 MHz reference sourceapplied to VCXO differential inputs to drive 7 of 14 outputs, internal SYSREFgenerator off, 960 kHz input source applied to SYSREF differential inputs to drivethe other 7 outputs, dividers in clock distribution path bypassed in clockdistribution channelVDD (Pin 1, Pin 72) 17 19 mAVDD (Pin 10) 23 25 mAVDD (Pin 16) 2 3 mAVDD (Pin 20) 15 19 mAChip Power-DownModeVDD (Pin 1, Pin 10,15 mA Chip power-down bit enabled (Register 0x0500, Bit 0 = 1)Pin 16, Pin 20,and Pin 72)Rev. B | Page 4 of 67Data SheetAD9528ParameterMin Typ Max Unit Test Conditions/CommentsSUPPLY CURRENT FOR EACH CLOCK DISTRIBUTION CHANNELEach clock output channel has a dedicated VDD pin. The current draw for each VDD pin includes the divider, fine delay, and output driver, fine delay is off; see the Pin Configuration and Function Descriptions section for pin assignment LVDS Mode, 3.5 mA21 23 mA Output = 122.88 MHz, channel divider = 10 24 26 mA Output = 409.6 MHz, channel divider = 328 30 mA Output = 737.28 MHz, channel divider = 1, VCO divider = 5, LVDS boost mode of 4.5 mA recommended LVDS Boost Mode, 4.5 mA22 24 mA Output = 122.88 MHz, channel divider =10 25 27 mA Output = 409.6 MHz, channel divider = 329 31 mA Output = 737.28 MHz, channel divider = 1, VCO divider = 5 HSTL Mode, 9 mA25 27 mA Output = 122.88 MHz, channel divider =10 26 28 mA Output = 409.6 MHz, channel divider = 329 31 mA Output = 983.04 MHz, channel divider = 1, VCO divider = 5, VCO = 3932.16 MHz37 41 mA Output = 1228.8 MHz, channel divider = 1, only output channels OUT1 and OUT2 support output frequencies greater than ~1 GHzChip Power-Down Mode2.54mAFor each channel VDD pin, chip power-down bit enabled (Register 0x0500, Bit 0 = 1)POWER DISSIPATIONRev. B | Page 5 of 67AD9528 Data Sheet Parameter Min Typ Max Unit Test Conditions/CommentsHSTL Mode, 9 mA 80 mW Single 9 mA HSTL output at 122.88 MHz, channel divider = 1085 mW Single 9 mA HSTL output at 409.6 MHz, channel divider = 395 mW Single 9 mA HSTL output at 983.04 MHz, VCO divider = 5, channel divider = 1125 mW Single 9 mA HSTL output at 1228.8 MHz, channel divider = 1REFADifferential On 72 mW REFA and REFB running at 122.88 MHz, REF_SEL = REFBSingle-Ended 72 mW REFA and REFB running at 122.88 MHz, REF_SEL = REFBSYSREF GeneratorEnabled5 mW Single 3.5 mA LVDS output at 960 kHzFine Delay On 1 mW Maximum delay settingINPUT CHARACTERISTICS—REFA, REFA, REFB, REFB, VCXO_IN, VCXO_IN, SYSREF_IN, AND SYSREF_INTable 4.Parameter Min Typ Max Unit Test Conditions/CommentsDIFFERENTIAL MODEInput Frequency Range 400 MHzInput Frequency Range(VCXO_IN)1250 MHz For buffer modeInput Slew Rate (VCXO_IN) 500 V/µs Minimum limit imposed for jitter performanceCommon-Mode InternallyGenerated Input Voltage0.6 0.7 0.8 VInput Common-Mode Range 0.4 1.4 V DC-coupled LVDS mode and HSTL mode supportedDifferential Input Voltage, Sensitivity Frequency < 250 MHz 200 mV p-p Capacitive coupling required; can accommodate single-ended inputs via acgrounding of unused inputs; instantaneous voltage on either pin must notexceed 1.8 V dcDifferential Input Voltage, Sensitivity Frequency > 250 MHz 250 mV p-p Capacitive coupling required; can accommodate single-ended inputs via acgrounding of unused inputs; instantaneous voltage on either pin must notexceed 1.8 V dcDifferential Input Resistance 4.8 kΩDifferential Input Capacitance 4 pFDuty Cycle Duty cycle limits are set by pulse width high and pulse width low Pulse Width Low 1 nsPulse Width High 1 nsCMOS MODE, SINGLE-ENDEDINPUTInput Frequency Range 250 MHzInput High Voltage 1.4 VInput Low Voltage 0.65 VInput Capacitance 2 pFDuty Cycle Duty cycle limits are set by pulse width high and pulse width low Pulse Width Low 1.6 nsPulse Width High 1.6 nsPLL1 CHARACTERISTICSTable 5.Parameter Min Typ Max Unit Test Conditions/CommentsPFD FREQUENCY 110 MHzCharge Pump Current LSB Size 0.5 μA 7-bit resolutionReference Frequency Detector Threshold 950 kHz Do not use automatic holdover if the reference frequency isless than the minimum valueRev. B | Page 6 of 67Data Sheet AD9528VCXO_VT OUTPUT CHARACTERISTICSTable 6.Parameter Min Typ Max Unit Test Conditions/Comments OUTPUT VOLTAGEHigh VDD − 0.15 V R LOAD > 20 kΩLow 150 mVPLL2 CHARACTERISTICSTable 7.Parameter Min Typ Max Unit Test Conditions/CommentsVCO (ON CHIP)Frequency Range 3450 4025 MHzGain 48 MHz/VPLL2 FIGURE OF MERIT (FOM) −226 dBc/HzMAXIMUM PFD FREQUENCY 275 MHzCLOCK DISTRIBUTION OUTPUT CHARACTERISTICSTable 8.Parameter Min Typ Max Unit Test Conditions/CommentsHSTL MODEOutput Frequency 1000 MHz All outputs1250 MHz Outputs OUT1 and OUT2 onlyRise Time/Fall Time (20% to 80%) 60 160 ps 100 Ω termination across output pair Duty Cyclef < 500 MHz 48 50 53 %f = 500 MHz to 800 MHz 46 51 54 %f = 800 MHz to 1.25 GHz 44 50 62 %f = 800 MHz to 1.25 GHz 50 57 % If using PLL2Differential Output Voltage Swing 900 1000 1100 mV V OH − V OL for each leg of a differentialpair for default amplitude setting withthe driver not toggling; the peak-to-peak amplitude measured using adifferential probe across the differentialpair with the driver toggling is roughly2× these values (see Figure 5 forvariation over frequency)Common-Mode Output Voltage 0.88 0.9 0.94 VLVDS MODE, 3.5 mA 3.5 mAOutput Frequency 1000 MHz All outputs1250 GHz Outputs OUT1 and OUT2 onlyRise Time/Fall Time (20% to 80%) 50 216 ps 100 Ω termination across output pair Duty Cyclef < 500 MHz 47 50 53 %f = 500 MHz to 800 MHz 46 51 54 %f = 800 MHz to 1.25 GHz 48 54 58 %Balanced, Differential Output Swing (VOD) 345 390 mV Voltage swing between output pins;output driver static (see Figure 6 forvariation over frequency)Unbalanced, ∆VOD 3 mV Absolute difference between voltageswing of normal pin and inverted pin;output driver staticCommon-Mode Output Voltage 1.15 1.35 VCommon-Mode Difference 1.2 mV Voltage difference between output pins;output driver staticShort-Circuit Output Current 15 19 mA Output driver staticAD9528 Data Sheet OUTPUT TIMING ALIGNMENT CHARACTERISTICSTable 9.Parameter Min Typ Max Unit Test Conditions/CommentsOUTPUT TIMING SKEW Delay off on all outputs, maximum deviation between rising edges of outputs; all outputs are on and in HSTL mode, unless otherwise notedPLL1 OutputsPLL1 to PLL1 17 100 ps PLL1 clock to PLL1 clockPLL1 to SYSREF 17 100 ps SYSREF retimed by PLL1 clockPLL1 to SYSREF 361 510 ps SYSREF not retimed by any clockPLL1 to SYSREF 253 1150 ps SYSREF retimed by PLL2 clockPLL1 to PLL2 257 1000 ps PLL1 clock to PLL2 clockPLL2 OutputsPLL2 to PLL2 20 165 ps PLL2 clock to PLL2 clockPLL2 to SYSREF 20 165 ps SYSREF retimed by PLL2 clockPLL2 to SYSREF 620 750 ps SYSREF not retimed by any clockPLL2 to SYSREF 253 1150 ps SYSREF retimed by PLL1 clockPLL2 to PLL1 257 1000 ps PLL2 clock to PLL1 clockOUTPUT DELAYADJUSTEnables digital and analog delay capabilityCoarse AdjustableDelay32 Steps Resolution step is the period of VCO RF divider (M1) output/2Fine AdjustableDelay15 Steps Resolution stepResolution Step 31 psInsertion Delay 425 ps Analog delay enabled and delay setting equal to zeroSYSREF_IN, SYSREF_IN, VCXO_IN, AND VCXO_IN TIMING CHARACTERISTICSTable 10.Parameter Min Typ Max Unit Test Conditions/Comments PROPAGATION LATENCY OF VCXO PATH 1.92 2.3 2.7ns VCXO input to device clock output, not retimed PROPAGATION LATENCY OF SYSREF PATH 1.83 2.2 2.6ns SYSREF input to SYSREF output, not retimed RETIMED WITH DEVICE CLOCKSetup Time of External SYSREF Relative to Device Clock Output −1.13 ns Given a SYSREF input clock rate equal to122.88 MHzHold Time of External SYSREF Relative to Device ClockOutput0.7 nsRETIMED WITH VCXOSetup Time of External SYSREF Relative to VCXO Input −0.21 nsHold Time of External SYSREF Relative to VCXO 0.09 nsCLOCK OUTPUT ABSOLUTE PHASE NOISE—DUAL LOOP MODEApplication examples are based on a typical setups (see Table 2) using an external 122.88 MHz VCXO (Crystek CVHD-950); reference = 122.88 MHz; channel divider = 10 or 1; PLL2 loop bandwidth (LBW) = 450 kHz.Table 11.Parameter Min Typ Max Unit Test Conditions/CommentsHSTL OUTPUTf OUT = 122.88 MHz10 Hz Offset −87 dBc/Hz100 Hz Offset −106 dBc/Hz1 kHz Offset −126 dBc/Hz10 kHz Offset −135 dBc/Hz100 kHz Offset −139 dBc/HzRev. B | Page 8 of 67Data Sheet AD9528 Parameter Min Typ Max Unit Test Conditions/Comments 800 kHz Offset −147 dBc/Hz1 MHz Offset −149 dBc/Hz10 MHz Offset −161 dBc/Hz40 MHz Offset −162 dBc/Hzf OUT = 1228.8 MHz OUT1 and OUT2 only, channel divider = 110 Hz Offset −62 dBc/Hz100 Hz Offset −85 dBc/Hz1 kHz Offset −106 dBc/Hz10 kHz Offset −115 dBc/Hz100 kHz Offset −119 dBc/Hz800 kHz Offset −127 dBc/Hz1 MHz Offset −129 dBc/Hz10 MHz Offset −147 dBc/Hz100 MHz Offset −153 dBc/HzLVDS OUTPUTf OUT = 122.88 MHz10 Hz Offset −86 dBc/Hz100 Hz Offset −106 dBc/Hz1 kHz Offset −126 dBc/Hz10 kHz Offset −135 dBc/Hz100 kHz Offset −139 dBc/Hz800 kHz Offset −147 dBc/Hz1 MHz Offset −148 dBc/Hz10 MHz Offset −157 dBc/Hz40 MHz Offset −158 dBc/Hzf OUT = 1228.8 MHz OUT1 and OUT2 only, channel divider = 110 Hz Offset −66 dBc/Hz100 Hz Offset −86 dBc/Hz1 kHz Offset −106 dBc/Hz10 kHz Offset −115 dBc/Hz100 kHz Offset −119 dBc/Hz800 kHz Offset −127 dBc/Hz1 MHz Offset −129 dBc/Hz10 MHz Offset −147 dBc/Hz100 MHz Offset −152 dBc/HzCLOCK OUTPUT ABSOLUTE PHASE NOISE—SINGLE LOOP MODESingle loop mode is based on the typical setup (see Table 2) using an external 122.88 MHz reference (SMA100A generator); reference = 122.88 MHz; channel divider = 10; PLL2 LBW = 450 kHz.Table 12.Parameter Min Typ Max Unit Test Conditions/CommentsHSTL OUTPUTf OUT = 122.88 MHz10 Hz Offset −104 dBc/Hz100 Hz Offset −113 dBc/Hz1 kHz Offset −123 dBc/Hz10 kHz Offset −135 dBc/Hz100 kHz Offset −140 dBc/Hz800 kHz Offset −147 dBc/Hz1 MHz Offset −149 dBc/Hz10 MHz Offset −161 dBc/Hz40 MHz Offset −162 dBc/HzRev. B | Page 9 of 67AD9528 Data Sheet Parameter Min Typ Max Unit Test Conditions/Commentsf OUT = 1228.8 MHz OUT1 and OUT2 only, channel divider = 110 Hz Offset −85 dBc/Hz100 Hz Offset −95 dBc/Hz1 kHz Offset −103 dBc/Hz10 kHz Offset −114 dBc/Hz100 kHz Offset −120 dBc/Hz800 kHz Offset −126 dBc/Hz1 MHz Offset −128 dBc/Hz10 MHz Offset −147 dBc/Hz100 MHz Offset −153 dBc/HzLVDS OUTPUTf OUT = 122.88 MHz10 Hz Offset −111 dBc/Hz100 Hz Offset −113 dBc/Hz1 kHz Offset −123 dBc/Hz10 kHz Offset −135 dBc/Hz100 kHz Offset −140 dBc/Hz800 kHz Offset −147 dBc/Hz1 MHz Offset −148 dBc/Hz10 MHz Offset −157 dBc/Hz40 MHz Offset −157 dBc/Hzf OUT = 1228.8 MHz OUT1 and OUT2 only, channel divider = 110 Hz Offset −85 dBc/Hz100 Hz Offset −95 dBc/Hz1 kHz Offset −103 dBc/Hz10 kHz Offset −114 dBc/Hz100 kHz Offset −120 dBc/Hz800 kHz Offset −126 dBc/Hz1 MHz Offset −128 dBc/Hz10 MHz Offset −146 dBc/Hz100 MHz Offset −152 dBc/HzCLOCK OUTPUT ABSOLUTE TIME JITTERTable 13.Parameter Min Typ Max Unit Test Conditions/CommentsOUTPUT ABSOLUTE RMS TIME JITTER Application examples are based on typical setups (seeTable 2) using an external 122.88 MHz VCXO (Crystek CVHD-950);reference = 122.88 MHz; channel divider = 10 or 1;PLL2 LBW = 450 kHzDual Loop ModeHSTL Output 117 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 123 fs Integrated BW = 200 kHz to 10 MHz159 fs Integrated BW = 12 kHz to 20 MHz172 fs Integrated BW = 10 kHz to 40 MHz177 fs Integrated BW = 1 kHz to 40 MHz109 fs Integrated BW = 1 MHz to 40 MHz114 fs Integrated BW = 200 kHz to 5 MHzf OUT = 1228.8 MHz, ChannelDivider = 1116 fs Integrated BW = 200 kHz to 10 MHz147 fs Integrated BW = 12 kHz to 20 MHz154 fs Integrated BW = 10 kHz to 100 MHz160 fs Integrated BW = 1 kHz to 100 MHz74 fs Integrated BW = 1 MHz to 100 MHzRev. B | Page 10 of 67Parameter Min Typ Max Unit Test Conditions/Comments LVDS Output 124 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 136 fs Integrated BW = 200 kHz to 10 MHz179 fs Integrated BW = 12 kHz to 20 MHz209 fs Integrated BW = 10 kHz to 40 MHz213 fs Integrated BW = 1 kHz to 40 MHz160 fs Integrated BW = 1 MHz to 40 MHzf OUT = 1228.8 MHz, Channel116 fs Integrated BW = 200 kHz to 5 MHz Divider = 1118 fs Integrated BW = 200 kHz to 10 MHz150 fs Integrated BW = 12 kHz to 20 MHz157 fs Integrated BW = 10 kHz to 100 MHz163 fs Integrated BW = 1 kHz to 100 MHz76 fs Integrated BW = 1 MHz to 100 MHz Single Loop ModeHSTL Output 115 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 122 fs Integrated BW = 200 kHz to 10 MHz156 fs Integrated BW = 12 kHz to 20 MHz171 fs Integrated BW = 10 kHz to 40 MHz179 fs Integrated BW = 1 kHz to 40 MHz110 fs Integrated BW = 1 MHz to 40 MHz116 fs Integrated BW = 200 kHz to 5 MHzf OUT = 1228.8 MHz, ChannelDivider = 1118 fs Integrated BW = 200 kHz to 10 MHz146 fs Integrated BW = 12 kHz to 20 MHz153 fs Integrated BW = 10 kHz to 100 MHz163 fs Integrated BW = 1 kHz to 100 MHz81 fs Integrated BW = 1 MHz to 100 MHzLVDS Output 123 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 135 fs Integrated BW = 200 kHz to 10 MHz177 fs Integrated BW = 12 kHz to 20 MHz207 fs Integrated BW = 10 kHz to 40 MHz214 fs Integrated BW = 1 kHz to 40 MHz160 fs Integrated BW = 1 MHz to 40 MHz117 fs Integrated BW = 200 kHz to 5 MHzf OUT = 1228.8 MHz, ChannelDivider = 1119 fs Integrated BW = 200 kHz to 10 MHz147 fs Integrated BW = 12 kHz to 20 MHz155 fs Integrated BW = 10 kHz to 100 MHz164 fs Integrated BW = 1 kHz to 100 MHz83 fs Integrated BW = 1 MHz to 100 MHzRev. B | Page 11 of 67CLOCK OUTPUT ADDITIVE TIME JITTER (BUFFER MODE)Table 14.Parameter Min Typ Max Unit Test Conditions/CommentsOUTPUT ADDITIVE RMS TIME JITTER Application examples are based on typical performance (seeTable 2) using an external 122.88 MHz source driving VCXOinputs (distribution section only, does not include PLL andVCO)Buffer ModeHSTL Output 66 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 81 fs Integrated BW = 200 kHz to 10 MHz112 fs Integrated BW = 12 kHz to 20 MHz145 fs Integrated BW = 10 kHz to 40 MHz146 fs Integrated BW = 1 kHz to 40 MHz132 fs Integrated BW = 1 MHz to 40 MHz LVDS Output 79 fs Integrated BW = 200 kHz to 5 MHzf OUT = 122.88 MHz 101 fs Integrated BW = 200 kHz to 10 MHz140 fs Integrated BW = 12 kHz to 20 MHz187 fs Integrated BW = 10 kHz to 40 MHz189 fs Integrated BW = 1 kHz to 40 MHz176 fs Integrated BW = 1 MHz to 40 MHzLOGIC INPUT PINS—RESET, REF_SEL, AND SYSREF_REQSTATUS OUTPUT PINS—STATUS0 AND STATUS1Table 16.Parameter Min Typ Max Unit Test Conditions/CommentsOUTPUT VOLTAGEHigh 3 VLow 0.02 VRev. B | Page 12 of 67SERIAL CONTROL PORT—SERIAL PORT INTERFACE (SPI) MODERev. B | Page 13 of 67SERIAL CONTROL PORT—I2C MODETable 18.Parameter Symbol Min Typ Max Unit Test Conditions/CommentsSDA, SCL VOLTAGE When inputting dataInput Logic 1 0.7 × VDD VInput Logic 0 0.3 × VDD VInput Current −10 +10 µA Input voltage between 0.1 × VDD and0.9 × VDDHysteresis of Schmitt Trigger Inputs 0.015 ×VDDVSDA When outputting dataOutput Logic 0 Voltage at 3 mA SinkCurrent0.2 VOutput Fall Time from VIH MIN toVIL MAX20 + 0.1 C B1250 ns Bus capacitance from 10 pF to 400 pFTIMING All I2C timing values are referred toVIH MIN (0.3 × VDD) and VIL MAX levels (0.7 ×VDD)Clock Rate (SCL, f I2C) 400 kHzBus Free Time Between a Stop andStart Conditiont IDLE 1.3 µsSetup Time for a Repeated StartConditiont SET; STR0.6 µsHold Time (Repeated) Start Condition t HLD; STR0.6 µs After this period, the first clock pulse isgeneratedSetup Time for a Stop Condition t SET; STP0.6 µs Low Period of the SCL Clock t LOW 1.3 µs High Period of the SCL Clock t HIGH0.6 µs SCL, SDA Rise Time t RISE20 + 0.1 C B1300 ns SCL, SDA Fall Time t FALL20 + 0.1 C B1300 ns Data Setup Time t SET; DAT100 ns Data Hold Time t HLD; DAT0 ns Capacitive Load for Each Bus Line C B1400 pF 1 C B is the capacitance of one bus line in picofarads (pF).Rev. B | Page 14 of 67ABSOLUTE MAXIMUM RATINGSStresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. THERMAL RESISTANCEθJA is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.Table 20. Thermal ResistancePackage TypeAirflowVelocity(m/sec) θJA1, 2 θJC1, 3 θJB1, 4 JT1, 2Unit72-Lead LFCSP,10 mm ×10 mm0 21.3 1.7 12.6 0.1 °C/W1.0 20.1 0.2°C/W2.5 18.1 0.3°C/W1 Per JEDEC 51-7, plus JEDEC 51-5 2S2P test board.2 Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).3 Per MIL-Std 883, Method 1012.1.4 Per JEDEC JESD51-8 (still air).Additional power dissipation information can be found in thePower Dissipation and Thermal Considerations section.ESD CAUTIONRev. B | Page 15 of 67PIN CONFIGURATION AND FUNCTION DESCRIPTIONSFigure 2. Pin Configuration12345678910111213141516VDD REFA REFA REF_SELREFB REFB LF1VCXO_VTNIC VDD VCXO_IN VCXO_INNIC LF2_CAP LDO_VCOVDD 17NIC 18NIC19202122232425262728293031323334R E S E T V D D C S S C L K /S C L S D I O /S D A S D O O U T 13O U T 13V D D 13O U T 12O U T 12V D D 12O U T 11O U T 11V D D 11O U T 1035O U T 1036V D D 10545352515049484746454443424140393837VDD4OUT4OUT4VDD5OUT5OUT5VDD6OUT6OUT6VDD7OUT7OUT7VDD8OUT8OUT8VDD9OUT9OUT9727170696867666564636261605958575655V D D S Y S R E F _I N S Y S R E F _I N V D D 0O U T 0O U T 0V D D 1O U T 1O U T 1V D D 2O U T 2O U T 2V D D 3O U T 3O U T 3S Y S R E F _R E Q S T A T U S 1/S P 1S T A T U S 0/S P 0NOTES1. NIC = NO INTERNAL CONNECTION. THIS PIN CAN BE LEFT FLOATING.2. THE EXPOSED PAD IS THE GROUND CONNECTION ON THE CHIP.IT MUST BE SOLDERED TO THE ANALOG GROUND OF THE PCB TO ENSURE PROPER FUNCTIONALITY AND HEAT DISSIPATION, NOISE, AND MECHANICAL STRENGTH BENEFITS.12380-002Rev. B | Page 16 of 67。

linux的parallel参数

linux的parallel参数

parallel是一个用于执行并行任务的工具,它可以在Linux系统中同时运行多个命令或任务。

以下是parallel命令常用的一些参数:

-j N:指定并行执行的任务数,N为一个整数。

--jobs N:也是指定并行执行的任务数,N为一个整数。

-k:保持任务的顺序,在同时运行多个任务时保持任务的输出顺序。

--halt-on-error:如果出现错误,则停止执行后续的任务。

--keep-order:保持输入的顺序,按照输入的顺序输出结果。

--tagstring STRING:用于指定输出结果的标签字符串。

--dry-run:仅显示要执行的命令,而不实际运行。

--eta:显示预估的剩余时间。

--verbose:显示详细的执行信息。

这只是一些常用的参数,parallel还有其他更多的参数可用。

可以在终端上输入“man parallel”命令来查看完整的参数列表和使用说明。

EXPDPIMPDP中的并行度PARALLEL参数

EXPDPIMPDP中的并⾏度PARALLEL参数如果设置 EXPDP parallel=4 必须要设置4个EXPDP⽂件,不然PARALLEL是有问题的,同时EXPDP会使⽤⼀个WORKER进程导出METADATA,其他WORKER进程会同时出数据,如果EXPDP作业很于250M 只会启动⼀个WORKER进程如果是500M会启动2个,1000M 及会启动4个WOKER进程,⼀般来说加上%U来设置多个⽂件。

⽽IMPDP有所不同,会先启动⼀个WOKER进程METADATA导⼊,然后启动多个WORKER进程导⼊,所以再前期只会看到WOKER在导⼊METADATA,⽽且IMPDP如果PARALLE=4也需要>=4个DMP⽂件,也可以使⽤%U来进⾏导⼊。

nohup expdp system/**** PARALLEL=2 JOB_NAME=full_bak_job full=y dumpfile=exptest:back_%U.dmp logfile=exptest:back.log & impdp system/*** PARALLEL=2 EXCLUDE=STATISTICS JOB_NAME=full_imp cluster=no full=y dumpfile=test:back_%U.dmplogfile=test:back_imp.log;⽽在11GR2后EXPDP 和 IMDP的WORKER进程会在多个INSTANCE启动,所以DIRECTORY必须在共享磁盘上,如果没有设置共享磁盘还是指定cluster=no 来防⽌报错。

当观察EXPDP/IMPDP woker的时候如下:Import> statusJob: FULL_IMPOperation: IMPORTMode: FULLState: EXECUTINGBytes Processed: 150,300,713,536Percent Done: 80Current Parallelism: 6Job Error Count: 0Dump File: /expdp/back_%u.dmpDump File: /expdp/back_01.dmpDump File: /expdp/back_02.dmpDump File: /expdp/back_03.dmpDump File: /expdp/back_04.dmpDump File: /expdp/back_05.dmpDump File: /expdp/back_06.dmpDump File: /expdp/back_07.dmpDump File: /expdp/back_08.dmpWorker 1 Status:Process Name: DW00State: EXECUTINGObject Schema: ACRUNObject Name: T_PLY_UNDRMSGObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 3Completed Rows: 3,856,891Completed Bytes: 1,134,168,200Percent Done: 83Worker Parallelism: 1Worker 2 Status:Process Name: DW01State: EXECUTINGObject Schema: ACRUNObject Name: T_FIN_PAYDUEObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 5Completed Rows: 2,646,941Completed Bytes: 1,012,233,224Percent Done: 93Worker Parallelism: 1Worker 3 Status:Process Name: DW02State: EXECUTINGObject Schema: ACRUNObject Name: MLOG$_T_FIN_CLMDUEObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 6Completed Bytes: 382,792,584Worker Parallelism: 1Worker 4 Status:Process Name: DW03State: EXECUTINGObject Schema: ACRUNObject Name: T_PAY_CONFIRM_INFOObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 5Completed Rows: 2,443,790Completed Bytes: 943,310,104Percent Done: 83Worker Parallelism: 1Worker 5 Status:Process Name: DW04State: EXECUTINGObject Schema: ACRUNObject Name: T_PLY_TGTObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 6Completed Rows: 2,285,353Completed Bytes: 822,501,496Percent Done: 64Worker Parallelism: 1Worker 6 Status:Process Name: DW05State: EXECUTINGObject Schema: ACRUNObject Name: T_FIN_PREINDRCT_CLMFEEObject Type: DATABASE_EXPORT/SCHEMA/TABLE/TABLE_DATACompleted Objects: 5Completed Rows: 6,042,384Completed Bytes: 989,435,088Percent Done: 79Worker Parallelism: 1英⽂如下:For Data Pump Export, the value that is specified for the parallel parameter should be less than or equal to the number of files in the dump file set. Each worker or Parallel Execution Process requires exclusive access to the dump file, so having fewer dump files than the degree of parallelism will mean that some workers or PX processes will be unable to write the information they are exporting. If this occurs, the worker processes go into an idle state and will not be doing any work until more files are added to the job. See the explanation of the DUMPFILE parameter in the Database Utilities guide for details on how to specify multiple dump files for a Data Pump export job.For Data Pump Import, the workers and PX processes can all read from the same files. However, if there are not enough dump files, the performance may not be optimal because multiple threads of execution will be trying to access the same dump file. The performance impact of multiple processes sharing the dump files depends on the I/O subsystem containing the dump files. For this reason, Data Pump Import should not have a value for the PARALLEL parameter that is significantly larger than the number of files in the dump file set.In a typical export that includes both data and metadata, the first worker process will unload the metadata: tablespaces, schemas, grants, roles, tables, indexes, and so on. This single worker unloads the metadata, and all the rest unload the data, all at the same time. If the metadata worker finishes and there are still data objects to unload, it will start unloading the data too. The examples in this document assume that there is always one worker busy unloading metadata while the rest of the workers are busy unloading table data objects.If the external tables method is chosen, Data Pump will determine the maximum number of PX processes that can work on a table data object. It does this by dividing the estimated size of the table data object by 250 MB and rounding the result down. If the result is zero or one, then PX processes are not used to unload the tableThe PARALLEL parameter works a bit differently in Import than Export. Because there are various dependencies that exist when creating objects during import, everything must be done in order. For Import, no data loading can occur until the tables are created because data cannot be loaded into tables that do not yet exist。

parallel analysis jobs

parallel analysis jobs“parallel analysis jobs”,即并行分析工作,是指同时进行多项分析工作的一种方法。

在这篇文章中,我们将逐步回答以下问题,以帮助读者深入了解并行分析工作的概念、优势和应用。

第一步:介绍并行分析工作并行分析工作是指同时进行多项分析工作的方法。

通过利用并行计算技术,可以在短时间内处理大规模数据,提高工作效率。

不同于传统的串行分析工作,只能一个一个地处理数据,并行分析工作可以同时进行多项任务,大大缩短了分析时间。

第二步:解释并行分析工作的优势并行分析工作有以下几个优势:1. 处理大规模数据:在传统方法中,处理大规模数据需要较长时间,而并行分析工作可以通过利用多个处理单元,同时处理不同的数据段,从而快速完成分析任务。

2. 提高工作效率:由于并行分析工作可以同时进行多项任务,所以能够更快地完成工作,从而提高工作效率。

3. 实现实时分析:并行分析工作可以快速处理数据,并实时生成分析结果。

对于需要实时响应的应用场景,如金融交易或实时监控系统,这一优势尤为重要。

第三步:探讨并行分析工作的应用并行分析工作可应用于各个领域,以下是一些具体应用案例:1. 大数据分析:在大数据时代,处理海量数据是一项挑战。

并行分析工作可以同时处理多个数据集,从而更高效地进行大数据分析。

2. 基因组学研究:基因组学研究需要处理大量的遗传数据,并进行比对、注释等分析。

并行分析工作可以加速这一过程,快速提取关键信息。

3. 金融风险分析:金融领域需要进行大规模数据的风险评估和建模。

并行分析工作可以快速处理大量数据,从而更及时地进行风险分析。

4. 视频处理:视频处理需要对大量连续帧进行分析,如目标检测、运动跟踪等。

并行分析工作可以同时处理多个帧,提高视频处理的效率。

第四步:讨论并行分析工作的挑战与解决方案并行分析工作面临的挑战主要包括数据通信、负载均衡和并行算法设计等方面。

以下是一些常见的解决方案:1. 数据通信优化:通过减少数据通信的次数和数据量,可以提高并行分析工作的效率。

oracle 多段with as用法 -回复

oracle 多段with as用法-回复什么是Oracle多段WITH AS语句?Oracle多段WITH AS语句是一种被称为“公共表表达式(CTE)”的SQL 语法,它允许我们定义一个或多个临时命名结果集,以供后续查询使用。

这样,我们可以在一个SQL查询中多次引用这个结果集,从而简化复杂查询的编写过程,提高查询的可读性和可维护性。

为什么需要使用Oracle多段WITH AS语句?在Oracle数据库中,为了获取所需数据,我们常常需要进行多个嵌套的子查询。

这样的查询结构不仅使得SQL语句繁琐复杂,也降低了查询的效率。

使用Oracle多段WITH AS语句,我们可以将这些子查询转换为临时命名结果集,使得查询语句更加清晰简洁,同时也提高了查询的性能。

使用Oracle多段WITH AS语句的步骤是怎么样的?Step 1: 定义WITH AS子句及其结果集首先,在你的SQL查询语句之前,使用WITH AS子句来定义一个或多个临时命名结果集。

每个结果集由一个唯一的名称和一个SQL查询语句组成。

可以在结果集中使用列别名来为列命名。

例如,我们想要计算订单表中每个用户的总订单金额,可以使用以下WITH AS语句来定义结果集:WITH order_totals AS (SELECT customer_id, SUM(order_amount) AS total_amount FROM ordersGROUP BY customer_id)Step 2: 引用WITH AS结果集进行查询一旦我们定义了临时命名结果集,就可以在后续的查询中引用它们。

可以像引用表一样引用结果集,并在查询中使用它们来筛选、排序或汇总数据。

例如,我们想要获取订单总金额大于1000的所有用户的详细信息,可以使用以下查询语句:SELECT *FROM customersWHERE customer_id IN (SELECT customer_id FROM order_totals WHERE total_amount > 1000)Step 3: 完成查询,并使用WITH AS语句的结果集最后,在你的查询语句结束后,你可以继续使用WITH AS语句定义的结果集。

美国消防泵认证FM 1312-1999 Centrifugal Fire Pumps

LTE系统消息翻译

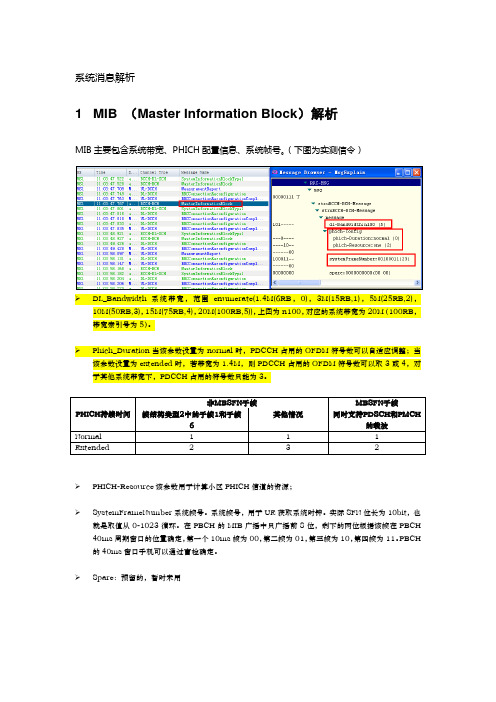

系统消息解析1 MIB (Master Information Block)解析MIB主要包含系统带宽、PHICH配置信息、系统帧号。

(下图为实测信令)➢DL_Bandwidth系统带宽,范围enumerate(1.4M(6RB,0),3M(15RB,1),5M(25RB,2),10M(50RB,3),15M(75RB,4),20M(100RB,5)),上图为n100,对应的系统带宽为20M(100RB,带宽索引号为5)。

➢Phich_Duration当该参数设置为normal时,PDCCH占用的OFDM符号数可以自适应调整;当该参数设置为extended时,若带宽为1.4M,则PDCCH占用的OFDM符号数可以取3或4,对于其他系统带宽下,PDCCH占用的符号数只能为3。

➢PHICH-Resource该参数用于计算小区PHICH信道的资源;➢SystemFrameNumber系统帧号。

系统帧号,用于UE获取系统时钟。

实际SFN位长为10bit,也就是取值从0-1023循环。

在PBCH的MIB广播中只广播前8位,剩下的两位根据该帧在PBCH 40ms周期窗口的位置确定,第一个10ms帧为00,第二帧为01,第三帧为10,第四帧为11。

PBCH 的40ms窗口手机可以通过盲检确定。

➢Spare:预留的,暂时未用2 SIB1 (System Information Block Type1)解析SIB1上主要传输评估UE能否接入小区的相关信息及其他系统消息的调度信息。

主要包括4部分:➢小区接入相关信息(cell Access Related Info)➢小区选择信息(cell Selection Info)➢调度信息(scheduling Info List)➢TDD配置信息(tdd-Config)SIB1消息解析(UE侧):RRC-MSG..msg....struBCCH-DL-SCH-Message......struBCCH-DL-SCH-Message........message..........c1............systemInformationBlockType1..............cellAccessRelatedInfo//小区接入相关信息................plmn-IdentityList//PLMN标识列表..................PLMN-IdentityInfo....................plmn-Identity ......................mcc//460 ........................MCC-MNC-Digit:0x4 (4) ........................MCC-MNC-Digit:0x6 (6) ........................MCC-MNC-Digit:0x0 (0) ......................mnc//00 ........................MCC-MNC-Digit:0x0 (0) ........................MCC-MNC-Digit:0x0 (0) ....................cellReservedForOperatorUse:notReserved (1) ................trackingAreaCode:11100(890C)//TAC跟踪区(890C)为16进制数,转换成十进制为35084,查TAC在该消息中可以查到,此条信元重要。

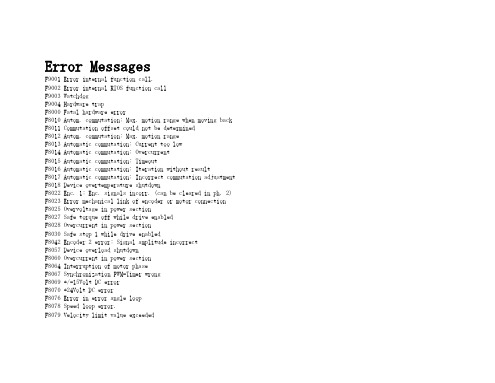

Indradrive 系列 故障代码

Error MessagesF9001 Error internal function call.F9002 Error internal RTOS function callF9003 WatchdogF9004 Hardware trapF8000 Fatal hardware errorF8010 Autom. commutation: Max. motion range when moving back F8011 Commutation offset could not be determinedF8012 Autom. commutation: Max. motion rangeF8013 Automatic commutation: Current too lowF8014 Automatic commutation: OvercurrentF8015 Automatic commutation: TimeoutF8016 Automatic commutation: Iteration without resultF8017 Automatic commutation: Incorrect commutation adjustment F8018 Device overtemperature shutdownF8022 Enc. 1: Enc. signals incorr. (can be cleared in ph. 2) F8023 Error mechanical link of encoder or motor connectionF8025 Overvoltage in power sectionF8027 Safe torque off while drive enabledF8028 Overcurrent in power sectionF8030 Safe stop 1 while drive enabledF8042 Encoder 2 error: Signal amplitude incorrectF8057 Device overload shutdownF8060 Overcurrent in power sectionF8064 Interruption of motor phaseF8067 Synchronization PWM-Timer wrongF8069 +/-15Volt DC errorF8070 +24Volt DC errorF8076 Error in error angle loopF8078 Speed loop error.F8079 Velocity limit value exceededF8091 Power section defectiveF8100 Error when initializing the parameter handlingF8102 Error when initializing power sectionF8118 Invalid power section/firmware combinationF8120 Invalid control section/firmware combinationF8122 Control section defectiveF8129 Incorrect optional module firmwareF8130 Firmware of option 2 of safety technology defectiveF8133 Error when checking interrupting circuitsF8134 SBS: Fatal errorF8135 SMD: Velocity exceededF8140 Fatal CCD error.F8201 Safety command for basic initialization incorrectF8203 Safety technology configuration parameter invalidF8813 Connection error mains chokeF8830 Power section errorF8838 Overcurrent external braking resistorF7010 Safely-limited increment exceededF7011 Safely-monitored position, exceeded in pos. DirectionF7012 Safely-monitored position, exceeded in neg. DirectionF7013 Safely-limited speed exceededF7020 Safe maximum speed exceededF7021 Safely-limited position exceededF7030 Position window Safe stop 2 exceededF7031 Incorrect direction of motionF7040 Validation error parameterized - effective thresholdF7041 Actual position value validation errorF7042 Validation error of safe operation modeF7043 Error of output stage interlockF7050 Time for stopping process exceeded8.3.15 F7051 Safely-monitored deceleration exceeded (159)8.4 Travel Range Errors (F6xxx) (161)8.4.1 Behavior in the Case of Travel Range Errors (161)8.4.2 F6010 PLC Runtime Error (162)8.4.3 F6024 Maximum braking time exceeded (163)8.4.4 F6028 Position limit value exceeded (overflow) (164)8.4.5 F6029 Positive position limit exceeded (164)8.4.6 F6030 Negative position limit exceeded (165)8.4.7 F6034 Emergency-Stop (166)8.4.8 F6042 Both travel range limit switches activated (167)8.4.9 F6043 Positive travel range limit switch activated (167)8.4.10 F6044 Negative travel range limit switch activated (168)8.4.11 F6140 CCD slave error (emergency halt) (169)8.5 Interface Errors (F4xxx) (169)8.5.1 Behavior in the Case of Interface Errors (169)8.5.2 F4001 Sync telegram failure (170)8.5.3 F4002 RTD telegram failure (171)8.5.4 F4003 Invalid communication phase shutdown (172)8.5.5 F4004 Error during phase progression (172)8.5.6 F4005 Error during phase regression (173)8.5.7 F4006 Phase switching without ready signal (173)8.5.8 F4009 Bus failure (173)8.5.9 F4012 Incorrect I/O length (175)8.5.10 F4016 PLC double real-time channel failure (176)8.5.11 F4017 S-III: Incorrect sequence during phase switch (176)8.5.12 F4034 Emergency-Stop (177)8.5.13 F4140 CCD communication error (178)8.6 Non-Fatal Safety Technology Errors (F3xxx) (178)8.6.1 Behavior in the Case of Non-Fatal Safety Technology Errors (178)8.6.2 F3111 Refer. missing when selecting safety related end pos (179)8.6.3 F3112 Safe reference missing (179)8.6.4 F3115 Brake check time interval exceeded (181)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand ControlsI Bosch Rexroth AG VII/XXIITable of ContentsPage8.6.5 F3116 Nominal load torque of holding system exceeded (182)8.6.6 F3117 Actual position values validation error (182)8.6.7 F3122 SBS: System error (183)8.6.8 F3123 SBS: Brake check missing (184)8.6.9 F3130 Error when checking input signals (185)8.6.10 F3131 Error when checking acknowledgment signal (185)8.6.11 F3132 Error when checking diagnostic output signal (186)8.6.12 F3133 Error when checking interrupting circuits (187)8.6.13 F3134 Dynamization time interval incorrect (188)8.6.14 F3135 Dynamization pulse width incorrect (189)8.6.15 F3140 Safety parameters validation error (192)8.6.16 F3141 Selection validation error (192)8.6.17 F3142 Activation time of enabling control exceeded (193)8.6.18 F3143 Safety command for clearing errors incorrect (194)8.6.19 F3144 Incorrect safety configuration (195)8.6.20 F3145 Error when unlocking the safety door (196)8.6.21 F3146 System error channel 2 (197)8.6.22 F3147 System error channel 1 (198)8.6.23 F3150 Safety command for system start incorrect (199)8.6.24 F3151 Safety command for system halt incorrect (200)8.6.25 F3152 Incorrect backup of safety technology data (201)8.6.26 F3160 Communication error of safe communication (202)8.7 Non-Fatal Errors (F2xxx) (202)8.7.1 Behavior in the Case of Non-Fatal Errors (202)8.7.2 F2002 Encoder assignment not allowed for synchronization (203)8.7.3 F2003 Motion step skipped (203)8.7.4 F2004 Error in MotionProfile (204)8.7.5 F2005 Cam table invalid (205)8.7.6 F2006 MMC was removed (206)8.7.7 F2007 Switching to non-initialized operation mode (206)8.7.8 F2008 RL The motor type has changed (207)8.7.9 F2009 PL Load parameter default values (208)8.7.10 F2010 Error when initializing digital I/O (-> S-0-0423) (209)8.7.11 F2011 PLC - Error no. 1 (210)8.7.12 F2012 PLC - Error no. 2 (210)8.7.13 F2013 PLC - Error no. 3 (211)8.7.14 F2014 PLC - Error no. 4 (211)8.7.15 F2018 Device overtemperature shutdown (211)8.7.16 F2019 Motor overtemperature shutdown (212)8.7.17 F2021 Motor temperature monitor defective (213)8.7.18 F2022 Device temperature monitor defective (214)8.7.19 F2025 Drive not ready for control (214)8.7.20 F2026 Undervoltage in power section (215)8.7.21 F2027 Excessive oscillation in DC bus (216)8.7.22 F2028 Excessive deviation (216)8.7.23 F2031 Encoder 1 error: Signal amplitude incorrect (217)VIII/XXII Bosch Rexroth AG | Electric Drivesand ControlsRexroth IndraDrive | Troubleshooting GuideTable of ContentsPage8.7.24 F2032 Validation error during commutation fine adjustment (217)8.7.25 F2033 External power supply X10 error (218)8.7.26 F2036 Excessive position feedback difference (219)8.7.27 F2037 Excessive position command difference (220)8.7.28 F2039 Maximum acceleration exceeded (220)8.7.29 F2040 Device overtemperature 2 shutdown (221)8.7.30 F2042 Encoder 2: Encoder signals incorrect (222)8.7.31 F2043 Measuring encoder: Encoder signals incorrect (222)8.7.32 F2044 External power supply X15 error (223)8.7.33 F2048 Low battery voltage (224)8.7.34 F2050 Overflow of target position preset memory (225)8.7.35 F2051 No sequential block in target position preset memory (225)8.7.36 F2053 Incr. encoder emulator: Pulse frequency too high (226)8.7.37 F2054 Incr. encoder emulator: Hardware error (226)8.7.38 F2055 External power supply dig. I/O error (227)8.7.39 F2057 Target position out of travel range (227)8.7.40 F2058 Internal overflow by positioning input (228)8.7.41 F2059 Incorrect command value direction when positioning (229)8.7.42 F2063 Internal overflow master axis generator (230)8.7.43 F2064 Incorrect cmd value direction master axis generator (230)8.7.44 F2067 Synchronization to master communication incorrect (231)8.7.45 F2068 Brake error (231)8.7.46 F2069 Error when releasing the motor holding brake (232)8.7.47 F2074 Actual pos. value 1 outside absolute encoder window (232)8.7.48 F2075 Actual pos. value 2 outside absolute encoder window (233)8.7.49 F2076 Actual pos. value 3 outside absolute encoder window (234)8.7.50 F2077 Current measurement trim wrong (235)8.7.51 F2086 Error supply module (236)8.7.52 F2087 Module group communication error (236)8.7.53 F2100 Incorrect access to command value memory (237)8.7.54 F2101 It was impossible to address MMC (237)8.7.55 F2102 It was impossible to address I2C memory (238)8.7.56 F2103 It was impossible to address EnDat memory (238)8.7.57 F2104 Commutation offset invalid (239)8.7.58 F2105 It was impossible to address Hiperface memory (239)8.7.59 F2110 Error in non-cyclical data communic. of power section (240)8.7.60 F2120 MMC: Defective or missing, replace (240)8.7.61 F2121 MMC: Incorrect data or file, create correctly (241)8.7.62 F2122 MMC: Incorrect IBF file, correct it (241)8.7.63 F2123 Retain data backup impossible (242)8.7.64 F2124 MMC: Saving too slowly, replace (243)8.7.65 F2130 Error comfort control panel (243)8.7.66 F2140 CCD slave error (243)8.7.67 F2150 MLD motion function block error (244)8.7.68 F2174 Loss of motor encoder reference (244)8.7.69 F2175 Loss of optional encoder reference (245)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand Controls| Bosch Rexroth AG IX/XXIITable of ContentsPage8.7.70 F2176 Loss of measuring encoder reference (246)8.7.71 F2177 Modulo limitation error of motor encoder (246)8.7.72 F2178 Modulo limitation error of optional encoder (247)8.7.73 F2179 Modulo limitation error of measuring encoder (247)8.7.74 F2190 Incorrect Ethernet configuration (248)8.7.75 F2260 Command current limit shutoff (249)8.7.76 F2270 Analog input 1 or 2, wire break (249)8.7.77 F2802 PLL is not synchronized (250)8.7.78 F2814 Undervoltage in mains (250)8.7.79 F2815 Overvoltage in mains (251)8.7.80 F2816 Softstart fault power supply unit (251)8.7.81 F2817 Overvoltage in power section (251)8.7.82 F2818 Phase failure (252)8.7.83 F2819 Mains failure (253)8.7.84 F2820 Braking resistor overload (253)8.7.85 F2821 Error in control of braking resistor (254)8.7.86 F2825 Switch-on threshold braking resistor too low (255)8.7.87 F2833 Ground fault in motor line (255)8.7.88 F2834 Contactor control error (256)8.7.89 F2835 Mains contactor wiring error (256)8.7.90 F2836 DC bus balancing monitor error (257)8.7.91 F2837 Contactor monitoring error (257)8.7.92 F2840 Error supply shutdown (257)8.7.93 F2860 Overcurrent in mains-side power section (258)8.7.94 F2890 Invalid device code (259)8.7.95 F2891 Incorrect interrupt timing (259)8.7.96 F2892 Hardware variant not supported (259)8.8 SERCOS Error Codes / Error Messages of Serial Communication (259)9 Warnings (Exxxx) (263)9.1 Fatal Warnings (E8xxx) (263)9.1.1 Behavior in the Case of Fatal Warnings (263)9.1.2 E8025 Overvoltage in power section (263)9.1.3 E8026 Undervoltage in power section (264)9.1.4 E8027 Safe torque off while drive enabled (265)9.1.5 E8028 Overcurrent in power section (265)9.1.6 E8029 Positive position limit exceeded (266)9.1.7 E8030 Negative position limit exceeded (267)9.1.8 E8034 Emergency-Stop (268)9.1.9 E8040 Torque/force actual value limit active (268)9.1.10 E8041 Current limit active (269)9.1.11 E8042 Both travel range limit switches activated (269)9.1.12 E8043 Positive travel range limit switch activated (270)9.1.13 E8044 Negative travel range limit switch activated (271)9.1.14 E8055 Motor overload, current limit active (271)9.1.15 E8057 Device overload, current limit active (272)X/XXII Bosch Rexroth AG | Electric Drivesand ControlsRexroth IndraDrive | Troubleshooting GuideTable of ContentsPage9.1.16 E8058 Drive system not ready for operation (273)9.1.17 E8260 Torque/force command value limit active (273)9.1.18 E8802 PLL is not synchronized (274)9.1.19 E8814 Undervoltage in mains (275)9.1.20 E8815 Overvoltage in mains (275)9.1.21 E8818 Phase failure (276)9.1.22 E8819 Mains failure (276)9.2 Warnings of Category E4xxx (277)9.2.1 E4001 Double MST failure shutdown (277)9.2.2 E4002 Double MDT failure shutdown (278)9.2.3 E4005 No command value input via master communication (279)9.2.4 E4007 SERCOS III: Consumer connection failed (280)9.2.5 E4008 Invalid addressing command value data container A (280)9.2.6 E4009 Invalid addressing actual value data container A (281)9.2.7 E4010 Slave not scanned or address 0 (281)9.2.8 E4012 Maximum number of CCD slaves exceeded (282)9.2.9 E4013 Incorrect CCD addressing (282)9.2.10 E4014 Incorrect phase switch of CCD slaves (283)9.3 Possible Warnings When Operating Safety Technology (E3xxx) (283)9.3.1 Behavior in Case a Safety Technology Warning Occurs (283)9.3.2 E3100 Error when checking input signals (284)9.3.3 E3101 Error when checking acknowledgment signal (284)9.3.4 E3102 Actual position values validation error (285)9.3.5 E3103 Dynamization failed (285)9.3.6 E3104 Safety parameters validation error (286)9.3.7 E3105 Validation error of safe operation mode (286)9.3.8 E3106 System error safety technology (287)9.3.9 E3107 Safe reference missing (287)9.3.10 E3108 Safely-monitored deceleration exceeded (288)9.3.11 E3110 Time interval of forced dynamization exceeded (289)9.3.12 E3115 Prewarning, end of brake check time interval (289)9.3.13 E3116 Nominal load torque of holding system reached (290)9.4 Non-Fatal Warnings (E2xxx) (290)9.4.1 Behavior in Case a Non-Fatal Warning Occurs (290)9.4.2 E2010 Position control with encoder 2 not possible (291)9.4.3 E2011 PLC - Warning no. 1 (291)9.4.4 E2012 PLC - Warning no. 2 (291)9.4.5 E2013 PLC - Warning no. 3 (292)9.4.6 E2014 PLC - Warning no. 4 (292)9.4.7 E2021 Motor temperature outside of measuring range (292)9.4.8 E2026 Undervoltage in power section (293)9.4.9 E2040 Device overtemperature 2 prewarning (294)9.4.10 E2047 Interpolation velocity = 0 (294)9.4.11 E2048 Interpolation acceleration = 0 (295)9.4.12 E2049 Positioning velocity >= limit value (296)9.4.13 E2050 Device overtemp. Prewarning (297)Troubleshooting Guide | Rexroth IndraDrive Electric Drivesand Controls| Bosch Rexroth AG XI/XXIITable of ContentsPage9.4.14 E2051 Motor overtemp. prewarning (298)9.4.15 E2053 Target position out of travel range (298)9.4.16 E2054 Not homed (300)9.4.17 E2055 Feedrate override S-0-0108 = 0 (300)9.4.18 E2056 Torque limit = 0 (301)9.4.19 E2058 Selected positioning block has not been programmed (302)9.4.20 E2059 Velocity command value limit active (302)9.4.21 E2061 Device overload prewarning (303)9.4.22 E2063 Velocity command value > limit value (304)9.4.23 E2064 Target position out of num. range (304)9.4.24 E2069 Holding brake torque too low (305)9.4.25 E2070 Acceleration limit active (306)9.4.26 E2074 Encoder 1: Encoder signals disturbed (306)9.4.27 E2075 Encoder 2: Encoder signals disturbed (307)9.4.28 E2076 Measuring encoder: Encoder signals disturbed (308)9.4.29 E2077 Absolute encoder monitoring, motor encoder (encoder alarm) (308)9.4.30 E2078 Absolute encoder monitoring, opt. encoder (encoder alarm) (309)9.4.31 E2079 Absolute enc. monitoring, measuring encoder (encoder alarm) (309)9.4.32 E2086 Prewarning supply module overload (310)9.4.33 E2092 Internal synchronization defective (310)9.4.34 E2100 Positioning velocity of master axis generator too high (311)9.4.35 E2101 Acceleration of master axis generator is zero (312)9.4.36 E2140 CCD error at node (312)9.4.37 E2270 Analog input 1 or 2, wire break (312)9.4.38 E2802 HW control of braking resistor (313)9.4.39 E2810 Drive system not ready for operation (314)9.4.40 E2814 Undervoltage in mains (314)9.4.41 E2816 Undervoltage in power section (314)9.4.42 E2818 Phase failure (315)9.4.43 E2819 Mains failure (315)9.4.44 E2820 Braking resistor overload prewarning (316)9.4.45 E2829 Not ready for power on (316)。

replica_parallel_workers 参数

replica_parallel_workers 参数

replica_parallel_workers 参数是用于设置并行工作进程数量的参数。

它通常用于分布式计算或并行处理环境中,以加速数据读取和处理。

当设置 replica_parallel_workers 参数时,它指定了用于并行读取副本数据的进程数量。

这意味着在读取数据时,可以同时使用多个工作进程来并行读取数据,从而提高数据读取的效率。

这个参数的设置取决于你的计算环境、数据集大小和网络带宽等因素。

通常,你可以通过调整这个参数来优化数据读取的性能。

但是,需要注意的是,增加并行工作进程数量也会增加系统的资源消耗,因此需要根据实际情况进行权衡和调整。

请注意,具体的参数名称和用法可能因不同的编程语言、框架或工具而有所不同。

因此,在使用replica_parallel_workers 参数时,建议查阅相关文档或参考示例代码以了解更详细的信息和用法。

CASTEP最常出错原因及解决方法

CASTEP最常出错原因及解决方法CASTEP Error abort handlingAn abnormal or premature exit from a CASTEP run can have three causes.1. CASTEP has detected an error of some kind and chosen to perform a controlled abort ofthe run. This may occur if1. There is a syntax or other error in your input files2. some condition has occurred during the run which prevents it from continuing.This might be a check on the validity of the physics assumptions or acomputational constraint.c)3. CASTEP has requested an action of the operating system (via the Fortranrun-time library) which has returned a failure status to CASTEP2. The operating system has chosen to terminate the CASTEP run and killed it. In a batchsystem this may be because it exceeded some system resource or queue cputime limit.3. There is a bug in CASTEP and the process, or one of the parallel processes has terminatedwith a "segmentation violation" or "bus error" signal (UNIX and Linux) or "access violation" (windows).When trying to understand the cause of the error it is important to work out which of the above three cases has occurred. In case (1) CASTEP always writes a (hopefully) explanatory error message into one of its stderr files. The havenames of the form .nnnn.err where is the root name of your castep run, and nnnn is a 4-digit integer showing which parallel process issued the error message (always 0001 for a serial run). They are deleted on a normal end-of-run exit. If any of these files contains an informational message that proves that CASTEP chose a controlled abort. If on the other hand all of the .nnnn.err files are empty that proves that the running CASTEP processes were killed externally, either because of an operating system action (case 2) or a bug (case 3).Further diagnosis: Cases (2) and (3)To understand these cases you should look at the logfiles written by the batch job manager (if you are using one) which should contain some information on the reason for aborting the run. These can sometimes be verbose and cryptic; it is usually best to study the output logs of a successful run and to look for differences. You may well have to ask your systems staff to interpret these for you.A further indication of an external abort is the presence of "core" files, which are dumped on a signal. These can sometimes be useful to a guru in further diagnosis of a bug.Running out of memoryThis is such a common error with plane-wave calculations that it merits a section of its own.HEAP Memory exceededIf any of the .nnnn.err files contain the messages* Error in allocating /variable/ in /function/ (CASTEP versions <= 4.0.1) * Out of RAM for /variable/ in /function/ (CASTEP versions >= 4.1) this means that CASTEP requested some memory from the operating system (using Fortran's ALLOCATE statement) and the request was denied, usually because availablememory has been exhausted. After checking that your input settings do not contain an error, your options are1. to use some of CASTEP's memory-saving options eg set parameterOPT_STRATEGY=MEMORY (or OPT_STRATEGY_BIAS to 0 or -3) and PAGE_WVFNS=-1 or PAGE_WVFNS=/max-size/2. to find a computer with more memory to run on, (or go to your local computer shop, buyand install some additional memory)3. If on a parallel system, increase the number of processors for the job. This way the totalmemory needed will be distributed over a larger number of processes, and the requirement per processor will be smaller STACK Memory exceededDue to a design limitation of linux and most unix and microsoft operating systems, there is another "memory exceeded" condition which can not be trapped by CASTEP. This occurs when the stack memory is exhausted, and the result is the process is killed with a "segmentation fault" on unix/linux. This is harder to diagnose, but be aware that there are O/S-enforced stack limits which might be much smaller than the physical memory in the system. Google for process stack limits stacksize for more information. the shell command ulimit -s unlimited can be used to increase stack size (bash shells).CASTEP error messages explainedIt is intended that the error messages CASTEP writes to the .nnnn.err6 files are as far as possible self-explanatory. Unfortunately it is not always possible to give useful "end-user" explanations. Here are some commonly encountered abort messages with some explanation.* ERROR: cell_read - failure to open freeform cell file /filename/* Error model_continuation: Failed to open file /filename/CASTEP was unable to open the input files for the run specified on the command line, probably because there is no file of that name. Check your command lines and input files.* Error in allocating /variable/ in /function/ (CASTEP versions <= 4.0.1)* Out of RAM for /variable/ in /function/ (CASTEP versions >= 4.1)This common error means that CASTEP ran out of memory. See section "Running out of memory" for more information * Error reading wavefunction coefficients from file in wave_read_all_ser/parThis or similar messages means that CASTEP was attempting to read a continuation file but the read failed. This is commonly because the .check file is truncated or corrupt. The wavefunction coefficients are fairly far down the file, after the parameters and cell data, and if the read got that far before failing, it is likely that the file was truncated. This can happen if the previous CASTEP run crashed or was killed while writing the .check file. Check to see if the file size is consistent with any similar .check files you may have.* Trapped SIGINT or SIGTERM. Exiting... (CASTEP versions <= 4.0.1) This message is generated by an otherwise useless signal handler in earlier versions of CASTEP. It means that CASTEP was killed by an external signal. Diagnosis should proceed as for major case (3)* Error check_elec_ground_state : electronic_minimisation of initial cell failed. * Error calculate_finite_basis : Convergence failedwhen doing finite basis set correction.* Error in /subroutine/ - electronic_minimisation of current_cell failedAny of these messages means that the SCF convergence loop did not converge in in the maximum allowed number of iterations. If you read the end of the .castep file it ought to be obvious whether the run only just failed to converge. In that case specifying a larger value of MAX_SCF_CYCLES in the .param file ought to work. But sometimes it is apparent that the energy is unlikely ever to converge, for example it may oscillate, or be decreasing linearly and slowly. This may indicate that the system is in a poorly-bonded or co-ordinated state, and it's best to ask advice if you don't know how to preceed.* Error in parameters_restore: missing END_GENERALThis can occur on a continuation run where the .check file used for restart is incompatible with the version of CASTEP you are using. We aim for nearly full compatibility, but there are always exceptions.。

3GPP 5G基站(BS)R16版本一致性测试英文原版(3GPP TS 38.141-1)

4.2.2

BS type 1-H.................................................................................................................................................. 26

4.3

Base station classes............................................................................................................................................27

1 Scope.......................................................................................................................................................13

All rights reserved. UMTS™ is a Trade Mark of ETSI registered for the benefit of its members 3GPP™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners LTE™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners GSM® and the GSM logo are registered and owned by the GSM Association

mpirun each processor is running a duplicate job

mpirun each processor is running a

duplicate job

这个错误提示表明在使用 `mpirun` 运行 MPI 程序时,每个处理器都在运行相同的任务,而不是分配给不同的任务。

这种情况可能发生的原因有以下几种:

1. 你可能在使用 `mpirun` 命令时没有正确指定任务的数量或分配任务给不同的处理器。

请确保你使用正确的参数来指定要运行的任务数量,并将任务分配给不同的处理器。

2. 你的 MPI 程序可能没有正确地实现任务分配。

请检查你的程序代码,确保在初始化阶段正确地分配任务给不同的处理器。

3. 你的 MPI 实现可能存在问题。

尝试使用不同的 MPI 实现(如 OpenMPI、MPICH 等),看看问题是否仍然存在。

4. 你的硬件环境可能存在问题。

检查你的计算机是否支持 MPI 并行计算,并且确保所有的处理器都正常工作。

为了解决这个问题,你可以尝试以下步骤:

1. 检查你的 `mpirun` 命令参数,确保正确指定了任务数量和处理器分配。

2. 检查你的程序代码,确保在初始化阶段正确地分配任务给不同的处理器。

3. 尝试使用不同的 MPI 实现。

4. 检查你的硬件环境。

如果你仍然遇到问题,请提供更多的上下文和错误信息,以便更深入地了解问题所在并给出更具体的解决方案。

jenkins script块中parallel方法

jenkins script块中parallel方法Jenkins是一款开源的自动化构建和持续集成服务器,广泛应用于软件开发领域。

它可以帮助开发者自动化构建、测试、部署等流程,大大提高了开发效率。

Jenkins Script块是Jenkins中的一种配置方式,允许用户通过编写Groovy 脚本来自定义和管理Jenkins 流水线。

今天我们将重点介绍Jenkins Script块中的parallel方法,看看它如何帮助我们更高效地管理构建任务。

Jenkins Script块中的parallel方法主要用于并行执行多个任务。

在使用parallel方法之前,我们需要了解它的几个重要参数:1.parallel( computers: "$computers", pool: "$pool", tasks: ["$tasks"]):这个方法的核心部分,用于定义并行执行的计算机、任务池和任务列表。

puters:一个Computer对象列表,表示要执行任务的计算机。

3.pool:一个Pool对象,表示任务执行的线程池。

4.tasks:一个字符串列表,包含要执行的任务名称。

在使用parallel方法时,我们可以根据实际需求灵活地配置这些参数。

并行执行任务的优势在于,它可以提高构建速度,缩短项目周期。

尤其在大型项目中,通过并行执行任务,可以将原本需要很长时间完成的任务缩短到可接受的范围内。

下面我们通过一个实例来演示如何使用parallel方法:```groovypipeline {agent anystages {stage("Build") {steps {parallel(computers: ["computer1", "computer2"],pool: "custom_pool",tasks: ["build_task1", "build_task2"]) {echo "Building on ${computer}..."sh "echo "Building ${task}""}}}stage("Deploy") {steps {echo "Deploying..."sh "echo "Deploying""}}}}```在这个实例中,我们设置了两个计算机(computer1和computer2)和一个自定义任务池(custom_pool)。

IBM Cognos Transformer V11.0 用户指南说明书

欧洲道路标准

欧洲道路标准集团档案编码:[YTTR-YTPT28-YTNTL98-UYTYNN08]E N13201-3Edition: 2007-06-01路灯第三部分:性能计算Road lightingPart 3: Calculation of performanceNational ForewordThe present ?NORM EN has been reissued without prior public enquiry and represents a consolidated national new edition of EN 13201-3:2003-11, including Corrigendum EN 13201-3:2003/AC:2007-02.The preceding European corrigendum EN 13201-3:2003/AC:2005-06 has been considered and incorporated in this version of ?NORM EN 13201-3.Following clauses were changed:Ad Figure 11 was replacedText after figure title was addedAd Equation (35) was includedEnglish versionRoad lighting - Part 3: Calculation of performanceThis European Standard was approved by CEN on 1 September 2003.This corrigendum becomes effective on 22 June 2005.This corrigendum becomes effectice on 28 February 2007.CEN members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate theconditions for giving this European Standard the status of a national standard without any alteration. Up-to-date lists and bibliographical references concerning such national standards may be obtained on application to the Management Centre or to any CEN member.This European Standard exists in three official versions (English, French, German). A version in any other language made by translation under the responsibility of a CEN member into its own language and notified to the Management Centre has the same status as the official versions.CEN members are the national standards bodies of Austria, Belgium, Bulgaria, Cyprus, Czech Republic, Denmark, Estonia, Finland, France, Germany, Greece, Hungary, Iceland, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, Netherlands, Norway, Poland, Portugal, Romania, Slovakia, Slovenia, Spain, Sweden, Switzerland and United Kingdom.Contents pageForeword ......................................................................... .. (4)Introduction ..................................................................... . (5)1 Scope............................................................................. . (5)2 Normativereferences............ ........................................................... . (5)3 Terms, definitions, symbols and abbreviations (5)Terms and definitions....................................................................... . (5)List of symbols and abbreviations..................................................................... . (8)4 Mathematicalconventions ............ ......................................................... . (10)5 Photometric data.............................................................................. . (10)General .......................................................................... .. (10)The _-table ............................................................................ (10)Interpolation in the _-table ............................................................................ .. (12)General .......................................................................... .. (12)Linear interpolation..................................................................... (12)Quadratic interpolation..................................................................... . (13)Quadratic interpolation in the region of C = 0_, or _ = 0_ or180_ (15)The r-table ............................................................................ (15)Interpolation in the r-table............................................................................. . (18)6 Calculation of_(C,_) ........................................................................... (19)General .......................................................................... .. (19)Mathematical conventions for distances measured on the road (19)Mathematical conventions for rotations (20)Calculation of C and_ ................................................................................ .. (21)7 Calculation of photometric quantities........................................................................ (22)Luminance ........................................................................ . (22)Luminance at apoint ............................................................................ .. (22)Total luminance at a point............................................................................. .. (23)Field of calculation for luminance......................................................................... .. (23)Position of calculationpoints ........................................................................... (24)llluminance....................................................................... .. (29)General .......................................................................... .. (29)Horizontal illuminance at a point............................................................................. .. 29Hemispherical illuminance at a point (29)Semicylindrical illuminance at apoint (30)Vertical iluminance at apoint ............................................................................ (31)Total illuminance at a point............................................................................. (32)Field of calculation for illuminance....................................................................... .. (33)Position of calculationpoints ........................................................................... .. (33)Luminaires included incalculation ...................................................................... (34)llluminance on areas of irregularshape (35)8 Calculation of qualitycharacteristics .................................................................. .. (35)General .......................................................................... .. (35)Averageluminance ........................................................................ .. (35)Overall uniformity........................................................................ .. (35)Longitudinaluniformity ....................................................................... . (35)Threshold increment......................................................................... .. (35)Surroundratio ............................................................................ .. (36)Measures ofilluminance ...................................................................... (39)General .......................................................................... . (39)Averageilluminance ...................................................................... (39)Minimum illuminance....................................................................... .. (40)Uniformity ofilluminance ...................................................................... . (40)9 Ancillary data.............................................................................. .. (40)Bibliography ..................................................................... (41)ForewordThis document (EN 13201-3:2003) has been prepared by Technical Committee CEN/TC 169 “Light and lighting”, the secretariat of which is held by DIN.This European Standard shall be given the status of a national standard, either by publication of an identical text or by endorsement, at the latest by May 2004, and conflicting national standards shall be withdrawn at the latest by May 2004.This European Standard was worked out by the Joint Working Group of CEN/TC 169 "Light and lighting" and CEN/TC 226 "Road Equipment", the secretariat of which is held by AFNOR.This document includes a Bibliography.This standard, EN 13201 Road lighting, consists of three parts. This document is:Part 3: Calculation of performanceThe other parts of EN 13201 are:Part 2: Performance requirementsPart 4: Methods of measuring lighting performanceAccording to the CEN/CENELEC Internal Regulations, the national standards organizations of thefollowing countries are bound to implement this European Standard: Austria, Belgium, Czech Republic, Denmark, Finland, France, Germany, Greece, Hungary, Iceland, Ireland, Italy, Luxembourg, Malta, Netherlands, Norway, Portugal, Slovakia, Spain, Sweden, Switzerland and the United Kingdom.IntroductionThe calculation methods described in this Part of this European Standard enable road lighting quality characteristics to be calculated by agreed procedures so that results obtained from different sources will have a uniform basis.引言本部分欧洲标准中描述的计算方法能使路灯指标通过认可的程序计算出,以使不同光源的结果具有统一的计算依据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

On the Performance of Parallel Concatenated Joint Source-Channel Coding with Variable-Length CodesJ¨o rg KliewerUniversity of KielInstitute for Circuits and Systems TheoryKaiserstr.2,24143Kiel,Germanye-mail:jkl@tf.uni-kiel.deAbstract—A novel approach for robust sourcetransmission is presented where variable-length code(VLC)source and convolutional channel encoding areconcatenated in parallel.Simulation results show thatthe proposed scheme leads to a strong increase in thesignal-to-noise ratio at the decoder output comparedto a serial concatenation of VLCs and channel codes.In the considered transmission system indices I k,k=1,...,K,from afinite alphabet I={0,1,...,2M−1}areobtained by scalar quantization of packetized correlated sourcesymbols U k.The mutual dependencies between the I k aremodeled as afirst-order stationary Gauss-Markov process withtransition probabilities P(I k=λ|I k−1=µ),λ,µ∈I.Eachindex I k=λis then mapped to a variable-length bit vec-tor c(λ)leading to a bitstream w of length N S.In paral-lel,a bit-interleaved version of the binary vector[I1,...,I K]is applied to a terminated recursive systematic convolutional(RSC)channel code.Only the parity bits of each codewordare considered,which results in a length-N C binary sequencev p.Then,the sequences w and v p are multiplexed and trans-mitted over an AWGN channel.At the channel output thesoft-bit vectorsˆw andˆv p are received.In the corresponding iterative decoder one constituentdecoder consists of the symbol-level soft-input soft-output(SISO)VLC source decoder from[1],which calculates a-posteriori probabilities P(I k=λ|ˆw)for the source indicesI k.These reliabilities are converted to L-values L(S)(i k, )=L(S)e(i k, )+L (S)a(i k, )for the source index bits i k, =λ ,=1,...,M,where L(S)a(i k, )denotes the a-priori term. Due to the non-systematic property of the VLC the L-valuesL(S)e(i k, )cannot be further separated into a channel and an extrinsic term.Therefore,in contrast to turbo decoding with systematic codes where the received information bits are also applied to the second constituent decoder,here this informa-tion is provided by using L(S)e(i k, )as a-priori information for the SISO channel decoder after bit-interleaving.The feedback to the source decoder is carried out as in standard turbo de-coding by sending extrinsic information L(C)extr (i k, ).Since theVLC source decoder requires index-based a-priori information, the bit-based a-priori L-values from the channel decoder are converted to index-based probabilities P a(I k=λ|ˆv p).After each iteration,reliability values˜P(I k=λ|ˆw,ˆv p)emerge at the output of the source decoder,which are used in order to obtain a mean-squares estimate of the source symbol U k.In order to increase the performance of iterative decoding an optimization of the VLC codeword index assignments can be carried out for the proposed parallel concatenated joint source-channel coding(PCJSCC)approach in the same way as for the serially concatenatedfixed-length case[2].This is due to the fact that in the iterative decoder in both cases extrinsic information is generated for the information bits. In the VLC case only index permutations between code-words of equal lengths are allowed,where the index map-ping function g:{0,1}M→{0,1}M is optimized such that E{(uλ−uκ)2}is maximized.Herein,uλdenotes the quan-tizer reconstruction level for the undistorted source hypoth-esisλ,and uκrepresents the reconstruction level with the indexκ=g−1(g(λ)⊕t)∈I where g(λ)∈I is distorted by a single bit error generated from the weight-one error pattern t∈{0,1}M.In contrast,for the VLC-based serially concate-nated JSCC approach(SCJSCC)[1]being used for compari-son,it has to be considered for the mapping optimization that in the corresponding iterative decoder extrinsic information is calculated for the VLC code bits and not for the bits i k, .The simulation results for both parallel and serially con-catenated schemes are shown in Fig.1for both an opti-mized(suffix”Map”)and an identity(natural)index map-ping.The source redundancy is modeled by a strongly cor-Fig.1:b0P S≈0.3, AR(1)source process with a=0.9,M=5,optimized RSC generator polynomials(g0,g r)8:(15,11)8for SCJSCC,(12,11)8for PCJSCC) related AR(1)source process quantized with M=5bits,and both approaches use a symmetrical reversible VLC(RVLC). The parameters K,N S,and N C are assumed to be transmit-ted without errors to the decoder.The RSC codes are selected for reconstruction SNR(RSNR)maximization by an exhaus-tive code search over all unpunctured mother codes with code memoryµ=3and R C=1/2based on test simulations in the desired operating range of0dB≤E b/N0≤2dB.The overall code rates R P and R S for PCJSCC and SCJSCC,resp.,take the additional rate contributions from the residual source re-dundancy and the RVLC into account.Fig.1reveals that in the desired operating range the PCJSCC approach shows a strong RSNR gain compared to SCJSCC.AcknowledgmentsThe author would like to thank Ragnar Thobaben for con-tributing parts of the simulation software.References[1]J.Kliewer and R.Thobaben,“Combining FEC and optimalsoft-input source decoding for the reliable transmission of cor-related variable-length encoded signals,”Proc.IEEE Data Com-pression Conference,Apr.2002,pp.83-91,Snowbird,USA. [2]N.Goertz,“Optimization of bit-mappings for iterative source-channel decoding,”Proc.International Symp.on Turbo Codes and Related Topics,Sept.2003,pp.255-258,Brest,France.。