存储随笔《PCIe科普教程》

4.1pcie总线的基础知识

4.1 PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe总线使用的层次结构与网络协议栈较为类似。

4.1.1端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4?1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC耦合电容。

PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。

因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。

由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。

这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。

当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

了解 PCI Express的基本工作原理

下面两节更深入地探讨了PHY和控制器的设计问题。

PCIe SerDes设计难题

为PCIe设计PCIe PHY对于设计人员尤有难度,原因在于:

• 串行至并行的数据转换要求采用先进的模拟设计方案。 • 模拟设计在各种制程技术之间不可移植,所以必须针对用于制造芯片的每一种新制程技术重新设计

PHY。 • 高速本身就已经属于设计难题,而模拟链路增加了设计的复杂度,更加剧了设计难度。例如,由于信

发送眼图接收眼图经过26英寸的fr4材料频率升高后的二进制眼图性能降级这种损失现象会随着频率增加而加大导致在1010位流中出现不能接受的畸变现象实际上交流信号但一串全部是1或全部是0实际上直流信号可以成功地发送

White Paper

了解 PCI Express的基本工作原理

Synopsys产品市场营销经理Scott Knowlton 2007年9月

虽然最初的目标是计算机扩展卡以及图形卡,但PCIe目前也广泛适用于涵盖更广的应用门类,包括网络 组建、通信、存储、工业电子设备和消费类电子产品。

本白皮书的目的在于帮助读者进一步了解PCI Express以及成功PCIe成功应用。

PCI Express基本工作原理

拓扑结构

本节介绍了PCIe协议的基本工作原理以及当今系统中实现和支持PCIe协议所需要的各个组成部分。本节 的目标在于提供PCIe的相关工作知识,并未涉及到PCIe协议的具体复杂性。

PCS Layer

Electrical Sub-block

TxData Command Status RxData PClk

Transaction Link xx

State machines for Link Training and Status State Machine (LTSSM) and lane0lane deskew

第1章 PCI总线的基本知识

PCI(Peripheral Component Interconnect)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关。

在处理器体系结构中,PCI总线属于局部总线(Local Bus)。

局部总线作为系统总线的延伸,主要功能是为了连接外部设备。

处理器主频的不断提升,要求速度更快,带宽更高的局部总线。

起初PC使用8位的XT总线作为局部总线,并很快升级到16位的ISA(Industry Standard Architecture)总线,逐步发展到32位的EISA(Extended Industry Standard Architecture)、VESA(Video Electronics Standards Association)和MCA(Micro Channel Architecture)总线。

PCI总线规范在上世纪九十年代提出。

这条总线推出之后,很快得到了各大主流半导体厂商的认同,迅速统一了当时并存的各类局部总线。

EISA、VESA等其他32位总线很快就被PCI总线淘汰了。

从那时起,PCI总线一直在处理器体系结构中占有重要地位。

在此后相当长的一段时间里,PC处理器系统的大多数外部设备都是直接或者间接地与PCI总线相连。

即使目前PCI Express总线逐步取代了PCI总线成为PC局部总线的主流,也不能掩盖PCI总线的光芒。

从软件层面上看,PCI Express总线与PCI总线基本兼容;从硬件层面上看,PCI Express总线在很大程度上继承了PCI总线的设计思路。

因此PCI总线依然是软硬件工程师在进行处理器系统的开发与设计时,必须要掌握的一条局部总线。

PCI总线V1.0规范仅针对在一个PCB(Printed Circuit Board)环境内的,器件之间的互连,而1993年4月30日发布的V2.0规范增加了对PCI插槽的支持。

1995年6月1日,PCI V2.1总线规范发布,这个规范具有里程碑意义。

pcie基础知识(二)

pcie基础知识(二)本文主要讲述PCIE的相关缩写、术语;不同模式、配置;枚举等基础知识。

一、designware pcie产品:Dual Mode coreRC coreEP coreSwitch core二、架构:Common Xpress Port Logic (CXPL)实现大部分的传输层逻辑,所有的数据链路层逻辑,物理层的MAC部分(包括LTSSM)。

这个module就是所说的core。

XADM和RADM都是针对传输应用添加的模块。

比如说添加传输队列,仲裁TLP transmmision。

Transmit Application-Dependent Module (XADM)Receive Application-Dependent Module (RADM)Configuration-Dependent Module (CDM)Power Management Controller (PMC)Local Bus Controller (LBC)Message Generation (MSG_GEN)Hot Plug Control (hotplug_ctrl)三、核心(CXPL)操作3.1 DM/RC/EP 模式下的初始化在reset之后,通过检测device_type输入进入到RC或者EP模式,CDM内部配置寄存器为复位值。

LTSSM前配置:keep the app_ltssm_enable signal deasserted after reset until the application is ready to establish a Link and start receiving and transmitting TLPs,在这个阶段通过DBI配置好配置寄存器。

开始LTSSM:assert app_ltssm_enable to allow the LTSSM to begin Link establishment3.2 Link EstablishmentPIPE口,和usb3.0一样。

pcie工作原理

pcie工作原理PCIe是一种高速串行总线接口技术,用于连接计算机主板和外部设备,如显卡、网卡和存储设备等。

它是Peripheral Component Interconnect Express的简称,意为外围设备互联扩展。

PCIe的工作原理是通过使用差分信号传输数据,以实现高速、可靠的数据传输。

PCIe的工作原理基于串行传输技术,与传统的并行总线不同。

在传统的并行总线中,数据是同时通过多根传输线传输的,而在PCIe中,数据是通过一对差分传输线(TX和RX)进行传输的。

差分信号指的是两个信号线上的电压差,其变化可以表示二进制数据的0和1。

差分传输技术可以减少电磁干扰和信号失真,提高信号的传输质量和可靠性。

PCIe的工作原理可以简单描述为以下几个步骤:1. 初始化和握手:当计算机开机时,主板会对PCIe总线进行初始化,并与连接的设备进行握手。

这个过程包括识别设备、分配资源和建立通信链路等操作。

2. 数据传输:一旦建立了通信链路,PCIe就可以开始进行数据传输。

数据传输是通过发送和接收数据包来完成的。

数据包是一组有序的二进制数据,包括有效数据、错误检测和纠正码等信息。

发送端将数据包分成小的数据块,并添加控制信息,然后使用差分传输线将数据块发送给接收端。

接收端接收数据块,并进行错误检测和纠正,然后将数据块重新组装成完整的数据包。

3. 中断和信号处理:在数据传输过程中,设备可以向计算机发送中断信号,以通知计算机某个事件的发生。

中断是一种异步的事件,可以打断计算机的正常执行流程,并触发相应的中断处理程序。

中断处理程序可以根据中断的类型和设备的标识符来处理相应的事件。

PCIe的工作原理还涉及到一些其他的概念和机制,如虚拟化、多通道和速率控制等。

虚拟化是一种将物理资源划分为多个逻辑资源的技术,可以提高资源的利用率和灵活性。

多通道是一种将总线划分为多个独立的通道的技术,可以提高总线的带宽和吞吐量。

速率控制是一种动态调整总线速率的技术,可以根据实际需求来调整数据传输速度。

几个搞了好久才明白的pci驱动基本知识点

几个搞了好久才明白的pci驱动基本知识点几个搞了好久才明白的pci驱动基本知识点2008-03-17 10:42接手pci驱动已经好久了,可是长期的惰性真的很难改掉,每天工作时间算算居然不足半小时!老板不来实验室了,我就闲中更闲,kill the precious time...其实,框架我已经都搭好了,只是停留在设备地址和总线地址的解析上。

非常想弄清楚,所谓的pci配置空间,究竟是在pci总线上,还是在pci芯片卡上?现在我觉得,这个问题好像很傻冒,把总线搞的和硬件一样了。

总线难道也有寄存器么?所谓总线支持的空间,应该是总线能寻址的pc上的存储空间把!pci总线支持存储器地址空间,io地址空间和配置空间。

那这个配置空间应该也是pc上的一块存储区,通过pci总线能访问而已。

cy师兄说做驱动其实不需要担心这些问题,只要把数据按照基址+偏移传下去或传上来就行。

可是我总纠结于哪个寄存器、哪块地址空间具体在什么位置。

都是自己没做过硬件,对系统结构的知识也忘得差不多了:(我还是想弄清楚的!好不容易明白了一些东西:1、pci芯片的配置寄存器分为pci配置寄存器pci configuration registers和局部配置寄存器local configuration registers。

这个我看pci9054 databook时一直以为local configuration registers是说dsp上的寄存器。

太久没做事情了,这个英文和中文都断点了。

2、6个pci bar(0-5),其中bar2-5对应4个局部空间0-3,再加上外部rom,pci总线可以访问5个局部地址空间。

一个4个寄存器集合定义了每个空间和空间的特性:pci bar局部范围local range局部基地址local base address局部总线区域描述符local bus region descriptor(指定了局部总线特性,如总线宽度,猝发,预取,和几个等待状态)3、seeprom不能访问pci bar,seeprom可访问局部配置寄存器,bar是主机bios动态分配的。

PCIe的原理及体系架构_学习笔记

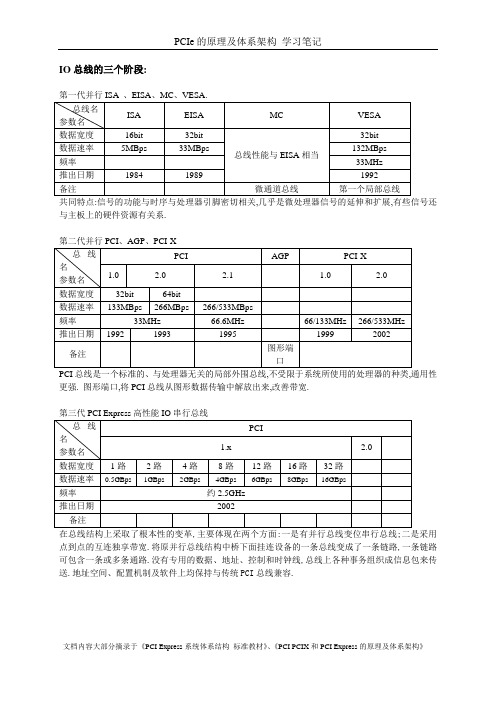

IO总线的三个阶段:第一代并行ISA 、EISA、MC、VESA.共同特点:信号的功能与时序与处理器引脚密切相关,几乎是微处理器信号的延伸和扩展,有些信号还与主板上的硬件资源有关系.第二代并行PCI、AGP、PCI-XPCI总线是一个标准的、与处理器无关的局部外围总线,不受限于系统所使用的处理器的种类,通用性更强. 图形端口,将PCI总线从图形数据传输中解放出来,改善带宽.第三代PCI Express高性能IO串行总线在总线结构上采取了根本性的变革,主要体现在两个方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽.将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路.没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容.第一代和第二代都是并行总线,有多条地址线、数据线和控制线,挂接多个设备,称为下挂式总线(Multi-Drop),总线带宽由多个设备共享.通过提高数据宽度和频率来改善带宽的代价是挂接的电器负载减少(由于功耗增加和静态定时减少).PCIx与PCI相比:由于采用了PLL,频率更高性能更好;在地址和数据的基础上增加属性,从而可以高效管理缓冲区;分离事务协议相对延迟事务协议来说,提高了总线利用效率;可不需要中断引脚,改用消息信号中断(带内)体系结构,中断效率更高.基于PCI总线的结构最基本的PCI总线平台包含三级总线:FSB(Front-Side Bus)、PCI和ISA,FSB是处理器子系统的总线(Host总线),总线定义完全取决于系统所用的处理器;PCI局部总线是一个完全与处理器无关的总线,不受限微处理器的种类;ISA总线(IO扩展总线),也有采用EISA或MC总线的.不同的总线之间通过相应的桥芯片来连接.平台中两极桥是必须的,一是Host到PCI的(常称为主桥——Host桥),即北桥;另一个是PCI总线的桥(常称为扩展总线桥),即南桥.最基本的基于PCI总线的平台PCI地址空间映射x86 CPU的内存与I/O独立编址,I/O对应寄存器,内存对应RAM.因此,访问IO空间用IO读写指令,访问内存空间用内存读写指令.IO读写一般用于低速传输一些状态、控制寄存器的读写等。

PCI Express技术及其接口的介绍

PCI Express 拓扑结构

PCI Express 拓扑结构

PCI Express 在总线技术与结构上实现了新的飞 跃,提供高速的、高性能的、点到点的、双单工的、 串行、差分信号链路来互连设备。 PCI Express 系统中以链路进行两个 PCI Express 设备间的连接,每条链路点到点的互连两 个设备。一条链路相当于一条只挂一个设备的总线。 在数据发送和接收的过程中,每个数据字节实际上 是被转换为 10 位的符号发送的,以保证所有的符 号都含有信号电平的跳变,因为链路上没有时钟信 号,接收器使用 PLL 从进入位流的 0-1 和 1-0 的跳 变中恢复时钟,但发送一个字节数据的开销附加了 25%的开销。PCI Express1.0 规范支持通路中每个 方向上发送/接收速率为 2.5GBps,乘以 2 为,乘以 通路数,除以 10 位/字节,可计算出各种链路宽度 的总的带宽。

PCI Express gen 2

PCI Express2.0规范 于2007年1月发布, 在2008年进入实际应用。它在 1.0 版本基础 上更进了一步,将端口速率提升到了5GHz,传 输性能也翻了一番。PCI Express2.0 保持对 现行 1.0/1.1 规范的兼容,旧的 PCI Express 扩展卡依然可以在 PCI Express2.0 规范的系统中正常运行。同样,PCI Express2.0 扩展设备也可以工作在 1.0 的系 统中,只不过此时设备必须工作在 1.0 兼容 模式下。

PCI Express技术及其接 口的介绍

三大队七队 方清华 韩宗达 滑冬冬

PCI E的定义

PCI Express is a serial interconnect technology, developed by the PCI-Sig (PCI Special Interest Group ) organization, which provides high bandwidth data transmission with the added benefits of reduced board space requirements, smaller connectors and simplified PCB layouts. PCI Express is the third generation of multipurpose I/O interface.

PCIe基础篇(一)、基础知识扫盲

PCIe基础篇(⼀)、基础知识扫盲1、PCIe:Peripheral Component interconnect Expess,外围组件接⼝互联,属于第三代IO总线,PCIe的传输速率指的是实际的有效传输速率,为RAW data(原始数据)的80%,因为其采⽤了8b/10b编解码技术,有效数据是原始数据的0.8,PCIe的iyidai和第⼆代采⽤8b/10b编解码技术,第三代、第四代、第五代采⽤128b/130b编解码技术。

2、PCI总线是⼀种共享总线,所以需要有特定的仲裁器(Arbiter)来决定当前时刻总线的控制权。

⼀般该仲裁器位于北桥中,⽽仲裁器(主机)通过⼀对引脚REQ#和GNT#(grant)来与各个从机连接。

PCI总线是⼀种地址和数据复⽤的总线,地址和数据占⽤同⼀组信号线。

PCIe采⽤了差分、全双⼯的传输设计,允许在同⼀时刻,同时进⾏发送进⽽接收数据,设备之间通过双向的Link连接,每个Link⽀持1~32个通道(lane),由于是串⾏总线,因此所有的数据(包括配置信息等)都是以数据包为单位进⾏发送。

PCIe中还引⼊了嵌⼊式时钟计数,发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据通道中恢复出时钟.PCIe是⼀种点对点连接的总线,不是共享总线。

但是PCIe可以通过SWITCH连接多个PCIe设备,Switch包含了多个类似于PCI总线中桥的该概念。

上图中,Root Component作为Root,是CPU和PCIe总线系统通信的媒介。

endpoint位于PCIe总线系统拓扑结构中的最末段,⼀般作为总线操作的发起作者(initiator,类似于主机)与终结者(Completers,类似于从机),endpoint只能接收上级拓扑的数据包或者向上级发送数据包。

此外,Leagcy PCIe Endpoint指的是元贝准备设计为PCI-X总线接⼝的设备,却被改为PCIe接⼝的设备,native PCIe ENDpoint指的是标准的PCIe设备。

PCIE基础知识-fyf

1 PCI总线发展历史1.1 PCIPCI, Peripheral Component Interconnect(外设部件互联标准),是由Intel 公司1991年推出的一种局部总线。

最早提出的PCI总线工作在33MHz频率之下,传输带宽达到132MB/s(33MHz * 32bit/8),基本上满足了当时处理器的发展需要。

随着对更高性能的要求,后来又提出把PCI 总线的频率提升到66MHz,传输带宽能达到264MB/s。

虽然,除了3D显示卡以外,直到现在还没有哪个计算机配件脱离PCI总线的束缚另起炉灶,诸如千兆网卡、声卡、RAID卡等都还在循规蹈矩的奉行着PCI规范,但,PC技术的快速发展已经让PCI总线越来越显现出不足,尤其是最近的千兆网络以及视频应用等外设,会使PCI可怜的133MB/s带宽难以承受,当几个类似外设同时满负荷运转,PCI总线几近瘫痪。

不但如此,随着技术的不断进步,PCI电压难以降低的缺陷越来越凸出出来,PCI规范已经成为现在PC系统的发展桎梏,彻底升级换代迫在眉睫。

1.2 PCI-XPCI-X接口是1998年由IBM, HP, 以及 Compaq等公司制定,是并连的PCI 总线的更新版本,仍采用传统的总线技术,不过有更多数量的接线针脚,同时,所有的连接装置会共享所有可用的频宽。

与原先PCI接口所不同的是:一改过去的32位,PCI-X采用64位宽度来传送数据,所以传输带宽就自动倍增,而扩充槽的长度当然就不可避免的加大了,除此之外,其余的包含传输通讯协议、讯号和标准的接头格式都一并兼容。

后来PCI-X 2.0又分别提升频率,经历过266Mhz,533Mhz,这个带宽可以说是非常足够的了,不过这个时候PCI-X也面临一些问题:一方面是频率提高造成的并行信号串扰,另一方面是共享式总线造成的资源争用,总之也就是说虽然规格上去了,但实际效果可能跑不了这些指标。

1.3 PCI-ExpressPCI-Express,简称PCI-E,于2001年春季由Intel公司提出。

PCIe基础知识 文档

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

4.1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。

因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。

由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。

这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。

当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCI浅说

现如今,如果您鼓捣计算机,就离不开PCI这个东西。

尽管现在PCI-E总线已经相当流行,但是采用PCI 总线技术的设备和带PCI插槽的主板仍旧随处可见。

看来,PCI-E要完全取代PCI还需要一定的过渡期。

所以,简单了解PCI总线还是有必要的。

在网上,介绍PCI的文章比比皆是。

但大多数不是太简单,就是太专业。

本文尽量避免那些艰涩难懂的专业术语和内容,力求用通俗的语言,简单说说PCI这个玩意儿。

因此,难免不专业,不规范,不准确,不科学。

好在不是学术论文,仅为“扫盲”而已。

大部分内容都是拜读许多网络文章后整理而得。

纯属个人理解,绝非权威观点。

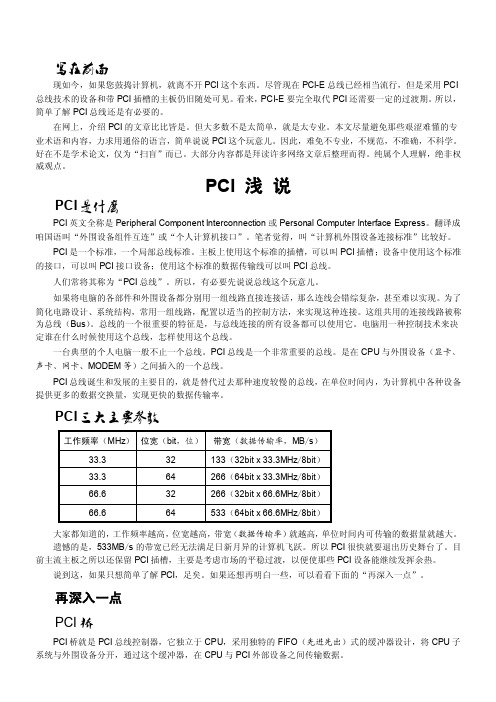

PCI 浅说PCIPCI英文全称是Peripheral Component Interconnection或Personal Computer Interface Express。

翻译成咱国语叫“外围设备组件互连”或“个人计算机接口”。

笔者觉得,叫“计算机外围设备连接标准”比较好。

PCI是一个标准,一个局部总线标准。

主板上使用这个标准的插槽,可以叫PCI插槽;设备中使用这个标准的接口,可以叫PCI接口设备;使用这个标准的数据传输线可以叫PCI总线。

人们常将其称为“PCI总线”。

所以,有必要先说说总线这个玩意儿。

如果将电脑的各部件和外围设备都分别用一组线路直接连接话,那么连线会错综复杂,甚至难以实现。

为了简化电路设计、系统结构,常用一组线路,配置以适当的控制方法,来实现这种连接。

这组共用的连接线路被称为总线(Bus)。

总线的一个很重要的特征是,与总线连接的所有设备都可以使用它。

电脑用一种控制技术来决定谁在什么时候使用这个总线,怎样使用这个总线。

一台典型的个人电脑一般不止一个总线。

PCI总线是一个非常重要的总线。

是在CPU与外围设备(显卡、声卡、网卡、MODEM等)之间插入的一个总线。

PCI总线诞生和发展的主要目的,就是替代过去那种速度较慢的总线,在单位时间内,为计算机中各种设备提供更多的数据交换量,实现更快的数据传输率。

PCI总线技术(doc 7页)

PCI总线技术(doc 7页)PCI总线技术概论各种PCI总线产品经过几年的发展,PCI总线以其优越的电性能获得了业界的一致认可。

同时利用PCI总线的电性能,结合不同的机械结构,产生了各种各样的总线。

在此做一简要介绍:CPCI总线:将PCI总线与欧规卡的机械结构相结合,具有抗振性能好、高可用性等优点,而且可以支持热插拔(Hot Swap)、后走线(Rear IO),目前在电信、军工、交通等领域正在得到广泛的应用。

PXI总线:在CPCI基础上加入同步时钟、触发等量测专用总线,在测量、控制领域正得到越来越多的应用。

PC104 Plus总线:将PCI总线与PC104板的机械结构相结合,具有效率高、维护量少、体积小型等特点,在各种嵌入式应用中很受欢迎。

另外还有笔记本电脑常用的PCMCIA总线、电信行业中最近配合CPCI使用的PMC等等,电特性都是PCI总线。

从1992年创立规范到如今,PCI总线已成为了事实上计算机的标准总线。

由PCI 总线构成的标准系统结构如图一所示。

32bit PCI系统的管脚按功能来分有以下几类:系统控制:CLK,PCI时钟,上升沿有效RST ,Reset信号传输控制:FRAME#,标志传输开始与结束IRDY#,Master可以传输数据的标志DEVSEL#,当Slave发现自己被寻址时置低应答TRDY#,Slave可以转输数据的标志STOP#,Slave主动结束传输数据的信号IDSEL,在即插即用系统启动时用于选中板卡的信号地址与数据总线:AD[31::0],地址/数据分时复用总线C/BE#[3::0],命今/字节使能信号PAR,奇偶校验信号仲裁号:REQ#,Master用来请求总线使用权的信号GNT#,Arbiter允许Master得到总线使用权的信号错误报告:PERR#,数据奇偶校验错SERR#,系统奇偶校验错当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。

PCIE接口介绍-修改

PCIe接口介绍PCIe接口简介PCIe(Peripheral Component Interconnect Express)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Group,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe 的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)。

PCI总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe总线(在2001年发布,采用点对点串行连接)替代。

目前PCIe的主流应用是3.0,4.0还没正式推出,但标准已经制定的差不多了。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

实际使用中,PCIe无法一直维持在峰值传输状态,因为编码方式、链路管理消耗、存储时间延迟等原因,一般只有50%~60%的效率。

PCIe接口原理连接方式PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图一。

PCI配置寄存器

PCI总线简介

PCI寻址(物理)

pci域:(16位) 总线号:(8位) 设备号:(5位) 功能号:(3位) 总线号、设备号和功能号共同组成pci外设的16位硬件地址。 但是由于256个总线对许多大系统是不够的, Linux 现在支持 PCI 域。每个 PCI 域可以占用多达 256 个总线. 每个总线占 用 32 个设备, 每个设备可以是一个多功能卡(例如一个声音 设备, 带有一个附加的 CD-ROM 驱动)有最多 8 个功能 这样,linux系统可以支持更多的pci设备

标准pci配置寄存器

取得设备的io或mem

此pci设备用到了几个BAR?应该从哪个bar里读取所需的io地址或内存地 址? 这些信息是硬件相关的,需要查阅pci设备的datasheet才能得到以上信息 读取内存或io地址的函数: unsigned long pci_resource_start(struct pci_dev *dev, int bar); unsigned long pci_resource_end(struct pci_dev *dev, int bar); unsigned long pci_resource_len(struct pci_dev *dev, int bar); bar的取值为0~5 unsigned long pci_resource_flags(struct pci_dev *dev, int bar); 这个函数返回和这个资源相关联的标识. IORESOURCE_IO:io端口 IORESOURCE_MEM :内存

(2)为这个结构体填充设备vendor id、device id、 subvendor id、subdevice id以及地址和irq信息(通过读 取pci配置寄存器得到)

PCI-Express详解

基础篇随着Intel 800MHz FSB芯片组i875P的推出,Intel同时也向世人显示一个全新的总线技术即将推出,那就是由Intel首先提出并开发的3GIO总线。

后来这一技术提交PCI-SIG(PCI 特殊兴趣组织),由PCI-SIG改名为"PCI Express",以标准的形式正式推出,目前的最新版本为v1.0。

本连载就要带大家深入了解这一即将改变整个计算机系统结构、成为下一代总线标准的总线技术。

首先本文要向大家介绍的是一些基础知识。

一、PCI标准的发展历史要了解PCI Express总线技术的提出原因,我们先来简要回顾一下PCI总线的发展历史目前应用的计算机内部总线技术为PCI,即"Peripheral Component Interconnect",中文名为"外围组件互连",它是由Intel于1991年提出的(与本文要介绍的PCI-Express总线技术属同一个公司开发的)。

后来,PCI-SIG小组接替了Intel的PCI规范的发展,在1993年5月发布了PCI 2.0。

那时,PCI的竞争对手是VESA本地总线(VL-bus或VLB),它是由视频电子标准协会提出的32bit总线,在标准的ISA插槽之后提供附加的第三和第四接口,额定频率33MHz,并且能够提供超过ISA。

但是当时作为486处理器/内存总线的直接扩展,VESA 是运行在与处理器相同的频率上,因此名为"本地总线",这种直接的扩展意味着如果连接的设备过多,则很可能会干扰处理器自身的工作,特别是当信号通过一个插槽时。

于是VESA标准中建议在33MHz频率上只使用2个插槽,或者在总线使用电子缓冲时使用3个。

在更高的频率上不能连接2个以上的设备,而在50MHz时它们则必须都内建于主板内。

由于VESA与处理器同步工作,因而随着处理器频率的提高,VESA总线类型的外围设备工作频率也得随着提高,但是外围设备要求的速度越高,其造价也就更高,对外围设备的生产成本控制造成了极大的不利。

PCI学习心得

PCI学习记录2013-11-4PCI总线是32位同步复用总线。

其地址和数据线引脚是AD31~AD0。

PCI的工作频率为33MHz。

PCI9054通过有效LHOLD来申请本地总线。

当LHOLD和LHOLDA被有效时它就获得了本地总线。

本地总线周期可以是Single周期或突发周期。

BLAST#信号被用于决定是一个Single周期被执行还是一个突发周期被执行。

PCI9054是一个PCI总线Target和一个本地总线Master一PCI总线特性1.PCI总线特点(1)传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。

这是其他总线难以比拟的。

它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输的需要。

(2)多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。

通过HOST-PCI桥接组件芯片,使CPU总线和PCI总线桥接;通过PCI-ISA/EISA 桥接组件芯片,将PCI总线与ISA/EISA总线桥接,构成一个分层次的多总线系统。

高速设备从ISA/EISA总线卸下来,移到PCI总线上,低速设备仍可挂在ISA/EISA总线上,继承原有资源,扩大了系统的兼容性。

(3)独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

(4)自动识别与配置外设用户使用方便。

(5)并行操作能力。

2.PCI总线的主要性能(1)总线时钟频率33.3MHz/66.6MHz。

(2)总线宽度32位/64位。

(3)最大数据传输率132MB/s(264MB/s)。

(4)支持64位寻址。

(5)适应5V和3.3V电源环境。

二PCI总线信号PCI总线标准所定义的信号线通常分成必需的和可选的两大类。

其信号线总数为120条(包括电源、地、保留引脚等)。

其中,必需信号线:主控设备49条,目标设备47条。

pcie学习计划

pcie学习计划一、入门阶段1. 了解PCIe的基本概念和原理在入门阶段,首先要对PCIe(Peripheral Component Interconnect Express)的基本概念和原理进行了解。

PCIe是一种用于连接扩展卡和主板的高速接口标准,它是PCI总线的后继者,在传输速度、带宽和功耗方面都有了显著的提升。

了解PCIe的发展历程、工作原理和技术特点,对后续的学习和应用都有很大的帮助。

2. 学习PCIe的物理层和数据链路层PCIe接口包括物理层和数据链路层两个部分,这两个部分是理解PCIe技术的关键。

在学习物理层时,要掌握信号传输的基本原理、组成部分和接口规范;在学习数据链路层时,要了解数据传输的机制、连接管理和控制流程。

对PCIe接口的物理层和数据链路层有深入的理解,有助于后续的应用和故障排除。

3. 学习PCIe的架构和规范PCIe接口有多个版本和规范,每个版本都有其特定的架构和规范。

在入门阶段,要学习PCIe的各个版本的架构和规范,包括连接类型、带宽规格、电气特性等。

对PCIe的各个版本的架构和规范有全面的了解,有助于选择合适的接口版本和了解其应用场景。

4. 学习PCIe的设备驱动开发PCIe接口的设备驱动开发是PCIe学习的重要内容之一。

在入门阶段,要学习PCIe设备驱动的基本概念、开发流程和调试技巧。

了解设备驱动的开发原理和方法,对后续的应用和系统优化都有很大的帮助。

二、进阶阶段1. 深入学习PCIe的协议和传输层PCIe接口的协议和传输层是PCIe学习的进阶内容,包括数据传输协议、报文格式、序列管理和错误控制等。

在进阶阶段,要深入学习PCIe接口的协议和传输层,包括数据包的格式、传输流程和错误检测与纠正等。

对PCIe接口的协议和传输层有深入的了解,有助于应用和系统性能的提升。

2. 学习PCIe的性能优化和调试技巧PCIe接口的性能优化和调试技巧是PCIe学习的重要内容之一。

在进阶阶段,要学习PCIe 接口的性能优化技巧,包括传输速度、带宽利用和延迟控制等。

PCIe SSD存储介绍

PCIe 接口的Flash

• SATA 向PCIe接口转化, Enterprise

Source: HGST

PCIe 接口的Flash

• SATA 向PCIe接口转化, Client

Source: Marvell

不同存储设备比较 – HDD, SATA SSD, PCIe Flash

单位容量价格提升20~40倍

PCIe Flash使用者

1. Facebook 2. Apple 3. …

Shannon PCIe Flash支撑业务发展

部署时间点

谢谢聆听!

Thank you for listening

数据库 云计算 虚拟化

•PCIe固态存储应用范围急 剧扩大

•数据库,虚拟化,数据

仓库都越来越多采用PCIe 固态存储

数据仓库

内容,存档

性能

容量成本

PCIe Flash加速应用

数据库

虚拟化

搜索

大数据分析

高性能计算

提纲

• 数据中心架构的变迁 – 闪存革命 • PCIe 固态闪存卡简介 • 使用PCIe固态闪存卡的顾虑

完善的容错数据保护机制

- 高达 40bit/1KB ECC或更高 - 读写,擦除出错处理及数据保护 - 页面,坏块出错处理及数据保护

内置RAID机制

- RAID-(N+1)冗余阵列 - 动态,可配置冗余度 - 进一步防止数据丢失

端到端数据保护

- 企业级端到端数据链路保护 - 多重数据完整性及正确性校验

• 机械硬盘性能十年2倍

•固态存储技术基于全 半导体存储,与 CPU/DRAM同步

• SSD随机读写性能优异, 延迟极低,稳定可靠

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微信公众号【存储随笔】荣誉出品《PCIe科普教程》2017.6PCIe 科普教程古猫著目录1.0PCIe概述_______________________________________________________42.0Transaction layer事务层概述____________________________________7 2.1TLP的前世今生__________________________________________________9 2.2TLP事务处理方式_______________________________________________12 2.3TLP结构解析___________________________________________________16 2.4Flow Control机制概述__________________________________________21 2.5Flow Control缓存架构及信用积分________________________________22 2.6Flow Control初始化____________________________________________23 2.7Flow Control的实现过程________________________________________282.8事务排序机制___________________________________________________323.0数据链路层概述_________________________________________________35 3.1数据链路层DLLP结构及类型______________________________________363.2数据链路层Ack/Nak机制_________________________________________404.0物理层结构解析_________________________________________________544.1物理层数据流解析_______________________________________________595.0PCIe总线电源管理______________________________________________656.0PCIe系统复位方式______________________________________________727.0PCIe热插拔____________________________________________________78微信公众号平台:PCIe专题文章列表(点击即可跳转) PCIe系列专题之一:PCIe技术概述PCIe系列专题之二:2.0Transaction layer事务层概述PCIe系列专题之二:2.1TLP的前世今生PCIe系列专题之二:2.2TLP事务处理方式解析PCIe系列专题之二:2.3TLP结构解析PCIe系列专题之二:2.4Flow Control机制概述PCIe系列专题之二:2.5Flow Control缓存架构及信用积分PCIe系列专题之二:2.6Flow Control初始化PCIe系列专题之二:2.7Flow Control的实现过程PCIe系列专题之二:2.8事务排序机制PCIe系列专题之三:3.0数据链路层概述PCIe系列专题之三:3.1数据链路层DLLP结构及类型PCIe系列专题之三:3.2数据链路层Ack/Nak机制解析PCIe系列专题之四:4.0物理层结构解析PCIe系列专题之四:4.1物理层数据流解析PCIe系列专题之五:PCIe总线电源管理PCIe系列专题之六:PCIe系统复位方式PCIe系列专题之七:PCIe热插拔1.0PCIe概述SSD的协议标准除了SATA,还有一个更先进的协议标准,就是PCIe。

PCIe总线使用了高速差分总线,并采用了端到端的连接方式。

两个设备之间的的传输通道,称为Link,由1,2,4,8,16,32个Lane组成。

Lane的数目代表Link的传输宽度(x1,x2,x4,x8,x16,x32)。

Lane是发送端与接收端之间的一个传输回路。

由两组差分信号组成。

如下图,扩展:PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,能有效抑制电磁干扰EMI(Electro Magnetic Interference)。

目前正式发布的最新是仍是第三代PCIe技术。

不过,第四代PCIe协议预计在今年6月会的PCIe开发者大会上正式发布,相信很快也会跟大家见面了。

我们这里就先列出PCIe Gen1/2/3的传输速率对比如下表:这里需要提一下:Gen1/Gen2采用是8b/10b的编码,而Gen3则采用的是128b/130b的编码。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含通过PLL锁相环从接收报文中提取接收时钟,从而进行同步数据传递。

PCIe是一种封装分层协议,主要包括事务层(Transaction layer),数据链路层(Data link layer)和物理层(Physical layer)。

在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。

而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

在一条PCIe链路中,这两个端口是完全对等的,分别连接发送与接收设备,而且一个PCIe链路的一端只能连接一个发送设备或者接收设备。

因此PCIe链路必须使用Switch扩展PCIe链路后,才能连接多个设备。

2.0Transaction layer事务层概述在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer),最终发送出去。

而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

事务层的主要职责可以概述为:事务层是PCIe总线层次结构的最高层,该层次将接收PCIe设备核心层的数据请求,并将其转换为PCIe总线事务,PCIe总线使用的这些总线事务在TLP头中定义。

PCIe总线继承了PCI/PCI-X总线的大多数总线事务,如存储器读写(Memory Read/Write)、I/O读写、配置读写总线事务,并增加了Message总线事务和原子操作等总线事务。

扩展:PCIe中有两大类总线事务:Non-Posted和Posted:a,Non-Posted:需要completion返回响应包;b,Posted:不需要completion返回响应包.在PCIe总线中,Non-Posted总线事务分两部分进行,首先是发送端向接收端提交总线读写请求,之后接收端再向发送端发送完成(Completion)报文。

PCIe总线使用Split传送方式处理所有Non-Posted总线事务,存储器读、I/O读写和配置读写这些Non-Posted总线事务都使用Split传送方式。

PCIe的事务层还支持流量控制(Flow control)和虚通路管理(Virtual Channel Management)等一系列特性,而PCI总线并不支持这些新的特性。

在PCIe总线中,不同的总线事务采用的路由方式不相同。

PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也被称之为事务层数据报文,即TLP,TLP在经过数据链路层时被加上Sequence Number前缀和CRC后缀,然后发向物理层。

2.1TLP的前世今生PCIe总线使用的数据报文首先在事务层中形成,这个数据报文也被称之为事务层数据报文,即TLP(Transaction Layer Packet),TLP在经过数据链路层时被加上Sequence Number前缀和CRC后缀,然后发向物理层。

生活中,有时,我们会陷入一个哲学性的思考:"我们来自哪里,终归何方?"同样,TLP也有这个命题的解答。

TLP来自发送设备的事务层,历经“磨难”,终归接收端的事务层。

那么,在TLP传递的过程中到底经历哪些“磨难”呢?请看下图~我们逐层解析一下这些“磨难”:1.发送端Device Core发送事务请求:数据读写,完成反馈(Completions),信息(Message)等;2.事务层根据Device Core的请求,生成TLP Header,加上Device Core提供的data,最后加上ECRC(End to End CRC)。

此时TLP会放入事务层缓存(VirtualChannel Buffer)之中;此时,生成"加强版"TLP,并放入数据链路层的Retry buffer;4.当TLP传至物理层时,被加上头和尾,到这里,TLP在发送端就组装完毕咯;5.在接收端就跟发送端做的事情相反了,在物理层需要掐头去尾,然后传输至数据链路层;6.数据链路层收到传入的TLP后,通过计算LCRC验证传输是否正确,正确的话就去掉Sequence Number和LCRC,将TLP传输至事务层;7.事务层接收到TLP之后,解析其内容,并将信息传给接收端Device Core,至此,发送端传过来的组装TLP已拆解完毕。

2.2TLP事务处理方式看过前面TLP的前世今生精彩大剧之后,想必大家应该都知道TLP(Transaction Layer Packet)在事务层的角色。

如果不知道,就默默翻一下前面的文章哈~TLP很重要,也有很多种类。

我们先来个全局的认识,看看PCIe到底定义了多少TLP种类呢?瞅下面的表格~这么多TLP啊,每个都是什么含义,到底是干什么的呢?不急,我们慢慢的揭开他们神秘的面纱~之前的介绍中,我们提到过PCIe中总线事务有两大类:Non-Posted和Posted:(1)Non-Posted:需要completion返回响应包;(2)Posted:不需要completion返回响应包注:Memory Read Lock只适用在兼容PCI/PCI-X的陈旧设备中,在这里就先忽略了。