VGA显示器彩色信号发生器电路

实验9 VGA显示控制器实验

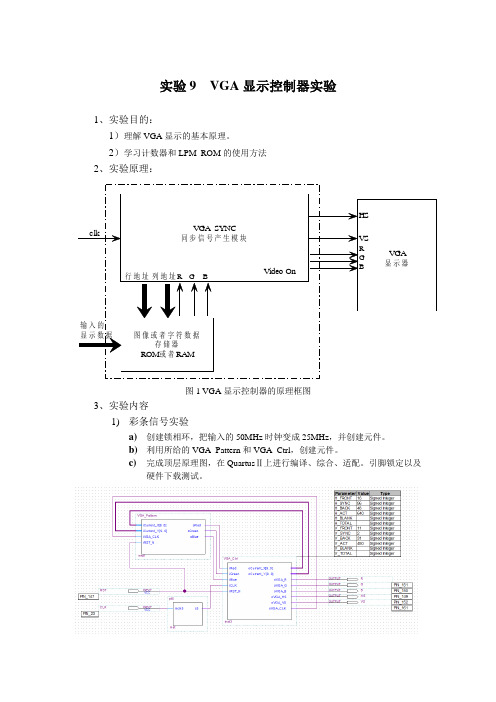

实验9 VGA显示控制器实验1、实验目的:1)理解VGA显示的基本原理。

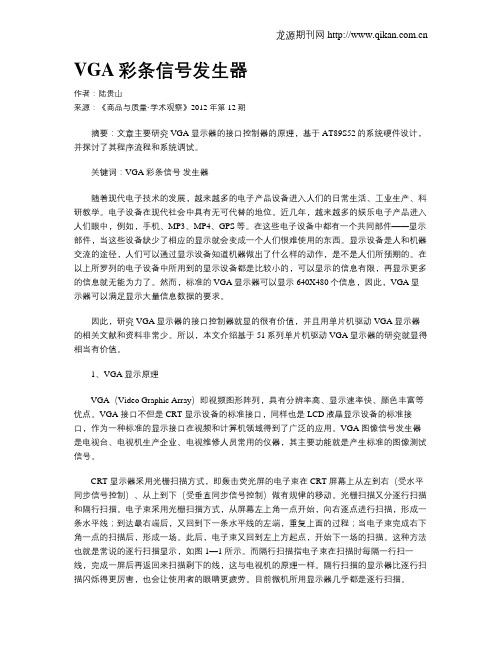

2)学习计数器和LPM_ROM的使用方法2、实验原理:图1 VGA显示控制器的原理框图3、实验内容1)彩条信号实验a)创建锁相环,把输入的50MHz时钟变成25MHz,并创建元件。

b)利用所给的VGA_Pattern和VGA_Ctrl,创建元件。

c)完成顶层原理图,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

2)显示自己的姓实验。

修改VGA_Pattern,利用if语句控制相应区域的相应值,在QuartusⅡ上进行编译、综合、适配。

引脚锁定以及硬件下载测试。

3)显示数字实验a)创建lpm_rom,手动输入“0”的mif文件。

b)顶层文件为numTop.v,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

4)计数显示实验a)创建“1~9”的lpm_rom,mif文件已给出。

b)加入计数器。

c)完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

5)数字钟实验在4)基础上加入位置控制,完成顶层文件,在QuartusⅡ上进行编译、综合、适配,硬件下载测试。

6)显示理工校徽实验(2)moduleVGA_Pattern(//HostSideoRed,oGreen,oBlue,iCurrent_X,iCurrent_Y,iVGA_CLK,iRST_N); // Host Sideoutput reg oRed;output reg oGreen;output reg oBlue;input [9:0] i Current_X;input [9:0] i Current_Y;// Control Signalinput iVGA_CLK;input iRST_N;always@(posedge iVGA_CLK or negedge iRST_N)beginif(!iRST_N)beginoRed <= 0;oGreen <= 0;oBlue <= 0;endelsebeginif((( iCurrent_Y>60)&& (iCurrent_Y <80))&&((iCurrent_X>200)&&(iCurrent_X <400)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>80)&& (iCurrent_Y <240))&&((iCurrent_X>200)&&(iCurrent_X <240)))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end/*else if((( iCurrent_Y>150)&& (iCurrent_Y <170))&&((iCurrent_X>260)&&(iCurrent_X <340)))/*else if((150 < iCurrent_Y < 170)&&(260<iCurrent_X < 340))beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelse if((( iCurrent_Y>170)&& (iCurrent_Y <240))&&((iCurrent_X>290)&&(iCurrent_X <310)))/*else if((170 < iCurrent_Y < 240)&&(290 < iCurrent_X < 310))beginoRed <= 1;oGreen <= 0;oBlue <= 0;end*/else if((( iCurrent_Y>240)&& (iCurrent_Y <260))&&((iCurrent_X>200)&&(iCurrent_X <400)))/*else if((240 < iCurrent_Y < 260)&&(150 < iCurrent_X < 450))*/beginoRed <= 1;oGreen <= 0;oBlue <= 0;endelsebeginoRed <= 0;oGreen <= 0;oBlue <= 0;endendendendmodule(3)(4)module numTop1(CLK,RST,R,G,B,HS,VS); input CLK,RST;output R,G,B,HS,VS;wire clk25Mhz,vga_clk;wire [9:0]ram_data;wire [9:0] X,Y;wire [6:0] ram_addr;wire [3:0]COUNT;wire carry1;wire CLK1HZ;reg vga_data;assign ram_addr = {Y[5:2],X[4:2]};altPLL0 u1(CLK,clk25Mhz);VGA_Ctrl u2(.iRed(vga_data),.iGreen(vga_data),.iBlue(vga_data),.oCurrent_X(X),.oCurrent_Y(Y),// VGA Side.oVGA_R(R),.oVGA_G(G),.oVGA_B(B),.oVGA_HS(HS),.oVGA_VS(VS),.oVGA_CLK(vga_clk),// Control Signal.iCLK(clk25Mhz),.iRST_N(RST) ); demo_shuzi u17(ram_addr,vga_clk,ram_data[0]); ROM1 u21(ram_addr,vga_clk,ram_data[1]);ROM2 u14(ram_addr,vga_clk,ram_data[2]);ROM3 u15(ram_addr,vga_clk,ram_data[3]);ROM4 u6(ram_addr,vga_clk,ram_data[4]);ROM5 u7(ram_addr,vga_clk,ram_data[5]);ROM6 u8(ram_addr,vga_clk,ram_data[6]);ROM7 u9(ram_addr,vga_clk,ram_data[7]);ROM8 u10(ram_addr,vga_clk,ram_data[8]);ROM9 u11(ram_addr,vga_clk,ram_data[9]);/*demo_shuzi u3(ram_addr,vga_clk,ram_data);*/ GeneralCnt #(4,9) u4(CLK1HZ,RST,1,COUNT,carry1); ClkDiv #(26,50000000) u5(CLK,RST,CLK1HZ);always@(X,Y)if(X<32 && Y<64)vga_data=ram_data[COUNT];else if(X<64 && Y<64)vga_data=ram_data[COUNT];elsevga_data=0;endmodule//任意倍整数分频器module ClkDiv(clk_in,rst_n,clk_out);parameter MSB = 4, DIV_TIMES = 10;input clk_in,rst_n;output clk_out;reg clk_out;reg [MSB-1:0] count;always @(negedge rst_n or posedge clk_in)beginif(rst_n==0)begincount<=0;endelsebeginif(count < (DIV_TIMES-1))count<=count+1'b1;elsecount<=0;endendalways @(negedge rst_n or posedge clk_in) beginif(rst_n==0)beginclk_out<=1'b0;endelsebeginif(count<(DIV_TIMES>>1))clk_out<=1'b0;elseclk_out<=1'b1;endendendmodule//通用计数器module GeneralCnt(clk,reset_n,ena,cnt,carry_out);parameter MSB = 4, CNT_END = 9; input clk;input reset_n;input ena;output [MSB-1:0]cnt;output carry_out;reg [MSB-1:0]cnt;reg carry_out;//计数always@(posedge clk or negedge reset_n) beginif(!reset_n)cnt <= 0;else if(ena && cnt==CNT_END)cnt <= 0;else if (ena && cnt < CNT_END)cnt <= cnt + 1'b1;end//产生进位输出always@(posedge clk or negedge reset_n) begin if(!reset_n)carry_out <= 1'b0;else if(ena && cnt==CNT_END)carry_out <= 1'b1;elsecarry_out <= 1'b0;endendmodule。

VGA彩条信号显示控制器设计

电子设计自动化课程设计报告学生姓名:学号:课设题目: VGA彩条信号显示控制器设计同组人:电子设计自动化课程设计报告一、课程设计内容1、使用Verilog语言和Modelsim仿真器完成可显示横彩条、竖彩条、棋盘格相间的VGA控制器的设计和验证2、设计并验证可显示英语单词”HIT”的VGA控制器3、使用Quartus II和SOPC实验箱验证设计的正确性4、Verilog代码要符合微电子中心编码标准二、FPGA原理CPLD、FPGA是在PAL、GAL等基础上发展起来的一种具有丰富的可编程I/O 引脚、逻辑宏单元、门电路以及RAM空间的可编程逻辑器件,几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

CPLD的设计是基于乘积项选择矩阵来实现的,而FPGA基于查找表来设计的。

查找表就是实现将输入信号的各种组合功能以一定的次序写入RAM中,然后在输入信号的作用下,输出特定的函数运算结果。

其结构图如图1所示:图1. FPGA查找表单元一个N输入查找表(LUT,Look Up Table)可以实现N个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。

输入多于N个的函数、方程必须分开用几个查找表(LUT)实现(如图2所示)。

图2 FPGA查找表单元内部结构该系统设计中,FPGA芯片用的是ALTERA公司的EP1K30QC208-2,它的系统结构如图3所示。

它由若干个逻辑单元和中央布线池加I/O端口构成图3 EP1K30QC208内部结构三、VGA接口VGA的全称为Video Graphic Array,即显示绘图阵列。

在PC行业发展的初期,VGA以其支持在640X480的较高分辨率下同时显示16种色彩或256种灰度,同时在320X240分辨率下可以同时显示256种颜色的良好特性得到广泛支持。

后来,厂商们纷纷在VGA基础上加以扩充,如将显存提高至1M并使其支持更高分辨率如800X600或1024X768,这些扩充的模式就称之为VESA(Video Electronics Standards Association,视频电子标准协会)的Super VGA模式,简称SVGA,现在的显卡和显示器都支持SVGA模式。

VGA显示器彩色信号显示控制器课程设计

第一部分任务要求1.1课题要求设计一个VGA 图像显示控制器,通过实验箱的VGA接口控制VGA显示器控制,利用键盘作为输入控制显示器上不同彩色条纹输出,通过VHDL编程实现简VGA彩色信号显示控制。

1.2设计目标1、查阅资料确定设计方案。

(建议采用顶层设计方法)2、理解VGA显示器的工作原理,并编写和调试驱动。

3、理解键盘控制的工作原理,并编写和调试驱动程序。

4、编写顶层文件,实现VGA彩色信号显示控制器,并进行相关扩展(如图片显示等)。

第二部分系统设计2.1设计思路设计采用自顶向下(Top-down)的方法。

第一步:系统功能分析和描述VGA显示控制器实现的主要功能是向CRT显示器发出图形控制信号,产生相应的图形显示。

由此,容易得到系统结构框图,有关系统功能分析和输入输出约束。

第二步:系统层次模块划分由系统功能可以将系统从逻辑上划分为输入子系统、模式检测子系统和VGA控制子系统。

从系统逻辑结构出发,将系统设计为3层。

顶层用于描述整个系统的功能和运行;第二层承接顶层,负责实现系统中各个独立而完整的功能部分;第三层为第二层的子模块,用于扩展第二层的功能,具体负责用户模式的实现。

每个层次可用一个或多个具体模块加以实现。

控制器部分是系统的核心部分,负责协调和控制各子模块的工作。

控制器设计采用有限状态机的方法。

第三步:硬件语言描述在前述工作的基础上,采用VHDL语言对VGA显示控制器的三个层次依次进行描述,具体描述出每个模块,生成具体电路视图。

详述与2.3小节中。

第四步:仿真验证经过前三步之后,系统设计基本完成,需要对系统主要功能进行仿真验证,更进一步分析状态机、电路逻辑和时序配合等是否正确。

详述于2.4小节中。

2.2系统结构设计2.2.1系统结构框图图2.1 VGA显示控制器系统结构框图VGA显示控制器的输入是用户控制信息,如显示模式的切换命令、图形移动的控制命令等。

控制器根据用户的输入信息,决定工作模式,这里定义为横彩模式、纵彩模式、纯色模式、用户模式。

EDA-课程设计-VGA彩条信号发生器

1绪论1.1 背景如今人们的生活水平和质量不断提高,对生活设备的智能化程度的要求越来越高。

现代电子产品在性能提高、复杂度增大的同时,价格却一直呈下降趋势,而且产品更新换代的步伐也越来越快,实现这种进步的主要因素是生产制造技术和电子设计技术的发展。

前者以微细加工技术为代表,目前已进展到深亚微米阶段,可以在几平方厘米的芯片上集成数千万个晶体管。

后者的核心就是EDA技术,EDA是指以计算机为工作平台,融合应用电子技术、计算机技术、智能化技术最新成果而研制成的电子CAD通用软件包,主要能辅助进行三方面的设计工作:IC设计、电子电路设计、PCB设计。

没有EDA技术的支持,想要完成上述超大规模集成电路的设计制造是不可想象的,反过来,生产制造技术的不断进步又必将对EDA技术提出新的要求。

随着电子技术的发展和人们对电子设计开发的难度及周期要求,EDA技术必将广发应用于电子设计的各个领域,因此本设计也采用了EDA的设计方法,其设计的优越性明显高于传统的设计方法。

为了实现VGA彩色显示的原理,我们从本质上去认识了生成图像的原理,从而制造更多更复杂的元器件做铺垫,本设计立足系统可靠性及稳定性等高技术要求,采用FPGA芯片实现VGA显示屏控制电路,通过对接口的认识,我们知道了怎么去设置接口成像参数。

其电路设计比较简单,外围电路少,易于控制和检查,较传统的分离元件实现方式有着明显的优势,尤其是其设计电路实现周期,其抗干扰及调试过程都很简单。

1.2 EDA技术的发展趋势各科研院所和高等院校的实验教学和科研工作中 EDA 技术将得到广泛的应用。

由于可编程逻辑器件性能价格比的不断提高,开发软件功能的不断完善,而且由于用 EDA 技术设计电子系统具有用软件的方式设计硬件;设计过程中可用有关软件进行各种仿真; 系统可现场编程,在线升级;整个系统可集成在一个芯片上等特点,使其将广泛应用于专用集成电路和机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域新产品的开发研制中。

VGA彩条信号显示控制器设计解析

编号:EDA技术实训实训(论文)说明书题目:VGA彩条信号显示控制器设计院(系):信息与通信学院专业:电子信息工程学生姓名:***学号: ********** 指导教师:付强、陈小毛、归发第2013 年1 月4 日本设计采用EDA技术,通过FPGA芯片实现了实现VGA彩条信号的显示的设计,本文采用VHDL 硬件描述语言描述VGA彩条信号的显示电路,完成对电路的功能仿真。

通过按键来实现横彩条、竖彩条、棋盘式方格图案的选择。

显示图像分辨率为640×480,刷新率为60Hz。

与传统的设计方式相比,本设计由于采用了FPGA芯片来实现,它将大量的电路功能集成到一个芯片中,并且可以由用户自行设计逻辑功能,提高了系统的集成度和可靠性。

关键词:电子设计自动化、可编程门阵列、硬件描述语言、状态机This design used the EDA technology, through the FPGA chip realized the realization of the signal that striped VGA is adopted in this paper, the design of the VHDL hardware description language describe VGA striped signal display circuit and the completion of the function of the circuit simulation. By pressing buttons horizontal striped, perpendicular striped, chessboard type pane design choice. Display image resolution for 640 x 480, refresh rate of 60 Hz ac. Compared with the traditional design methods, the design with FPGA chip to achieve, it will be a lot of circuit function integration to a chip, and can be by the user to design logical function, improve the system integrity and reliability.Keywords:Electronic Design Automatic technology,Flied Programmable,Gate Array, Hardware Description Language, State Machine1. 绪论 (1)1.1 EDA技术的发展 (1)1.2 课程设计的任务 (1)2. 系统设计 (2)2.1 系统的工作原理 (2)2.2 VGA显示原理 (2)2.3 键盘驱动 (4)3 系统设计 (4)3.1图像信号产生模块的设计 (4)3.2 视频输出接口电路部分设计 (5)3.3 模式控制与显示部分设计 (6)3.4 VGA显示模块 (6)4 课程设计心得 (9)5 致谢 (10)参考文献 (11)附录 (12)附录A 总原理图 (12)附录B 实验现象 (12)附录C 引脚分布图 (14)附录D 实验程序 (14)1.绪论1.1 EDA技术的发展我们已经进入数字化和信息化的时代,其特点就是各种数字产品的广泛应用。

彩色电视机信号处理电路分析

彩色电视机信号处理电路分析彩色电视机信号处理电路是电视机中的核心部件之一,它负责接收、解码和处理来自广播信号或其他输入源的视频和音频信号,使其能够在电视屏幕上显示出清晰、鲜艳的彩色图像和清晰的声音。

本文将对彩色电视机信号处理电路的主要组成部分进行分析。

首先,彩色电视机信号处理电路包括视频信号处理电路和音频信号处理电路两部分。

视频信号处理电路主要包括以下几个组成部分:输入接口、视频解码器、图像处理电路和视频输出接口。

输入接口负责接收来自广播信号源或其他输入源的视频信号,并将其转换成数字信号传递给其他部分进行进一步处理。

在现代彩色电视机中,常用的输入接口为HDMI、AV输入口等。

视频解码器是视频信号处理电路中的关键部分,它负责将数字视频信号解码成RGB(红绿蓝)三个基本颜色信号,以及亮度和色度信号。

解码后的RGB信号和亮度色度信号经过处理后,可以描绘出彩色图像的每一个像素点。

图像处理电路是为了提高图像质量而设计的。

它可以对亮度、对比度、饱和度等图像参数进行调节,提高图像的清晰度和真实感。

常见的图像处理电路包括降噪电路、锐化电路、亮度调节电路等。

视频输出接口是将经过处理后的图像信号输出到电视屏幕上显示的部分。

常见的视频输出接口有VGA、HDMI等。

通过视频输出接口,图像处理电路可以将图像信号发送到显示屏幕上,并根据需要进行时序控制和调整。

音频信号处理电路主要包括音频解码器、音量控制电路和音频输出接口。

音频解码器负责将数字音频信号解码成左右声道的模拟音频信号。

通过音量控制电路,可以调节音频信号的音量大小。

音频输出接口用于将处理过的音频信号传递给扬声器或其他外部音频设备输出声音。

在彩色电视机信号处理电路中,各个组成部分紧密配合,相互协作,使得电视机能够正常工作,并显示出高质量的彩色图像和音频。

这些电路不仅需要具备高速、高精度的处理能力,还需要考虑功耗、成本、稳定性等因素。

综上所述,彩色电视机信号处理电路是电视机中的重要组成部分,通过接收、解码和处理视频和音频信号,实现了电视机图像和声音的高质量输出。

VGA彩条信号显示控制器设计

一、课程设计内容1、使用Verilog语言和Modelsim仿真器完成可显示横彩条、竖彩条、棋盘格相间的VGA控制器的设计和验证2、设计并验证可显示英语单词”HIT”的VGA控制器3、使用Quartus II和SOPC实验箱验证设计的正确性4、Verilog代码要符合微电子中心编码标准二、FPGA原理CPLD、FPGA是在PAL、GAL等基础上发展起来的一种具有丰富的可编程I/O 引脚、逻辑宏单元、门电路以及RAM空间的可编程逻辑器件,几乎所有应用门阵列、PLD和中小规模通用数字集成电路的场合均可应用FPGA和CPLD器件。

CPLD 的设计是基于乘积项选择矩阵来实现的,而FPGA基于查找表来设计的。

查找表就是实现将输入信号的各种组合功能以一定的次序写入RAM中,然后在输入信号的作用下,输出特定的函数运算结果。

其结构图如图1所示:图1. FPGA查找表单元一个N输入查找表(LUT,Look Up Table)可以实现N个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。

输入多于N个的函数、方程必须分开用几个查找表(LUT)实现(如图2所示)。

图2 FPGA查找表单元内部结构该系统设计中,FPGA芯片用的是ALTERA公司的EP1K30QC208-2,它的系统结构如图3所示。

它由若干个逻辑单元和中央布线池加I/O端口构成图3 EP1K30QC208内部结构三、VGA接口VGA的全称为Video Graphic Array,即显示绘图阵列。

在PC行业发展的初期,VGA以其支持在640X480的较高分辨率下同时显示16种色彩或256种灰度,同时在320X240分辨率下可以同时显示256种颜色的良好特性得到广泛支持。

后来,厂商们纷纷在VGA基础上加以扩充,如将显存提高至1M并使其支持更高分辨率如800X600或1024X768,这些扩充的模式就称之为VESA(Video Electronics Standards Association,视频电子标准协会)的Super VGA模式,简称SVGA,现在的显卡和显示器都支持SVGA模式。

实验九 VGA彩条信号显示

实验九VGA彩条信号显示控制器设计1.实验目的:学习VGA彩条信号发生器的设计。

2.实验内容设计并调试好一个VGA彩条信号发生器,并用EDA实验开发系统(拟采用的实验芯片的型号可选Altera CycloneII系列的EP2C5T144C8 FPGA,)进行硬件验证。

(1)R,G,B:三基色信号HS:行同步信号VS:场同步信号VGA工业标准要求的频率:时钟频率25.175MHz行频31469Hz场频59.94Hz(2)程序可参照书本P177(3)实验程序:通过对彩条模式选择按键的控制来改变彩条模式, 可产生竖彩条、横彩条、棋盘格等多种彩条模式。

出来的彩条信号并不是书里要求的按照横条,竖条,棋盘分布,而是按照棋盘,竖条,横条分布,原因是程序执行时是离进程最近的最先执行,可以通过修改程序把希望最先显示的信号放在离进程最近的地方。

由于受到存储器件容量的限制,本设计中存储的图像数据所采用的像素位深为3位,共可显示8种颜色。

在实际应用中,可以使用更大的存储器,最终实现256色图像,乃至真彩色图像的显示。

LIBRARY IEEE; -- 显示器彩条发生器USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COLOR ISPORT ( CLK, MD : IN STD_LOGIC;HS, VS, R, G, B : OUT STD_LOGIC ); -- 行场同步/红,绿,兰END COLOR;ARCHITECTURE behav OF COLOR ISSIGNAL HS1,VS1,FCLK,CCLK : STD_LOGIC;SIGNAL MMD : STD_LOGIC_VECTOR(1 DOWNTO 0);-- 方式选择SIGNAL FS : STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CC : STD_LOGIC_VECTOR(4 DOWNTO 0); --行同步/横彩条生成SIGNAL LL : STD_LOGIC_VECTOR(8 DOWNTO 0); --场同步/竖彩条生成 SIGNAL GRBX : STD_LOGIC_VECTOR(3 DOWNTO 1);-- X横彩条SIGNAL GRBY : STD_LOGIC_VECTOR(3 DOWNTO 1);-- Y竖彩条SIGNAL GRBP : STD_LOGIC_VECTOR(3 DOWNTO 1);SIGNAL GRB : STD_LOGIC_VECTOR(3 DOWNTO 1);BEGINGRB(2) <= (GRBP(2) XOR MD) AND HS1 AND VS1;GRB(3) <= (GRBP(3) XOR MD) AND HS1 AND VS1;GRB(1) <= (GRBP(1) XOR MD) AND HS1 AND VS1;PROCESS( MD )BEGINIF MD'EVENT AND MD = '0' THENIF MMD = "10" THEN MMD <= "00";ELSE MMD <= MMD + 1; --三种模式END IF;END IF;END PROCESS;PROCESS( MMD )BEGINIF MMD = "00" THEN GRBP <= GRBX; -- 选择横彩条ELSIF MMD = "01" THEN GRBP <= GRBY; -- 选择竖彩条ELSIF MMD = "10" THEN GRBP <= GRBX XOR GRBY; --产生棋盘格ELSEGRBP <= "000";END IF;END PROCESS;PROCESS( CLK )BEGINIF CLK'EVENT AND CLK = '1' THEN -- 12MHz 13分频IF FS = 12 THEN FS <= "0000";ELSEFS <= (FS + 1);END IF;END IF;END PROCESS;FCLK <= FS(3);PROCESS( FCLK )BEGINIF FCLK'EVENT AND FCLK = '1' THENIF CC = 29 THEN CC <= "00000";ELSECC <= CC + 1;END IF;END IF;END PROCESS;CCLK <= CC(4);PROCESS( CCLK )BEGINIF CCLK'EVENT AND CCLK = '0' THENIF LL = 481 THEN LL <= "000000000";ELSELL <= LL + 1;END IF;END IF;END PROCESS;PROCESS( CC,LL )BEGINIF CC > 23 THEN HS1 <= '0'; --行同步ELSEHS1 <= '1';END IF;IF LL > 479 THEN VS1 <= '0'; --场同步ELSEVS1 <= '1';END IF;END PROCESS;PROCESS(CC, LL)BEGINIF CC < 3 THEN GRBX <= "111"; -- 横彩条ELSIF CC < 6 THEN GRBX <= "110";ELSIF CC < 9 THEN GRBX <= "101";ELSIF CC < 12 THEN GRBX <= "100";ELSIF CC < 15 THEN GRBX <= "011";ELSIF CC < 18 THEN GRBX <= "010";ELSIF CC < 21 THEN GRBX <= "001";ELSE GRBX <= "000";END IF;IF LL < 60 THEN GRBY <= "111"; -- 竖彩条ELSIF LL < 120 THEN GRBY <= "110";ELSIF LL < 180 THEN GRBY <= "101";ELSIF LL < 240 THEN GRBY <= "100";ELSIF LL < 300 THEN GRBY <= "011";ELSIF LL < 360 THEN GRBY <= "010";ELSIF LL < 420 THEN GRBY <= "001";ELSE GRBY <= "000";END IF;END PROCESS;HS <= HS1 ; VS <= VS1 ;R <= GRB(2) ;G <= GRB(3) ; B <= GRB(1);END behav;选择模式5CLK 选CLOCK0 ,对应引脚PIN_89 选用12MHzMD 选PIN48 ,对应引脚PIN_8. 键1R 选PIN40 ,对应引脚PIN_99.G 选PIN41 ,对应引脚PIN_100 .B 选PIN42 ,对应引脚PIN_101.HS 选PIN43 ,对应引脚PIN_103VS 选PIN44 ,对应引脚PIN_104.由于本次实验要用到两台显示器,请1号机房的同学将编译成功仿真成功的代码拷贝到第21台电脑上运行。

EDA实验报告-VGA彩条显示

EDA技术实验报告—VGA彩条实验班级:光094-2姓名:……学号:4229VGA彩条信号显示控制一、实验目的:1. 熟练掌握Verilog HDL语言和QuartusII 软件的使用;2. 理解状态机的工作原理和设计方法;3. 熟悉VGA 接口协议规范。

4.通过对VGA接口的显示控制设计,理解VGA接口的时序工作原理,掌握通过计数器产生时序控制信号的方法以及用MEGEFUNCTION制作锁相环的方法。

二、实验原理1、显示控制原理常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

2、VGA时序信号计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B 三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

对于模拟显示设备,如模拟CRT 显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。

设计VGA 控制器的关键是产生符合VGA 接口协议规定的行同步和场同步信号,它们的时序关系如下图所示:h_sync:水平同步信号(负脉冲),每个水平扫描周期显示器刷新一行;v_sync:垂直同步信号(负脉冲),每个垂直扫描周期显示器刷新一帧;行同步信号(HS)场同步信号(VS)时序名称时钟数(像素数)时序名称行数前沿16 前沿10行同步96 场同步 2数据640 数据480后沿48 后沿33总像素数800 总行数525按照每秒60帧的刷新速度来计算,所需要的时钟频率为:频率=60Hz(帧数)×525(行)×800(每一行像素数)=25.2MHz所以我们通过开发系统的50MHz时钟资源,通过时钟分频产生25MHz的频率即可。

VGA彩条信号发生器__课程设计

VGA彩条信号发生器__课程设计目录1绪论 - 2 -1.1 EDA技术的介绍 - 2 -1.2 EDA技术的应用- 3 -1.3 EDA技术的发展- 3 -1.4 课程设计任务- 4 -2 系统总体方案设计- 5 -2.1 设计的主要内容- 5 -2.2 设计方案- 5 -2.3系统原理- 7 -3 系统模块设计- 9 -3.1 VGA时序控制器模块- 9 -3.2 彩条图形生成模块- 10 -3.3 显示模块- 10 -3.4 存储模块- 11 -4 程序设计- 11 -4.1 程序总体设计- 11 -4.2 按键模式选择程序设计- 12 -4.3 4*4键盘控制程序设计- 13 -4.4 16*16点阵显示程序设计 - 14 -5 总结- 15 -5.1设计小结- 15 -5.2致谢- 15 -参考文献- 16 -附录A 实验结果显示- 17 -附录B 电路原理图- 17 -附录C 源程序 - 19 -1绪论1.1 EDA技术的介绍20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

VGA彩条信号发生器

VGA彩条信号发生器作者:陆贵山来源:《商品与质量·学术观察》2012年第12期摘要:文章主要研究VGA显示器的接口控制器的原理,基于AT89S52的系统硬件设计,并探讨了其程序流程和系统调试。

关键词:VGA 彩条信号发生器随着现代电子技术的发展,越来越多的电子产品设备进入人们的日常生活、工业生产、科研教学。

电子设备在现代社会中具有无可代替的地位。

近几年,越来越多的娱乐电子产品进入人们眼中,例如,手机、MP3、MP4、GPS等。

在这些电子设备中都有一个共同部件——显示部件,当这些设备缺少了相应的显示就会变成一个人们很难使用的东西。

显示设备是人和机器交流的途径,人们可以通过显示设备知道机器做出了什么样的动作,是不是人们所预期的。

在以上所罗列的电子设备中所用到的显示设备都是比较小的,可以显示的信息有限,再显示更多的信息就无能为力了。

然而,标准的VGA显示器可以显示640X480个信息,因此,VGA显示器可以满足显示大量信息数据的要求。

因此,研究VGA显示器的接口控制器就显的很有价值,并且用单片机驱动VGA显示器的相关文献和资料非常少。

所以,本文介绍基于51系列单片机驱动VGA显示器的研究就显得相当有价值。

1、VGA显示原理VGA(Video Graphic Array)即视频图形阵列,具有分辨率高、显示速率快、颜色丰富等优点。

VGA 接口不但是CRT 显示设备的标准接口,同样也是LCD液晶显示设备的标准接口,作为一种标准的显示接口在视频和计算机领域得到了广泛的应用。

VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

CRT 显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT 屏幕上从左到右(受水平同步信号控制)、从上到下(受垂直同步信号控制)做有规律的移动。

光栅扫描又分逐行扫描和隔行扫描。

电子束采用光栅扫描方式,从屏幕左上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后,形成一场。

VGA彩条信号发生器的设计

VGA彩条信号发生器的设计一、实验目的1.了解普通显示器正确显示的时序。

2.了解VHDL产生VGA显示时序的方法。

3.进一步加强对FPGA的认识。

二、实验原理尽管显示器的新品层出不穷,但CRT(Cathode Ray Tube,阴极射线管)的基本工作原理一直沿用了几十年,直到今天也没有太大的变化。

显示器是一种复杂的设备,其扩展性和可靠性也十分惊人,在这一方面,电子控制起了很大的作用,任何机械都会有磨损,唯有用电子才能延长寿命,甚至能适应数千小时的工作。

电子枪是显示像管的核心,安发出的电子束击中光敏材料(荧光屏),刺激荧光粉就能产生图像。

实际上,电子枪和大体积的、功率强劲的二极管没有什么区别,其原理也适用于电视机和示波器。

CRT分为几个部分:Deflection Coil(偏转线圈)用于电子枪发射器的定位,它能够产生一个强磁场,通过改变强度来移动电子枪。

线圈偏转的角度有限,当电子束传播到一个平坦的表面时,能量会轻微的偏移目标,仅有部分荧光粉被击中,四边的图像会产生弯曲现象。

为了解决这个问题,显示器生产厂把显像管做成球形,让荧光粉充分地接受能量,缺点是屏幕将变得弯曲,电子束射击由左至右,由上至下的过程称为刷新,不断重复的刷新能保持图像的持续性。

显示器屏幕的色彩是由RGB(红、绿、蓝)三色光所合成的,我们可通过调整这三个基色调出其它的颜色,在许多图像处理软件里都有提供色彩调配功能,你可输入三基色的数值来调配颜色,也可直接根据软件提供的调色板来选择颜色。

在这一部分的功能上实验系统采用专用的编解码芯片来完成。

其具体实现、原理我们将在以后的实验中做详细的说明。

在本实验中只用到了RGB三基色来组成八种颜色构成彩条信号。

VGA显示器在显示过程中主要由五个信号来控制,分别是R、G、B、HS和VS。

其中R、G、B分别用来驱动显示器三个基色的显示,即红、绿和篮,HS是行同步信号,VS是场同步信号。

在做本实验时,由于没有任何显示器驱动,所以显示器工作在默认状态,分辨率:640×480,刷新率:60Hz。

VGA彩条信号发生器

FPGA课程设计报告—VGA彩条信号发生器学院:班级:学号:姓名:完成日期:目录一.设计课题背景 (2)二.设计要求 (2)三.设计原理 (2)四. 设计方案 (3)五. 电路图 (5)六. 结果图 (5)七. 实验心得 (7)附录 (8)一.设计背景实验设计了基于VHDL描述的VGA显示控制器,通过FPGA控制CRT显示器显示色彩和图形,完成的功能包括横向和纵向彩色条幅的显示以及正方形色块。

二.设计要求1. 熟练掌握 VHDL语言和QuartusII 软件的使用。

2. 理解状态机的工作原理和设计方法。

3. 熟悉 VGA 接口协议规范。

4. 通过对VGA接口的显示控制设计,理解VGA接口的时序工作原理。

5. 利用 FPGA 实现 VGA 彩条信号发生器.6. 可以产生彩色横条, 彩色竖条信号, 彩色棋盘格信号.7. 由一个按键按照顺序选择不同模式的信号输出.三.设计原理1、显示控制原理常见的彩色显示器一般由阴极射线管(CRT)构成,彩色由GRB(Green Red Blue)基色组成。

显示采用逐行扫描的方式解决,阴极射线枪发出电子束打在涂有荧光粉的荧光屏上,产生GRB基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间,CRT、对电子束进行消隐,每行结束时,用行同步信号进行行同步;扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

2、VGA时序信号计算机内部以数字方式生成的显示图像信息,被显卡中的数字/模拟转换器转变为R、G、B 三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

对于模拟显示设备,如模拟CRT 显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。

1、VGA彩条信号产生彩条信号产生模块包括了彩条模式控制、竖彩条发生、横彩条发生和棋盘格发生三个模块。

基于FPGA的VGA图象信号发生器设计

VGA(视频图形阵列)作为一种标准的显示接口在视频和计算机领域得到了广泛的应用。

VGA图像信号发生器是电视台、电视机生产企业、电视维修人员常用的仪器,其主要功能就是产生标准的图像测试信号。

VGA图像信号发生器的设计涉及到图像数据的处理,对电路的工作速度和性能要求较高,VGA工业标准要求的时钟频率高达25MHz,使用传统的电子电路设计方法是难以实现的。

采用专用的视频处理芯片,其设计技术难度大、开发成本高。

本文采用FPGA+MCU方案,利用了Cyclone系列的FPGA高达上百兆的工作频率特性为图像数据处理提供了良好的实时性,其内部集成的数字锁相环为系统的工作时钟提供的良好的稳定性,其内部嵌入的存储器可以存储一定容量的图像信息,丰富的I/O资源可以随即扩展外接大容量存储器的特性,因此由 FPGA完成对图像数据的处理及产生行场扫描时序信号。

很好地实现了图象数据处理的实时性和稳定性,达到了性能与价格的完美统一。

此外,FPGA的电路可重构性,为系统功能更改和升级以及功能扩展提供了很大的设计空间。

由微控制器完成功能设置与控制,如键盘扫描,模式选择与显示控制等。

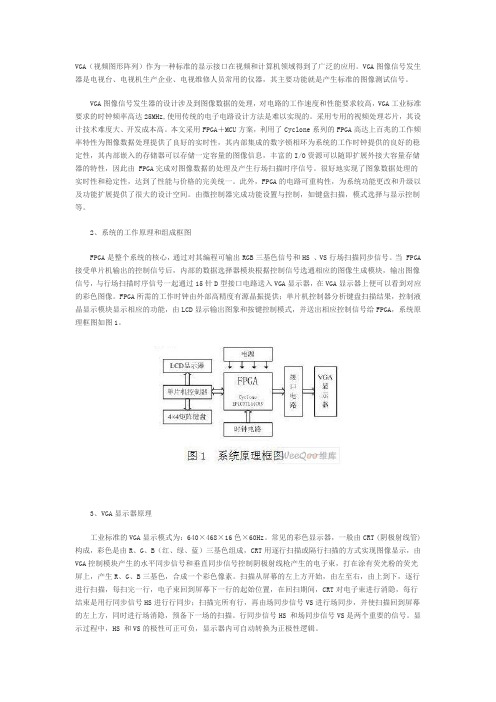

2、系统的工作原理和组成框图FPGA是整个系统的核心,通过对其编程可输出RGB三基色信号和HS 、VS行场扫描同步信号。

当 FPGA 接受单片机输出的控制信号后,内部的数据选择器模块根据控制信号选通相应的图像生成模块,输出图像信号,与行场扫描时序信号一起通过15针D型接口电路送入VGA显示器,在VGA显示器上便可以看到对应的彩色图像。

FPGA所需的工作时钟由外部高精度有源晶振提供;单片机控制器分析键盘扫描结果,控制液晶显示模块显示相应的功能,由LCD显示输出图象和按键控制模式,并送出相应控制信号给FPGA,系统原理框图如图1。

3、VGA显示器原理工业标准的VGA显示模式为:640×468×16色×60Hz。

常见的彩色显示器,一般由CRT (阴极射线管)构成,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描或隔行扫描的方式实现图像显示,由VGA控制模块产生的水平同步信号和垂直同步信号控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA课程设计报告—VGA显示器彩色信号发生器电路班级:08通信A班姓名:崔儒学号: 0815231013指导老师:凌朝东摘要:VGA(Video Graphic Array)接口是与显示器进行通信的唯一接口。

通过FPGA器件控制RGB信号、行同步信号、场同步信号等信号,并参照有关标准,最后可以实现对VGA显示器的控制。

本设计与传统的图像显示方法不同,为节省储存空间在设计中采用R、G、B三种基色利用FPGA芯片和EDA设计方法,可以显示8种颜色,设计出针对性强的VGA显示控制器,而且不需要依靠计算机,既能够大大降低成本,又可以满足生产实践中不断变化的需要,同时产品的升级换代也方便迅速。

本设计采用Altera公司的EDA软件0uartus II,并以Cylone 系列FPGA器件为硬件平台进行系统设计。

关键词:VGA;FPGA:VHDL;Ouartus II目录1、系统设计 (4)2、单元电路设计 (6)3、软件设计 (8)4、系统测试 (11)5、小结 (12)6、参考文献 (12)7、附录 (13)一、系统设计1、设计要求:VGA显示器彩色信号发生器电路,能在VGA显示器上显示8种颜色的图形(条型、方块型)。

2、系统设计方案:方案一:采用传统的图像显示方法,将图像数据传回电脑在传输过程中通过CPU对图像数据信号进行控制,通过显示器显示出来。

方案二:采用FPGA和EDA的设计方法,通过FPGA器件控制RGB信号、行同步信号、场同步信号等信号,并参照有关标准,最终可以实现对VGA 的控制。

方案一为传统的图像显示方法,在传输过程中需要CPU不断对图像数据信号进行控制,这样就造成了CPU的浪费,同时系统还需要依赖电脑,降低了系统的灵活性。

方案二是利用可编程器件FPGA和EDA的设计方法,可以根据设计的需要设计出针对性比较强的VGA显示器,而且不需要依靠计算机,大大降低了成本提高了系统的灵活性。

综合上诉分析本设计中采用方案二。

3、系统的工作原理:计算机显示器的显示有许多接口标准,常见的有VGA、SVGA等。

VGA接口,也叫D-Sub接口,是15针的梯形插头,分成3排,每排5个,传输模拟信号。

VGA接口采用非对称分布的15针连接方式,其工作原理是:将显存内以数字格式存储的图像(帧)信号在RAMDAC里经过模拟调制成模拟高频信号,然后再输出到显示设备成像。

VGA支持在640 X480的较高分辨率下同时显示16种色彩或256种灰度,同时在320×240分辨率下可以同时显示256种颜色。

常见的彩色显示器一般由CRT(阴极射线管)够成,彩色是有R、G、B(红:Red,绿:Green,蓝:Blue)三基色组成,用逐行扫描的方式解决图像显示。

阴极射线枪发出的电子束打在涂有荧光粉的屏幕上,产生R、G、B三基色,合成一个彩色像素。

扫描从屏幕的左上方开始,从左到右,从上到下,逐行扫描,每扫完一行,电子束回到屏幕的左边下一行的起始位置,在这期间对电子束进行行消隐,每行结束时,用行同步信号进行行同步,扫描完所有行,用场同步信号进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,并预备进行下一次的扫描。

在本设计中采用普通的VGA显示器,一共引出5条信号线:R、G、B:三基色信号;HS:行同步信号;VS:场同步信号。

在设计过程中严格按照VGA的工业标准要求进行设计,其中时钟频率为25.175MHZ,行频为31469HZ,场频为59.94HZ。

4、实现电路:二、单元电路设计1、时序信号的产生图片要想在显示器上显示出来,它主要需要5个信号,行同步信号HS(Hor i Zontal—Sync)、场同步信号VS(Vertical—Sync)和RGB三基色信号。

VGA时序控制模块是整个显示控制器的关键部分,最终输出的行、场同步信号必须严格按照VGA时序标准产生相应的脉冲信号。

图1和图2所示为行扫描和场扫描的时序图。

图1行扫描时序示意图图2场扫描时序示意图对此5个信号的时序驱动,VGA显示器也要严格遵守“VGA-I-业标准”即640×480 X 60Hz模式,否则会损害V6A显示器。

行、场扫描时序要求如表1和表2所示。

表1 行扫描时序要求:(单位:像素即输出一个像素PixeI的时间间隔)表2 场扫描时序要求:(单位:行即每输出一行line的时间间隔)VGA的工业标准显示模式要求行同步和场同步都为负极性,即同步头脉冲要求是负脉冲。

对于一些VGA显示器,HS和VS的极性可正可负,显示器内可以自动转换为正极性逻辑。

在图1和图2中,R、G、B为正极性信号即高电平有效。

当VS=0、HS=1时,CRT现实的内容为亮的过程,即正向扫描过程约为26us。

当一行扫描完毕,行同步HS=1,约需6us。

期间,CRT扫描产生消隐,电子束回到CRT左边下一行的起始位置(X=0,Y=1);当扫描完480行后,CRT的场同步VS=1,产生场同步使扫描线回到CRT的第一行第一列(X=0,Y=0)处(约为两个行周期)。

2、彩色信号的生成本设计中采用3位数字表达式R、G、B(纯数字方式)三种基色,可以显示8中颜色,表三是此八种颜色的对应的编码电平。

利用数字逻辑关系将R、G、B进行逻辑运算便可得到显示的图形。

表三颜色编码3、显示控制模块经编译后的彩条信号经过显示模块处理后送到显示器进行显示。

利用行、场同步信号的计数器,在图像有效区间内按照图片的大小划定行和列的起始坐标和终止坐标。

本设计使用和行、场计数器相同频率的时钟信号作为图像地址计数器的时钟,当扫描信号到达显示图片的区间时,图像地址计数器开始计数,同时从相应位置读出数据送往显示器进行显示,显示模块的输出直接连到VGA的接口。

在设计中还增加了一个模式选择按键MD,用来控制图像的显示模式,本设计中共有6中显示变化的图像如表4所示。

表4 彩色信号发生器的显示模式三、软件设计本设计采用Altera公司的EDA软件0uartusII,采用VHDL语言进行软件程序的编写,来实现VGA彩条信号显示控制器的设计。

流程图为具体程序为:LIBRARY IEEE; -- VGA显示器彩条发生器USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COLOR ISPORT ( CLK, MD : IN STD_LOGIC;HS, VS, R, G, B : OUT STD_LOGIC );-- 行场同步/红,绿,蓝END COLOR;ARCHITECTURE behav OF COLOR ISSIGNAL HS1,VS1,FCLK,CCLK : STD_LOGIC;SIGNAL MMD : STD_LOGIC_VECTOR(1 DOWNTO 0);-- 方式选择SIGNAL FS : STD_LOGIC_VECTOR (3 DOWNTO 0);SIGNAL CC : STD_LOGIC_VECTOR(4 DOWNTO 0); --行同步/横彩条生成SIGNAL LL : STD_LOGIC_VECTOR(8 DOWNTO 0); --场同步/竖彩条生成 SIGNAL GRBX : STD_LOGIC_VECTOR(3 DOWNTO 1);-- X横彩条SIGNAL GRBY : STD_LOGIC_VECTOR(3 DOWNTO 1);-- Y竖彩条SIGNAL GRBP : STD_LOGIC_VECTOR(3 DOWNTO 1);SIGNAL GRB : STD_LOGIC_VECTOR(3 DOWNTO 1);BEGINGRB(1) <= (GRBP(1) XOR MD) AND HS1 AND VS1;GRB(2) <= (GRBP(2) XOR MD) AND HS1 AND VS1;GRB(3) <= (GRBP(3) XOR MD) AND HS1 AND VS1;PROCESS( MD )BEGINIF MD'EVENT AND MD = '0' THENIF MMD = "10" THEN MMD <= "00";ELSE MMD <= MMD + 1;END IF; --三种模式END IF;END PROCESS;PROCESS( MMD )BEGINIF MMD = "00" THEN GRBP <= GRBX; -- 选择横彩条ELSIF MMD = "01" THEN GRBP <= GRBY; -- 选择竖彩条ELSIF MMD = "10" THEN GRBP <= GRBX XOR GRBY; --产生棋盘格 ELSE GRBP <= "000";END IF;END PROCESS;PROCESS( CLK )BEGINIF CLK'EVENT AND CLK = '1' THEN -- 12MHz 13分频IF FS = 12 THEN FS <= "0000";ELSE FS <= (FS + 1);END IF;END IF;END PROCESS;FCLK <= FS(3); CCLK <= CC(4);PROCESS( FCLK )BEGINIF FCLK'EVENT AND FCLK = '1' THENIF CC = 29 THEN CC <= "00000";ELSE CC <= CC + 1;END IF;END IF;END PROCESS;PROCESS( CCLK )BEGINIF CCLK'EVENT AND CCLK = '0' THENIF LL = 481 THEN LL <= "000000000";ELSE LL <= LL + 1;END IF;END IF;END PROCESS;PROCESS( CC,LL )BEGINIF CC > 23 THEN HS1 <= '0'; --行同步ELSE HS1 <= '1'; END IF;IF LL > 479 THEN VS1 <= '0'; --场同步ELSE VS1 <= '1'; END IF;END PROCESS;PROCESS(CC, LL)BEGINIF CC < 3 THEN GRBX <= "111"; -- 横彩条ELSIF CC < 6 THEN GRBX <= "110";ELSIF CC < 9 THEN GRBX <= "101";ELSIF CC < 12 THEN GRBX <= "100";ELSIF CC < 15 THEN GRBX <= "011";ELSIF CC < 18 THEN GRBX <= "010";ELSIF CC < 21 THEN GRBX <= "001";ELSE GRBX <= "000";END IF;IF LL < 60 THEN GRBY <= "111"; -- 竖彩条ELSIF LL < 120 THEN GRBY <= "110";ELSIF LL < 180 THEN GRBY <= "101";ELSIF LL < 240 THEN GRBY <= "100";ELSIF LL < 300 THEN GRBY <= "011";ELSIF LL < 360 THEN GRBY <= "010";ELSIF LL < 420 THEN GRBY <= "001";ELSE GRBY <= "000";END IF;END PROCESS;HS <= HS1 ; VS <= VS1 ;R <= GRB(2) ;G <= GRB(3) ; B <= GRB(1); END behav;四、系统测试采用Cylone系列FPGA器件为硬件平台进行系统测试,芯片型号为EP2C5T144C8。