sp enhanced 综述

老年人中的炎性肠病

第1期超声造影在肝脏肿瘤的应用研究进展肝脏疾病的评估过程中发挥更加巨大的作用。

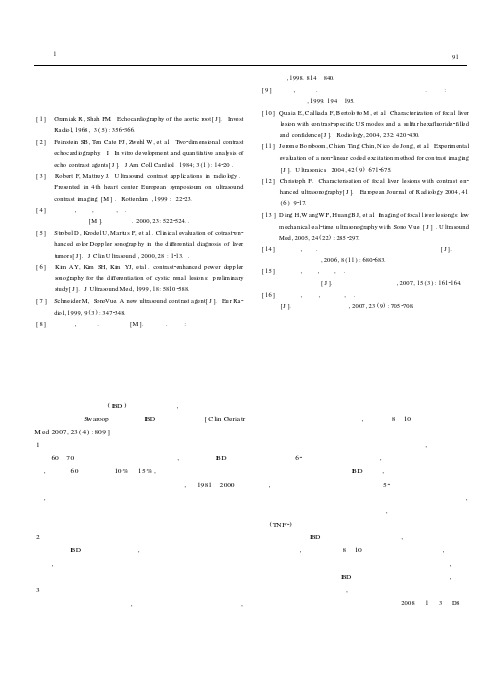

参考文献[1] Gra m iak R,Shah P M.Echocardi ograp hy of the aortic root[J].InvestRadi o l,1968,3(5):3562366.[2] Feinstei n S B,Ten Cate FJ,Z wehl W,et al.T wo2di m ensi onal contrastechocard i ography.I.In vitro devel opment and quan tit ative anal ysis ofecho contrast agents[J].J Am Coll Card i ol.1984;3(1):14220. [3] Robert F,Mattrey J.U ltras ound contrast app li cati ons i n radi o l ogy.Pres ented in4th heart center European s ymposi oum on ultras oundcontrast i magi ng[M].Rotterda m,1999:22223.[4] 王文平,齐青,季正标,等.经周围静脉超声造影在肝内占位性病变中的应用[M].上海医学.2000,23:5222524..[5] Str obel D,Krodel U,Mart u s P,et al.Cl i n i cal evaluati on of cotrast2en2hanced c o l or Dopp ler s onograp hy i n the d i fferential diagnosis of li vert umors[J].J C lin U ltras ound,2000,28:1213..[6] Ki m AY,Ki m S H,Ki m YJ,etal.contrast2enhanced power dopp lers onography for the d i fferentiati on of cystic renal lesi on s:p reli m i narys tudy[J].J Ultras ound Med,1999,18:58102588.[7] SchneiderM,S onoVue.A new ultras ound cont rast agent[J].Eu r Ra2di o l,1999,9(3):3472348.[8] 周永昌,郭万学.超声医学[M].第三版.北京:科学技术文献出版社,1998.814~840.[9] 唐杰,董宝玮.腹部和外周血管彩色多普勒诊断学.北京:人民卫生出版社,1999.194~195.[10]Quaia E,C al li ada F,B ertol o tt o M,et al.Charact eri zati on of focal li verl esi on with c on trast2s p ecific US modes and a s u l fu r hexafluoride2fi ll ed and confidence[J].Rodi o l ogy,2004,232:4202430.[11]J er om e Bo rs boom,C hien Ting Chin,N i co de Jong,et al.Experi m entaleval uati on of a non2linear coded excitati on m ethod for con tras t i magi ng [J].U ltras onics.2004,42(9)6712675.[12]Ch rist oph F.Characterisat i on of focal liver lesi ons with contrast en2hanced ultras onography[J].Eu r opean Journal of R ad i ol ogy2004,41(6)9217.[13]D ing H,W angWP,HuangB J,et al.I m aging of focal l i ver lesi ongs:l owm echanical eal2ti me u ltras onography wi t h Sono Vue[J].U ltras ound Med,2005,24(22):2852297.[14]张不林,胡兵.超声造影在肝脏功能成像上的研究进展[J].临床超声医学杂志,2006,8(11):6802683.[15]于小玲,梁萍,唐杰,等.实时超声造影技术在诊断肝脏微小局灶性病变的价值[J].中国医学影像学杂志,2007,15(3):1612164. [16]王知力,唐杰,李俊来,等.肝脏局灶性病变超声造影误诊分析[J].中国超声医学杂志,2007,23(9):7052708.老年人中的炎性肠病 老年人炎性肠病(I BD)具有许多特点,最近美国德州大学西南医学中心S waroop对老年人I BD进行了综述。

SP488E中文资料

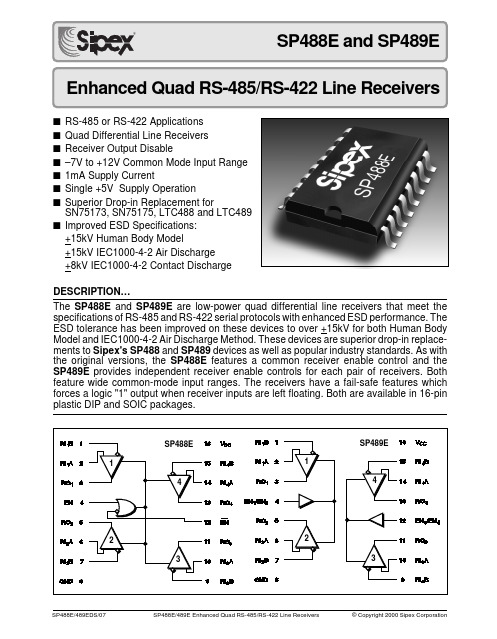

s RS-485 or RS-422 Applications s Quad Differential Line Receivers s Receiver Output Disables –7V to +12V Common Mode Input Range s 1mA Supply Currents Single +5V Supply Operation sSuperior Drop-in Replacement forSN75173, SN75175, LTC488 and LTC489s Improved ESD Specifications:+15kV Human Body Model+15kV IEC1000-4-2 Air Discharge +8kV IEC1000-4-2 Contact DischargeDESCRIPTION…The SP488E and SP489E are low-power quad differential line receivers that meet the specifications of RS-485 and RS-422 serial protocols with enhanced ESD performance. The ESD tolerance has been improved on these devices to over +15kV for both Human Body Model and IEC1000-4-2 Air Discharge Method. These devices are superior drop-in replace-ments to Sipex's SP488 and SP489 devices as well as popular industry standards. As with the original versions, the SP488E features a common receiver enable control and the SP489E provides independent receiver enable controls for each pair of receivers. Both feature wide common-mode input ranges. The receivers have a fail-safe features which forces a logic "1" output when receiver inputs are left floating. Both are available in 16-pin plastic DIP and SOIC packages.ABSOLUTE MAXIMUM RATINGSThese are stress ratings only and functionaloperation of the device at these or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.V CC ..................................................................+7V Input VoltagesLogic....................................–0.5V to (V CC +0.5V) Receiver .....................................................+14V Receiver Output Voltage........–0.5V to (V CC +0.5V)Input CurrentsLogic........................................................+25mA Storage Temperature .................–65°C to +150°C Power DissipationPlastic DIP..............................................375mW (derate 7mW/°C above +70°C)Small Outline ..........................................375mW (derate 7mW/°C above +70°C)Lead Temperature (soldering, 10 sec).........300°CSPECIFICATIONSV= 5V ±5%; typicals at 25°C; T ≤ T ≤ T unless otherwise noted.元器件交易网Figure 1. Timing Test Circuit Figure 2. Enable/Disable Timing Test CircuitPin 6 — RI 2A — Receiver 2 input A.Pin 7 — RI 2B — Receiver 2 input B.Pin 8 — GND — Digital Ground.Pin 9 — RI 3B — Receiver 3 input B.Pin 10 — RI 3A — Receiver 3 input A.Pin 11 — RO 3 — Receiver 3 Output — If Receiver 3 output is enabled, if RI 3A > RI 3B by 200mV, Receiver 3 output is high. If Receiver 3output is enabled, and if RI 3A < RI 3B by 200mV,Receiver 3 output is low.Pin 12 — EN — Receiver Output Enable. Please refer to SP488E Truth Table (1).SP488 PINOUTPin 1 — RI 1B — Receiver 1 input B.Pin 2 — RI 1A — Receiver 1 input A.Pin 3 — RO 1 — Receiver 1 Output — If Receiver 1 output is enabled, if RI 1A > RI 1B by 200mV, Receiver output is high. If Receiver 1output is enabled, and if RI 1A < RI 1B by 200mV,Receiver 1 output is low.Pin 4 — EN — Receiver Output Enable. Please refer to SP488E Truth Table (1).Pin 5 — RO 2 — Receiver 2 Output —If Receiver 2 output is enabled, if RI 2A > RI 2B by 200mV, Receiver 2 output is high. If Receiver 2 output is enabled, and if RI 2A < RI 2B by 200mV, Receiver 2 output is low.PINOUTPin 13 — RO 4 — Receiver 4 Output — If Receiver 4 output is enabled, if RI 4A > RI 4B by 200mV, Receiver 4 output is high. If Receiver 4output is enabled, and if RI 4A < RI 4B by 200mV, Receiver 4 output is low.Pin 14 — RI 4A — Receiver 4 input A.Pin 15 — RI 4B — Receiver 4 input B.Pin 16 — Supply Voltage V CC — 4.75V ≤ V CC ≤5.25V.SP489E PINOUTPin 1 — RI 1B — Receiver 1 input B.Pin 2 — RI 1A — Receiver 1 input A.Pin 3 — RO 1 —Receiver 1 Output — If Receiver 1 output is enabled, if RI 1A > RI 1B by 200mV, Receiver output is high. If Receiver 1output is enabled, and if RI 1A < RI 1B by 200mV,Receiver 1 output is low.Pin 4 — EN1/EN2 — Receiver 1 and 2 Output Enable. Please refer to SP489E Truth Table (2).Pin 5 — RO 2 — Receiver 2 Output — If Receiver 2 output is enabled, if RI 2A > RI 2B by 200mV, Receiver 2 output is high. If Receiver 2output is enabled, and if RI 2A < RI 2B by 200mV, Receiver 2 output is low.Pin 6 — RI 2A — Receiver 2 input A.Pin 7 — RI 2B — Receiver 2 input B.Pin 8 — GND — Digital Ground.DIFFERENTIALENABLES OUTPUT A – B EN EN ROV ID ≥ 0.2V H X H X L H –0.2V < V ID < +0.2VH X X X L X V ID ≤ 0.2VH X L X L L XLHHi–ZTable 1. SP488E Truth Table Pin 9 — RI 3B — Receiver 3 input B.Pin 10 — RI 3A — Receiver 3 input A.Pin 11 — RO 3 — Receiver 3 Output — If Receiver 3 output is enabled, if RI 3A > RI 3B by 200mV, Receiver 3 output is high. If Receiver 3output is enabled, and if RI 3A < RI 3B by 200mV, Receiver 3 output is low.Pin 12 — EN3/EN4 — Receiver 3 and 4 Output Enable. Please refer to SP489E Truth Table (2).Pin 13 — RO 4 — Receiver 4 Output — If Receiver 4 output is enabled, if RI 4A > RI 4B by 200mV, Receiver 4 output is high. If Receiver 4output is enabled, and if RI 4A < RI 4B by 200mV, Receiver 4 output is low.Pin 14 — RI 4A — Receiver 4 input A.Pin 15 — RI 4B — Receiver 4 input B.Pin 16 — Supply Voltage V CC — 4.75V ≤ V CC ≤5.25V.Table 2. SP489E Truth TableDIFFERENTIALENABLESOUTPUT A – B EN 1/EN 2 or EN 3/EN 4ROV ID ≥ 0.2V H H –0.2V < V ID < +0.2VH X V ID ≤ 0.2VH L XLHi–ZFEATURES…The SP488E and SP489E are low–power quad differential line receivers meeting RS-485 and RS-422 standards. The SP488E features active high and active low common receiver enable controls; the SP489E provides independent,active high receiver enable controls for each pair of receivers. Both feature tri–state outputs and a -7V to +12V common–mode input range permitting a +7V ground difference between devices on the communications bus. The SP488E/489E are equipped with a fail–safe feature which forces a logic high at the receiver output when the input is left floating. Data rates up to 10Mbps are supported. Both are available in 16-pin plastic DIP and SOIC packages.元器件交易网Figure 4. Receiver Enable/Disable TimingFigure 3. Receiver Propagation DelaysAC PARAMETERSV CC = 5V ±5%; typicals at 25°C; T AMB = 25°C unless otherwise noted.元器件交易网Figure 5. ESD Test Circuit for Human Body ModelFigure 6. ESD Test Circuit for IEC1000-4-2 ESD TOLERANCEThe SP488E and SP489E devices incorporate ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static discharges and associated transients. The improved ESD tolerance is at There are different methods of ESD testing applied:a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Dischargec) IEC1000-4-2 Direct Contact The Human Body Model has been the generally accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 5. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently. The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outsideFigure 7. ESD Test Waveform for IEC1000-4-2t=0nst=30ns0A15A30At ¥i ¥environment and human presence. The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage. The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2 is shown on Figure 6. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT)through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system.This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage. Variables with an air discharge such as approach speed of the object carrying the ESDpotential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.The Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit model in Figures 5 and 6 represent the typical ESD testing circuit used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on.Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S , the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2switch is pulsed so that the device under test receives a duration of voltage.For the Human Body Model, the current limiting resistor (R S ) and the source capacitor (C S ) are 1.5kW an 100pF, respectively. For IEC-1000-4-2,the current limiting resistor (R S ) and the source capacitor (C S ) are 330W an 150pF, respectively.The higher C S value and lower R S value in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.DEVICE PIN HUMAN BODY IEC1000-4-2 TESTED MODEL Air Discharge Direct Contact LevelDriver Outputs +15kV +15kV +8kV 4Receiver Inputs +15kV+15kV +8kV 4Table 3. Transceiver ESD Tolerance Levels元器件交易网ORDERING INFORMATIONQuad RS485 Receivers:Model........................Enable/Disable......................................Temperature Range........................Package mon; active Low and Active High..0°C to +70°C....................16–pin Plastic DIP mon; active Low and Active High..0°C to +70°C.............................16–pin SOIC mon; active Low and Active High..–40°C to +85°C................16–pin Plastic DIP mon; active Low and Active High..–40°C to +85°C.........................16–pin SOICSP489ECP...............One per driver pair; active High............0°C to +70°C....................16–pin Plastic DIP SP489ECT................One per driver pair; active High............0°C to +70°C.............................16–pin SOIC SP489EEP................One per driver pair; active High............–40°C to +85°C................16–pin Plastic DIP SP489EET................One per driver pair; active High............–40°C to +85°C.........................16–pin SOICSipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.。

离子液体强化不饱和键差异化合物分离的研究进展

化工进展Chemical Industry and Engineering Progress2024 年第 43 卷第 1 期离子液体强化不饱和键差异化合物分离的研究进展容凡丁1,丁泽相1,曹义风1,2,陈俐吭1,2,杨柳1,2,申福星1,2,杨启炜1,2,鲍宗必1,2(1 浙江大学化学工程与生物工程学院,浙江 杭州 310058;2 浙江大学衢州研究院,浙江 衢州 324000)摘要:结构相似物的分离是物耗和能耗最集中的化工过程之一。

对于具有不饱和键差异的化合物而言,它们的物化性质极为相近,高效分离极具挑战。

离子液体因其特殊的理化性质、结构可设计以及多重分子间相互作用位点等特点而广泛应用于不饱和键差异化合物的分子辨识分离。

本文综述了离子液体强化不饱和键差异化合物分离的研究进展,重点介绍了常温常压下为气态的低碳烃、液态的中等碳链烃及固态的天然活性同系物等代表性体系的分离,突出了离子液体分离不饱和键差异化合物的构效关系、分离机理及分离工艺流程评价,并展望了离子液体强化不饱和键差异化合物分离的未来方向。

关键词:离子液体;分子辨识分离;萃取;选择性;不饱和键中图分类号:TQ028.8 文献标志码:A 文章编号:1000-6613(2024)01-0198-17Progress in enhanced separation of compounds differing in unsaturatedbonds by ionic liquidsRONG Fanding 1,DING Zexiang 1,CAO Yifeng 1,2,CHEN Lihang 1,2,YANG Liu 1,2,SHEN Fuxing 1,2,YANG Qiwei 1,2,BAO Zongbi 1,2(1 College of Chemical and Biological Engineering, Zhejiang University, Hangzhou 310058, Zhejiang, China; 2 Institute ofZhejiang University-Quzhou, Quzhou 324000, Zhejiang, China)Abstract: The separation of structurally similar compounds represents one of the most energy-intensiveprocesses, particularly for compounds that differ in unsaturated bonds. This challenge arises from their extremely similar physicochemical properties. Ionic liquids (ILs) have emerged as promising candidates for the separation of compounds with different unsaturated bonds through molecular recognition, which is mainly attributed to the unique physicochemical properties of ILs, their designable structures, and their ability to facilitate multiple intermolecular interactions. This work aims to provide a comprehensive review of the progress of utilizing ILs for the separation of compounds with disparities in unsaturated bonds. It presents a detailed analysis of some representative systems, including gaseous light hydrocarbons, liquid-state medium-chain hydrocarbons, and solid-state natural active compounds. This review highlights the relationship between the molecular structure and separation efficiency, elucidates the underlyingseparation mechanisms, and evaluates the effectiveness of the separation process. Furthermore, it brieflydiscusses the future trend in the design and optimization of ILs for this specific area.特约评述DOI :10.16085/j.issn.1000-6613.2023-1489收稿日期:2023-08-28;修改稿日期:2023-12-01。

SP485E中文资料

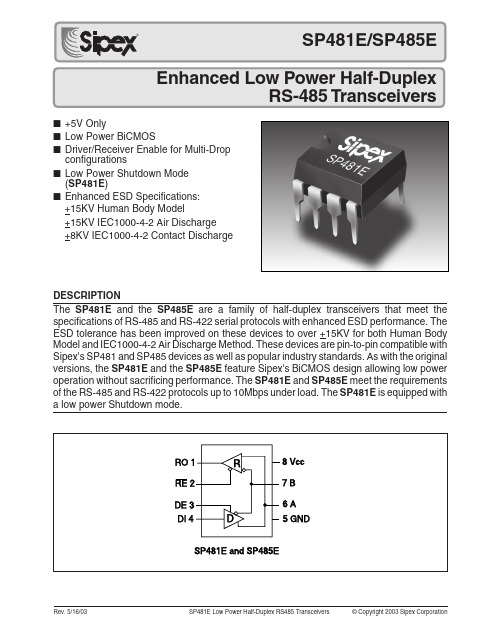

■+5V Only■Low Power BiCMOS■Driver/Receiver Enable for Multi-Drop configurations■Low Power Shutdown Mode (SP481E )■Enhanced ESD Specifications:DESCRIPTIONThe SP481E and the SP485E are a family of half-duplex transceivers that meet the specifications of RS-485 and RS-422 serial protocols with enhanced ESD performance. The ESD tolerance has been improved on these devices to over +15KV for both Human Body Model and IEC1000-4-2 Air Discharge Method. These devices are pin-to-pin compatible with Sipex's SP481 and SP485 devices as well as popular industry standards. As with the original versions, the SP481E and the SP485E feature Sipex's BiCMOS design allowing low power operation without sacrificing performance. The SP481E and SP485E meet the requirements of the RS-485 and RS-422 protocols up to 10Mbps under load. The SP481E is equipped with a low power Shutdown mode.+15KV Human Body Model+15KV IEC1000-4-2 Air Discharge +8KV IEC1000-4-2 Contact DischargeABSOLUTE MAXIMUM RATINGSThese are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.V CC ............................................................................................................+7V Input VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers..................................................-0.3V to (V CC +0.5V)Receivers................................................................. ±15VSPECIFICATIONST MIN to T MAX and V CC = 5V ± 5% unless otherwise noted.PARAMETERSMIN.TYP.MAX.UNITS CONDITIONSSP481E/SP485E DRIVER DC CharacteristicsDifferential Output Voltage GND V CC Volts Unloaded; R = ∞; see Figure 1Differential Output Voltage 2V CC Volts with load; R = 50Ω; (RS-422);see Figure 1Differential Output Voltage 1.5V CC Volts with load; R = 27Ω; (RS-485);see Figure 1Change in Magnitude of Driver Differential Output Voltage for Complimentary States 0.2Volts R = 27Ω or R = 50Ω; see Figure 1Driver Common-Mode Output Voltage 3Volts R = 27Ω or R = 50Ω; see Figure 1Input High Voltage 2.0Volts Applies to DE, DI, RE Input Low Voltage 0.8Volts Applies to DE, DI, RE Input Current±10µA Applies to DE, DI, RE Driver Short-Circuit Current V OUT = HIGH ±250mA -7V ≤ V O ≤ +12V V OUT = LOW±250mA-7V ≤ V O ≤ +12VSP481E/SP485E DRIVER AC Characteristics Maximum Data Rate 10Mbps RE = 5V, DE = 5V; R DIFF = 54Ω,C L1 = C L2 = 100pFDriver Input to Output 203060ns t PLH ; R DIFF = 54Ω, C L1 = C L2 = 100pF;see Figures 3 and 5Driver Input to Output 203080ns t PLH ; R DIFF = 54Ω, C LI = C L2 = 100pF;(SP485EMN ONLY)See Figures 3 and 5Driver Input to Output 203060ns t PHL ; R DIFF = 54Ω, C L1 = C L2 = 100pF;see Figures 3 and 5Driver Input to Output 203080ns t PHL ; R DIFF = 54Ω, C L1 = C L2 = 100pF;(SP485EMN ONLY)see Figures 3 and 5Driver Skew510ns see Figures 3 and 5,t SKEW = | t DPLH - t DPHL |Driver Rise or Fall Time 31540ns From 10% to 90%; R DIFF = 54Ω,C L1 = C L2 = 100pF; s ee Figures 3 & 6Driver Enable to Output High 4070ns C L = 100pF; see Figures 4 & 6; S 2closedDriver Enable to Output Low 4070ns C L = 100pF; see Figures 4 & 6; S 1closedDriver Disable Time from Low 4070ns C L = 100pF; see Figures 4 & 6; S 1closedDriver Disable Time from High 4070nsC L = 100pF; see Figures 4 & 6; S 2closedOutput VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers...................................................................... ±15V Receivers............................................-0.3V to (V CC +0.5V)Storage Temperature.......................................................-65˚C to +150˚C Power Dissipation per Package8-pin NSOIC (derate 6.60mW/o C above +70o C)...........................550mW 8-pin PDIP (derate 11.8mW/o C above +70o C)............................1000mW元器件交易网SPECIFICATIONS (continued)T MIN to T MAX and V CC = 5V ± 5% unless otherwise noted.PARAMETERS MIN.TYP.MAX.UNITS CONDITIONSSP481E/SP485E RECEIVER DC CharacteristicsDifferential Input Threshold -0.2+0.2Volts -7V ≤ V CM ≤ +12V Differential Input Threshold -0.4+0.4Volts -7V ≤ V CM ≤ +12V (SP485EMN ONLY)Input Hysteresis 20mV V CM = 0VOutput Voltage High 3.5Volts I O = -4mA, V ID = +200mV Output Voltage Low0.4Volts I O = +4mA, V ID = -200mVThree-State (High Impedance)Output Current ±1µA 0.4V ≤ V O ≤ 2.4V; RE = 5V Input Resistance 1215k Ω-7V ≤ V CM ≤ +12VInput Current (A, B); V IN = 12V +1.0mA DE = 0V, V CC = 0V or 5.25V, V IN = 12V Input Current (A, B); V IN = -7V -0.8mA DE = 0V, V CC = 0V or 5.25V, V IN = -7V Short-Circuit Current 795mA0V ≤ V O ≤ V CCSP481E/SP485E RECEIVER AC Characteristics Maximum Data Rate 10Mbps RE = 0V, DE = 0V Receiver Input to Output 2045100ns t PLH ; R DIFF = 54Ω,C L1 = C L2 = 100pF; Figures 3 & 7Receiver Input to Output 2045100ns t PHL ; R DIFF = 54Ω,C L1 = C L2 = 100pF; Figures 3 & 7Diff. Receiver Skew It PLH -t PHL I 13nsR DIFF = 54Ω; C L1 = C L2 = 100pF;Figures 3 & 7Receiver Enable to Output Low4570ns C RL = 15pF; Figures 2 & 8; S 1 closed Receiver Enable to Output High4570ns C RL = 15pF; Figures 2 & 8; S 2 closed Receiver Disable from Low 4570ns C RL = 15pF; Figures 2 & 8; S 1 closed Receiver Disable from High 4570nsC RL = 15pF; Figures 2 & 8; S 2 closed SP481EShutdown Timing Time to Shutdown 50200600ns RE = 5V, DE = 0VDriver Enable from Shutdown to Output High40100ns C L = 100pF; See Figures 4 & 6; S 2 closed Driver Enable from Shutdown to Output Low40100ns C L = 100pF; See Figures 4 & 6; S 1 closed Receiver Enable from Shutdown to Output High 3001000ns C L = 15pF; See Figures 2 & 8; S 2 closed Receiver Enable from Shutdown to Output Low 3001000ns C L = 15pF; See Figures 2 & 8; S 1 closedPOWER REQUIREMENTS Supply Voltage +4.75+5.25VoltsSupply Current SP481E/485E No Load900µA RE, DI = 0V or V CC ; DE = V CC 600µA RE = 0V, DI = 0V or 5V; DE = 0V SP481EShutdown Mode10µADE = 0V, RE=V CCENVIRONMENTAL AND MECHANICAL Operating Temperature Commercial (_C_)0+70°C Industrial (_E_)-40+85°C (_M_)-40+125°C Storage Temperature -65+150°CPackagePlastic DIP (_P) NSOIC (_N)元器件交易网PIN FUNCTIONPin 1 – RO – Receiver Output.Pin 2 – RE – Receiver Output Enable Active LOW.Pin 3 – DE – Driver Output Enable Active HIGH.Pin 4 – DI – Driver Input.Pin 5 – GND – Ground Connection.Pin 6 – A – Driver Output/Receiver Input Non-inverting.Pin 7 – B – Driver Output/Receiver Input Inverting.Pin 8 – Vcc – Positive Supply 4.75V<Vcc< 5.25V.Figure 5. Driver Propagation DelaysFigure 3. RS-485 Driver/Receiver Timing Test CircuitFigure 4. RS-485 Driver Timing Test Load #2 CircuitINPUTS OUTPUTSLINERE DE DI CONDITION B A X11No Fault01 X10No Fault10 X0X X Z Z X1X Fault Z ZINPUTS OUTPUTS RE DE A - B R00 +0.2V100 -0.2V000Inputs Open110X ZTable 1. Transmit Function Truth TableTable 2. Receive Function Truth TableFigure 8. Receiver Enable and Disable Times元器件交易网ReceiversThe SP481E and SP485E receivers have differ-ential inputs with an input sensitivity as low as ±200mV. Input impedance of the receivers is typically 15k Ω (12k Ω minimum). A wide com-mon mode range of -7V to +12V allows for large ground potential differences between systems.The receivers of the SP481E and SP485E have a tri-state enable control pin. A logic LOW on RE (pin 2) will enable the receiver, a logic HIGH on RE (pin 2) will disable the receiver.The receiver for the SP481E and SP485E will operate up to at least 10Mbps. The receiver for each of the two devices is equipped with the fail-safe feature. Fail-safe guarantees that the receiver output will be in a HIGH state when the input is left unconnected.Shutdown Mode SP481EThe SP481E is equipped with a Shutdown mode.To enable the Shutdown state, both the driver and receiver must be disabled simultaneously.A logic LOW on DE (pin 3) and a logic HIGH on RE (pin 2) will put the SP481E into Shutdown mode. In Shutdown, supply current will drop to typically 1µA.ESD TOLERANCEThe SP481E Family incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static dis-charges and associated transients. The improved ESD tolerance is at least ±15kV without damage nor latch-up.There are different methods of ESD testing applied:a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Discharge c) IEC1000-4-2 Direct ContactDESCRIPTIONThe SP481E and SP485E are half-duplex differ-ential transceivers that meet the requirements of RS-485 and RS-422. Fabricated with a Sipex proprietary BiCMOS process, all three products require a fraction of the power of older bipolar designs.The RS-485 standard is ideal for multi-drop applications and for long-distance interfaces.RS-485 allows up to 32 drivers and 32 receivers to be connected to a data bus, making it an ideal choice for multi-drop applications. Since the cabling can be as long as 4,000 feet, RS-485transceivers are equipped with a wide (-7V to +12V) common mode range to accommodate ground potential differences. Because RS-485 is a differential interface, data is virtually immune to noise in the transmission line.DriversThe driver outputs of the SP481E and SP485E are differential outputs meeting the RS-485 and RS-422 standards. The typical voltage output swing with no load will be 0 Volts to +5 Volts.With worst case loading of 54Ω across the differ-ential outputs, the drivers can maintain greater than 1.5V voltage levels. The drivers of the SP481E , and SP485E have an enable control line which is active HIGH. A logic HIGH on DE (pin 3) will enable the differential driver outputs.A logic LOW on DE (pin 3) will tri-state the driver outputs.The transmitters of the SP481E and SP485E will operate up to at least 10Mbps.元器件交易网The Human Body Model has been the generally accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 7. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently. The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outside environment and human presence. The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage. The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2 is shown on Figure 8. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.Figure 7. ESD Test Circuit for Human Body ModelFigure 8. ESD Test Circuit for IEC1000-4-2元器件交易网With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT) through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system. This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage. Variables with an air discharge such as approach speed of the object carrying the ESD potential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.The Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit model in Figures 7 and 8 represent the typical ESD testing circuit used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on. Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S, the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2 switch is pulsed so that the device under test receives a duration of voltage.For the Human Body Model, the current limiting resistor (RS) and the source capacitor (CS) are 1.5kΩ an 100pF, respectively. For IEC-1000-4-2, the current limiting resistor (RS) and the source capacitor (CS) are 330Ω an 150pF, respectively.The higher CSvalue and lower RSvalue in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.Figure 9. ESD Test Waveform for IEC1000-4-2t=0ns t=30ns0A15A30At ➙i➙元器件交易网元器件交易网ORDERING INFORMATIONModel Temperature Range PackageSP481ECN.......................................................0˚C to +70˚C...............................................8-pin Narrow SOICSP481ECP........................................................0˚C to +70˚C...................................................8-pin Plastic DIPSP481EEN.......................................................-40˚C to +85˚C.............................................8-pin Narrow SOICSP481EEP......................................................-40˚C to +85˚C.................................................8-pin Plastic DIPSP485ECN.......................................................0˚C to +70˚C...............................................8-pin Narrow SOICSP485ECP........................................................0˚C to +70˚C...................................................8-pin Plastic DIPSP485EEN......................................................-40˚C to +85˚C.............................................8-pin Narrow SOICSP485EEP......................................................-40˚C to +85˚C.................................................8-pin Plastic DIPSP485EMN....................................................-40˚C to +125˚C............................................8-pin Narrow SOICPlease consult the factory for pricing and availability on a Tape-On-Reel option.CorporationSIGNAL PROCESSING EXCELLENCESipex CorporationHeadquarters andSales Office233 South Hillview DriveMilpitas, CA 95035TEL: (408) 934-7500FAX: (408) 935-7600Sales Office22 Linnell CircleBillerica, MA 01821TEL: (978) 667-8700FAX: (978) 670-9001e-mail: sales@Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of theapplication or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.Rev. 5/16/03SP481E Low Power Half-Duplex RS485 Transceivers© Copyright 2003 Sipex Corporation11。

(完整word版)表面增强拉曼光谱学SERS综述

《表面增强拉曼光谱学SERS 综述,简史,原理,实验,展望》本文回顾表面增强拉曼光谱学SERS,surface Enhanced Raman Scattering。

作者出身物理,主要关注器件和技术,尽可能简单平实,少用公式。

SERS结合灵敏的Raman谱,表面科学甚至电化学,是重要的灵敏特异检测技术。

目录1.简史2.定义3.理论3.1 电磁增强理论3。

2 化学增强理论4 实验4。

1 总的实验结构4.2 衬底制造4。

3 谱的解读5 应用6 展望简史欲说SERS先说Raman谱,欲说Raman先说散射光散射的核心含义是散射中心,如微粒,吸收辐射并再次辐射电磁波的过程,据此定义,磷光和荧光都可视为散射。

传统的散射暗示了入射波的传播方向和散射光的方向有偏折,甚至完全反向,即背散射,实际上,受激散射的散射波的方向和入射波是一致的,受激性使然.故散射的散只有历史意义了。

最早被系统研究的光散射当属Rayleigh散射,即散射中心尺度远远小于光波长的情况,其最重要的规律就是散射强度正比于频率四次方变化。

可见光谱中长波或曰红端频率低,其Rayleigh 散射强度远比短波端弱,即著名的天空为何呈现蓝色的问题的答案。

之后Mie用电磁论系统的研究了光散射,解决了不同大小的各类规则散射体问题,至今仍然意义重大,常说的Mie散射其实不确切,Mie给出的是各类散射的解甚至包含了Rayleigh散射。

此外的Dyndall散射,临界乳光之类的光散射现象暂时省略.在上述光散射中,散射波和入射波的频率相同,Stockes早前甚至提出所谓的Stokes定律:考虑能量守恒,散射波的波长不可能小于激发散射的光的波长。

考察诸如荧光,磷光等过程,此定律没错,但是Stokes定律的范围仅仅限于入射波和散射中心无动量,无能量交换的过程,即所谓的弹性散射。

后来Smekel最早预言了频率变化的非弹性散射.Brillioun观测到了以其名字命名的Brillioun散射,即低频声声子对光子的散射,频移较小。

SP483E资料

s +5V Onlys Low Power BiCMOSs Driver/Receiver Enable for Multi-Drop configurationss Enhanced ESD Specifications:+15KV Human Body Model+15KV IEC1000-4-2 Air Discharge +8KV IEC1000-4-2 Contact Discharge s Low EMI Transceiver limited to 250kbpsDESCRIPTIONThe SP483E is a half-duplex transceiver that meets the specifications of RS-485 and RS-422serial protocols with enhanced ESD performance. The ESD tolerance has been improved on this device to over ±15kV for both Human Body Model and IEC1000-4-2 Air Discharge Method. This device is pin-to-pin compatible with Sipex's SP483 device as well as popular industry standards. As with the original version, the SP483E features Sipex's BiCMOS design allowing low power operation without sacrificing performance. The SP483E meet the requirements of the RS-485 and RS-422 protocols up to 250kbps under load. The SP483E is internally slew rate limited to reduce EMI and can meet the requirements of RS-485 and RS-422 up to 250kbps. The SP483E is also equipped with a low power Shutdown mode.SPECIFICATIONSABSOLUTE MAXIMUM RATINGSThese are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.V CC ............................................................................................................+7V Input VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers..................................................-0.3V to (V CC +0.5V)Receivers................................................................. ±15VOutput VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers...................................................................... ±15V Receivers............................................-0.3V to (V CC +0.5V)Storage Temperature.......................................................-65˚C to +150˚C Power Dissipation...........................................................................500mW元器件交易网元器件交易网SPECIFICATIONS (continued)PIN FUNCTIONPin 1 – RO – Receiver Output.Pin 2 – RE – Receiver Output Enable Active LOW.Pin 3 – DE – Driver Output Enable Active HIGH.Pin 4 – DI – Driver Input.Pin 5 – GND – Ground Connection.Pin 6 – A – Driver Output/Receiver Input Non-inverting.Pin 7 – B – Driver Output/Receiver Input Inverting.Pin 8 – Vcc – Positive Supply 4.75V<Vcc< 5.25V.Figure 5. Driver Propagation DelaysFigure 3. RS-485 Driver/Receiver Timing Test CircuitFigure 4. RS-485 Driver Timing Test Load #2 CircuitINPUTS OUTPUTSLINERE DE DI CONDITION B A X11No Fault01 X10No Fault10 X0X X Z Z X1X Fault Z ZINPUTS OUTPUTS RE DE A - B R00 +0.2V100 -0.2V000Inputs Open110X ZTable 1. Transmit Function Truth TableTable 2. Receive Function Truth TableFigure 8. Receiver Enable and Disable Times元器件交易网Receivers...The SP483E receivers have differential inputs with an input sensitivity as low as ±200mV.Input impedance of the receivers is typically 15k Ω (12k Ω minimum). A wide common mode range of -7V to +12V allows for large ground potential differences between systems. The receivers have a tri-state enable control pin.A logic LOW on RE (pin 2) will enable the receiver, a logic HIGH on RE (pin 2) will disable the receiver.The SP483E receiver is rated for data rates up to 250 Kbps. The receivers are equipped with the fail-safe feature. Fail-safe guarantees that the receiver output will be in a HIGH state when the input is left unconnected.Shutdown Mode...The SP483E is equipped with a Shutdown mode.To enable the Shutdown state, both the driver and receiver must be disabled simultaneously. A logic LOW on DE (pin 3) and a logic HIGH on RE (pin 2) will put the SP483E into Shutdown mode. In Shutdown, supply current will drop to typically 1µA.ESD TOLERANCE...The SP483E device incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static discharges and associated transients. The improved ESD tolerance is at least ±15kV without damage nor latch-up.There are different methods of ESD testing applied:a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Discharge c) IEC1000-4-2 Direct ContactDESCRIPTION...The SP483E is a half-duplex differential transceiver that meets the requirements of RS-485 and RS-422. Fabricated with a Sipex proprietary BiCMOS process, the SP483E requires a fraction of the power of older bipolar designs.The RS-485 standard is ideal for multi-drop applications and for long-distance interfaces.RS-485 allows up to 32 drivers and 32 receivers to be connected to a data bus, making it an ideal choice for multi-drop applications. Since the cabling can be as long as 4,000 feet, RS-485transceivers are equipped with a wide (-7V to +12V) common mode range to accommodate ground potential differences. Because RS-485 is a differential interface, data is virtually immune to noise in the transmission line.Drivers...The driver outputs of the SP483E are differential outputs meeting the RS-485 and RS-422 stan-dards. The typical voltage output swing with no load will be 0 Volts to +5 Volts. With worst case loading of 54Ω across the differential outputs,the drivers can maintain greater than 1.5V volt-age levels. The drivers have an enable control line which is active HIGH. A logic HIGH on DE (pin 3) will enable the differential driver outputs.A logic LOW on DE (pin 3) will tri-state the driver outputs.The SP483E has internally slew rate limited driver outputs to minimize EMI. The maximum data rate for the SP483E drivers is 250 Kbps under load.元器件交易网The Human Body Model has been the generally accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 9. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently. The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outside environment and human presence. The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage. The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2 is shown on Figure 10. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.Figure 9. ESD Test Circuit for Human Body ModelFigure 10. ESD Test Circuit for IEC1000-4-2元器件交易网With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT) through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system. This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage. Variables with an air discharge such as approach speed of the object carrying the ESD potential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.The Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit model in Figures 9 and 10 represent the typical ESD testing circuit used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on. Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S, the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2 switch is pulsed so that the device under test receives a duration of voltage.For the Human Body Model, the current limiting resistor (RS) and the source capacitor (CS) are 1.5kΩ an 100pF, respectively. For IEC-1000-4-2, the current limiting resistor (RS) and the source capacitor (CS) are 330Ω an 150pF, respectively.The higher CSvalue and lower RSvalue in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.Figure 11. ESD Test Waveform for IEC1000-4-2t=0ns t=30ns0A15A30At ¥i¥Table 1. Transceiver ESD Tolerance Levels 元器件交易网元器件交易网ORDERING INFORMATIONModel Temperature Range PackageSP483ECN.......................................................0˚C to +70˚C...............................................8-pin Narrow SOICSP483ECP........................................................0˚C to +70˚C...................................................8-pin Plastic DIPSP483EEN.......................................................-40˚C to +85˚C.............................................8-pin Narrow SOICSP483EEP......................................................-40˚C to +85˚C.................................................8-pin Plastic DIPSipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of theapplication or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.SP483EDS/05SP483E Low EMI Half-Duplex RS485 Transceiver© Copyright 2000 Sipex Corporation11。

SP485EEN

■+5V Only■Low Power BiCMOS■Driver/Receiver Enable for Multi-Drop configurations■Low Power Shutdown Mode (SP481E )■Enhanced ESD Specifications:DESCRIPTIONThe SP481E and the SP485E are a family of half-duplex transceivers that meet the specifications of RS-485 and RS-422 serial protocols with enhanced ESD performance. The ESD tolerance has been improved on these devices to over +15KV for both Human Body Model and IEC1000-4-2 Air Discharge Method. These devices are pin-to-pin compatible with Sipex's SP481 and SP485 devices as well as popular industry standards. As with the original versions, the SP481E and the SP485E feature Sipex's BiCMOS design allowing low power operation without sacrificing performance. The SP481E and SP485E meet the requirements of the RS-485 and RS-422 protocols up to 10Mbps under load. The SP481E is equipped with a low power Shutdown mode.+15KV Human Body Model+15KV IEC1000-4-2 Air Discharge +8KV IEC1000-4-2 Contact DischargeABSOLUTE MAXIMUM RATINGSThese are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.V CC ............................................................................................................+7V Input VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers..................................................-0.3V to (V CC +0.5V)Receivers................................................................. ±15VSPECIFICATIONST MIN to T MAX and V CC = 5V ± 5% unless otherwise noted.PARAMETERSMIN.TYP.MAX.UNITS CONDITIONSSP481E/SP485E DRIVER DC CharacteristicsDifferential Output Voltage GND V CC Volts Unloaded; R = ∞; see Figure 1Differential Output Voltage 2V CC Volts with load; R = 50Ω; (RS-422);see Figure 1Differential Output Voltage 1.5V CC Volts with load; R = 27Ω; (RS-485);see Figure 1Change in Magnitude of Driver Differential Output Voltage for Complimentary States 0.2Volts R = 27Ω or R = 50Ω; see Figure 1Driver Common-Mode Output Voltage 3Volts R = 27Ω or R = 50Ω; see Figure 1Input High Voltage 2.0Volts Applies to DE, DI, RE Input Low Voltage 0.8Volts Applies to DE, DI, RE Input Current±10µA Applies to DE, DI, RE Driver Short-Circuit Current V OUT = HIGH ±250mA -7V ≤ V O ≤ +12V V OUT = LOW±250mA-7V ≤ V O ≤ +12VSP481E/SP485E DRIVER AC Characteristics Maximum Data Rate 10Mbps RE = 5V, DE = 5V; R DIFF = 54Ω,C L1 = C L2 = 100pFDriver Input to Output 203060ns t PLH ; R DIFF = 54Ω, C L1 = C L2 = 100pF;see Figures 3 and 5Driver Input to Output 203080ns t PLH ; R DIFF = 54Ω, C LI = C L2 = 100pF;(SP485EMN ONLY)See Figures 3 and 5Driver Input to Output 203060ns t PHL ; R DIFF = 54Ω, C L1 = C L2 = 100pF;see Figures 3 and 5Driver Input to Output 203080ns t PHL ; R DIFF = 54Ω, C L1 = C L2 = 100pF;(SP485EMN ONLY)see Figures 3 and 5Driver Skew510ns see Figures 3 and 5,t SKEW = | t DPLH - t DPHL |Driver Rise or Fall Time 31540ns From 10% to 90%; R DIFF = 54Ω,C L1 = C L2 = 100pF; s ee Figures 3 & 6Driver Enable to Output High 4070ns C L = 100pF; see Figures 4 & 6; S 2closedDriver Enable to Output Low 4070ns C L = 100pF; see Figures 4 & 6; S 1closedDriver Disable Time from Low 4070ns C L = 100pF; see Figures 4 & 6; S 1closedDriver Disable Time from High 4070nsC L = 100pF; see Figures 4 & 6; S 2closedOutput VoltagesLogic........................................................-0.3V to (V CC +0.5V)Drivers...................................................................... ±15V Receivers............................................-0.3V to (V CC +0.5V)Storage Temperature.......................................................-65˚C to +150˚C Power Dissipation per Package8-pin NSOIC (derate 6.60mW/o C above +70o C)...........................550mW 8-pin PDIP (derate 11.8mW/o C above +70o C)............................1000mWSPECIFICATIONS (continued)T MIN to T MAX and V CC = 5V ± 5% unless otherwise noted.PARAMETERS MIN.TYP.MAX.UNITS CONDITIONSSP481E/SP485E RECEIVER DC CharacteristicsDifferential Input Threshold -0.2+0.2Volts -7V ≤ V CM ≤ +12V Differential Input Threshold -0.4+0.4Volts -7V ≤ V CM ≤ +12V (SP485EMN ONLY)Input Hysteresis 20mV V CM = 0VOutput Voltage High 3.5Volts I O = -4mA, V ID = +200mV Output Voltage Low0.4Volts I O = +4mA, V ID = -200mVThree-State (High Impedance)Output Current ±1µA 0.4V ≤ V O ≤ 2.4V; RE = 5V Input Resistance 1215k Ω-7V ≤ V CM ≤ +12VInput Current (A, B); V IN = 12V +1.0mA DE = 0V, V CC = 0V or 5.25V, V IN = 12V Input Current (A, B); V IN = -7V -0.8mA DE = 0V, V CC = 0V or 5.25V, V IN = -7V Short-Circuit Current 795mA0V ≤ V O ≤ V CCSP481E/SP485E RECEIVER AC Characteristics Maximum Data Rate 10Mbps RE = 0V, DE = 0V Receiver Input to Output 2045100ns t PLH ; R DIFF = 54Ω,C L1 = C L2 = 100pF; Figures 3 & 7Receiver Input to Output 2045100ns t PHL ; R DIFF = 54Ω,C L1 = C L2 = 100pF; Figures 3 & 7Diff. Receiver Skew It PLH -t PHL I 13nsR DIFF = 54Ω; C L1 = C L2 = 100pF;Figures 3 & 7Receiver Enable to Output Low4570ns C RL = 15pF; Figures 2 & 8; S 1 closed Receiver Enable to Output High4570ns C RL = 15pF; Figures 2 & 8; S 2 closed Receiver Disable from Low 4570ns C RL = 15pF; Figures 2 & 8; S 1 closed Receiver Disable from High 4570nsC RL = 15pF; Figures 2 & 8; S 2 closed SP481EShutdown Timing Time to Shutdown 50200600ns RE = 5V, DE = 0VDriver Enable from Shutdown to Output High40100ns C L = 100pF; See Figures 4 & 6; S 2 closed Driver Enable from Shutdown to Output Low40100ns C L = 100pF; See Figures 4 & 6; S 1 closed Receiver Enable from Shutdown to Output High 3001000ns C L = 15pF; See Figures 2 & 8; S 2 closed Receiver Enable from Shutdown to Output Low 3001000ns C L = 15pF; See Figures 2 & 8; S 1 closedPOWER REQUIREMENTS Supply Voltage +4.75+5.25VoltsSupply Current SP481E/485E No Load900µA RE, DI = 0V or V CC ; DE = V CC 600µA RE = 0V, DI = 0V or 5V; DE = 0V SP481EShutdown Mode10µADE = 0V, RE=V CCENVIRONMENTAL AND MECHANICAL Operating Temperature Commercial (_C_)0+70°C Industrial (_E_)-40+85°C (_M_)-40+125°C Storage Temperature -65+150°CPackagePlastic DIP (_P) NSOIC (_N)PIN FUNCTIONPin 1 – RO – Receiver Output.Pin 2 – RE – Receiver Output Enable Active LOW.Pin 3 – DE – Driver Output Enable Active HIGH.Pin 4 – DI – Driver Input.Pin 5 – GND – Ground Connection.Pin 6 – A – Driver Output/Receiver Input Non-inverting.Pin 7 – B – Driver Output/Receiver Input Inverting.Pin 8 – Vcc – Positive Supply 4.75V<Vcc< 5.25V.Figure 5. Driver Propagation DelaysFigure 3. RS-485 Driver/Receiver Timing Test CircuitFigure 4. RS-485 Driver Timing Test Load #2 CircuitINPUTS OUTPUTSLINERE DE DI CONDITION B A X11No Fault01 X10No Fault10 X0X X Z Z X1X Fault Z ZINPUTS OUTPUTS RE DE A - B R00 +0.2V100 -0.2V000Inputs Open110X ZTable 1. Transmit Function Truth TableTable 2. Receive Function Truth TableFigure 8. Receiver Enable and Disable TimesReceiversThe SP481E and SP485E receivers have differ-ential inputs with an input sensitivity as low as ±200mV. Input impedance of the receivers is typically 15k Ω (12k Ω minimum). A wide com-mon mode range of -7V to +12V allows for large ground potential differences between systems.The receivers of the SP481E and SP485E have a tri-state enable control pin. A logic LOW onRE (pin 2) will enable the receiver, a logic HIGH on RE (pin 2) will disable the receiver.The receiver for the SP481E and SP485E will operate up to at least 10Mbps. The receiver for each of the two devices is equipped with the fail-safe feature. Fail-safe guarantees that the receiver output will be in a HIGH state when the input is left unconnected.Shutdown Mode SP481EThe SP481E is equipped with a Shutdown mode.To enable the Shutdown state, both the driver and receiver must be disabled simultaneously.A logic LOW on DE (pin 3) and a logic HIGH on RE (pin 2) will put the SP481E into Shutdown mode. In Shutdown, supply current will drop to typically 1µA.ESD TOLERANCEThe SP481E Family incorporates ruggedized ESD cells on all driver output and receiver input pins. The ESD structure is improved over our previous family for more rugged applications and environments sensitive to electro-static dis-charges and associated transients. The improved ESD tolerance is at least ±15kV without damage nor latch-up.There are different methods of ESD testing applied:a) MIL-STD-883, Method 3015.7b) IEC1000-4-2 Air-Discharge c) IEC1000-4-2 Direct ContactDESCRIPTIONThe SP481E and SP485E are half-duplex differ-ential transceivers that meet the requirements of RS-485 and RS-422. Fabricated with a Sipex proprietary BiCMOS process, all three products require a fraction of the power of older bipolar designs.The RS-485 standard is ideal for multi-drop applications and for long-distance interfaces.RS-485 allows up to 32 drivers and 32 receivers to be connected to a data bus, making it an ideal choice for multi-drop applications. Since the cabling can be as long as 4,000 feet, RS-485transceivers are equipped with a wide (-7V to +12V) common mode range to accommodate ground potential differences. Because RS-485 is a differential interface, data is virtually immune to noise in the transmission line.DriversThe driver outputs of the SP481E and SP485E are differential outputs meeting the RS-485 and RS-422 standards. The typical voltage output swing with no load will be 0 Volts to +5 Volts.With worst case loading of 54Ω across the differ-ential outputs, the drivers can maintain greater than 1.5V voltage levels. The drivers of the SP481E , and SP485E have an enable control line which is active HIGH. A logic HIGH on DE (pin 3) will enable the differential driver outputs.A logic LOW on DE (pin 3) will tri-state the driver outputs.The transmitters of the SP481E and SP485E will operate up to at least 10Mbps.The Human Body Model has been the generally accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by using a test model as shown in Figure 7. This method will test the IC’s capability to withstand an ESD transient during normal handling such as in manufacturing areas where the ICs tend to be handled frequently. The IEC-1000-4-2, formerly IEC801-2, is generally used for testing ESD on equipment and systems. For system manufacturers, they must guarantee a certain amount of ESD protection since the system itself is exposed to the outside environment and human presence. The premise with IEC1000-4-2 is that the system is required to withstand an amount of static electricity when ESD is applied to points and surfaces of the equipment that are accessible to personnel during normal usage. The transceiver IC receives most of the ESD current when the ESD source is applied to the connector pins. The test circuit for IEC1000-4-2 is shown on Figure 8. There are two methods within IEC1000-4-2, the Air Discharge method and the Contact Discharge method.Figure 7. ESD Test Circuit for Human Body ModelFigure 8. ESD Test Circuit for IEC1000-4-2With the Air Discharge Method, an ESD voltage is applied to the equipment under test (EUT) through air. This simulates an electrically charged person ready to connect a cable onto the rear of the system only to find an unpleasant zap just before the person touches the back panel. The high energy potential on the person discharges through an arcing path to the rear panel of the system before he or she even touches the system. This energy, whether discharged directly or through air, is predominantly a function of the discharge current rather than the discharge voltage. Variables with an air discharge such as approach speed of the object carrying the ESD potential to the system and humidity will tend to change the discharge current. For example, the rise time of the discharge current varies with the approach speed.The Contact Discharge Method applies the ESD current directly to the EUT. This method was devised to reduce the unpredictability of the ESD arc. The discharge current rise time is constant since the energy is directly transferred without the air-gap arc. In situations such as hand held systems, the ESD charge can be directly discharged to the equipment from a person already holding the equipment. The current is transferred on to the keypad or the serial port of the equipment directly and then travels through the PCB and finally to the IC.The circuit model in Figures 7 and 8 represent the typical ESD testing circuit used for all three methods. The C S is initially charged with the DC power supply when the first switch (SW1) is on. Now that the capacitor is charged, the second switch (SW2) is on while SW1 switches off. The voltage stored in the capacitor is then applied through R S, the current limiting resistor, onto the device under test (DUT). In ESD tests, the SW2 switch is pulsed so that the device under test receives a duration of voltage.For the Human Body Model, the current limiting resistor (RS) and the source capacitor (CS) are 1.5kΩ an 100pF, respectively. For IEC-1000-4-2, the current limiting resistor (RS) and the source capacitor (CS) are 330Ω an 150pF, respectively.The higher CSvalue and lower RSvalue in the IEC1000-4-2 model are more stringent than the Human Body Model. The larger storage capacitor injects a higher voltage to the test point when SW2 is switched on. The lower current limiting resistor increases the current charge onto the test point.Figure 9. ESD Test Waveform for IEC1000-4-2t=0ns t=30ns0A15A30At ➙i➙ORDERING INFORMATIONModel Temperature Range PackageSP481ECN.......................................................0˚C to +70˚C...............................................8-pin Narrow SOIC SP481ECP........................................................0˚C to +70˚C...................................................8-pin Plastic DIP SP481EEN.......................................................-40˚C to +85˚C.............................................8-pin Narrow SOIC SP481EEP......................................................-40˚C to +85˚C.................................................8-pin Plastic DIPSP485ECN.......................................................0˚C to +70˚C...............................................8-pin Narrow SOIC SP485ECP........................................................0˚C to +70˚C...................................................8-pin Plastic DIP SP485EEN......................................................-40˚C to +85˚C.............................................8-pin Narrow SOIC SP485EEP......................................................-40˚C to +85˚C.................................................8-pin Plastic DIP SP485EMN....................................................-40˚C to +125˚C............................................8-pin Narrow SOICPlease consult the factory for pricing and availability on a Tape-On-Reel option.CorporationSIGNAL PROCESSING EXCELLENCESipex CorporationHeadquarters andSales Office233 South Hillview DriveMilpitas, CA 95035TEL: (408) 934-7500FAX: (408) 935-7600Sales Office22 Linnell CircleBillerica, MA 01821TEL: (978) 667-8700FAX: (978) 670-9001e-mail: sales@Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Rev. 5/16/03SP481E Low Power Half-Duplex RS485 Transceivers© Copyright 2003 Sipex Corporation11。

表面增强拉曼光谱学SERS综述

For personal use only in study and research; not for commercial use《表面增强拉曼光谱学SERS 综述,简史,原理,实验,展望》本文回顾表面增强拉曼光谱学SERS,surface Enhanced Raman Scattering。

作者出身物理,主要关注器件和技术,尽可能简单平实,少用公式。

SERS结合灵敏的Raman谱,表面科学甚至电化学,是重要的灵敏特异检测技术。

目录1.简史2.定义3.理论3.1 电磁增强理论3.2 化学增强理论4 实验4.1 总的实验结构4.2 衬底制造4.3 谱的解读5 应用6 展望简史欲说SERS先说Raman谱,欲说Raman先说散射光散射的核心含义是散射中心,如微粒,吸收辐射并再次辐射电磁波的过程,据此定义,磷光和荧光都可视为散射。

传统的散射暗示了入射波的传播方向和散射光的方向有偏折,甚至完全反向,即背散射,实际上,受激散射的散射波的方向和入射波是一致的,受激性使然。

故散射的散只有历史意义了。

最早被系统研究的光散射当属Rayleigh散射,即散射中心尺度远远小于光波长的情况,其最重要的规律就是散射强度正比于频率四次方变化。

可见光谱中长波或曰红端频率低,其Rayleigh散射强度远比短波端弱,即著名的天空为何呈现蓝色的问题的答案。

之后Mie用电磁论系统的研究了光散射,解决了不同大小的各类规则散射体问题,至今仍然意义重大,常说的Mie散射其实不确切,Mie给出的是各类散射的解甚至包含了Rayleigh散射。

此外的Dyndall散射,临界乳光之类的光散射现象暂时省略。

在上述光散射中,散射波和入射波的频率相同,Stockes早前甚至提出所谓的Stokes定律:考虑能量守恒,散射波的波长不可能小于激发散射的光的波长。

考察诸如荧光,磷光等过程,此定律没错,但是Stokes定律的范围仅仅限于入射波和散射中心无动量,无能量交换的过程,即所谓的弹性散射。

标准化病人(SP)文献综述

国内关于标准化病人的研究现状分析一、概念与历史(一)标准化病人的概念标准化病人(Standardized Patient,SP),又称模拟病人(Simulated Patient),或病人指导者(Patient Instructor),是指从事非医技工作的正常人或轻症患者,经过标准化、系统化培训后,能准备表现患者临床症状、体征或病史而接受临床检查者,旨在恒定、逼真地复制真实临床情况。

由于经过专业的培训,这些人能够准确地模仿相应病例的症状,包括走路姿势、身体动作、疼痛的程度、面部表情、病史病状等。

学生根据“病人”表现出来的症状询问病史、判断病情,作出正确的诊断。

标准化病人可以给操作者进行评分和对操作技巧进行反馈,发挥扮演患者、充当评估者和教学指导者三种功能。

(二)标准化病人的起源与发展1963年,美国南加州大学神经病学家Howard Barrow以教学为目的,开发了“模拟病人”;1968年,衣阿华大学的Robert Kretzschoman博士开发了第一个“妇产科教学合作者”。

20世纪60年代,美国率先开始进行标准化病人的培训与应用,现在发达国家已较成熟,而且在加拿大、美国及日本等国已在医师执照考试中使用。

1970年代中期,邓迪大学的Ron Harden开发并第一次实现了标准化病人在客观结构化临床能力考试中的应用。

1970年代后期,亚利桑那大学儿科医师Paula Stillman开发了“亚利桑那临床等级量表”,以评估学生的表现。

1975年M.R,Harden开发了客观结构化临床考试(Objective Structured Clinical Examination,简称OSCE)这一全新的考试方法,要求考生参加多个站点的考试,在每一个程序站点中,要求学生采集病史和体格检查或完成其他任务,标准化病人的出现很好地避免了真正病人的种种不便,增强了其实际操作性。

自20世纪70年代开始,标准化病人作为教学媒介进入医学教学领域,在美、日、德、法等国的医学院校普遍应用。

石墨烯研究进展

石墨烯复合材料的研究进展石墨烯以其优异的性能和独特的二维结构成为材料领域研究热点。

本文综述了石墨烯的制备方法并简单介绍了石墨烯的力学、光学、电学及热学性能,并对石墨烯的复合材料应用做了展望。

1制备方法熔融共混法:将原始石墨氧化,经过剥离并还原制成石墨烯,与聚合物在熔融状态下共混制得复合材料。

原位聚合法:将石墨烯与聚合物单体混合,加入引发剂引发反应,最后制得复合材料。

溶液混合法:在溶液共混法中,常常先制备氧化石墨烯,对其进行改性得到在有机溶剂中能够分散的分散液,通过还原得到石墨烯,然后与聚合物进行溶液共混制备石墨烯/ 聚合物复合材料。

乳液混合法:利用氧化石墨烯在水中具有良好的分散性,可将氧化石墨烯的水性分散液与聚合物胶乳进行混合,通过还原制备石墨烯/ 聚合物复合材料。

2性能特点导电性:石墨烯结构非常稳定,迄今为止,研究者仍未发现石墨烯中有碳原子缺失的情况。

石墨烯中各碳原子之间的连接非常柔韧,当施加外部机械力时,碳原子面就弯曲变形,从而使碳原子不必重新排列来适应外力,也就保持了结构稳定导热性能:石墨烯优异的热传输性能可应用于微型电子设备的热管理如导热膏热驱动、形状记忆聚合物等。

机械特性:石墨烯是人类已知强度最高的物质,比钻石还坚硬,强度比世界上最好的钢铁还要高上100倍。

相互作用:石墨烯中电子间以及电子与蜂窝状栅格间均存在着强烈的相互作用。

化学性质:类似石墨表面,石墨烯可以吸附和脱附各种原子和分子。

从表面化学的角度来看,石墨烯的性质类似于石墨,可利用石墨来推测石墨烯的性质。

3结论与展望目前,无论是在理论还是实验研究方面,石墨烯均已展示出重大的科学意义和应用价值,且已在生物、电极材料、传感器等方面展现出独特的应用优势。

随着对石墨烯研究的不断深入,其内在的一些特殊性能如荧光性能、模板性能等也相继被发现。

由于石墨烯具有较大的比表面积、径厚比、热导率和电导率,与传统填料相比,石墨烯增强的复合材料具有更加优异的物理性能。

血管生成素-2诱导动脉粥样硬化斑块进展的潜在机制

of postintensive care syndrome identified in surgical ICU survivors after implementation of a multidisciplinary clinic [J].J Trauma Acute Care Surg,2021,91(2):406-412.[15]Cao Y ,Wang YJ,he QY ,et al.Study on the correlation between diabe-tes and cognitive dysfunction based on the comprehensive assess-ment of elderly health [J].Chin Gen Prac,2020,23(33):4252-4255.曹颖,王意君,贺清悦,等.基于老年健康综合评估探讨糖尿病与认知功能障碍的相关性研究[J].中国全科医学,2020,23(33):4252-4255.[16]Hastings SN,Mahanna EP,Berkowitz TSZ,et al.Video-enhancedcare management for medically complex older adults with cognitive impairment [J].J Am Geriatr Soc,2021,69(1):77-84.[17]Li J,Wang L,Zhao FX,et al.The current situation and correlation be-tween dyskinesia syndrome and Mild cognitive impairment in the el-derly in the community [J].J Xinxiang Med Coll,2022,39(7):617-621.李洁,王岚,赵丰雪,等.社区老年人运动障碍综合征与轻度认知障碍发生现状及其相关性[J].新乡医学院学报,2022,39(7):617-621.[18]Tierney SM,Woods SP,Sheppard D,et al.Extrapyramidal motorsigns in older adults with HIV disease:frequency,1-year course,and associations with activities of daily living and quality of life [J].J Neurovirol,2021,25(2):162-173.(收稿日期:2023-08-10)血管生成素-2诱导动脉粥样硬化斑块进展的潜在机制文姣姣1,杨学远1综述赵永超1,2,马懿1审校遵义医科大学附属医院心血管内科1、科研部2,贵州遵义563000【摘要】在动脉粥样硬化(atherosclerosis ,AS)病理过程中,斑块内不成熟血管形成和(或)破裂出血、内皮功能障碍是冠脉疾病进展的重要原因,尽管治疗斑块进展的药物和非药物取得了一定成效、早期挽救了生命,但患者的预后并不乐观,因此迫切需要一种干预斑块进展的治疗。

胰腺实性假乳头状瘤的不典型ct表现

关键词 不典型;胰腺实性假乳头状瘤;体层摄影术,X线计算机 中图分类号:R735.9 文献标识码:A 文章编号:10009760(2020)0204405

TheatypicalCTappearancesofsolidpseudopapillarytumorofthepancreas

LIXian1,WANGLinsheng2,ZHANGLihong3,LIUXiaolong2 (12ndSchoolofClinicalMedicine,JiningMedicalUniversity,Jining272067,China;

Keywords:Atypical;Solidpseudopapillarytumorofthepancreas;Tomography;Xraycomputer

摘 要 目的 总结胰腺实性假乳头状瘤(SPTP)的不典型 CT表现,以减少术前误诊率。方法 回顾性分 析经手术病理证实 53例 SPTP的临床和 CT资料,其中 11例表现不典型,均行 CT平扫和增强扫描。结果 不典 型 CT表现的 SPTP所占比约为 20.7%(11/53)。其中 3例完全囊性:CT平扫均呈边界清晰薄壁囊性肿物,2例 囊壁合并结节状钙化,1例囊内有多发纤细分隔;增强扫描囊壁呈轻度延迟强化。5例实性:CT平扫呈均匀低密 度影,边界欠清晰;增强扫描呈均匀轻度延迟强化,其中 1例合并胰腺体尾部萎缩、胰管扩张。2例富血供囊实 性肿块:CT平扫表现为边界清晰软组织密度,瘤内均见点状钙化;增强扫描肿块动脉期呈明显强化,静脉期对比 剂快速廓清,瘤内均见局灶性坏死。1例异位的囊实性肿块:肿块位于腹膜后,CT平扫表现为软组织密度为主, 内多发点状钙化;增强扫描肿块呈明显延迟强化,瘤内见局灶性坏死。结论 SPTP的不典型 CT表现具有多样 性特征,了解其不典型表现,有助于减少术前误诊率。

PCR反应体系25ulBCL2、...

目录英、汉缩略名词对照表 (1)中文摘要 (3)英文摘要 (5)前言 (7)第一部分rh-RPO可能的作用通路以及与炎症介质的关系材料与方法 (10)结果 (17)讨论 (20)第二部分rh-RPO对裸鼠移植瘤的影响材料与方法 (22)结果 (37)讨论 (50)全文小结 (58)参考文献 (59)致谢 (64)综述 (65)英、汉缩略名词对照表英文缩写英文全称中文全称AP Ammonium peroxydisulfate 过硫酸铵BCA Bicinchoninic acid 二喹林甲酸COX-2 Cyclooxygenase-2 环氧合酶-2 DAB Diaminobenzidin 二氨基联苯氨DEPC Diethypyrocarbonate 焦碳酸二乙酯DMSO Dimethyl sulfoxide 二甲基亚砜EB Ethidium bromide 溴化乙锭ECL Enhanced Chemiluminescence 超敏电化学发光ELISA Enzyme Linked Immunosorbent Assay 酶联免疫吸附试验EPO Erythropoietin 促红细胞生成素EPO-R Erythropoietin receptor 促红细胞生成素受体FBS Fetal bovine serum 胎牛血清h Hour 小时HE hematoxyln-eosin 苏木素-伊红HRP Horseradish peroxidase 辣根过氧化物酶IL-10 Interleukin-10白介素-10 min mintute 分MTT Thiazolyl tetrazolium bromide 四甲基偶氮唑蓝MVD microvessel density 微血管密度OD Optical density 光密度PBS Phosphate buffered saline 磷酸盐缓冲液PCR Polymerase chain reaction 聚合酶链反应PMSF Phenylmethanesulfonyl fluoride 苯甲基磺酰氟PVDF Polytetrafluoroethene 聚偏二氟乙烯rh-EPO Recombinant human erythropoietin 重组促红细胞生成素rpm revolutions per minutes 转∕分RT Reverse transcription 逆转录SDS Sodium dodecyl sulfate 十二烷基硫酸钠TBS Tris-Buffered Saline Tris-HCL 缓冲盐溶液TBST Tris-Buffered Saline Tween-20 含吐温-20的TBS TEMED N,N,N',N'-Tetramethylethylenediamine 四甲基乙二胺TNF-αtumor necrosis factor肿瘤坏死因子-αTris Tris(hydroxymethyl)aminomethane 三羟甲基氨基甲烷VEGF Vascularendothelial growth factor 血管内皮生长因子rh-EPO对人MDA-MB-231乳腺癌细胞在裸鼠体内外生长的影响及其机制研究中文摘要目的:研究rh-EPO对人MDA-MB-231乳腺癌细胞在裸鼠体内外生长的影响并探讨其在调控肿瘤生长、血管生成和细胞凋亡中作用及机制。

直肠癌壁外血管侵犯影像学评价的研究进展

•综述•直肠癌壁外血管侵犯影像学评价的研究进展高伟,刘挨师1王泽锋1任建军2赵磊1郝粉娥11内蒙古医科大学附属医院影像诊断科,呼和浩特010050;:内蒙古医科大学附属医院肝胆外科,呼和浩特 010050通信作者:郝粉娘,Email:hfel022@ 【摘要】直肠癌壁外血管侵犯是影响直肠癌病人预后的重要W素,术前准确诊断壁外血管侵犯,可指导治疗方案的制订,从而改善病人预后和远期牛.存MR丨检查和CT检查是术前评估直肠癌的主要检查手段笔者将对影像学检查在直肠癌壁外血管侵犯评价的作用进行综述【关键词】直肠肿瘤;壁外血管侵犯;影像学检查;诊断;治疗;预后基金项目:内朶古内治区自然科学基金(2020MS08051、2020LH08045);内蒙古K科大学科技W万T.程联合项目[YKD2018KJBW( LH )059]Research advances in imaging evaluation of extramural vascular invasion of rectal cancerG a o W ei1, L iu A i s h i1, W a n g Z e fe n g1, R e n J ia n ju n2, Z h a o L e i1, H a o F e n'e11 D e p a r tm e n t o f Im a g in g D ia g n o s is, th e A ffilia te d H o s p ita l o f I n n e r M o n g o lia M e d ic a l U n iv e rs ity,H o h h o t 010050, C h i n a;2 D e p a r t m e n t o f H e p a t o b ilia r y S u r g e r y, th e A f f ilia te d H o s p it a l o f I n n e r M o n g o liaM e d ic a l U n iv e rsity, H o h h o t 010050, C h in aC o r r e s p o n d in g a u t h o r: H a o F e n'e,E m a i l:h f e l022@l63.c o m【Abstract 】Extramural vascular invasion of rectal cancer is an important factor affectingthe prognosis of patients with rectal cancer. Accurate diagnosis of extramural vascular invasionbefore surgery can guide the formulation of treatment plans, thereby improving prognosis and longterm survival of patients. Magnectic resonance imaging examination and computed tomographyexamination are the main examination methods for preoperative evaluation of rectal cancer. Theauthors review the role of imaging examinations in the evaluation of extramural vascular invasion ofrectal cancer.【K eywords】Rectal neoplasms; Extramural vascular invasion; Imaging examination;Diagnosis; Treatment; PrognosisFund programs: Natural Science Foundation of Inner Mongolia Autonomous Region(2020MS08051, 2020LH08045); Science and Technology Million Project Joint Projectof Inner Mongolia Medical University [YKD2018K(BW(LH)059]结直肠癌是消化系统常见的恶性肿瘤,西方w家发病 率呈逐年下降趋势,m我国发病率却呈上升趋势,其中直 肠癌约占结直肠癌发生率的49.6%」目前结直肠癌以手 术切除为主要治疗方式,放化疗、生物免疫治疗及靶向治 疗为辅直肠癌治疗前需评估肿瘤大小、位置、TNM分朗、直肠癌环周筋膜切缘以及直肠癌壁外血管侵犯t丨a n〗u r a1 vascular invasion,EMV丨)等情况 17%〜52%结直肠癌病人EMV1呈阳性:EMV丨状态在直肠肿瘤的术前评估中很重 要,是直肠癌的重要预后因素,可作为局部复发以及总体生 存时间缩短的独立预测因素,也是行新辅助治疗的重要依 据V5对于预后不良的直肠癌病人,新辅助治疗已获得广 泛认同,新辅助治疗比术后放化疗具有更好的肿瘤局部控 制率h_7因此,木前准确评估直肠癌EMVI状态对制订治 疗策略和改善病人预后具有重要临床意义K笔荇将对影DOI:10.3760/l15610-20210201-00054收稿日期2021-02-01引用本文:高伟.刘挨师.王泽锋,等.直肠癌壁外血管侵犯影像学评价的研究进展UI.中华消化外科杂 志-2021, 20(3): 355-358. D01: 10.3760八115610-202102(H-00054.像学检查在直肠癌EMVI评价的作用进行综述一、直肠癌EMV1的定义及病理学检查直肠癌EMVI是指直肠癌所在肠道固有肌层以外的血 管,出现肿瘤细胞浸润":病理学检查结果:(1)直肠癌瘤周血管壁被癌细胞浸润破坏:(2)瘤周血管内出现癌栓11:“种子和土壤”假说将转移扩散确定为一个多步骤过程:首先,肿瘤细胞直接通过血管或间接通过淋巴系统脱离肿瘤 原发部位进人血液循环进入血液循环后,肿瘤细胞必须 在循环中存活。

芬太尼类新精神活性物质检测技术研究进展

第39卷第12期2020年12月分析测试学报FENXI CESHI XUEBAO(Journal of Instrumental Analysis)Vol.39No.121548-1555d o i: 10.3969/j.issn.1004 -4957. 2020.12. 018芬太尼类新精神活性物质检测技术研究进展郭项雨1马麟12,尚宇瀚1白桦1,马强“(1.中国检验检疫科学研究院,北京100176; 2.北京中医药大学东方学院,河北廊坊065001)摘要:毒品滥用是全球性问题,对人们的身心健康、经济发展和社会进步造成巨大危害。

毒品稽查是保障公共安全和社会秩序的重要手段,而科学精准的检测技术为开展毒品稽查工作提供了有力支撑。

近年来,芬太尼类新精神活性物质迅速蔓延,其具有更强的兴奋、致幻、麻醉等效果,已成为继传统毒品、合成毒品后全球流行的第三代毒品,并在一些国家流行、滥用,已造成大量人员死亡,引发严重社会问题。

对此,各国政府密切关注并制定了相应法律法规进行管控,科研人员也开发了一系列检测技术。

该文重点论述了芬太尼类新精神活性物质的传统实验室检测技术和现场快速检测技术的研究进展,并对这些技术的发展趋势和应用前景进行了展望,以期为相关领域研究人员提供技术参考。

关键词:芬太尼;新精神活性物质;检测技术;综述中图分类号:O657.3文献标识码:A文章编号:1004 -4957(2020)12 -1548 -08Research Advances in Analytical Techniques for New PsychoactiveSubstances of Fentanyl CompoundsG U O X ia n g-y u1,M A L i n1’2,S H A N G Y u-h a n1,B A I H u a1,M A Q ia n g1**(1.Chinese Academy of Inspection and Quarantine,Beijing100176,China; 2.D ongfang College,Beijing UniversiChinese Medicine,Langang065001,China)A b s t r a c t:D ru g abuse is a glob al p ro b le m,posing a m ajor threat to people’s p h ysica l and m entalh e a lth,econom ic d evelopm ent and social progress.D rug in spe ction is a key m easure to ensure p u blic security and s ocial o rd e r,c a llin g fo r developm ent o f sensitive and accurate a n a ly tic a l te ch n iq u e s.In recent y e a rs,new^psychoactive substances such as fe n ta n yl com pounds have been spreading ra p idly due to th e ir stronger effects o f e x c ite m e n t,h a llu c in a tio n s and anesthesia,w h ic h ha th ird-g e n e ra tio n drugs after tra d itio n a l drugs and synthetic dru gs.The abuse o f fe n ta n yl dru caused a large nu m be r o f deaths and serious social pro blem s.In th is re g a rd,the au thorities w o rldw id e have attached great im portance to fo rm u la tin g laws and regulations fo r th e ir c o n tro l,and researchers have developed a va rie ty o f a n a ly tic a l tech n iq u e s.In th is p a p e r,the advances in tra d itio n a lla bo ratory a n a ly tic a l techniques and ra p id on-site a n a ly tic a l techniques were sum m a rized,and the developm ent trend and a p p lic a tio n prospects were discu sse d,w h ic h m ay p ro vid e some te c h n ica l in s tru ctions fo r the researchers in related fie ld s.K e y w o rd s:fe n ta n y l;new^psychoactive substances;a n a lytic a l te c h n iq u e s;review^当前,全球毒品问题不断蔓延,毒品滥用持续泛滥。

Cisco Adaptive wIPS Enhanced Local Mode (ELM) 配置和部