zl30109中文资料_数据手册_IC数据表

zl30119中文资料_数据手册_IC数据表

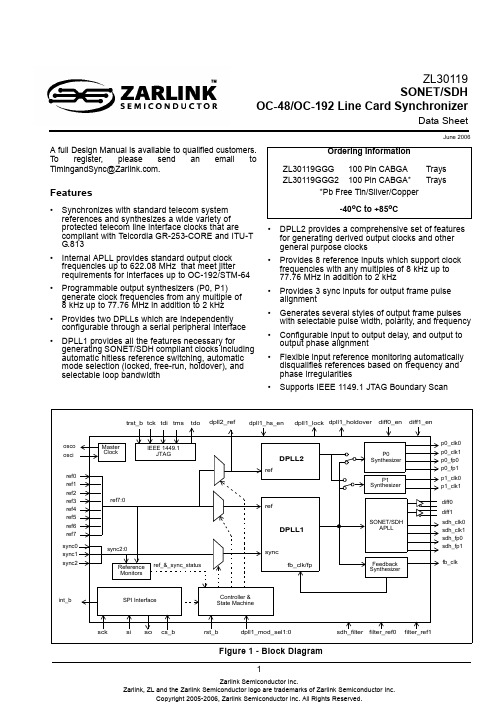

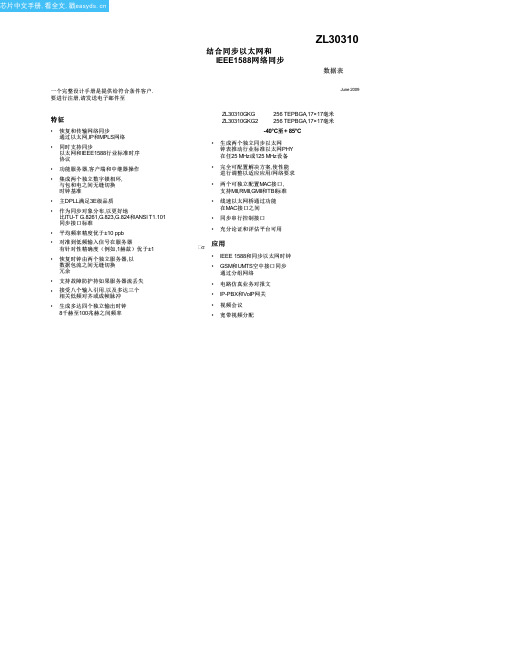

1A full Design Manual is available to qualified customers.To register, please send an email to TimingandSync@.Features•Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-253-CORE and ITU-T G.813•Internal APLL provides standard output clock frequencies up to 622.08MHz that meet jitter requirements for interfaces up to OC-192/STM-64•Programmable output synthesizers (P0, P1) generate clock frequencies from any multiple of 8kHz up to 77.76MHz in addition to 2kHz •Provides two DPLLs which are independently configurable through a serial peripheral interface •DPLL1 provides all the features necessary forgenerating SONET/SDH compliant clocks including automatic hitless reference switching, automatic mode selection (locked, free-run, holdover), and selectable loop bandwidth•DPLL2 provides a comprehensive set of features for generating derived output clocks and other general purpose clocks•Provides 8 reference inputs which support clock frequencies with any multiples of 8kHz up to 77.76MHz in addition to 2kHz•Provides 3 sync inputs for output frame pulse alignment•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay, and output to output phase alignment•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•Supports IEEE 1149.1 JTAG Boundary ScanJune 2006Figure 1 - Block DiagramZL30119 SONET/SDHOC-48/OC-192 Line Card SynchronizerData SheetOrdering InformationZL30119GGG 100 Pin CABGA Trays ZL30119GGG2100 Pin CABGA*Trays*Pb Free Tin/Silver/Copper-40o C to +85o CZL30119Data SheetApplications•AMCs for AdvancedTCA TM and MicroTCA Systems•Multi-Service Edge Switches or Routers•DSLAM Line Cards•WAN Line Cards•RNC/Mobile Switching Center Line Cards•ADM Line CardsZL30119Data SheetTable of Contents1.0 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.1 DPLL Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121.2 DPLL Mode Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.3 Ref and Sync Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.4 Ref and Sync Monitoring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151.5 Output Clocks and Frame Pulses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161.6 Configurable Input-to-Output and Output-to-Output Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182.0 Software Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193.0 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26ZL30119Data SheetList of FiguresFigure 1 - Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2 - Automatic Mode State Machine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Figure 3 - Reference and Sync Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 4 - Output Frame Pulse Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM Failures. . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Figure 6 - Output Clock Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Figure 7 - Phase Delay Adjustments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18ZL30119Data SheetList of TablesTable 1 - DPLL1 and DPLL2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Table 2 - Set of Pre-Defined Auto-Detect Clock Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 3 - Set of Pre-Defined Auto-Detect Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Table 4 - Output Clock and Frame Pulse Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 5 - Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19ZL30119Data Sheet The following table captures the changes from the December 2005 issue.Page Item Change22-23Software Register Description Changed the naming and description of the framepulse delay offset registers to clearly show thatthey form a 22-bit register spread out over 3 8-bitregisters. The 22-bit register must be considered amulti-byte register during a read or write operation.This affects registers 0x40-0x42, 0x45-0x47, and0x58-0x5A.ZL30119Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I d Input References (LVCMOS, Schmitt Trigger). These are input referencesavailable to both DPLL1 and DPLL2 for synchronizing output clocks. All eightinput references can be automatically or manually selected using softwareregisters. These pins are internally pulled down to Vss.B1 A1 A2sync0sync1sync2I d Frame Pulse Synchronization References (LVCMOS, Schmitt Trigger).These are the frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5 ns.These pins are internally pulled down to V ss.Output Clocks and Frame PulsesD10sdh_clk0O SONET/SDH Output Clock 0 (LVCMOS). This output can be configured toprovide any one of the SONET/SDH clock outputs up to 77.76MHz. The defaultfrequency for this output is 77.76MHz.G10sdh_clk1O SONET/SDH Output Clock 1 (LVCMOS). This output can be configured toprovide any one of the SONET/SDH clock outputs up to 77.76MHz. The defaultfrequency for this output is 19.44MHz.E10sdh_fp0O SONET/SDH Output Frame Pulse 0 (LVCMOS). This output can be configuredto provide virtually any style of output frame pulse synchronized with anassociated SONET/SDH family output clock. The default frequency for this framepulse output is 8kHz.F10sdh_fp1O SONET/SDH Output Frame Pulse 1 (LVCMOS). This output can be configuredto provide virtually any style of output frame pulse synchronized with anassociated SONET/SDH family output clock. The default frequency for this framepulse output is 2kHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 77.76MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2 kHz to 77.76 MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.J7p0_fp1O Programmable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30119Data SheetJ10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 77.76MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p1_clk0 frequency within the range of 2kHz to 77.76MHz. The default frequency for this output is 3.088MHz (2x DS1).H10fb_clk OFeedback Clock (LVCMOS). This output is a buffered copy of the feedback clock for DPLL1. The frequency of this output always equals the frequency of the selected reference.E1dpll2_ref ODPLL2 Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for DPLL2. Switching between input reference clocks at this output is not hitless.A9B10diff0_p diff0_n ODifferential Output Clock 0 (LVPECL). This output can be configured to provide any one of the available SDH clocks. The default frequency for this clock output is 155.52MHz.A10B9diff1_p diff1_nODifferential Output Clock 1 (LVPECL). This output can be configured to provide any one of the available SDH clocks. The default frequency for this clock output is 622.08MHz clock.Control H5rst_b IReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5dpll1_hs_enI uDPLL1 Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns DPLL1’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pull up to Vdd.C2D2dpll1_mod_sel0dpll1_mod_sel1I uDPLL1 Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for DPLL1 (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can becontrolled directly with these pins, or by accessing the dpll1_modesel register through the serial interface. This pin is internally pull up to Vdd.K1diff0_enI uDifferential Output 0 Enable (LVCMOS, Schmitt Trigger). When set high, the differential LVPECL output 0 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pull up to Vdd.D3diff1_enI uDifferential Output 1 Enable (LVCMOS, Schmitt Trigger). When set high, the differential LVPECL output 1 driver is enabled. When set low, the differential driver is tristated reducing power consumption.This pin is internally pull up to Vdd.Pin # Name I/O Type DescriptionZL30119Data SheetStatus H1dpll1_lockOLock Indicator (LVCMOS). This is the lock indicator pin for DPLL1. This output goes high when DPLL1’s output is frequency and phase locked to the input reference.J1dpll1_holdover OHoldover Indicator (LVCMOS). This pin goes high when DPLL1 enters the holdover mode.Serial Interface E2sck I Clock for Serial Interface (LVCMOS). Serial interface clock.F1si I Serial Interface Input (LVCMOS). Serial interface data input pin.G1so O Serial Interface Output (LVCMOS). Serial interface data output pin.E3cs_b I u Chip Select for Serial Interface (LVCMOS). Serial interface chip select. This pin is internally pull up to Vdd.G2int_bOInterrupt Pin (LVCMOS). Indicates a change of device status prompting the processor to read the enabled interrupt service registers (ISR). This pin is an open drain, active low and requires an external pull up to VDD.APLL Loop Filter A6sdh_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1AAnalog PLL External Loop Filter Reference.JTAG and Test J4tdoOTest Serial Data Out (Output). JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.K2tdiI uTest Serial Data In (Input). JTAG serial test instructions and data are shifted in on this pin. This pin is internally pull up to Vdd. If this pin is not used then it should be left unconnected.H4trst_bI uTest Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck I Test Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.J3tmsI uTest Mode Select (LVCMOS). JTAG signal that controls the state transitions of the TAP controller. This pin is internally pulled up to V DD . If this pin is not used then it should be left unconnected.Pin # NameI/O TypeDescriptionZL30119Data SheetMaster ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousB5C5G3NC No Connection. Leave unconnected.J2J6H7IC Internal Connection. Connect to ground.D1K6F2F3IC Internal Connection. Leave unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.Pin # Name I/OType DescriptionZL30119Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundD4D5D6D7E5E6E7F5F6F7G4G5G6G7E9F8F9H9V SSG G G G G G G G G G G G G G G G G G Ground. 0 Volts.A7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30119Data Sheet1.0 Functional DescriptionThe ZL30119 SONET/SDH Line Card Synchronizer is a highly integrated device that provides timing and synchronization for network interface cards. It incorporates two independent DPLLs, each capable of locking to one of eight input references and provides a wide variety of synchronized output clocks and frame pulses.1.1 DPLL FeaturesThe ZL30119 provides two independently controlled Digital Phase-Locked Loops (DPLL1, DPLL2) for clock and/or frame pulse synchronization. Table 1 lists the feature summary for both DPLLs.FeatureDPLL1DPLL2Modes of Operation Free-run, Normal (locked), Holdover Free-run, Normal (locked), Holdover.Loop Bandwidth User selectable: 14Hz, 28Hz, or wideband 1 (890Hz / 56Hz / 14Hz)1. In the wideband mode, the loop bandwidth depends on the frequency of the reference input. For reference frequencies equal to or greater than 64kHz, the loop bandwidth = 890 Hz. For reference frequencies equal to or greater than 8kHz and less than 64 kHz, the loop bandwidth = 56 Hz. For reference frequencies equal to 2kHz, the loop bandwidth is equal to 14Hz.Fixed: 14HzPhase Slope Limiting User selectable: 885ns/s, 7.5µs/s, 61µs/s, or unlimited User selectable: 61µs/s, or unlimited Pull-in Range Fixed: 130ppm Fixed: 130ppm Reference Inputs Ref0 to Ref7Ref0 to Ref7Sync InputsSync0, Sync1, Sync2Sync inputs are not supported.Input Ref Frequencies 2kHz, N * 8kHz up to 77.76 MHz 2kHz, N * 8kHz up to 77.76 MHz Supported Sync Input Frequencies 166.67Hz, 400Hz, 1kHz, 2kHz, 8kHz, 64kHz.Sync inputs are not supported.Input Reference Selection/Switching Automatic (based on programmable priority and revertiveness), or manual Automatic (based on programmable priority and revertiveness), or manual Hitless Ref Switching Can be enabled or disabledCan be enabled or disabled Output Clocksdiff0_p/n, diff1_p/n, sdh_clk0, sdh_clk1, p0_clk0, p0_clk1, p1_clk0, p1_clk1, fb_clk.p0_clk0, p0_clk1, p1_clk0, p1_clk1.Output Frame Pulses sdh_fp0, sdh_fp1, p0_fp0, p0_fp1 synchronized to active sync reference.p0_fp0, p0_fp1 not aligned to sync reference.Supported Output Clock Frequencies As listed in Table 4As listed in Table 4 for p0_clk0, p0_clk1, p1_clk0, p1_clk1Supported Output Frame Pulse Frequencies As listed in Table 4As listed in Table 4 for p0_fp0, p0_fp not aligned to sync reference.External Pins Status IndicatorsLock, HoldoverNoneTable 1 - DPLL1 and DPLL2 FeaturesZL30119Data Sheet1.2 DPLL Mode ControlBoth DPLL1 and DPLL2 independently support three modes of operation - free-run, normal and holdover. The mode of operation can be manually set or controlled by an automatic state machine as shown in Figure 2.Figure 2 - Automatic Mode State MachineFree-runThe free-run mode occurs immediately after a reset cycle or when the DPLL has never been synchronized to areference input. In this mode, the frequency accuracy of the output clocks is equal to the frequency accuracy of the external master oscillator. Lock AcquisitionThe input references are continuously monitored for frequency accuracy and phase regularity. If at least one of the input references is qualified by the reference monitors, then the DPLL will begin lock acquisition on that input. Given a stable reference input, the ZL30119 will enter in the Normal (locked) mode.Normal (locked)The usual mode of operation for the DPLL is the normal mode where the DPLL phase locks to a selected qualified reference input and generates output clocks and frame pulses with a frequency accuracy equal to the frequency accuracy of the reference input. While in the normal mode, the DPLL’s clock and frame pulse outputs comply with the MTIE and TDEV wander generation specifications as described in Telcordia and ITU-T telecommunication standards.HoldoverWhen the DPLL operating in the normal mode loses its reference input, and no other qualified references are available, it will enter the holdover mode and continue to generate output clocks based on historical frequency data collected while the DPLL was synchronized.ResetAnother reference is qualified and availablefor selectionPhase lock on the selected reference is achievedLock AcquisitionNormal (Locked)No references are qualified and available for selectionFree-RunHoldoverSelected referencefailsAll references are monitored for frequency accuracy and phase regularity, and at least one reference is qualified.Normal (Locked)ZL30119Data Sheet1.3 Ref and Sync InputsThere are eight reference clock inputs (ref0 to ref7) available to both DPLL1 and DPLL2. The selected reference input is used to synchronize the output clocks. Each of the DPLLs have independent reference selectors which can be controlled using a built-in state machine or set in a manual mode.Figure 3 - Reference and Sync InputsIn addition to the reference inputs, DPLL1 has three optional frame pulse synchronization inputs (sync0 to sync2)used to align the output frame pulses. The sync n input is selected with its corresponding ref n input, where n = 0, 1,or 2. Note that the sync input cannot be used to synchronize the DPLL, it only determines the alignment of the frame pulse outputs. An example of output frame pulse alignment is shown in Figure 4.Figure 4 - Output Frame Pulse Alignmentref7:0sync2:0DPLL2DPLL1ref nsdh/p0/p1_clk xsdh/p0_fp xWithout a frame pulse signal at the sync input, the output frame pulses will align to any arbitrary cycle of its associated output clock.sync n - no frame pulse signal presentWhen a frame pulse signal is present at the sync input, the DPLL will align the output frame pulses to the output clock edge that is aligned to the input frame pulse.ref n sdh/p0/p1_clk xsdh/p0_fp xsync nn = 0, 1, 2x = 0, 1n = 0, 1, 2x = 0, 1ZL30119Data Sheet Each of the ref inputs accept a single-ended LVCMOS clock with a frequency ranging from 2kHz to 77.76MHz. Built-in frequency detection circuitry automatically determines the frequency of the reference if its frequency is within the set of pre-defined frequencies as shown in Table 2. Custom frequencies definable in multiples of 8kHz are also available.2 kHz8 kHz64 kHz1.544 MHz2.048 MHz6.48 MHz8.192 MHz16.384 MHz19.44 MHz38.88 MHz77.76 MHzCustom ACustom BTable 2 - Set of Pre-Defined Auto-Detect Clock FrequenciesEach of the sync inputs accept a single-ended LVCMOS frame pulse. Since alignment is determined from the rising edge of the frame pulse, there is no duty cycle restriction on this input, but there is a minimum pulse width requirement of 5 ns. Frequency detection for the sync inputs is automatic for the supported frame pulse frequencies shown in Table 3.166.67 Hz(48x 125 µs frames)400 Hz1 kHz2 kHz8 kHz64 kHzTable 3 - Set of Pre-Defined Auto-Detect Sync Frequencies1.4 Ref and Sync MonitoringAll input references (ref0 to ref7) are monitored for frequency accuracy and phase regularity. New references are qualified before they can be selected as a synchronization source, and qualified references are continuously monitored to ensure that they are suitable for synchronization. The process of qualifying a reference depends on four levels of monitoring.Single Cycle Monitor (SCM)The SCM block measures the period of each reference clock cycle to detect phase irregularities or a missing clock edge. In general, if the measured period deviates by more than 50% from the nominal period, then an SCM failure (scm_fail) is declared.ZL30119Data SheetCoarse Frequency Monitor (CFM)The CFM block monitors the reference frequency over a measurement period of 30 µs so that it can quickly detect large changes in frequency. A CFM failure (cfm_fail) is triggered when the frequency has changed by more than 3%or approximately 30000ppm.Precise Frequency Monitor (PFM)The PFM block measures the frequency accuracy of the reference over a 10 second interval. To ensure an accurate frequency measurement, the PFM measurement interval is re-initiated if phase or frequency irregularities are detected by the SCM or CFM. The PFM provides a level of hysteresis between the acceptance range and the rejection range to prevent a failure indication from toggling between valid and invalid for references that are on the edge of the acceptance range.When determining the frequency accuracy of the reference input, the PFM uses the external oscillator’s output frequency (f ocsi ) as its point of reference. Guard Soak Timer (GST)The GST block mimics the operation of an analog integrator by accumulating failure events from the CFM and the SCM blocks and applying a selectable rate of decay when no failures are detected.As shown in Figure 5, a GST failure (gst_fail) is triggered when the accumulated failures have reached the upper threshold during the disqualification observation window. When there are no CFM or SCM failures, the accumulator decrements until it reaches its lower threshold during the qualification window.Figure 5 - Behaviour of the Guard Soak Timer during CFM or SCM FailuresAll sync inputs (sync0 to sync2) are continuously monitored to ensure that there is a correct number of reference clock cycles within the frame pulse period.1.5 Output Clocks and Frame PulsesThe ZL30119 offers a wide variety of outputs including two low-jitter differential LVPECL clocks (diff0_p/n,diff1_p/n ), two SONET/SDH LVCMOS (sdh_clk0, sdh_clk1) output clocks and four programmable LVCMOS (p0_clk0, p0_clk1, p1_clk0, p1_clk1) output clocks. In addition to the clock outputs, two LVCMOS SONET/SDH frame pulse outputs (sdh_fp0, sdh_fp1) and two LVCMOS programmable frame pulses (p0_fp0, p0_fp1) are also available.refCFM or SCM failuresupper thresholdlower thresholdt d - disqualification timet q - qualification time = n * t dt dt qgst_failZL30119Data SheetThe feedback clock (fb_clk ) of DPLL1 is available as an output clock. Its output frequency is always equal to DPLL1’s selected input frequency.The output clocks and frame pulses derived from the SONET/SDH APLL are always synchronous with DPLL1, and the clocks and frame pulses generated from the programmable synthesizers can be synchronized to either DPLL1or DPLL2. This allows the ZL30119 to have two independent timing paths.Figure 6 - Output Clock ConfigurationThe supported frequencies for the output clocks and frame pulses are shown in Table 4.diff0_p/n, diff1_p/n (LVPECL)sdh_clk0, sdh_clk1(LVCMOS)p0_clk0, p1_clk0(LVCMOS)p0_clk1, p1_clk1(LVCMOS)sdh_fp0, shd_fp1, p0_fp0, p0_fp1(LVCMOS)6.48 MHz 6.48 MHz 2 kHz p x _clk0 p x _clk1 =2M166.67 Hz (48x 125 µs frames)19.44 MHz 9.72 MHz N * 8 kHz (up to 77.76 MHz)400 Hz 38.88 MHz 12.96 MHz 1 kHz 51.84 MHz 19.44 MHz 2 kHz 77.76 MHz 25.92 MHz 4 kHz 155.52 MHz 38.88 MHz 8 kHz 311.04 MHz 51.84 MHz 32 kHz 622.08 MHz77.76 MHz64 kHzTable 4 - Output Clock and Frame Pulse FrequenciesDPLL2p0_clk0p0_fp0p0_clk1p0_fp1 P0 SynthesizerDPLL1p1_clk0p1_clk1P1 Synthesizersdh_clk0sdh_fp0sdh_clk1sdh_fp1SONET/SDHAPLLdiff0diff1Feedback Synthesizerfb_clkZL30119Data Sheet1.6 Configurable Input-to-Output and Output-to-Output DelaysThe ZL30119 allows programmable static delay compensation for controlling input-to-output and output-to-output delays of its clocks and frame pulses.All of the output synthesizers (SONET/SDH, P0, P1, Feedback) locked to DPLL1 can be configured to lead or lag the selected input reference clock using the DPLL1 Fine Delay . The delay is programmed in steps of 119.2ps with a range of -128 to +127 steps giving a total delay adjustment in the range of -15.26ns to +15.14ns. Negative values delay the output clock, positive values advance the output clock. Synthesizers that are locked to DPLL2 are unaffected by this delay adjustment.In addition to the fine delay introduced in the DPLL1 path, the SONET/SDH, P0, and P1 synthesizers have the ability to add their own fine delay adjustments using the P0 Fine Delay , P1 Fine Delay , and SDH Fine Delay .These delays are also programmable in steps of 119.2ps with a range of -128 to +127 steps.In addition to these delays, the single-ended output clocks of the SONET/SDH, P0, and P1 synthesizers can be independently offset by 90, 180 and 270 degrees using the Coarse Delay , and the SONET/SDH differential outputs can be independently delayed by -1.6ns, 0ns, +1.6ns or +3.2ns using the Diff Delay . The output frame pulses (SONET/SDH, P0) can be independently offset with respect to each other using the FP Delay .Figure 7 - Phase Delay AdjustmentsDPLL1DPLL2P0 Fine Delayp0_clk0p0_clk1p0_fp0p0_fp1 P0 SynthesizerCoarse DelayCoarse Delay FP Delay FP Delay fb_clkp1_clk0p1_clk1 P1 Fine DelayDiff Delay Diff Delaydiff0diff1 SONET/SDHAPLLsdh_clk0sdh_clk1sdh_fp0sdh_fp1 SDH Fine DelayFeedback SynthesizerDPLL1 Fine DelayCoarse Delay Coarse Delay FP Delay FP DelayCoarse Delay Coarse DelayP1 Synthesizer。

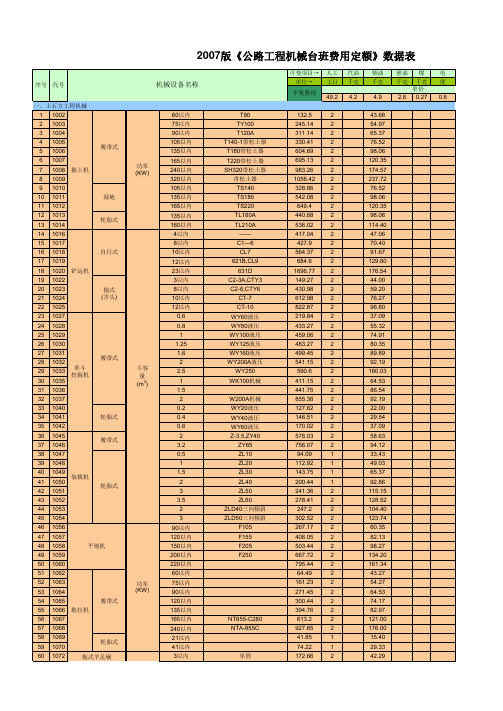

版公路工程机械台班费用定额数据表 含柴油发电机油料消耗

7000以内 9000以内

YLY-7000 YLY-9000

135 1188

22000以内

CZL9350

136 1190 137 1191

沥青洒布机

容量 (L)

500以内 1000以内

LS-500 LSA-1000A

138 1192

2000以内

LS-1700

139 1193 140 1194

沥青洒布车

2

330.41

2

604.69

2

695.13

2

983.26

2

1056.42

2

328.86

2

542.08

2

649.4

2

440.68

2

536.02

2

417.04

2

427.9

2

564.37

2

684.6

2

1696.77

2

149.27

2

430.98

2

612.98

2

822.87

2

219.84

2

433.27

2

459.06

19 1022

20 1023 21 1024

拖式 (含头)

22 1025

23 1027

24 1028

25 1029

26 1030

27 1031

28 1032

29

1033

单斗 挖掘机

30 1035

履带式

31 1036

32 1037

33 1040 34 1041

轮胎式

35 1042

36 1045 37 1046

YZ8 YZJ10B CA25PD YZ18A,YZJ19A TZT16(K) HW-280 HB-120 带10t夯锤头 带15t夯锤头 带20t夯锤头

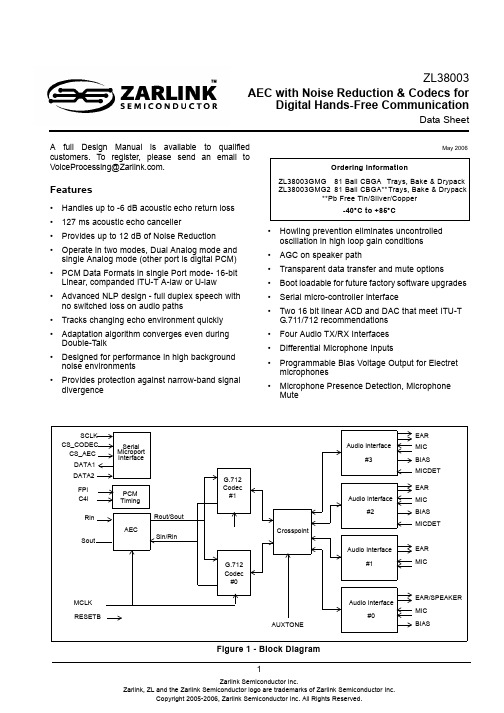

zl38003中文资料_数据手册_IC数据表

• Handles up to -6 dB acoustic echo return loss

• 127 ms acoustic echo canceller

• Provides up to 12 dB of Noise Reduction

• Operate in two modes, Dual Analog mode and single Analog mode (other port is digital PCM)

The AEC uses an advanced adaptive filter algorithm that is double-talk stable, allowing convergence even while both parties are talking. This algorithm continually tracks changes in the echo path, regardless of double-talk, as long as a reference signal is available for the echo canceller.

• PCM Data Formats in single Port mode- 16-bit Linear, companded ITU-T A-law or U-law

• Advanced NLP design - full duplex speech with no switched loss on audio paths

MT93L16

ZL38001

ZL38002

ZL38003

Description AEC for analog hands- AEC for analog hands- AEC with noise reduction for digital

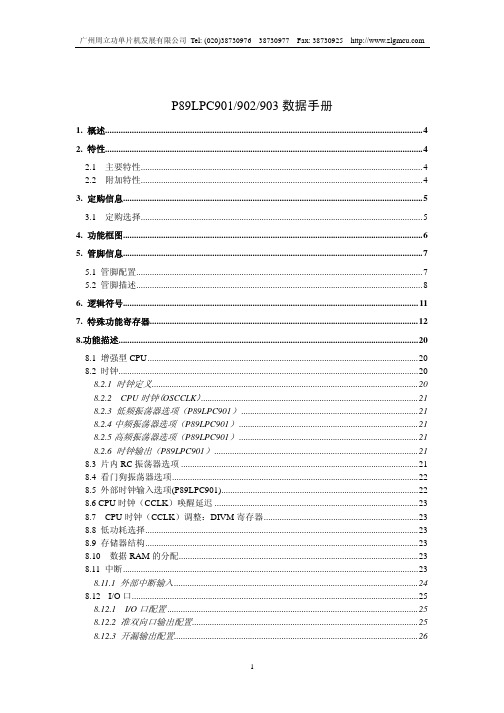

P89LPC901_902_903中文数据完整手册

3. 定购信息......................................................................................................................................5 3.1 定购选择..............................................................................................................................5

4. 功能框图......................................................................................................................................6 5. 管脚信息......................................................................................................................................7 5.1 管脚配置................................................................................................................................7 5.2 管脚描述................................................................................................................................8 6. 逻辑符号.................................................................................................................................... 11 7. 特殊功能寄存器........................................................................................................................12 8.功能描述......................................................................................................................................20 8.1 增强型 CPU.........................................................................................................................20 8.2 时钟......................................................................................................................................20 8.2.1 时钟定义 .......................................................................................................................20 8.2.2 CPU 时钟(OSCCLK) .................................................................................................21 8.2.3 低频振荡器选项(P89LPC901) ...............................................................................21 8.2.4 中频振荡器选项(P89LPC901) ................................................................................21 8.2.5 高频振荡器选项(P89LPC901) ................................................................................21 8.2.6 时钟输出(P89LPC901) ...........................................................................................21 8.3 片内 RC 振荡器选项 ..........................................................................................................21 8.4 看门狗振荡器选项 ..............................................................................................................22 8.5 外部时钟输入选项(P89LPC901)........................................................................................22 8.6 CPU 时钟(CCLK)唤醒延迟 ...........................................................................................23 8.7 CPU 时钟(CCLK)调整:DIVM 寄存器 .....................................................................23 8.8 低功耗选择 ..........................................................................................................................23 8.9 存储器结构 ..........................................................................................................................23 8.10 数据 RAM 的分配...........................................................................................................23 8.11 中断 ....................................................................................................................................23 8.11.1 外部中断输入 .............................................................................................................24 8.12 I/O 口 ................................................................................................................................25 8.12.1 I/O 口配置 ................................................................................................................25 8.12.2 准双向口输出配置 .....................................................................................................25 8.12.3 开漏输出配置 .............................................................................................................26

微塞米ZL3066系列1-3通道10输入18输出线路卡时间IC产品简介说明书

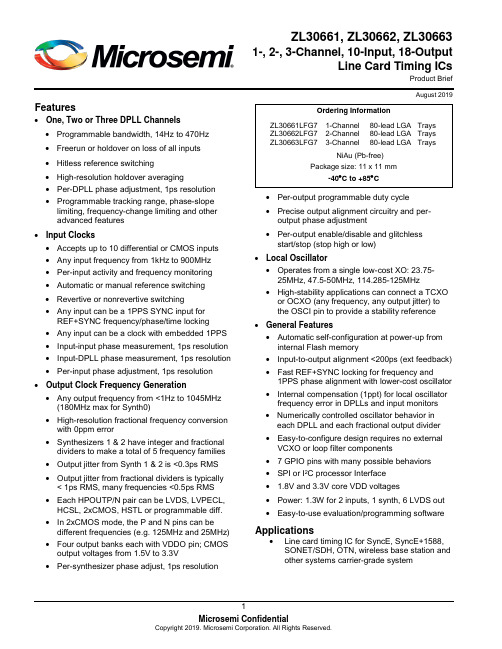

ZL30661, ZL30662, ZL306631-, 2-, 3-Channel, 10-Input, 18-OutputLine Card Timing ICsProduct BriefAugust 2019 Features•One, Two or Three DPLL Channels•Programmable bandwidth, 14Hz to 470Hz•Freerun or holdover on loss of all inputs•Hitless reference switching•High-resolution holdover averaging•Per-DPLL phase adjustment, 1ps resolution•Programmable tracking range, phase-slope limiting, frequency-change limiting and otheradvanced features•Input Clocks•Accepts up to 10 differential or CMOS inputs•Any input frequency from 1kHz to 900MHz•Per-input activity and frequency monitoring•Automatic or manual reference switching•Revertive or nonrevertive switching•Any input can be a 1PPS SYNC input for REF+SYNC frequency/phase/time locking •Any input can be a clock with embedded 1PPS •Input-input phase measurement, 1ps resolution •Input-DPLL phase measurement, 1ps resolution •Per-input phase adjustment, 1ps resolution •Output Clock Frequency Generation•Any output frequency from <1Hz to 1045MHz (180MHz max for Synth0)•High-resolution fractional frequency conversion with 0ppm error•Synthesizers 1 & 2 have integer and fractional dividers to make a total of 5 frequency families •Output jitter from Synth 1 & 2 is <0.3ps RMS•Output jitter from fractional dividers is typically < 1ps RMS, many frequencies <0.5ps RMS •Each HPOUTP/N pair can be LVDS, LVPECL, HCSL, 2xCMOS, HSTL or programmable diff.•In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz) •Four output banks each with VDDO pin; CMOS output voltages from 1.5V to 3.3V•Per-synthesizer phase adjust, 1ps resolution•Per-output programmable duty cycle•Precise output alignment circuitry and per-output phase adjustment•Per-output enable/disable and glitchlessstart/stop (stop high or low)•Local Oscillator•Operates from a single low-cost XO: 23.75-25MHz, 47.5-50MHz, 114.285-125MHz •High-stability applications can connect a TCXO or OCXO (any frequency, any output jitter) tothe OSCI pin to provide a stability reference •General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <200ps (ext feedback) •Fast REF+SYNC locking for frequency and 1PPS phase alignment with lower-cost oscillator •Internal compensation (1ppt) for local oscillator frequency error in DPLLs and input monitors •Numerically controlled oscillator behavior in each DPLL and each fractional output divider•Easy-to-configure design requires no external VCXO or loop filter components•7 GPIO pins with many possible behaviors•SPI or I2C processor Interface• 1.8V and 3.3V core VDD voltages•Power: 1.3W for 2 inputs, 1 synth, 6 LVDS out•Easy-to-use evaluation/programming software Applications•Line card timing IC for SyncE, SyncE+1588, SONET/SDH, OTN, wireless base station andother systems carrier-grade systemOrdering InformationZL30661LFG7 1-Channel 80-lead LGA TraysZL30662LFG7 2-Channel 80-lead LGA TraysZL30663LFG7 3-Channel 80-lead LGA TraysNiAu (Pb-free)Package size: 11 x 11 mm-40︒C to +85︒C1. Block DiagramFigure 1 - Functional Block Diagram2. Application ExampleFigure 2 - Synchronous Ethernet and IEEE 1588 Line Card ApplicationFracDiv IntDiv FracDivIntDivHP Synthesizer 2low-jitterHPOUT6P HPOUT6N HPOUT7P HPOUT7NDIVREF0P DPLL0R S T _BC S _B _A S E L 0S C K _S C LS O _A S E L 1S I _S D AG P I O [8:0]Microprocessor Port SPI or I2C I/F & GPIO Pins One Diff / Two Single-Ended REF0N REF1P One Diff / Two Single-Ended REF1N REF2P One Diff / Two Single-EndedREF2NREF3P One Diff / Two Single-Ended REF3N REF4P One Diff / Two Single-EndedREF4NReference Monitors & State MachinesDPLL1DPLL2HP Synthesizer 1low-jitterGP Synthesizer 0general purpos eGPOUT0GPOUT1DIV DIVXO Optional x2O S C IO S C OMaster Clock M C L K I N _PDIVHPOUT4P HPOUT4N HPOUT5P HPOUT5N DIV DIVHPOUT0P HPOUT0N HPOUT1P HPOUT1N DIVDIV HPOUT2P HPOUT2N HPOUT3P HPOUT3NDIVDIVM C L K I N _NS R S T _BDPLL0Synth0DPLL1Synth1Synth22x 156.25MHz differential 2x 125MHz differential 25MHz CMOS 2x 155.52MHz, 161.1328125MHz or other frequencyto PHY transmitters, line card Ethernet switch IC, etc.from PHY receivers2x 156.25MHz differential 2x 125MHz differential 2x 25MHz CMOS2x 19.44MHz, 25MHzor 8kHz CMOS to central timing functionsfrom central timing functionsXO2x 19.44MHz or 25MHz CMOS1PPS CMOSoptional 2x 1PPS CMOSDPLL1 only present on ZL30662 and ZL30663 DPLL2 only present on ZL306633. Detailed Features3.1 Input Block Features•Ten input reference pins; each can accept a CMOS signal or the POS side of a differential pair; or two can be paired to accept both sides of a differential pair•Any input can be a SYNC signal for REF+SYNC frequency/phase/time locking•Any input can be a clock signal with embedded PPS signal (duty cycle distortion indicates PPS location) •Input clocks can be any frequency from 1kHz up to 900MHz (180MHz max for CMOS inputs)•Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN, wireless•Inputs constantly monitored by programmable frequency and single-cycle monitors•Single-cycle monitor can quickly disqualify a reference when measured period is incorrect•Frequency measurement (ppb or Hz) and monitoring (coarse, fine, and frequency-step monitors)•Optional input clock invalidation on GPIO assertion to react to LOS signals from PHYs•Input-to-input phase measurement, 1ps resolution•Input-to-DPLL phase measurement, 1ps resolution•Per-input phase adjustment, 1ps resolution3.2 DPLL Features•One, two or three full-featured DPLLs•Very high-resolution DPLL architecture•State machine automatically transitions among freerun, tracking and holdover states•Revertive or nonrevertive reference selection algorithm•Programmable bandwidth from 14Hz to 470Hz•Less than 0.1dB gain peaking•Fast frequency/phase/time lock capability for clock+1PPS input references•Programmable phase-slope limiting (PSL)•Programmable frequency rate-of-change limiting (FCL)•Programmable tracking range (i.e. hold-in range)•Truly hitless reference switching•Per-DPLL phase adjustment, 1ps resolution•High-resolution frequency and phase measurement•Fast detection of input clock failure and transition to holdover mode•High-resolution holdover frequency averaging•Time-of-Day registers: 48-bit seconds, 32-bit nanoseconds, writeable on input PPS edge3.3 Synthesizer Features•Any-to-any frequency conversion with 0ppm error•Two low-jitter synthesizers (Synth1, Synth2) with very high-resolution fractional scaling (i.e. non-integer multiplication)•Two output dividers per low-jitter synthesizer: one integer (4 to 15 plus half divides 4.5 to 7.5) and one 40-bit fractional•One general-purpose synthesizer (Synth0)• A total of five output frequency families•Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter components3.4 Low-Jitter Output Clock Features•Up to 16 single-ended outputs (up to 8 differential outputs) from Synth1 and Synth2•Each output can be one differential output or two CMOS outputs•Output clocks can be any frequency from 1Hz to 1045MHz (250MHz max for CMOS and HSTL outputs) •Output jitter from Synth1 and Synth2 integer dividers is <0.3ps RMS•Output jitter from fractional dividers is <1ps RMS, many frequencies <0.5ps RMS•In CMOS mode, the HPOUTxN frequency can be an integer divisor of the HPOUTxP frequency (Example 1: HPOUT3P 125MHz, HPOUT3N 25MHz. Example 2: HPOUT2P 25MHz, HPOUT2N 1Hz)•Outputs directly interface (DC coupled) with LVDS, LVPECL, HSTL, HCSL and CMOS components •Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN•Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components•Can produce PCIe clocks•Sophisticated output-to-output phase alignment•Per-synthesizer phase adjustment, 1ps resolution•Per-output phase adjustment•Per-output duty cycle / pulse width configuration•Per-output enable/disable•Per-output glitchless start/stop (stop high or low)3.5 General-Purpose Output Clock Features•Two CMOS outputs from Synth0•Any frequency from 1Hz to 180MHz•Output jitter is typically 20-30ps•Useful for applications where the component or system receiving the signal has low bandwidth such asa central timing IC•Can output a clock signal with embedded PPS (ePPS) (duty cycle distortion indicates PPS location) 3.6 Local Oscillator•Operates from a single low-cost XO (jitter reference for the device). Acceptable frequencies: 23.75MHz to 25MHz, 47.5MHz to 50MHz, 114.285MHz to 125MHz. Best jitter: ≥48MHz.•High stability applications can connect a TCXO or OCXO (any frequency, any output jitter) to a REF pin to provide a separate stability reference•This ability to have separate jitter and stability references greatly reduces the cost of the TCXO or OCXO (no jitter requirement, no high-frequency-requirement) and allows reuse of already-qualifiedTCXO and OCXO components3.7 General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <200ps with external feedback•Fast REF+SYNC locking for frequency and 1PPS phase alignment with lower-cost oscillator•Generates output SYNC signals: 1PPS (IEEE 1588), 2kHz or 8kHz (SONET/SDH) or other frequency •JESD204B clocking: device clock and SYSREF signal generation with skew adjustment•Internal compensation for local oscillator frequency error in DPLLs and input monitors, 1ppt resolution •Numerically controlled oscillator (NCO) behavior allows system software to steer DPLL frequency or fractional output divider frequency with resolution better than 0.005ppt•Spread-spectrum modulation available in each fractional output divider (PCIe compliant)•Seven general-purpose I/O pins each with many possible status and control options•SPI or I2C serial microprocessor interface3.8 Evaluation Software•Simple, intuitive Windows-based graphical user interface•Supports all device features and register fields•Makes lab evaluation of the device quick and easy•Generates configuration scripts to be stored in internal Flash memory•Generates full or partial configuration scripts to be run on a system processor•Works with or without an evaluation boardMicrosemi Corporate Headquarters One EnterpriseAliso Viejo, CA 92656 USAWithin the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at .Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer’s responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.。

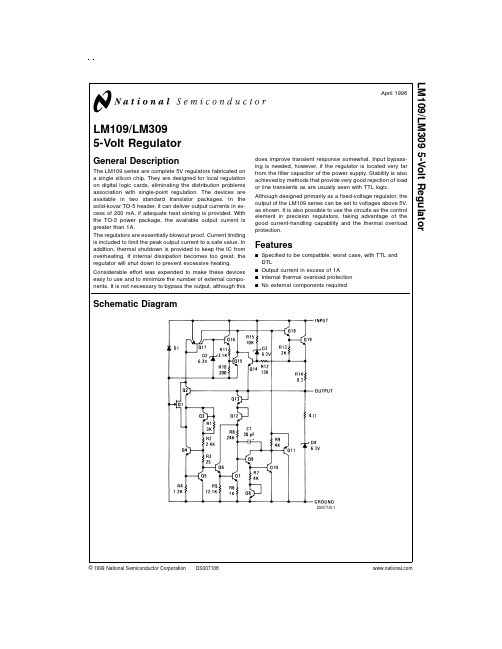

LM109资料

LM109/LM3095-Volt RegulatorGeneral DescriptionThe LM109series are complete 5V regulators fabricated on a single silicon chip.They are designed for local regulation on digital logic cards,eliminating the distribution problems association with single-point regulation.The devices are available in two standard transistor packages.In the solid-kovar TO-5header,it can deliver output currents in ex-cess of 200mA,if adequate heat sinking is provided.With the TO-3power package,the available output current is greater than 1A.The regulators are essentially blowout proof.Current limiting is included to limit the peak output current to a safe value.In addition,thermal shutdown is provided to keep the IC from overheating.If internal dissipation becomes too great,the regulator will shut down to prevent excessive heating.Considerable effort was expended to make these devices easy to use and to minimize the number of external compo-nents.It is not necessary to bypass the output,although thisdoes improve transient response somewhat.Input bypass-ing is needed,however,if the regulator is located very far from the filter capacitor of the power supply.Stability is also achieved by methods that provide very good rejection of load or line transients as are usually seen with TTL logic.Although designed primarily as a fixed-voltage regulator,the output of the LM109series can be set to voltages above 5V,as shown.It is also possible to use the circuits as the control element in precision regulators,taking advantage of the good current-handling capability and the thermal overload protection.Featuresn Specified to be compatible,worst case,with TTL and DTLn Output current in excess of 1An Internal thermal overload protection n No external components requiredSchematic DiagramDS007138-1April 1998LM109/LM3095-Volt Regulator©1999National Semiconductor Corporation Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Input Voltage35VPower DissipationInternally LimitedOperating Junction Temperature Range LM109−55˚C to +150˚C LM3090˚C to +125˚C Storage Temperature Range −65˚C to +150˚CLead Temperature (Soldering,10sec.)300˚CElectrical Characteristics (Note 2)ParameterConditionsLM109LM309UnitsMinTyp Max Min Typ Max Output Voltage T j =25˚C 4.75.05 5.3 4.85.05 5.2V Line Regulation T j =25˚C 4.0504.050mV 7.10V ≤V IN ≤25V Load RegulationT j =25˚CTO-39Package 5mA ≤I OUT ≤0.5A 15501550mV TO-3Package5mA ≤I OUT ≤1.5A 1510015100mV Output Voltage7.40V ≤V IN ≤25V, 4.65.44.755.25V5mA ≤I OUT ≤I MAX ,P <P MAXQuiescent Current 7.40V ≤V IN ≤25V 5.210 5.210mA Quiescent Current Change 7.40V ≤V IN ≤25V 0.50.5mA 5mA ≤I OUT ≤I MAX 0.80.8mA Output Noise Voltage T A =25˚C4040µV10Hz ≤f ≤100kHzLong Term Stability 1020mV Ripple Rejection T j =25˚C 5050dBThermal Resistance,(Note 3)Junction to CaseTO-39Package 1515˚C/W TO-3Package2.52.5˚C/WNote 1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note 2:Unless otherwise specified,these specifications apply −55˚C ≤T j ≤+150˚C for the LM109and 0˚C ≤T j ≤+125˚C for the LM309;V IN =10V;and I OUT =0.1A for the TO-39package or I OUT =0.5A for the TO-3package.For the TO-39package,I MAX =0.2A and P MAX =2.0W.For the TO-3package,I MAX =1.0A and P MAX =20W.Note 3:Without a heat sink,the thermal resistance of the TO-39package is about 150˚C/W,while that of the TO-3package is approximately 35˚C/W.With a heat sink,the effective thermal resistance can only approach the values specified,depending on the efficiency of the sink.Note 4:Refer to RETS109H drawing for LM109H or RETS109K drawing for LM109K military specifications.Connection DiagramsMetal Can PackagesDS007138-33Order Number LM109H,LM109H/883or LM309HSee NS Package Number H03ADS007138-34Order Number LM109K STEEL orLM309K STEELSee NS Package Number K02A Order Number LM109K/883See NS Package Number K02C2Application Hints1.Bypass the input of the LM109to ground with≥0.2µFceramic or solid tantalum capacitor if main filter capaci-tor is more than4inches away.2.Avoid insertion of regulator into“live”socket if inputvoltage is greater than10V.The output will rise to within 2V of the unregulated input if the ground pin does not make contact,possibly damaging the load.The LM109 may also be damaged if a large output capacitor is charged up,then discharged through the internal clamp zener when the ground pin makes contact.3.The output clamp zener is designed to absorb tran-sients only.It will not clamp the output effectively if a fail-ure occurs in the internal power transistor structure.Ze-ner dynamic impedance is≈4Ω.Continuous RMS current into the zener should not exceed0.5A.4.Paralleling of LM109s for higher output current is notrecommended.Current sharing will be almost nonexist-ent,leading to a current limit mode operation for devices with the highest initial output voltage.The current limit devices may also heat up to the thermal shutdown point (≈175˚C).Long term reliability cannot be guaranteed under these conditions.5.Preventing latchoff for loads connected to negativevoltage:If the output of the LM109is pulled negative by a high cur-rent supply so that the output pin is more than0.5V negative with respect to the ground pin,the LM109can latch off.This can be prevented by clamping the ground pin to the output pin with a germanium or Schottky diode as shown.A silicon diode(1N4001)at the output is also needed to keep the positive output from being pulled too far negative.The10Ωresistor will raise+V OUT by≈0.05V.Crowbar Overvoltage Protection Typical Performance Characteristics DS007138-7Input CrowbarDS007138-8Output CrowbarDS007138-9*Zener is internal to LM109.**Q1must be able to withstand7A continuous current if fusing is not used at regulator input.LM109bond wires will fuse at currents above7A.†Q2is selected for surge capability.Consideration must be given to filter capacitor size,transformer impedance,and fuse blowing time.††Trip point is≈7.5V.Maximum AveragePower Dissipation(LM109K)DS007138-16Maximum AveragePower Dissipation(LM309K)DS007138-17Output ImpedanceDS007138-18 3Typical Performance Characteristics(Continued)Maximum AveragePower Dissipation (LM109H)DS007138-19Maximum AveragePower Dissipation (LM309H)DS007138-20Ripple RejectionDS007138-21Current LimitCharacteristics (Note 5)DS007138-22Thermally Induced Output Voltage VariationDS007138-23Ripple RejectionDS007138-24Note 5:Current limiting foldback characteristics are determined by input output differential,not by output voltage.Input-Output Differential (V)DS007138-25Output Voltage (V)DS007138-26Output Voltage (V)DS007138-27 4Typical Performance Characteristics(Continued)Typical ApplicationsQuiescent CurrentDS007138-28Quiescent CurrentDS007138-29Output Voltage NoiseDS007138-30Line Transient Response DS007138-31Load Transient ResponseDS007138-32Fixed 5V RegulatorDS007138-2*Required if regulator is located more than 4"from power supply filter capacitor.†Although no output capacitor is needed for stability,it does improve transient response.C2should be used whenever long wires are used to connect to the load,or when transient response is critical.Note:Pin 3electrically connected to case.Adjustable Output RegulatorDS007138-45Typical Applications(Continued)High Stability Regulator*DS007138-5*Regulation better than0.01%,load,line and temperature,can be obtained.†Determines zener current.May be adjusted to minimize thermal drift.‡Solid tantalum.Current RegulatorDS007138-6 *Determines output current.If wirewound resistor is used,bypass with0.1µF.6Physical Dimensions inches(millimeters)unless otherwise notedMetal Can Package(H)Order Number LM109H,LM109H/883or LM309HNS Package Number H03AMetal Can Package(K)Order Number LM109K STEEL,LM309K STEELNS Package Number K02A7Physical Dimensionsinches (millimeters)unless otherwise noted (Continued)LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant intothe body,or (b)support or sustain life,and whose fail-ure to perform when properly used in accordancewith instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507Metal Can Package (K)Mil-Aero ProductOrder Number LM109K/883NS Package Number K02CL M 109/L M 3095-V o l t R e g u l a t o rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

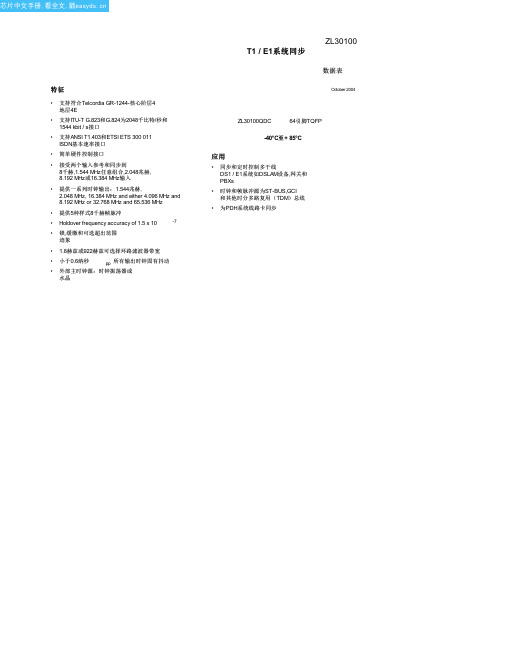

ZL30100_06中文资料(Zarlink Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

特征

• 支持符合Telcordia GR-1244-核心阶层4 地层4E

• 支持ITU-T G.823和G.824为2048千比特/秒和 1544 kbit / s接口

• 支持ANSI T1.403和ETSI ETS 300 011 ISDN基本速率接口

• 简单硬件控制接口

• 接受两个输入参考和同步到 8千赫,1.544 MHz任意组合,2.048兆赫, 8.192 MHz或16.384 MHz输入

• 提供一系列时钟输出:1.544兆赫, 2.048 MHz, 16.384 MHz and either 4.096 MHz and 8.192 MHz or 32.768 MHz and 65.536 MHz

3.0功能描述. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3.1参考选择多路复用器(MUX). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3.2参考监视器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3.3时间间隔误差(TIE)校正电路. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 3.4数字锁相环(DPLL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 3.5频率合成器. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 3.6状态机. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 3.7主时钟. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

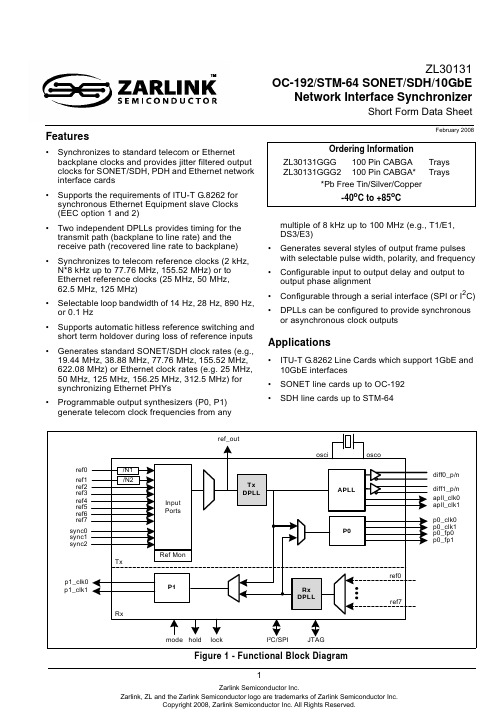

zl30131中文资料_数据手册_IC数据表

1Features•Synchronizes to standard telecom or Ethernet backplane clocks and provides jitter filtered output clocks for SONET/SDH, PDH and Ethernet network interface cards•Supports the requirements of ITU-T G.8262 for synchronous Ethernet Equipment slave Clocks (EEC option 1 and 2)•Two independent DPLLs provides timing for the transmit path (backplane to line rate) and the receive path (recovered line rate to backplane) •Synchronizes to telecom reference clocks (2kHz, N*8kHz up to 77.76MHz, 155.52MHz) or to Ethernet reference clocks (25MHz, 50MHz, 62.5MHz, 125MHz)•Selectable loop bandwidth of 14Hz, 28Hz, 890Hz, or 0.1Hz•Supports automatic hitless reference switching and short term holdover during loss of reference inputs •Generates standard SONET/SDH clock rates (e.g., 19.44MHz, 38.88MHz, 77.76MHz, 155.52MHz, 622.08MHz) or Ethernet clock rates (e.g. 25MHz, 50MHz, 125MHz, 156.25MHz, 312.5MHz) for synchronizing Ethernet PHYs•Programmable output synthesizers (P0, P1) generate telecom clock frequencies from anymultiple of 8kHz up to 100MHz (e.g., T1/E1, DS3/E3)•Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency •Configurable input to output delay and output to output phase alignment•Configurable through a serial interface (SPI or I 2C)•DPLLs can be configured to provide synchronous or asynchronous clock outputsApplications•ITU-T G.8262 Line Cards which support 1GbE and 10GbE interfaces•SONET line cards up to OC-192•SDH line cards up to STM-64February 2008Figure 1 - Functional Block DiagramZL30131OC-192/STM-64 SONET/SDH/10GbENetwork Interface SynchronizerShort Form Data SheetOrdering InformationZL30131GGG 100 Pin CABGA TraysZL30131GGG2 100 Pin CABGA*Trays*Pb Free Tin/Silver/Copper-40o C to +85o CZL30131Short Form Data Sheet Pin DescriptionPin # Name I/OType DescriptionInput ReferenceC1 B2 A3 C3 B3 B4 C4 A4ref0ref1ref2ref3ref4ref5ref6ref7I u Input References 7:0 (LVCMOS, Schmitt Trigger). These input references areavailable to both the Tx DPLL and the Rx DPLL for synchronizing output clocks.All eight input references can lock to any multiple of 8kHz up to 77.76MHzincluding 25MHz and 50MHz. Input ref0 and ref1 have additional configurablepre-dividers allowing input frequencies of 62.5MHz, 125MHz, and 155.52MHz.These pins are internally pulled up to V dd.B1 A1 A2sync0sync1sync2I u Frame Pulse Synchronization References 2:0 (LVCMOS, Schmitt Trigger).These are optional frame pulse synchronization inputs associated with inputreferences 0, 1 and 2. These inputs accept frame pulses in a clock format (50%duty cycle) or a basic frame pulse format with minimum pulse width of 5 ns.These pins are internally pulled up to V dd.Output Clocks and Frame PulsesA9 B10diff0_pdiff0_nO Differential Output Clock 0 (LVPECL). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks(6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz, 77.76MHz, 155.52MHz,311.04MHz, 622.08MHz). When in Ethernet mode, this output can beconfigured to provide any of the Ethernet clocks (25MHz, 50MHz, 62.5MHz,125MHz, 156.25MHz, 312.5MHz). See “Output Clocks and Frame Pulses”section on page22 more detail on clock frequency settings.A10 B9diff1_pdiff1_nO Differential Output Clock 1 (LVPECL). When in SONET/SDH mode, this output can be configured to provide any one of the available SONET/SDH clocks(6.48MHz, 19.44MHz, 38.88MHz, 51.84MHz, 77.76MHz, 155.52MHz,311.04MHz, 622.08MHz). When in Ethernet mode, this output can beconfigured to provide any of the Ethernet clocks (25MHz, 50MHz, 62.5MHz,125MHz, 156.25MHz, 312.5MHz). See “Output Clocks and Frame Pulses”section on page22 more detail on clock frequency settings.D10apll_clk0O APLL Output Clock 0 (LVCMOS). This output can be configured to provide anyone of the SONET/SDH clock outputs up to 77.76MHz or any of the Ethernetclock rates up to 125MHz. The default frequency for this output is 77.76MHz.G10apll_clk1O APLL Output Clock 1 (LVCMOS). This output can be configured to provide anyone of the SONET/SDH clock outputs up to 77.76MHz or any of the Ethernetclock rates up to 125MHz. The default frequency for this output is 19.44MHz.K9p0_clk0O Programmable Synthesizer 0 - Output Clock 0 (LVCMOS). This output can beconfigured to provide any frequency with a multiple of 8kHz up to 100MHz inaddition to 2kHz. The default frequency for this output is 2.048MHz.K7p0_clk1O Programmable Synthesizer 0 - Output Clock 1 (LVCMOS). This is aprogrammable clock output configurable as a multiple or division of the p0_clk0frequency within the range of 2 kHz to 100 MHz. The default frequency for thisoutput is 8.192MHz.K8p0_fp0O Programmable Synthesizer 0 - Output Frame Pulse 0 (LVCMOS). This outputcan be configured to provide virtually any style of output frame pulse associatedwith the p0 clocks. The default frequency for this frame pulse output is 8kHz.ZL30131Short Form Data SheetJ7p0_fp1OProgrammable Synthesizer 0 - Output Frame Pulse 1 (LVCMOS). This output can be configured to provide virtually any style of output frame pulse associated with the p0 clocks. The default frequency for this frame pulse output is 8kHz J10p1_clk0OProgrammable Synthesizer 1 - Output Clock 0 (LVCMOS). This output can be configured to provide any frequency with a multiple of 8kHz up to 100MHz in addition to 2kHz. The default frequency for this output is 1.544MHz (DS1).K10p1_clk1OProgrammable Synthesizer1 - Output Clock 1 (LVCMOS). This is a programmable clock output configurable as a multiple or division of the p1_clk0frequency within the range of 2kHz to 100MHz. The default frequency for this output is 3.088MHz (2x DS1).E1ref_out ORx DPLL Selected Output Reference (LVCMOS). This is a buffered copy of the output of the reference selector for the Rx DPLL. Switching between input reference clocks at this output is not hitless.Control H5rst_bIReset (LVCMOS, Schmitt Trigger). A logic low at this input resets the device. To ensure proper operation, the device must be reset after power-up. Reset should be asserted for a minimum of 300ns.J5hs_enI uTx DPLL Hitless Switching Enable (LVCMOS, Schmitt Trigger). A logic high at this input enables hitless reference switching. A logic low disables hitless reference switching and re-aligns the Tx DPLL’s output phase to the phase of the selected reference input. This feature can also be controlled through software registers. This pin is internally pulled up to Vdd.C2D2mode_0mode_1I uTx DPLL Mode Select 1:0 (LVCMOS, Schmitt Trigger). During reset, the levels on these pins determine the default mode of operation for the Tx DPLL (Automatic, Normal, Holdover or Freerun). After reset, the mode of operation can be controlled directly with these pins, or by accessing the tx_dpll_modesel register (0x1F) through the serial interface. This pin is internally pulled up to Vdd.K1diff0_enI uDifferential Output 0 Enable (LVCMOS, Schmitt Trigger). When set high, the differential LVPECL output 0 driver is enabled. When set low, the differential driver is tristated reducing power consumption. This pin is internally pulled up to Vdd.D3diff1_enI uDifferential Output 1 Enable (LVCMOS, Schmitt Trigger). When set high, the differential LVPECL output 1 driver is enabled. When set low, the differential driver is tristated reducing power consumption.This pin is internally pulled up to Vdd.Status H1lockOLock Indicator (LVCMOS). This is the lock indicator pin for the Tx DPLL. This output goes high when the Tx DPLL’s output is frequency and phase locked to the input reference.J1hold OHoldover Indicator (LVCMOS). This pin goes high when the Tx DPLL enters the holdover mode.Pin # Name I/O Type DescriptionZL30131Short Form Data SheetSerial Interface E2sck_sclI/BClock for Serial Interface (LVCMOS). Serial interface clock. When i2c_en = 0,this pin acts as the sck pin for the serial interface. When i2c_en = 1, this pin acts as the scl pin (bidirectional) for the I 2C interface.F1si_sda I/BSerial Interface Input (LVCMOS). Serial interface data pin. When i2c_en = 0,this pin acts as the si pin for the serial interface. When i2c_en = 1, this pin acts as the sda pin (bidirectional) for the I 2C interface.G1so OSerial Interface Output (LVCMOS). Serial interface data output. When i2c_en =0, this pin acts as the so pin for the serial interface. When i2c_en = 1, this pin is unused and should be left unconnected.E3cs_b_asel0I uChip Select for SPI/Address Select 0 for I 2C (LVCMOS). When i2c_en = 0, this pin acts as the chip select pin (active low) for the serial interface. When i2c_en =1, this pin acts as the asel0 pin for the I 2C interface.F3asel1I uAddress Select 1 for I 2C (LVCMOS). When i2c_en = 1, this pin acts as the asel1 pin for the I 2C interface. Internally pulled up to Vdd. Leave open when not in use.F2asel2I uAddress Select 2 for I 2C (LVCMOS). When i2c_en = 1, this pin acts as the asel2 pin for the I 2C interface. Internally pulled up to Vdd. Leave open when not in use.G2int_b OInterrupt Pin (LVCMOS). Indicates a change of device status prompting the processor to read the enabled interrupt service registers (ISR). This pin is an open drain, active low and requires an external pulled-up to Vdd.J2i2c_enI uI 2C Interface Enable (LVCMOS). If set high, the I 2C interface is enabled, if set low, the SPI interface is enabled. Internally pull-up to Vdd.APLL Loop Filter A6apll_filter A External Analog PLL Loop Filter terminal.B6filter_ref0A Analog PLL External Loop Filter Reference.C6filter_ref1AAnalog PLL External Loop Filter Reference.JTAG and Test J4tdoOTest Serial Data Out (Output). JTAG serial data is output on this pin on the falling edge of tck. This pin is held in high impedance state when JTAG scan is not enabled.K2tdiI uTest Serial Data In (Input). JTAG serial test instructions and data are shifted in on this pin. This pin is internally pulled up to Vdd. If this pin is not used then it should be left unconnected.H4trst_bI uTest Reset (LVCMOS). Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low on power-up to ensure that the device is in the normal functional state. This pin is internally pulled up to Vdd. If this pin is not used then it should be connected to GND.K3tck ITest Clock (LVCMOS): Provides the clock to the JTAG test logic. If this pin is not used then it should be pulled down to GND.Pin #NameI/O TypeDescriptionZL30131Short Form Data Sheet J3tms I u Test Mode Select (LVCMOS). JTAG signal that controls the state transitions ofthe TAP controller. This pin is internally pulled up to V DD. If this pin is not usedthen it should be left unconnected.Master ClockK4osci I Oscillator Master Clock Input (LVCMOS). This input accepts a 20MHzreference from a clock oscillator (TCXO, OCXO). The stability and accuracy ofthe clock at this input determines the free-run accuracy and the long termholdover stability of the output clocks.K5osco O Oscillator Master Clock Output (LVCMOS). This pin must be left unconnectedwhen the osci pin is connected to a clock oscillator.MiscellaneousJ6IC Internal Connection. Connect to ground.C5B5K6H10IC Internal Connection. Leave unconnected.H7G3E10F10D1NC No Connection. Leave Unconnected.Power and GroundD9 E4 G8 G9 J8 J9 H6 H8V DD PPPPPPPPPositive Supply Voltage. +3.3V DC nominal.E8 F4V CORE PPPositive Supply Voltage. +1.8V DC nominal.A5 A8 C10AV DD PPPPositive Analog Supply Voltage. +3.3V DC nominal.B7 B8 H2AV CORE PPPPositive Analog Supply Voltage. +1.8V DC nominal.Pin # Name I/OType DescriptionZL30131Short Form Data SheetI - InputI d -Input, Internally pulled down I u -Input, Internally pulled up O -Output A -Analog P -Power G -GroundD4D5D6D7E5E6E7F5F6F7G4G5G6G7E9F8F9H9V SSG G G G G G G G G G G G G G G G G G Ground. 0 Volts.A7C7C8C9D8H3AV SSG G G G G GAnalog Ground. 0 Volts.Pin # Name I/O Type DescriptionZL30131Short Form Data Sheet1.0 Pin DiagramBCDEFGHJK234567891011 - A1 corner is identified with a dot.Async1TOP VIEWsync2ref2ref7AV DDapll_filterAV SSAV DDdiff0_pdiff1_psync0ref1ref4ref5ICfilter_ref0AV COREAV COREdiff1_ndiff0_nref0mode_0ref3ref6ICfilter_ref1AV SSAV SSAV SSAV DDNCmode_1diff1_enV SSV SSV SSV SSAV SSV DDapll_clk0ref_outsck/ cs_b/VDDV SSV SSV SSV COREV SSNCsi/asel2asel1V COREV SSV SSV SSV SSV SSNCsoint_bNCV SSV SSV SSV SSV DDV DDapll_clk1lockAV COREAV SStrst_brst_bV DDNCV DDV SSICholdi2c_entmstdohs_enICp0_fp1V DDV DDp1_clk0diff0_entditckoscioscoICp0_clk1p0_fp0p0_clk0p1_clk11scl sdhasel0ZL30131Short Form Data Sheet 2.0 Functional DescriptionThe ZL30131 OC-192/STM-64 PDH/SONET/SDH/10GbE Network Interface Synchronizer is a highly integrated device that provides timing for both PDH/SONET/SDH and Ethernet network interface cards. A functional block diagram is shown in Figure 1.This device is ideally suited for designs that require both a transmit timing path (backplane to PHY) and a receive timing path (PHY to backplane). Each path is controlled with separate DPLLs (Tx DPLL, Rx DPLL) which are both independently configurable through the serial interface (SPI or I2C). A typical application of the ZL30131 is shown in Figure 2. In this application, the ZL30131 translates the 19.44MHz clock from the telecom rate backplane (system timing bus), translates the frequency to 622.08MHz or 156.25MHz for the PHY Tx clock, and filters the jitter to ensure compliance with the related standards. A programmable synthesizer (P0) provides synchronous PDH clocks with multiples of 8kHz for generating PDH interface clocks. On the receive path, the Rx DPLL and the P1 synthesizer translate the line recovered clock (8kHz or 25MHz) from the PHY to the 19.44MHz telecom backplane (line recovered timing) for the central timing cards. The ZL30131 allows easy integration of Ethernet line rates with today’s telecom backplanes.Figure 2 - Typical Application of the ZL30131Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively “Zarlink”) is believed to be reliable.However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink’s conditions of sale which are available on request.Purchase of Zarlink’s I 2C components conveys a licence under the Philips I 2C Patent rights to use these components in and I 2C System, provided that the system conforms to the I 2C Standard Specification as defined by Philips.Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.Copyright Zarlink Semiconductor Inc. All Rights Reserved.TECHNICAL DOCUMENTATION - NOT FOR RESALEFor more information about all Zarlink productsvisit our Web Site at。

CRIO-4010 单相、三相全参数交流 电量采集模块 用户手册说明书

CRIO-4010单相、三相全参数交流电量采集模块用户手册版本号:Q7-30-02修订日期:2016-11-1国控精仪(北京)科技有限公司2016年版权所有本软件文档及相关套件均属国控精仪(北京)科技有限公司所有,包含专利信息,其知识产权受国家法律保护,除非本公司书面授权许可,其他公司、组织不得非法使用和拷贝。

为提高产品的性能、可靠性,本文档中的信息如有完善或修改,恕不另行通知,客户可从公司网站下载或致电我们通过电子邮件索取,制造商无需作成承诺和承担责任。

客户使用产品和软件文档进行设备调试和生产时,应进行可靠性、功能性等全面测试,方可进行整体设备的运行或交付。

我们提供7*24电话技术支持服务,及时解答客户问题。

如何从国控精仪获得技术服务我们将为客户提供满意全面的技术服务。

请您通过以下信息联系我们。

国控精仪公司信息网址: 英文中文销售服务: **************销售分机:801 电话: 400 9936 400 ************传真: ************地址: 北京市海淀区安宁庄东路18号2号办公楼420-423室请将您下列的信息通过邮件或传真发送给我们1概述...................................................................................................................................... - 1 -1.1产品特性.................................................................................................................. - 1 -1.2产品应用.................................................................................................................. - 1 -1.3产品详细指标.......................................................................................................... - 2 -1.3.1电量参数...................................................................................................... - 2 -1.3.2系统稳定时间.............................................................................................. - 2 -1.3.3物理特征...................................................................................................... - 3 -1.3.4产品功耗(典型值) ..................................................................................... - 3 -1.3.5工作环境...................................................................................................... - 3 -1.3.6存储环境...................................................................................................... - 3 -1.4软件支持.................................................................................................................. - 3 -2设备安装.............................................................................................................................. - 5 -2.1产品开箱.................................................................................................................. - 5 -2.2软件安装.................................................................................................................. - 5 -2.3产品布局图.............................................................................................................. - 6 -3信号连接说明...................................................................................................................... - 7 -3.1连接器管脚分配...................................................................................................... - 7 -3.2电源与通讯连接...................................................................................................... - 8 -3.3信号连接.................................................................................................................. - 9 -4 模拟量输入(AI)模块功能码........................................................................................ - 10 -4.1读保持寄存器........................................................................................................ - 10 -4.2读输入寄存器........................................................................................................ - 11 -4.3设置单个保持寄存器............................................................................................ - 13 -4.4设置多个保持寄存器............................................................................................ - 13 -5产品注意事项、保修、校准............................................................................................ - 15 -图2-1 CRIO4010产品图................................................................................................... - 6 -图3-1 电源与通讯接线图 ................................................................................................ - 8 -图3-2 单相电示意图 ........................................................................................................ - 9 -图3-3 三相电示意图 ........................................................................................................ - 9 -表3-1 16P端子标注 .......................................................................................................... - 8 -1概述CRIO-4010是基于RS485的高性能通信模块。

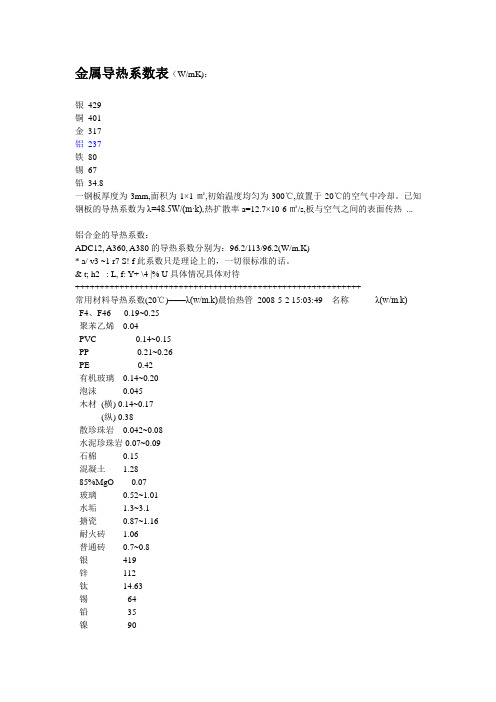

金属导热系数表

金属导热系数表(W/mK):银 429铜 401金 317铝 237铁 80锡 67铅一钢板厚度为3mm,面积为1×1㎡,初始温度均匀为300℃,放置于20℃的空气中冷却。

已知钢板的导热系数为λ=(m·k),热扩散率a=×10-6㎡/s,板与空气之间的表面传热 ...铝合金的导热系数:ADC12, A360, A380的导热系数分别为:113/(W/* a/ v3 ~1 r7 S! f此系数只是理论上的,一切很标准的话。

& t; h2 _: L, f: Y+ \4 |% U具体情况具体对待++++++++++++++++++++++++++++++++++++++++++++++++++++++++++常用材料导热系数(20℃)——λ(w/晨怡热管 2008-5-2 15:03:49 名称λ(w/F4、F46 ~聚苯乙烯PVC ~PP ~ PE有机玻璃~泡沫木材 (横) ~(纵)散珍珠岩~水泥珍珠岩~石棉混凝土85%MgO玻璃~水垢~搪瓷~耐火砖普通砖~银419锌112钛锡 64铅 35镍 90钢36~54铸铁42~90钝铜381黄铜118青铜 71纯铝218+++++++++++++++++++++++++++++++++++++++++++++++++++++++++铸铝138~147不锈钢17空气温度 [10^-2(w/]100K150K200K250K300K350K400K水温度w/0℃10℃20℃30℃40℃50℃60℃70℃80℃水蒸汽硫酸5~25% ~25~50% ~++++++++++++++++++++++++++++++++++++++++++++++++++++++++++导热系数导热系数是指在稳定传热条件下,1m厚的材料,两侧表面的温差为1度(K,°C),在1小时内,通过1平方米面积传递的热量,单位为瓦/米?度(W/m?K,此处的K可用°C代替)。

Z87L00中文资料(zilog)中文数据手册「EasyDatasheet - 矽搜」