【精品】EDA课程设计报告 N沟MOS管工艺模拟与器件模拟(毕业实践)

eda技术实验报告

eda技术实验报告EDA技术实验报告引言EDA(Electronic Design Automation)技术是电子设计自动化的缩写,是现代电子设计中不可或缺的一环。

它通过计算机辅助设计,提高了电路设计的效率和质量。

本文将介绍EDA技术的背景、应用和实验结果。

背景随着电子产品的不断发展,电路设计变得越来越复杂,传统的手工设计已经无法满足需求。

EDA技术的出现填补了这一空白。

它利用计算机的强大计算能力和算法,帮助设计师完成电路设计、仿真、布局和验证等工作。

应用1. 电路设计EDA技术的核心应用是电路设计。

通过EDA工具,设计师可以绘制电路图、选择器件、进行参数设置等。

EDA工具还可以自动进行电路优化,提高电路性能。

2. 仿真验证在电路设计完成后,需要对电路进行仿真验证。

EDA技术可以提供准确的仿真结果,帮助设计师分析电路的性能和稳定性。

仿真验证可以帮助设计师发现潜在的问题,提前解决。

3. 物理布局物理布局是将电路逻辑转化为实际的物理结构。

EDA技术可以自动进行物理布局,优化电路的面积和功耗。

物理布局的好坏直接影响到电路的性能和可靠性。

4. 电路验证在电路设计完成后,需要进行电路验证,确保电路的正确性和可靠性。

EDA技术可以自动进行电路验证,提供准确的验证结果。

电路验证可以帮助设计师发现设计缺陷,提高电路的可靠性。

实验设计在本次实验中,我们选择了一款EDA工具进行实验。

首先,我们设计了一个简单的数字电路,包括与门和或门。

然后,利用EDA工具进行电路仿真和优化。

最后,对电路进行物理布局和验证。

实验结果通过实验,我们得到了以下结果:1. 仿真结果显示,设计的数字电路在不同输入条件下均能正确输出结果,验证了电路的正确性。

2. 通过优化算法,我们成功提高了电路的性能,减少了功耗和面积。

3. 物理布局结果显示,电路的布局紧凑,满足了设计要求。

4. 电路验证结果显示,电路的功能和性能均符合设计要求,验证了电路的可靠性。

MOS放大电路设计仿真与实现实验报告

MOS放大电路设计仿真与实现实验报告实验报告:MOS放大电路设计、仿真与实现一、实验目的本实验的主要目的是通过设计、仿真和实现MOS放大电路来加深对MOSFET的理解,并熟悉模拟电路的设计过程。

二、实验原理MOSFET是一种主要由金属氧化物半导体场效应管构成的电流驱动元件。

与BJT相比,MOSFET具有输入阻抗高、功率损耗小、耐电压高、尺寸小等优点。

在MOS放大电路中,可以采用共源共源极放大电路、共栅共栅极放大电路等不同的电路结构。

三、实验步骤1.根据实验要求选择合适的电路结构,并计算所需材料参数(参考已知电流源和负载阻抗)。

2.选择合适的MOS管,并仿真验证其工作参数。

3.根据仿真结果确定电路的放大倍数、频率响应等。

4.根据电路需求,设计电流源电路和源极/栅极电路。

5.仿真整个电路的性能,并调整参数以优化电路性能。

6.根据仿真结果确定电路的工作参数,并进行电路的实现。

7.通过实验测量电路性能,验证仿真结果的正确性。

8.对实验结果进行分析,总结实验的过程和经验。

四、实验设备和材料1.计算机及电子仿真软件。

2.实验电路板。

3.集成电路元器件(MOSFET、电阻等)。

4.信号发生器。

5.示波器。

6.万用表等实验设备。

五、实验结果与分析通过仿真和实验,可以得到MOS放大电路的电压增益、输入输出阻抗、频率响应等参数。

根据实验结果,可以验证设计的合理性,并进行参数调整优化。

在实际应用中,MOS放大电路被广泛应用于音频放大器、功率放大器、运算放大器等场合。

因为MOSFET具有较大输入阻抗,所以MOS放大电路可以在输入端直接连接信号源,而不需要额外的输入电阻。

此外,MOS放大电路的功率损耗较小,适用于各种功率要求不同的应用场合。

六、实验心得通过设计、仿真和实现MOS放大电路的实验,我更加深入地理解了MOSFET的原理和应用。

在实验过程中,我通过不断调整电路参数和元器件选择,逐步提高了电路的性能。

通过与实验结果的对比,我发现仿真和实验结果基本吻合,验证了仿真的准确性。

mos工艺流程实验报告

mos工艺流程实验报告下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!一、实验目的本次实验的目的是了解金属-氧化物-半导体(MOS)工艺流程,并通过实验操作掌握其关键步骤。

EDA课程设计报告概论

天津工业大学毕业实践实习报告N沟道MOS管工艺模拟与器件模拟班级:电科1103学号:1110940316姓名:汪兆明成绩:2015年4月1日一、实践目的熟练氧化、离子注入与扩散工艺,使用Silvaco软件进行模拟,掌握CMOS 工艺流程。

学会用Silvaco软件提取MOS晶体管的各种参数,掌握用SILVACO 工具对MOS晶体管进行器件模拟二、实践要求1、用Anthena构建一个NMOS管,要求沟道长度不小于0.8微米,阈值电压在-0.5v 至 1V之间。

2、工艺模拟过程要求提取S/D结结深、阈值电压、沟道表面掺杂浓度、S/D区薄层电阻等参数。

3、进行器件模拟,要求得到NMOS输出特性曲线族以及特定漏极电压下的转移特性曲线,并从中提取MOS管的阈值电压和β值。

4、分析各关键工艺步骤对器件性能的影响。

三、操作步骤1、启动silvaco软件。

2、创建一个网格并定义衬底的参数。

3、由于本实验运用了cmos工艺,所以先在衬底上做一个p阱,严格定义p阱的浓度,注入能量,以及阱区的推进。

4、生长栅氧化层,严格控制各参数。

diffus time=10 temp=950 dryo2 press=1.00 hcl.pc=35、淀积多晶硅,其厚度为0.2um。

6、刻蚀掉x=0.35左面的多晶硅,然后低剂量注入磷离子,形成轻掺杂层,剂量为3e13,能量为20kev。

7、淀积氧化层,然后再进行刻蚀,以进行下一步的源漏区注入。

8、进行源漏砷离子的注入,剂量为4e15,能量为40kev。

9、淀积铝,形成S/D金属接触。

10、进行向右镜像操作,形成完整的nmos结构并定义电极。

11、抽取源漏结深,阈值电压,n+区薄层电阻,沟道表面掺杂浓度,轻掺杂源漏区的薄层电阻等参数。

12、描述输出特性曲线并绘出。

13、描述转移特性曲线并绘出,同时从中提取MOS管的阈值电压和β值。

四.测试结果4.1 测试结果分析4.1.1.工艺图4.1.2.获取器件参数在这一部分,我们将提取这半个NMOS结构的一些器件参数,这些参数包括:a.结深b.N++源漏方块电阻c.边墙下LDD区的方块电阻d.长沟阈值电压计算结深计算结深的语句如下:extract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1获取N++源/漏极薄层电阻extract name="n++ sheet rho" sheet.res material="Silicon"mat.occno=1 x.val=0.05 region.occno=1测量沟道阈值电压extract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49在这条extract语句中,1dvt指测量一维阈值电压;ntype指器件类型;x.val=0.49为器件沟道内一点;qss=1e10指浓度为1e10cm-3的表面态电荷;vb=0.0栅极偏置0V。

MOS管相关仿真实验报告

MOS管相关仿真实验报告

一.MOS管共源放大电路仿真(基本要求)

电路如右图所示,

注意:1)设置静态工作点时,调整电位器Rp,使Vd为5~6V.

2)仿真时输出端必须接负载,否则会报错(可以将阻值设为很大的值来仿真开路情况)

放大电路仿真验证设计与仿真要求

(1)电路图

(2)静态工作点:ID、VGs、Vs

得ID=1.34862mA,VGs=2.16362V,Vs=1.41740V

(3)输入、输出电压波形,并计算电压增益A

即得电压增益为Av=45.4773

(4)幅频响应曲线:db((vo)(vs:+),测中频增益、上限频率fH和下限频率fL

如图,由图可知,测得中频增益为45.5854,上限频率fH=797.844kHz,下限频率fL=33.4688Hz (5)相频响应曲线:Vp(Vo)-p(vs:+)或p(V(vo)/Vvs:+))

(6)输入电阻的频率响应:Ri—V(v(i))/I(Vs)

(7)输出电阻的频率响应:Ro—V(V(o))/I(Vs)

(8)非线性失真现象

1)将Rp调整为最大值,做静态分析和瞬态分析,记录静态工作点和波形。

静态分析如下

瞬态分析如下

2)将Rp调整为最小值(不能为0,0是非法值),再做静态分析和瞬态分析,记录静态工作点和波形。

(如果发现没有失真,可以增大输入信号幅值。

)

静态分析如下

瞬态分析如下

由于此时失真不明显,故将输入振幅调至9V得到波形如下

得到明显失真图像。

选做部分

二.MOS管特性曲线仿真任务一:MOSFET输出特性曲线仿真

任务二:MOSFET转移特性曲线仿真。

eda实验报告完整版

EDA实验报告焦中毅201300121069实验1 4选1数据选择器的设计一、实验目的1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台三、实验说明本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。

例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。

学会管脚锁定以及编程下载的方法等。

四、实验要求1.完成4选1数据选择器的原理图输入并进行编译;2.对设计的电路进行仿真验证;3.编程下载并在实验开发系统上验证设计结果。

五、实验结果4选1数据选择器的原理图:仿真波形图:管脚分配:实验2 四位比较器一、实验目的1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和0123B B B B ,输出为M (A=B ),G (A>B )和L (A<B )(如图所示)。

用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

四、实验要求1.用硬件描述语言编写四位二进制码 比较器的源文件; 2.对设计进行仿真验证; 3.编程下载并在实验开发系统上进行 硬件验证。

实验报告4(MOSFET工艺器件仿真)

学生实验报告院别课程名称器件仿真与工艺综合设计实验班级实验三MOSFET工艺器件仿真姓名实验时间学号指导教师成绩批改时间报告内容一、实验目的和任务1.理解半导体器件仿真的原理,掌握Silvaco TCAD 工具器件结构描述流程及特性仿真流程;2.理解器件结构参数和工艺参数变化对主要电学特性的影响。

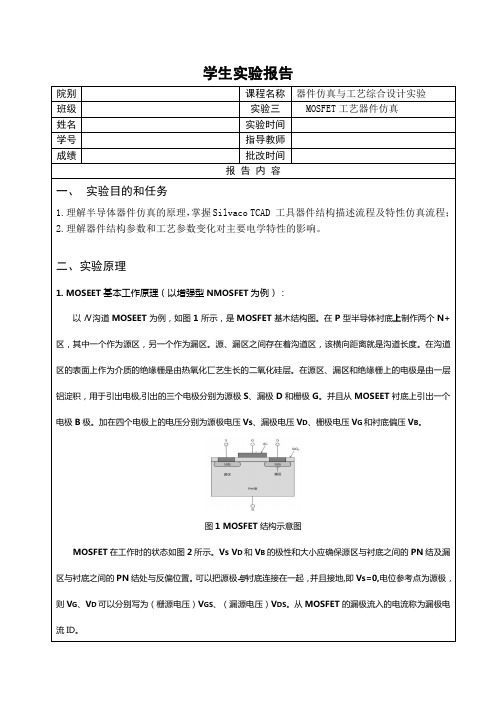

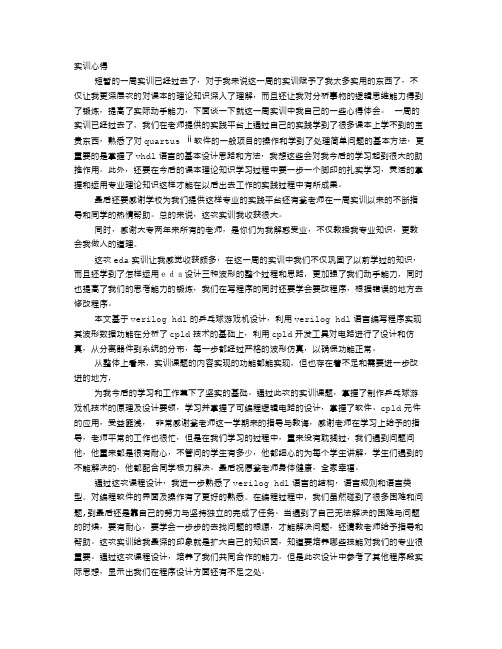

二、实验原理1. MOSEET基本工作原理(以增强型NMOSFET为例):以N沟道MOSEET为例,如图1所示,是MOSFET基木结构图。

在P型半导体衬底上制作两个N+区,其中一个作为源区,另一个作为漏区。

源、漏区之间存在着沟道区,该横向距离就是沟道长度。

在沟道区的表面上作为介质的绝缘栅是由热氧化匸艺生长的二氧化硅层。

在源区、漏区和绝缘栅上的电极是由一层铝淀积,用于引出电极,引出的三个电极分别为源极S、漏极D和栅极G。

并且从MOSEET衬底上引出一个电极B极。

加在四个电极上的电压分别为源极电压Vs、漏极电压V D、栅极电压V G和衬底偏压V B。

图1 MOSFET结构示意图MOSFET在工作时的状态如图2所示。

Vs V D和V B的极性和大小应确保源区与衬底之间的PN结及漏区与衬底之间的PN结处与反偏位置。

可以把源极与衬底连接在一起,并且接地,即Vs=0,电位参考点为源极,则V G、V D可以分别写为(栅源电压)V GS、(漏源电压)V DS。

从MOSFET的漏极流入的电流称为漏极电流ID。

(1)在N沟道MOSFET中,当栅极电压为零时,N+源区和N+漏区被两个背靠背的二极管所隔离。

这时如果在漏极与源极之间加上电压V DS,只会产生PN 结反向电流且电流极其微弱,其余电流均为零。

(2)当栅极电压V GS不为零时,栅极下面会产生一个指向半导体体内的电场。

(3)当V GS增大到等于阈值电压V T的值时,在半导体内的电场作用下,栅极下的P型半导体表面开始发生强反型,因此形成连通N+源区和N+漏区的N型沟道,如图2所示。

实验报告4(MOSFET工艺器件仿真)

学生实验报告报告内容实验目的和任务1.理解半导体器件仿真的原理,掌握Silvaco TCAD 工具器件结构描述流程及特性仿真流程;2.理解器件结构参数和工艺参数变化对主要电学特性的影响。

二、实验原理1. MOSEET 基本工作原理(以增强型NMOSFET 为例):以N 沟道MOSEET 为例,如图1所示,是MOSFET 基木结构图。

在P 型半导体衬底上制作两个N+区,其中一个作为源区,另一个作为漏区。

源、漏区之间存在着沟道区,该横向距离就是沟道长度。

在沟道区的表面上作为介质的绝缘栅是由热氧化匸艺生长的二氧化硅层。

在源区、漏区和绝缘栅上的电极是由一层铝淀积,用于引出电极,引出的三个电极分别为源极S、漏极 D 和栅极G。

并且从MOSEET 衬底上引出一个电极B 极。

加在四个电极上的电压分别为源极电压Vs 、漏极电压V D 、栅极电压V G 和衬底偏压V B图 1 MOSFET 结构示意图MOSFET 在工作时的状态如图 2 所示。

Vs V D 和V B的极性和大小应确保源区与衬底之间的PN 结及漏区与衬底之间的PN 结处与反偏位置。

可以把源极与衬底连接在一起,并且接地,即Vs=0, 电位参考点为源极,则V G、V D 可以分别写为(栅源电压)V GS、(漏源电压)V DS。

从MOSFET 的漏极流入的电流称为漏极电流ID (1 )在N 沟道MOSFET 中,当栅极电压为零时,N+ 源区和N+ 漏区被两个背靠背的二极管所隔离。

这时如果在漏极与源极之间加上电压V DS,只会产生PN 结反向电流且电流极其微弱,其余电流均为零。

(2)当栅极电压V GS 不为零时,栅极下面会产生一个指向半导体体内的电场。

(3)当V GS增大到等于阈值电压V T的值时,在半导体内的电场作用下,栅极下的P 型半导体表面开始发生强反型,因此形成连通N+ 源区和N+ 漏区的N 型沟道,如图 2 所示。

(4)由于大量的可动电子存在于沟道内,当在漏、源极之间加上漏源电压V GS 后,会产牛漏极电流I D。

EDA课设报告

1.1试用频率分别为f1= 200 Hz、f2= 2000 Hz的两个正弦信号源,合成一调制信号y(t)=5sin(2πf1t)*cos(2πf2t),观察其频谱与输出信号波形。

注意根据信号的频率选择适当的系统采样速率。

仿真电路图结果分析:(上图为时域图,下图为频谱图)。

可以在频谱图上很容易就看出此电路的电路图经由乘法器变换后出现了两个频率,经过计算可以肯定是f0与f1的和频与差频分别为2200HZ与1800HZ。

1.2将一正弦信号与高斯噪声相加后观察输出波形及其频谱。

从小到大改变高斯噪声的功率,重新观察输出波形及其频谱。

仿真电路图0:振幅1V ,频率10Hz ,相位为0°的正弦波 1:高斯噪声,标准方差设为0.1,均值为02:加法器,将图符0和图符1的信号进行相加得到所要的调制信号,加法器相当于传输信道,信号在信道中传输,加入的高斯噪声相当于噪声源采样频率为50000HZ 高斯方差0.1高斯方差1第一张图是输出信号的波形,可看出输出信号是周期为0.1s,振幅为1V的正弦波,但由于加入了噪声源,所以输出的信号不再平滑,出现了波折,并随着高斯噪声功率的增加输出信号曲线出现的波折越大,如第三张图中信号已经很难分辨。

1.3已知DTMF双音频编码器的低组频率为697 Hz,,770 Hz,852 Hz,941Hz,高组频率为1209 Hz,1336 Hz,1477 Hz,1633 Hz,试合成0~9、*、#的双音频,并使用接收器图符中的单声道音频文件(8bit wav)输出,通过计算机的声卡输出声音,与实际电话输出的声音比较。

注意,在输出端应加入一定的增益来放大波形。

仿真电路图1~7全部都是题目中出现的高低频率的组合,每两个为一组通过加法器连接,而后早通过增益将这些加和平率放大,然后通过单声道的输出,为了方便的观察每组的频谱变化故在每个音频输出的后面加上了波形输出,其时域和频域图谱如图所示,虽然选择了其中的一组但还是可以反映出其他组的情况,从频谱上虽然有很多频率分量但还是可以清楚的看出有几个主要的频率,他们就是这段音频的主要组成部分。

EDA课程设计实验报告

《EDA课程设计》报告学号:姓名:班级:指导教师:2013年6 月24日- 2013年7 月5日目录1.引言 ............................................................................................................... 错误!未定义书签。

2.原理图的设计................................................................................................ 错误!未定义书签。

文件的新建............................................................................................... 错误!未定义书签。

原理图文件XX .Sch的建立 ..................................................................... 错误!未定义书签。

元件库的导入........................................................................................... 错误!未定义书签。

原理图中各元件的布局和连线 (3)3.原理图新元件的设计 (4)元件库XX .Lib文件的建立 (4)原理图元件的画法................................................................................... 错误!未定义书签。

注意事项................................................................................................... 错误!未定义书签。

EDA技术及应用实验报告

EDA技术及应用实验报告摘要:EDA(Electronic Design Automation),即电子设计自动化,是一种用于半导体芯片设计的计算机辅助设计工具。

本实验通过对EDA技术的学习和应用,了解了EDA在电路设计中的重要性和实际应用。

1.引言电子设计自动化(EDA)是为了提高电子电路设计的效率和质量而发展的一种计算机辅助设计工具。

本实验通过学习EDA技术的相关知识和应用实例,深入了解EDA在电路设计中的应用及其优势。

2.EDA技术的基本原理EDA技术是通过计算机辅助分析、合成和验证电路的工具。

它包括电路仿真、布局布线、逻辑综合等多个方面。

其中,电路仿真是通过计算机模拟电路的工作原理和特性;布局布线是将电路逻辑设计映射为实际的物理设计;逻辑综合是将逻辑电路转换为门级或者布尔级电路。

3.EDA技术在电路设计中的应用3.1电路仿真电路仿真是一个重要的EDA技术应用,通过仿真可以验证电路的运行情况,提前发现并解决潜在的问题,从而降低设计风险和成本。

3.2布局布线布局布线是指将逻辑电路映射为物理电路的过程。

通过EDA工具的自动布局布线功能,可以将逻辑电路转换为最优的电路布线,减少电路面积和功耗,并提高电路的稳定性和性能。

3.3逻辑综合逻辑综合是将高级语言描述的逻辑电路转换为可实现的门级或布尔级电路。

通过EDA工具的逻辑综合功能,可以快速生成电路的逻辑结构,避免手工设计过程中的错误和繁琐性。

4.实验设计及结果本实验选取了一款集成电路芯片设计作为实验对象,使用EDA工具进行电路仿真、布局布线和逻辑综合三个方面的实验。

4.1电路仿真实验在电路仿真实验中,我们首先通过EDA工具搭建了待仿真的电路原理图,然后设置仿真条件和参数,运行仿真,并得到了仿真结果。

仿真结果显示,电路工作正常,符合预期。

4.2布局布线实验在布局布线实验中,我们将电路的逻辑设计转换为物理设计,通过EDA工具的自动布局布线功能进行布局布线。

EDA实训报告总结

实训心得短暂的一周实训已经过去了,对于我来说这一周的实训赋予了我太多实用的东西了,不仅让我更深层次的对课本的理论知识深入了理解,而且还让我对分析事物的逻辑思维能力得到了锻炼,提高了实际动手能力,下面谈一下就这一周实训中我自己的一些心得体会。

一周的实训已经过去了,我们在老师提供的实践平台上通过自己的实践学到了很多课本上学不到的宝贵东西,熟悉了对quartusⅱ软件的一般项目的操作和学到了处理简单问题的基本方法,更重要的是掌握了vhdl语言的基本设计思路和方法,我想这些会对我今后的学习起到很大的助推作用。

此外,还要在今后的课本理论知识学习过程中要一步一个脚印的扎实学习,灵活的掌握和运用专业理论知识这样才能在以后出去工作的实践过程中有所成果。

最后还要感谢学校为我们提供这样专业的实践平台还有瓮老师在一周实训以来的不断指导和同学的热情帮助。

总的来说,这次实训我收获很大。

同时,感谢大专两年来所有的老师,是你们为我解惑受业,不仅教授我专业知识,更教会我做人的道理。

这次eda实训让我感觉收获颇多,在这一周的实训中我们不仅巩固了以前学过的知识,而且还学到了怎样运用eda设计三种波形的整个过程和思路,更加强了我们动手能力,同时也提高了我们的思考能力的锻炼,我们在写程序的同时还要学会要改程序,根据错误的地方去修改程序。

本文基于verilog hdl的乒乓球游戏机设计,利用verilog hdl语言编写程序实现其波形数据功能在分析了cpld技术的基础上,利用cpld开发工具对电路进行了设计和仿真,从分离器件到系统的分布,每一步都经过严格的波形仿真,以确保功能正常。

从整体上看来,实训课题的内容实现的功能都能实现,但也存在着不足和需要进一步改进的地方,为我今后的学习和工作奠下了坚实的基础。

通过此次的实训课题,掌握了制作乒乓球游戏机技术的原理及设计要领,学习并掌握了可编程逻辑电路的设计,掌握了软件、cpld元件的应用,受益匪浅,非常感谢瓮老师这一学期来的指导与教诲,感谢老师在学习上给予的指导,老师平常的工作也很忙,但是在我们学习的过程中,重来没有耽搁过,我们遇到问题问他,他重来都是很有耐心,不管问的学生有多少,他都细心的为每个学生讲解,学生们遇到的不能解决的,他都配合同学极力解决。

EDA仿真实验报告

EDA仿真实验报告本次实验主要是基于EDA工具完成的仿真实验,主要是通过Multisim 14.0这一EDA 工具,设计和仿真了基于电容的RC低通滤波器电路。

下面就本次实验的过程和结果进行具体的介绍。

1. 实验目的本次实验的主要目的如下:1. 理解RC低通滤波器的基本原理;2. 通过Multisim 14.0这一EDA工具,完成RC低通滤波器电路的设计和仿真;3. 分析RC低通滤波器对信号的频率响应特性和滤波效果。

2. 实验原理RC低通滤波器是一种常用的模拟滤波器,它的基本原理是利用电容和电阻构成电路来对输入信号进行滤波。

在RC电路中,当输入信号频率较低时,电容器的充放电过程比较缓慢,电容器上的电压基本上可以维持在稳定状态;但当输入信号频率较高时,电容器的充放电过程加速,电容器上的电压就不能完全跟随输入信号的变化,从而实现对高频信号的滤波。

3. 装置和实验步骤1. 1个7400、1个7412、1个74138、1个74139、1个LED;2. 3个220欧姆电阻、2个1K欧姆电阻、1个10K欧姆电阻、2个10UF电容、1个2N2222晶体管。

1. 打开Multisim 14.0软件并创建新的电路文件;2. 将一个电压源V2接到输入端口,并将其电压设置为5V;3. 通过工具栏上的元件库中的电阻和电容元件,构建一个RC低通滤波器电路,其中电阻的值为1K欧姆,电容的值为10UF;4. 在输出端口添加一个示波器元件并将其连接到电路的输出端口;5. 单击“仿真”按钮,然后选择“时间域示波器”以查看电路的时间响应;6. 将示波器元件上的“点选”功能切换到“频域响应”,然后单击“仿真”按钮以观察电路的频率响应。

4. 结果分析通过以上实验步骤,我们完成了一个简单的RC低通滤波器电路的设计和仿真,下面来分析一下实验结果。

4.1 时间响应我们可以看到,在电路输入端口输入一个简单脉冲信号后,电路的输出会逐渐达到稳定值。

EDA、Multisim仿真、模拟电路报告

EDA技术及其应用实训报告1、实训目的1.1实训目的(1)掌握EDA技术及开放流程。

(2)掌握Multisim的使用方法和仿真操作。

(3)能够用Multisim软件进行搭建电路原理图,并对电路进行仿真。

(4)熟练运用Multisim软件并掌握其界面模块的功能。

(5)理解并掌握EDA技术在电路以及模电、数字电路设计中的应用。

1.2 实训要求(1)利用Multisim仿真L、C串联谐振电路,并用波特图仪测定频率特性。

(2)利用Multisim仿真三相三线制Y形非对称电路,并按要求分析。

(3)利用Multisim仿真模拟电路,并按要求进行分析。

(4)利用Multisim仿真数字电路,并按要求进行分析。

2、实验内容2.1 模拟电路部分要求:单管共射极分压式放大电路1、分析静态工作点(直流分析)2、电压放大倍数、输入电阻、输出电阻(交流分析)解:①电路截图如下:② 电路示波器及电压表显示(截图)如下:由上图波形数据可知:实测数据7.76-438.4573.340-=≈UA③ 原电路直流通路如下:测量值如下:B U=C I=CE U④ 理论值计算◆ 静态工作点的分析Vk k kU R R R U CC b b b B 73.212511515212≈+=+=mA R U U I I e BE B E C 135.11000246.073.2=⨯-=-=≈()()VR R I U R I R I U U e C C CC e E C C CC CE 94.321.5135.112=+⨯-=+-=--=◆ 三极管的输入电阻1208.882uAm 073.1==≈A I I BQ CQ β()Ω=⨯+=++≈K I r r EQ bb be 071.3135.126121300261'β◆ 该放大电路的各项交流参数分别为Ω=≈Ω==Ω===⨯-=-=K R r K R R r r R R R r R A C O b b be i L C L be L u 1.538.2////k 2//87-071.3212021''β⑤ 经第三、第四步骤的比较,测量值与理论计算值存在一定的误差,差异范围很小,说明理论与实测相对来说是符合一致的。

EDA期末报告-s

electrode name=source x=0.1 electrode name=drain x=1.9

electrode name=substrate backside 2.17 保存 ATHENA 结构文件 完成设计之后对结构进行保存。

(二)NMOS 的器件仿真 2.18 NMOS 管的输出特性曲线族 输出特性曲线如图 15 所示:

18

四、各关键步骤对器件性能的影响

4.1 氧化工艺的影响 栅氧化层厚度会影响阈值电压的值。改变氧化工艺进行的条件,如采用 1.2Pa,950 度, 3%HCL, 11 分钟, 在其他条件不变的情况下, 通过仿真可以得到阈值电压为: 0.897216. 而够到表面掺杂浓度,S/D 区薄层电阻变化不大。 不同的掺杂浓度对氧化速率也有影响。 图 24 表示硼离子掺杂浓度为 4e15 时得到氧 化层的厚度,与本次仿真得到的结果明显发生变化。 4.2 离子注入工艺的影响 阈值电压调整是利用离子注入,与注入离子的浓度有关系。改变硼的掺杂浓度可以 调整阈值电压,例如当掺杂浓度变为 3×1011cm-3 时,仿真得到的阈值电压仿真结果为 -0.269139 V。 4.3 外延工艺的影响 外延得到的多晶硅的厚度和栅氧化层的厚度共同影响阈值电压及其他参数。 本次仿 真中外延的多晶硅的厚度为 0.25um。如果将其变为 0.3um,其他条件不变,可得到阈 值电压为 0.895723V。对其他参数影响不大。 4.4 源漏注入及退火工艺的影响 源漏注入浓度及退火时间等对器件性能有重要的影响。主要影响结深,薄层电阻, 阈值电压,表面够到浓度等。 由仿真结果可以看到,随着源极/漏极注入浓度增加,结深有明显的提高,Idmax、 阈值电压无明显变化; 当注入浓度从 5e12cm-2 增加到 5e15cm-2 时长沟阈值电压、沟道 表面浓度无明显变化,n++区方块电阻、Idd 区方块电阻减小,当浓度由 5e15cm-2 增加 到 5e17cm-2 时,n++区方块电阻、Idd 区方块电阻明显下降,沟道表面浓度、长沟阈值 电压基本无变化。

MOS晶体管器件与工艺模拟

MOS晶体管器件与工艺模拟一.实验目的1.熟练氧化、离子注入与扩散工艺,使用Silvaco软件进行模拟2.掌握CMOS工艺流程。

3.学会用Silvaco软件提取MOS晶体管的各种参数4.掌握MOS晶体管器件模拟二.实验要求1.用Anthena构建一个NMOS管,要求沟道长度不小于0.8微米,阈值电压在-0.5v 至1V之间。

2.工艺模拟过程要求提取S/D结结深、阈值电压、沟道表面掺杂浓度、S/D区薄层电阻等参数。

进行器件模拟,要求得到NMOS输出特性曲线族以及特定漏极电压下的转移特性曲线,并从中提取MOS管的阈值电压和 值。

3.分析各关键工艺步骤对器件性能的影响。

三.试验程序go athena#line x loc=0.0 spac=0.1line x loc=0.2 spac=0.006line x loc=0.4 spac=0.006line x loc=0.8 spac=0.01#line y loc=0.0 spac=0.002line y loc=0.2 spac=0.005line y loc=0.5 spac=0.05line y loc=0.8 spac=0.15#init orientation=100 c.phos=1e14 space.mul=2#pwell formation including masking off of the nwell#diffus time=30 temp=1000 dryo2 press=1.00 hcl=3#etch oxide thick=0.02##P-well Implant#implant boron dose=8e12 energy=100 pears#diffus temp=950 time=100 weto2 hcl=3##N-well implant not shown -## welldrive starts herediffus time=50 temp=1000 t.rate=4.000 dryo2 press=0.10 hcl=3 #diffus time=220 temp=1200 nitro press=1#diffus time=90 temp=1200 t.rate=-4.444 nitro press=1#etch oxide all##sacrificial "cleaning" oxidediffus time=20 temp=1000 dryo2 press=1 hcl=3#etch oxide all##gate oxide grown here:-diffus time=11 temp=925 dryo2 press=1.00 hcl=3## Extract a design parameterextract name="gateox" thickness oxide mat.occno=1 x.val=0.05 ##vt adjust implantimplant boron dose=9.5e11 energy=10 pearson#depo poly thick=0.2 divi=10##from now on the situation is 2-Detch poly left p1.x=0.35#method fermi compressdiffuse time=3 temp=900 weto2 press=1.0#implant phosphor dose=3.0e13 energy=20 pearson#depo oxide thick=0.120 divisions=8#etch oxide dry thick=0.120#implant arsenic dose=5.0e15 energy=50 pearson#method fermi compressdiffuse time=1 temp=900 nitro press=1.0## pattern s/d contact metaletch oxide left p1.x=0.2deposit alumin thick=0.03 divi=2etch alumin right p1.x=0.18# Extract design parameters# extract final S/D Xjextract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1# extract the N++ regions sheet resistanceextract name="n++ sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.05 region.occno=1# extract the sheet rho under the spacer, of the LDD regionextract name="ldd sheet rho" sheet.res material="Silicon" \ mat.occno=1 x.val=0.3 region.occno=1# extract the surface conc under the channel.extract name="chan surf conc" surf.conc impurity="Net Doping" \ material="Silicon" mat.occno=1 x.val=0.45# extract a curve of conductance versus bias.extract start material="Polysilicon" mat.occno=1 \bias=0.0 bias.step=0.2 bias.stop=2 x.val=0.45extract done name="sheet cond v bias" \curve(bias,1dn.conduct material="Silicon" mat.occno=1 region.occno=1)\outfile="extract.dat"# extract the long chan Vtextract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49structure mirror rightelectrode name=gate x=0.8 y=0.1electrode name=source x=0.1electrode name=drain x=1.6electrode name=substrate backsidestructure outfile=mos1ex01_0.str# plot the structuretonyplot mos1ex01_0.str############# Vt Test : Returns Vt, Beta and Theta ################ go atlas# set material modelsmodels cvt srh printcontact name=gate n.polyinterface qf=3e10method gummel newtonsolve init# Bias the drainsolve vdrain=0.1# Ramp the gatelog outf=mos1ex01_1.log mastersolve vgate=0 vstep=0.25 vfinal=3.0 name=gatesave outf=mos1ex01_1.str# plot resultstonyplot mos1ex01_1.log# extract device parametersextractname="nvt"(xintercept(maxslope(curve(abs(v."gate"),abs(i."drain ")))) \- abs(ave(v."drain"))/2.0)extractname="nbeta"slope(maxslope(curve(abs(v."gate"),abs(i."drain")))) \* (1.0/abs(ave(v."drain")))go atlas# define the Gate workfunctioncontact name=gate n.poly# Define the Gate Qssinterface qf=3e10# Use the cvt mobility model for MOSmodels cvt srh print numcarr=2# set gate biases with Vds=0.0solve initsolve vgate=3 outf=solve_tmp1solve vgate=4 outf=solve_tmp2solve vgate=5 outf=solve_tmp3#load in temporary files and ramp Vdsload infile=solve_tmp1log outf=mos1ex01_2.logsolve name=drain vdrain=0 vfinal=3.3 vstep=0.3load infile=solve_tmp2log outf=mos1ex01_3.logsolve name=drain vdrain=0 vfinal=3.3 vstep=0.3load infile=solve_tmp3log outf=mos1ex01_4.logsolve name=drain vdrain=0 vfinal=3.3 vstep=0.3# plot resultstonyplot -overlay -st mos1ex01_2.log mos1ex01_3.log mos1ex01_4.log quit四.实验结果=0.00015369v阈值电压:vt=0.52419vS/D结结深:nxj=0.175357 um沟道表面掺杂浓度:chan surf conc=3.9595e+016 cm3 S/D区薄层电阻:ldd sheet rho=2146.56 ohm/square NMOS输出特性曲线族漏极电压下的转移特性曲线。

MOS管仿真报告

STARTING SAVING DATA AFTER:0

得如上结果,可得V2=VA=7.72V

V1=VB=4.28V

ID=0.4A

上表为IRFPG42的转移特性曲线,

仿真时采用DC SWEEP

主变量PIRMARY SWEEP为V1(VGS)

STRAT:0V

END:10V

INCREMENT:0.1V

副变量PIRMARY SWEEP为V2(VDS)

采样点:5V,6V,7V

第八题,按1-5画安置元器件,仿真时进行TIME DOMAIN扫描

仿真时采用DC SWEEP

主变量PIRMARY SWEEP为V2(VDS)

STRAT:0V

END:500V

INCREMENT:0.1V

副变量SECONDRAY SWEEP为V1(VGS)

STRAT:0V

END:10V

INCREMENT:1V

这张表为VGS=5V时的传输特性曲线,从表中ቤተ መጻሕፍቲ ባይዱ以看出当VGS=5V, VDS=20V时,Id=2.1A

mos管仿真报告第七题上图为irfpg42的输出特性曲线绘图放置两个直流电压源v1v2其中v1极电压vgsv2为漏极电压vds仿真时采用dcsweep主变量pirmarysweep为v2vdsstrat

MOS管仿真报告

第七题,上图为IRFPG42的输出特性曲线,绘图放置两个直流电压源V1,V2,其中V1为栅极电压VGS,V2为漏极电压VDS