出租车计价器 课程设计报告

出租车计价器专业课程设计报告(含代码)

摘要随着社会的发展,出租车是人们生活中非常方便且较普遍的交通工具,出租车计价器的使用日益完善,现在我们引用单片机技术,使用编码和解码信息传递这种方式来完成计价器计数脉冲的形成;单片机可以很精确地检测到传感器信号。

用较少的硬件和适当的软件相互配合可以很容易的实现设计要求,且灵活性强,可以通过软件编程来完成更多的附加功能,本课程设计采用89C51的定时器T0产生的时钟,通过HD8255键盘显示电路用来显示行驶路程和价格及对计价的控制等从而实现了一个小型计价器系统。

关键字:计价器、单片机、89C51、HD8255目录一、设计要求 (1)1.1、基本要求: (3)1.2、要求分析: (3)二、系统组成及工作原理 (3)2.1系统的硬件构成及功能 (3)2.2 AT89S51单片机及其引脚说明 (4)2.3 AT24C01存储单元 (5)2.4系统工作原理 (5)三、方案设计对比 (6)3.1方案一: (6)3.2方案二: (6)3.3方案选择 (7)四、软件设计 (7)4.1系统主程序分析 (7)4.2计算程序 (8)4.3中途等待中断程序 (8)五、实验调试分析与结果 (9)5.1 实验调试 (9)5.2实验结果 (9)六、结论 (10)参考文献 (11)附录一: (12)一、设计要求1.1、基本要求:里程显示为:***.**公里;能预置起步价及单价:如起步3公里6.00元;1.60/公里;1.2、要求分析:1)起步价:乘客上车,显示起步价(6元),行车距离在3公里以内。

2)里程计价:(计价单位为元,并进行四舍五入)a.行车里程 < 3公里时,计价为6元;b.3公里≤行车里程时,计价为:6元+(里程-3)*1.6元/公里二、系统组成及工作原理2.1系统的硬件构成及功能本次设计主要有四个部分模块电组成,脉冲源产生脉冲提供给单片机,用来计算行驶路程,变换电路用来对产生的脉冲进行整形放大,单片机电路则控制整个系统的运行,8255键盘显示电路用来显示行驶路程和价格及对计价的控制。

课程设计出租车计费器

推南呼紐厚院电子技术课程设计报告题 目:基于Multisum 的出租车计价器课程设计级:3班指导教师:聂文艳机械与电气工程学院制2015年3月学生姓名: 学生学号: 李少华1314050317 13级年 级:业: 电气工程及其自动化目录设计任务 .......................1.1 设计目的和意义 . ......................1.1.1 目的 ................... 1.1.2 意义 ................... 1.2 初始参数和要求 . ......................1.2.1 74LS160 计数器的简介 1.2.2 1.2.3 1.2.4 1.2.5 系统设计 2.1 2.274LS85 比较器的简介 74LS283 加法器的简介 初始要求 . ..........................所用软件工具 . .............. 2.3 系统工作原理 . .......................................... 器件选择 ...............................2.2.1 74LS160 计数器的功能 ............. 2.2.2 74LS283 加法器组成预置数计数器2.2.3 74LS85 比较器的组成和内部结构 2.2.4 设计所需的器件归纳 . ................................. 电路设计 . ................................................2.3.1 2.3.2 2.3.3 2.3.4 路程的计数及显示 .....路程与预设值的比较 . 加法器的预置 . ............... 电路整体的整合 . .........电路仿真测试 ............................2.4.1 路程计数及显示 . ...............................2.4.2 系统整体电路运行及车费的显示 .2.4.3 仿真结论 . .........................................总结 ........................................ 3.1 结论 . ......................................................3.2 优点与不足 . .............................................. 3.3 心得与体会 ..............................参考文献 ...................................2.4 333 4 4 4 4 4 4 4556 6789 9 9 10 10 11 11 11 12 12131313 13 14基于Multisum 的出租车计价器课程设计学生:李少华指导教师:聂文艳机械与电气工程学院:电气工程及其自动化设计任务1.1 设计目的和意义1.1.1 目的1. 能构实现计程功能2. 实现计费功能,计费标准为:按行驶里程收费,起步费为6.0 元,并在车行3 公里后再按2.0 元/公里,最高计费为99.9 元,车停止不计费,能将车费显示出来。

EDA课程设计报告--出租车计价器

EDA课程设计报告--出租车计价器课程设计课程设计名称:出租车计价器专业班级学生姓名:学号:指导教师:课程设计时间:1 设计任务及要求出租车计价器根据乘客乘坐汽车行驶距离和等候时间的多少进行计价,并在行程中同步显示车费值。

从起步开始,行程3公里内,且等待累计时间2分钟内,起步费10元;3公里以外以每公里1.6元计费,等待累计时间2分钟外以每分钟1.5元计费。

并能显示行驶公里数、等待累计时间、总费用。

设计的主要技术指标:(1)计价范围:0—999.9元计价分辨率:0.1元(2)计程范围:0—99公里计程分辨率:1公里(3)计时范围:0—59分计时分辨率:1分本次设计中假设出租车的速度传感器具有出租车每行驶1Km提供1000个脉冲信号的特性。

当行驶速度小于等于6KM/h时为等待。

本设计的最终任务是显示出租车的等待时间和行驶里程,并计算出所需费用。

根据要求需要进行如下分工,首先要有一个分频模块(FPQ)产生系统工作用的基准信号1HZ,供系统中的有关模块计时用。

其次要有一个判断等待与否的模块(DDPB),再者就是要有计时和计程模块(DDSJ和LCJS),最后要有计费模块和显示译码模块(JFZ和YIMA)。

2设计原理及总体框图(1)设计总体框图图1总设计框图(2)设计总原理图图2设计总原理图设计总原理:测控FPGA芯片通过采集速度传感器脉冲信号WCLK进行行驶里程计算,利用外部脉冲信号CLK1产生标准时钟信号,用来计算等待时间,最后根据行驶里程、等待时间来计算计价值。

并用译码电路显示行驶里程、等待时间和计价值。

3 程序设计1.VHDL语言简单介绍VHDL语言(VHSIC Hardware Description Language,甚高速集成电路硬件描述语言)是一种设计、仿真、综合的标准硬件描述语言,是对可编程逻辑器件进行开发与设计的重要工具,其优点是:支持自上而下和基于库的设计,支持范围广,具有多层次描述系统硬件功能的能力。

出租车计价器设计报告

出租车计价器设计

出租车计价器设计

3. 设计实现 该设计内容可分为分频模块,控制模块,计量模块和显示模块 设计一个出租车计费器,具有行车里程计费、等候时间计费以及起步价三部分,用数码管 显示行驶里程 行车里程单价1元/公里,等候时间大于五分钟后单价1元/1分钟,起价5元(4公里起价 ) 行车里程的计费电路将汽车行驶的里程数转换成与之成正比的脉冲数,然后由计数译码电 路转换成收费金额,实验中以一个脉冲模拟汽车前进十米,则每100个脉冲表示1公里,然 后用BCD码比例乘法器将里程脉冲乘以每公里单价的比例系数,比例系数可由开关预置

例如单价是1元/公里,则脉冲当量为w0.01元/脉冲

出租车计价器设计

用LED显示行驶公里数,两个数码管显示收费金额 硬件设计 1、 主控制器:选择一个合适的微控制器作为系统整体的主控制模块 2、 里程表接口:设计电路接受和处理来自出租车里程表的信号来获取行驶里程 3、 等待时间计数器:使用定时器来测量为顾客停留的等待时间 4、 显示模块:选择LED数码管用于实时显示行驶的里程和费用 软件设计 1、 里程和等待时间费用计算:编写程序来实现里程表和等待时间测量器计算费用。对应 不同时间以及不同里程段,应用不同的计费规则 2、 显示驱动:编写程序驱动显示模块进行实时更新

随着城市旅游业的发展,出租车行业已成为城市的窗口,象征着一个城市的文明程度

出租车计价器设计

随着EDA技术的高速发展,电子系统的设计技术发生了深刻的变化,大 规模可编程逻辑器件CPLD/FPGA的出现,给设计人员带来了诸多方便。 利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。本次课程设计采用FPGA作为控制芯片,其中只需控制 FPGA中的RAM的状态即可。FPGA芯片可以重复使用,其原因是内容逻辑 关系会在断电后自动消失。4

出租车自动计费器课程设计

出租车自动计费器课程设计一、课程目标知识目标:1. 学生能够理解出租车自动计费器的基本工作原理,掌握其计算方法;2. 学生能够运用所学的数学知识,对出租车计费器进行简单的故障分析与计算;3. 学生掌握并能够解释与出租车计费相关的名词,如起步价、里程价、时间价等。

技能目标:1. 学生能够运用编程思维,设计一个简单的出租车自动计费程序;2. 学生能够运用数学知识,解决实际生活中的出租车计费问题;3. 学生能够通过小组合作,共同完成一个具有实际应用价值的计费器设计项目。

情感态度价值观目标:1. 学生培养对数学学科的兴趣,认识到数学知识在实际生活中的应用价值;2. 学生在小组合作中学会沟通、协作,培养团队精神;3. 学生能够关注社会热点问题,将所学知识与实际生活相结合,提高解决问题的能力。

课程性质:本课程为信息技术与数学学科的融合课程,注重培养学生的实践操作能力和创新思维。

学生特点:六年级学生已具备一定的数学知识基础和逻辑思维能力,对新鲜事物充满好奇,具备初步的编程能力。

教学要求:结合学生的特点,注重理论与实践相结合,充分调动学生的积极性,培养其动手操作能力和团队协作能力。

通过课程学习,使学生在掌握知识的基础上,提高解决实际问题的能力。

二、教学内容1. 理论知识:- 了解出租车自动计费器的基本构成及工作原理;- 学习计费器涉及的数学知识,如里程计算、时间计算、总价计算等;- 掌握与出租车计费相关的名词概念,如起步价、里程价、时间价等。

2. 实践操作:- 设计并编写一个简单的出租车自动计费程序;- 分析并解决实际生活中的出租车计费问题;- 小组合作,完成一个具有实际应用价值的计费器设计项目。

3. 教学大纲:- 第一课时:介绍出租车自动计费器的基本构成、工作原理及相关数学知识;- 第二课时:学习起步价、里程价、时间价的计算方法,并进行实际案例分析;- 第三课时:指导学生编写简单的出租车自动计费程序,并进行调试;- 第四课时:小组合作,完成计费器设计项目,展示成果。

数字电路课程设计报告 出租车计价器

五邑大学数字电路课程设计报告题目:出租车计价器院系信息工程学院专业通信工程学号学生姓名指导教师报告题目:出租车计价器一、题目的要求和意义题目要求:租车计价器使用中小型集成电路和门电路设计出租车计价器要求完成以下功能●使用555定时器产生一个20ms的周期信号作为时钟信号。

●每1s的时间代表行驶1公里,每公里的收费为2元。

●有开始计价的按键和停止计价的按键。

●使用两位数码管动态显示所需收的费用,单位为元。

出租车计价器的设计任务分解成时钟模块、计时显示模块这样两个部分组成,如图1-1所示。

图1-1 出租车计价器框图我负责的是第二部分的即使显示模块。

系统总功能为:第一部分分别产生1s的计数信号和20ms扫频信号。

第二部分接收计数信号,数码管从0开始计数,每秒2的累加。

系统有暂停和复位功能。

意义:随着社会的进步以及人们生活水平的日益提高都促使交通工具的不断变化,无论是在大城市或是中小城市越来越多的出租车公司不断的出现。

出租车的出现方便了人们的生活,对于现在快节奏生活方式的人们来说出租车无疑是最好的交通工具。

那么其收费的方式自然而然就被给予关注,比如收费标准以及行驶里程等。

这时出租车计价器就在乘客和司机之间充当一个重要的角色了。

出租车计价器是乘客与司机双方的交易准则,它是出租车行业发展的重要标志,是租车中最重要的工具。

它关系着交易双方的利益。

具有良好性能的计价器无论是对广大出租车司机朋友还是乘客来说都是很必要的。

因此,汽车计价器的研究也是十分有一个应用价值的。

现在我们就利用中小型集成电路和门电路来设计一个性能可靠、精准度高的出租车计价器。

1.培养学生根据需要选学参考书,查阅手册,图表和文献资料的自学能力,通过独立思考﹑深入钻研有关问题,学会自己分析解决问题的方法。

2.利用所学过的知识,通过设计计算﹑元件选取﹑电路板制作调试等环节,初步掌握工程设计的技能。

3.掌握常用仪表的正确使用方法,学会简单电路的实验调试和整机指标测试方法,使学生巩固和加深对数字逻辑电路的理论知识,锻炼学生的动手能力。

出租车计价器-课程设计报告

软件学院课程设计报告课程题目出租车计价器班级集成13-4专业集成电路设计与集成系统学生学号指导教师(填写自己班的指导教师)年月日1.课程设计目的全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对常用的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

2.课程设计题目描述和要求2.1.课程设计题目描述①.实现计费功能,计费标准为:按行驶里程计费,起步价为7.0元,并在车行3km 后按2.2元/km 计费,当计费器达到或超过20元时,每公里加收50%的车费,车停止不计费。

②.现场模拟功能:以开关或按键模拟公里计数,能模拟汽车起动、停止、暂停等状态。

③.将车费和路程显示出来,各有一位小数。

2.2.总体设计思路框架2.3.课程设计题目要求①.设计正确,方案合理。

②.程序精炼,结构清晰。

③.设计报告含程序设计说明,用户使用说明,源程序清单及程序框图。

④.上机演示。

⑤.有详细的文档。

文档中包括设计思路、设计仿真程序、仿真结果及相应的分析与结论。

3.设计思想和设计内容3.1 出租车计费设计该出租车计费器按下开关S1后开始计费和计里程数,起步价是7元,行驶3公里,以后2.2元/公里。

并且设计选择模块,在车费超过20元每公里加收50%车费即3.3元/公里。

3.2 基本设计思想出租车计费器根据设计要求可初步分为3方面——显示、记里程数、记费。

之后再根据三方面分别设计模块。

1.显示模块。

一般计数器显示数字为1-F即16进制,而16进制不方便观看,所以在设计这一模块时我们将16进制改为10进制输出进而设计了译码模块。

2、里程模块。

设计要求对里程计数主要分为两个方面,计数以及公里数比较。

即3公里之内收7元,3公里之后20元(通过计算为9公里)以内每公里2.2元,9公里以外为每公里3.3元。

出租车计价器__毕业设计(完整版)

摘要现在各大中城市出租车行业都已普及自动计价器,所以计价器技术的发展已成定局,预计未来计价器市场很有前景。

计价器作为出租车的一个重要组成部分,关系着出租车司机和乘客双方利益,起着重要的作用,因此,具有良好性能的计价器对广大出租车司机朋友和乘客来说是很必要的。

但是现阶段出租车的计费系统功能有时候并不能满足出租车司机的意愿。

本课题是出租车计价器系统的设计。

重点是设计出租车计价器的实用性,并尽量使最后的成品接近于商品。

整个系统是以89S51单片机为中心,采用A44E霍尔传感器对轮胎转数进行计数,实现对出租车里程的测量,并最终计算出结果。

其中采用掉电存储芯片AT24C02使系统在掉电的时候对单价、里程等信息进行存储,人机交换界面采用的是LCD1602液晶屏显示,并且通过语音芯片进行播报。

本电路设计的出租车计价器不但能实现计价的功能,同时还能实现根据时钟芯片自动调整白天、黑天计价模式,能自动处理中途等待等功能。

关键词:单片机AT89S51;LCD1602;出租车计价器;霍尔传感器;AT24C02ABSTRACTAutomatic taximeter has been universal among Cities for now. The taximeter technology is a foregone conclusion already. So taximeter of cars is still potential at next generation. As an important component taximeter is not only the interests of taxi drivers but also the passengers, so it has played an important role. The good performed taximeter is necessary for the public. The current taxi billing systems don’t meet the wishes of people. In this article we talk about various designs of taximeter system.The point is to design the practicality of the taximeter and as far as possible to make the final finished product close to commodities. The whole system is based on single-chip 89S51 and use a hall-sensor A44E to count the number of revolutions. In this way we can achieve the statistics of the taxi mileage and give out the final results. In this design we use AT24C02 to store the price, mileage and other information when the power is down. The man-machine interface of the exchange is LCD1602 screen, and through the voice chip broadcasts. This circuit design can not only realize the meter taxi valuation function, but also can realize the automatic adjustment according to the clock chips during the day, dark pricing mode, it can automatic processing midway waiting for function. Keywords: single-chip AT89S51; LCD1602; Taximeter; Hall sensor; AT24C02目录摘要 (I)ABSTRACT ....................................................................................... I I 1 绪论. (1)1.1 国内外出租车计价器的研究现状 (1)1.2 国内外出租车计价器的发展趋势 (2)1.3 本课题的研究目的及意义 (2)2 出租车计价器的方案论证 (4)2.1 出租车计价器的功能要求 (4)2.2 方案论证与比较 (5)3 出租车计价器的硬件设计 (7)3.1 单片机的介绍 (7)3.2 单片机最小系统 (11)3.3 里程计算模块的设计 (13)3.4 显示模块设计 (16)3.5 语音模块的设计 (18)3.6 掉电存储电路的设计 (21)3.7 按键电路的设计 (23)3.8 时钟电路的设计 (24)4 出租车计价器的软件设计 (27)4.1 模块介绍 (27)4.2 主程序模块 (27)4.3 里程计数中断程序 (28)4.3 定时中断服务程序 (29)4.4 中途等待服务程序 (30)4.5 显示服务子程序 (31)4.6 键盘服务程序 (33)5 系统调试 (34)5.1 软件调试 (34)5.2 里程计价测试 (35)5.2 掉电存储测试 (37)结论与展望 (38)可行性分析报告 (39)参考文献 (40)致谢 (41)附录一 (42)附录二 (43)附录三 (76)1 绪论出租车计价器是出租车营运收费的专用智能化仪表,随着电子技术的发展,出租车计价器技术也在不断进步和提高。

出租车计价器课程设计报告

HEFEI UNIVERSITY微机原理和接口技术课程设计系别电子信息和电气工程系班级 09自动化(1)班姓名梁超蒋业万完成时间 2011-12-28论文题目出租车计价器的设计设计类型导师姓名主要内容及目标1.要求:①里程显示、起步价(5公里后按里程计费);②等时收费;③复位具有的设计条件1.PC机一台,EL教学实验箱一台及汇编程序;计划学生数及任务3人(1):明确课题对程序功能,运算精度等方面的要求及硬件条件(2):把复杂问题分解为若干模块,确定各模块处理方法,画出流程图。

(3):存储器资源分配(4):编制程序,根据流程图精心选择合适的指令和寻址方式来编制源程序(5):对程序进行汇编,调试和修改,直到程序运行结果正确为止。

计划设计进程(按课程设计周计算)第一周设计任务:(1):明确课题对程序功能,运算精度等方面的要求及硬件条件(2):把复杂问题分解为若干模块,确定各模块处理方法,画出流程图。

(3):存储器资源分配第二周设计任务:(4):编制程序,根据流程图精心选择合适的指令和寻址方式来编制源程序(5):对程序进行汇编,调试和修改,直到程序运行结果正确为止。

参考文献《微型计算机原理及接口技术》中国科技大学出版社吴秀清周荷琴编著《16-32位微型计算机技术及使用》清华大学出版社戴梅萼史嘉权编著<<汇编语言程序设计》南京大学出版社姚君遗编著《汇编语言程序设计教程》清华大学出版社杨记文编著《微型计算机原理及接口技术》实验指导书自动化专业微机原理课程设计任务书目录一、引言 (1)二、总体设计方案 (1)(一)、软硬件流程图 (2)(二)、源程序设计和硬件介绍 (5)2.1 8086最小系统模块 (5)2.2 芯片8255A (6)2.3 芯片8253 (7)2.4可编程控制芯片8259A (8)(三)、遇到的问题 (9)三、总结和体会 (10)四、参考文献: (10)附录 (11)一、引言汽车计价器是乘客和司机双方的交易准则,它是出租车行业发展的重要标志,是出租车中最重要的工具。

数电课设报告——出租车计价器

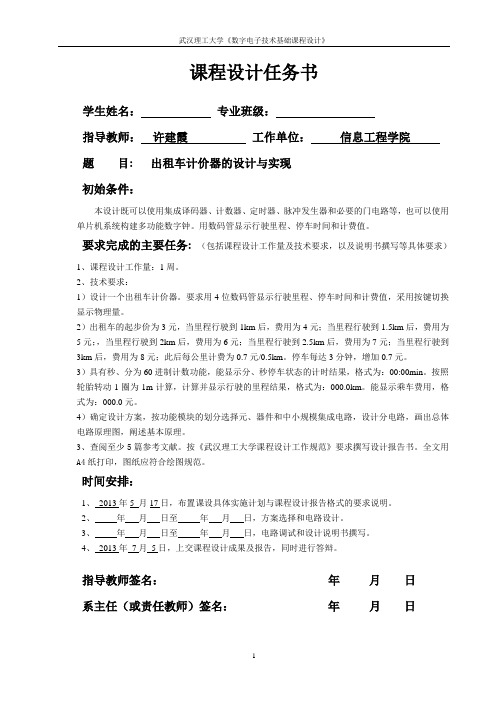

课程设计任务书学生姓名:专业班级:指导教师:许建霞工作单位:信息工程学院题目: 出租车计价器的设计与实现初始条件:本设计既可以使用集成译码器、计数器、定时器、脉冲发生器和必要的门电路等,也可以使用单片机系统构建多功能数字钟。

用数码管显示行驶里程、停车时间和计费值。

要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1周。

2、技术要求:1)设计一个出租车计价器。

要求用4位数码管显示行驶里程、停车时间和计费值,采用按键切换显示物理量。

2)出租车的起步价为3元,当里程行驶到1km后,费用为4元;当里程行驶到1.5km后,费用为5元;,当里程行驶到2km后,费用为6元;当里程行驶到2.5km后,费用为7元;当里程行驶到3km后,费用为8元;此后每公里计费为0.7元/0.5km。

停车每达3分钟,增加0.7元。

3)具有秒、分为60进制计数功能,能显示分、秒停车状态的计时结果,格式为:00:00min。

按照轮胎转动1圈为1m计算,计算并显示行驶的里程结果,格式为:000.0km。

能显示乘车费用,格式为:000.0元。

4)确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出总体电路原理图,阐述基本原理。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:1、2013年5 月17日,布置课设具体实施计划与课程设计报告格式的要求说明。

2、年月日至年月日,方案选择和电路设计。

3、年月日至年月日,电路调试和设计说明书撰写。

4、2013年7月5日,上交课程设计成果及报告,同时进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1. 1 原理图的设计 (4)1.1方案的选择、比较 (4)1.1.1 方案一 (4)1.1.2 方案二 (5)1.1.3 方案比较选择 (6)1.2 方案二的说明及电路 (6)1.2.1 AT89S52单片机及最小系统 (6)1.2.2 振荡电路 (7)1.2.3 按键单元 (7)1.2.4 显示单元 (8)1.2.5 存储单元 (9)1.3 系统总程序 (10)1.3.1系统总程序 (10)1.3.2 行驶路程子程序 (11)1.3.3 等待时间子程序 (12)1.4主要电路图及工作原理 (14)2 仿真结果分析 (15)3 分析测试数据 (16)4收获、体会、建议 (17)5元器件清单 (18)5.1单片机主板BOM清单 (18)5.2 显示部分器件 (19)6 主要参考文献资料 (20)附录一 (22)附录二 (23)摘要随着生活水平的提高,人们已不再满足于衣食住的享受,出行的舒适已受到越来越多人的关注。

出租车自动计费器课程设计报告

电子课程设计——出租车自动计费器出租车自动计费器一、 设计任务与要求出租车自动计费器是根据客户用车的实际情况而自动显示用车费用的数字仪表。

仪表根据用车起价、行车里程两项求得用车的总费用,通过数码自动显示。

1. 设计一个自动计费器,具有行车里程计费,起价等部分。

用四位数码管显示总金额,最大金额是99.99。

2. 行车起价为8.00元,超过5公里为1.6元/公里(60公里每小时)二、总体框图模块功能与设计思路:计费的电路将汽车行驶的里程数转换成与之成正比的脉冲个数,在出租车转轴上加装传感器,以便获得“行驶里程信号”。

脉冲源为电路提供的脉冲的周期与行车里程正比。

起价部分电路通过脉冲源加在八百进制计数器上,在800个脉冲之前显示器一直显示0800,当八百进制计数器显示799时通过门电路控制使其停止计数(此时到达五公里)。

然后160进制计数有效,每计一个数,10000进制计数器也计一个数,显示器的数值加一。

三、器件选择与功能简介元器件名称数量备注555定时器 1 构成脉冲电路74LS190 8 十进制计数器74LS191 1 十六进制计数器单刀单掷开关 1 控制总电路行车里程 脉冲源 起价10000进制计数器脉冲源160进制计数800进制计数器显示器单刀双掷开关 1 控制10000进制的置数端非门 1 构成八百进制计数器或门 2 控制八百进制计数器停在799的位置七输入与门 1 当799时输出高电平,八百进制计数器不再计数四位数码显示器9 显示数字电阻 2 1个367ohm 1个4、7kohm电容 1 1个100uf 1个1 uf 电源电压vcc 1 5v二输入与门 1 控制800进制计数器到达799时,10000进制计数器开始计数74LS190逻辑符号 74LS191逻辑符号74ls190外接引线排列 74ls191外接引线排列74ls190时序图 74ls191时序图74ls190内部原理图 74ls191内部原理图74LS190是可预置数同步可逆加减十进制计数器,符号如图所示,它具有异步置数端LOAD,加减控制端D/U和计数控制端CTEN,为方便级联,设置了两个级联输出端RCO和MAX/MIN.;当加减控制端等于1时减计数,否则为加计数;当异步置数端等于0时置数,当计数控制段为1时禁止计数,为0时,四个触发器将在时钟上升沿开始计数;当计数器加计数,计数值为9或减计数,计数值为0时,MAX/MIN端输出与时钟周期相同的正脉冲,而RCO产生一个宽度为时钟低电平宽度的低电平,74LS191为四位二进制即十六进制同步加法计数器,其功能表与74LS190相同,如图所示输入输出CTEN LOAD D / U D C B A CPX O X d c b aX异步预置 O 1 O加计数 O 1 1减计数11XX 保持图.74LS190、191功能表555定时器555 芯片是定时器,,是一种将数字功能和模拟功能集为一体的中规模集成电路。

出租车计费器课程设计报告

目录一、设计任务与要求 (3)二、总框体图 (3)三、选择器件 (5)四、功能模块 (6)1、模块se (6)2、模块di (7)3、模块jifei (8)4、模块zh (11)5、模块xxx1 (15)6、模块div_clk (17)7、模块docode3_8 (18)五、总体设计电路图 (19)1、总体电路原理图 (19)2、管脚分配图 (20)3、电路仿真结果 (21)4、硬件验证 (21)六、设计心得 (23)出租车计费器一、设计任务与要求1. 能实现计费功能,计费标准为:按行驶里程收费,起步费为7.00元,并在3km后按2.20元/km计费,当计费器计费达到或超过20元时,每公里加收50%的车费,车停止不计费。

2、现场模拟功能:能模拟汽车启动、停止及暂停以及加速状态。

3、设计动态扫描电路:将车费和里程显示出来,各有两位小数。

二、总体框图1、设计思路: (1) 根据出租车计费原理,将出租车计费部分由5个计数器来完成分别为counterA,counterB,counterC,counterD,counterE。

①计数器A完成车费百位。

②计数器B完成车费十位和个位。

③计数器C完成车费角和分。

④计数器D完成计数到30(完成车费的起步价)。

⑤计数器E完成模拟实现车行驶100 m的功能。

(2)行驶过程中车费附加50%的功能:由比较器实现。

(3)车费的显示:由动态扫描电路来完成。

用专用模块来实现,完成数据的输入即动2、设计方案比较:方案一:采用数字电路控制。

其原理方框图如图1.21.2所示。

采用传感器件,输出脉冲信号,经过放大整形作为移位寄存器的脉冲,实现计价,但是考虑到这种电路过于简单,性能不够稳定,而且不能调节单价,也不能根据天气调节计费标准,电路不够实用,所以我们不予采用。

图1.2方案二:采用单片机控制。

利用单片机丰富的IO端口,及其控制的灵活性,实现基本的里程计价功能和价格调节、时钟显示功能。

出租车计价器课程设计报告书

单片机应用与模拟训练设计报告摘要本设计基于AT89SC51单片机。

霍尔传感器用于采集轮胎转数信息,外部中断0用于将霍尔传感器采集的信息输入单片机,从而实现出租车里程的计算。

对于中间等待要等红绿灯的,用计时器计时,将时间换算成里程进行计费;输出器件采用数码管,本设计采用两个四合一共阴极数码管输出里程和费用;此外,本设计还设计了一个状态指示器来指示仪表的工作状态和显示状态。

出租车计价器是出租车行业计费系统的核心,是出租车行业发展的重要标志。

一个好的计价器对乘客和出租车行业都是必要的。

关键词:仪表,单片机,霍尔传感器目录1概述41.1出租车计价器概述41.2单片机概述42总体方案设计62.1设计任务要求6设计任务6设计要求62.2设计的主要功能62.3方案选择72.3.1硬件设计方案72.3.2软件设计方案73硬件设计93.1 AT89S52单片机及最小系统93.2测距装置113.3按键单元和状态显示单元143.4数字显示单元154软件设计174.1系统主程序174.2数据处理子程序184.3等待时间计时子程序194.4键盘扫描子程序205 Proteus软件仿真216课程设计过程中遇到的问题227课程设计的经验23参考231、原始程序代码242.附系统示意图301概述1.1出租车计价器概述出租车已成为我国城市公共交通的重要组成部分,是现代城市必不可少的基础设施,是人们工作生活中不可或缺的交通工具。

出租车服务行业与出租车计价器密切相关,因为出租车必须安装出租车计价器才能投入运营。

出租车计价器是一种可以根据乘客的距离和等待时间计算价格,直接显示车费数值的计量器具。

计价器是出租汽车经营者与出租汽车消费者公平交易结算的工具,因此计价器计价的准确性直接关系到经营者和消费者的经济利益。

根据国家相关法律法规,出租车计价器是首批列入国家强制检定的工作计量器具之一,也是国家质量技术监督部门近年来重点加强的六大计量器具之一。

最新设计报告-出租车计价器

目录设计任务…………………………………………………………………………设计要求基本要求…………………………………………………………………………发挥部分…………………………………………………………………………完成要求…………………………………………………………………………报告正文摘要及关键词……………………………………………………………………一、方案论证与比较方案比较方案一……………………………………………………………………………………方案二………………………………………………………………………………方案的确定………………………………………………………………………二、工作原理框图及电路设计工作原理…………………………………………………………………………单元(功能)电路分析……………………………………………………………控制部分…………………………………………………………………………功能面板示意图…………………………………………………………………特色功能…………………………………………………………………………三、程序框图主流程图…………………………………………………………………………计费状态图………………………………………………………………………时间设置…………………………………………………………………………计费设置…………………………………………………………………………四、测试方法及结果指标测试…………………………………………………………………………设计与测试使用仪器……………………………………………………………测试数据…………………………………………………………………………误差分析及措施…………………………………………………………………参考文献…………………………………………………………………………源程序……………………………………………………………………………英文摘要…………………………………………………………………………附录一设计任务设计并制作一台出租车计价器二设计要求1 基本要求(1)不同情况具有不同的计费标准■白天■晚上■途中等待(>10min开始收费)(2)能够进行手动修改单价(3)具有数据复位功能(4)I/O口分配的简易要求■距离检测使用霍尔开关A44E■白天/晚上收费标准使用转换开关■数据清零开关■单价的调整(最好使用“+”和“-”键来控制)(5)数据输出 (采用LCM103)■单价输出2位■路程输出2位■总金额输出3位(6)按键■启动计时开关■数据复位开关(清零)■白天/晚上转换开关2 发挥部分■能够在掉电的情况下存储单价等数据■能够显示当前的系统时间■语音播报数据信息三完成要求■8月7日到8日两天。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

软件学院课程设计报告课程题目出租车计价器班级集成13-4专业集成电路设计与集成系统学生学号指导教师(填写自己班的指导教师)年月日1.课程设计目的全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对常用的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

2.课程设计题目描述和要求2.1.课程设计题目描述①.实现计费功能,计费标准为:按行驶里程计费,起步价为7.0元,并在车行3km 后按2.2元/km 计费,当计费器达到或超过20元时,每公里加收50%的车费,车停止不计费。

②.现场模拟功能:以开关或按键模拟公里计数,能模拟汽车起动、停止、暂停等状态。

③.将车费和路程显示出来,各有一位小数。

2.2.总体设计思路框架2.3.课程设计题目要求 ①.设计正确,方案合理。

②.程序精炼,结构清晰。

③.设计报告含程序设计说明,用户使用说明,源程序清单及程序框图。

④.上机演示。

⑤.有详细的文档。

文档中包括设计思路、设计仿真程序、仿真结果及相应的分析与结论。

3.设计思想和设计内容3.1 出租车计费设计该出租车计费器按下开关S1后开始计费和计里程数,起步价是7元,行驶3公里,以后2.2元/公里。

并且设计选择模块,在车费超过20元每公里加收50%车费即3.3元/公里。

3.2 基本设计思想出租车计费器根据设计要求可初步分为3方面——显示、记里程数、记费。

之后再根据三方面分别设计模块。

1.显示模块。

一般计数器显示数字为1-F即16进制,而16进制不方便观看,所以在设计这一模块时我们将16进制改为10进制输出进而设计了译码模块。

2、里程模块。

设计要求对里程计数主要分为两个方面,计数以及公里数比较。

即3公里之内收7元,3公里之后20元(通过计算为9公里)以内每公里2.2元,9公里以外为每公里3.3元。

所以,我们将里程模块分为里程计数模块以为比较模块。

3.计费模块。

计费模块同里程比较模块所以将两个模块合二为一,为价格计算模块。

4.Verilog代码4.1顶层模块module taxi(clk,stop,rst_n,time1,time2,time3,time4,seg1,seg2,seg3,seg4);input clk;input stop;input rst_n;output [6:0]time1;output [6:0]time2;output [6:0]time3;output [6:0]time4;output [6:0]seg1;output [6:0]seg2;output [6:0]seg3;output [6:0]seg4;wire clk_fp;wire [15:0] distance;wire [15:0] price;wire [15:0]distan_bcd;wire [15:0]price_bcd;fp my_fp(clk,clk_fp,rst_n,stop);distance_counter dis_counter(clk_fp,rst_n,stop,distance);price_counterprice_coun(clk_fp,rst_n,stop,price,distance);yimaqi distance_BCD(distance,distan_bcd,clk_fp);yimaqi price_BCD(price,price_bcd,clk_fp);dispaly_my aa(clk_fp,distan_bcd,seg1,seg2,seg3,seg4);dispaly_my bb(clk_fp,price_bcd,time1,time2,time3,time4);endmodule4.2分频模块module fp(clk,clk_fp,rst_n,stop);//50mhzinput clk;input rst_n;input stop;output clk_fp;reg [25:0] counter;reg clk_fp;always@(posedge clk or negedge rst_n or negedge stop) beginif(!rst_n)beginclk_fp<=1'd0;counter<=26'd0;endelse if(!stop)begincounter<=counter;endelsebeginif(counter==26'd49_999_999)beginclk_fp<=1'b1;counter<=1'b0;endelsebeginclk_fp<=1'b0;counter<=counter+1'b1;endendendendmodule4.3里程计算模块clk_fp,rst_n,stop,distance);input clk_fp;//1Sinput rst_n;input stop;output [15:0]distance;reg [15:0]distance;always@(posedge clk_fp or negedge rst_n) beginif(!rst_n)distance<=8'd0;else if(!stop)distance<=distance;elsedistance<=distance+5'd10;endendmodule4.4价格计算模块module price_counter(clk_fp,rst_n,stop,price,distance);input clk_fp;//1Sinput rst_n;input stop;input [15:0]distance;output [15:0]price;reg [15:0]price;always@(posedge clk_fp or negedge rst_n or negedge stop) beginif(!rst_n)price<=8'd0;else if(!stop)price<=price;elseif(distance<=30)price<=16'd70;else if(distance<=90&&30<distance)price<=price+16'd22;elseprice<=price+16'd33;endendmodule4.5译码模块module yimaqi(num_hex,BCD,clk_fp);input [15:0]num_hex;input clk_fp;output [15:0]BCD;reg [15:0]BCD;reg [3:0] yima [3:0];always@(posedge clk_fp)beginyima[0]<=(num_hex)%10;yima[1]<=( num_hex/10)%10;yima[2]<=(num_hex/100)%10;yima[3]<=(num_hex/1000)%10;BCD<={yima[3],yima[2],yima[1],yima[0]}; endendmodule4.6显示器模块clk_fp,BCD,seg1,seg2,seg3,seg4);input clk_fp;input [15:0] BCD;output [6:0]seg1;output [6:0]seg2;output [6:0]seg3;output [6:0]seg4;reg [7:0] seg1;reg [7:0] seg2;reg [7:0] seg3;reg [7:0] seg4;reg [3:0]shumaguan_aa[3:0];always shumaguan_aa[0]<=BCD[3:0]; always shumaguan_aa[1]<=BCD[7:4]; always shumaguan_aa[2]<=BCD[11:8]; always shumaguan_aa[3]<=BCD[15:12];parameter seg_num0=7'hC0,seg_num1=7'hF9,seg_num2=7'hA4,seg_num3=7'hB0,seg_num4=7'h99,seg_num5=7'h92,seg_num6=7'h82,seg_num7=7'hF8,seg_num8=7'h80,seg_num9=7'h90;always@(posedge clk_fp)begincase(shumaguan_aa[0])4'd0:seg1<=seg_num0;4'd1:seg1<=seg_num1;4'd2:seg1<=seg_num2;4'd3:seg1<=seg_num3;4'd4:seg1<=seg_num4;4'd5:seg1<=seg_num5;4'd6:seg1<=seg_num6;4'd7:seg1<=seg_num7;4'd8:seg1<=seg_num8;4'd9:seg1<=seg_num9;default:seg1<=seg_num0 ;endcasecase(shumaguan_aa[1])4'd0:seg2<=(seg_num0&7'b0111_1111);4'd1:seg2<=(seg_num1&7'b0111_1111);4'd2:seg2<=(seg_num2&7'b0111_1111);4'd3:seg2<=(seg_num3&7'b0111_1111);4'd4:seg2<=(seg_num4&7'b0111_1111);4'd5:seg2<=(seg_num5&7'b0111_1111);4'd6:seg2<=(seg_num6&7'b0111_1111);4'd7:seg2<=(seg_num7&7'b0111_1111);4'd8:seg2<=(seg_num8&7'b0111_1111);4'd9:seg2<=(seg_num9&7'b0111_1111);default:seg2<=(seg_num0&7'b0111_1111 ); endcasecase(shumaguan_aa[2])4'd0:seg3<=seg_num0;4'd1:seg3<=seg_num1;4'd2:seg3<=seg_num2;4'd3:seg3<=seg_num3;4'd4:seg3<=seg_num4;4'd5:seg3<=seg_num5;4'd6:seg3<=seg_num6;4'd7:seg3<=seg_num7;4'd8:seg3<=seg_num8;4'd9:seg3<=seg_num9;default:seg3<=seg_num1 ;endcasecase(shumaguan_aa[3])4'd0:seg4<=seg_num0;4'd1:seg4<=seg_num1;4'd2:seg4<=seg_num2;4'd3:seg4<=seg_num3;4'd4:seg4<=seg_num4;4'd5:seg4<=seg_num5;4'd6:seg4<=seg_num6;4'd7:seg4<=seg_num7;4'd8:seg4<=seg_num8;4'd9:seg4<=seg_num9;default:seg4<=seg_num0 ;endcaseendendmodule5.经验总结在这次设计过程中,我们遇到了很多问题,例如,在预置好起步价时,当里程超过基本里程时,价钱开始增加,在复位时出现了一些问题,还有在里程比较器和时间比较器中,最初比较器只用了一个只能比较一位二进制数,然而当里程大于10km或时间大于10分钟时比较器出现了问题,还有就是将超过的时间和里程转化为价钱时,仿真时出现了错误,而在所有问题中最主要问题是整个电路的连接问题。